## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

Date: Feb.26.2007

# RENESAS TECHNICAL UPDATE

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan RenesasTechnology Corp.

| Product<br>Category   | MPU&MCU                                                                               |         | Document<br>No.         | TN-16C-A163A/E         | Rev. | 1.00 |

|-----------------------|---------------------------------------------------------------------------------------|---------|-------------------------|------------------------|------|------|

| Title                 | M32C/87 Group Document Revision for UART5 and UART6 in Serial interfaces (Serial I/O) |         | Information<br>Category | Technical Notification |      |      |

| Applicable<br>Product | M32C/87 Group                                                                         | Lot No. | Reference<br>Document   |                        |      |      |

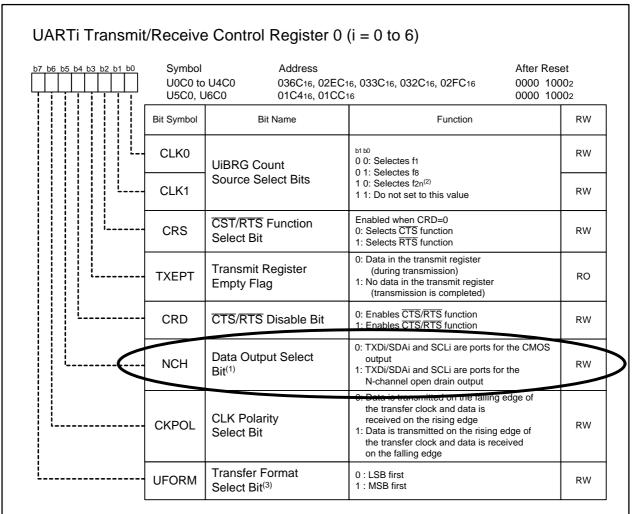

The description of the UiC0 register (UARTi Transmit/Receive Control Register 0) (i = 0 to 6) has been revised. When using the subject documents, please pay attention to the changes.

### 1. Subject Documents

M32C/87 Group Hardware Manual Rev.0.20 M32C/87 Group (M32C/87, M32C/87A, M32C/87B) Hardware Manual Rev.1.00

#### 2. Corrections

Refer to the following page in the subject documents.

M32C/87 Group Hardware Manual Rev.0.20 Page 196 (Figure 16.7) U0C0 to U6C0 registers

M32C/87 Group (M32C/87, M32C/87A, M32C/87B) Hardware Manual Rev.1.00 Page 200 (Figure 17.7) U0C0 to U6C0 registers

Rev.1.00 is used as an example for corrections shown in the following pages.

Date: Feb.26.2007 RENESAS TECHNICAL UPDATE TN-16C-A163A/E

M32C/87 Group (M32C/87, M32C/87A, M32C/87B) Hardware Manual Rev.1.00 Page 200

UiC0 register (UARTi Transmit/Receive Control Register 0) (i = 0 to 6) (Before)

#### NOTES:

Deleted 1. P70/TXD2 and P71/SCL2 are ports for the N-channel open drain output, but not for the CMOS output. This is used as the TXDi port only in UART5 and UART6.

2. The CNT3 to CNT0 bits in the TCSPR register select no division (n = 0) or divide-by-2n (n = 1 to 15).

Figure 17.7 U0C0 to U6C0 Registers

<sup>3.</sup> The UFORM bit setting is enabled when the SMD2 to SMD0 bits in the UiMR register are set to "0012" (clock synchronous serial I/O mode) or "1012" (UART mode, 8-bit transfer data). Set the UFORM bit to "1" when setting the SMD2 to SMD0 bits to "0102" (I2C mode), or to "0" when setting them to "1002" (UART mode, 7-bit transfer data) or "1102" (UART mode, 9-bit transfer data).

Date: Feb.26.2007 RENESAS TECHNICAL UPDATE TN-16C-A163A/E UiC0 register (UARTi Transmit/Receive Control Register 0) (i = 0 to 6) (After) UARTi Transmit/Receive Control Register 0 (i = 0 to 6) Symbol Address After Reset b7 b6 b5 b4 b3 b2 b1 b0 U0C0 to U4C0 036C16, 02EC16, 033C16, 032C16, 02FC16 0000 10002 U5C0, U6C0 01C416, 01CC16 0000 10002 Bit Symbol Bit Name Function RW CLK<sub>0</sub> RW 0 0: Selectes f1 **UiBRG Count** 0 1: Selectes f8 Source Select Bit 1 0: Selectes f2n(2) CLK1 RW 1 1: Do not set to this value Enabled when CRD=0 CST/RTS Function **CRS** 0: Selects CTS function RW Select Bit 1: Selects RTS function 0: Data in the transmit register Transmit Register (during transmission) **TXEPT** RO 1: No data in the transmit register **Empty Flag** (transmission is completed) 0: Enables CTS/RTS function **CTS/RTS** Disable Bit **CRD** RW : Enables CTS/RTS function 0: TXDi/SDAi and SCLi are ports for the CMOS **Data Output Select** NCH RW Bit(1)(4) 1: TXDi/SDAi and SCLi are ports for the N-channel open drain output of the transfer clock and data is **CLK Polarity** received on the rising edge **CKPOL** RW Select Bit 1: Data is transmitted on the rising edge of the transfer clock and data is received on the falling edge Transfer Format 0: LSB first **UFORM** RW Select Bit(3) 1: MSB first NOTES 1. P70/TXD2 and P71/SCL2 are ports for the N-channel open drain output, but not for the CMOS output. NT0 hits in the TCSPR register select no division (n = 0) or divide-by 3. The UFORM bit setting is enabled when the SMD2 to SMD0 bits in the UiMR register are set to "0012" (clock synchronous serial I/O mode) or "1012" (UART mode, 8-bit transfer data). Set the UFORM bit to "1" when setting the SMD2 to SMD0 bits to "0102" (I<sup>2</sup>C mode), or to "0" when bit transfer data) or "1102" (UART mode, 9-bit transfer data).

Figure 17.7 U0C0 to U6C0 Registers

4. This bit is reserved in UART5 and UART6. Set to "0"