発行日:2017年12月5日

# **RENESAS TECHNICAL UPDATE**

〒135-0061 東京都江東区豊洲 3-2-24 豊洲フォレシア ルネサス エレクトロニクス株式会社

問合せ窓口 http://japan.renesas.com/contact/

E-mail: csc@renesas.com

| 製   | 品分類   | MPU & MCU                                | 発行番号   | TN-RX*-A | 182A/J                                                                    | Rev. | 第1版 |  |

|-----|-------|------------------------------------------|--------|----------|---------------------------------------------------------------------------|------|-----|--|

| 題名  |       | グループ、RX651 グループ<br>- ズマニュアル ハードウェア編の誤記訂] | 情報分類   | 技術情報     |                                                                           |      |     |  |

| 適   |       |                                          | 対象ロット等 |          |                                                                           |      |     |  |

| 用製品 | RX65N | RX65N グループ、RX651 グループ                    | 全ロット   | 関連資料     | RX65N グループ、RX651 グループ<br>ユーザーズマニュアル ハードウェア編<br>Rev.2.10 (R01UH0590JJ0210) |      |     |  |

RX65N グループ、RX651 グループ ユーザーズマニュアル ハードウェア編 Rev.2.10 において、誤記がありましたので、以下の通り訂正いたします。

| No. |        | 章                | 訂正内容                                           |  |  |  |  |  |  |  |

|-----|--------|------------------|------------------------------------------------|--|--|--|--|--|--|--|

| 1   | 1章  概要 |                  | 「表 1.5 機能別端子一覧(177 ピン TFLGA, 176 ピン LFBGA)」、   |  |  |  |  |  |  |  |

|     |        |                  | 「表 1.6 機能別端子一覧(176 ピン LFQFP)」の機能記載抜けの追記および誤記訂正 |  |  |  |  |  |  |  |

| 2   | 25 章   | ポートアウトプットイネーブル 3 | 「MTU6 端子選択レジスタ(M6SELR)」の追記                     |  |  |  |  |  |  |  |

|     |        | (POE3a)          |                                                |  |  |  |  |  |  |  |

| 3   | 60 章   | 電気的特性            | 「表 60.46 12 ビット A/D (ユニット 0)変換特性」の誤記訂正         |  |  |  |  |  |  |  |

#### 1. 1.5 ピン配置図

• 「表 1.5 機能別端子一覧(177 ピン TFLGA, 176 ピン LFBGA)」において、機能の記載抜けおよび誤記がありましたので、以下の通り訂正いたします。

# 【変更前】

発行日:2017年12月5日

#### 表 1.5 機能別端子一覧(177 ピン TFLGA, 176 ピン LFBGA)

| ピン<br>番号<br>177 ピン<br>TFLGA<br>176 ピン<br>LFBGA | 電源<br>クロック<br>システム<br>制御 | l/O ポート | バス<br>EXDMAC<br>SDRAMC | タイマ<br>(MTU,<br>TPU, TMR,<br>PPG, RTC,<br>CMTW,<br>POE, CAC) | 通信<br>(ETHERC,<br>SCI, RSPI,<br>RIIC, CAN,<br>USB)            | メモリ I/F<br>カメラ I/F<br>(QSPI,<br>SDHI,<br>SDSI,<br>MMCIF,<br>PDC) | GLCDC           | 割り込み  | A/D<br>D/A |  |

|------------------------------------------------|--------------------------|---------|------------------------|--------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|-----------------|-------|------------|--|

|                                                | ~省略~                     |         |                        |                                                              |                                                               |                                                                  |                 |       |            |  |

| M8                                             |                          | P55     | D0[A0/D0]/<br>EDREQ0   | MTIOC4D/<br>TMO3                                             | ET0_EXOU<br>T/TXD7/<br>SMOSI7/<br>SSDA7/<br>MISOC-B/<br>CRX1  |                                                                  | LCD_DATA<br>5-A | IRQ10 |            |  |

| ~省略~                                           |                          |         |                        |                                                              |                                                               |                                                                  |                 |       |            |  |

| N8                                             |                          | P54     | D1[A1/D1]/<br>EDACK0   | MTIOC4B/<br>TMCI1                                            | ET0_LINKS<br>TA/CTS2#/<br>RTS2#/<br>SS2#/<br>MOSIC-B/<br>CTX1 |                                                                  | LCD_DATA<br>6-A |       |            |  |

|                                                |                          |         |                        | ~省                                                           | ]略~                                                           |                                                                  |                 |       |            |  |

| P5                                             | VSS_USB                  |         |                        |                                                              |                                                               |                                                                  |                 |       |            |  |

| P6                                             | VCC_USB                  |         |                        | 1                                                            |                                                               |                                                                  |                 |       |            |  |

|                                                | ~省略~                     |         |                        |                                                              |                                                               |                                                                  |                 |       |            |  |

### 【変更後】

# 表 1.5 機能別端子一覧(177 ピン TFLGA, 176 ピン LFBGA)

| ピン<br>番号<br>177 ピン<br>TFLGA<br>176 ピン<br>LFBGA | 電源<br>クロック<br>システム<br>制御 | l/Oポート   | バス<br>EXDMAC<br>SDRAMC         | タイマ<br>(MTU,<br>TPU, TMR,<br>PPG, RTC,<br>CMTW,<br>POE, CAC) | 通信<br>(ETHERC,<br>SCI, RSPI,<br>RIIC, CAN,<br>USB)            | メモリ I/F<br>カメラ I/F<br>(QSPI,<br>SDHI,<br>SDSI,<br>MMCIF,<br>PDC) | GLCDC           | 割り込み     | A/D<br>D/A |  |

|------------------------------------------------|--------------------------|----------|--------------------------------|--------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|-----------------|----------|------------|--|

|                                                | ~省略~                     |          |                                |                                                              |                                                               |                                                                  |                 |          |            |  |

| M8                                             |                          | P55      | D0[A0/D0]/<br>EDREQ0/<br>WAIT# | MTIOC4D/<br>TMO3                                             | ET0_EXOU<br>T/TXD7/<br>SMOSI7/<br>SSDA7/<br>MISOC-B/<br>CRX1  |                                                                  | LCD_DATA<br>5-A | IRQ10    |            |  |

| ~省略~                                           |                          |          |                                |                                                              |                                                               |                                                                  |                 |          |            |  |

| N8                                             |                          | P54      | D1[A1/D1]/<br>EDACK0/<br>ALE   | MTIOC4B/<br>TMCI1                                            | ET0_LINKS<br>TA/CTS2#/<br>RTS2#/<br>SS2#/<br>MOSIC-B/<br>CTX1 |                                                                  | LCD_DATA<br>6-A |          |            |  |

|                                                | <u> </u>                 | <u> </u> | ·                              | ~省                                                           | `略~                                                           | <u> </u>                                                         | ·               | <u> </u> |            |  |

| P5                                             | VCC_USB                  |          |                                |                                                              |                                                               |                                                                  |                 |          |            |  |

| P6                                             | VSS_USB                  |          |                                | <u> </u>                                                     |                                                               |                                                                  |                 |          |            |  |

|                                                |                          |          |                                | ~省                                                           | 略~                                                            |                                                                  |                 |          |            |  |

• 「表 1.6 機能別端子一覧(176 ピン LFQFP)」において、機能の記載抜けがありましたので、以下の通り訂正いたします。

発行日:2017年12月5日

# 【変更前】

| ~省略~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ~省略~ |  |  |  |  |  |  |  |  |  |

| P55   D0[A0/D0]/ EDREQ0   MTIOC4D/ ET0_EXOU   LCD_DATA   IRQ10   T/TXD7/ SMOSI7/ SSDA7/ MISOC-B/ CRX1   IRQ10   ET0_EXOU   T/TXD7/ SAMOSIT/ SSDA7/ MISOC-B/ CRX1   IRQ10   I |      |  |  |  |  |  |  |  |  |  |

| P54   D1[A1/D1]/   MTIOC4B/   ET0_LINKS   LCD_DATA   6-A     FT0_LINKS   TA/CTS2#/   RTS2#/   SS2#/   MOSIC-B/   CTX1   ~省略~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |  |  |  |  |  |  |  |  |  |

# 【変更後】

| ピン<br>番号<br>176 ピン<br>LFQFP | 電源<br>クロック<br>システム<br>制御 | l/O ポート | バス<br>EXDMAC<br>SDRAMC         | タイマ<br>(MTU,<br>TPU, TMR,<br>PPG, RTC,<br>CMTW,<br>POE, CAC) | 通信<br>(ETHERC,<br>SCI, RSPI,<br>RIIC, CAN,<br>USB)            | メモリ I/F<br>カメラ I/F<br>(QSPI,<br>SDHI,<br>SDSI,<br>MMCIF,<br>PDC) | GLCDC           | 割り込み  | A/D<br>D/A |

|-----------------------------|--------------------------|---------|--------------------------------|--------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|-----------------|-------|------------|

| ~省略~                        |                          |         |                                |                                                              |                                                               |                                                                  |                 |       |            |

| 65                          |                          | P55     | D0[A0/D0]/<br>EDREQ0/<br>WAIT# | MTIOC4D/<br>TMO3                                             | ET0_EXOU<br>T/TXD7/<br>SMOSI7/<br>SSDA7/<br>MISOC-B/<br>CRX1  |                                                                  | LCD_DATA<br>5-A | IRQ10 |            |

| 66                          |                          | P54     | D1[A1/D1]/<br>EDACK0/<br>ALE   | MTIOC4B/<br>TMCI1                                            | ET0_LINKS<br>TA/CTS2#/<br>RTS2#/<br>SS2#/<br>MOSIC-B/<br>CTX1 |                                                                  | LCD_DATA<br>6-A |       |            |

#### 25. ポートアウトプットイネーブル 3 (POE3a)

「25.2 レジスタの説明」に、以下の通り"MTU6 端子選択レジスタ (M6SELR)"を追加します。

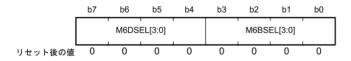

#### MTU6 端子選択レジスタ (M6SELR) 25.2.20

アドレス 0008 C4EAh

| ビット   | シンボル        | ビット名                   | 機能                                                                                                                             |             |  |  |  |  |

|-------|-------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|

| b3-b0 | M6BSEL[3:0] | MTU6-B(MTIOC6B)端子選択ビット | b3 b0<br>0000: PA5をMTIOC6B端子としてハイインピーダン<br>ス制御する<br>0001: PJ0をMTIOC6B端子としてハイインピーダン<br>ス制御する (注2)<br>上記以外は設定しないでください            | R/W<br>(注1) |  |  |  |  |

| b7-b4 | M6DSEL[3:0] | MTU6-D(MTIOC6D)端子選択ビット | b7 b4<br>0000: PA0をMTIOC6D端子としてハイインピーダン<br>ス制御する<br>0001: P84をMTIOC6D端子としてハイインピーダン<br>ス制御する <sup>(注2)</sup><br>上記以外は設定しないでください | R/W<br>(注1) |  |  |  |  |

注1. リセット後、1回のみ書き込み可能です。 注2. 176pin版のみ選択可能です。

M6SELR レジスタは、読み出し/書き込み可能な8ビットのレジスタで、ハイインピーダンス制御対象と なる MTU6-B/D の端子を選択します。

#### M6BSEL[3:0] ビット(MTU6-B(MTIOC6B)端子選択ビット)

ハイインピーダンス制御対象となる MTIOC6B 端子を選択します。

#### M6DSEL[3:0] ビット(MTU6-D(MTIOC6D)端子選択ビット)

ハイインピーダンス制御対象となる MTIOC6D 端子を選択します。

発行日:2017年12月5日

#### 3. 60.5 A/D 変換特性

「表 60.46 12 ビット A/D (ユニット 0)変換特性」において、変換時間特性を以下の通り訂正いたします。

#### 【変更前】

表 60.46 12 ビット A/D (ユニット 0)変換特性

条件: VCC = AVCC0 = AVCC1 = VCC\_USB = VBATT = 2.7~3.6V, 2.7V≦VREFH0≦AVCC0,

VSS = AVSS0 = AVSS1 = VREFL0 = VSS\_USB = 0V,

PCLKB = PCLKC = 1MHz~60MHz, Ta = Topr

|                                          | min                                                             | typ                                     | max | 単位  | 測定条件 |                                                               |  |  |

|------------------------------------------|-----------------------------------------------------------------|-----------------------------------------|-----|-----|------|---------------------------------------------------------------|--|--|

| 分解能                                      | 8                                                               | _                                       | 12  | ビット |      |                                                               |  |  |

| アナログ入力容量                                 | _                                                               | _                                       | 30  | pF  |      |                                                               |  |  |

| チャネル専用サンプル<br>ホールド回路使用時<br>(AN000~AN002) | 変換時間 (注 1)<br>(PCLKC = 60MHz 時)<br>許容信号源インピーダンス<br>max = 1.0 kΩ | 1.6<br>(0.4 + 0.25)<br><sup>(注 2)</sup> | -   | _   | μs   | ・ チャネル専用サンプル<br>ホールド回路のサンプリ<br>ング 24 ステート<br>・ サンプリング 15 ステート |  |  |

| ~省略~                                     |                                                                 |                                         |     |     |      |                                                               |  |  |

#### 【変更後】

表 60.46 12 ビット A/D (ユニット 0)変換特性

条件: VCC = AVCC0 = AVCC1 = VCC\_USB = VBATT = 2.7~3.6V, 2.7V≦VREFH0≦AVCC0,

VSS = AVSS0 = AVSS1 = VREFL0 = VSS\_USB = 0V,

PCLKB = PCLKC = 1MHz ~60MHz, Ta = Topr

|                                          | min                                                             | typ                                      | max | 単位  | 測定条件 |                                                             |  |

|------------------------------------------|-----------------------------------------------------------------|------------------------------------------|-----|-----|------|-------------------------------------------------------------|--|

| 分解能                                      | 8                                                               | _                                        | 12  | ビット |      |                                                             |  |

| アナログ入力容量                                 | _                                                               | _                                        | 30  | pF  |      |                                                             |  |

| チャネル専用サンプル<br>ホールド回路使用時<br>(AN000~AN002) | 変換時間 (注 1)<br>(PCLKC = 60MHz 時)<br>許容信号源インピーダンス<br>max = 1.0 kΩ | 1.06<br>(0.4 + 0.25)<br><sup>(注 2)</sup> | _   | _   | μs   | ・チャネル専用サンプル<br>ホールド回路のサンプリ<br>ング 24 ステート<br>・サンプリング 15 ステート |  |

| ~省略~                                     |                                                                 |                                          |     |     |      |                                                             |  |

以上

発行日:2017年12月5日