# **RENESAS TECHNICAL UPDATE**

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                      | Document<br>No.                             | TN-RX*-A041A/E        | Rev.                                        | 1.00                   |  |  |  |

|-----------------------|----------------------------------------------|---------------------------------------------|-----------------------|---------------------------------------------|------------------------|--|--|--|

| Title                 | Errata to RX210 Group Electrical Characteris | a to RX210 Group Electrical Characteristics |                       |                                             | Technical Notification |  |  |  |

| Applicable<br>Product | RX210 Group                                  | Lot No.<br>All                              | Reference<br>Document | RX210 Group User's N<br>Rev.1.10 (R01UH0037 |                        |  |  |  |

This document describes corrections to RX210 Group User's Manual: Hardware Rev.1.10.

Corrections are shown in red, and deletions are shown in strikethrough.

## • Page 1340 of 1420

Table 41.2 DC Characteristics (1) is corrected as follows:

Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V, T<sub>a</sub> = -40 to +105°C

|                     | Item                                                                                | Symbol | Min.       | Тур. | Max.      | Unit | Test<br>Conditions |

|---------------------|-------------------------------------------------------------------------------------|--------|------------|------|-----------|------|--------------------|

| Schmitt trigger     | RIIC input pin (except for SMBus, 5 V tolerant)                                     |        | VCC × 0.7  | _    | 5.8       |      |                    |

| input voltage       | Ports 12, 13, 16, and 17 (5 V tolerant)                                             | VIH    | VCC × 0.8  | _    | 5.8       |      |                    |

|                     | <del>Other pins</del> Ports 0, 14, 15, 2, 3, 4, 5, A, B, C, D,<br>E, H, J, and RES# | • IN   | VCC × 0.8  | -    | VCC + 0.3 | v    |                    |

|                     | RIIC input pin (except for SMBus)                                                   |        | -0.3       | _    | VCC × 0.3 | v    |                    |

|                     | Other than RIIC input pin                                                           | VIL    | -0.3       |      | VCC × 0.2 |      |                    |

|                     | RIIC input pin (except for SMBus)                                                   | ΔVT    | VCC × 0.05 | —    | —         |      |                    |

|                     | Other than RIIC input pin                                                           | ΔVT    | VCC × 0.1  | _    | —         |      |                    |

| Input level voltage | MD pin                                                                              |        | VCC × 0.9  |      | VCC + 0.3 |      |                    |

| (except for Schmitt | EXTAL, WAIT# <del>, XCIN</del>                                                      |        | VCC × 0.8  | _    | VCC + 0.3 |      |                    |

| trigger input pins) | RSPI input pins                                                                     | VIH    |            |      |           |      |                    |

|                     | D0 to D15                                                                           |        | VCC × 0.7  | _    | VCC + 0.3 |      |                    |

|                     | RIIC input pin (SMBus)                                                              |        | 2.1        | —    | VCC + 0.3 | V    |                    |

|                     | MD pin                                                                              |        | -0.3       | —    | VCC × 0.1 |      |                    |

|                     | EXTAL, WAIT# <del>, XCIN, RSPI input pins</del>                                     | V      | -0.3       | —    | VCC × 0.2 |      |                    |

|                     | D0 to D15                                                                           | VIL    | -0.3       | —    | VCC × 0.3 |      |                    |

|                     | RIIC input pin (SMBus)                                                              | 1      | -0.3       | —    | 0.8       |      |                    |

## Table 41.3 DC Characteristics (2) is corrected as follows:

Conditions: VCC = AVCC0 = 1.62 to 2.7 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a$  = -40 to +105°C

|                                            | Item                                                                                                                |                                                 | Symbol          | Min.       | Тур. | Max.      | Unit | Test<br>Conditions |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------|------------|------|-----------|------|--------------------|

| Schmitt trigger                            | Ports 12, 13, 16, and 17 (5 V tolerant)<br>Other pins Ports 0, 14, 15, 2, 3, 4, 5, A,<br>B, C, D, E, H, J, and RES# |                                                 |                 |            | _    | 5.8       |      |                    |

| input voltage                              |                                                                                                                     |                                                 | V <sub>IH</sub> | VCC × 0.8  | _    | VCC + 0.3 | -    |                    |

|                                            | All input pins                                                                                                      |                                                 | VIL             | -0.3       |      | VCC × 0.2 | v    |                    |

|                                            | <del>All input pins</del> Ports 0, 1,<br>2, 3, 4, 5, A, B, C, D, E,                                                 | VCC ≥ 2.2V                                      |                 | VCC × 0.05 | _    | _         |      |                    |

|                                            | H, and J                                                                                                            | VCC < 2.2V                                      | $\Delta V_{T}$  | VCC × 0.01 | -    | —         |      |                    |

|                                            | RES#                                                                                                                |                                                 | ] Î             | VCC × 0.1  | _    | _         |      |                    |

| Input level voltage                        | MD pin                                                                                                              |                                                 |                 | VCC × 0.9  | —    | VCC + 0.3 |      |                    |

| (except for Schmitt<br>trigger input pins) | EXTAL, WAIT# <del>, XCIN</del><br><del>RSPI input pins</del>                                                        |                                                 | V <sub>IH</sub> | VCC × 0.8  | -    | VCC + 0.3 |      |                    |

|                                            | D0 to D15                                                                                                           |                                                 | 1 ľ             | VCC × 0.7  | —    | VCC + 0.3 | V    |                    |

|                                            | MD pin                                                                                                              |                                                 |                 | -0.3       | -    | VCC × 0.1 | 1    |                    |

|                                            | EXTAL, WAIT# <del>, XCIN, RS</del>                                                                                  | EXTAL, WAIT# <del>, XCIN, RSPI input pins</del> |                 | -0.3       | —    | VCC × 0.2 | ]    |                    |

|                                            | D0 to D15                                                                                                           |                                                 |                 | -0.3       | —    | VCC × 0.3 |      |                    |

#### • Page 1342 of 1420

Table 41.6 DC Characteristics (5) is corrected as follows:

#### Before correction

|                            |                              | Item                     |                                                            |               | Symbol          | Тур.       | Unit | Test<br>Conditions |

|----------------------------|------------------------------|--------------------------|------------------------------------------------------------|---------------|-----------------|------------|------|--------------------|

| Current drawn <sup>1</sup> | High-speed<br>operating mode | Normal operating<br>mode | No peripheral<br>operating<br>All peripherals<br>operating | ICLK = 50 MHz | I <sub>cc</sub> | 10<br>28.5 | mA   | Ta = 25°C          |

|                            |                              | Sleep mode               |                                                            | ICLK = 50 MHz |                 | 7.5        |      |                    |

|                            |                              | All-module clock s       | top mode                                                   |               |                 | 6.7        |      |                    |

|                            |                              | Increase during B0       | GO <sup>*2</sup>                                           |               |                 | 25         |      |                    |

Note 1. Supply current values are with all output pins unloaded and all input pull-up MOSs in the off state.

BCLK, FCLK, and PCLK are ICLK divided by 64.

Note 2. This is the increase in current drawn if data are written to or erased from the ROM or the flash memory for data storage during program execution.

#### Corrections

| Γ | Item                       |                           |                       |                                                |               |                 | Тур. | Max. | Unit | Test<br>Conditions |

|---|----------------------------|---------------------------|-----------------------|------------------------------------------------|---------------|-----------------|------|------|------|--------------------|

| S | upply current <sup>1</sup> | High-speed operating mode | Normal operating mode | No peripheral operation <sup>*2</sup>          | ICLK = 50 MHz | I <sub>cc</sub> | 10   | _    |      |                    |

|   |                            |                           |                       | All peripheral operation: Normal <sup>*3</sup> | ICLK = 50 MHz |                 | 31.5 | —    |      |                    |

|   |                            |                           |                       | All peripheral operation: Max.* <sup>3</sup>   | ICLK = 50 MHz |                 | _    | 55   |      |                    |

|   |                            |                           |                       |                                                | ICLK = 50 MHz |                 | 7.5  |      | mA   |                    |

|   |                            |                           |                       | All peripheral operation: Normal               | ICLK = 50 MHz |                 | 17.5 | —    |      |                    |

|   |                            |                           | All-module clock      | stop mode                                      | ICLK = 50 MHz |                 | 6.7  |      |      |                    |

|   |                            |                           | Increase during B     | GO operation <sup>*4</sup>                     |               |                 | 25   | _    |      |                    |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequency is 100 MHz. BCLK, FCLK, and PCLK are set to divided by 64.

Note 3. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequency is 100 MHz. BCLK, FCLK, and PCLK are ICLK divided by 2.

Note 4. This is the increase if data is programmed to or erasing from the ROM or E2 DataFlash during program execution.

Table 41.7 DC Characteristics (6) is corrected as follows:

## Before correction

|                             |                                      | Item                  |                              |                | Symbol          | Тур.  | Unit | Test Conditions |

|-----------------------------|--------------------------------------|-----------------------|------------------------------|----------------|-----------------|-------|------|-----------------|

| Current drawn <sup>*1</sup> | Medium-speed                         | Normal operating      |                              | ICLK = 32 MHz  | I <sub>CC</sub> | 7.0   | mA   | Ta = 25°C       |

|                             | operating modes<br>A and B           | mode                  | operating                    | ICLK = 20 MHz  |                 | 6.0   |      |                 |

|                             |                                      |                       | All peripherals              | ICLK = 32 MHz  |                 | 22.5  |      |                 |

|                             |                                      |                       | operating                    | ICLK = 20 MHz  |                 | 16.5  |      |                 |

|                             |                                      | Sleep mode            |                              | ICLK = 32 MHz  |                 | 5.0   |      |                 |

|                             |                                      |                       |                              | ICLK = 20 MHz  |                 | 4.6   |      |                 |

|                             |                                      | All-module clock      | stop mode                    | ICLK = 32 MHz  |                 | 4.5   |      |                 |

|                             |                                      |                       |                              | ICLK = 20 MHz  |                 | 4.3   |      |                 |

|                             | Increase during<br>BGO <sup>*2</sup> | Medium-speed ope      | erating mode A               |                | 25              |       |      |                 |

|                             |                                      |                       | Medium-speed ope             | erating mode B |                 | 20    |      |                 |

|                             | Low-speed operating mode 1           | Normal operating mode | No peripheral<br>operating   | ICLK = 1 MHz   |                 | 0.68  |      |                 |

|                             |                                      |                       | All peripherals<br>operating | ICLK = 1 MHz   |                 | 2.4   |      |                 |

|                             |                                      | Sleep mode            |                              | ICLK = 1 MHz   |                 | 0.6   |      |                 |

|                             |                                      | All-module clock      | stop mode                    | ·              |                 | 0.58  |      |                 |

|                             | Low-speed operating mode 2           | Normal operating mode | No peripheral operating      | ICLK = 32 kHz  |                 | 0.024 |      |                 |

|                             |                                      |                       | All peripherals operating    | ICLK = 32 kHz  |                 | 0.05  |      |                 |

|                             |                                      | Sleep mode            | • •                          | ICLK = 32 kHz  | 1               | 0.02  |      |                 |

|                             |                                      | All-module clock      | stop mode                    | 1              |                 | 0.018 |      |                 |

Note 1. Supply current values are with all output pins unloaded and all input pull-up MOSs in the off state.

BCLK, FCLK, and PCLK are ICLK divided by 64. (However, divided by 32 when ICLK = 20 MHz.)

Note 2. This is the increase in current drawn if data are written to or erased from the ROM or the flash memory for data storage during program execution.

| Corrections   |                              |                             |                                                |               |                 |       |      |      |                   |

|---------------|------------------------------|-----------------------------|------------------------------------------------|---------------|-----------------|-------|------|------|-------------------|

|               |                              | Item                        |                                                |               | Symbol          | Тур.  | Max. | Unit | Test<br>Condition |

| upply current | Medium-speed                 | Normal operating            | No peripheral                                  | ICLK = 32 MHz | I <sub>cc</sub> | 7.0   | _    | mA   |                   |

|               | operating modes<br>1A and 1B | mode                        | operation <sup>*2</sup>                        | ICLK = 20 MHz |                 | 6.0   |      |      |                   |

|               |                              |                             | All peripheral                                 | ICLK = 32 MHz |                 | 26    | _    |      |                   |

|               |                              |                             | operation: Normal <sup>*3</sup>                | ICLK = 20 MHz |                 | 18.5  |      |      |                   |

|               |                              |                             | All peripheral                                 | ICLK = 32 MHz |                 | —     | 40   |      |                   |

|               |                              |                             | operation: Max.*3                              | ICLK = 20 MHz |                 | _     | 30   |      |                   |

|               |                              | Sleep mode                  | No peripheral                                  | ICLK = 32 MHz | _               | 5.0   | _    |      |                   |

|               |                              | -                           | operation                                      | ICLK = 20 MHz |                 | 4.6   | _    |      |                   |

|               |                              |                             | All peripheral                                 | ICLK = 32 MHz |                 | 15.5  |      |      |                   |

|               |                              |                             | operation: Normal                              | ICLK = 20 MHz |                 | 12    |      |      |                   |

|               |                              | All-module clock s          | top mode                                       | ICLK = 32 MHz | -               | 4.5   | _    |      |                   |

|               |                              |                             |                                                | ICLK = 20 MHz |                 | 4.3   |      |      |                   |

|               |                              | Increase during             | Medium-speed operating mode 1A                 |               |                 | 25    | _    |      |                   |

|               |                              | BGO operation <sup>*4</sup> | Medium-speed operation                         | ating mode 1B | -               | 20    |      |      |                   |

|               | Low-speed operating mode 1   | Normal operating mode       | No peripheral operation <sup>*5</sup>          | ICLK = 1 MHz  | -               | 0.68  |      |      |                   |

|               |                              |                             | All peripheral operation: Normal <sup>*6</sup> | ICLK = 1 MHz  |                 | 2.4   |      |      |                   |

|               |                              |                             | All peripheral operation: Max.*6               | ICLK = 1 MHz  |                 | _     | 7    |      |                   |

|               |                              | Sleep mode                  | No peripheral operation                        | ICLK = 1 MHz  |                 | 0.6   | _    |      |                   |

|               |                              |                             | All peripheral operation: Normal               | ICLK = 1 MHz  |                 | 2     |      |      |                   |

|               |                              | All-module clock s          | top mode                                       |               |                 | 0.58  |      |      |                   |

|               | Low-speed operating mode 2   | Normal operating mode       | No peripheral operation <sup>*7</sup>          | ICLK = 32 kHz |                 | 0.024 |      |      |                   |

|               |                              |                             | All peripheral operation: Normal <sup>*8</sup> | ICLK = 32 kHz |                 | 0.05  | _    |      |                   |

|               |                              |                             | All peripheral operation: Max. <sup>*8</sup>   | ICLK = 32 kHz |                 | _     | 3*9  |      |                   |

|               |                              | Sleep mode                  | No peripheral operation                        | ICLK = 32 kHz |                 | 0.02  |      |      |                   |

|               |                              |                             | All peripheral operation: Normal               | ICLK = 32 kHz |                 | 0.04  |      |      |                   |

|               |                              | All-module clock s          | top mode                                       |               | 1               | 0.018 | _    | 1    |                   |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequencies are 64 MHz and 40 MHz, respectively. BCLK, FCLK, and PCLK are set to divided by 64.

- Note 3. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequencies are 64 MHz and 40 MHz, respectively. BCLK, FCLK, and PCLK are ICLK divided by 1.

- Note 4. This is the increase if data is programmed to or erasing from the ROM or E2 DataFlash during program execution.

- Note 5. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is HOCO and the oscillation frequency is 32 MHz. BCLK, FCLK, and PCLK are set to divided by 64.

- Note 6. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is HOCO and the oscillation frequency is 32 MHz. BCLK, FCLK, and PCLK are ICLK divided by 1.

- Note 7. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is the sub oscillation circuit. BCLK, FCLK, and PCLK are set to divided by 64.

- Note 8. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is the sub oscillation circuit. BCLK, FCLK, and PCLK are ICLK divided by 1.

- Note 9. Value when the main clock continues oscillating at 12.5 MHz.

• Page 1348 of 1420

Table 41.10 DC Characteristics (9) is corrected as follows:

Conditions: VCC = AVCC0 = 1.62 to 5.5 V, VREFH = 1.8 to AVCC0, VREFH0 = 1.62 to AVCC0, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a = -40$  to  $+105^{\circ}$ C

|                                | Item                                              | Symbol             | Min. | Тур.                | Max.                 | Unit | Test<br>Conditions |

|--------------------------------|---------------------------------------------------|--------------------|------|---------------------|----------------------|------|--------------------|

| Analog power<br>supply current | During A/D conversion                             |                    | —    | <del>1.6</del> 1.0  | <del>3.0</del> 3.2   | mA   |                    |

| supply surrent                 | During D/A conversion (per channel) <sup>*1</sup> |                    | _    | 0.25                | <del>0.50</del> 0.75 |      |                    |

|                                | Temperature sensor                                | Alcc               | —    | 60                  | 200                  |      |                    |

|                                | Waiting for A/D, D/A conversion (all units)       |                    | _    | 0.2                 | <del>0.4</del> 5.0   | μA   |                    |

| Reference                      | During A/D conversion                             | I <sub>REFH,</sub> | —    | <del>0.01</del> 0.1 | <del>0.03</del> 0.2  | mA   |                    |

| power supply<br>current        | Waiting for A/D, D/A conversion (all units)       | I <sub>REFH0</sub> | _    | 0.2                 | 0.4                  | μA   |                    |

Note: • The values for A/D conversion apply when the sample and hold circuit is not in use.

Note 1. The reference power supply current is included in the power supply current value for D/A conversion.

• Pages 1348 and 1349 of 1420

Table 41.12 DC Characteristics (11) is corrected as follows:

Conditions: VCC = AVCC0 = 1.62 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V, T<sub>a</sub> = -40 to +105°C

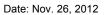

The ripple voltage must meet the allowable ripple frequency fr(VCC) within the range between the VCC upper limit (5.5 V) and lower limit (1.62 V). When VCC change exceeds VCC ±10%, the allowable voltage change rising/falling gradient dt/dVCC must be met.

| Item                                             | Symbol               | Min. | Тур. | Max. | Unit | Test Conditions                                              |

|--------------------------------------------------|----------------------|------|------|------|------|--------------------------------------------------------------|

| Allowable ripple frequency                       | f <sub>r (VCC)</sub> |      | _    | 10   | kHz  | Figure 41.18<br>VCC × 0.1 < V <sub>r(VCC)</sub> ≤ VCC × 0.2  |

|                                                  |                      | _    | —    | 1    | MHz  | Figure 41.18<br>VCC × 0.05 < V <sub>r(VCC)</sub> ≤ VCC × 0.1 |

|                                                  |                      | _    | —    | 10   | MHz  | Figure 41.18<br>V <sub>r(VCC)</sub> ≤ VCC × 0.05             |

| Allowable voltage change rising/falling gradient | dt/dVCC              | 1.0  | _    | —    | ms/V | When VCC change exceeds VCC ±10%                             |

Figure 41.9 Ripple Waveform is corrected as follows:

• Page 1353 of 1420

Table 41.24 BCLK Timing (3) is corrected as follows:

## Conditions: VCC = AVCC0 = 1.62 to 1.8 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,

fBCLK = up to 12 MHz (BCLK pin output frequency = up to 6 MHz),  $T_a = -40$  to +105°C

| Item                                           | Symbol            | Min.                   | Тур. | Max. | Unit | Test Conditions |

|------------------------------------------------|-------------------|------------------------|------|------|------|-----------------|

| BCLK pin output cycle time                     | t <sub>Bcyc</sub> | <del>166.7</del> 166.6 | —    | _    | ns   | Figure 41.10    |

| BCLK pin output high pulse width <sup>*1</sup> | t <sub>сн</sub>   | 42                     | —    |      | ns   |                 |

| BCLK pin output low pulse width <sup>*1</sup>  | t <sub>CL</sub>   | 42                     | —    | _    | ns   |                 |

| BCLK pin output rising time                    | t <sub>Cr</sub>   | —                      | —    | 35   | ns   |                 |

| BCLK pin output falling time                   | t <sub>Cf</sub>   | —                      | _    | 35   | ns   |                 |

Note: • Set high driving ability for the output port pin to be used for the BCLK pin function.

Note 1. When the EXTAL external clock input is used with divided by 1 (SCKCR.BCK[3:0] bits = 0000b and BCKCR.BCLKDIV bit = 0) to output from the BCLK pin, the above should be satisfied with a duty cycle of 45 to 55%.

Note 1 described above is also added to Table 41.22 BCLK Timing (1) and Table 41.23 BCLK Timing (2).

• Page 1354 of 1420

Sub-clock oscillation stabilization wait time is added to Table 41.25 Clock Timing.

Conditions: VCC = AVCC0 = 1.62 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a$  = -40 to +105°C

| Item                                                        | Symbol                | Min. | Тур. | Max. | Unit | Test Conditions |

|-------------------------------------------------------------|-----------------------|------|------|------|------|-----------------|

| Sub-clock oscillation stabilization wait time <sup>*5</sup> | t <sub>suboscwt</sub> | 4    |      |      | S    | Figure 41.19    |

## • Page 1364 of 1420

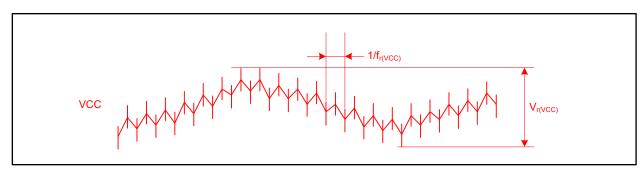

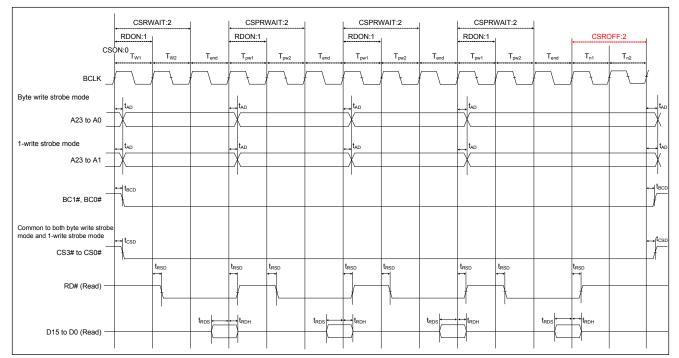

Description of CSROFF in Figure 41.26 External Bus Timing/Normal Read Cycle (Bus Clock Synchronized) is corrected as follows:

## • Page 1365 of 1420

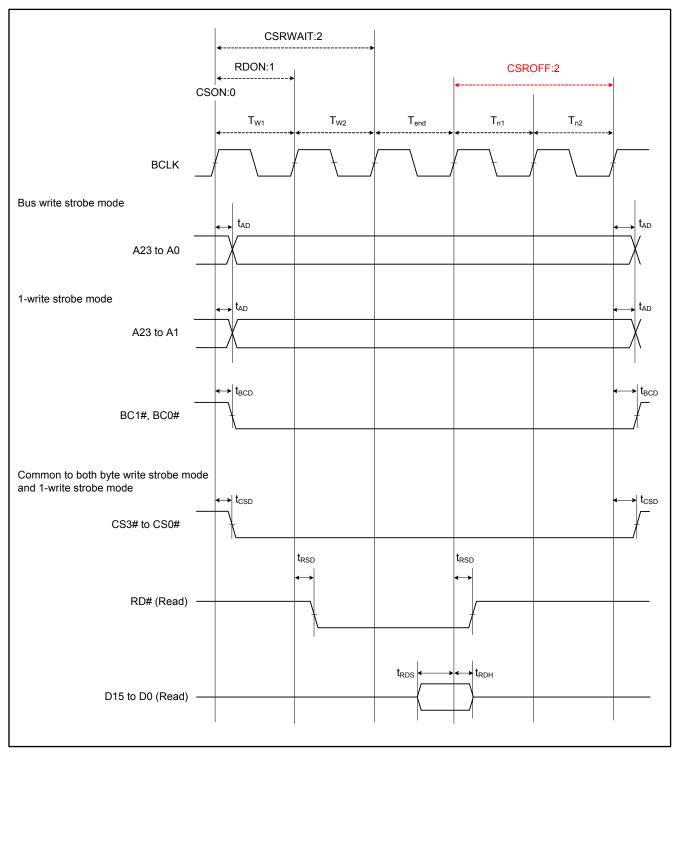

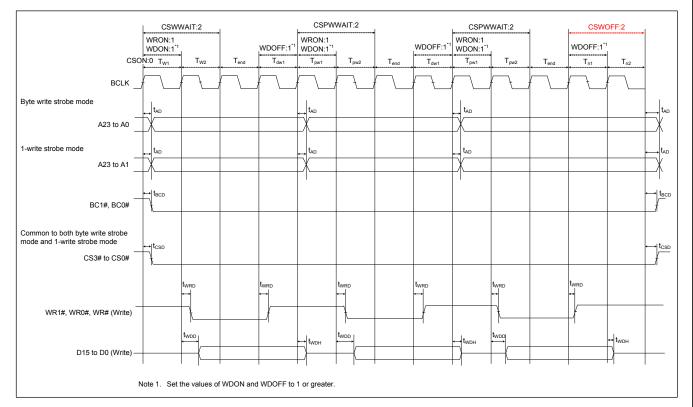

Description of CSWOFF in Figure 41.27 External Bus Timing/Normal Write Cycle (Bus Clock Synchronized) is corrected as follows:

## • Page 1366 of 1420

Description of CSROFF in Figure 41.28 External Bus Timing/Page Read Cycle (Bus Clock Synchronized) is corrected as follows:

Description of CSWOFF in Figure 41.29 External Bus Timing/Page Write Cycle (Bus Clock Synchronized) is corrected as follows:

#### • Page 1382 of 1420

Table 41.40 A/D Conversion Characteristics (1) is corrected as follows:

Conditions: VCC = AVCC0 = 2.7 to 5.5 V,  $\frac{VREFH}{VREFH} = 2.7 V \le VREFH0 = (AVCC0 - 0.9 V)$  to AVCC0<sup>\*4</sup>, VSS = AVSS0 = VREFL = VREFL0 = 0 V, fPCLKD = 1 to 50 MHz, T<sub>a</sub> = -40 to +105°C

|                                                                                  | Item                                                   | Min.                       | Тур.  | Max. | Unit | Test Conditions          |

|----------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------|-------|------|------|--------------------------|

| Resolution                                                                       |                                                        | _                          | _     | 12   | Bit  |                          |

| Conversion time <sup>*1</sup><br>(Operation at fPCLKD =<br>50 MHz) <sup>*3</sup> | Permissible signal source<br>impedance (Max.) = 0.5 kΩ | 1.0<br>(0.4) <sup>*2</sup> | —     | —    | μs   | Sampling in 20 states    |

| 50 WHZ)                                                                          | Permissible signal source<br>impedance (Max.) = 1 kΩ   | 1.1<br>(0.5) <sup>*2</sup> | —     | _    | ]    | Sampling in 25 states    |

|                                                                                  | Permissible signal source<br>impedance (Max.) = 5 kΩ   | 1.5<br>(0.9) <sup>*2</sup> | —     | —    | 1    | Sampling in 45 states    |

| Analog input capacitance                                                         |                                                        | —                          | _     | 30   | pF   |                          |

| Offset error                                                                     |                                                        |                            | .0.5  | ±4.5 | 1.00 | High-precision channel   |

|                                                                                  |                                                        | _                          | ±0.5  | ±7.5 | LSB  | Normal-precision channel |

| Full-scale error                                                                 |                                                        |                            | .0.75 | ±4.5 | 1.00 | High-precision channel   |

|                                                                                  |                                                        | —                          | ±0.75 | ±7.5 | LSB  | Normal-precision channel |

| Quantization error                                                               |                                                        | —                          | ±0.5  | —    | LSB  |                          |

| Absolute accuracy                                                                |                                                        | —                          | ±1.25 | ±5.0 | LSB  | High-precision channel   |

|                                                                                  |                                                        |                            | ±1.25 | ±8.0 | LSB  | Normal-precision channel |

| DNL differential nonlinearity error                                              |                                                        | —                          | ±1.0  | —    | LSB  |                          |

| INL integral nonlinearity e                                                      | rror                                                   | _                          | ±1.0  | ±3.0 | LSB  |                          |

Note: • PCLKD must be set to 40 MHz or lower when HOCO is to be selected as the A/D conversion clock. The characteristics apply when no pin functions other than A/D converter input are used. Absolute accuracy includes quantization errors. Offset error, fullscale error, DNL differential nonlinearity error, and INL integral nonlinearity error do not include quantization errors.

Note 1. The conversion time is the sum of the sampling time and the comparison time. As the test conditions, the number of sampling states is indicated.

Note 2. The value in parentheses indicates the sampling time.

Note 3. The lower-limit frequency of PCLKD is 1 MHz.

Note 4. When using the temperature sensor, use it when AVCC0 = VREFH0.

• Page 1383 of 1420

Table 41.43 A/D Conversion Characteristics (2) is corrected as follows:

Conditions: VCC = AVCC0 = 1.8 to 2.73.6 V, VREFH = VREFH0 = (AVCC0 - 0.9 V) to AVCC0, VREFH0 = 1.8 to 2.7 V<sup>\*4</sup>,

VSS = AVSS0 = VREFL = VREFL0 = 0 V, fPCLKD = 1 to 32 MHz,  $T_a$  = -40 to +105°C

|                                                                                  | Min.                                                      | Тур.                       | Max.  | Unit | Test Conditions |                       |

|----------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------|-------|------|-----------------|-----------------------|

| Resolution                                                                       |                                                           | _                          | _     | 12   | Bit             |                       |

| Conversion time <sup>*1</sup><br>(Operation at fPCLKD =<br>25 MHz) <sup>*3</sup> | Permissible signal source impedance (Max.) = 1 k $\Omega$ | 2.0<br>(0.8) <sup>*2</sup> | _     | —    |                 | Sampling in 20 states |

|                                                                                  | Permissible signal source impedance (Max.) = 5 k $\Omega$ | 2.2<br>(1.0) <sup>*2</sup> |       | —    | μs              | Sampling in 25 states |

| Analog input capacitance                                                         |                                                           | —                          |       | 30   | pF              |                       |

| Offset error                                                                     |                                                           | —                          | ±0.5  | ±7.5 | LSB             |                       |

| Full-scale error                                                                 |                                                           | —                          | ±1.25 | ±7.5 | LSB             |                       |

| Quantization error                                                               |                                                           | —                          | ±0.5  | _    | LSB             |                       |

| Absolute accuracy                                                                |                                                           | _                          | ±3.0  | ±8.0 | LSB             |                       |

| DNL differential nonlinearity error                                              |                                                           | —                          | ±1.25 | —    | LSB             |                       |

| INL integral nonlinearity e                                                      | error                                                     | _                          | ±1.5  | ±3.0 | LSB             |                       |

Note: • The characteristics apply when no pin functions other than A/D converter input are used. Absolute accuracy includes quantization errors. Offset error, full-scale error, DNL differential nonlinearity error, and INL integral nonlinearity error do not include quantization errors.

Note 1. The conversion time is the sum of the sampling time and the comparison time. As the test conditions, the number of sampling states is indicated.

Note 2. The value in parentheses indicates the sampling time.

Note 3. The lower-limit frequency of PCLKD is 1 MHz.

Note 4. When using the temperature sensor, use it when AVCC0 = VREFH0.

Table 41.44 A/D Conversion Characteristics (3) is corrected as follows:

#### Conditions: VCC = AVCC0 = 1.62 to 1.8 V, VREFH = VREFH0 = (AVCC0 - 0.9 V) to AVCC0,

VSS = AVSS0 = VREFL = VREFL0 = 0 V. fPCLKD = 1 to 16 MHz. T₂ = -40 to +105°C

| V33 - AV                                                                          | 350 = VREFL = VREFL0 = 0 V, fi                       |                              | 5 IVINZ, I <sub>a</sub> – -40 l | 0 + 105 C |      | 1                     |

|-----------------------------------------------------------------------------------|------------------------------------------------------|------------------------------|---------------------------------|-----------|------|-----------------------|

| Item                                                                              |                                                      | Min.                         | Тур.                            | Max.      | Unit | Test Conditions       |

| Resolution                                                                        |                                                      | —                            | —                               | 12        | Bit  |                       |

| Conversion time <sup>¬</sup><br>(Operation at fPCLKD =<br>12.5 MHz) <sup>*3</sup> | Permissible signal source<br>impedance (Max.) = 1 kΩ | 3.36<br>(0.96) <sup>*2</sup> | —                               | —         |      | Sampling in 12 states |

|                                                                                   | Permissible signal source<br>impedance (Max.) = 5 kΩ | 3.6<br>(1.2) <sup>*2</sup>   | —                               | _         | μs   | Sampling in 15 states |

| Analog input capacitance                                                          |                                                      | —                            | _                               | 30        | pF   |                       |

| Offset error                                                                      |                                                      | —                            | ±0.5                            | ±7.5      | LSB  |                       |

| Full-scale error                                                                  |                                                      | —                            | ±1.25                           | ±7.5      | LSB  |                       |

| Quantization error                                                                |                                                      | —                            | ±0.5                            | _         | LSB  |                       |

| Absolute accuracy                                                                 |                                                      | —                            | ±2.75                           | ±8.0      | LSB  |                       |

| DNL differential nonlinearity error                                               |                                                      | —                            | ±1.25                           | —         | LSB  |                       |

| INL integral nonlinearity e                                                       | rror                                                 | _                            | ±1.25                           | ±3.0      | LSB  |                       |

Note: • The characteristics apply when no pin functions other than A/D converter input are used. Absolute accuracy includes quantization errors. Offset error, full-scale error, DNL differential nonlinearity error, and INL integral nonlinearity error do not include quantization errors.

Note 1. The conversion time is the sum of the sampling time and the comparison time. As the test conditions, the number of sampling states is indicated.

Note 2. The value in parentheses indicates the sampling time.

Note 3. The lower-limit frequency of PCLKD is 1 MHz.

## • Page 1384 of 1420

Conditions in Table 41.47 Temperature Sensor Characteristics are corrected as follows:

Conditions: VCC = AVCC0 = VREFH0 = 1.8 to 5.5 V, VREFH = VREFH0 = (AVCC0 - 0.9 V) to AVCC0,

VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a$  = -40 to +105°C

## • Page 1391 of 1420

Table 41.53 ROM (Flash Memory for Code Storage) Characteristics (2): high-speed operating mode, medium-speed operating mode A is corrected as follows:

Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VREFH = VREFH0 = AVCC0, VSS = AVSS0 = VREFL = VREFL0 = 0 V Temperature range for the programming/erasure operation: T<sub>a</sub> = -40 to +105°C

| ltem                                                                            |           | Symbol             | FCLK                                          | ( = 4 MHz |       | FCLK                                          | FCLK = 32 MHz       |      |      |  |

|---------------------------------------------------------------------------------|-----------|--------------------|-----------------------------------------------|-----------|-------|-----------------------------------------------|---------------------|------|------|--|

| item                                                                            |           | Symbol             | Min.                                          | Тур.      | Max.  | Min.                                          | Тур.                | Max. | Unit |  |

| Programming time when                                                           | 2 bytes   | t <sub>P2</sub>    | —                                             | 0.52      | 4.8   | _                                             | <del>0.5</del> 0.19 | 2.5  |      |  |

| N <sub>PEC</sub> ≤ 100 times                                                    | 8 bytes   | t <sub>P8</sub>    | _                                             | 0.52      | 4.9   | —                                             | <del>0.5</del> 0.19 | 2.5  | ms   |  |

|                                                                                 | 128 bytes | t <sub>P128</sub>  | _                                             | 1.50      | 10.7  | _                                             | <del>1.0</del> 0.57 | 4.8  |      |  |

| Programming time when                                                           | 2 bytes   | t <sub>P2</sub>    | —                                             | 0.61      | 5.7   | —                                             | 0.23                | 3.0  |      |  |

| N <sub>PEC</sub> > 100 times                                                    | 8 bytes   | t <sub>P8</sub>    | —                                             | 0.61      | 6.2   | —                                             | 0.23                | 3.2  | ms   |  |

|                                                                                 | 128 bytes | t <sub>P128</sub>  | —                                             | 1.71      | 13.2  | —                                             | 0.65                | 6.0  |      |  |

| Erasure time when<br>N <sub>PEC</sub> ≤ 100 times                               | 2 Kbytes  | t <sub>E2K</sub>   | _                                             | 17.0      | 92.9  | —                                             | <del>16</del> 11.0  | 29   | ms   |  |

| Erasure time when<br>N <sub>PEC</sub> > 100 times 2 Kbytes                      |           | t <sub>E2K</sub>   | _                                             | 20.8      | 195.8 | _                                             | 13.5                | 60   | ms   |  |

| Suspend delay time during programming<br>(in programming/erasure priority mode) |           | t <sub>SPD</sub>   | -                                             | _         | 0.9   | _                                             | _                   | 0.8  | ms   |  |

| First suspend delay time of<br>programming (in suspend                          |           | t <sub>SPSD1</sub> | -                                             | _         | 220   | _                                             | —                   | 120  | μs   |  |

| Second suspend delay time during programming (in suspend priority mode)         |           | t <sub>SPSD2</sub> | _                                             |           | 0.9   | _                                             | —                   | 0.8  | ms   |  |

| Suspend delay time during erasing<br>(in programming/erasure priority mode)     |           | $t_{\text{SED}}$   | _                                             |           | 0.9   | _                                             | _                   | 0.8  | ms   |  |

| First suspend delay time during erasing<br>(in suspend priority mode)           |           | t <sub>SESD1</sub> | _                                             |           | 220   | _                                             | —                   | 120  | μs   |  |

| Second suspend delay time during erasing (in suspend priority mode)             |           | t <sub>SESD2</sub> | _                                             | _         | 0.9   | _                                             | _                   | 0.8  | ms   |  |

| FCU reset time                                                                  |           | t <sub>FCUR</sub>  | 20 µs or longer<br>and FCLK × 6<br>or greater |           | _     | 20 µs or longer<br>and FCLK × 6 or<br>greater | _                   | _    | μs   |  |

## • Page 1392 of 1420

Table 41.54 ROM (Flash Memory for Code Storage) Characteristics (3): medium-speed operating mode B is corrected as follows: Conditions: VCC = AVCC0 = 1.62 to 3.6 V, VREFH = VREFH0 = AVCC0, VSS = AVSS0 = VREFL = VREFL0 = 0 V Temperature range for the programming/erasure operation: T<sub>a</sub> = -40 to +105°C

| Item                                                                     |           | Symbol             | FCLK                                          | = 4 MHz |       |                                               | FCLK = 32           | 2 MHz                                                                                                           | Unit |  |

|--------------------------------------------------------------------------|-----------|--------------------|-----------------------------------------------|---------|-------|-----------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------|------|--|

| lien                                                                     |           | Symbol             | Min.                                          | Тур.    | Max.  | Min.                                          | Тур.                | Max.                                                                                                            | Unit |  |

| Programming time when                                                    | 2 bytes   | t <sub>P2</sub>    | —                                             | 0.69    | 6.0   | —                                             | <del>0.8</del> 0.30 | 3.5                                                                                                             |      |  |

| N <sub>PEC</sub> ≤ 100 times                                             | 8 bytes   | t <sub>P8</sub>    | —                                             | 0.69    | 6.0   | —                                             | <del>0.8</del> 0.30 | 3.5                                                                                                             | ms   |  |

|                                                                          | 128 bytes | t <sub>P128</sub>  | _                                             | 1.76    | 14.2  | —                                             | <del>1.6</del> 0.85 | 8.3                                                                                                             |      |  |

| Programming time when                                                    | 2 bytes   | t <sub>P2</sub>    | _                                             | 0.81    | 7.1   | —                                             | 0.35                | 4.2                                                                                                             |      |  |

| N <sub>PEC</sub> > 100 times                                             | 8 bytes   | t <sub>P8</sub>    | _                                             | 0.81    | 7.6   | —                                             | 0.35                | 4.5                                                                                                             | ms   |  |

|                                                                          | 128 bytes | t <sub>P128</sub>  | _                                             | 1.99    | 17.5  | —                                             | 0.96                | 10                                                                                                              |      |  |

| Erasure time when<br>N <sub>PEC</sub> ≤ 100 times                        | 2 Kbytes  | t <sub>E2K</sub>   | —                                             | 24.5    | 113.7 | _                                             | <del>27</del> 19.0  | 46                                                                                                              | ms   |  |

| Erasure time when<br>N <sub>PEC</sub> > 100 times                        | 2 Kbytes  | t <sub>E2K</sub>   | _                                             | 29.8    | 225.8 | _                                             | 23.2                | 90<br>90 (1000 times ≥<br>N <sub>PEC</sub> > 100 times),<br>98 (10000 times ≥<br>N <sub>PEC</sub> > 1000 times) | ms   |  |

| Suspend delay time during<br>(in programming/erasure )                   |           | t <sub>SPD</sub>   | _                                             | _       | 1.7   | _                                             | —                   | 1.6                                                                                                             | ms   |  |

| First suspend delay time of<br>programming (in suspend                   | 0         | t <sub>SPSD1</sub> | _                                             | _       | 220   | _                                             | _                   | 120                                                                                                             | μs   |  |

| Second suspend delay tin<br>programming (in suspend                      | 0         | t <sub>SPSD2</sub> | —                                             |         | 1.7   | _                                             |                     | 1.6                                                                                                             | ms   |  |

| Suspend delay time during erasing (in programming/erasure priority mode) |           | t <sub>SED</sub>   | _                                             |         | 1.7   | _                                             |                     | 1.6                                                                                                             | ms   |  |

| First suspend delay time during erasing (in suspend priority mode)       |           | t <sub>SESD1</sub> | _                                             |         | 220   | _                                             |                     | 120                                                                                                             | μs   |  |

| Second suspend delay time during<br>erasing (in suspend priority mode)   |           | t <sub>SESD2</sub> | _                                             | _       | 1.7   | _                                             | _                   | 1.6                                                                                                             | ms   |  |

| FCU reset time                                                           |           | t <sub>FCUR</sub>  | 20 µs or longer<br>and FCLK × 6<br>or greater |         | _     | 20 µs or longer<br>and FCLK × 6<br>or greater | _                   | _                                                                                                               | μs   |  |

Note 1. The operating frequency is 20 MHz (max.) when the voltage is in the range from 1.62 V to less than 1.8 V.

## RENESAS

## • Page 1393 of 1420

Table 41.56 E2 DataFlash Characteristics (2): high-speed operating mode, medium-speed operating mode A is corrected as follows: Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VREFH = VREFH0 = AVCC0, VSS = AVSS0 = VREFL = VREFL0 = 0 V Temperature range for the programming/erasure operation:  $T_a = -40$  to  $+105^{\circ}C$

| Item                                                                        |                                                                           | 0 1 1               | FCI  | _K = 4 MHz |      |      | FCLK = 32 MHz       |      |      |  |  |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------|------|------------|------|------|---------------------|------|------|--|--|

|                                                                             |                                                                           | Symbol              | Min. | Тур.       | Max. | Min. | Тур.                | Max. | Unit |  |  |

| Programming time when                                                       | 2 bytes                                                                   | t <sub>DP2</sub>    |      | 0.40       | 4.4  | _    | <del>0.3</del> 0.16 | 2.0  | ms   |  |  |

| N <sub>PEC</sub> ≤ 100 times                                                | 8 bytes                                                                   | t <sub>DP8</sub>    | _    | 0.45       | 5.1  | _    | <del>0.4</del> 0.17 | 2.2  |      |  |  |

| Programming time when                                                       | 2 bytes                                                                   | t <sub>DP2</sub>    | _    | 0.62       | 6.4  | _    | 0.25                | 3.0  | ms   |  |  |

| N <sub>PEC</sub> > 100 times                                                | 8 bytes                                                                   | t <sub>DP8</sub>    | _    | 0.69       | 7.5  | _    | 0.26                | 3.2  | 1115 |  |  |

| Erasure time when<br>N <sub>PEC</sub> ≤ 100 times                           | 128 byte                                                                  | t <sub>DE128</sub>  | _    | 5.6        | 27.1 | _    | 4 <del>.5</del> 2.8 | 8    | ms   |  |  |

| Erasure time when<br>N <sub>PEC</sub> > 100 times                           | 128 byte                                                                  | t <sub>DE128</sub>  | _    | 6.8        | 45.1 |      | 3.4                 | 12   | ms   |  |  |

| Blank check time                                                            | 2 bytes                                                                   | $t_{\text{DBC2}}$   | _    | —          | 98   | -    | —                   | 35   | μs   |  |  |

|                                                                             | 2 Kbytes                                                                  | t <sub>DBC2K</sub>  | _    | —          | 16   |      | —                   | 2.5  | ms   |  |  |

| Suspend delay time durin<br>(in programming/erasure                         | priority mode)                                                            | t <sub>DSPD</sub>   | _    | _          | 0.9  | _    | —                   | 0.8  | ms   |  |  |

|                                                                             | First suspend delay time during<br>programming (in suspend priority mode) |                     | _    | _          | 220  | _    | —                   | 120  | μs   |  |  |

| Second suspend delay time during programming (in suspend priority mode)     |                                                                           | t <sub>DSPSD2</sub> | _    | _          | 0.9  | _    | —                   | 0.8  | ms   |  |  |

| Suspend delay time during erasing<br>(in programming/erasure priority mode) |                                                                           | t <sub>DSED</sub>   | _    | _          | 0.9  | _    | —                   | 0.8  | ms   |  |  |

| First suspend delay time during erasing (in suspend priority mode)          |                                                                           | t <sub>DSESD1</sub> | _    | _          | 220  | _    | _                   | 120  | μs   |  |  |

| Second suspend delay tin<br>erasing (in suspend priorit                     |                                                                           | t <sub>DSESD2</sub> | _    | _          | 0.9  | _    | _                   | 0.8  | ms   |  |  |

### • Page 1394 of 1420

Table 41.57 E2 DataFlash Characteristics (3): medium-speed operating mode B is corrected as follows:

Conditions: VCC = AVCC0 =1.62 to 3.6 V, VREFH = VREFH0 = AVCC0, VSS = AVSS0 = VREFL = VREFL0 = 0 V Temperature range for the programming/erasure operation: T<sub>a</sub> = -40 to +105°C

| ltem                                                                       |                | <u> </u>            | FCI  | _K = 4 MHz |      | FCLK = 32 MHz |                     |                   |      |  |

|----------------------------------------------------------------------------|----------------|---------------------|------|------------|------|---------------|---------------------|-------------------|------|--|

|                                                                            |                | Symbol              | Min. | Тур.       | Max. | Min.          | Тур.                | Max.              | Unit |  |

| Programming time when                                                      | 2 bytes        | t <sub>DP2</sub>    | _    | 0.52       | 5.1  | _             | <del>0.6</del> 0.24 | 2.8               | ms   |  |

| N <sub>PEC</sub> ≤ 100 times                                               | 8 bytes        | t <sub>DP8</sub>    | _    | 0.57       | 6.0  | _             | <del>0.6</del> 0.26 | 3.2               |      |  |

| Programming time when                                                      | 2 bytes        | t <sub>DP2</sub>    | _    | 0.77       | 7.6  | _             | 0.36                | 4.2               | ms   |  |

| N <sub>PEC</sub> > 100 times                                               | 8 bytes        | t <sub>DP8</sub>    | _    | 0.84       | 8.8  | —             | 0.38                | 4.5               | ms   |  |

| Erasure time when<br>N <sub>PEC</sub> ≤ 100 times                          | 128 byte       | t <sub>DE128</sub>  | _    | 6.8        | 32.5 | _             | 74.4                | 12                | ms   |  |

| Erasure time when<br>N <sub>PEC</sub> > 100 times                          | 128 byte       | t <sub>DE128</sub>  |      | 8.2        | 51.4 |               | 5.3                 | 17                | ms   |  |

| Blank check time                                                           | 2 bytes        | t <sub>DBC2</sub>   |      | —          | 110  |               | -                   | 40                | μs   |  |

|                                                                            | 2 Kbytes       | t <sub>DBC2K</sub>  | _    | —          | 16.3 | _             | _                   | 2.6               | ms   |  |

| Suspend delay time durin (in programming/erasure                           | priority mode) | t <sub>DSPD</sub>   |      | _          | 1.7  | _             |                     | 1.6               | ms   |  |

| First suspend delay time of<br>programming (in suspend                     | priority mode) | t <sub>DSPSD1</sub> |      | _          | 220  |               |                     | 120               | μs   |  |

| Second suspend delay time during<br>programming (in suspend priority mode) |                | t <sub>DSPSD2</sub> | _    | _          | 1.7  | _             | _                   | 1.6               | ms   |  |

| Suspend delay time during erasing (in programming/erasure priority mode)   |                | t <sub>DSED</sub>   | _    | _          | 1.7  | _             | _                   | 1.6               | ms   |  |

| First suspend delay time during erasing (in suspend priority mode)         |                | t <sub>DSESD1</sub> |      | _          | 220  |               | _                   | <del>12</del> 120 | μs   |  |

| Second suspend delay tin<br>erasing (in suspend priori                     |                | t <sub>DSESD2</sub> | _    | _          | 1.7  | _             | _                   | 1.6               | ms   |  |

Note 1. The operating frequency is 20 MHz (max.) when the voltage is in the range from 1.62 V to less than 1.8 V.