## **RENESAS TECHNICAL UPDATE**

## 1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category                                                                                                                                                                                                                                                                | MPU & MCU                                                                                                                                                                                                                                                                          |                         | Document<br>No.        | TN-16C-A194A/E             | Rev.     | 1.00   |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|----------------------------|----------|--------|--|--|

| Title Errata to R32C/152 Group Hardware Manual                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                    | Information<br>Category | Technical Notification |                            |          |        |  |  |

| Applicable<br>Product                                                                                                                                                                                                                                                              | R32C/152 Group                                                                                                                                                                                                                                                                     | Lot No.                 | Reference<br>Document  | •                          |          |        |  |  |

|                                                                                                                                                                                                                                                                                    | nent describes corrections to the R320<br>tions are indicated in red in the list bel                                                                                                                                                                                               | •                       | Hardware Ma            | anual, Rev. 1.03.          |          |        |  |  |

| Table 1.8                                                                                                                                                                                                                                                                          | of 639, description "Output of the cloo<br>is corrected as follows:<br>at of the clock with the same frequency                                                                                                                                                                     |                         |                        |                            | ck outp  | out in |  |  |

| is correc                                                                                                                                                                                                                                                                          | of 639, description of register name "C<br>ted as follows:<br>o 1 Time Measurement Prescaler Reg                                                                                                                                                                                   |                         | r Measureme            | nt Prescaler Register 6/7' | ' in Tab | le 4.6 |  |  |

| is correc                                                                                                                                                                                                                                                                          | of 639, description of register name "C<br>ted as follows:<br>o 0 Time Measurement Prescaler Reg                                                                                                                                                                                   |                         | r Measureme            | nt Prescaler Register 6/7' | ' in Tab | le 4.9 |  |  |

| <ul> <li>Page 31 of 639, description of register name "Group 3 Timer Measurement Prescaler Register 6/7" in Table</li> <li>4.12 is corrected as follows:</li> <li>"Group 3 Time Measurement Prescaler Register 6/7"</li> </ul>                                                     |                                                                                                                                                                                                                                                                                    |                         |                        |                            |          |        |  |  |

| <ul> <li>Page 34 of 639, description of register name "UART2 Transmission/Receive Mode Register" in Table 4.15 is<br/>corrected as follows:<br/>"UART2 Transmit/Receive Mode Register"</li> </ul>                                                                                  |                                                                                                                                                                                                                                                                                    |                         |                        |                            |          |        |  |  |

| <ul> <li>Page 45 of 639, description of register name "External Interrupt Source Select Register 1/0" in Table 4.26 is<br/>corrected as follows:</li> <li>"External Interrupt Request Source Select Register 1/0"</li> </ul>                                                       |                                                                                                                                                                                                                                                                                    |                         |                        |                            |          |        |  |  |

| <ul> <li>Page 64 of 639, descriptions of register names "CAN2 Reception Error Count Register" and "CAN2<br/>Transmission Error Count Register" in Table 4.45 are corrected as follows:<br/>"CAN2 Receive Error Count Register" and "CAN2 Transmit Error Count Register"</li> </ul> |                                                                                                                                                                                                                                                                                    |                         |                        |                            |          |        |  |  |

| <ul> <li>Page 78 of 639, descriptions of register names "CAN1 Reception Error Count Register" and "CAN1<br/>Transmission Error Count Register" in Table 4.59 are corrected as follows:<br/>"CAN1 Receive Error Count Register" and "CAN1 Transmit Error Count Register"</li> </ul> |                                                                                                                                                                                                                                                                                    |                         |                        |                            |          |        |  |  |

| Transmis                                                                                                                                                                                                                                                                           | <ul> <li>Page 92 of 639, descriptions of register names "CAN0 Reception Error Count Register" and "CAN0<br/>Transmission Error Count Register" in Table 4.73 are corrected as follows:<br/>"CAN0 Receive Error Count Register" and "CAN0 Transmit Error Count Register"</li> </ul> |                         |                        |                            |          |        |  |  |

•Page 100 of 639, descriptions for the VDEN bit in Figure 6.4 are corrected as follows:

| Bit Symbol | Bit Name | Function                                                            | RW |

|------------|----------|---------------------------------------------------------------------|----|

| VDEN       |          | 0: Low voltage detector disabled<br>1: Low voltage detector enabled | RW |

•Page 100 of 639, descriptions of Notes 2 and 3 in Figure 6.4 are corrected as follows:

Note 2: "Before setting this bit to 1, set the VDEN bit to 1 (low voltage detecor enabled) first, and wait until the circuit is stablized."

Note 3: "This bit is enabled when the VDEN bit is set to 1 (low voltage detecor enabled)."

•Page 102 of 639, description in 6.2.1 is corrected as follows:

"The low voltage detector starts operating stably after td(E-A) when the VDEN bit in the LVDC register is set to 1 (low voltage detector enabled)."

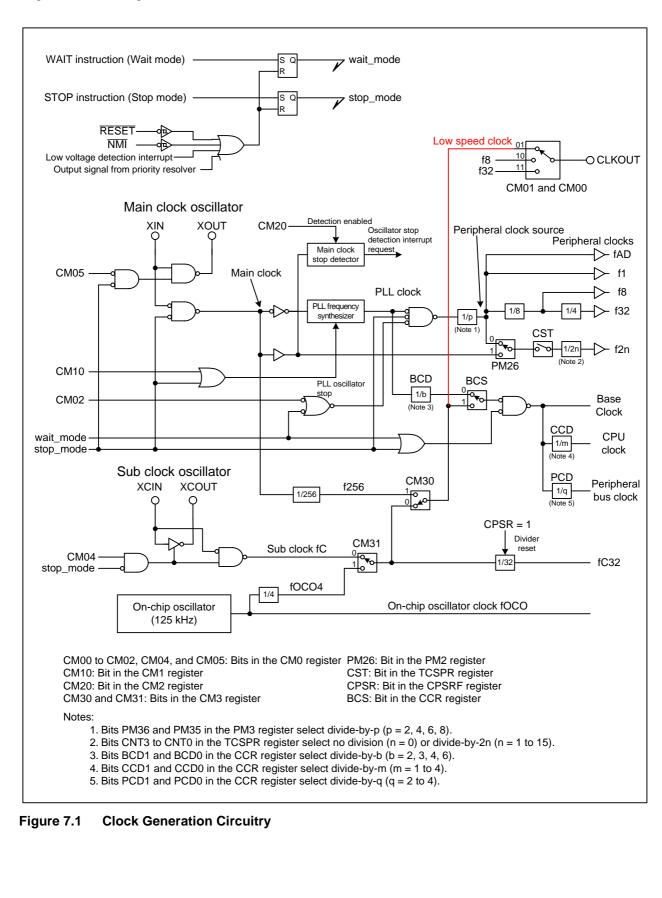

•Page 105 of 639, Figure 7.1 is corrected as follows:

•Page 106 of 639, descriptions of Notes 2 and 6 in Figure 7.2 are corrected as follows: Note 2: "The divide ratios of the base clock and peripheral bus clock should not be changed simultaneously. Otherwise, the peripheral bus clock frequency may be over the operational maximum." ("To increase the base clock frequency, the divide ratio of the peripheral bus clock should be increased before reducing the divide ratio of base clock." is deleted) Note 6: "To use these low speed clocks, select one of them by setting bits CM31 and CM30 in the CM3 register and then set the BCS bit to 1." •Pages 107, 121, 128, and 131 of 639, descriptions "fC" in the function column of bits CM01 and CM00 in Figure 7.3, Section 7.6, Tables 7.3, 7.4, and 7.6 are corrected as follows: Figure 7.3: "0 1 : Output a low speed clock" Section 7.6: "Low speed clocks, f8, and f32 are available to be output from the CLKOUT pin." Table 7.3: "Output a low speed clock" Table 7.4: "When a low speed clock is selected" Table 7.6: "When a low speed clock is selected" •Page 107 of 639, description is added as Note 7 in Figure 7.3 as follows: "Set this bit before activating the watchdog timer. When rewriting this bit while the watchdog timer is running, set it immediately after writing to the WDTS register." • Page 108 of 639, description of bit name "PLL Clock Oscillator Stop Bit" in Figure 7.4 is corrected as follows: "PLL Oscillator Stop Bit" •Page 108 of 639, description is added as Note 4 in Figure 7.4 as follows: "This bit becomes 1 when the main clock is stopped. Set it to 0 after the main clock oscillation is fully stabilized." •Page 109 of 639, description is corrected to Note 1 in Figure 7.6 as follows: "Rewrite this register after setting the PRC27 bit in the PRCR2 register to 1 (write enabled) and while the BCS bit in the CCR register is 0 (PLL clock)." •Page 111 of 639, descriptions in Note 3 in Figure 7.9 are corrected as follows: "CM05 bit in the CM0 register (main clock oscillator enabled/disabled) CM10 bit in the CM1 register (PLL oscillator enabled/disabled)" •Page 111 of 639, description is added as Note 6 in Figure 7.9 as follows: "Disable all the peripheral functions that use f2n before rewriting this bit." •Page 112 of 639, description is added to Note 1 in Figure 7.10 as follows: "Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting this register. Disable all the peripheral functions that use fAD, f1, f8, f32, or f2n (when the clock source is the peripheral clock source) to rewrite this register." •Page 116 of 639, descriptions for the SEO bit in Figure 7.15 are corrected as follows: Bit Symbol Bit Name Function RW 0: PLL lock-in SEO Self-Oscillating Setting Bit RW 1: Self-oscillating

•Page 116 of 639, description is added as Note 1 in Figure 7.16 as follows: "This register is reset after the SEO bit in the PLC1 register is set to 1 (self-oscillating). Stopping the main clock or PLL prevents the register from updating."

## •Page 119 of 639, description in 7.2.1 is corrected as follows:

"When the main clock oscillator resumes running after an oscillator stop is detected, the PLL clock frequency may temporarily exceed the preset value before the PLL frequency synthesizer oscillation stabilizes. As soon as an oscillator stop is detected, the main clock oscillator should be stopped from resuming (set the CM05 bit in the CM0 register to 1) or the divide ratios of the base clock and peripheral clock source should be increased by a program. The respective divide ratio can be set by bits BCD1 and BCD0 in the CCR register and bits PM36 and PM35 in the PM3 register."

•Page 122 of 639, description of 7.7 is corrected as follows:

"Power control contains three modes: wait mode, stop mode, and normal operating mode.

The name "normal operating mode" is used restrictively in this chapter, and it indicates all other modes except wait mode and stop mode. Figure 7.16 shows a block diagram of the state transition in normal operating mode, stop mode, and wait mode."

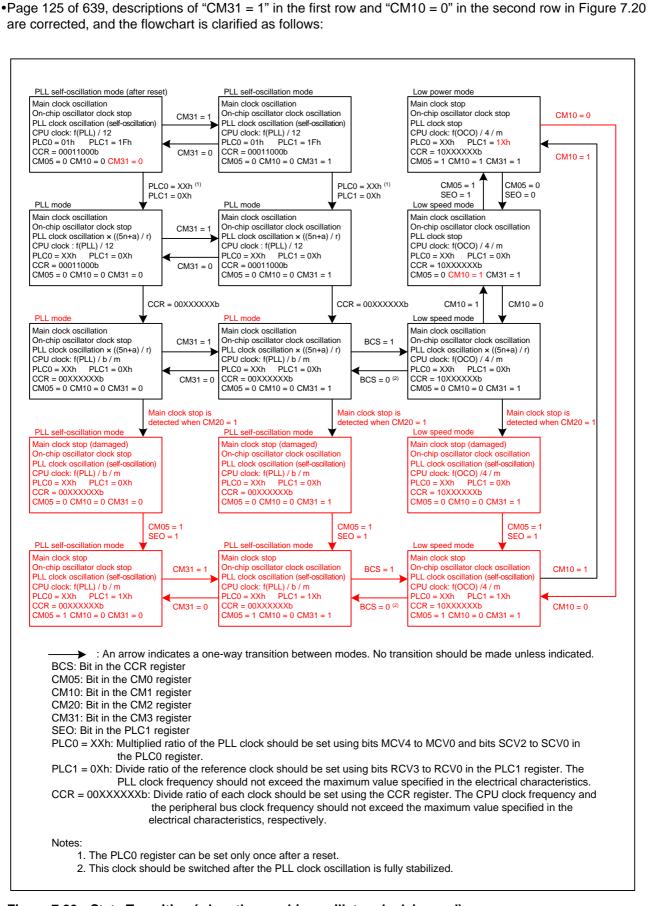

## Figure 7.20State Transition (when the on-chip oscillator clock is used)

(Note 3 "The CM05 bit is not set to 1 when an oscillator stop is detected through the oscillation stop detector." is deleted from Figure 7.20)

•Page 128 of 639, descriptions of 7.7.2.4 are corrected as follows: "Wait mode is exited by the hardware reset, an NMI, or peripheral interrupts assigned to software interrupt numbers from 0 to 63. To exit wait mode by either the hardware reset or an NMI, without using peripheral interrupts, bits ILVL2 to ILVL0 for the peripheral interrupts should be set to 000b (interrupt disabled) before executing the WAIT instruction. The CM02 bit setting in the CM0 register affects the peripheral interrupts. When the CM02 bit is set to 0 (peripheral clock source not stopped in wait mode), peripheral interrupts for software interrupt numbers from 0 to 63 can be used to exit wait mode. When this bit is set to 1 (peripheral clock source stopped in wait mode), peripheral functions operated using clocks (f1, f8, f32, f2n whose clock source is the peripheral clock source, and fAD) generated by the peripheral clock source stop operating. Therefore, the peripheral interrupts cannot be used to exit wait mode. However, peripheral functions operated using clocks which are independent from the peripheral clock source (fC32, external clock, and f2n whose clock source is the main clock) do not stop operating. Thus, interrupts generated by peripheral functions and assigned to software interrupt numbers from 0 to 63 can be used to exit wait mode. The CPU clock used when exiting wait mode by the peripheral interrupts or an NMI is the same clock used when the WAIT instruction is executed. Table 7.5 lists interrupts to be used to exit wait mode and usage conditions." •Page 129 of 639, description of Note 1 of Table 7.5 is added as follows: "INT6 to INT8 are available in the intelligent I/O interrupt only." •Page 130 of 639, description of 7.7.3 is corrected as follows: "In stop mode, all of the clocks, except for those that are protected, stop running." •Page 131 of 639, description in line 1 of 7.7.3.3 is corrected as follows: "Stop mode is exited by the hardware reset, an NMI, low voltage detection interrupt, or peripheral interrupts assigned to software interrupt numbers from 0 to 63."

•Page 131 of 639, description is added to Table 7.7 as follows:

| External interrupt | INT6 to INT8 are available when intelligent I/O interrupt is used |

|--------------------|-------------------------------------------------------------------|

|--------------------|-------------------------------------------------------------------|

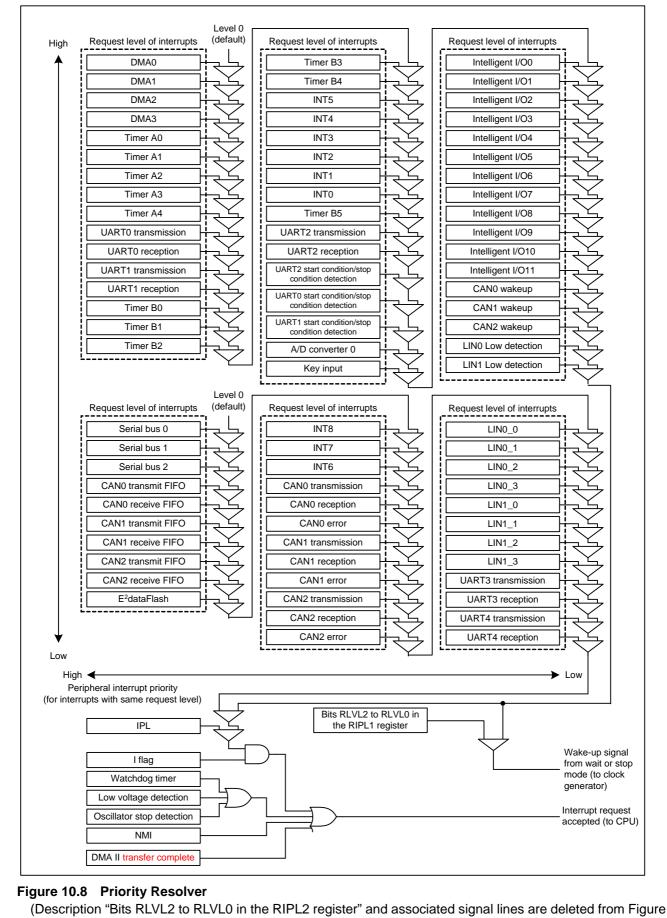

•Page 157 of 639, Figure 10.8 is corrected as follows:

10.8)

Page 164 of 639, descriptions for b0 and Note 3 in Figure 10.17 are corrected as follows: b0: "No register bit; this bit is read as 1" ("should be written with 0 and" is deleted) Note 3: "When this bit is function-assigned, it can be set to 0 only. It should not be set to 1. To set to 0, either the AND or BCLR instruction should be used; when the bit is not function-assigned, that is, reserved, it should be set to 0."

Page 166 of 639, description of the third bullet point in 10.14.3 is corrected as follows: "The interrupt input signals to pins INT6 to INT8 are also connected to bits INT6R to INT8R in registers IIO9IR to IIO11IR. Therefore, these input signals, when assigned to the intelligent I/O, can be used as a source for exiting wait mode or stop mode. Note that these signals are enabled only on the falling edge and not affected by the following bit settings: bits POL and LVS in the INTIIC register (i = 0 to 8), IFSR0i bit (i = 0 to 5) in the IFSR0 register, and the IFSR1j bit (j = i - 6; i = 6 to 8) in the IFSR1 register."

Page 168 of 639, descriptions are added as Notes 1 and 2 to Figure 11.2 as follows: Note 1: "When the on-chip oscillator clock is used as the count source, the read value may be undefined due

Note 1: "When the on-chip oscillator clock is used as the count source, the read value may be undefined due to a change in the count value while being read." Note2: "Set this bit before activating the watchdog timer."

•Page 169 of 639, description is added as Note 2 to Figure 11.3 as follows: "Set these bits before activating the watchdog timer."

•Page 170 of 639, description is added as Note 3 to Figure 11.5 as follows: "These bit settings are disabled when the WDTON bit is 1. The values set to these bits are reflected to registers WDK and PM2 when the WDTON bit is 0."

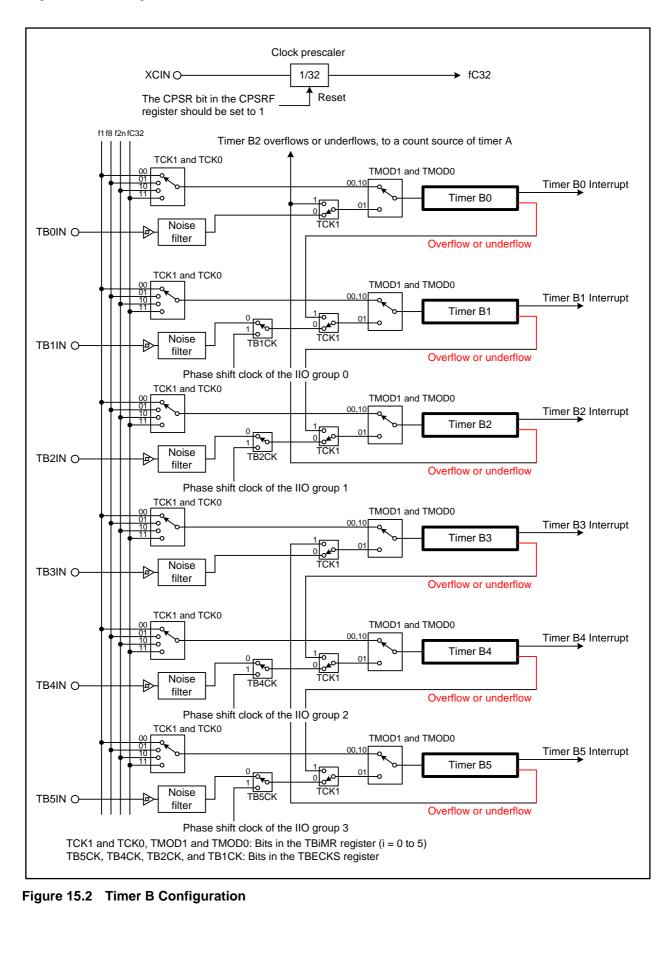

•Page 199 of 639, Figure 15.2 is corrected as follows:

| <ul> <li>Pages 235 and 241 of 639, descriptions of functions of the INV13 bit in Figure 16.3 and the PWCON bit in Figure 16.9 are corrected as follows:</li> <li>INV13: "0: Timer A1 reload control signal is 0</li> <li>1: Timer A1 reload control signal is 1"</li> <li>PWCON: "1: The underflow of timer B2 when the reload control signal for timer A1 is 0"</li> </ul>                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Page 240 of 639, descriptions of functions of bits MR2 and MR3 in Figure 16.8 are corrected as follows:<br/>MR2: "No register bit; should be written with 0 and read as undefined value"<br/>MR3: "Disabled in the three-phase motor control timers. Should be written with 0 and read as undefined<br/>value"</li> </ul>                                                                                                                                                                                                                                                |

| <ul> <li>Page 248 of 639, description of case 1 in Figure 16.18 is corrected as follows:</li> <li>"-INV01 = 0 and ICTB2 = 2h (timer B2 interrupt generated every 2nd time the timer B2 underflows), or</li> <li>INV01 = 1, INV00 = 1 and ICTB2 = 1h (timer B2 interrupt generated every time the timer B2 underflows when the reload control signal for timer A1 is set to 1)"</li> </ul>                                                                                                                                                                                         |

| •Page 250 of 639, descriptions in 16.6.1 are corrected as follows:<br>"When a low signal is applied to the NMI pin with the bit settings below, pins TA1OUT, TA2OUT, and<br>TA4OUT become high-impedance: the PM24 bit in the PM2 register is 1 (NMI enabled), the SDE bit in the<br>IOBC register is 1 (shutdown enabled), the INV02 bit in the INVC0 register is 1 (the three-phase motor<br>control timers used), and the INV03 bit is 1 (the three-phase motor control timer output enabled)."                                                                                |

| •Page 250 of 639, descriptions "overflows" and "overflow" in 16.6.2 are corrected as follows:<br>"Do not write to the TAi1 register (i = 1, 2, 4) in the timing that timer B2 underflows. Before writing to the TAi1<br>register, read the TB2 register to verify that sufficient time is left until timer B2 underflows. Then, immediately<br>write to the TAi1 register so that no interrupt handler is performed during this write procedure. If the TB2<br>register indicates little time is left until the underflow, write to the TAi1 register after timer B2 underflows." |

| <ul> <li>Page 256 of 639, Note 1 "Bits CNT3 to CNT0 in the TCSPR register select a divide ratio from two options: no division (n = 0) or divide-by-2n (n = 1 to 15)." is deleted from Figure 17.5</li> </ul>                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>Page 260 of 639, description of function of the SWC bit in Figure 17.11 is corrected as follows:</li> <li>"0: No wait-state/wait-state cleared</li> <li>1: Hold the SCLi pin low after the eighth bit is received"</li> </ul>                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>Page 262 of 639, description of function of the SWC9 bit in Figure 17.13 is corrected as follows:</li> <li>"0: No wait-state/wait-state cleared</li> <li>1: Hold the SCLi pin low after the ninth bit is received"</li> </ul>                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>Pages 262 and 288 of 639, descriptions "STARREQ" in Note 3 of Figure 17.13 and 17.3.2 are corrected as follows:</li> <li>Figure 17.13: "The STSPSEL bit should be set to 1 after setting the STAREQ, RSTAREQ, or STPREQ bit to 1."</li> <li>17.3.2: "The start condition, restart condition, and stop condition are generated by bits STAREQ, RSTAREQ, and STPREQ in the UiSMR4 register (i = 0 to 2), respectively."</li> </ul>                                                                                                                                         |

| <ul> <li>Pages 280 and 281 of 639, descriptions "Transmit/receive clock" in Figures 17.27 and 17.28 are corrected as<br/>follows:<br/>"CLKi"</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

•Page 290 of 639, descriptions in 17.3.4 are corrected as follows:

"Data transmission/reception in  $I^2C$  mode uses the transmit/receive clock as shown in Figure 17.30. The clock speed increase makes it difficult to secure the required time for ACK generation and data transmit procedure. The  $I^2C$  mode supports a function of wait-state insertion to secure this required time and a function of clock synchronization with a wait-state inserted by other devices.

The SWC bit in the UiSMR2 register (i = 0 to 2) is used to insert a wait-state for ACK generation. When the SWC bit is set to 1 (hold the SCLi pin low after the eighth bit is received), the SCLi pin is held low on the falling edge of the eighth bit of the SCLi. When the SWC bit is set to 0 (no wait-state/wait-state cleared), the SCLi line is released.

When the SWC2 bit in the UiSMR2 register is set to 1 (hold the SCLi pin low), the SCLi pin is forced low even during transmission or reception in progress. When the SWC2 bit is set to 0 (output the transmit/ receive clock at the SCLi pin), the SCLi line is released to output the transmit/receive clock.

The SWC9 bit in the UiSMR4 register is used to insert a wait-state for checking received acknowledge bits. While the CKPH bit in the UiSMR3 register is set to 1 (clock delayed), when the SWC9 bit is set to 1 (hold the SCLi pin low after the ninth bit is received), the SCLi pin is held low on the falling edge of the ninth bit of the SCLi. When the SWC9 bit is set to 0 (no wait-state/wait-state cleared), the SCLi line is released."

•Pages 292, 296, and 297 of 639, descriptions "(external clock selected)" in line 1 of 17.3.8 and line 2 of 17.4.2.2 and "(internal clock selected)" in line 2 of 17.4.2.1 are corrected as follows: "(external clock)" and "(internal clock)"

•Page 292 of 639, description "the SCLi pin is held low after the eighth bit of the SCLi is received)" in the third bullet point of 17.3.8 is corrected as follows:

"(hold the SCLi pin low after the eighth bit is received)"

•Page 298 of 639, description of the fourth dash in 17.5.2.1 is replaced as follows:

"- The TE bit in the UiC1 register is set to 1 (transmission enabled).

- The RE bit in the UiC1 register is set to 1 (reception enabled). This bit setting is not required in transmit operation only.

- The TI bit in the UiC1 register is set to 0 (data held in the UiTB register)."

Page 321 of 639, description in the ninth bullet point of 18.3.2 is corrected as follows:

"The external trigger cannot be used in DMAC operating mode. When the DMAC is configured to transfer converted results, do not read the AD00 register by a program."

•Page 324 of 639, description "CRC\_CCITT" in line 2 of Chapter 20 is corrected as follows: "A generator polynomial of CRC-CCITT (X<sup>16</sup> + X<sup>12</sup> + X<sup>5</sup> + 1) generates a CRC."

•Pages 332 to 335 of 639, descriptions "Request from the INT0 pin" in Figure 22.1, "Request from the INT1 pin" in Figure 22.2, "Request from the INT2 pin" in Figure 22.3, and "Request from the INT3 pin" in Figure 22.4 are corrected as follows:

Figure 22.1: "Request from the INTO pin or the INT1 pin"

Figure 22.2: "Request from the INTO pin or the INT1 pin"

Figure 22.3: "Request from the INTO pin or the INT1 pin"

Figure 22.4: "Request from the INTO pin or the INT1 pin"

•Page 338 of 639, descriptions in the function column of the RST2 bit and Note 3 in Figure 22.7 are corrected as follows:

RST2: "1: A low signal input into the INTO/INT1 pin"

Note 3: "The base timer is reset by an input of low signal to the external interrupt pin selected for signals UD0Z (for groups 0 and 2) and UD1Z (for groups 1 and 3) by the IFS2 register."

Page 346 of 639, description in the second bullet point of specification for reset conditions in Table 22.2 is corrected as follows:

"An input of low signal into the external interrupt pin as follows:

for groups 0 and 2: selected using bits IFS23 and IFS22 in the IFS2 register

for groups 1 and 3: selected using bits IFS27 and IFS26 in the IFS2 register"

- •Page 347 of 639, description "Low signal input to the INTk pin" in Figure 22.17 is corrected as follows: "Low signal input to the INT0/INT1 pin"

- •Page 368 of 639, bit name "SBUMS" in line 6 of 23. Serial Bus Interface is corrected as follows: "SSUMS"

- Pages 369 and 371 of 639, pin name "SSiCK" and register name "SSiRDR" in Tables 23.1 and 23.2 are corrected as follows:

"SSCKi" and "SSITDR"

•Page 371 of 639, descriptions "SSIi (I): Data input pin" and "SSOi (O): Data output pin" in the I/O pins row in Table 23.2 are corrected as follows:

"SSIi (I/O): Data I/O pin" and "SSOi (I/O): Data I/O pin"

•Page 375 of 639, description of function of bits BC2 to BC0 in Figure 23.5 is added as follows:

| Bit Symbol | Bit Name    | Function                                                                                                               | RW |

|------------|-------------|------------------------------------------------------------------------------------------------------------------------|----|

| BC0        |             | Bits left during transmission/reception<br>b2 b1 b0<br>0 0 0 : 8 bits left                                             | RW |

| BC1        | Bit Counter | <ul> <li>0 0 1:1 bits left</li> <li>0 1 0:2 bits left</li> <li>0 1 1:3 bits left</li> <li>1 0 0:4 bits left</li> </ul> | RW |

| BC2        |             | <ol> <li>1 0 1:5 bits left</li> <li>1 0:6 bits left</li> <li>1 1:7 bits left</li> </ol>                                | RW |

•Page 378 of 639, descriptions of functions of bits CE and ORER in Figure 23.8 are modified as follows:

| Bit Symbol | Bit Name                                                | Function                                           | RW |

|------------|---------------------------------------------------------|----------------------------------------------------|----|

| CE         | Conflict Error Flag <sup>(1, 3)</sup>                   | 0: No conflict error<br>1: Conflict error occurred | RW |

| (b1)       | No register bit; should be written with 0 and read as 0 |                                                    | _  |

| ORER       | Overrun Error Flag <sup>(1, 3)</sup>                    | 0: No overrun error<br>1: Overrun error occurred   | RW |

•Page 379 of 639, descriptions "input/output pin" and "Input/output pin" for the SCKS bit in Figure 23.9 are modified as follows:

"I/O pin"

|                                      | to 393, 397, and 399 of 639, description "(overrun error)" for the ORER bit when it is 1 in 3.1.6.2 to 23.1.6.4, 23.1.7.2, and 23.1.7.3 is modified as follows: or occurred)"                                                                                                             |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •Page 401 of 639<br>"(conflict error | 9, description "(conflict error)" in line 5 of 23.1.7.4 is modified as follows: r occurred)"                                                                                                                                                                                              |

|                                      | 9, descriptions "Break dominant" and "Break delimiter" in Table 24.1 are corrected as follows: ak length" and "Transmit break delimiter length"                                                                                                                                           |

| L0LD: "The bi<br>L1LD: "The bi       | 9, descriptions of functions of bits L3LD to L0LD in Figure 24.3 are corrected as follows:<br>it is read as the value of the LD bit in the LiST register of channel 0"<br>it is read as the value of the LD bit in the LiST register of channel 1"                                        |

|                                      | it is read as the value of the LD bit in the LiST register of channel 2"<br>it is read as the value of the LD bit in the LiST register of channel 3"                                                                                                                                      |

|                                      | 9, description of Note 1 of Figure 24.3 is added as follows:<br>rupt is generated by the input signal low detection when any one of these bits is 1."                                                                                                                                     |

| "The LD bit in<br>- When the fa      | 9, description of Note 4 of Figure 24.7 is corrected as follows:<br>the LiST register becomes 1 and an interrupt request is generated in the following cases:<br>Illing edge of the input signal is detected when this bit is set to 1.<br>it is set to 1 while the input signal is low." |

|                                      | 9, figure title of Figure 24.7 is corrected as follows:<br>MD0 and L1MD0"                                                                                                                                                                                                                 |

| corrected as foll                    | 9, descriptions of bit names of bits BLT3 to BLT0 and bits BDT1 and BDT0 in Figure 24.10 are lows:<br>BLT0: "Transmit Break (Low) Length Setting Bit"                                                                                                                                     |

| Bits BDT1 and                        | d BDT0: "Transmit Break Delimiter (High) Length Setting Bit"                                                                                                                                                                                                                              |

|                                      | 9, figure title of Figure 24.13 is corrected as follows: IDB and L1IDB"                                                                                                                                                                                                                   |

|                                      | 417 of 639, description of Note 1 of Figures 24.16 and 24.17 is corrected as follows:<br>o not become 0 automatically. Set them to 0 by a program. Writing 1 to these bits has no effect."                                                                                                |

| "When this bit<br>- When the LI      | 9, description of Note 3 of Figure 24.16 is added as follows:<br>t is 1, no new interrupt request is generated in the following cases:<br>D bits of other channels become 1.                                                                                                              |

| - When the co                        | onditions for the LD bit to become 1 are met in its channel."                                                                                                                                                                                                                             |

| "Bits BLT3 to                        | 9, bit names in the fourth bullet point of Table 24.3 are changed as follows:<br>BLT0 for break low (13 to 28 Tbit);<br>d BDT0 for break delimiter (1 to 4 Tbit)"                                                                                                                         |

| -                                    | 9, descriptions for (4) for "LIN Module Processing" in Table 24.4 are changed as follows:<br>ta 2, then the next interbyte space<br>a 3, then the next interbyte space                                                                                                                    |

|                                      |                                                                                                                                                                                                                                                                                           |

| Page 423 of 639, descriptions for (4) for "LIN Module Processing" in Table 24.5 are changed as follows:<br>"Receive Data 2 due to start bit detection<br>Receive Data 3 due to start bit detection                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Repeat this process for the data length specified in bits RFDL3 to RFDL0 in the LiRFC register. Abort reception and go to (5) if an error occurs. Checksum judgement is not performed in this case.)"                                        |

| Page 426 of 639, description "BPR0" in Note 1 of Table 24.6 is corrected as follows:<br>"BRP0"                                                                                                                                                |

| Page 433 of 639, Figure 24.30 is corrected as follows:                                                                                                                                                                                        |

| (START (Note 1)                                                                                                                                                                                                                               |

| Transmit "Go to Sleep" command to the LIN bus <sup>(2)</sup>                                                                                                                                                                                  |

| Set the LIN module to LIN wake-up mode or LIN reset mode (2)                                                                                                                                                                                  |

| Set the LIN transceiver to sleep mode (3)                                                                                                                                                                                                     |

| Set the I flag to 0 (interrupt disabled)                                                                                                                                                                                                      |

| Set the LDE bit in the LiMD0 register to 1<br>(input signal low detection enabled)                                                                                                                                                            |

| Set the IR bit in the LiLDIC register to 0 and bits ILVL2 to ILVL0 to 000b                                                                                                                                                                    |

| Set the LD bit in the LiST register to 0                                                                                                                                                                                                      |

| Execute steps before entering wait mode from (2) to (5)                                                                                                                                                                                       |

| Set the interrupt request level of the LiLDIC register                                                                                                                                                                                        |

| Set the IPL in the flag register                                                                                                                                                                                                              |

| Set the interrupt priority level for resuming to the same level as the IPL                                                                                                                                                                    |

| Set the I flag to 1 (interrupt enabled) (4)                                                                                                                                                                                                   |

| Execute the WAIT instruction                                                                                                                                                                                                                  |

| END                                                                                                                                                                                                                                           |

| Notes:<br>1. This flowchart shows an example of the setting procedure to exit wait mode using a wake-up signal from the<br>LIN bus after entering wait mode.                                                                                  |

| <ol> <li>Set the LIN module in PLL mode (high speed mode or medium speed mode).</li> <li>The setting depends on the LIN transceiver specification.</li> <li>Enter low speed mode or low power mode before setting the I flag to 1.</li> </ol> |

| Figure 24.30 Example of Setting Before Transmition to Wait Mode (i = 0, 1)                                                                                                                                                                    |

|                                                                                                                                                                                                                                               |

•Page 434 of 639, description for Detecting Condition for Input signal low detection in Table 24.8 is changed as follows:

"When the falling edge of input signal at the LINi\_jIN pin is detected with the setting of the LDE bit in the LiMD0 register to 1 (Input signal low detection enabled), or when setting the LDE bit to 1 while the LINi\_jIN pin is low."

•Page 435 of 639, value range "; j = 0 to 3" in the title of Table 24.9 is deleted.

•Page 437 of 639, description in lines 9 to 10 of 24.11 is added as follows:

"The respective interrupt request is output when the corresponding flag in the LiST register becomes 1 while the corresponding bit in the LiMD0 register is set to 1 (interrupt enabled). No new interrupt request is generated by the other sources if any of them is 1 since multiple interrupt sources are aggregated."

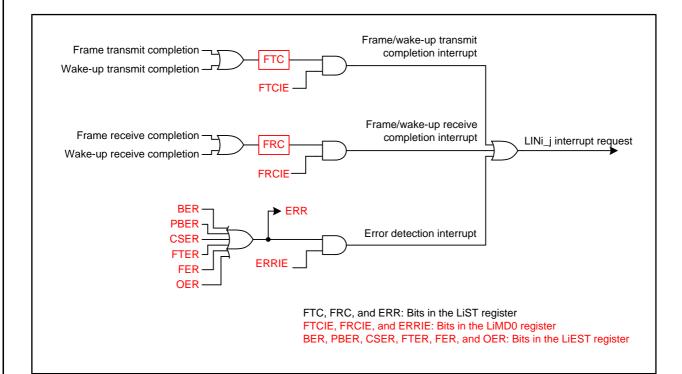

•Page 437 of 639, Figure 24.32 is corrected as follows:

Figure 24.32 LINi\_j Interrupt Block Diagram (i = 0, 1; j = 0 to 3)

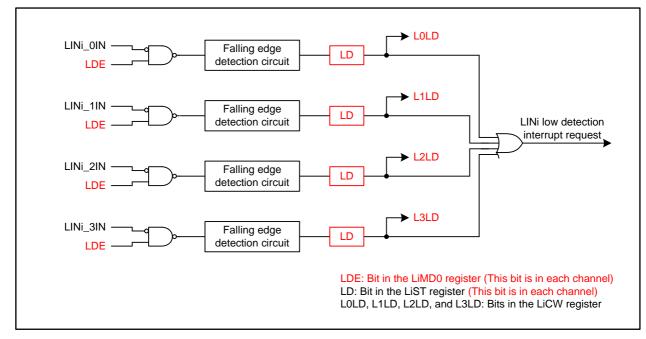

•Page 438 of 639, Figure 24.33 is corrected as follows:

•Page 462 of 639, description of Note 2 "Write 0 to the RFE bit simultaneously with the RFMLF bit." in Figure 25.11 is corrected as follows:

"When setting the RFE bit to 0, set the RFMLF bit to 0 as well."

•Page 484 of 639, description of Note 4 in Figure 25.28 is modified as follows: "If more than one error condition is detected simultaneously, all corresponding bits are set to 1."

•Page 494 of 639, description "CiSTR" in 25.2.4 is corrected as follows:

"Transmit mode: A CAN message is being transmitted. The CAN module may receive its own message simultaneously when self-test mode 0 (TSTM bit in the CiTCR register = 10b) or self-test mode 1 (TSTM bit = 11b) is selected."

•Page 535 of 639, description of bit name "P14\_1 to P14\_3 Pull-Up Control Bit" in Figure 26.29 is corrected as follows:

PU40: "P14\_1 and P14\_3 Pull-Up Control Bit"

•Page 541 of 639, descriptions in Table 27.3 are corrected as follows:

| Protection Type               | Lock Bit Protection | ROM Code Protection | ID Code Protection              |

|-------------------------------|---------------------|---------------------|---------------------------------|

| Operations to be<br>protected | Erase, write        | Read, write         | Read, <mark>erase,</mark> write |

(Deleted description "erase" from the ROM Code Protection column)

| Protection     | Setting the LBD bit in the   | Erasing all blocks whose  | Inputting a proper ID code |

|----------------|------------------------------|---------------------------|----------------------------|

| deactivated by | FMR register to 1 (lock bit  | protect bits are set to 0 | to the serial programmer   |

|                | protection disabled). Or, by |                           |                            |

|                | erasing the blocks whose     |                           |                            |

|                | lock bits are set to 0 to    |                           |                            |

|                | permanently deactivate the   |                           |                            |

|                | protection                   |                           |                            |

(Deleted description "by using the serial programmer" from the ROM Code Protection column)

•Page 541 of 639, description "use the serial programmer to" in line 3 of 27.2.2 is deleted.

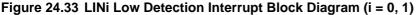

•Page 543 of 639, Figure 27.2 is corrected as follows:

Figure 27.2 Addresses for ID Code Stored

•Page 545 of 639, descriptions in Table 27.5 are corrected as follows:

| Restriction on software | None | <ul> <li>Do not execute either the program</li> </ul>      |

|-------------------------|------|------------------------------------------------------------|

| command                 |      | command or the block erase command                         |

|                         |      | for blocks where the rewrite control                       |

|                         |      | programs are written to                                    |

|                         |      | • Do not execute the enter read status                     |

|                         |      | register mode command                                      |

|                         |      | <ul> <li>Execute the enter read lock bit status</li> </ul> |

|                         |      | mode command in RAM                                        |

|                         |      | <ul> <li>Execute the enter read protect bit</li> </ul>     |

|                         |      | status mode command in RAM                                 |

| Flash memory state                                  | <ul> <li>Reading the FMSR0 register by a</li> </ul> | Reading the FMSR0 register by a |

|-----------------------------------------------------|-----------------------------------------------------|---------------------------------|

| detection by                                        | program                                             | program                         |

| <ul> <li>Executing the enter read status</li> </ul> |                                                     |                                 |

|                                                     | register mode command to read data                  |                                 |

•Page 545 of 639, description "Figure 27.11" in the last line below Table 27.5 is corrected as follows: "Figure 27.12"

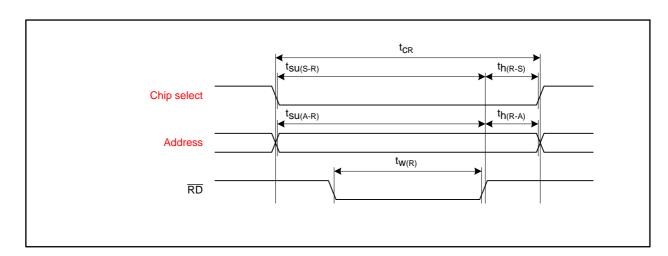

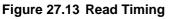

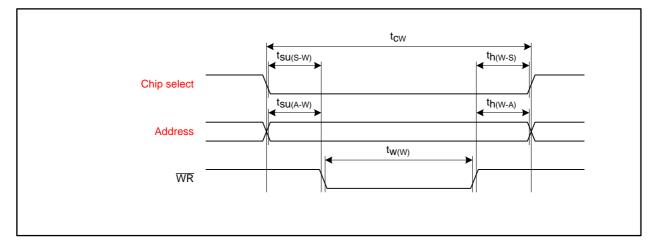

•Pages 552 and 554 of 639, descriptions in Figures 27.13 and 27.14 are corrected as follows:

Figure 27.14 Write Timing

- •Page 572 of 639, description of Note 3 in Figure 28.2 is corrected as follows: "When this bit is set to 1, the module stops ongoing operations to enter its initial state. However, the registers are not initialized."

- •Page 572 of 639, description "This mode setting prevents data from being overwritten if a program goes out of control." is deleted from Note 5 of Figure 28.2.

- •Page 574 of 639, figure title "F2FI Register" for Figure 28.7 is corrected as follows: "E2FI Register"

- •Page 578 of 639, description for EERR bit setting in Figure 28.12 is corrected as follows: "EERR bit in the E2FS0 register is 0?"

•Page 589 of 639, Table 29.13 is corrected as follows:

| Symbol                   | Characteristics                      | Measurement         | Value |      |      | Unit |

|--------------------------|--------------------------------------|---------------------|-------|------|------|------|

|                          |                                      | condition           | Min.  | Тур. | Max. | Onit |

| f <sub>SO(PLL)</sub>     | PLL clock self-oscillation frequency |                     | 35    | 57   | 80   | MHz  |

| $ \Delta f_{LOCK} $      | Lock detection <sup>(1)</sup>        |                     |       |      | 2    | %    |

| $ \Delta f_{UNLOCK} $    | Unlock detection <sup>(1)</sup>      |                     | 2     |      |      | %    |

| t <sub>LOCK(PLL)</sub>   | PLL lock time <sup>(2, 3)</sup>      | $f_{(XRef)} = 4MHz$ |       |      | 1    | ms   |

| t <sub>jitter(p-p)</sub> | PLL jitter period (p-p)              |                     |       |      | 2.0  | ns   |

| f <sub>(OCO)</sub>       | On-chip oscillator frequency         |                     | 94    | 125  | 156  | kHz  |

•Page 591 of 639, descriptions in Figure 29.5 are corrected as follows:

Figure 29.5 Flash Memory CPU Rewrite Mode Timing

•Page 621 of 639, description of the third bullet point in 30.4.3 is corrected as follows:

"The interrupt input signals to pins  $\overline{INT6}$  to  $\overline{INT8}$  are also connected to bits INT6R to INT8R in registers IIO9IR to IIO11IR. Therefore, these input signals, when assigned to the intelligent I/O, can be used as a source for exiting wait mode or stop mode. Note that these signals are enabled only on the falling edge and not affected by the following bit settings: bits POL and LVS in the INTIIC register (i = 0 to 8), IFSR0i bit (i = 0 to 5) in the IFSR0 register, and the IFSR1j bit (j = i - 6; i = 6 to 8) in the IFSR1 register."

•Page 626 of 639, descriptions in 30.7.1 are corrected as follows:

"When a low signal is applied to the NMI pin with the bit settings below, pins TA1OUT, TA2OUT, and TA4OUT become high-impedance: the PM24 bit in the PM2 register is 1 (NMI enabled), the SDE bit in the IOBC register is 1 (shutdown enabled), the INV02 bit in the INVC0 register is 1 (the three-phase motor control timers used), and the INV03 bit is 1 (the three-phase motor control timer output enabled)."

•Page 626 of 639, descriptions "overflows" and "overflow" in 30.7.2 are corrected as follows:

"Do not write to the TAi1 register (i = 1, 2, 4) in the timing that timer B2 underflows. Before writing to the TAi1 register, read the TB2 register to verify that sufficient time is left until timer B2 underflows. Then, immediately write to the TAi1 register so that no interrupt handler is performed during this write procedure. If the TB2 register indicates little time is left until the underflow, write to the TAi1 register after timer B2 underflows."

•Page 627 of 639, description of the fourth dash in 30.8.2.1 is replaced as follows:

"- The TE bit in the UiC1 register is set to 1 (transmission enabled).

- The RE bit in the UiC1 register is set to 1 (reception enabled). This bit setting is not required in transmit operation only.

- The TI bit in the UiC1 register is set to 0 (data held in the UiTB register)."

•Page 629 of 639, description in the ninth bullet point of 30.9.2 is corrected as follows:

"The external trigger cannot be used in DMAC operating mode. When the DMAC is configured to transfer converted results, do not read the AD00 register by a program."