発行日: 2011年12月14日

# RENESAS TECHNICAL UPDATE

〒211-8668 神奈川県川崎市中原区下沼部 1753 ルネサス エレクトロニクス株式会社

問合せ窓口 http://japan.renesas.com/inquiry

E-mail: csc@renesas.com

| 製   | 品分類                         | MPU & MCU | 発行番号   | TN-16C-A                               | 210A/J        | Rev.    | 第1版 |

|-----|-----------------------------|-----------|--------|----------------------------------------|---------------|---------|-----|

| 題名  |                             |           |        | 情報分類                                   | 技術情報          |         |     |

| 適   |                             |           | 対象ロット等 |                                        | MacCON D. 354 | a Curan | 23o |

| 用製品 | M16C/5LD グループ、M16C/56D グループ |           | 関連資料   | M16C/5LD、M1<br>ユーザーズマニュ<br>ア編 Rev.1.20 |               |         |     |

M16C/5LD、56D グループの仕様の一部を変更します。また、使用方法や設定手順を追加・変更します。 なお [ ] 内は M16C/5LD、M16C/56D グループ ユーザーズマニュアル ハードウェア編 Rev.1.20 上の掲載箇所を示します。

## 1.仕様変更

1.1 クロック [8.9.5 PLL 周波数シンセサイザ使用時]

PLL 周波数シンセサイザをご使用になる場合は、電源リップルの許容範囲内で電源電圧を安定させてください。表に電源リップルの許容範囲を、図に電源変動のタイミングを示します。

| en B         |                     |           | H (+ |    |     |      |

|--------------|---------------------|-----------|------|----|-----|------|

| 記号           | 項目                  | 最小        | 標準   | 最大 | 単位  |      |

| f(ripple)    | 電源リップル許容周波数(VCC)    |           |      | 10 | kHz |      |

| Vp-p(ripple) | 電源リップル許容振幅電圧        | (VCC=5V時) |      |    | 0.5 | V    |

|              |                     | (VCC=3V時) |      |    | 0.3 | V    |

| Vcc( ΔV/ΔT ) | 電源リップル立ち上がり/立ち下がり勾配 | (VCC=5V時) |      |    | 0.3 | V/ms |

|              |                     | (VCC=3V時) |      |    | 0.3 | V/ms |

G1BT レジスタには何も書かないでください。

(補足)

G1BT レジスタは、G1BCR1 レジスタの BTS ビットを "0" (ベースタイマリセット)にすると、"0000h" になります。この機能は従来どおり変更ありません。

- 2. 使用上の注意事項の変更

- 2.1 時間測定機能選択時の割り込み要求 [18.5.6 時間測定機能選択時の割り込み要求]

G1FS レジスタの FSCj (j=0~7)ビットを "1" (時計計測機能)、かつ G1FE レジスタの IFEj ビットを "1" に すると、最大で fBT1 の 2 サイクル後に G1IR レジスタの G1IRj ビットや ICOCiIC (i=0、1)、ICOCHjIC (ただ し j=0~3)レジスタの IR ビットが "1" (割り込み要求あり)になることがあります。

発行日: 2011年12月14日

このため、IC/OC 割り込み i または IC/OC チャネル j 割り込みを使用する場合、FSCj ビットを "1" かつ IFEj ビットを "1" にした後、次の処理をしてください。

- (1) fBT1 の 2 サイクル以上待つ

- (2) ICOCiIC、ICOCHjIC レジスタの IR ビットを"0" にする

- (3) (時間測定機能選択から fBT1 の 3 サイクル以上待ってから)G1IR レジスタを "00h" にする (G1IR レジスタは ICOCiIC レジスタの IR ビットを "0" にした後で、"00h" にする)

- 3. 使用方法、設定手順等の追加・変更

- 3.1 フラッシュメモリ

- 3.1.1 ユーザブートプログラム [26.11.4.1 ユーザブートプログラム]

ユーザブートモードに次の注意事項を追加します。

- ・ユーザブートモードで起動し実行するプログラムは、プログラム ROM2 に配置してください。

- ・OFS1 番地の LVDAS ビット、OFS2 番地の WDTRCS1~WDTRCS0 ビットはブートモードでは無効です。

- ・ユーザブートモードで起動した後、再度ユーザブートモードで起動すると RAM が不定になります。

- 13FF8h~13FFBh 番地の値がすべて "00h" の場合は、標準シリアル入出力モードにはなりません。 したがって、ライタやオンチップデバッガには接続できません。

- ・リセットシーケンスが異なりますので、プログラムを実行し始めるまでの時間がシングルチップモードより 長くなります。

- ・ユーザブートモードの機能は、オンチップデバッギングエミュレータ、フルスペックエミュレータでは デバッグできません。

- ・ユーザブート機能使用中は、ユーザブートモードエントリに使用する端子の入力レベルを変更しないでください。入力レベルが変化する場合は、ユーザブートモードで必要な処理を行った後、入力レベルが変化する前にシングルチップモードで起動し直してください。

- ・標準シリアル入出力モード後、ユーザブートモードを使用する場合、標準シリアル入出力モードを使用した後、一度電源を切り、再度電源を立ち上げてください(コールドスタートしてください)。このとき、ユーザブートモードになる条件が整っていれば、ユーザブートモードになります。

#### 3.1.2 サスペンド機能許可時の手順

[26.8.1.1 サスペンド機能(EW0 モード)、26.8.2.1 サスペンド機能(EW1 モード)]

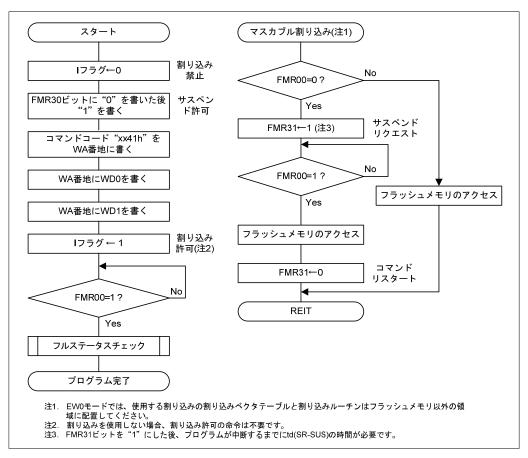

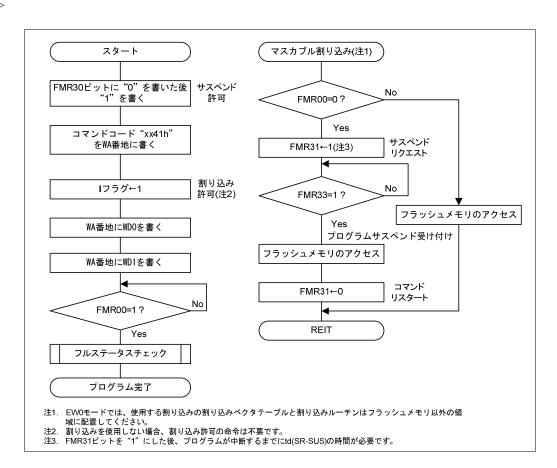

サスペンド機能許可時の手順を変更します。変更する図と変更箇所は次の通りです。次のページに EW0 モードのプログラムコマンドの例を示します。

# <変更する図>

EW0 モードのプログラムフローチャート(サスペンド機能許可時)

EW0 モードのブロックイレーズフローチャート(サスペンド機能許可時)

EW0 モードのロックビットプログラムフローチャート(サスペンド機能許可時)

## <変更箇所>

- ·Iフラグを"1"(割り込み許可)にする場所を変更します。

- ・マスカブル割り込みルーチンで判定に使用するフラグを FMR32 ビットまたは FMR33 ビットから FMR00 ビットに変更します。

## <変更する図>

EW1 モードのプログラムフローチャート(サスペンド機能許可時)

EW1 モードのブロックイレーズフローチャート(サスペンド機能許可時)

EW1 モードのロックビットプログラムフローチャート(サスペンド機能許可時)

#### <変更箇所>

·Iフラグを"1"(割り込み許可)にする場所を変更します。

発行日: 2011年12月14日

# 発行日: 2011年12月14日

# <変更後>

EW0モードのプログラムフローチャート(サスペンド機能許可時)

# <変更前>

EW0 モードのプログラムフローチャート(サスペンド機能許可時)

# RENESAS TECHNICAL UPDATE TN-16C-A210A/J

4. 電気的特性の追加・変更

4.1 推奨動作条件 VCC [27.1.2 推奨動作条件]

VCC 電源電圧の最小値の規格を訂正します。

| 記号  | 項目   |     | 規格値 | 直  | 単位  |   |

|-----|------|-----|-----|----|-----|---|

|     |      | 最小  |     | 標準 | 最大  |   |

|     |      | 変更前 | 変更後 |    |     |   |

| VCC | 電源電圧 | 3.0 | 2.7 |    | 5.5 | V |

4.2 電圧検出 2 回路 [27.1.5 電圧検出回路、電源回路の電気的特性]

電圧検出 2 回路の電圧検出レベル Vdet2\_0~Vdet2\_3、Vdet2\_5~Vdet2\_7 の規格を追加します。

| 記号      | 項目              | 測定条件       |          | 規格値  |    | 単位 |

|---------|-----------------|------------|----------|------|----|----|

|         |                 |            | 最小       | 標準   | 最大 |    |

| Vdet2_0 | 電圧検出レベル Vdet2_0 | VCC 立ち下がり時 |          | 3.21 |    | V  |

| Vdet2_1 | 電圧検出レベル Vdet2_1 |            |          | 3.36 |    | V  |

| Vdet2_2 | 電圧検出レベル Vdet2_2 |            |          | 3.51 |    | V  |

| Vdet2_3 | 電圧検出レベル Vdet2_3 |            |          | 3.66 |    | V  |

| Vdet2_5 | 電圧検出レベル Vdet2_5 |            |          | 3.96 |    | V  |

| Vdet2_6 | 電圧検出レベル Vdet2_6 |            |          | 4.10 |    | V  |

| Vdet2_7 | 電圧検出レベル Vdet2_7 |            | <u> </u> | 4.25 |    | V  |

4.3 電源回路のタイミング特性 [27.1.5 電圧検出回路、電源回路の電気的特性]

td(W-S)の最大値を変更します。

| 記号      | 項目                     | 測定条件         | 規格値 |    |     |     | 単  |

|---------|------------------------|--------------|-----|----|-----|-----|----|

|         |                        |              | 最小  | 標準 | 最   | 大   | 位  |

|         |                        |              |     |    | 変更前 | 変更後 |    |

| td(W-S) | 低消費電力モードウェイトモード解<br>除時 | Vcc=3.0~5.5V |     |    | 150 | 300 | μs |

4.4 発振回路 「27.1.6 発振回路の電気的特性」

ウォッチドッグタイマ専用 125kHz オンチップオシレータの規格を追加します。

| 記号           | 項目                                      |     | 規格値 |     | 単位  |

|--------------|-----------------------------------------|-----|-----|-----|-----|

|              |                                         | 最小  | 標準  | 最大  |     |

| $ m f_{WDT}$ | ウォッチドッグタイマ専用 125kHz オンチップオシレータ<br>発振周波数 | 100 | 125 | 150 | kHz |

発行日: 2011年12月14日

## 4.5 ヒステリシス VT+-VT- TA0IN 他

[27.2.1 電気的特性 (VCC=5V)]

下の $V_{T+}$ - $V_{T}$  ヒステリシスの最大値を変更します。

| 記号              | 項目     |                              | 測定 規格値 |     |    |     |           | 単 |

|-----------------|--------|------------------------------|--------|-----|----|-----|-----------|---|

|                 |        |                              | 条件     | 最小  | 標準 | 最   | <b></b> 大 | 位 |

|                 |        |                              |        |     |    | 変更前 | 変更後       |   |

| $V_{T+}-V_{T-}$ | ヒステリシス | TA0IN~TA4IN, TB0IN~TB2IN,    |        | 0.2 |    | 2.5 | 0.4VCC    | V |

|                 |        | <u>INT0~INT5</u> , NMI,      |        |     |    |     |           |   |

|                 |        | ADTRG, CTS0~CTS3, SCL2,      |        |     |    |     |           |   |

|                 |        | SDA2, CLK0~CLK4,             |        |     |    |     |           |   |

|                 |        | TA0OUT~TA4OUT,               |        |     |    |     |           |   |

|                 |        | KIO~KI3, RXDO~RXD4, ZP, IDU, |        |     |    |     |           |   |

|                 |        | IDW, IDV, SD,                |        |     |    |     |           |   |

|                 |        | INPC1_0~INPC1_7, CRX0        |        |     |    |     |           |   |

[27.3.1 電気的特性 (VCC=3V)]

下の $V_{T+}$ - $V_{T-}$  ヒステリシスの最大値を変更します。

| 記号                    | 項目     |                                                                                             | 測定 |    | 夫  | 見格値 |           | 単 |

|-----------------------|--------|---------------------------------------------------------------------------------------------|----|----|----|-----|-----------|---|

|                       |        |                                                                                             | 条件 | 最小 | 標準 | 最   | <b></b> 大 | 位 |

|                       |        |                                                                                             |    |    |    | 変更前 | 変更後       |   |

| $V_{T^+}$ - $V_{T^-}$ | ヒステリシス | TA0IN~TA4IN, TB0IN~TB2IN,                                                                   |    |    |    | 1.8 | 0.4VCC    | V |

|                       |        | $\overline{\text{INT0}} \sim \overline{\text{INT5}}, \overline{\text{NMI}},$                |    |    |    |     |           |   |

|                       |        | $\overline{\text{ADTRG}}, \overline{\text{CTS0}} \sim \overline{\text{CTS3}}, \text{SCL2},$ |    |    |    |     |           |   |

|                       |        | SDA2, CLK0~CLK4,                                                                            |    |    |    |     |           |   |

|                       |        | TA0OUT~TA4OUT,                                                                              |    |    |    |     |           |   |

|                       |        | KIO~KI3, RXDO~RXD4, ZP, IDU,                                                                |    |    |    |     |           |   |

|                       |        | IDW, IDV, SD,                                                                               |    |    |    |     |           |   |

|                       |        | INPC1_0~INPC1_7, CRX0                                                                       |    |    |    |     |           |   |

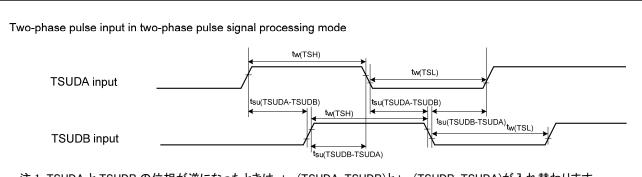

# 4.6 タイマS入力 二相パルス入力 [27.2.2.5 タイマS入力、27.3.2.5 タイマS入力]

二相パルス信号処理モードの二相パルス入力の規格を追加します。

端子名も P8\_0 に TSUDA、P8\_1 に TSUDB を追加しました。

| 記号               | 項目                    | 規格 | ·値 | 単位 |

|------------------|-----------------------|----|----|----|

|                  |                       | 最小 | 最大 |    |

| tw(TSH)          | TSUDA、TSUDB 入力"H"パルス幅 | 2  |    | μs |

| tw(TSL)          | TSUDA、TSUDB 入力"L"パルス幅 | 2  |    | μs |

| tsu(TSUDA-TSUDB) | TSUDB 入力セットアップ時間      | 1  |    | μs |

| tsu(TSUDB-TSUDA) | TSUDA 入力セットアップ時間      | 1  |    | μs |

注 1. TSUDAとTSUDBの位相が逆になったときは、tsu(TSUDA-TSUDB)とtsu(TSUDB-TSUDA)が入れ替わります。

以上

発行日: 2011年12月14日