# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                                                 |                | Document<br>No.         | TN-RX*-A185A/E                                                                                                                                                         | Rev. | 1.00 |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| Title                 | Corrections to Descriptions for the P/E Suspend<br>Command of Flash Memory in RX62N Group, RX621<br>Group, RX62T Group, and RX62G Group |                | Information<br>Category | Technical Notification                                                                                                                                                 |      |      |

| Applicable<br>Product | RX62N Group,<br>RX621 Group,<br>RX62T Group,<br>RX62G Group                                                                             | Lot No.<br>All | Reference<br>Document   | RX62N Group, RX621 Group<br>User's Manual: Hardware Rev.1.40<br>(R01UH0033EJ0140)<br>RX62T Group, RX62G Group<br>User's Manual: Hardware Rev.2.00<br>(R01UH0034EJ0200) |      |      |

This document describes corrections to the descriptions for the SUSRDY bit and the flow chart of the P/E suspend command in the "ROM (Flash Memory for Code Storage)" section of User's Manual: Hardware for the applicable products mentioned above.

Page and section numbers are based on the RX62N Group and RX621 Group. Refer to the table on the last page for the corresponding page and section numbers in the RX62T Group and RX62G Group.

## • Page 1780 of 2026

Clearing conditions of the SUSRDY bit in section 38.2.5, Flash Status Register 0 (FSTATR0) are corrected as follows.

### **Before Correction**

[Clearing conditions]

- The FCU has accepted a P/E suspend command.

- During programming/erasure process, the FCU enters the command-locked state.

#### After Correction

[Clearing conditions]

- The FCU has accepted a P/E suspend command.

- During programming/erasure process, the FCU enters the command-locked state.

- When programming/erasure process has been completed.

#### • Page 1817 of 2026

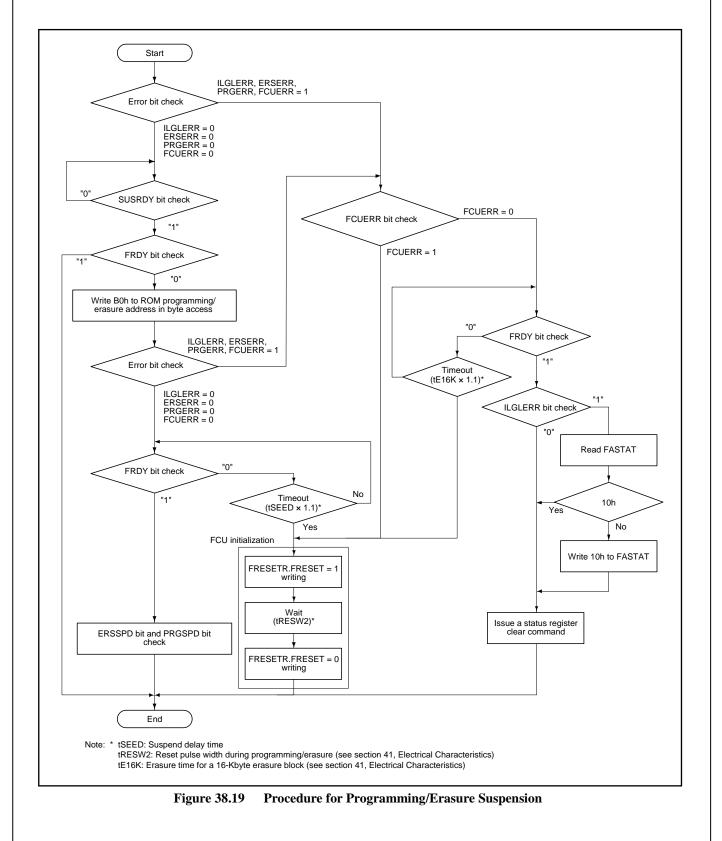

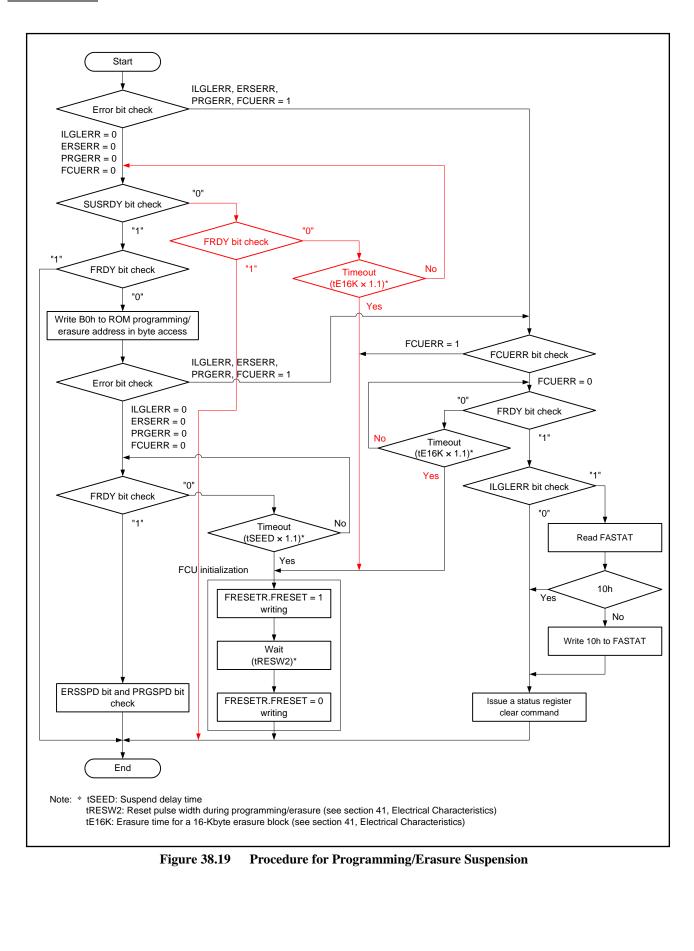

In Figure 38.19, Procedure for Programming/Erasure Suspension, a processing flow never escapes from the loop for a checking procedure if the programming/erasure processing completed before checking the SUSRDY bit. Therefore, a timeout processing and a breaking processing when the FRDY bit is 1 are to be added.

#### Before correction

#### After correction

#### Reference Documents

| Group          | Manual Title                                              | Document Number | Page                                   | Number                 |  |  |  |

|----------------|-----------------------------------------------------------|-----------------|----------------------------------------|------------------------|--|--|--|

| RX62N<br>RX621 | RX62N Group, RX621 Group User's Manual: Hardware Rev.1.40 | R01UH0033EJ0140 | Page 1780 of 2026<br>Page 1817 of 2026 | 38.2.5<br>Figure 38.19 |  |  |  |

| RX62T<br>RX62G | RX62T Group, RX62G Group User's Manual: Hardware Rev.2.00 | R01UH0034EJ0200 | Page 1340 of 1489<br>Page 1374 of 1489 | 31.2.5<br>Figure 31.19 |  |  |  |

End of document