Date: Oct. 28, 2015

# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                                | Document<br>No.         | TN-RL*-A055A/E                                                                             | Rev. | 1.00 |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------|------|------|--|

| Title                 | Correction for Incorrect Description Notice<br>RL78/G1C Descriptions in the User's Manua<br>Hardware Rev. 1.10 Changed | Information<br>Category | Technical Notification                                                                     |      |      |  |

|                       |                                                                                                                        | Lot No.                 |                                                                                            |      |      |  |

| Applicable<br>Product | RL78/G1C Group                                                                                                         | All Lots                | Reference<br>Document RL78/G1C User's Manual: Ha<br>Rev. 1.10<br>R01UH0348EJ0110 (Nov. 201 |      |      |  |

This document describes misstatements found in the RL78/G1C User's Manual: Hardware Rev. 1.10 (R01UH0348EJ0110).

# **Corrections**

| Applicable Item                                                                                             | Applicable<br>Page | Contents                          |

|-------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------|

| 5.3.10 PLL control register (DSCCTL)                                                                        | p.136              | Additional entry                  |

| 5.4.5 PLL (Phase Locked Loop)                                                                               | p.142              | Incorrect descriptions<br>revised |

| 5.6.4 Example of setting PLL circuit                                                                        | p.148              | Incorrect descriptions<br>revised |

| 5.6.5 CPU clock status transition diagram                                                                   | p.149              | Incorrect descriptions<br>revised |

| 5.6.5 CPU clock status transition diagram Table 5-4. CPU Clock Transition and SFR Register Setting Examples | p.150 –<br>p.154   | Incorrect descriptions<br>revised |

| 5.6.6 Condition before changing CPU clock and processing after changing CPU clock                           | p.157 –<br>p.168   | Incorrect descriptions revised    |

| 7.3.4 Real-time clock control register 1 (RTCC1)                                                            | p.280              | Additional entry                  |

#### **Document Improvement**

The above corrections will be made for the next revision of the User's Manual: Hardware.

# Corrections in the User's Manual: Hardware

|    |                                                                                                               | Correction              | ns and Applicable Ite | ms     |                  | Pages in this               |

|----|---------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|--------|------------------|-----------------------------|

| No |                                                                                                               | Document No.            | English               | R01UH0 | 348EJ0110        | document for<br>corrections |

| 1  | 5.3.10 PLL control                                                                                            | register (DSCCTL)       |                       |        | p.136            | p.3                         |

| 2  | 5.4.5 PLL (Phase L                                                                                            | ocked Loop)             |                       |        | p.142            | p.4                         |

| 3  | 3 5.6.4 Example of setting PLL circuit                                                                        |                         |                       |        |                  | p.6 – p.7                   |

| 4  | 5.6.5 CPU clock sta                                                                                           |                         | p.149                 | p.8    |                  |                             |

| 5  | 5 5.6.5 CPU clock status transition diagram Table 5-4. CPU Clock Transition and SFR Register Setting Examples |                         |                       |        | p.150 –<br>p.154 | p.9 – p.15                  |

| 6  | 6 5.6.6 Condition before changing CPU clock and processing after changing CPU clock                           |                         |                       |        | p.157 –<br>p.168 | p.16 – p.17                 |

| 7  | 7.3.4 Real-time cloo                                                                                          | ck control register 1 ( | RTCC1)                |        | p.280            | p.18                        |

# Incorrect: Bold with underline; Correct: Gray hatched

# **Revision History**

RL78/G1C Correction for incorrect description notice

| Document Number | Issue Date    | Description                                                              |

|-----------------|---------------|--------------------------------------------------------------------------|

| TN-RL*-A046A/E  | Jul. 6 , 2015 | Correction No.7 revised                                                  |

| TN-RL*-A055A/E  | Oct. 28, 2015 | First edition issued<br>Corrections No.1 to No.6 revised (This document) |

#### 1. 5.3.10 PLL control register (DSCCTL) (Page 136)

Additional entry to Figure 5 - 11 Format of PLL control register (DSCCTL)

# <u>Old:</u>

#### Figure 5-11. Format of PLL Control Register (DSCCTL)

| Address: | F02E5H | After rese | et: 00H | R/W |   |         |      |       |

|----------|--------|------------|---------|-----|---|---------|------|-------|

| Symbol   | 7      | 6          | 5       | 4   | 3 | 2       | 1    | 0     |

| DSCCTL   | 0      | 0          | 0       | 0   | 0 | DSFRDIV | DSCM | DSCON |

| DSFRDIV | PLL reference clock divider control |  |  |  |

|---------|-------------------------------------|--|--|--|

| 0       | No division                         |  |  |  |

| 1       | Divided by 2                        |  |  |  |

**Remark** PLL reference clock is the high-speed system clock (f<sub>MX</sub>).

| DSCM | PLL multiplication selection |

|------|------------------------------|

| 0    | 12 times (6 times)           |

| 1    | 16 times (8 times)           |

**Remark** The frequency is divided by 2 in the last stage of the PLL oscillator,

therefore the multiplication ratio becomes the value in parentheses.

| DSCON | PLL oscillation and output control |

|-------|------------------------------------|

| 0     | Stop                               |

| 1     | Ocsillation, output                |

Caution Be sure to clear bits 3 to 7 to 0.

### New:

#### Figure 5-11. Format of PLL Control Register (DSCCTL)

| Address: | F02E5H | After rese | et: 00H | R/W |   |         |      |       |

|----------|--------|------------|---------|-----|---|---------|------|-------|

| Symbol   | 7      | 6          | 5       | 4   | 3 | 2       | 1    | 0     |

| DSCCTL   | 0      | 0          | 0       | 0   | 0 | DSFRDIV | DSCM | DSCON |

| DSFRDIV | PLL reference clock divider control |

|---------|-------------------------------------|

| 0       | No division                         |

| 1       | Divided by 2                        |

**Remark** PLL reference clock is the high-speed system clock (f<sub>MX</sub>).

| DSCM | PLL multiplication selection |

|------|------------------------------|

| 0    | 12 times (6 times)           |

| 1    | 16 times (8 times)           |

Remark The frequency is divided by 2 in the last stage of the PLL oscillator,

therefore the multiplication ratio becomes the value in parentheses.

| DSCON | PLL oscillation and output control |

|-------|------------------------------------|

| 0     | Stop                               |

| 1     | Ocsillation, output                |

Caution 1. Be sure to clear bits 3 to 7 to 0.

Caution 2. Be sure to set the DSCON bit to 0 before changing DSFRDIV and DSCM.

Caution 3. Do not set the DSCON bit to 0 while the PLL clock is selected as the system

clock.

#### 2. 5.4.5 PLL (Phase Locked Loop) (Page 142)

Incorrect descriptions revised to Caution 2.

# <u>Old:</u>

Caution 1. When switching from PLL mode to the internal high-speed oscillation clock and the high speed system clock, stop the function (USB function controller) that provides the PLL output clock (f<sub>PLL</sub>).

Caution 2. PLL operations cannot be performed while the subsystem clock is

operating

Date: Oct. 28, 2015

# New:

Caution 1. When switching from PLL mode to the internal high-speed oscillation clock and the high speed system clock, stop the function (USB function controller) that provides the PLL output clock (f<sub>PLL</sub>).

Caution 2. Do not set the DSCON bit to 1 to start the PLL operating while the subsystem clock is the operating clock for the CPU.

#### 3. 5.6.4 Example of setting PLL circuit (Page 148)

Incorrect descriptions revised to 5.6.4 Example of setting PLL circuit.

# <u>Old:</u>

[Register settings] Set the register in the order of <1> to <5> below.

<1> Set the DSFRDIV bit and DSCM bit in the DSCCTL register to set the PLL multiplication and division.

|             | 7          | 6          | 5         | 4                                                                                                     | 3          | 2           | 1          | 0        |

|-------------|------------|------------|-----------|-------------------------------------------------------------------------------------------------------|------------|-------------|------------|----------|

| DOCOTI      |            |            |           |                                                                                                       |            | DSFRDIV     | DSCM       | DSCON    |

| DSCCTL      | 0          | 0          | 0         | 0                                                                                                     | 0          | 0/1         | 0/1        | 0        |

| <2> Set the | e RDIV1, F | RDIV0 bits | of the MC | <c register<="" td=""><td>to set the</td><td>division of</td><td>the system</td><td>n clock.</td></c> | to set the | division of | the system | n clock. |

|             | 7          | 6          | 5         | 4                                                                                                     | 3          | 2           | 1          | 0        |

|             |            |            |           |                                                                                                       |            |             |            |          |

| MCKC |   |   |   |   |   | RDIV1 | RDIV0 | CKSELR |

|------|---|---|---|---|---|-------|-------|--------|

| MCKC | 0 | 0 | 0 | 0 | 0 | 0/1   | 0/1   | 0      |

AMPHS0 and AMPHS1 bits: These bits are used to specify the oscillation mode of the XT1 oscillator.

<3> Set (1) the DSCON bit of the DSCCTL register to operate the PLL circuit Note.

|        | 7 | 6 | 5 | 4 | 3 | 2       | 1    | 0     | _ |

|--------|---|---|---|---|---|---------|------|-------|---|

| DOOOTI |   |   |   |   |   | DSFRDIV | DSCM | DSCON |   |

| DSCCTL | 0 | 0 | 0 | 0 | 0 | 0/1     | 0/1  | 1     |   |

#### <4> Wait for 40 $\mu$ s by using software.

<5> Set (1) the CKSELR bit of the MCKC register to select PLL output for the system clock.

|      | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0      |

|------|---|---|---|---|---|-------|-------|--------|

| MCKC |   |   |   |   |   | RDIV1 | RDIV0 | CKSELR |

| MCKC | 0 | 0 | 0 | 0 | 0 | 0/1   | 0/1   | 1      |

**Note** After the X1 oscillator clock stabilizes, allow at least 1  $\mu$  s to elapse before operating the PLL. When operating the PLL again after it has been stopped, wait for at least 4  $\mu$  s before operating.

# New:

[Register settings] Set the register in the order of <1> to <5> below.

<1> Set the HIOSTOP bit in the CSC register to make the high-speed on-chip oscillator run.

|     | 7   | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|-----|-----|---|---|---|---|---|---|

| CSC | 0/1 | 0/1 | 0 | 0 | 0 | 0 | 0 |   |

|     | 0/1 | 0/1 | U | 0 | 0 | 0 | U | 0 |

<2> Set the DSFRDIV bit and DSCM bit in the DSCCTL register to set the PLL multiplication

and division.

| _      | 7 | 6 | 5 | 4 | 3 | 2       | 1    | 0     |

|--------|---|---|---|---|---|---------|------|-------|

| DECCTI |   |   |   |   |   | DSFRDIV | DSCM | DSCON |

| DSCCTL | 0 | 0 | 0 | 0 | 0 | 0/1     | 0/1  | 0     |

<3> Set the RDIV1, RDIV0 bits of the MCKC register to set the division of the system clock.

|      | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0      |

|------|---|---|---|---|---|-------|-------|--------|

| MOKO |   |   |   |   |   | RDIV1 | RDIV0 | CKSELR |

| MCKC | 0 | 0 | 0 | 0 | 0 | 0/1   | 0/1   | 0      |

AMPHS0 and AMPHS1 bits: These bits are used to specify the oscillation mode of the XT1 oscillator.

#### <4> Set (1) the DSCON bit of the DSCCTL register to operate the PLL circuit Note.

|            | 7         | 6            | 5       | 4           | 3          | 2          | 1          | 0        |

|------------|-----------|--------------|---------|-------------|------------|------------|------------|----------|

| DSCCTL     |           |              |         |             |            | DSFRDIV    | DSCM       | DSCON    |

| DSCCIL     | 0         | 0            | 0       | 0           | 0          | 0/1        | 0/1        | 1        |

| <5> Set (1 | ) the CKS | ELR bit of t | he MCKC | register to | select PLL | output for | the system | n clock. |

|            | 7         | c            | F       | 4           | 2          | 2          | 4          | 0        |

|      | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0      |

|------|---|---|---|---|---|-------|-------|--------|

| МСКС |   |   |   |   |   | RDIV1 | RDIV0 | CKSELR |

| MCKC | 0 | 0 | 0 | 0 | 0 | 0/1   | 0/1   | 1      |

| Date: | Oct. | 28, | 2015 |

|-------|------|-----|------|

|-------|------|-----|------|

| <6> Use s                                                                                               | <6> Use software to set up a wait of 65 μs. <sup>Note3</sup>                                                 |           |               |             |     |   |   |   |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------|---------------|-------------|-----|---|---|---|--|--|--|--|--|

| <7> Set the HIOSTOP bit in the CSC register to stop the high-speed on-chip oscillator. <sup>Note2</sup> |                                                                                                              |           |               |             |     |   |   |   |  |  |  |  |  |

|                                                                                                         | 7 6 5 4 3 2 1 0<br>HIOSTOP                                                                                   |           |               |             |     |   |   |   |  |  |  |  |  |

| CSC                                                                                                     | 0/1 0/1 0 0 0 0 1 <sup>Note1</sup>                                                                           |           |               |             |     |   |   |   |  |  |  |  |  |

| <8> When                                                                                                | <8> When the PLL clock frequency divided by 2, 4, or 8 is selected as the main system clock                  |           |               |             |     |   |   |   |  |  |  |  |  |

| (f <sub>MAIN</sub> ), set                                                                               | (f <sub>MAIN</sub> ), set the MCM0 bit in the CKC register to select the source for deriving the main system |           |               |             |     |   |   |   |  |  |  |  |  |

| clock as a                                                                                              | signal with                                                                                                  | a frequen | cy (fін) of u | ip to 24 Mł | Ηz. |   |   |   |  |  |  |  |  |

|                                                                                                         | 7                                                                                                            | 6         | 5             | 4           | 3   | 2 | 1 | 0 |  |  |  |  |  |

| СКС                                                                                                     | CLS                                                                                                          | CSS       | MCS           | MCM0        |     |   |   |   |  |  |  |  |  |

| ono                                                                                                     | 0/1                                                                                                          | 0/1       | 0             | 0           | 0   | 0 | 0 | 0 |  |  |  |  |  |

|                                                                                                         |                                                                                                              |           |               |             |     |   |   |   |  |  |  |  |  |

| Note 1. No setting is required to change to the PLL while the CKSELR bit is 1.                          |                                                                                                              |           |               |             |     |   |   |   |  |  |  |  |  |

| W                                                                                                       | When setting the CKSELR bit to 1, ensure that the high-speed on-chip oscillator is                           |           |               |             |     |   |   |   |  |  |  |  |  |

| ru                                                                                                      | nning.                                                                                                       |           |               |             |     |   |   |   |  |  |  |  |  |

Note 2. After oscillation by the X1 oscillator clock has become stable, allow at least 1  $\mu$ s to elapse before starting the PLL. When restarting the PLL after it has been stopped, wait for at least 4  $\mu$ s before using it in operations.

Note 3. Wait for 40  $\mu s$  for oscillation by the oscillator clock to become stabled if the HIOSTOP

bit is not set to 0.

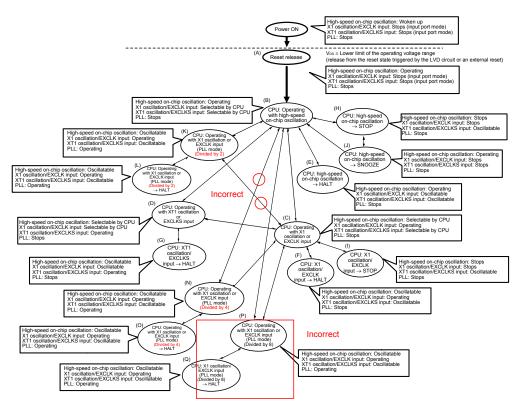

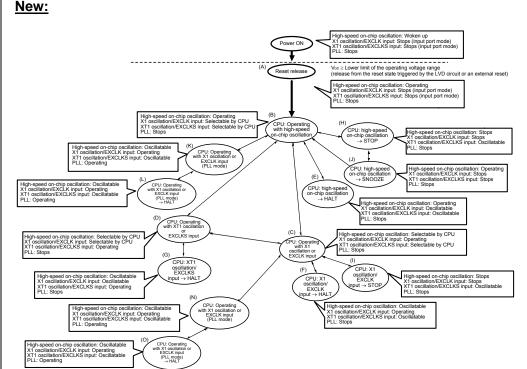

# 4. 5.6.5 CPU clock status transition diagram (Page 149)

Incorrect descriptions revised to Figure 5 - 18 CPU Clock Status Transition Diagram

# <u>Old:</u>

# 5. 5.6.5 CPU clock status transition diagram

# Table 5 - 4 CPU Clock Transition and SFR Register Setting Examples (pages 150 to 154)

# <u>Old:</u>

(2) CPU operating with high-speed system clock (C) after reset release (A)

(The CPU operates with the high-speed on-chip oscillator clock immediately after a reset release (B).)

| (Setting sequence of SFR registers)                                                                                |       |         |                     |                  |                 |                        |                 |

|--------------------------------------------------------------------------------------------------------------------|-------|---------|---------------------|------------------|-----------------|------------------------|-----------------|

| Setting Flag of SFR Register                                                                                       | СМС   | Registe | r <sup>Note 1</sup> | OSTS<br>Register | CSC<br>Register | OSTC<br>Register       | CKC<br>Register |

| Status Transition                                                                                                  | EXCLK | OSCSEL  | AMPH                |                  | MSTOP           |                        | MCM0            |

| $\begin{array}{l} (A) \rightarrow (B) \rightarrow (C) \\ (X1 \ clock: 1 \ MHz \leq f_X \leq 10 \ MHz) \end{array}$ | 0     | 1       | 0                   | Note 2           | 0               | Must be<br>checked     | 1               |

| $\begin{array}{l} (A) \rightarrow (B) \rightarrow (C) \\ (X1 \ clock: 10 \ MHz < f_X \leq 20 \ MHz) \end{array}$   | 0     | 1       | Q                   | Note 2           | 0               | Must be<br>checked     | 1               |

| $(A) \rightarrow (B) \rightarrow (C)$<br>(external main clock)                                                     | 1     | 1       | ×                   | Note 2           | 0               | Must not be<br>checked | 1               |

#### New:

(2) CPU operating with high-speed system clock (C) after reset release (A)

(The CPU operates with the high-speed on-chip oscillator clock immediately after a reset release (B).)

| (Setting sequence of SFR registers)                                                                                |                     |        |      |                  |                 |                     |                 |

|--------------------------------------------------------------------------------------------------------------------|---------------------|--------|------|------------------|-----------------|---------------------|-----------------|

| Setting Flag of SFR Register                                                                                       | CMC Register Note 1 |        |      | OSTS<br>Register | CSC<br>Register | OSTC<br>Register    | CKC<br>Register |

| Status Transition                                                                                                  | EXCLK               | OSCSEL | AMPH |                  | MSTOP           |                     | MCM0            |

|                                                                                                                    | 0                   | 1      | 0    | Note 2           | 0               | Must be<br>checked  | 1               |

| $\begin{array}{l} (A) \rightarrow (B) \rightarrow (C) \\ (X1 \ clock: 10 \ MHz < f_{X} \leq 20 \ MHz) \end{array}$ | 0                   | 1      | 1    | Note 2           | 0               | Must be<br>checked  | 1               |

| $(A) \rightarrow (B) \rightarrow (C)$<br>(external main clock)                                                     | 1                   | 1      | ×    | Note 2           | 0               | Must not be checked | 1               |

# Old:

(4) CPU clock changing from high-speed on-chip oscillator clock (B) to high-speed system

clock (C)

#### (Setting sequence of SFR -(Setting sequence of SER registers) Setting Flag of SFR Register CMC RegisterNote 1 OSTS CSC **OSTC** Register СКС Register Register Register Status Transition St EXCLK OSCSEL AMPH MSTOP MCM0 $(B) \rightarrow (C)$ 0 1 0 Note 2 0 Must be checked 1 (B (X1 clock: 1 MHz $\leq$ f<sub>x</sub> $\leq$ 10 MHz) (X $(B) \rightarrow (C)$ 0 Note 2 Must be checked 1 1 0 1 (B (X1 clock: 10 MHz < $f_X \le 20$ (X MHz) Μ (B) → (**D**)... 1 1 Note 2 0 Must not be 1 (B х checked (external main clock) (e Unnecessary if these Unnecessary if the CPU is registers are already set operating with the high-speed system clock (6) CPU clock changing from high-speed system clock (C) to high-speed on-chip oscillator (6) clock (B) cloo (Setting sequence of SFR registers) / Setting Flag of SFR Register CSC Register Oscillation accuracy **CKC** Register stabilization time HIOSTOP MCM0 Status Transition Stat 0 $(C) \rightarrow (B)$ Note 0 (C) Unnecessary if the CPU is operating with the high-speed on-chip oscillator clock the high-speed on-chip oscillator clock Note When FRQSEL4 = 0: 18 $\mu$ s to 65 $\mu$ s Note When FRQSEL4 = 0: 18 $\mu$ s to 65 $\mu$ s When FRQSEL4 = 1: 18 $\mu$ s to 75 $\mu$ s When FRQSEL4 = 1:18 $\mu$ s to 135 $\mu$ s

Date: Oct. 28, 2015

# New:

(4) CPU clock changing from high-speed on-chip oscillator clock (B) to high-speed system clock (C)

| registers)                                                                   |                       |                                                               |        |                       |                     |                                             |          |

|------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------|--------|-----------------------|---------------------|---------------------------------------------|----------|

| Setting Flag of SFR Register                                                 | СМС                   | CMC Register <sup>Note 1</sup> OSTS CSC O<br>RegisterRegister |        | OSTC Register         | CKC<br>Register     |                                             |          |

| Status Transition                                                            | EXCLK                 | OSCSEL                                                        | AMPH   |                       | MSTOP               |                                             | MCM0     |

| $B) \to (C)$                                                                 | 0                     | 1                                                             | 0      | Note 2                | 0                   | Must be checked                             | 1        |

| X1 clock: 1 MHz $\leq f_X \leq$ 10 MHz)                                      |                       |                                                               |        |                       |                     |                                             |          |

| $B) \to (C)$                                                                 | 0                     | 1                                                             | 1      | Note 2                | 0                   | Must be checked                             | 1        |

| X1 clock: 10 MHz < f <sub>X</sub> ≤ 20<br>MHz)                               |                       |                                                               |        |                       |                     |                                             |          |

| $B) \rightarrow (C)$                                                         | 1                     | 1                                                             | ×      | Note 2                | 0                   | Must not be                                 | 1        |

| external main clock)                                                         |                       |                                                               |        |                       |                     | checked                                     |          |

| ) CPU clock changing from hig<br>ock (B)<br>(Setting sequence of SFR registe | registers<br>gh-speed | sary if the                                                   | dy set | operating<br>system c | g with the<br>clock | e CPU is<br>high-speed<br>d on-chip oscilla | ator     |

| Setting Flag of SFR Regis                                                    | ster C                | SC Regis                                                      | ster   | Oscillatio            | on accura           | CKC                                         | Register |

| Sourig - idy of of the syloid                                                |                       | HIOSTO                                                        |        | stabilizat            |                     |                                             | CM0      |

| atus Transition                                                              |                       |                                                               |        |                       |                     |                                             |          |

|                                                                              |                       | 0                                                             |        |                       | Note                |                                             |          |

# <u>Old:</u>

(8) CPU clock changing from subsystem clock (D) to high-speed on-chip oscillator clock (B)

(Setting sequence of SFR registers)

| Setting Flag of SFR Register | CSC Register | Oscillation                    | CKC Register |

|------------------------------|--------------|--------------------------------|--------------|

| Status Transition            | HIOSTOP      | accuracy<br>stabilization time | CSS          |

| $(D) \to (B)$                | 0            | Note                           | 0            |

Unnecessary if the CPU is operating with the high-speed on-chip oscillator clock

Note When FRQSEL4 = 0: 18  $\mu$  s to 65  $\mu$  s

When FRQSEL4 = 1: 18  $\mu$  s to 75  $\mu$  s

Date: Oct. 28, 2015

# New:

(8) CPU clock changing from subsystem clock (D) to high-speed on-chip oscillator clock (B)

(Setting sequence of SFR registers)

| Setting Flag of SFR Register | CSC Register | Oscillation                    | CKC Register |

|------------------------------|--------------|--------------------------------|--------------|

| Status Transition            | HIOSTOP      | accuracy<br>stabilization time | CSS          |

| $(D) \rightarrow (B)$        | 0            | Note                           | 0            |

|                              |              |                                |              |

Unnecessary if the CPU is operating with the high-speed on-chip oscillator

clock

Note When FRQSEL4 = 0: 18  $\mu$  s to 65  $\mu$  s

When FRQSEL4 = 1:18  $\mu$  s to 135  $\mu$  s

# <u>Old:</u>

- (10) CPU clock changing from high-speed on-chip oscillator clock (B) to high-speed system clock (PLL mode) (divided by 2) (K)

- CPU clock changing from high-speed on-chip oscillator clock (B) to high-speed

system clock (PLL mode) (divided by 4) (N)

- CPU clock changing from high-speed on-chip oscillator clock (B) to high-speed

system clock (PLL mode) (divided by 8) (P)

- CPU clock changing from high-speed system clock (C) to high-speed system clock (PLL mode) (divided by 2) (K)

- CPU clock changing from high-speed system clock (C) to high-speed system clock (PLL mode) (divided by 4) (N)

- CPU clock changing from high-speed system clock (C) to high-speed system clock (PLL mode) (divided by 8) (P)

| (Setting sequence of SFR registers) |                     |            |                  |            |                            | >                 |

|-------------------------------------|---------------------|------------|------------------|------------|----------------------------|-------------------|

| Setting Flag of SFR Register        | DSCCTL.<br>Register |            | MCKC<br>Register |            | Waiting for<br>Oscillation | MCKC.<br>Register |

| Status Transition                   | DSFRDI<br>V         | DSCM       | RDIV1            | RDIVO      | Stabilization              | CKSELR            |

| (B)                                 | <b>0/1</b>          | <b>0/1</b> | <b>0/1</b>       | <b>Q/1</b> | 40.µs                      | 1                 |

| (B)                                 |                     |            |                  |            |                            |                   |

| (B)                                 |                     |            |                  |            |                            |                   |

| (C)                                 |                     |            |                  |            |                            |                   |

| (C)→.(N)                            |                     |            |                  |            |                            |                   |

| (C)                                 |                     |            |                  |            |                            |                   |

# New:

- (10) CPU clock changing from high-speed on-chip oscillator clock (B) to high-speed system clock (PLL mode) (K)

- CPU clock changing from high-speed system clock (C) to high-speed system clock (PLL mode) (N)

Continue

(Setting sequence of SFR registers)

| Setting Flag of SFR Register         | CMC Re | gister Note 1 |      | OSTS<br>Register | CSC<br>Register | OSTC<br>Register | DSCCTL F    | Register | MCKC  | Register | Waiting for<br>Oscillation | DSCCT<br>L<br>Register | Waiting for<br>Oscillation | MCKC<br>Registe<br>r |

|--------------------------------------|--------|---------------|------|------------------|-----------------|------------------|-------------|----------|-------|----------|----------------------------|------------------------|----------------------------|----------------------|

| Status Transition                    | EXCLK  | OSCSEL        | AMPH |                  | MSTOP           |                  | DSFRDI<br>V | DSCM     | RDIV1 | RDIV0    | Stabilization              | DSCON                  | Stabilization              | CKSEL<br>R           |

| (B) $\rightarrow$ (K) (divided by 2) | 0/1    | 1             | 0/1  | Note 2           | 0               | Must be checked  | 0/1         | 0/1      | 0     | 0        |                            | 1                      |                            | 1                    |

| (B) $\rightarrow$ (K) (divided by 4) | 0/1    | 1             | 0/1  | Note 2           | 0               | Must be checked  | 0/1         | 0/1      | 0     | 1        | 1us                        | 1                      | 40us                       | 1                    |

| (B) $\rightarrow$ (K) (divided by 8) | 0/1    | 1             | 0/1  | Note 2           | 0               | Must be checked  | 0/1         | 0/1      | 1     | 0        |                            | 1                      |                            | 1                    |

Note 1. Writing to the clock operating mode control register (CMC) can only proceed once and must be by an 8-bit memory manipulation instruction after release from the reset state.

Note 2. Set the oscillation stabilization time in the oscillation stabilization time select register (OSTS) as follows.

• Desired oscillation stabilization time setting of the oscillation stabilization time counter status register (OSTC) < Oscillation stabilization time set in the OSTS register

Caution: Completion of clock switching after the CKSELR bit has been set to 1 requires up to 2 clock cycles when the FRQSEL4 bit is 1, and up to 10 clock cycles when the FRQSEL4 bit is 0.

Until the clock switching is completed, do not stop the high-speed on-chip oscillator.

(Setting sequence of SFR registers)

| Setting Flag of SFR Register          | CSC<br>Register    | DSCCTL Registe | er   | MCKC Regi | ster  | DSCCTL<br>Register | MCKC<br>Register   | Waiting for<br>Oscillation | CSC<br>Register    | CKC<br>Register |

|---------------------------------------|--------------------|----------------|------|-----------|-------|--------------------|--------------------|----------------------------|--------------------|-----------------|

|                                       | HIOSTOP            | DSFRDIV        | DSCM | RDIV1     | RDIV0 | DSCON              | CKSELR             | Stabilization              | HIOSTOP            | MCM0            |

| $(C) \rightarrow (N)  (divided by 2)$ | 0 <sup>Note3</sup> | 0/1            | 0/1  | 0         | 0     | 1                  | 1 <sup>Note3</sup> |                            | 1 <sup>Note3</sup> | 0               |

| $(C) \rightarrow (N)  (divided by 2)$ | 0 <sup>Note3</sup> | 0/1            | 0/1  | 0         | 1     | 1                  | 1 <sup>Note3</sup> | 135us <sup>Note4</sup>     | 1 <sup>Note3</sup> | 0               |

| $(C) \rightarrow (N)$ (divided by 2)  | 0 <sup>Note3</sup> | 0/1            | 0/1  | 1         | 0     | 1                  | 1 <sup>Note3</sup> |                            | 1 <sup>Note3</sup> | 0               |

Note 3. No setting is required to change to the PLL while the CKSELR bit is 1. When setting the CKSELR bit to 1, ensure that the high-speed on-chip oscillator is running.

Note 4. Wait for 40  $\mu$ s for oscillation by the oscillator clock to become stable if the HIOSTOP bit is not set to 0

Date: Oct. 28, 2015

# <u>Old:</u>

- (11) CPU clock changing from high-speed system clock (PLL mode) (divided by 2) (K) to high-speed on-chip oscillator clock (B)

- CPU clock changing from high-speed system clock (PLL mode) (divided by 4)

(N) to high-speed on-chip oscillator clock (B)

- CPU clock changing from high-speed system clock (PLL mode) (divided by 8)

(P) to high-speed on-chip oscillator clock (B)

- CPU clock changing from high-speed system clock (PLL mode) (divided by 2) (K) to high-speed system clock (C)

- CPU clock changing from high-speed system clock (PLL mode) (divided by 4) (N) to high-speed system clock (C)

- CPU clock changing from high-speed system clock (PLL mode) (divided by 8)

(P) to high-speed system clock (C)

| (Setting sequence of SFR registers) - |               |                 |

|---------------------------------------|---------------|-----------------|

| Setting Flag of SFR Register          | MCKC Register | DSCCTL Register |

| Status Transition                     | CKSELR        | DSCON           |

| (K)(B)                                | Q             | Q               |

| (N)                                   |               |                 |

| (P)→.(B)                              |               |                 |

| (K)⇒.(C)                              |               |                 |

| (N)→.(C)                              |               |                 |

| (P).→.(C)                             |               |                 |

# New:

- (11) CPU clock changing from high-speed system clock (PLL mode) (K) to high-speed on-chip oscillator clock (B)

- CPU clock changing from high-speed system clock (PLL mode) (N) to high-speed system clock (C)

| Setting Flag of SFR Register    | CSC Register | Waiting for<br>Oscillation | MCKC<br>Register | Waiting<br>for  | DSCCTL<br>Register |

|---------------------------------|--------------|----------------------------|------------------|-----------------|--------------------|

| Status Transition               | HIOSTOP      | Stabilization              | CKSELR           | clock<br>change | DSCON              |

| (K) $\rightarrow$ (B) FRQSEL4=0 | 0            | 18∼65 µs                   | 0                | 256<br>clokc    | 0                  |

| (K) $\rightarrow$ (B) FRQSEL4=1 |              | 18∼135 µs                  |                  | 16<br>clock     |                    |

Continue

-►

(Setting sequence of SFR registers) -

| Setting Flag of SFR Register<br>Status Transition                                                                                                                      | CKC<br>Register<br>MCM0 | Waiting for<br>clock change | DSCCTL<br>Register<br>DSCON |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------|-----------------------------|

| (N) $\rightarrow$ (C) (divided by 2) (RDIV1,0 = 00)<br>High-speed system clock (fMX) = 16MHz                                                                           |                         | 3 Clock                     |                             |

| (N) $\rightarrow$ (C) (divided by 2) (RDIV1,0 = 00)<br>High-speed system clock (fMX) = 12MHz                                                                           |                         | 4 Clock                     |                             |

| (N) $\rightarrow$ (C) (divided by 2) (RDIV1,0 = 00)<br>High-speed system clock (fMX) = 8MHz                                                                            |                         | 6 Clock                     |                             |

| (N) $\rightarrow$ (C) (divided by 2) (RDIV1,0 = 00)<br>High-speed system clock (fMX) = 6MHz                                                                            |                         | 8 Clock                     |                             |

| (N) $\rightarrow$ (C) (divided by 4) (RDIV1,0 = 01)<br>High-speed system clock (fMX) = 16MHz                                                                           |                         | 2 Clock                     |                             |

| $\begin{array}{ll} ({\sf N}) & \rightarrow & ({\sf C}) & ({\rm divided \ by \ 4}) \ ({\sf RDIV1,0=01}) \\ {\rm High-speed \ system \ clock \ (fMX)=12MHz} \end{array}$ | 1                       | 2 Clock                     | 0                           |

| $\begin{array}{ll} (N) & \rightarrow & (C) & (\text{divided by 4})  (RDIV1,0=01) \\ \text{High-speed system clock (fMX) = 8MHz} \end{array}$                           |                         | 3 Clock                     | 0                           |

| (N) $\rightarrow$ (C) (divided by 4) (RDIV1,0 = 01)<br>High-speed system clock (fMX) = 6MHz                                                                            |                         | 4 Clock                     |                             |

| (N) $\rightarrow$ (C) (divided by 8) (RDIV1,0 = 10)<br>High-speed system clock (fMX) = 16MHz                                                                           |                         | 2 Clock                     |                             |

| (N) $\rightarrow$ (C) (divided by 8) (RDIV1,0 = 10)<br>High-speed system clock (fMX) = 12MHz                                                                           |                         | 2 Clock                     |                             |

| (N) $\rightarrow$ (C) (divided by 8) (RDIV1,0 = 10)<br>High-speed system clock (fMX) = 8MHz                                                                            |                         | 2 Clock                     |                             |

| $\begin{array}{ll} ({\sf N}) & \rightarrow & ({\sf C}) & ({\rm divided \ by \ 8}) \ ({\sf RDIV1,0=10}) \\ {\rm High-speed \ system \ clock \ (fMX)=6MHz} \end{array}$  |                         | 2 Clock                     |                             |

# <u>Old:</u>

(12)  $\bullet\,$  HALT mode (E) set while CPU is operating with high-speed on-chip oscillator clock

(B)

- HALT mode (F) set while CPU is operating with high-speed system clock (C)

- HALT mode (G) set while CPU is operating with subsystem clock (D)

- HALT mode (L) set while CPU is operating with high-speed system clock (PLL mode) (divided by 2) (K)

- HALT mode (O) set while CPU is operating with high-speed system clock (PLL mode) (divided by 4) (N)

HALT mode (Q) set while CPU is operating with high-speed system clock (PLL

#### mode) (divided by 8) (P)

| Status Transition     | Setting                    |

|-----------------------|----------------------------|

| $(B) \to (E)$         | Executing HALT instruction |

| $(C) \rightarrow (F)$ |                            |

| $(D) \rightarrow (G)$ |                            |

| $(K) \to (L)$         |                            |

| $(N) \rightarrow (Q)$ |                            |

| (P).→.(Q)             |                            |

(15) • STOP mode (I) set while CPU is operating with high-speed system clock (PLL mode)

#### (divided by 2) (K)

• STOP mode (I) set while CPU is operating with high-speed system clock (PLL

#### mode) (divided by 4) (N)

• STOP mode (I) set while CPU is operating with high-speed system clock (PLL

#### mode) (divided by 8) (P)

Switch from PLL mode operation to **high-speed on-chip oscillator clock** and high-speed system clock operations

(refer to 5.6.5 (11)) and stop the PLL (DSCON = 0), then execute the STOP instruction

Date: Oct. 28, 2015

# New:

(12) • HALT mode (E) set while CPU is operating with high-speed on-chip oscillator clock(B)

- HALT mode (F) set while CPU is operating with high-speed system clock (C)

- HALT mode (G) set while CPU is operating with subsystem clock (D)

• HALT mode (L) set while CPU is operating with high-speed system clock (PLL mode) (K)

• HALT mode (O) set while CPU is operating with high-speed system clock (PLL mode)

(N)

| Status Transition     | Setting                    |

|-----------------------|----------------------------|

| $(B) \to (E)$         | Executing HALT instruction |

| $(C) \rightarrow (F)$ |                            |

| $(D) \to (G)$         |                            |

| $(K) \to (L)$         |                            |

| $(N) \to (O)$         |                            |

(15) • Changing to STOP mode (I) from the high-speed system clock (PLL mode) as the

operating clock for the CPU (K)

Switch to high-speed system clock operation from PLL mode, stop the PLL (DSCON = 0),

and then execute the STOP instruction.

# 6.5.6.6 Condition before changing CPU clock and processing after

# changing CPU clock (pages 157 158)

# <u>Old:</u>

# Table 5-5. Changing CPU Clock (1/3)

| CPU Clock     |              | Condition Before Change           | Processing After Change |

|---------------|--------------|-----------------------------------|-------------------------|

| Before Change | After Change |                                   |                         |

| X1 clock      | (omitted)    |                                   |                         |

|               | PLL clock    | Oscillation of PLL<br>• DSCON = 1 | _                       |

#### New:

# Table 5-5. Changing CPU Clock (1/3)

| CPU Clock     |              | Condition Before Change                       | Processing After Change |

|---------------|--------------|-----------------------------------------------|-------------------------|

| Before Change | After Change |                                               |                         |

| X1 clock      |              | (omitted)                                     |                         |

|               | PLL clock    | Oscillation of PLL<br>• DSCON = 1             | -                       |

|               |              | Enabling oscillation of high-speed<br>on-chip |                         |

|               |              | oscillator<br>· HIOSTOP = 0                   |                         |

|               |              | The oscillation accuracy stabilization time   |                         |

|               |              | has elapsed                                   |                         |

<u>Old:</u>

# Table 5-5. Changing CPU Clock (2/3)

| CPU Clock                     |                                           | Condition Before Change                                                                                                                                                      | Processing After Change                                             |

|-------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Before Change                 | After Change                              |                                                                                                                                                                              |                                                                     |

| External main<br>system clock | High-speed<br>on-chip<br>oscillator clock | <ul> <li>Enabling oscillation of high-speed</li> <li>on-chip oscillator</li> <li>HIOSTOP = 0</li> <li>After elapse of oscillation<br/>accuracy stabilization time</li> </ul> | External main system clock<br>input can be disabled (MSTOP =<br>1). |

|                               | X1 clock Transition not possible          |                                                                                                                                                                              | _                                                                   |

|                               | XT1 clock                                 | Stabilization of XT1 oscillation<br>• OSCSELS = 1, EXCLKS = 0,<br>XTSTOP = 0<br>• After elapse of oscillation<br>stabilization time                                          | External main system clock<br>input can be disabled (MSTOP =<br>1). |

|                               | External<br>subsystem<br>clock            | Enabling input of external clock<br>from the EXCLKS pin<br>• OSCSELS = 1, EXCLKS = 1,<br>XTSTOP = 0                                                                          | External main system clock<br>input can be disabled (MSTOP =<br>1). |

|                               | PLL clock                                 | Oscillation of PLL<br>• DSCON = 1                                                                                                                                            | -                                                                   |

| (omitted)                     |                                           |                                                                                                                                                                              |                                                                     |

# New:

#### Table 5-5. Changing CPU Clock (2/3)

| CPU Clock                     |                                           | Condition Before Change                                                                                                                                                              | Processing After Change                                             |

|-------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Before Change                 | After Change                              |                                                                                                                                                                                      |                                                                     |

| External main<br>system clock | High-speed<br>on-chip<br>oscillator clock | Enabling oscillation of high-speed<br>on-chip oscillator<br>• HIOSTOP = 0<br>• After elapse of oscillation<br>accuracy stabilization time<br>Transition not possible                 | External main system clock<br>input can be disabled (MSTOP =<br>1). |

|                               | XT1 clock                                 | Stabilization of XT1 oscillation<br>• OSCSELS = 1, EXCLKS = 0,<br>XTSTOP = 0<br>• After elapse of oscillation<br>stabilization time                                                  | External main system clock<br>input can be disabled (MSTOP =<br>1). |

|                               | External<br>subsystem<br>clock            | Enabling input of external clock<br>from the EXCLKS pin<br>• OSCSELS = 1, EXCLKS = 1,<br>XTSTOP = 0                                                                                  | External main system clock<br>input can be disabled (MSTOP =<br>1). |

|                               | PLL clock                                 | Oscillation of PLL<br>• DSCON = 1<br>Enabling oscillation of high-speed<br>on-chip<br>oscillator<br>• HIOSTOP = 0<br>• The oscillation accuracy<br>stabilization time<br>has elapsed | _                                                                   |

| has elapsed (omitted)         |                                           |                                                                                                                                                                                      |                                                                     |

# 7. 7.3.4 Real-time clock control register 1 (RTCC1)

Additional entry to Figure 7 - 5 Format of Real-time clock control register 1 (RTCC1) (2/2)

# <u>Old:</u>

| RWAIT                                           | Wait control of real-time clock 2                                                                   | RWAIT                                                                                                         | Wait control of real-time clock 2                                                                  |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|

| 0                                               | Sets counter operation.                                                                             | 0                                                                                                             | Sets counter operation.                                                                            |  |

| 1                                               | Stops SEC to YEAR counters. Mode to read or write counter value                                     | 1                                                                                                             | Stops SEC to YEAR counters. Mode to read or write counter value                                    |  |

| This bit controls the operation of the counter. |                                                                                                     | This bit controls the operation of the counter.                                                               |                                                                                                    |  |

| Be sure to                                      | write "1" to it to read or write the counter value.                                                 | Be sure to write "1" to it to read or write the counter value.                                                |                                                                                                    |  |

| As the inte                                     | ernal counter (16-bit) is continuing to run, complete reading or writing within one second and turn | As the internal counter (16-bit) is continuing to run, complete reading or writing within one second and turn |                                                                                                    |  |

| back to                                         |                                                                                                     | back to                                                                                                       |                                                                                                    |  |

| 0.                                              |                                                                                                     | 0.                                                                                                            |                                                                                                    |  |

| When RW                                         | AIT = 1, it takes up to one cycle of fRTCuntil the counter value can be read or written (RWST =     | When RWAIT = 1, it takes up to one cycle of fRTC until the counter value can be read or written (RWST =       |                                                                                                    |  |

| 1).                                             |                                                                                                     | 1) <sup>Notes1,2</sup>                                                                                        |                                                                                                    |  |

| When the                                        | internal counter (16-bit) overflowed while RWAIT = 1, it keeps the event of overflow until RWAIT    | When the in                                                                                                   | nternal counter (16-bit) overflowed while RWAIT = 1, it keeps the event of overflow until RWAIT    |  |

| = 0, then o                                     | counts up.                                                                                          | = 0, then co                                                                                                  | punts up.                                                                                          |  |

| However,                                        | when it wrote a value to second count register, it will not keep the overflow event.                | However, w                                                                                                    | hen it wrote a value to second count register, it will not keep the overflow event.                |  |

|                                                 |                                                                                                     | Note1.                                                                                                        | When setting RWAIT=1 during 1 operating clock ( $f_{RTC}$ ), after setting RTCE=1, it may take     |  |

|                                                 |                                                                                                     |                                                                                                               | two clock time of the operation clock ( $f_{RTC}$ ), until RWST bit is set to "1".                 |  |

|                                                 |                                                                                                     | Note2.                                                                                                        | When setting RWAIT=1 during 1 operating clock ( $f_{\text{RTC}}),$ after returning from a stand-by |  |

|                                                 |                                                                                                     |                                                                                                               | (HALT mode, STOP mode and SNOOZE mode), it may take two clock time of the operation                |  |

|                                                 |                                                                                                     |                                                                                                               | clock (f <sub>RTC</sub> ), until RWST bit is set to "1".                                           |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     |                                                                                                               |                                                                                                    |  |

|                                                 |                                                                                                     | I                                                                                                             |                                                                                                    |  |

New: