# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                  |                         | Document<br>No.        | TN-RL*-A031B/E                                         | Rev. | 3.00 |

|-----------------------|----------------------------------------------------------------------------------------------------------|-------------------------|------------------------|--------------------------------------------------------|------|------|

| Title                 | Correction for Incorrect Description Notice RI<br>Descriptions in the User's Manual: Hardware<br>Changed | Information<br>Category | Technical Notification |                                                        |      |      |

|                       |                                                                                                          | Lot No.                 |                        |                                                        |      |      |

| Applicable<br>Product | RL78/L13 Group                                                                                           | All lots                | Reference<br>Document  | RL78/L13 User's Man<br>Rev. 2.00<br>R01UH0382EJ0200 ([ |      |      |

This document describes misstatements found in the RL78/L13 User's Manual: Hardware Rev. 2.00 (R01UH0382EJ0200).

## **Corrections**

| Applicable Item                                                                                                | Applicable<br>Page | Contents                          |

|----------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------|

| 5.6.4 CPU clock status transition diagram<br>Table 5-3. CPU Clock Transition and SFR Setting Examples<br>(3/5) | Page 179           | Incorrect descriptions revised    |

| 8.3.5 Real-time clock control register 1 (RTCC1)                                                               | Page 401           | Additional entry                  |

| 8.4.1 Starting operation of real-time clock 2                                                                  | Page 414           | Incorrect descriptions<br>revised |

## Document Improvement

The above corrections will be made for the next revision of the User's Manual: Hardware.

|     |                     |                                                                           | Corrections and Applicable Items                   |                        | Pages in this               |  |  |  |

|-----|---------------------|---------------------------------------------------------------------------|----------------------------------------------------|------------------------|-----------------------------|--|--|--|

| No. |                     | Document No.                                                              | English                                            | R01UH0382EJ0200        | document for<br>corrections |  |  |  |

| 1   | 5.3.9 Hi            | gh-speed on-chip osc                                                      | illator trimming register (HIOTRM)                 | Page 164               | Page 3                      |  |  |  |

| 2   | Timing (            | SNOOZE mode function<br>Chart of SNOOZE Mo<br>14-71. and Figure 14        | Pages 592 and 594                                  | Page 4 and 5           |                             |  |  |  |

| 3   | 14.6.3 S            | NOOZE mode function                                                       | n                                                  | Page 618               | Page 6                      |  |  |  |

| 4   | Timing (            | NOOZE mode functi<br>Chart of SNOOZE Mo<br>14-90., Figure 14-91.          | de Operation                                       | Pages 620, 621 and 623 | Page 7 to 9                 |  |  |  |

| 5   | Table 1<br>Multiple | Iultiple interrupt servi<br>9-5. Relationship Be<br>Interrupt Servicing D | Page 864                                           | Page 10                |                             |  |  |  |

| 6   | Figure              | nfiguration of Power-<br>23-2. Timing of Ge<br>on-reset Circuit and V     | neration of Internal Reset Signal by               | Page 900               | Page 11                     |  |  |  |

| 7   |                     | solute Maximum Rati                                                       |                                                    | Page 1001 Page 12      |                             |  |  |  |

| 8   | 32.8 Da<br>Charact  |                                                                           | de Low Supply Voltage Data Retention               | Page 1056              | Page 13                     |  |  |  |

| 9   |                     | solute Maximum Rati                                                       |                                                    | Page 1065              | Page 14                     |  |  |  |

| 10  | Charact             | eristics                                                                  | de Low Supply Voltage Data Retention               | Page 1114              | Page 15                     |  |  |  |

| 11  |                     | mer mode register mr<br>3-12. Format of Timer                             | i (TMRmn)<br>Mode Register mn (TMRmn) (4/4)        | Page 212               | Page 16                     |  |  |  |

| 12  | 32.3.1              | Pin characteristics                                                       |                                                    | Page 1004 and 1005     | Pages 17 and 18             |  |  |  |

| 13  | 33.3.1              | Pin characteristics                                                       |                                                    | Page 1068 and 1069     | Pages 19 and 20             |  |  |  |

| 14  |                     | eal-time clock control                                                    |                                                    | Page 401               | Page 21                     |  |  |  |

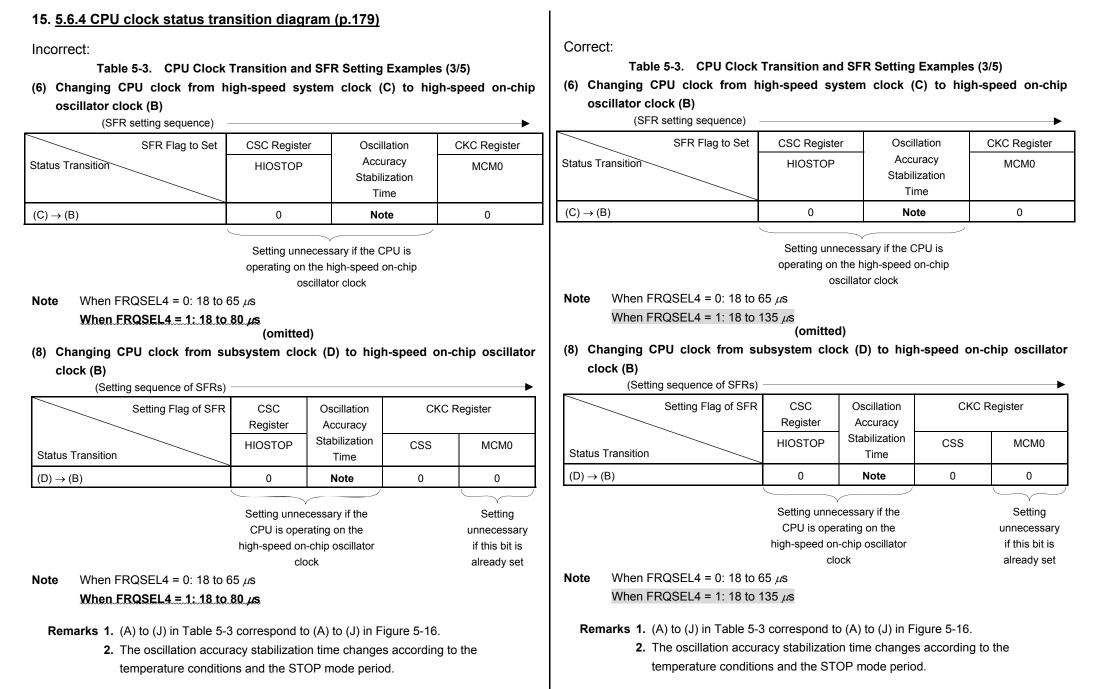

| 15  |                     | PU clock status transi<br>-3. CPU Clock Transi                            | tion diagram<br>ion and SFR Setting Examples (3/5) | Page 179               | Page 22                     |  |  |  |

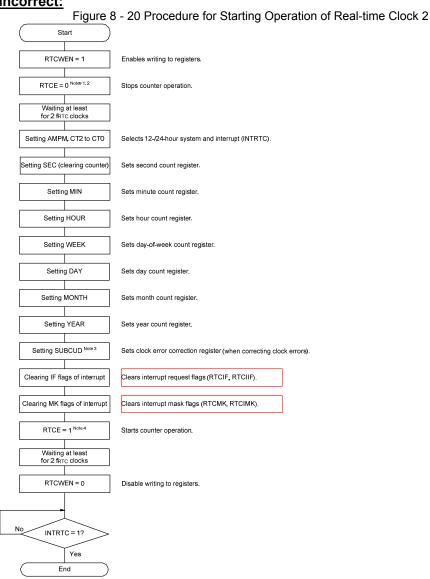

| 16  | 8.4.1 St            | arting operation of rea                                                   | al-time clock 2                                    | Page 414               | Page 23                     |  |  |  |

Incorrect: Bold with underline: Correct: Gray hatched

## **Revision History**

RL78/L13 Correction for incorrect description notice

| Document Number | Issue Date    | Description                                       |

|-----------------|---------------|---------------------------------------------------|

| TN-RL*-A029A/E  | Jun. 27, 2014 | First edition issued                              |

|                 |               | Corrections No.1 to No.10 revised                 |

| TN-RL*-A031A/E  | Aug 18, 2014  | Second edition issued                             |

|                 |               | Correction No.11 to 13revised                     |

| TN-RL*-A046A/E  | Jul. 6 , 2015 | Correction No.14 revised                          |

|                 |               |                                                   |

| TN-RL*-A031B/E  | Oct .27, 2015 | Third edition issued                              |

|                 |               | Correction No.15 and No.16 revised(this document) |

## 1. <u>5.3.9 High-speed on-chip oscillator trimming register (HIOTRM)</u> (Page 243)

#### Incorrect:

5.3.9 High-speed on-chip oscillator trimming register (HIOTRM) (omitted)

Figure 5-10. Format of High-Speed On-Chip Oscillator Trimming Register (HIOTRM)

| Address | F00A0H |   | F00A0H After reset: |         | Note R/W |         |         |         |

|---------|--------|---|---------------------|---------|----------|---------|---------|---------|

| Symbol  | 7      | 6 | 5                   | 4       | 3        | 2       | 1       | 0       |

| HIOTRM  | 0      | 0 | HIOTRM5             | HIOTRM4 | HIOTRM3  | HIOTRM2 | HIOTRM1 | HIOTRM0 |

| HIOTRM5 | HIOTRM4 | HIOTRM3 | HIOTRM2 | HIOTRM1 | HIOTRM0 | High-speed on-chip oscillator |

|---------|---------|---------|---------|---------|---------|-------------------------------|

| 0       | 0       | 0       | 0       | 0       | 0       | Minimum speed                 |

| 0       | 0       | 0       | 0       | 0       | 1       | 4                             |

| 0       | 0       | 0       | 0       | 1       | 0       |                               |

| 0       | 0       | 0       | 0       | 1       | 1       |                               |

| 0       | 0       | 0       | 1       | 0       | 0       |                               |

|         |         |         | •       |         |         |                               |

| 1       | 1       | 1       | 1       | 1       | 0       | •                             |

| 1       | 1       | 1       | 1       | 1       | 1       | Maximum speed                 |

**Note** The value after reset is the value adjusted at shipment.

Remarks 1. The HIOTRM register can be used to adjust the high-speed on-chip oscillator clock to an accuracy within about 0.05%.

**2.** For the usage example of the HIOTRM register, see the application note for RL78 MCU series High-speed On-chip Oscillator (HOCO) Clock Frequency Correction (R01AN0464).

#### Correct:

5.3.9 High-speed on-chip oscillator trimming register (HIOTRM) (omitted)

#### Figure 5-10. Format of High-Speed On-Chip Oscillator Trimming Register (HIOTRM)

| Address | E FOOAOH |   | After rese | After reset: undefined Note |         |         |         |         |

|---------|----------|---|------------|-----------------------------|---------|---------|---------|---------|

| Symbol  | 7        | 6 | 5          | 4                           | 3       | 2       | 1       | 0       |

| HIOTRM  | 0        | 0 | HIOTRM5    | HIOTRM4                     | HIOTRM3 | HIOTRM2 | HIOTRM1 | HIOTRM0 |

| HIOTRM5 | HIOTRM4 | HIOTRM3 | HIOTRM2 | HIOTRM1 | HIOTRM0 | High-speed on-chip oscillator |  |  |

|---------|---------|---------|---------|---------|---------|-------------------------------|--|--|

| 0       | 0       | 0       | 0       | 0       | 0       | Minimum speed                 |  |  |

| 0       | 0       | 0       | 0       | 0       | 1       | 4                             |  |  |

| 0       | 0       | 0       | 0       | 1       | 0       |                               |  |  |

| 0       | 0       | 0       | 0       | 1       | 1       |                               |  |  |

| 0       | 0       | 0       | 1       | 0       | 0       |                               |  |  |

|         |         | •       | •       |         |         |                               |  |  |

| 1       | 1       | 1       | 1       | 1       | 0       | •                             |  |  |

| 1       | 1       | 1       | 1       | 1       | 1       | Maximum speed                 |  |  |

**Note** The value after reset is the value adjusted at shipment.

**Remarks 1**. The HIOTRM register holds a six-bit value used to adjust the high-speed on-chip oscillator with an increment of 1 corresponding to an increase of frequency by about 0.05%.

**2.** For the usage example of the HIOTRM register, see the application note for RL78 MCU series High-speed On-chip Oscillator (HOCO) Clock Frequency Correction (R01AN0464).

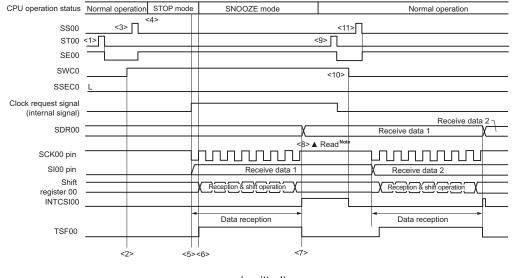

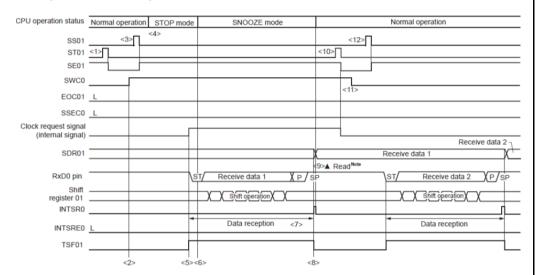

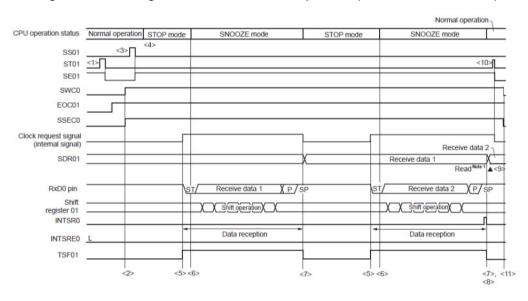

## 2. 14.5.7 SNOOZE mode function

Timing Chart of SNOOZE Mode Operation (Figure 14-71. and Figure 14-73.) (Pages 592 and 594)

It is correction of "CPU operation status", "Clock request signal (internal signal)" and "TSF00" in this Figure.

#### Incorrect:

#### Figure 14-71. Timing Chart of SNOOZE Mode Operation (once startup) (Type 1: DAPmn = 0, CKPmn = 0)

(omitted)

## Correct:

## Figure 14-71. Timing Chart of SNOOZE Mode Operation (once startup) (Type 1: DAPmn = 0, CKPmn = 0)

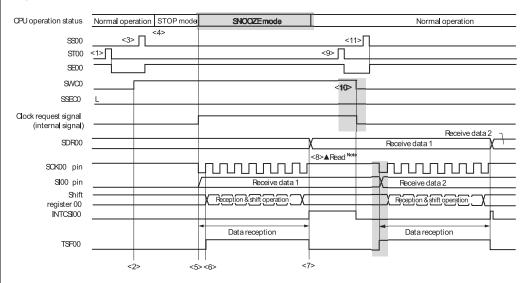

It is correction of "CPU operation status", "Clock request signal (internal signal)" and "INTCSI00" in this Figure.

#### Incorrect:

Figure 14-73. Timing Chart of SNOOZE Mode Operation (continuous startup) (Type 1: DAPmn = 0, CKPmn = 0)

(omitted)

#### Correct:

Figure 14-73. Timing Chart of SNOOZE Mode Operation (continuous startup) (Type 1: DAPmn = 0, CKPmn = 0)

## 3. <u>14.6.3 SNOOZE mode function (Page 618)</u>

#### Incorrect:

#### 14.6.3 SNOOZE mode function

The SNOOZE mode makes the UART perform reception operations upon RxDq pin input detection while in the STOP mode. Normally the UART stops communication in the STOP mode. However, using the SNOOZE mode enables the UART to perform reception operations without CPU operation.

#### (omitted)

Cautions 1. The SNOOZE mode can only be used when the high-speed on-chip oscillator clock (fin) is selected for fclk.

#### (omitted)

4. If a parity error, framing error, or overrun error occurs while the SSECm bit is set to 1, the PEFmn, FEFmn, or OVFmn flag is not set and an error interrupt (INTSREq) is not generated. Therefore, when the setting of SSECm = 1 is made, clear the PEFmn, FEFmn, or OVFmn flag before setting the SWC0 bit to 1 and read the value in bits 7 to 0 (RxDq register) of the SDRm1 register.

#### Correct:

#### 14.6.3 SNOOZE mode function

The SNOOZE mode makes the UART perform reception operations upon RxDq pin input detection while in the STOP mode. Normally the UART stops communication in the STOP mode. However, using the SNOOZE mode enables the UART to perform reception operations without CPU operation.

#### (omitted)

Cautions 1. The SNOOZE mode can only be used when the high-speed on-chip oscillator clock (fill) is selected for fcLk.

- 4. If a parity error, framing error, or overrun error occurs while the SSECm bit is set to 1, the PEFmn, FEFmn, or OVFmn flag is not set and an error interrupt (INTSREq) is not generated. Therefore, when the setting of SSECm = 1 is made, clear the PEFmn, FEFmn, or OVFmn flag before setting the SWC0 bit to 1 and read the value in bits 7 to 0 (RxDq register) of the SDRm1 register.

- 5. The CPU shifts from the STOP mode to the SNOOZE mode on detecting the valid edge of the RxDq signal. Note, however, that transfer through the UART channel may not start and the CPU may remain in the SNOOZE mode if an input pulse on the RxDq pin is too short to be detected as a start bit. In such cases, data may not be received correctly, and this may lead to a framing error or parity error in the next UART transfer.

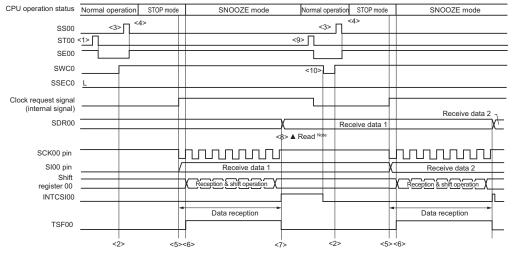

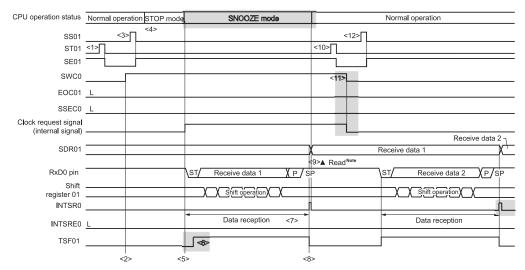

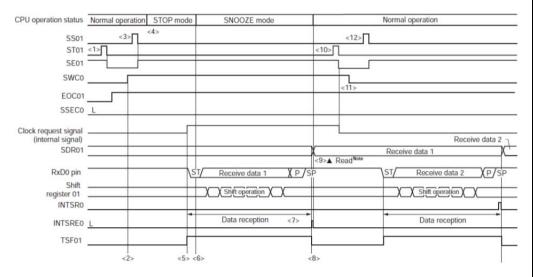

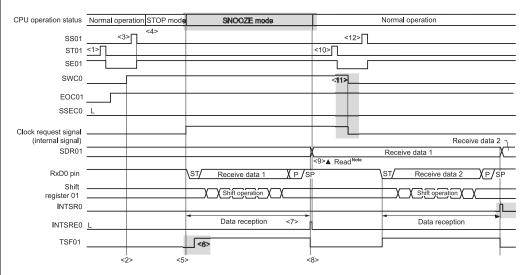

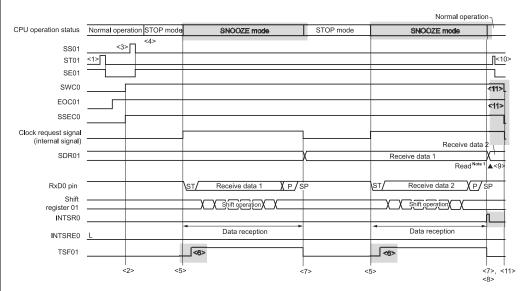

#### 4. <u>14.6.3 SNOOZE mode function</u> <u>Timing Chart of SNOOZE Mode Operation (Figure 14-90., Figure 14-91.</u> and Figure 14-93.) (Pages 620, 621 and 623)

It is correction of "CPU operation status", "Clock request signal (internal signal)", "INTSR0" and "TSF01" in this Figure.

#### Incorrect:

Figure 14-90. Timing Chart of SNOOZE Mode Operation (EOCm1 = 0, SSECm = 0/1)

(omitted)

#### Correct:

#### Figure 14-90. Timing Chart of SNOOZE Mode Operation (EOCm1 = 0, SSECm = 0/1)

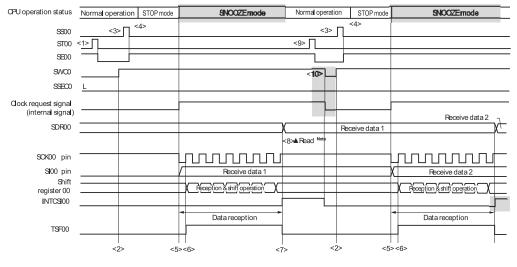

It is correction of "CPU operation status", "Clock request signal (internal signal)", "INTSR0" and "TSF01" in this Figure.

#### Incorrect:

(omitted)

#### Correct:

#### Figure 14-91. Timing Chart of SNOOZE Mode Operation (EOCm1 = 1, SSECm = 0)

It is correction of "CPU operation status", "Clock request signal (internal signal)", "INTSR0" and "TSF01" in this Figure.

#### Incorrect:

Figure 14-93. Timing Chart of SNOOZE Mode Operation (EOCm1 = 1, SSECm = 1)

(omitted)

#### Correct:

Figure 14-93. Timing Chart of SNOOZE Mode Operation (EOCm1 = 1, SSECm = 1)

## 5. <u>19.4.3 Multiple interrupt servicing</u> <u>Table 19-5. Relationship Between Interrupt Requests Enabled for</u> <u>Multiple Interrupt Servicing During Interrupt Servicing (Page 864)</u>

Incorrect:

## Table 19-5. Relationship Between Interrupt Requests Enabled for Multiple Interrupt Servicing During Interrupt Servicing

| Multip                | Multiple Interrupt   |        | Maskable Interrupt Request |                 |                  |                     |        |        |                  |                      |

|-----------------------|----------------------|--------|----------------------------|-----------------|------------------|---------------------|--------|--------|------------------|----------------------|

| Request               |                      |        | Level 0<br>= 00)           | Priority<br>(PR | Level 1<br>= 01) | Priority L<br>(PR = |        | -      | Level 3<br>= 11) | Interrupt<br>Request |

| Being Servic          | ced                  | IE = 1 | IE = 0                     | IE = 1          | IE = 0           | IE = 1              | IE = 0 | IE = 1 | IE = 0           |                      |

| Maskable<br>interrupt | ISP1 = 0<br>ISP0 = 0 | 0      | ×                          | ×               | ×                | ×                   | ×      | ×      | ×                | 0                    |

|                       | ISP1 = 0<br>ISP0 = 1 | 0      | ×                          | 0               | ×                | ×                   | ×      | ×      | ×                | 0                    |

|                       | ISP1 = 1<br>ISP0 = 0 | 0      | ×                          | 0               | ×                | 0                   | ×      | ×      | ×                | 0                    |

|                       | ISP1 = 1<br>ISP0 = 1 | 0      | Q                          | 0               | Q                | 0                   | Q      | 0      | Q                | 0                    |

| Software interrupt    |                      | 0      | ×                          | 0               | ×                | 0                   | ×      | 0      | ×                | 0                    |

(omitted)

Correct:

## Table 19-5.Relationship Between Interrupt Requests Enabled for Multiple InterruptServicing During Interrupt Servicing

| Multipl               | Multiple Interrupt   |                               | Maskable Interrupt Request |        |                               |        |                               |        |                               |   |

|-----------------------|----------------------|-------------------------------|----------------------------|--------|-------------------------------|--------|-------------------------------|--------|-------------------------------|---|

| Request               |                      | Priority Level 0<br>(PR = 00) |                            | ,      | Priority Level 1<br>(PR = 01) |        | Priority Level 2<br>(PR = 10) |        | Priority Level 3<br>(PR = 11) |   |

| Being Servic          | ced                  | IE = 1                        | IE = 0                     | IE = 1 | IE = 0                        | IE = 1 | IE = 0                        | IE = 1 | IE = 0                        |   |

| Maskable<br>interrupt | ISP1 = 0<br>ISP0 = 0 | 0                             | ×                          | ×      | ×                             | ×      | ×                             | ×      | ×                             | 0 |

|                       | ISP1 = 0<br>ISP0 = 1 | 0                             | ×                          | 0      | ×                             | ×      | ×                             | ×      | ×                             | 0 |

|                       | ISP1 = 1<br>ISP0 = 0 | 0                             | ×                          | 0      | ×                             | 0      | ×                             | ×      | ×                             | 0 |

|                       | ISP1 = 1<br>ISP0 = 1 | 0                             | ×                          | 0      | ×                             | 0      | ×                             | 0      | ×                             | 0 |

| Software interrupt    |                      | 0                             | ×                          | 0      | ×                             | 0      | ×                             | 0      | ×                             | 0 |

6. <u>23.2 Configuration of Power-on-reset Circuit</u> <u>Figure 23-2. Timing of Generation of Internal Reset Signal by</u> <u>Power-on-reset Circuit and Voltage Detector (1) (Page 900)</u>

Incorrect:

Figure 23-2. Timing of Generation of Internal Reset Signal by Power-on-reset Circuit and Voltage Detector (1/3)

(1) When the externally input reset signal on the  $\overline{\text{RESET}}$  pin is used

#### (omitted)

Notes 3. The time until normal operation starts includes the following reset processing time when the external reset is released (after the first release of POR) after the RESET signal is driven high (1) as well as the voltage stabilization wait time after VPOR (1.51 V, typ.) is reached. Reset processing time when the external reset is released is shown below. After the first release of POR:

0.672 ms (typ.), 0.832 ms (max.) (when the LVD is in use)

0.399 ms (typ.), 0.519 ms (max.) (when the LVD is off)

4. Reset processing time when the external reset is released after the second release of POR is shown below.

#### After the second release of POR:

0.531 ms (typ.), 0.675 ms (max.) (when the LVD is in use) 0.259 ms (typ.), 0.362 ms (max.) (when the LVD is off) (omitted) Correct:

Figure 23-2. Timing of Generation of Internal Reset Signal by Power-on-reset Circuit and Voltage Detector (1/3)

(1) When the externally input reset signal on the RESET pin is used

#### (omitted)

Notes 3. The time until normal operation starts includes the following reset processing time when the external reset is released (release from the first external reset following release from the POR state) after the RESET signal is driven high (1) as well as the voltage stabilization wait time after VPOR (1.51 V, typ.) is reached. Reset processing time when the external reset is released is shown below. Release from the first external reset following release from the POR state: 0.672 ms (typ.), 0.832 ms (max.) (when the LVD is in use) 0.399 ms (typ.), 0.519 ms (max.) (when the LVD is off)

Reset times in cases of release from an external reset other than the above are listed below.

Release from the reset state for external resets other than the above case: 0.531 ms (typ.), 0.675 ms (max.) (when the LVD is in use) 0.259 ms (typ.), 0.362 ms (max.) (when the LVD is off) (omitted)

## 7. <u>32.1 Absolute Maximum Ratings</u> (Page 1001)

## Incorrect:

Absolute Maximum Ratings (3/3)

| Parameter               | Symbol |                              | Conditions                                                                                                              | Ratings     | Unit |  |  |  |

|-------------------------|--------|------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------|------|--|--|--|

| Output current,<br>high | Іон1   | Per pin                      | P00 to P07, <b>P14 to P17.</b><br>P30 to P35, P40 to P47,<br>P50 to P57, P60, P61,<br>P70 to P77, P125 to P127,<br>P130 | -40         | mA   |  |  |  |

|                         |        | Total of all pins<br>–170 mA | P00 to P07, <b>P14 to P17,</b><br>P30 to P35, P40 to P47,<br>P50 to P57, P60, P61,<br>P70 to P77, P125 to P127,<br>P130 | -170        | mA   |  |  |  |

|                         | Іон2   | Per pin                      | P10 to P13. P20 to P27                                                                                                  | -0.5        | mA   |  |  |  |

|                         |        | Total of all pins            |                                                                                                                         |             |      |  |  |  |

| Output current,<br>Iow  | Iol1   | Per pin                      | P00 to P07, <b>P14 to P17,</b><br>P30 to P35, P40 to P47,<br>P50 to P57, P60, P61,<br>P70 to P77, P125 to P127,<br>P130 | 40          | mA   |  |  |  |

|                         |        | Total of all pins            | P40 to P47, P130                                                                                                        | 70          | mA   |  |  |  |

|                         |        | 170 mA                       | P00 to P07, <b>P14 to P17,</b><br>P30 to P35, P50 to P57,<br>P60, P61, P70 to P77,<br>P125 to P127                      | 100         | mA   |  |  |  |

|                         | IOL2   | Per pin                      | P10 to P13. P20 to P27                                                                                                  | 1           | mA   |  |  |  |

|                         |        | Total of all pins            |                                                                                                                         | 5           | mA   |  |  |  |

| Operating ambient       | TA     | In normal operation          | on mode                                                                                                                 | -40 to +85  | °C   |  |  |  |

| temperature             |        | In flash memory p            |                                                                                                                         |             |      |  |  |  |

| Storage temperature     | Tstg   |                              |                                                                                                                         | -65 to +150 | °C   |  |  |  |

| Correct:                       |  |

|--------------------------------|--|

| Absolute Maximum Ratings (3/3) |  |

| Parameter               | Symbol |                              | Conditions                                                                                                                   | Ratings     | Unit |

|-------------------------|--------|------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------|------|

| Output current,<br>high | Іон1   | Per pin                      | P00 to P07, P10 to P17, P22 to<br>P27, P30 to P35, P40 to P47,<br>P50 to P57, P60, P61,<br>P70 to P77, P125 to P127,<br>P130 | -40         | mA   |

|                         |        | Total of all pins<br>−170 mA | P00 to P07, P10 to P17, P22 to<br>P27, P30 to P35, P40 to P47,<br>P50 to P57, P60, P61,<br>P70 to P77, P125 to P127,<br>P130 | -170        | mA   |

|                         | Іон2   | Per pin                      | P20, P21                                                                                                                     | -0.5        | mA   |

|                         |        | Total of all pins            |                                                                                                                              | -1          | mA   |

| Output current,<br>Iow  | Iol1   | Per pin                      | P00 to P07, P10 to P17, P22 to<br>P27, P30 to P35, P40 to P47,<br>P50 to P57, P60, P61,<br>P70 to P77, P125 to P127,<br>P130 | 40          | mA   |

|                         |        | Total of all pins            | P40 to P47, P130                                                                                                             | 70          | mA   |

|                         |        | 170 mA                       | P00 to P07, P10 to P17, P22 to<br>P27,P30 to P35, P50 to P57,<br>P60, P61, P70 to P77,<br>P125 to P127                       | 100         | mA   |

|                         | IOL2   | Per pin                      | P20, P21                                                                                                                     | 1           | mA   |

|                         |        | Total of all pins            | ]                                                                                                                            | 2           | mA   |

| Operating ambient       | TA     | In normal operation          | -40 to +85                                                                                                                   | °C          |      |

| temperature             |        | In flash memory p            |                                                                                                                              |             |      |

| Storage temperature     | Tstg   |                              |                                                                                                                              | -65 to +150 | °C   |

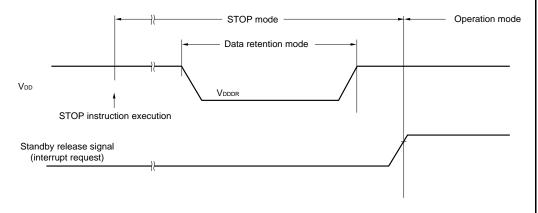

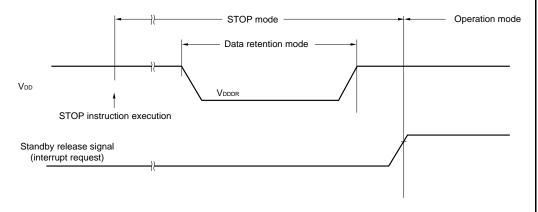

## 8. <u>32.8 Data Memory STOP Mode Low Supply Voltage Data Retention</u> <u>Characteristics (Page 1056)</u>

Old:

## 32.8 Data Memory STOP Mode Low Supply Voltage Data Retention Characteristics

#### (T<sub>A</sub> = -40 to +85°C, Vss = 0 V)

| Parameter             | Symbol | Conditions | MIN.                 | TYP. | MAX. | Unit |

|-----------------------|--------|------------|----------------------|------|------|------|

| Data retention supply | VDDDR  |            | 1.46 <sup>Note</sup> |      | 5.5  | V    |

| voltage               |        |            |                      |      |      |      |

Note The value depends on the POR detection voltage. When the voltage drops, the data is retained before a POR reset is effected, but data is not retained when a POR reset is effected.

#### New:

## 32.8 RAM Data Retention Characteristics

#### (T<sub>A</sub> = -40 to +85°C, V<sub>SS</sub> = 0 V)

| Parameter                     | Symbol | Conditions | MIN.                 | TYP. | MAX. | Unit |

|-------------------------------|--------|------------|----------------------|------|------|------|

| Data retention supply voltage | Vdddr  |            | 1.46 <sup>Note</sup> |      | 5.5  | V    |

**Note** This depends on the POR detection voltage. For a falling voltage, data in RAM are retained until the voltage reaches the level that triggers a POR reset but not once it reaches the level at which a POR reset is generated.

## 9. <u>33.1 Absolute Maximum Ratings</u> (Page 1065)

## Incorrect:

Absolute Maximum Ratings (3/3)

| Parameter               | Symbol |                              | Conditions                                                                                                               | Ratings     | Unit |

|-------------------------|--------|------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------|------|

| Output current,<br>high | Іон1   | Per pin                      | P00 to P07, <b>P14 to P17</b> ,<br>P30 to P35, P40 to P47,<br>P50 to P57, P60, P61,<br>P70 to P77, P125 to P127,<br>P130 | -40         | mA   |

|                         |        | Total of all pins<br>−170 mA | P00 to P07, <b>P14 to P17</b> ,<br>P30 to P35, P40 to P47,<br>P50 to P57, P60, P61,<br>P70 to P77, P125 to P127,<br>P130 | -170        | mA   |

|                         | Іон2   | Per pin                      | P10 to P13. P20 to P27                                                                                                   | -0.5        | mA   |

|                         |        | Total of all pins            |                                                                                                                          | <b>=2</b>   | mA   |

| Output current,<br>low  | lol1   | Per pin                      | P00 to P07, <b>P14.to P17</b> ,<br>P30 to P35, P40 to P47,<br>P50 to P57, P60, P61,<br>P70 to P77, P125 to P127,<br>P130 | 40          | mA   |

|                         |        | Total of all pins            | P40 to P47, P130                                                                                                         | 70          | mA   |

|                         |        | 170 mA                       | P00 to P07, <b>P14 to P17</b> ,<br>P30 to P35, P50 to P57,<br>P60, P61, P70 to P77,<br>P125 to P127                      | 100         | mA   |

|                         | Iol2   | Per pin                      | P10 to P13. P20 to P27                                                                                                   | 1           | mA   |

|                         |        | Total of all pins            |                                                                                                                          | 5           | mA   |

| Operating ambient       | Та     | In normal operation mode     |                                                                                                                          | -40 to +105 | °C   |

| temperature             |        | In flash memory p            | rogramming mode                                                                                                          |             |      |

| Storage temperature     | Tstg   |                              |                                                                                                                          | -65 to +150 | °C   |

| Correct:                 |       |

|--------------------------|-------|

| Absolute Maximum Ratings | (3/3) |

| Parameter               | Symbol |                              | Conditions                                                                                                                   | Ratings     | Unit |

|-------------------------|--------|------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------|------|

| Output current,<br>high | Іон1   | Per pin                      | P00 to P07, P10 to P17, P22 to<br>P27, P30 to P35, P40 to P47,<br>P50 to P57, P60, P61,<br>P70 to P77, P125 to P127,<br>P130 | -40         | mA   |

|                         |        | Total of all pins<br>–170 mA | P00 to P07, P10 to P17, P22 to<br>P27, P30 to P35, P40 to P47,<br>P50 to P57, P60, P61,<br>P70 to P77, P125 to P127,<br>P130 | -170        | mA   |

|                         | Іон2   | Per pin                      | P20, P21                                                                                                                     | -0.5        | mA   |

|                         |        | Total of all pins            |                                                                                                                              | -1          | mA   |

| Output current,<br>low  | Iol1   | Per pin                      | P00 to P07, P10 to P17, P22 to<br>P27, P30 to P35, P40 to P47,<br>P50 to P57, P60, P61,<br>P70 to P77, P125 to P127,<br>P130 | 40          | mA   |

|                         |        | Total of all pins            | P40 to P47, P130                                                                                                             | 70          | mA   |

|                         |        | 170 mA                       | P00 to P07, P10 to P17, P22 to<br>P27, P30 to P35, P50 to P57,<br>P60, P61, P70 to P77,<br>P125 to P127                      | 100         | mA   |

|                         | IOL2   | Per pin                      | P20, P21                                                                                                                     | 1           | mA   |

|                         |        | Total of all pins            |                                                                                                                              | 2           | mA   |

| Operating ambient       | Та     | In normal operation          | -40 to +105                                                                                                                  | °C          |      |

| temperature             |        | In flash memory p            |                                                                                                                              |             |      |

| Storage temperature     | Tstg   |                              |                                                                                                                              | -65 to +150 | °C   |

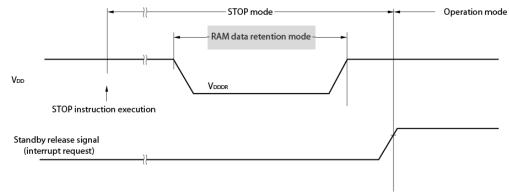

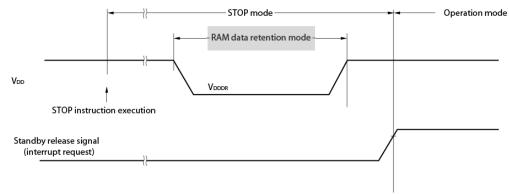

## 10. <u>33.8 Data Memory STOP Mode Low Supply Voltage Data Retention</u> <u>Characteristics (Page 1114)</u>

Old:

33.8 Data Memory STOP Mode Low Supply Voltage Data Retention Characteristics

#### (T<sub>A</sub> = -40 to +105°C)

| Parameter             | Symbol | Conditions | MIN.                 | TYP. | MAX. | Unit |

|-----------------------|--------|------------|----------------------|------|------|------|

| Data retention supply | VDDDR  |            | 1.44 <sup>Note</sup> |      | 5.5  | V    |

| voltage               |        |            |                      |      |      |      |

Note The value depends on the POR detection voltage. When the voltage drops, the data is retained before a POR reset is effected, but data is not retained when a POR reset is effected.

#### New:

## 33.8 RAM Data Retention Characteristics

### (T<sub>A</sub> = -40 to +105°C)

| Parameter                     | Symbol | Conditions | MIN.                 | TYP. | MAX. | Unit |

|-------------------------------|--------|------------|----------------------|------|------|------|

| Data retention supply voltage | Vdddr  |            | 1.44 <sup>Note</sup> |      | 5.5  | V    |

**Note** This depends on the POR detection voltage. For a falling voltage, data in RAM are retained until the voltage reaches the level that triggers a POR reset but not once it reaches the level at which a POR reset is generated.

## 11. 6.3.3 Timer mode register mn (TMRmn)

Figure 6-12. Former of Timer mode Register mn (TMRmn)(4/4)

Incorrect:

#### Figure 6-12. Format of Timer Mode Register mn (TMRmn) (4/4)

Address: F0190H, F0191H (TMR00) to F019EH, F019FH (TMR07) After reset: 0000H

H R/W

| Operation mode<br>(Value set by the MDmn3 to MDmn1 bits<br>(see the previous page) | MD<br>mn<br>0 | Setting of starting counting and interrupt                                                                                                                                                               |

|------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>Interval timer mode</li><li>(0, 0, 0)</li></ul>                            | 0             | Timer interrupt is not generated when counting is started (timer output does not change, either).                                                                                                        |

| • Capture mode<br>(0, 1, 0)                                                        | 1             | Timer interrupt is generated when counting is started (timer output also changes).                                                                                                                       |

| • Event counter mode<br>(0, 1, 1)                                                  | 0             | Timer interrupt is not generated when counting is started (timer output does not change, either).                                                                                                        |

| • One-count mode <sup>Note 2</sup><br>(1, 0, 0)                                    | 0             | Start trigger is invalid during counting operation.<br>At that time, interrupt is not generated.                                                                                                         |

|                                                                                    | 1             | Start trigger is valid during counting operation <sup>Note 3</sup> .<br>At that time, interrupt is <b>generated.</b>                                                                                     |

| • Capture & one-count mode<br>(1, 1, 0)                                            | 0             | Timer interrupt is not generated when counting is started<br>(timer output does not change, either).<br>Start trigger is invalid during counting operation.<br>At that time, interrupt is not generated. |

| Other than above                                                                   |               | Setting prohibited                                                                                                                                                                                       |

#### Correct:

#### Figure 6-12. Format of Timer Mode Register mn (TMRmn) (4/4)

Address: F0190H, F0191H (TMR00) to F019EH, F019FH (TMR07) After reset: 0000H R/W

| Operation mode<br>(Value set by the MDmn3 to MDmn1 bits<br>(see the previous page) | MD<br>mn<br>0 | Setting of starting counting and interrupt                                                                                                                                                               |

|------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>Interval timer mode</li><li>(0, 0, 0)</li></ul>                            | 0             | Timer interrupt is not generated when counting is started (timer output does not change, either).                                                                                                        |

| • Capture mode (0, 1, 0)                                                           | 1             | Timer interrupt is generated when counting is started (timer output also changes).                                                                                                                       |

| • Event counter mode<br>(0, 1, 1)                                                  | 0             | Timer interrupt is not generated when counting is started (timer output does not change, either).                                                                                                        |

| • One-count mode <sup>Note 2</sup><br>(1, 0, 0)                                    | 0             | Start trigger is invalid during counting operation.<br>At that time, interrupt is not generated.                                                                                                         |

|                                                                                    | 1             | Start trigger is valid during counting operation <sup>Note 3</sup> .<br>At that time, interrupt is not generated.                                                                                        |

| Capture & one-count mode     (1, 1, 0)                                             | 0             | Timer interrupt is not generated when counting is started<br>(timer output does not change, either).<br>Start trigger is invalid during counting operation.<br>At that time, interrupt is not generated. |

| Other than above                                                                   |               | Setting prohibited                                                                                                                                                                                       |

## 12. 32.3.1 Pin characteristics(p.1004 , p1005)

## Incorrect:

## $(T_A = -40 \text{ to } +85^{\circ}C, 1.6 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

| Parameter                                    | Symbol                                                | Conditions                                                                                                                        |                                                                           | MIN. | TYP. | MAX.                       | Unit |

|----------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|------|----------------------------|------|

| Output<br>current,<br>high <sup>Note 1</sup> | current, F<br>high <sup>Note 1</sup> F<br>F<br>t<br>t | Per pin for P00 to P07, P10 to<br>P17,<br>P22 to P27, P30 to P35, P40 to<br>P47,<br>P50 to P57, P70 to P77, P125<br>to P127, P130 | $\begin{array}{l} 1.6 \ V \leq V_{\text{DD}} \leq \\ 5.5 \ V \end{array}$ |      |      | –10.0 <sup>Note</sup><br>2 | mA   |

|                                              |                                                       | Total of P00 to P07, <b>P14 to</b> .<br><b>P17.</b><br>P30 to P35, P40 to P47, P50 to<br>P57,<br>P70 to P77, P70 to P47, P50 to   | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq \\ 5.5 \ V \end{array}$ |      |      | -90.0                      | mA   |

|                                              |                                                       |                                                                                                                                   | $2.7 V \le V_{DD} < 4.0 V$                                                |      |      | -15.0                      | mA   |

|                                              |                                                       | P70 to P77, P125 to P127,<br>P130<br>(When duty = 70% <sup>Note 3</sup> )                                                         | $1.8 V \le V_{DD} < 2.7 V$                                                |      |      | -7.0                       | mA   |

|                                              |                                                       | (,                                                                                                                                | 1.6 V ≤ V <sub>DD</sub> <<br>1.8 V                                        |      |      | -3.0                       | mA   |

|                                              | Іон2                                                  | Per pin for P20 and P21                                                                                                           | $\begin{array}{l} 1.6 \ V \leq V_{\text{DD}} \leq \\ 5.5 \ V \end{array}$ |      |      | –0.1 <sup>Note 2</sup>     | mA   |

|                                              |                                                       | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                                         | $\begin{array}{l} 1.6 \ V \leq V_{\text{DD}} \leq \\ 5.5 \ V \end{array}$ |      |      | -0.2                       | mA   |

Date: Oct .27, 2015

## Correct:

## $(T_A = -40 \text{ to } +85^{\circ}C, 1.6 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

| Parameter                                    | Symbol                                 | Conditions                                                                                                                        |                                                                                              | MIN. | TYP.  | MAX.                       | Unit |

|----------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|-------|----------------------------|------|

| Output<br>current,<br>high <sup>Note 1</sup> | Іон1                                   | Per pin for P00 to P07, P10 to<br>P17,<br>P22 to P27, P30 to P35, P40 to<br>P47,<br>P50 to P57, P70 to P77, P125<br>to P127, P130 | 5.5 V                                                                                        |      |       | –10.0 <sup>Note</sup><br>2 | mA   |

|                                              |                                        | Total of P00 to P07, P10 to<br>P17, P22 to P27                                                                                    | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq \\ 5.5 \ V \end{array}$                    |      |       | -90.0                      | mA   |

|                                              | P30 to P35, P40 to P47, P50 to<br>P57, | $2.7 V \le V_{DD} < 4.0 V$                                                                                                        |                                                                                              |      | -15.0 | mA                         |      |

|                                              |                                        | P70 to P77, P125 to P127,<br>P130<br>(When duty = 70% <sup>Note 3</sup> )                                                         | 1.8 V ≤ V <sub>DD</sub> < 2.7 V                                                              |      |       | -7.0                       | mA   |

|                                              |                                        | , , ,                                                                                                                             | $1.6 V \le V_{DD} < 1.8 V$                                                                   |      |       | -3.0                       | mA   |

|                                              | Іон2                                   | Per pin for P20 and P21                                                                                                           | $\begin{array}{l} 1.6 \text{ V} \leq \text{V}_{\text{DD}} \leq \\ 5.5 \text{ V} \end{array}$ |      |       | –0.1 <sup>Note 2</sup>     | mA   |

|                                              |                                        | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                                         | $\begin{array}{l} 1.6 \ V \leq V_{\text{DD}} \leq \\ 5.5 \ V \end{array}$                    |      |       | -0.2                       | mA   |

Incorrect:

## $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.6 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{ V}_{SS} = 0 \text{ V})$

| Parameter                                   | Symbol | Conditions                                                                                                                     |                                                                                           | MIN. | TYP. | MAX.                      | Unit |

|---------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|---------------------------|------|

| Output<br>current,<br>low <sup>Note 1</sup> | Iol1   | Per pin for P00 to P07, P10 to<br>P17, P22 to P27, P30 to P35,<br>P40 to P47, P50 to P57, P70<br>to P77,<br>P125 to P127, P130 |                                                                                           |      |      | 20.0 <sup>Note</sup><br>2 | mA   |

|                                             |        | Per pin for P60 and P61                                                                                                        |                                                                                           |      |      | 15.0 <sup>Note</sup><br>2 | mA   |

|                                             |        | Total of P40 to P47, P130<br>(When duty = 70% <sup>Note 3</sup> )                                                              | $\begin{array}{c} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$                   |      |      | 70.0                      | mA   |

|                                             |        | Total of P00 to P07, <b>P14 to</b><br><b>P17</b><br>P30 to P35, P50 to P57, P70<br>to P77, P125 to P127                        | $\begin{array}{l} 2.7 \ \text{V} \leq \text{V}_{\text{DD}} < 4.0 \\ \text{V} \end{array}$ |      |      | 15.0                      | mA   |

|                                             |        |                                                                                                                                | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 2.7 \\ V \end{array}$                             |      |      | 9.0                       | mA   |

|                                             |        |                                                                                                                                | $\begin{array}{l} 1.6 \ V \leq V_{\text{DD}} < 1.8 \\ V \end{array}$                      |      |      | 4.5                       | mA   |

|                                             |        |                                                                                                                                | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$                   |      |      | 90.0                      | mA   |

|                                             |        |                                                                                                                                | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} < 4.0 \\ V \end{array}$                      |      |      | 35.0                      | mA   |

|                                             |        | (When duty = 70% <sup>Note 3</sup> )                                                                                           | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 2.7 \\ V \end{array}$                             |      |      | 20.0                      | mA   |

|                                             |        |                                                                                                                                | $\begin{array}{l} 1.6 \ V \leq V_{\text{DD}} < 1.8 \\ V \end{array}$                      |      |      | 10.0                      | mA   |

|                                             |        | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                                      |                                                                                           |      |      | 160.0                     | mA   |

|                                             | IOL2   | Per pin for P20 and P21                                                                                                        |                                                                                           |      |      | 0.4 <sup>Note 2</sup>     | mA   |

|                                             |        | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                                      | $\begin{array}{l} 1.6 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$                   |      |      | 0.8                       | mA   |

## Correct:

## $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.6 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{ V}_{SS} = 0 \text{ V})$

| Parameter                                   | Symbol | Conditions                                                                                                                     |                                                                         | MIN. | TYP. | MAX.                      | Unit |

|---------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|---------------------------|------|

| Output<br>current,<br>low <sup>Note 1</sup> | Iol1   | Per pin for P00 to P07, P10 to<br>P17, P22 to P27, P30 to P35,<br>P40 to P47, P50 to P57, P70<br>to P77,<br>P125 to P127, P130 |                                                                         |      |      | 20.0 <sup>Note</sup><br>2 | mA   |

|                                             |        | Per pin for P60 and P61                                                                                                        |                                                                         |      |      | 15.0 <sup>Note</sup><br>2 | mA   |

|                                             |        | Total of P40 to P47, P130<br>(When duty = 70% <sup>Note 3</sup> )                                                              | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | 70.0                      | mA   |

|                                             |        |                                                                                                                                | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} < 4.0 \\ V \end{array}$    |      |      | 15.0                      | mA   |

|                                             |        |                                                                                                                                | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 2.7 \\ V \end{array}$           |      |      | 9.0                       | mA   |

|                                             |        |                                                                                                                                | $\begin{array}{l} 1.6 \ V \leq V_{\text{DD}} < 1.8 \\ V \end{array}$    |      |      | 4.5                       | mA   |

|                                             |        | Total of P00 to P07, P10 to P17, P22 to P27                                                                                    | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | 90.0                      | mA   |

|                                             |        | to D77 D125 to D127                                                                                                            | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} < 4.0 \\ V \end{array}$    |      |      | 35.0                      | mA   |

|                                             |        | (when duty = 70%  mm)                                                                                                          | $\begin{array}{l} 1.8 \ V \leq V_{DD} < 2.7 \\ V \end{array}$           |      |      | 20.0                      | mA   |

|                                             |        |                                                                                                                                | $\begin{array}{l} 1.6 \ V \leq V_{\text{DD}} < 1.8 \\ V \end{array}$    |      |      | 10.0                      | mA   |

|                                             |        | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                                      |                                                                         |      |      | 160.0                     | mA   |

|                                             | IOL2   | Per pin for P20 and P21                                                                                                        |                                                                         |      |      | 0.4 <sup>Note 2</sup>     | mA   |

|                                             |        | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                                      | $\begin{array}{l} 1.6 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | 0.8                       | mA   |

## 13. 33.3.1 Pin characteristics(p.1068, p1069)

## Incorrect:

## (TA = -40 to +105°C, 2.4 V $\leq$ VDD $\leq$ 5.5 V, Vss = 0 V)

| Parameter                                    | Symbol | Conditions                                                                                                                     |                                                                         | MIN. | TYP. | MAX.                      | Unit |

|----------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|---------------------------|------|

| Output<br>current,<br>high <sup>Note 1</sup> | Іон1   | Per pin for P00 to P07, P10 to<br>P17,<br>P22 to P27, P30 to P35, P40 to<br>P47, P50 to P57, P70 to P77,<br>P125 to P127, P130 | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | -3.0 <sup>Note</sup><br>2 | mA   |

|                                              |        | Total of P00 to P07, <b>P14 to P17</b> ,<br>P30 to P35, P40 to P47, P50 to                                                     | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | -45.0                     | mA   |

|                                              | P130   | P57, P70 to P77, P125 to P127,<br>P130<br>(When duty = 70% <sup>Note 3</sup> )                                                 | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} < 4.0 \\ V \end{array}$    |      |      | -15.0                     | mA   |

|                                              |        |                                                                                                                                | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} < 2.7 \\ V \end{array}$    |      |      | -7.0                      | mA   |

|                                              | Іон2   | Per pin for P20 and P21                                                                                                        | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | –0.1 <sup>Note</sup><br>2 | mA   |

|                                              |        | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                                      | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | -0.2                      | mA   |

#### Date: Oct. 27, 2015

## Correct:

## (TA = -40 to +105°C, 2.4 V $\leq$ VDD $\leq$ 5.5 V, Vss = 0 V)

| Parameter                                    | Symbol | Conditions                                                                                                                     |                                                                         | MIN. | TYP. | MAX.                      | Unit |

|----------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|---------------------------|------|

| Output<br>current,<br>high <sup>Note 1</sup> | Іон1   | Per pin for P00 to P07, P10 to<br>P17,<br>P22 to P27, P30 to P35, P40 to<br>P47, P50 to P57, P70 to P77,<br>P125 to P127, P130 | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | -3.0 <sup>Note</sup><br>2 | mA   |

|                                              |        | Total of P00 to P07, P10 to P17,<br>P22 to P27                                                                                 | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | -45.0                     | mA   |

|                                              |        | P30 to P35, P40 to P47, P50 to<br>P57, P70 to P77, P125 to P127,<br>P130                                                       | $2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0 \text{ V}$                |      |      | -15.0                     | mA   |

|                                              |        | (When duty = $70\%^{\text{Note }3}$ )                                                                                          | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} < 2.7 \\ V \end{array}$    |      |      | -7.0                      | mA   |

|                                              | Іон2   | Per pin for P20 and P21                                                                                                        | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | –0.1 <sup>Note</sup><br>2 | mA   |

|                                              |        | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                                      | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | -0.2                      | mA   |

Incorrect:

## $(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

| Parameter                                   | Symbol                               | Conditions                                                                                                                     |                                                                                           | MIN. | TYP. | MAX.                      | Unit |

|---------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|---------------------------|------|

| Output<br>current,<br>low <sup>Note 1</sup> | Iol1                                 | Per pin for P00 to P07, P10 to<br>P17, P22 to P27, P30 to P35,<br>P40 to P47, P50 to P57, P70<br>to P77,<br>P125 to P127, P130 |                                                                                           |      |      | 8.5 <sup>Note 2</sup>     | mA   |

|                                             |                                      | Per pin for P60 and P61                                                                                                        |                                                                                           |      |      | 15.0 <sup>Note</sup><br>2 | mA   |

|                                             |                                      | Total of P40 to P47, P130<br>(When duty = 70% <sup>Note 3</sup> )                                                              | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$                   |      |      | 40.0                      | mA   |

|                                             |                                      |                                                                                                                                | $\begin{array}{l} 2.7~V \leq V_{\text{DD}} < 4.0 \\ V \end{array}$                        |      |      | 15.0                      | mA   |

|                                             |                                      |                                                                                                                                | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} < 2.7 \\ V \end{array}$                      |      |      | 9.0                       | mA   |

|                                             |                                      | Total of P00 to P07, <b>P14 to</b><br><b>P17</b><br>P30 to P35, P50 to P57, P70<br>to P77, P125 to P127                        | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$                   |      |      | 60.0                      | mA   |

|                                             |                                      |                                                                                                                                | $\begin{array}{l} 2.7 \ \text{V} \leq \text{V}_{\text{DD}} < 4.0 \\ \text{V} \end{array}$ |      |      | 35.0                      | mA   |

|                                             | (When duty = 70% <sup>Note 3</sup> ) | (when duty = 70%)                                                                                                              | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} < 2.7 \\ V \end{array}$                      |      |      | 20.0                      | mA   |

|                                             |                                      | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                                      |                                                                                           |      |      | 100.0                     | mA   |

|                                             | IOL2                                 | Per pin for P20 and P21                                                                                                        |                                                                                           |      |      | 0.4 <sup>Note 2</sup>     | mA   |

|                                             |                                      | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                                      | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$                   |      |      | 0.8                       | mA   |

Correct:

## $(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

| Parameter                                   | Symbol | Conditions                                                                                                                                    |                                                                         | MIN. | TYP. | MAX.                      | Unit |

|---------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|---------------------------|------|

| Output<br>current,<br>low <sup>Note 1</sup> | Iol1   | Per pin for P00 to P07, P10 to<br>P17, P22 to P27, P30 to P35,<br>P40 to P47, P50 to P57, P70<br>to P77,<br>P125 to P127, P130                |                                                                         |      |      | 8.5 <sup>Note 2</sup>     | mA   |

|                                             |        | Per pin for P60 and P61                                                                                                                       |                                                                         |      |      | 15.0 <sup>Note</sup><br>2 | mA   |

|                                             |        | Total of P40 to P47, P130<br>(When duty = 70% <sup>Note 3</sup> )                                                                             | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | 40.0                      | mA   |

|                                             |        |                                                                                                                                               | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} < 4.0 \\ V \end{array}$    |      |      | 15.0                      | mA   |

|                                             |        |                                                                                                                                               | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} < 2.7 \\ V \end{array}$    |      |      | 9.0                       | mA   |

|                                             |        | Total of P00 to P07, P10 to<br>P17, P22 to P27<br>P30 to P35, P50 to P57, P70<br>to P77, P125 to P127<br>(When duty = 70% <sup>Note 3</sup> ) | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | 60.0                      | mA   |

|                                             |        |                                                                                                                                               | $\begin{array}{l} 2.7 \ V \leq V_{\text{DD}} < 4.0 \\ V \end{array}$    |      |      | 35.0                      | mA   |

|                                             |        | (when duty = 70%)                                                                                                                             | $\begin{array}{l} 2.4 \ V \leq V_{DD} < 2.7 \\ V \end{array}$           |      |      | 20.0                      | mA   |

|                                             |        | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                                                     |                                                                         |      |      | 100.0                     | mA   |

|                                             | Iol2   | Per pin for P20 and P21                                                                                                                       |                                                                         |      |      | 0.4 <sup>Note 2</sup>     | mA   |

|                                             |        | Total of all pins<br>(When duty = 70% <sup>Note 3</sup> )                                                                                     | $\begin{array}{l} 2.4 \ V \leq V_{\text{DD}} \leq 5.5 \\ V \end{array}$ |      |      | 0.8                       | mA   |

## 14. 8.3.5 Real-time clock control register 1 (RTCC1)

Additional entry to Figure 8 - 6 Format of Real-time clock control register 1 (RTCC1) (3/3)

## <u>Old:</u>

| RWAIT        | Wait control of real-time clock 2                                                                   | RWAIT                                                                                                         | Wait control of real-time clock 2                                                                  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|

| 0            | Sets counter operation.                                                                             | 0                                                                                                             | Sets counter operation.                                                                            |  |  |  |

| 1            | Stops SEC to YEAR counters. Mode to read or write counter value                                     | 1                                                                                                             | Stops SEC to YEAR counters. Mode to read or write counter value                                    |  |  |  |

| This bit con | trols the operation of the counter.                                                                 | This bit con                                                                                                  | trols the operation of the counter.                                                                |  |  |  |

| Be sure to v | vrite "1" to it to read or write the counter value.                                                 | Be sure to                                                                                                    | write "1" to it to read or write the counter value.                                                |  |  |  |

| As the coun  | ter (16-bit) is continuing to run, completereading or writing within one second and turn back to 0. | As the counter (16-bit) is continuing to run, completereading or writing within one second and turn back to 0 |                                                                                                    |  |  |  |