# **RENESAS TECHNICAL UPDATE**

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                       | Document<br>No.         | TN-RL*-A041A/E         | Rev.                                                   | 1.00 |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|--------------------------------------------------------|------|--|

| Title                 | Correction for Incorrect Description Notice<br>RL78/G14 Descriptions in the Hardware Use<br>Rev. 3.10 Changed | Information<br>Category | Technical Notification |                                                        |      |  |

|                       |                                                                                                               | Lot No.                 |                        |                                                        |      |  |

| Applicable<br>Product |                                                                                                               |                         | Reference<br>Document  | RL78/G14 User's Man<br>Rev.3.10<br>R01UH0186EJ0310 (\$ |      |  |

This document describes misstatements found in the RL78/G14 User's Manual: Hardware Rev.3.10 (R01UH0186EJ0310).

#### **Corrections**

| Applicable Item                                                                                           | Applicable Page                                                                      | Contents                       |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------|

| 1.2 Ordering Information<br>Deletion of R5F104JK and R5F104JL from 52-pin                                 | Page 8                                                                               | Content change                 |

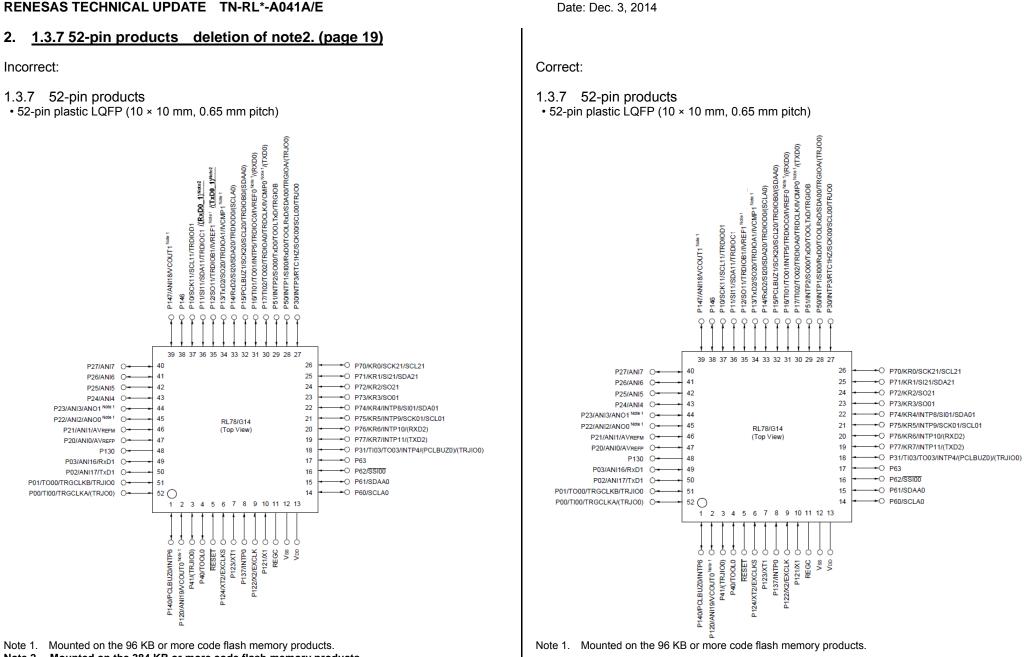

| 1.3.7 52-pin products deletion of note2.                                                                  | Page 19                                                                              | Content change                 |

| 1.6 Outline of Functions<br>Deletion of 52-pin information                                                | Pages 48 to 50                                                                       | Content change                 |

| 2.1.15 52-pin (Code Flash Memory 96 KB to 512 KB)<br>Deletion of ROM 384KB and 512KB information          | Page 84                                                                              | Content change                 |

| Deletion of R5F104JK and R5F104JL information                                                             | Pages 131, 132, 136,<br>137, 138, 143, 148,<br>193, 958, 981, 1086,<br>1134 and 1304 | Content change                 |

| 6.3.3 Timer mode register mn<br>Figure 6 - 12 the count clock selection                                   | Page 303                                                                             | Incorrect descriptions revised |

| 17.3.12 Serial output register m (SOm)<br>Figure 17 - 19 Reset value of serial output register m<br>(SOm) | Page 708                                                                             | Incorrect descriptions revised |

| 19.5.3 DTC Pending Instruction                                                                            | Page 982                                                                             | Incorrect descriptions revised |

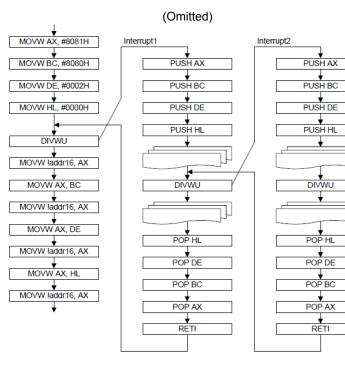

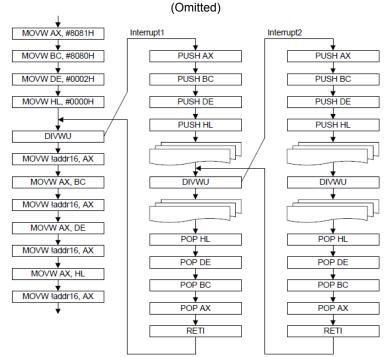

| 21.4.4 Interrupt servicing during division instruction                                                    | Page 1021                                                                            | Specifications added           |

| 21.4.5 Interrupt request hold                                                                             | Page 1022                                                                            | Incorrect descriptions revised |

| 33.2 Operation List                                                                                       | Page 1153                                                                            | Specifications added           |

#### Document Improvement

The above corrections will be made for the next revision of the User's Manual: Hardware.

Corrections in the User's Manual: Hardware

| No.  | Corrections and                                                                                  | 19           | Pages in this document                                                                  |                 |

|------|--------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------|-----------------|

| 110. | Document No.                                                                                     | English      | R01UH0186EJ0310                                                                         | for corrections |

| 1    | 1.2 Ordering Information<br>Deletion of R5F104JK and R5F104J<br>52-pin                           |              | Page 8                                                                                  | p.3             |

| 2    | 1.3.7 52-pin products deletion of r                                                              | note2.       | Page 19                                                                                 | p.4             |

| 3    | 1.6 Outline of Functions<br>Deletion of 52-pin information                                       |              | Pages 48-50                                                                             | p.5-7           |

| 4    | 2.1.15 52-pin (Code Flash Memo<br>512 KB)<br>Deletion of ROM 384KB and 512KB                     | -            | Page 84                                                                                 | p.8             |

| 5    | Deletion of R5F104JK and R5F104J information                                                     | L            | Pages 131, 132,<br>136, 137, 138, 143,<br>148, 193, 958, 981,<br>1086, 1134 and<br>1304 | p.9-14          |

| 6    | 6.3.3 Timer mode register mn<br>Figure 6 - 12 the count clock selection                          | on           | Page 303                                                                                | p.15            |

| 7    | 17.3.12 Serial output register m (SO<br>Figure 17 - 19 Reset value of serial<br>register m (SOm) |              | Page 708                                                                                | p.16            |

| 8    | 19.5.3 DTC Pending Instruction                                                                   |              | Page 981                                                                                | p.17            |

| 9    | 21.4.4 Interrupt servicing dur<br>instruction                                                    | ing division | Page 1021                                                                               | p.18            |

| 10   | 21.4.5 Interrupt request hold                                                                    |              | Page 1022                                                                               | p.19            |

| 11   | 33.2 Operation List                                                                              |              | Page 1153                                                                               | p.20            |

Incorrect: Bold with underline: Correct: Gray hatched

### **Revision History**

RL78/G14 User's Manual: Hardware Rev.3.10 Correction for Incorrect Description Notice

| Document Number | Date         | Description                                                     |

|-----------------|--------------|-----------------------------------------------------------------|

| TN-RL*-A041A/E  | Dec. 3, 2014 | First edition issued<br>No.1 to 11 in corrections (This notice) |

Incorrect:

#### 1. <u>1.2 Ordering Information</u> <u>Deletion of R5F104JK and R5F104JL from 52-pin (page 8)</u>

Date: Dec. 3, 2014

#### Correct:

| Pin Package count                                 | Fields of<br>Application<br>Note 1 | Ordering Part Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin<br>count | Package                                                  | Fields of<br>Application<br>Note 1 | Ordering Part Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52 pins<br>LQFP<br>(10 × 10 mm,<br>0.65 mm pitch) | A<br>D<br>G                        | (Omitted)<br>R5F104JCAFA#V0, R5F104JDAFA#V0,<br>R5F104JCAFA#V0, R5F104JFAFA#V0,<br>R5F104JCAFA#V0, R5F104JHAFA#V0, R5F104JJAFA#V0<br>R5F104JCAFA#X0, R5F104JDAFA#X0,<br>R5F104JCAFA#X0, R5F104JDAFA#X0,<br>R5F104JGAFA#X0, R5F104JHAFA#X0, R5F104JJAFA#X0<br><b>R5F104JGAFA#X0</b> , R5F104JHAFA#X0, R5F104JJAFA#X0<br><b>R5F104JCBFA#V0</b> , R5F104JLAFA#30 <sup>Note2</sup><br><b>R5F104JCBFA#V0</b> , R5F104JDDFA#V0,<br>R5F104JCBFA#V0, R5F104JDDFA#V0,<br>R5F104JCBFA#V0, R5F104JDDFA#V0,<br>R5F104JCBFA#V0, R5F104JDDFA#V0,<br>R5F104JCDFA#X0, R5F104JDDFA#V0,<br>R5F104JCDFA#X0, R5F104JDDFA#X0,<br>R5F104JCDFA#X0, R5F104JDDFA#X0,<br>R5F104JCBFA#X0, R5F104JDDFA#X0,<br>R5F104JCGFA#V0, R5F104JDGFA#V0,<br>R5F104JCGFA#V0, R5F104JDGFA#V0,<br>R5F104JCGFA#V0, R5F104JDGFA#V0,<br>R5F104JCGFA#V0, R5F104JDGFA#V0,<br>R5F104JCGFA#X0, R5F104JDGFA#V0,<br>R5F104JCGFA#X0, R5F104JDGFA#V0,<br>R5F104JCGFA#X0, R5F104JDGFA#V0,<br>R5F104JCGFA#X0, R5F104JDGFA#V0,<br>R5F104JCGFA#X0, R5F104JDGFA#V0,<br>R5F104JCGFA#X0, R5F104JDGFA#V0,<br>R5F104JCGFA#X0, R5F104JDGFA#X0,<br>R5F104JCGFA#X0, R5F104JCGFA#X0,<br>R5F104JCGFA#X0, R5F104JCGFA#X0,<br>R5F104JCGFA#X0, R5F104JCGFA#X0,<br>R5F104JCGFA#X0, R5F104JCGFA#X0,<br>R5F104JCGFA#X0, R5F104JCGFA#X0,<br>R5F104JCGFA#X0, R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104JCGFA#X0,<br>R5F104 | 52 pins      | 52-pin plastic<br>LQFP<br>(10 × 10 mm,<br>0.65 mm pitch) | A<br>D<br>G                        | R5F104JCAFA#V0, R5F104JDAFA#V0,<br>R5F104JCAFA#V0, R5F104JFAFA#V0,<br>R5F104JGAFA#V0, R5F104JHAFA#V0, R5F104JJAFA#V0<br>R5F104JCAFA#X0, R5F104JDAFA#X0,<br>R5F104JCAFA#X0, R5F104JDAFA#X0,<br>R5F104JGAFA#X0, R5F104JHAFA#X0, R5F104JJAFA#X0<br>R5F104JCDFA#V0, R5F104JDDFA#V0,<br>R5F104JGDFA#V0, R5F104JHDFA#V0,<br>R5F104JGDFA#V0, R5F104JHDFA#V0,<br>R5F104JGDFA#V0, R5F104JHDFA#X0,<br>R5F104JGDFA#X0, R5F104JHDFA#X0,<br>R5F104JGDFA#X0, R5F104JHDFA#X0,<br>R5F104JGDFA#X0, R5F104JHDFA#X0,<br>R5F104JGDFA#X0, R5F104JHDFA#X0,<br>R5F104JGGFA#V0, R5F104JHDFA#X0,<br>R5F104JGGFA#V0, R5F104JHDFA#X0,<br>R5F104JGGFA#V0, R5F104JHGFA#V0,<br>R5F104JGGFA#V0, R5F104JHGFA#V0,<br>R5F104JGGFA#V0, R5F104JHGFA#V0,<br>R5F104JGGFA#X0, R5F104JHGFA#X0,<br>R5F104JGGFA#X0, R5F104JHGFA#X0, R5F104JJGFA#X0,<br>R5F104JGGFA#X0, R5F104JHGFA#X0, R5F104JJGFA#X0,<br>R5F104JGGFA#X0, R5F104JHGFA#X0, R5F104JJGFA#X0,<br>R5F104JGGFA#X0, R5F104JHGFA#X0, R5F104JJGFA#X0,<br>R5F104JGGFA#X0, R5F104JHGFA#X0, R5F104JJGFA#X0,<br>R5F104JGGFA#X0, R5F104JHGFA#X0, R5F104JJGFA#X0,<br>R5F104JGGFA#X0, R5F104JHGFA#X0, R5F104JHGFA#X0,<br>R5F104JGGFA#X0, R5F104JHGFA#X0, R5F104JHGFA#X0, |

Note 2. Mounted on the 384 KB or more code flash memory products.

#### 3. <u>1.6 Outline of Functions</u> <u>Deletion of 52-pin information (Pages 48 to 50)</u>

Incorrect:

[48-pin, 52-pin, 64-pin products (code flash memory 384 KB to 512 KB)]

Caution This outline describes the functions at the time when Peripheral I/O redirection register 0, 1(PIOR0, 1) are set to 00H.

|                                               |                                        |                                     |                                                               | (1/2          |  |  |

|-----------------------------------------------|----------------------------------------|-------------------------------------|---------------------------------------------------------------|---------------|--|--|

|                                               |                                        | 48-pin                              | 52-pin                                                        | 64-pin        |  |  |

|                                               | Item                                   | R5F104Gx                            | .R5F104Jx                                                     | R5F104Lx      |  |  |

|                                               |                                        | (x = K, L)                          | (x = K, L)                                                    | (x = K, L)    |  |  |

| Code flash                                    | memory (KB)                            | 384 to 512                          | 384 to 512                                                    | 384 to 512    |  |  |

|                                               | memory (KB)                            | 8                                   | 8                                                             | 8             |  |  |

| RAM (KB)                                      |                                        | 32 to 48 Note                       | 32 to 48 Note                                                 | 32 to 48 Note |  |  |

| Address sp                                    | ace                                    | 1 MB                                | •                                                             | •             |  |  |

|                                               |                                        | (Omitted)                           |                                                               |               |  |  |

| I/O port                                      | Total                                  | 44                                  | 48                                                            | 58            |  |  |

|                                               | CMOS I/O                               | 34                                  |                                                               | 48            |  |  |

|                                               | CMOS input                             | 5                                   | 5                                                             | 5             |  |  |

|                                               | CMOS output                            | 1                                   | 1                                                             | 1             |  |  |

|                                               | N-ch open-drain I/O<br>(6 V tolerance) | 4                                   | 4                                                             | 4             |  |  |

| Timer                                         | 16-bit timer                           | 8 channels                          | 8 channels                                                    |               |  |  |

|                                               |                                        |                                     | (TAU: 4 channels, Timer RJ: 1 channel, Timer RD: 2            |               |  |  |

|                                               |                                        | channels, Timer RG: 1 channel)      |                                                               |               |  |  |

| Watchdog timer                                |                                        | 1 channel                           |                                                               |               |  |  |

| Real-time clock(RTC)<br>12-bit interval timer |                                        | 1 channel                           |                                                               |               |  |  |

|                                               |                                        | 1 channel                           |                                                               |               |  |  |

|                                               | Timer output                           |                                     | Timer outputs: 14 channels                                    |               |  |  |

|                                               |                                        | PWM outputs: 9 cl                   | hannels                                                       |               |  |  |

|                                               | RTC output                             | 1                                   |                                                               |               |  |  |

|                                               |                                        | <ul> <li>1 Hz (subsystem</li> </ul> | <ul> <li>1 Hz (subsystem clock: fsub = 32.768 kHz)</li> </ul> |               |  |  |

(Note is listed on the next page.)

Date: Dec. 3, 2014

#### Correct:

[48-pin, 64-pin products (code flash memory 384 KB to 256 KB)] Caution This outline describes the functions at the time when Peripheral I/O redirection register 0, 1(PIOR0, 1) are set to 00H.

|                       |                     |                                                    | (1/2)                      |  |  |

|-----------------------|---------------------|----------------------------------------------------|----------------------------|--|--|

|                       |                     | 48-pin                                             | 64-pin                     |  |  |

|                       | Item                | R5F104Gx                                           | R5F104Lx                   |  |  |

|                       |                     | (x = K, L)                                         | (x = K, L)                 |  |  |

| Code flash            | memory (KB)         | 384 to 512                                         | 384 to 512                 |  |  |

| Data flash r          | memory (KB)         | 8                                                  | 8                          |  |  |

| RAM (KB)              |                     | 32 to 48 Note                                      | 32 to 48 Note              |  |  |

| Address sp            | ace                 | 1 MB                                               |                            |  |  |

|                       |                     | (Omitted)                                          |                            |  |  |

| I/O port              | Total               | 44                                                 | 58                         |  |  |

|                       | CMOS I/O            | 34                                                 | 48                         |  |  |

|                       | CMOS input          | 5                                                  | 5                          |  |  |

|                       | CMOS output         | 1                                                  | 1                          |  |  |

|                       | N-ch open-drain I/O | 4                                                  | 4                          |  |  |

|                       | (6 V tolerance)     |                                                    |                            |  |  |

| Timer                 | 16-bit timer        | 8 channels                                         |                            |  |  |

|                       |                     | (TAU: 4 channels, Timer RJ: 1 channel, Timer RD: 2 |                            |  |  |

|                       |                     | channels, Timer RG: 1 channel)                     |                            |  |  |

|                       | Watchdog timer      | 1 channel                                          | 1 channel                  |  |  |

| Real-time clock(RTC)  |                     | 1 channel                                          |                            |  |  |

| 12-bit interval timer |                     | 1 channel                                          |                            |  |  |

| Timer output          |                     | Timer outputs: 14 channels                         | Timer outputs: 14 channels |  |  |

|                       |                     | PWM outputs: 9 channels                            |                            |  |  |

|                       | RTC output          | 1                                                  |                            |  |  |

|                       |                     | <ul> <li>1 Hz (subsystem clock: fsue</li> </ul>    | a = 32.768 kHz)            |  |  |

(Note is listed on the next page.)

Date: Dec. 3, 2014

Incorrect:

Note The flash library uses RAM in self-programming and rewriting of the data flash memory. The target products and start address of the RAM areas used by the flash library are shown below.

#### R5F104xL (x = G, J, L, M, P): Start address F3F00H

For the RAM areas used by the flash library, see Self RAM list of Flash Self-Programming Library for RL78 Family (R20UT2944).

Correct:

Note The flash library uses RAM in self-programming and rewriting of the data flash memory. The target products and start address of the RAM areas used by the flash library are shown below.

R5F104xL (x = G, L, M, P): Start address F3F00H

For the RAM areas used by the flash library, see Self RAM list of Flash Self-Programming Library for RL78 Family (R20UT2944).

Date: Dec. 3, 2014

Item

Incorrect:

Correct:

|                          |                      |                                                                                       |                                                                  | (2/2)          |  |  |

|--------------------------|----------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------|--|--|

|                          |                      | 48-pin                                                                                | _ <b>52-</b> pin_                                                | 64-pin         |  |  |

| Item                     |                      | R5F104Gx                                                                              | R5F104Jx                                                         | R5F104Lx       |  |  |

|                          |                      | (x = K, L)                                                                            | _(x = K. L)_                                                     | (x = K, L)     |  |  |

| Clock output/buzzer o    | utput                | 2                                                                                     | 2                                                                | 2              |  |  |

|                          |                      | • 2.44 kHz, 4.88 kHz, 9                                                               | • 2.44 kHz, 4.88 kHz, 9.76 kHz, 1.25 MHz, 2.5 MHz, 5 MHz, 10 MHz |                |  |  |

|                          |                      | (Main system clock: f                                                                 | MAIN = 20 MHz operation                                          | )              |  |  |

|                          |                      | • 256 Hz, 512 Hz, 1.02                                                                | 4 kHz, 2.048 kHz, 4.096 k                                        | Hz, 8.192 kHz, |  |  |

|                          |                      | 16.384 kHz, 32.768 kH                                                                 | lz                                                               |                |  |  |

|                          |                      | (Subsystem clock: fS                                                                  | UB = 32.768 kHz operation                                        | n)             |  |  |

| 8/10-bit resolution A/E  | ) converter          | 10 channels                                                                           | _12_channels_                                                    | 12 channels    |  |  |

| D/A converter            |                      | 2 channels                                                                            |                                                                  |                |  |  |

| Comparator               |                      | 2 channels                                                                            |                                                                  |                |  |  |

| Serial interface         |                      | [48-pin, 52-pin produc                                                                | ts]                                                              |                |  |  |

|                          |                      | <ul> <li>CSI: 2 channels/UAR</li> </ul>                                               | T (UART supporting LIN-b                                         | ous): 1        |  |  |

|                          |                      | channel/simplified I2C                                                                | 2 channels                                                       |                |  |  |

|                          |                      |                                                                                       | : 1 channel/simplified I2C:                                      |                |  |  |

|                          |                      |                                                                                       | T: 1 channel/simplified I20                                      | C: 2 channels  |  |  |

|                          |                      | [64-pin products]                                                                     |                                                                  |                |  |  |

|                          |                      | <ul> <li>CSI: 2 channels/UAR</li> </ul>                                               | T (UART supporting LIN-b                                         | ous): 1        |  |  |

|                          |                      | channel/simplified I2C: 2 channels                                                    |                                                                  |                |  |  |

|                          |                      | <ul> <li>CSI: 2 channels/UART: 1 channel/simplified I2C: 2 channels</li> </ul>        |                                                                  |                |  |  |

|                          |                      | CSI: 2 channels/UART: 1 channel/simplified I2C: 2 channels                            |                                                                  |                |  |  |

|                          | I <sup>2</sup> C bus | 1 channel                                                                             | <u>1.channel</u>                                                 | 1 channel      |  |  |

| Data transfer controlle  | ( - )                | 32 sources                                                                            |                                                                  | 33 sources     |  |  |

| Event link controller (E | ELC)                 | Event input: 22                                                                       |                                                                  |                |  |  |

|                          |                      | Event trigger output: 9                                                               |                                                                  |                |  |  |

| Vectored interrupt       | Internal             | 24                                                                                    | 24                                                               | 24             |  |  |

| sources                  | External             | 10                                                                                    | 12                                                               | 13             |  |  |

| Key interrupt            |                      | 6                                                                                     | 8                                                                | 8              |  |  |

| Reset                    |                      | Reset by RESET pin                                                                    |                                                                  |                |  |  |

|                          |                      | <ul> <li>Internal reset by wate</li> </ul>                                            | chdog timer                                                      |                |  |  |

|                          |                      | <ul> <li>Internal reset by pow</li> </ul>                                             |                                                                  |                |  |  |

|                          |                      | <ul> <li>Internal reset by voltage detector</li> </ul>                                |                                                                  |                |  |  |

|                          |                      | <ul> <li>Internal reset by illegal instruction execution Note</li> </ul>              |                                                                  |                |  |  |

|                          |                      | <ul> <li>Internal reset by RAM parity error</li> </ul>                                |                                                                  |                |  |  |

|                          |                      | Internal reset by illegal-memory access                                               |                                                                  |                |  |  |

| Power-on-reset circuit   |                      | • Power-on-reset: 1.51 ±0.03 V                                                        |                                                                  |                |  |  |

|                          |                      | • Power-down-reset: 1.50 ±0.03 V                                                      |                                                                  |                |  |  |

| Voltage detector         |                      | 1.63 V to 4.06 V (14 stages)                                                          |                                                                  |                |  |  |

| On-chip debug function   | n                    | Provided                                                                              |                                                                  |                |  |  |

| Power supply voltage     |                      | $V_{DD}$ = 1.6 to 5.5 V<br>TA = -40 to +85°C (A: Consumer applications, D: Industrial |                                                                  |                |  |  |

| Operating ambient ter    | nperature            |                                                                                       | Consumer applications, D:                                        | Industrial     |  |  |

|                          |                      | applications),                                                                        |                                                                  |                |  |  |

|                          |                      | $T_A = -40$ to +105°C (G: Industrial applications)                                    |                                                                  |                |  |  |

(Omitted)

Clock output/buzzer output 2 2 • 2.44 kHz, 4.88 kHz, 9.76 kHz, 1.25 MHz, 2.5 MHz, 5 MHz, 10 MHz (Main system clock: fMAIN = 20 MHz operation) • 256 Hz, 512 Hz, 1.024 kHz, 2.048 kHz, 4.096 kHz, 8.192 kHz, 16.384 kHz. 32.768 kHz (Subsystem clock: fSUB = 32.768 kHz operation) 8/10-bit resolution A/D converter 10 channels 12 channels D/A converter 2 channels Comparator 2 channels Serial interface [48-pin products] CSI: 2 channels/UART (UART supporting LIN-bus): 1 channel/simplified I2C: 2 channels CSI: 1 channel/UART: 1 channel/simplified I2C: 1 channel CSI: 2 channels/UART: 1 channel/simplified I2C: 2 channels [64-pin products] CSI: 2 channels/UART (UART supporting LIN-bus): 1 channel/simplified I2C: 2 channels • CSI: 2 channels/UART: 1 channel/simplified I2C: 2 channels • CSI: 2 channels/UART: 1 channel/simplified I2C: 2 channels I<sup>2</sup>C bus 1 channel 1 channel Data transfer controller (DTC) 32 sources 33 sources Event input: 22 Event link controller (ELC) Event trigger output: 9 Vectored interrupt Internal 24 24 sources 10 13 External 6 Key interrupt 8 Reset Reset by RESET pin · Internal reset by watchdog timer Internal reset by power-on-reset Internal reset by voltage detector · Internal reset by illegal instruction execution Note Internal reset by RAM parity error Internal reset by illegal-memory access Power-on-reset: 1.51 ±0.03 V Power-on-reset circuit Power-down-reset: 1.50 ±0.03 V Voltage detector 1.63 V to 4.06 V (14 stages) On-chip debug function Provided Power supply voltage VDD = 1.6 to 5.5 V Operating ambient temperature TA = -40 to +85°C (A: Consumer applications, D: Industrial applications),  $T_A = -40$  to  $+105^{\circ}C$  (G: Industrial applications)

48-pin

R5F104Gx

(x = K, L)

(2/2)

64-pin

R5F104Lx

(x = K, L)

(Omitted)

(c) 2014. Renesas Electronics Corporation. All rights reserved.

#### 4. <u>2.1.15 52-pin (Code Flash Memory 96 KB to 512 KB)</u> Deletion of ROM 384KB and 512KB information (Page 84)

Incorrect:

#### 2.1.15 52-pin (Code Flash Memory 96 KB to 512 KB)

|                  |                |     |                           |                                                                         | (1/2)                                                                          |  |

|------------------|----------------|-----|---------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| Function<br>Name | Pin Type       | I/O | After<br>Reset<br>Release | Alternate Function                                                      | Function                                                                       |  |

| (Omitted)        |                |     |                           |                                                                         |                                                                                |  |

| P10<br>P11       | 8-1-8<br>7-1-8 | I/O | Input<br>port             | SCK11/SCL11/TRDIOD1<br>SI11/SDA11/TRDIOC1(<br>(RxD0_1) <sup>Note3</sup> | Port 1.<br>8-bit I/O port.<br>Input/output can be specified in<br>1-bit units. |  |

| P12              | 7-6-6          |     |                           | SO11/TRDIOB1/IVREF1/<br>(INTP5)/(TxD0_1) <sup>Note3</sup>               | (Omitted)                                                                      |  |

|                  | (Omitted)      |     |                           |                                                                         |                                                                                |  |

- Note 1. Each pin can be specified as either digital or analog by setting port mode control register x (PMCx) (Can be specified in 1-bit units).

- Note 2. Each pin can be specified as either digital or analog by setting the A/D port configuration register (ADPC).

- Note 3. Mounted on the 384 KB or more code flash memory products.

- Remark Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection registers 0, 1(PIOR0, 1).

Date: Dec. 3, 2014

Correct:

#### 2.1.15 52-pin (Code Flash Memory 96 KB to 256 KB)

|           |          |     |                           |                                 | (1/2)                                                         |  |  |

|-----------|----------|-----|---------------------------|---------------------------------|---------------------------------------------------------------|--|--|

|           | Pin Type | I/O | After<br>Reset<br>Release | Alternate Function              | Function                                                      |  |  |

|           |          |     |                           | (Omitted)                       |                                                               |  |  |

| P10       | 8-1-8    | I/O | Input                     | SCK11/SCL11/TRDIOD1             | Port 1.                                                       |  |  |

| P11       | 7-1-8    |     | port                      | SI11/SDA11/TRDIOC1              | 8-bit I/O port.                                               |  |  |

| P12       | 7-6-6    |     |                           | SO11/TRDIOB1/IVREF1/<br>(INTP5) | Input/output can be specified in<br>1-bit units.<br>(Omitted) |  |  |

| (Omitted) |          |     |                           |                                 |                                                               |  |  |

(1/2)

Note 1. Each pin can be specified as either digital or analog by setting port mode control register x (PMCx) (Can be specified in 1-bit units).

Note 2. Each pin can be specified as either digital or analog by setting the A/D port configuration register (ADPC).

Remark Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection registers 0, 1(PIOR0, 1).

| RENESAS TECHNICAL UPDATE TN-RL*-A041A/E                                                                                                                                                                                                                                                                    | Date: Dec. 3, 2014                                                                                                                                                                                                                                                                                    |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 5. <u>Deletion of R5F104JK and R5F104JL information</u><br>(the corresponding page is indicated below.)                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                       |  |  |

| 3.1 Memory Space (Page 131)         Incorrect:         Figure 3 - 9 Memory Map (R5F104xK (x = G, J, L, M, P)).         3.1 Memory Space (Page 132)         Incorrect:         Figure 3 - 10 Memory Map (R5F104xL (x = G, J, L, M, P)).                                                                     | 3.1 Memory Space (Page 131)         Correct:         Figure 3 - 9 Memory Map (R5F104xK (x = G, L, M, P))         3.1 Memory Space (Page 132)         Correct:         Figure 3 - 10 Memory Map (R5F104xL (x = G, L, M, P))                                                                            |  |  |

| Remark of Correspondence Between Address Values and Block Numbers in Flash Memory (Page 136)         Incorrect:         Table 3 - 3 Correspondence Between Address Values and Block Numbers in Flash Memory (3/4)         (Omitted)         Remark R5F104xK (x = G, J, L, M, P): Block numbers 00H to 17FH | Remark of Correspondence Between Address Values and Block Numbers in Flash Memory (Page 136)         Correct:         Table 3 - 3 Correspondence Between Address Values and Block Numbers in Flash Memory (3/4)         (Omitted)         Remark R5F104xK (x = G, L, M, P): Block numbers 00H to 17FH |  |  |

| Remark of Correspondence Between Address Values and Block Numbers in Flash Memory (Page 137)         Incorrect:         Table 3 - 4 Correspondence Between Address Values and Block Numbers in Flash Memory (4/4)         (Omitted)         Remark R5F104xL (x = G, J, L, M, P): Block numbers 00H to 1FFH | Remark of Correspondence Between Address Values and Block Numbers in Flash Memory (Page 137)         Correct:         Table 3 - 4 Correspondence Between Address Values and Block Numbers in Flash Memory (4/4)         (Omitted)         Remark R5F104xL (x = G, L, M, P): Block numbers 00H to 1FFH |  |  |

|                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                       |  |  |

#### 3.1.1 Internal program memory space (page 138)

Incorrect:

| Table 3 - 5 Internal ROM Capacity         |              |                                  |  |  |  |  |

|-------------------------------------------|--------------|----------------------------------|--|--|--|--|

| Part Number                               | Internal ROM |                                  |  |  |  |  |

| Fait Nulliber                             | Structure    | Capacity                         |  |  |  |  |

| R5F104xA (x = A to C, E to G)             | Flash memory | 16384 × 8bits(00000H to 03FFFH)  |  |  |  |  |

| R5F104xC (x = A to C, E to G, J, L)       |              | 32768 × 8bits(00000H to 07FFFH)  |  |  |  |  |

| R5F104xD (x = A to C, E to G, J, L)       |              | 49152 × 8bits(00000H to 0BFFFH)  |  |  |  |  |

| R5F104xE (x = A to C, E to G, J, L)       |              | 65536 × 8bits(00000H to 0FFFFH)  |  |  |  |  |

| R5F104xF (x = A to C, E to G, J, L, M, P) |              | 98304 × 8bits(00000H to 17FFFH)  |  |  |  |  |

| R5F104xG (x = A to C, E to G, J, L, M, P) |              | 131072 × 8bits(00000H to 1FFFFH) |  |  |  |  |

| R5F104xH (x = E to G, J, L, M, P)         |              | 196608 × 8bits(00000H to 2FFFH)  |  |  |  |  |

| R5F104xJ (x = F, G ,J , L, M, P)          |              | 262144 × 8bits(00000H to 3FFFFH) |  |  |  |  |

| R5F104xK.(x.=.G., J. L. M. P)             | ]            | 393216 × 8bits(00000H to 5FFFFH) |  |  |  |  |

| R5F104xL (x = G, J, L, M, P)              |              | 524288 × 8bits(00000H to 7FFFH)  |  |  |  |  |

(Omitted)

#### 3.1.3 Internal data memory space (page 143)

Incorrect:

| Table 3 - 8 Inter                         | nal RAM Capacity                |

|-------------------------------------------|---------------------------------|

| Part Number                               | Internal RAM                    |

| R5F104xA (x = A to C, E to G)             | 2560 × 8bits(FF500H to FFEFFH)  |

| R5F104xC (x = A to C, E to G, J, L)       | 4096 × 8bits(FEF00H to FFEFFH)  |

| R5F104xD (x = A to C, E to G, J, L)       | 5632 × 8bits(FE900H to FFEFFH)  |

| R5F104xE (x = A to C, E to G, J, L)       |                                 |

| R5F104xF (x = A to C, E to G, J, L, M, P) | 12288 × 8bits(FCF00H to FFEFFH) |

| R5F104xG (x = A to C, E to G, J, L, M, P) | 16384 × 8bits(FBF00H to FFEFFH) |

| R5F104xH (x = E to G, J, L, M, P)         | 20480 × 8bits(FAF00H to FFEFFH) |

| R5F104xJ (x = F, G ,J , L, M, P)          | 24576 × 8bits(F9F00H to FFEFFH) |

| R5F104xK (x = G, J, L, M, P)              | 32768 × 8bits(F7F00H to FFEFFH) |

| R5F104xL (x = G, J, L, M, P)              | 49152 × 8bits(F3F00H to FFEFFH) |

(Omitted)

#### 3.1.1 Internal program memory space (page 138)

Correct:

#### Table 3 - 5 Internal ROM Capacity

| Part Number                               |              | Internal ROM                     |

|-------------------------------------------|--------------|----------------------------------|

| Fait Nulliber                             | Structure    | Capacity                         |

| R5F104xA (x = A to C, E to G)             | Flash memory | 16384 × 8bits(00000H to 03FFFH)  |

| R5F104xC (x = A to C, E to G, J, L)       |              | 32768 × 8bits(00000H to 07FFFH)  |

| R5F104xD (x = A to C, E to G, J, L)       |              | 49152 × 8bits(00000H to 0BFFFH)  |

| R5F104xE (x = A to C, E to G, J, L)       |              | 65536 × 8bits(00000H to 0FFFFH)  |

| R5F104xF (x = A to C, E to G, J, L, M, P) |              | 98304 × 8bits(00000H to 17FFFH)  |

| R5F104xG (x = A to C, E to G, J, L, M, P) |              | 131072 × 8bits(00000H to 1FFFFH) |

| R5F104xH (x = E to G, J, L, M, P)         |              | 196608 × 8bits(00000H to 2FFFH)  |

| R5F104xJ (x = F, G ,J , L, M, P)          |              | 262144 × 8bits(00000H to 3FFFFH) |

| R5F104xK (x = G, L, M, P)                 |              | 393216 × 8bits(00000H to 5FFFFH) |

| R5F104xL (x = G, L, M, P)                 |              | 524288 × 8bits(00000H to 7FFFFH) |

(Omitted)

#### 3.1.3 Internal data memory space (page 143)

Correct:

#### Table 3 - 8 Internal RAM Capacity

| Part Number                               | Internal RAM                    |

|-------------------------------------------|---------------------------------|

| R5F104xA (x = A to C, E to G)             | 2560 × 8bits(FF500H to FFEFFH)  |

| R5F104xC (x = A to C, E to G, J, L)       | 4096 × 8bits(FEF00H to FFEFFH)  |

| R5F104xD (x = A to C, E to G, J, L)       | 5632 × 8bits(FE900H to FFEFFH)  |

| R5F104xE (x = A to C, E to G, J, L)       |                                 |

| R5F104xF (x = A to C, E to G, J, L, M, P) | 12288 × 8bits(FCF00H to FFEFFH) |

| R5F104xG (x = A to C, E to G, J, L, M, P) | 16384 × 8bits(FBF00H to FFEFFH) |

| R5F104xH (x = E to G, J, L, M, P)         | 20480 × 8bits(FAF00H to FFEFFH) |

| R5F104xJ (x = F, G ,J , L, M, P)          | 24576 × 8bits(F9F00H to FFEFFH) |

| R5F104xK (x = G, L, M, P)                 | 32768 × 8bits(F7F00H to FFEFFH) |

| R5F104xL (x = G, L, M, P)                 | 49152 × 8bits(F3F00H to FFEFFH) |

(Omitted)

#### 3.2.1 Control registers (page 148)

Incorrect:

(Omitted)

Caution 4. The flash library uses RAM in self-programming and rewriting of the memory. The target products and start address of the RAM areas us flash library are shown below. R5F104xD (x = A to C, E to G, J, L): Start address FE900H R5F104xE (x = A to C, E to G, J, L): Start address FE900H R5F104xJ (x = F, G, J, L, M, P): Start address F9F00H R5F104xL (x = G, J, L, M, P): Start address F3F00H For the RAM areas used by the flash library, see Self RAM list Self-Programming Library for RL78 Family (R20UT2944). Caution 5. The internal RAM area in the following products cannot be used as stac when using the on-chip debugging trace function. R5F104xJ (x = A to C, E to G, J, L): FA300H to FA6FFH R5F104xL (x = G, J, L, M, P) F4300H to F46FFH

#### 4.3 Registers Controlling Port Function (page 193)

Incorrect:

(Omitted)

- Note 1. 30-pin and 32-pin products only.

- Note 2. R5F104xF (x = A to C, E to G, J, L, M, P), R5F104xG (x = A to C, E to G, J, L, M, P), R5F104xH (x = E to G, J, L, M,P), R5F104xJ (x = F, G, J, L, M, P), R5F104xK (x = G, J, L, M, P), R5F104xL (x = G, J, L, M, P) only.

Date: Dec. 3, 2014

#### 3.2.1 Control registers (page 148)

Correct:

|                             | (Omitted)                                                                                                                                                                                           |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e data flash<br>used by the | Caution 4. The flash library uses RAM in self-programming and rewriting of the data flash memory. The target products and start address of the RAM areas used by the flash library are shown below. |

|                             | R5F10 $4$ xD (x = A to C, E to G, J, L): Start address FE900H                                                                                                                                       |

|                             | R5F104xE (x = A to C, E to G, J, L): Start address FE900H                                                                                                                                           |

|                             | R5F104xJ (x = F, G, J, L, M, P): Start address F9F00H                                                                                                                                               |

|                             | R5F104xL (x = G, L, M, P): Start address F3F00H                                                                                                                                                     |

| st of Flash                 | For the RAM areas used by the flash library, see Self RAM list of Flash                                                                                                                             |

|                             | Self-Programming Library for RL78 Family (R20UT2944).                                                                                                                                               |

| ack memory                  | Caution 5. The internal RAM area in the following products cannot be used as stack memory                                                                                                           |

| -                           | when using the on-chip debugging trace function.                                                                                                                                                    |

|                             | R5F104xJ (x = A to C, E to G, J, L): FA300H to FA6FFH                                                                                                                                               |

|                             | R5F104xL (x = G, L, M, P): F4300H to F46FFH                                                                                                                                                         |

#### 4.3 Registers Controlling Port Function (page 193)

Correct:

(Omitted)

Note 1. 30-pin and 32-pin products only.

Note 2. R5F104xF (x = A to C, E to G, J, L, M, P), R5F104xG (x = A to C, E to G, J, L, M, P), R5F104xH (x = E to G, J, L, M,P), R5F104xJ (x = F, G, J, L, M, P), R5F104xK (x = G, L, M, P), R5F104xL (x = G, L, M, P) only.

#### 19.3.1 Allocation of DTC Control Data Area and DTC Vector Table Area (Page 958)

Incorrect:

(Omitted)

Caution 3. The internal RAM area in the following products cannot be used as the DTC control data area or DTC vector table area when using the self-programming and data-flash functions. R5F104xD (x = A to C, E to G, J, L): FE900H to FED09H R5F104xE (x = A to C, E to G, J, L): FE900H to FED09H R5F104xJ (x = A to C, E to G, J, L): F9F00H to FA309H R5F104xL (x = G, J, L, M, P): F3F00H to F4309H Caution 4. The internal RAM area in the following products cannot be used as the DTC control data area or DTC vector table area when using the on-chip debugging trace function. R5F104xJ (x = A to C, E to G, J, L): FA300H to FA6FFH R5F104xL (x = G, J, L, M, P): F4300H to F46FFH

#### 19.5.2 Allocation of DTC Control Data Area and DTC Vector Table Area (Page 981)

Incorrect:

#### (Omitted)

- The internal RAM area in the following products cannot be used as the DTC control data area or DTC vector table area when using the self-programming and data-flash functions.

- R5F104xD (x = A to C, E to G, J, L): R5F104xE (x = A to C, E to G, J, L): R5F104xJ (x = A to C, E to G, J, L): R5F104xL (x = G, J, L, M, P):

FE900H to FED09H F9F00H to FA309H F3F00H to F4309H

FE900H to FED09H

The internal RAM area in the following products cannot be used as the DTC control data area or DTC vector table area when using the on-chip debugging trace function.

R5F104xJ (x = A to C. E to G. J. L): FA300H to FA6FFH R5F104xL (x = G, J, L, M, P): F4300H to F46FFH

Initialize the DTRLD register to 00H even in normal mode when parity error resets are enabled (RPERDIS = 0) using the RAM parity error detection function.

Date: Dec. 3, 2014

#### 19.3.1 Allocation of DTC Control Data Area and DTC Vector Table Area (Page 958)

Correct:

(Omitted)

Caution 3. The internal RAM area in the following products cannot be used as the DTC control data area or DTC vector table area when using the self-programming and data-flash functions. R5F104xD (x = A to C, E to G, J, L): FE900H to FED09H

R5F104xE (x = A to C, E to G, J, L): FE900H to FED09H R5F104xJ (x = A to C, E to G, J, L): F9F00H to FA309H R5F104xL(x = G, L, M, P): F3F00H to F4309H

Caution 4. The internal RAM area in the following products cannot be used as the DTC control data area or DTC vector table area when using the on-chip debugging trace function.

R5F104xJ (x = A to C, E to G, J, L): FA300H to FA6FFH R5F104xL (x = G. L. M. P): F4300H to F46FFH

#### 19.5.2 Allocation of DTC Control Data Area and DTC Vector Table Area (Page 981)

Correct:

(Omitted)

The internal RAM area in the following products cannot be used as the DTC control data area or DTC vector table area when using the self-programming and data-flash functions.

R5F104xD (x = A to C, E to G, J, L): FE900H to FED09H R5F104xE (x = A to C, E to G, J, L): FE900H to FED09H R5F104xJ (x = A to C, E to G, J, L): F9F00H to FA309H R5F104xL (x = G, L, M, P): F3F00H to F4309H

The internal RAM area in the following products cannot be used as the DTC control data area or DTC vector table area when using the on-chip debugging trace function.

R5F104xJ (x = A to C. E to G. J. L): FA300H to FA6FFH F4300H to F46FFH

Initialize the DTRLD register to 00H even in normal mode when parity error resets are enabled (RPERDIS = 0) using the RAM parity error detection function.

R5F104xL(x = G, L, M, P):

#### 27.3.6 Invalid memory access detection function (Page 1086)

Incorrect:

#### 27.3.6 Invalid memory access detection function (Page 1086)

Correct:

(Omitted)

(Omitted)

Note The code flash memory, RAM, and lowest detection address of each product are as follows. Note The code flash memory, RAM, and lowest detection address of each product are as follows.

| 10110W5.                              |                                         |                                                |                                                                                                 | 10110W5.                              |                                         |                                      |                                                                                                 |

|---------------------------------------|-----------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------|

| Products                              | Code Flash Memory<br>(00000H to xxxxxH) | RAM<br>(zzzzzH to FFEFFH)                      | Lowest Detection<br>Address<br>(yyyyyH) when<br>Reading/Fetching<br>(Executing)<br>Instructions | Products                              | Code Flash Memory<br>(00000H to xxxxxH) | RAM<br>(zzzzzH to FFEFFH)            | Lowest Detection<br>Address<br>(yyyyyH) when<br>Reading/Fetching<br>(Executing)<br>Instructions |

| R5F104xA(x=A to C, E to G)            | 16384 × 8 bits<br>(00000H to 03FFFH)    | 2560 × _ <b>8_bit</b> _<br>(FF500H to FFEFFH)  | 10000H                                                                                          | R5F104xA(x=A to C, E to G)            | 16384 × 8 bits<br>(00000H to 03FFFH)    | 2560 × 8 bits<br>(FF500H to FFEFFH)  | 10000H                                                                                          |

| R5F104xC(x=A to C,E to G,J,L)         | 32768 × 8 bits<br>(00000H to 07FFFH)    | 4096 × <u>8 bit</u><br>(FEF00H to FFEFFH)      | 10000H                                                                                          | R5F104xC(x=A to C,E to G,J,L)         | 32768 × 8 bits<br>(00000H to 07FFFH)    | 4096 × 8 bits<br>(FEF00H to FFEFFH)  | 10000H                                                                                          |

| R5F104xD(x=A to C,E to G,J,L)         | 49152 × 8 bits<br>(00000H to 0BFFFH)    | 5632 × <u>8 bit</u><br>(FE900H to FFEFFH)      | 10000H                                                                                          | R5F104xD(x=A to C,E to G,J,L)         | 49152 × 8 bits<br>(00000H to 0BFFFH)    | 5632 × 8 bits<br>(FE900H to FFEFFH)  | 10000H                                                                                          |

| R5F104xE(x=A to C,E to G,J,L)         | 65536 × 8 bits<br>(00000H to 0FFFFH)    | 5632 × <u>8 bit</u><br>(FE900H to FFEFFH)      | 10000H                                                                                          | R5F104xE(x=A to C,E to G,J,L)         | 65536 × 8 bits<br>(00000H to 0FFFFH)    | 5632 × 8 bits<br>(FE900H to FFEFFH)  | 10000H                                                                                          |

| R5F104xF<br>(x=A to C,E to G,J,L,M,P) | 98304 × 8 bits<br>(00000H to 17FFFH)    | 12288 × <u>8 bit</u><br>(FCF00H to FFEFFH)     | 20000H                                                                                          | R5F104xF<br>(x=A to C,E to G,J,L,M,P) | 98304 × 8 bits<br>(00000H to 17FFFH)    | 12288 × 8 bits<br>(FCF00H to FFEFFH) | 20000H                                                                                          |

| R5F104xG<br>(x=A to C,E to G,J,L,M,P) | 131072 × 8 bits<br>(00000H to 1FFFFH)   | 16384 × _ <b>8 bit</b> _<br>(FBF00H to FFEFFH) | 20000H                                                                                          | R5F104xG<br>(x=A to C,E to G,J,L,M,P) | 131072 × 8 bits<br>(00000H to 1FFFFH)   | 16384 × 8 bits<br>(FBF00H to FFEFFH) | 20000H                                                                                          |

| R5F104xH(x=E to G,J,L,M,P)            | 196608 × 8 bits<br>(00000H to 2FFFFH)   | 20480 × _ <b>8 bit</b><br>(FAF00H to FFEFFH)   | 30000H                                                                                          | R5F104xH(x=E to G,J,L,M,P)            | 196608 × 8 bits<br>(00000H to 2FFFFH)   | 20480 × 8 bits<br>(FAF00H to FFEFFH) | 30000H                                                                                          |

| R5F104xJ(x=F,G,J,L,M,P)               | 262144 × 8 bits<br>(00000H to 3FFFFH)   | 24576 × _ <b>8 bit</b> _<br>(F9F00H to FFEFFH) | 40000H                                                                                          | R5F104xJ(x=F,G,J,L,M,P)               | 262144 × 8 bits<br>(00000H to 3FFFFH)   | 24576 × 8 bits<br>(F9F00H to FFEFFH) | 40000H                                                                                          |

| R5F104xK(x=G,J.L.M.P)                 | 393216 × 8 bits<br>(00000H to 5FFFFH)   | 32768 × <u>8 bit</u><br>(F7F00H to FFEFFH)     | 60000H                                                                                          | R5F104xK(x=G,L,M,P)                   | 393216 × 8 bits<br>(00000H to 5FFFFH)   | 32768 × 8 bits<br>(F7F00H to FFEFFH) | 60000H                                                                                          |

| R5F104xL(x=G.J.L.M.P)                 | 524688 × 8 bits<br>(00000H to 7FFFFH)   | 49152 × <u>8 bit</u><br>(F3F00H to FFEFFH)     | 80000H                                                                                          | R5F104xL(x=G,L,M,P)                   | 524688 × 8 bits<br>(00000H to 7FFFFH)   | 49152 × 8 bits<br>(F3F00H to FFEFFH) | 80000H                                                                                          |

#### 31.3 Securing of User Resources (Page 1134)

Incorrect:

(Omitted)

#### Note 1. Address differs depending on products as follows.

| Products (code flash memory capacity)     | Address of Note 1. |

|-------------------------------------------|--------------------|

| R5F104xA (x = A to C, E to G)             | 03FFFH             |

| R5F104xC (x = A to C, E to G, J, L)       | 07FFFH             |

| R5F104xD (x = A to C, E to G, J, L)       | 0BFFFH             |

| R5F104xE (x = A to C, E to G, J, L)       | 0FFFFH             |

| R5F104xF (x = A to C, E to G, J, L, M, P) | 17FFFH             |

| R5F104xG (x = A to C, E to G, J, L, M, P) | 1FFFFH             |

| R5F104xH (x = E to G, J, L, M, P)         | 2FFFFH             |

| R5F104xJ (x = F, G ,J , L, M, P)          | 3FFFFH             |

| R5F104xK(x = G, J, L, M, P)               | 5FFFH              |

| R5F104xL (x = G, J, L, M, P)              | 7FFFH              |

(Omitted)

#### 36.7 52-pin products (Page 1304)

#### Incorrect:

R5F104JCAFA, R5F104JDAFA, R5F104JEAFA, R5F104JFAFA, R5F104JGAFA, R5F104JHAFA, R5F104JJAFA R5F104JCDFA, R5F104JDDFA, R5F104JEDFA, R5F104JFDFA, R5F104JGDFA, R5F104JHDFA, R5F104JDGFA, R5F104JEGFA, R5F104JFGFA, R5F104JGGFA, R5F104JHGFA, R5F104JJGFA R5F104JHGFA, R5F104JJGFA **R5F104GKGNA, R5F104JLGFA R5F104JKGFA, R5F104JLGFA**

(Omitted)

#### Date: Dec. 3, 2014

#### 31.3 Securing of User Resources (Page 1134)

Correct:

#### (Omitted)

#### Note 1. Address differs depending on products as follows.

| <br>, danced amere depending on products do renow | 0.                 |

|---------------------------------------------------|--------------------|

| Products (code flash memory capacity)             | Address of Note 1. |

| R5F104xA (x = A to C, E to G)                     | 03FFFH             |

| R5F104xC (x = A to C, E to G, J, L)               | 07FFFH             |

| R5F104xD (x = A to C, E to G, J, L)               | 0BFFFH             |

| R5F104xE (x = A to C, E to G, J, L)               | 0FFFFH             |

| R5F104xF (x = A to C, E to G, J, L, M, P)         | 17FFFH             |

| R5F104xG (x = A to C, E to G, J, L, M, P)         | 1FFFFH             |

| R5F104xH (x = E to G, J, L, M, P)                 | 2FFFFH             |

| R5F104xJ (x = F, G ,J , L, M, P)                  | 3FFFFH             |

| R5F104xK (x = G, L, M, P)                         | 5FFFH              |

| R5F104xL (x = G, L, M, P)                         | 7FFFH              |

|                                                   |                    |

(Omitted)

#### 36.7 52-pin products (Page 1304)

Correct:

R5F104JCAFA, R5F104JDAFA, R5F104JEAFA, R5F104JFAFA, R5F104JGAFA, R5F104JHAFA, R5F104JJAFA R5F104JCDFA, R5F104JDDFA, R5F104JEDFA, R5F104JFDFA, R5F104JGDFA, R5F104JHDFA, R5F104JDGFA, R5F104JEGFA, R5F104JFGFA, R5F104JGGFA, R5F104JHGFA, R5F104JJGFA

#### 6. <u>6.3.3 Timer mode register mn (TMRmn)</u> Figure 6 - 12 the count clock selection (Page 303)

Incorrect:

Figure 6 - 12 Format of Timer mode register mn (TMRmn) (1/4)

Address: F0190H, F0191H (TMR00) to F0196H, F0197H (TMR03), After reset: 0000H R/W F01D0H, F01D1H (TMR10) to F01D6H, F01D7H (TMR13)

| Symbol         | 15  | 14  | 13 | 12  | 11    | 10  | 9   | 8   | 7   | 6   | 5 | 4 | 3   | 2   | 1   | 0   |

|----------------|-----|-----|----|-----|-------|-----|-----|-----|-----|-----|---|---|-----|-----|-----|-----|

| TMRmn<br>(n=2) | CKS | CKS | 0  | CCS | MAS   | STS | STS | STS | CIS | CIS | 0 | 0 | MD  | MD  | MD  | MD  |

| (n=2)          | mn1 | mn0 | 0  | mn  | TERmn | mn2 | mn1 | mn0 | mn1 | mn0 | 0 | U | mn3 | mn2 | mn1 | mn0 |

(Omitted)

| CCS<br>mn | Selection of count clock ( $f_{TCLK}$ ) of channel n                                          |

|-----------|-----------------------------------------------------------------------------------------------|

| 0         | Operation clock ( $f_{\mbox{\scriptsize MCK}}$ ) specified by the CKSmn0 and CKSmn1 bits      |

| 1         | Valid edge of input signal input from the TImn pin                                            |

| Cour      | nt clock ( $f_{TCLK}$ ) is used for the counter, output controller, and interrupt controller. |

(Omitted)

Date: Dec. 3, 2014

Correct:

Figure 6 - 12 Format of Timer mode register mn (TMRmn) (1/4)

## Address: F0190H, F0191H (TMR00) to F0196H, F0197H (TMR03), After reset: 0000H R/W F01D0H, F01D1H (TMR10) to F01D6H, F01D7H (TMR13)

| Symbol         | 15         | 14         | 13 | 12        | 11           | 10         | 9          | 8          | 7          | 6          | 5 | 4 | 3         | 2         | 1         | 0         |

|----------------|------------|------------|----|-----------|--------------|------------|------------|------------|------------|------------|---|---|-----------|-----------|-----------|-----------|

| TMRmn<br>(n=2) | CKS<br>mn1 | CKS<br>mn0 | 0  | CCS<br>mn | MAS<br>TERmn | STS<br>mn2 | STS<br>mn1 | STS<br>mn0 | CIS<br>mn1 | CIS<br>mn0 | 0 | 0 | MD<br>mn3 | MD<br>mn2 | MD<br>mn1 | MD<br>mn0 |

(Omitted)

| CCS<br>mn | Selection of count clock ( $f_{TCLK}$ ) of channel n                                                                                                                                                                                                           |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | Operation clock ( $f_{\mbox{\scriptsize MCK}}$ ) specified by the CKSmn0 and CKSmn1 bits                                                                                                                                                                       |

| 1         | Valid edge of input signal input from the TImn pin<br>When using unit 0:<br>In channel 0, Valid edge of input signal selected by TIS0<br>In channel 1, Valid edge of input signal selected by TIS0<br>In channel 3, Valid edge of input signal selected by ISC |