# **RENESAS TECHNICAL UPDATE**

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                       |            | Document<br>No.         | TN-RL*-A001A/E                                                               | Rev. | 1.00 |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------|------------|-------------------------|------------------------------------------------------------------------------|------|------|--|

| Title                 | Correction for Incorrect Description Notice<br>RL78/G13 Descriptions in the Hardware Use<br>Rev. 1.00 Changed | r's Manual | Information<br>Category | Technical Notification                                                       |      |      |  |

|                       |                                                                                                               | Lot No.    |                         | RL78/G13 User's Manual: Hardware<br>Rev. 1.00<br>R01UH0146EJ0100 (Sep. 2011) |      |      |  |

| Applicable<br>Product | RL78/G13 Group<br>R5F100xxx, R5F101xxx                                                                        | All lot    | Reference<br>Document   |                                                                              |      |      |  |

This document describes misstatements found in the RL78 hardware user's manual Rev. 1.00 (R01UH0146EJ0100).

#### **Corrections**

| Applicable Page   | Applicable Item                                                                                                                                         | Contents                          |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Pages 4, 17, 1055 | 64-pin plastic TQFP (7 x 7)                                                                                                                             | Incorrect descriptions<br>deleted |

| Pages 439 to 444  | Count registers in real-time clock                                                                                                                      | Incorrect descriptions<br>deleted |

| Page 460          | Interval timer control register (ITMC)                                                                                                                  | Explanations added                |

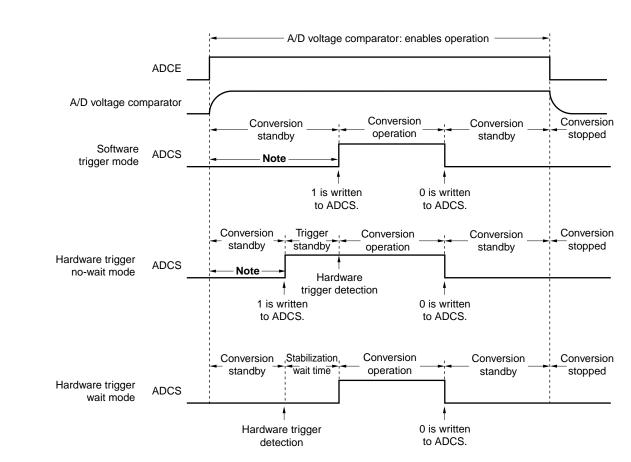

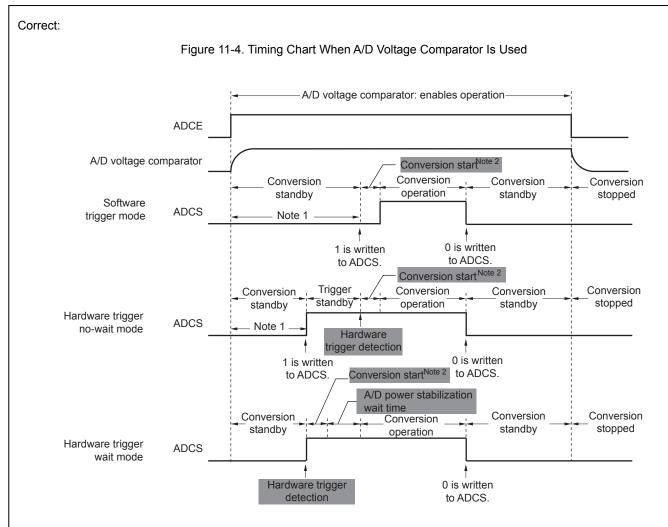

| Page 483          | Timing chart when A/D voltage comparator is used                                                                                                        | Explanations added                |

| Pages 489 to 491  | A/D conversion time selection, there is stabilization wait time (6/8) to (8/8)                                                                          | Incorrect descriptions<br>revised |

| Pages 493, 497    | Notes when entering A/D converter standby mode                                                                                                          | Explanations added                |

| Pages 842, 844    | Maskable interrupt request acknowledgment                                                                                                               | Incorrect descriptions<br>revised |

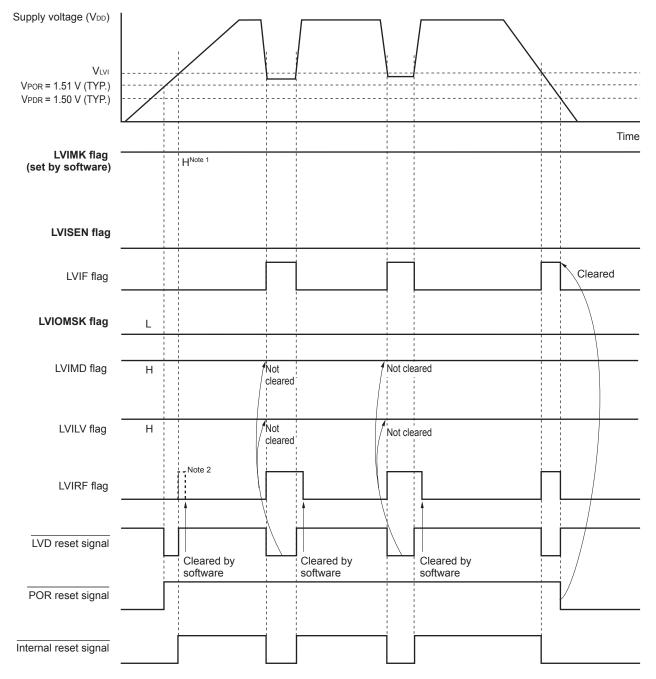

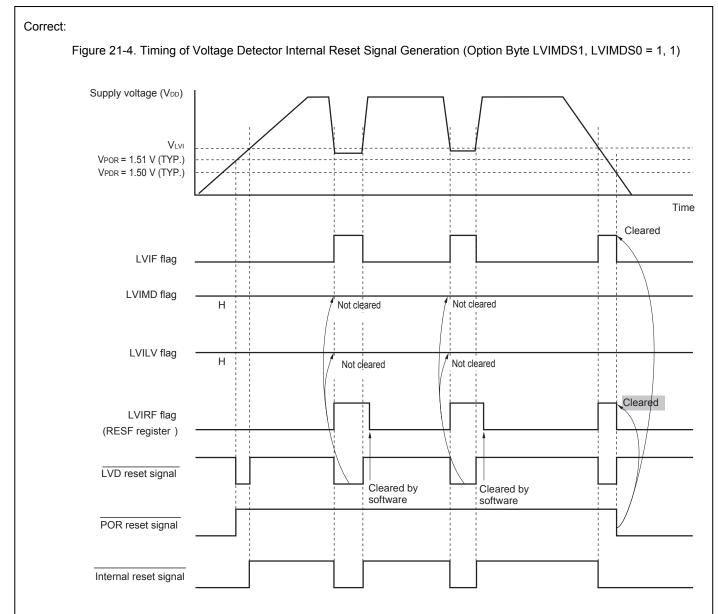

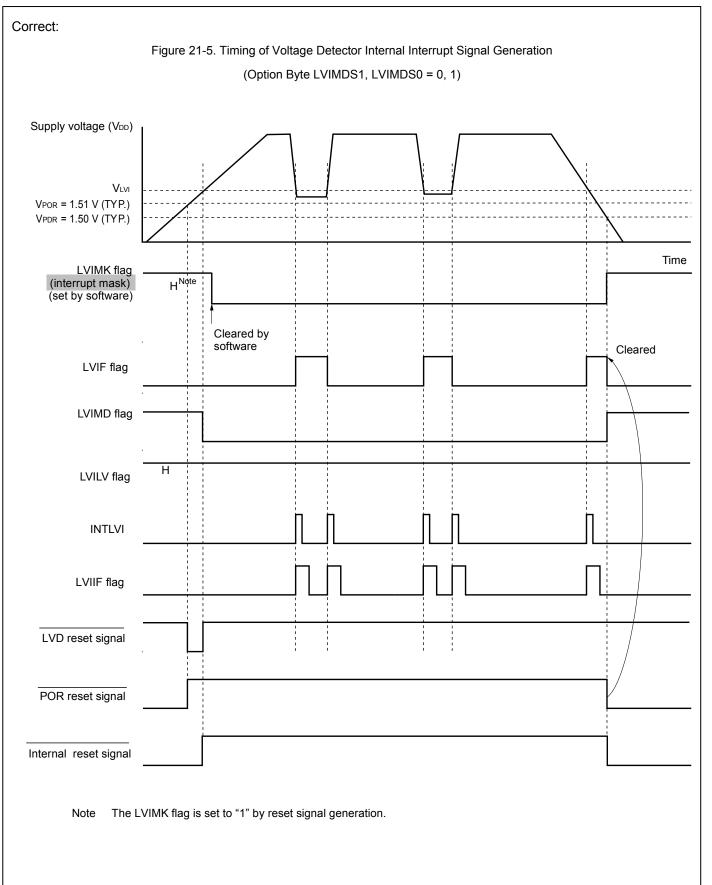

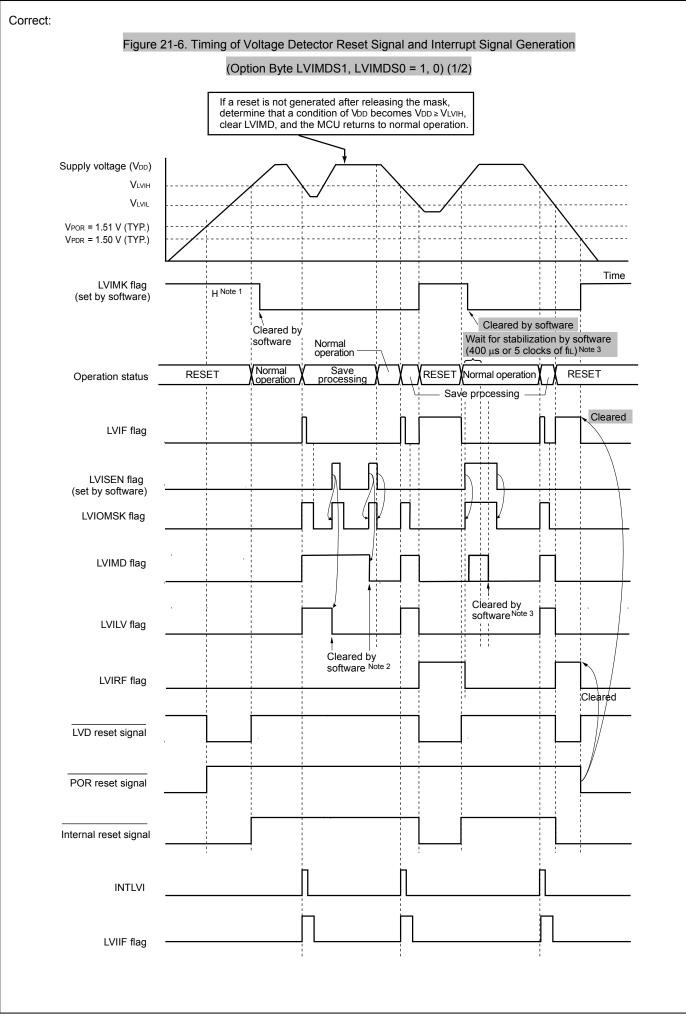

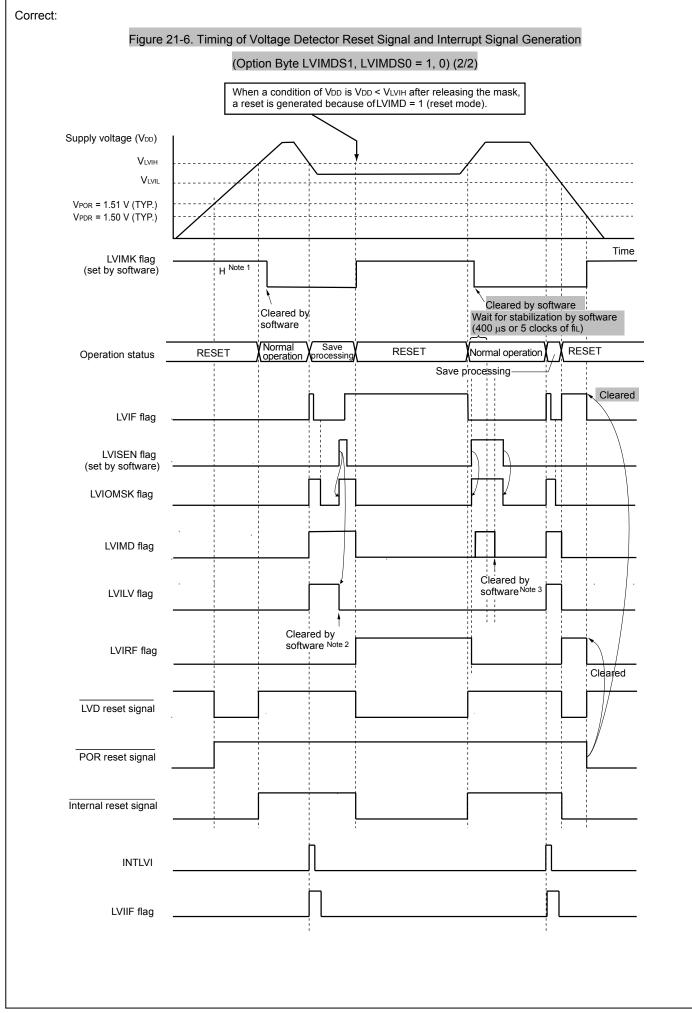

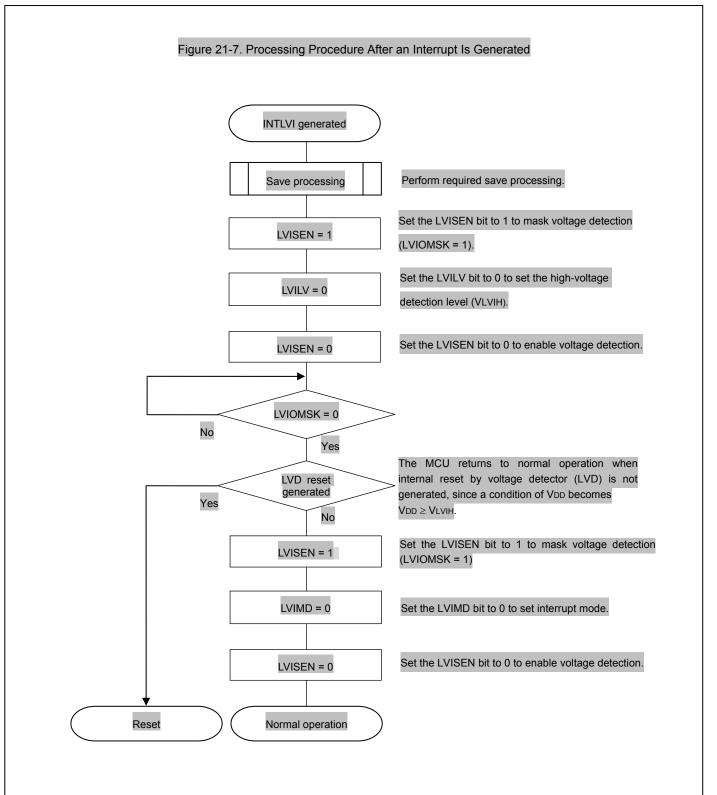

| Pages 894, 896    | Timing chart of voltage detector (LVD)                                                                                                                  | Incorrect descriptions<br>revised |

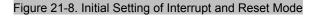

| Pages 897 to 899  | Voltage detector (LVD) interrupt and reset mode                                                                                                         | Incorrect descriptions<br>revised |

| Page 1005         | Number (4) of the supply current characteristics in the Electrical Specifications chapter (section 29.4.2) is the same for all RL78/G13 Group products. | Explanations added                |

Incorrect: Bold with underline; Correct: Gray hatched

#### Document Improvement

The above corrections will be made for the next revision of the hardware user's manual around February, 2012. Contact a Renesas Electronics sales department details on the publishing schedule.

#### Corrections in the hardware User's manual

|    | Applicable Iter                                                                                                                  | n                       | Rev 1.00        | After Rev 2.00 <sup>Note</sup> |  |  |  |

|----|----------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|--------------------------------|--|--|--|

| No | Document No.                                                                                                                     | Japanese                | R01UH0146JJ0100 | R01UH0146JJ0200                |  |  |  |

|    | Document No.                                                                                                                     | English                 | R01UH0146EJ0100 | R01UH0146EJ0200                |  |  |  |

| 1  | Incorrect descriptions of 64-<br>TQFP (7 x 7) deleted                                                                            | oin plastic             | _               | $\checkmark$                   |  |  |  |

| 2  | Incorrect descriptions of cou<br>real-time clock deleted                                                                         | nt registers, in        | _               | $\checkmark$                   |  |  |  |

| 3  | Explanations of interval time<br>register (ITMC) added                                                                           | r control               | _               | $\checkmark$                   |  |  |  |

| 4  | Explanations of timing chart<br>voltage comparator is used a                                                                     |                         | _               | $\checkmark$                   |  |  |  |

| 5  | Incorrect descriptions of A/D time selection, there is stabil time (6/8) to (8/8) revised                                        |                         | - v             |                                |  |  |  |

| 6  | Explanations when entering<br>standby mode added                                                                                 | A/D converter           | _               | $\checkmark$                   |  |  |  |

| 7  | Incorrect descriptions of mas<br>request acknowledgment op                                                                       |                         | _               | $\checkmark$                   |  |  |  |

| 8  | Incorrect descriptions of volta<br>(LVD) timing chart revised                                                                    | age detector            | _               | $\checkmark$                   |  |  |  |

| 9  | Incorrect descriptions of volta<br>(LVD) interrupt and reset mo                                                                  |                         | _               |                                |  |  |  |

| 10 | Number (4) of the supply cur<br>characteristics in the Electric<br>Specifications chapter (section<br>same for all RL78/G13 Grou | al<br>on 29.4.2) is the | _               | $\checkmark$                   |  |  |  |

Note A revised hardware user's manual is scheduled to be released around February, 2012.

Remarks  $\sqrt{\cdot}$ : Corrected

-: Items should be corrected

# 1. <u>Descriptions of related information according to discontinued development of 64-pin plastic</u> <u>TQFP (7 x 7) package deleted</u>

## Order information of 64-pin plastic TQFP (7 x 7) deleted (page 4)

Incorrect:

(2/3)

| Pin count | Package                          | Data flash | Part Number                                         |  |  |  |  |  |  |

|-----------|----------------------------------|------------|-----------------------------------------------------|--|--|--|--|--|--|

|           |                                  |            | (Omitted)                                           |  |  |  |  |  |  |

|           |                                  |            | R5F100LCAFA, R5F100LDAFA, R5F100LEAFA, R5F100LFAFA, |  |  |  |  |  |  |

|           |                                  | Mounted    | R5F100LGAFA, R5F100LHAFA, R5F100LJAFA, R5F100LKAFA, |  |  |  |  |  |  |

|           | 64-pin plastic LQFP (12x12)      |            | R5F100LLAFA                                         |  |  |  |  |  |  |

|           | 04-pill plastic LQFF (12x12)     | Not        | R5F101LCAFA, R5F101LDAFA, R5F101LEAFA, R5F101LFAFA  |  |  |  |  |  |  |

|           |                                  | mounted    | R5F101LGAFA, R5F101LHAFA, R5F101LJAFA, R5F101LKAFA  |  |  |  |  |  |  |

|           |                                  | mounteu    | R5F101LLAFA                                         |  |  |  |  |  |  |

|           |                                  |            | R5F100LCAFB, R5F100LDAFB, R5F100LEAFB, R5F100LFAFB  |  |  |  |  |  |  |

|           |                                  | Mounted    | R5F100LGAFB, R5F100LHAFB, R5F100LJAFB, R5F100LKAFB  |  |  |  |  |  |  |

|           | 64-pin plastic LQFP (fine pitch) |            | R5F100LLAFB                                         |  |  |  |  |  |  |

| 64 pins   | (10 × 10)                        | Not        | R5F101LCAFB, R5F101LDAFB, R5F101LEAFB, R5F101LFAFB  |  |  |  |  |  |  |

| 04 pins   |                                  | mounted    | R5F101LGAFB, R5F101LHAFB, R5F101LJAFB, R5F101LKAFB  |  |  |  |  |  |  |

|           |                                  | mounted    | R5F101LLAFB                                         |  |  |  |  |  |  |

|           |                                  | Mounted    | R5F100LCAFC, R5F100LDAFC, R5F100LEAFC, R5F100LFAFC  |  |  |  |  |  |  |

|           | 64-pin plastic TQFP              | Mounted    | R5F100LGAFC, R5F100LHAFC, R5F100LJAFC               |  |  |  |  |  |  |

|           | (fine_pitch) (7 × 7)             | Not        | R5F101LCAFC, R5F101LDAFC, R5F101LEAFC, R5F101LFAFC  |  |  |  |  |  |  |

|           |                                  | mounted    | R5F101LGAFC, R5F101LHAFC, R5F101LJAFC               |  |  |  |  |  |  |

|           |                                  | Mounted    | R5F100LCABG, R5F100LDABG, R5F100LEABG, R5F100LFABG  |  |  |  |  |  |  |

|           |                                  | Mounted    | R5F100LGABG, R5F100LHABG, R5F100LJABG               |  |  |  |  |  |  |

|           | 64-pin plastic FBGA (4 × 4)      | Not        | R5F101LCABG, R5F101LDABG, R5F101LEABG, R5F101LFABG  |  |  |  |  |  |  |

|           |                                  | mounted    | R5F101LGABG, R5F101LHABG, R5F101LJABG               |  |  |  |  |  |  |

| ct:       |                                  |                | (2                                                                                                                        |

|-----------|----------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------|

| Pin count | Package                          | Data flash     | Part Number                                                                                                               |

|           |                                  |                | (Omitted)                                                                                                                 |

|           | 64 pip plastic LOED (12:42)      | Mounted        | R5F100LCAFA, R5F100LDAFA, R5F100LEAFA, R5F100LFAFA,<br>R5F100LGAFA, R5F100LHAFA, R5F100LJAFA, R5F100LKAFA,<br>R5F100LLAFA |

|           | 64-pin plastic LQFP (12x12)      | Not<br>mounted | R5F101LCAFA, R5F101LDAFA, R5F101LEAFA, R5F101LFAFA,<br>R5F101LGAFA, R5F101LHAFA, R5F101LJAFA, R5F101LKAFA,<br>R5F101LLAFA |

| 64 pins   | 64-pin plastic LQFP (fine pitch) | Mounted        | R5F100LCAFB, R5F100LDAFB, R5F100LEAFB, R5F100LFAFB,<br>R5F100LGAFB, R5F100LHAFB, R5F100LJAFB, R5F100LKAFB,<br>R5F100LLAFB |

|           | (10 × 10)                        | Not<br>mounted | R5F101LCAFB, R5F101LDAFB, R5F101LEAFB, R5F101LFAFB,<br>R5F101LGAFB, R5F101LHAFB, R5F101LJAFB, R5F101LKAFB,<br>R5F101LLAFB |

|           |                                  | Mounted        | R5F100LCABG, R5F100LDABG, R5F100LEABG, R5F100LFABG<br>R5F100LGABG, R5F100LHABG, R5F100LJABG                               |

|           | 64-pin plastic FBGA (4 × 4)      | Not<br>mounted | R5F101LCABG, R5F101LDABG, R5F101LEABG, R5F101LFABG<br>R5F101LGABG, R5F101LHABG, R5F101LJABG                               |

#### Pin configuration of 64-pin plastic TQFP (7 x 7) deleted (page 17)

Incorrect:

1.3.11 64-pin products

• 64-pin plastic LQFP (12 × 12)

• 64-pin plastic LQFP (fine pitch) (10 × 10)

• 64-pin plastic TQFP (fine pitch) (7  $\times$  7)

(Omitted)

Correct:

- 1.3.11 64-pin products

- 64-pin plastic LQFP (12 × 12)

- 64-pin plastic LQFP (fine pitch) (10 × 10)

(Omitted)

## Package drawings of 64-pin plastic TQFP (7 x 7) deleted (page 1055)

Incorrect:

R5F100LCAFC, R5F100LDAFC, R5F100LEAFC, R5F100LFAFC, R5F100LGAFC, R5F100LHAFC, R5F100LJAFC R5F101LCAFC, R5F101LDAFC, R5F101LEAFC, R5F101LFAFC, R5F101LGAFC, R5F101LHAFC, R5F101LJAFC

64-PIN PLASTIC TQFP (7x7)

Under development

Correct: Applicable page deleted

#### 2. Incorrect descriptions of count registers in real-time clock deleted

#### Incorrect description of second count register (SEC) in real-time clock deleted (page 439)

Incorrect:

(5) Second count register (SEC)

The SEC register is an 8-bit register that takes a value of 0 to 59 (decimal) and indicates the count value of seconds.

It counts up when the sub-count register overflows.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (fRTC) later. Set a decimal value of 00 to 59 to this register in BCD code. If a value outside the range is set, the register value returns to the normal value after 1 period.

The SEC register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

Correct:

(5) Second count register (SEC)

The SEC register is an 8-bit register that takes a value of 0 to 59 (decimal) and indicates the count value of seconds. It counts up when the sub-count register overflows. When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (fRTC) later. Set a decimal value of 00 to 59 to this register in BCD code.

The SEC register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

#### Incorrect description of minute count register (MIN) in real-time clock deleted (page 439)

Incorrect:

(6) Minute count register (MIN)

The MIN register is an 8-bit register that takes a value of 0 to 59 (decimal) and indicates the count value of minutes. It counts up when the second counter overflows.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (frc) later. Even if the second count register overflows while this register is being written, this register ignores the overflow and is set to the value written. Set a decimal value of 00 to 59 to this register in BCD code. **If a value outside the range is set, the register value**

### returns to the normal value after 1 period.

The MIN register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

#### Correct:

(6) Minute count register (MIN)

The MIN register is an 8-bit register that takes a value of 0 to 59 (decimal) and indicates the count value of minutes.

It counts up when the second counter overflows.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (frc) later. Even if the second count register overflows while this register is being written, this register ignores the overflow and is set to the value written. Set a decimal value of 00 to 59 to this register in BCD code.

The MIN register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

#### Incorrect description of hour count register (HOUR) in real-time clock deleted (page 440)

Incorrect:

(7) Hour count register (HOUR)

The HOUR register is an 8-bit register that takes a value of 00 to 23 or 01 to 12 and 21 to 32 (decimal) and indicates the count value of hours.

It counts up when the minute counter overflows.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (f<sub>RTC</sub>) later. Even if the minute count register overflows while this register is being written, this register ignores the overflow and is set to the value written. Specify a decimal value of 00 to 23, 01 to 12, or 21 to 32 by using BCD code according to the time system specified using bit 3 (AMPM) of real-time clock control register 0 (RTCC0). If the AMPM bit value is changed, the values of the HOUR register change according to the specified time system. **If a value outside the range is set, the register value returns to**

#### the normal value after 1 period.

The HOUR register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 12H.

However, the value of this register is 00H if the AMPM bit (bit 3 of the RTCC0 register) is set to 1 after reset.

#### Correct:

(7) Hour count register (HOUR)

The HOUR register is an 8-bit register that takes a value of 00 to 23 or 01 to 12 and 21 to 32 (decimal) and indicates the count value of hours.

It counts up when the minute counter overflows.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (frc) later. Even if the minute count register overflows while this register is being written, this register ignores the overflow and is set to the value written. Specify a decimal value of 00 to 23, 01 to 12, or 21 to 32 by using BCD code according to the time system specified using bit 3 (AMPM) of real-time clock control register 0 (RTCC0). If the AMPM bit value is changed, the values of the HOUR register change according to the specified time system.

The HOUR register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 12H.

However, the value of this register is 00H if the AMPM bit (bit 3 of the RTCC0 register) is set to 1 after reset.

#### Incorrect description of day count register (DAY) in real-time clock deleted (page 442)

Incorrect:

(8) Day count register (DAY)

The DAY register is an 8-bit register that takes a value of 1 to 31 (decimal) and indicates the count value of days. It counts up when the hour counter overflows.

This counter counts as follows.

#### (Omitted)

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (frc) later. Even if the hour count register overflows while this register is being written, this register ignores the overflow and is set to the value written. Set a decimal value of 01 to 31 to this register in BCD code. If a value outside the range is set, the register value

#### returns to the normal value after 1 period.

The DAY register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 01H.

#### Correct:

#### (8) Day count register (DAY)

The DAY register is an 8-bit register that takes a value of 1 to 31 (decimal) and indicates the count value of days. It counts up when the hour counter overflows.

This counter counts as follows.

#### (Omitted)

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (fRTC) later. Even if the hour count register overflows while this register is being written, this register ignores the overflow and is set to the value written. Set a decimal value of 01 to 31 to this register in BCD code.

The DAY register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 01H.

#### Incorrect description of week count register (WEEK) in real-time clock deleted (page 443)

Incorrect:

(9) Week count register (WEEK)

The WEEK register is an 8-bit register that takes a value of 0 to 6 (decimal) and indicates the count value of weekdays. It counts up in synchronization with the day counter.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (frtc) later. Set a decimal

value of 00 to 06 to this register in BCD code. If a value outside the range is set, the register value returns to the

#### normal value after 1 period.

The WEEK register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

#### Correct:

(9) Week count register (WEEK)

The WEEK register is an 8-bit register that takes a value of 0 to 6 (decimal) and indicates the count value of weekdays.

It counts up in synchronization with the day counter.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (fRTC) later. Set a decimal value of 00 to 06 to this register in BCD code.

The WEEK register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

#### Incorrect description of month count register (MONTH) in real-time clock deleted (page 444)

Incorrect:

(10) Month count register (MONTH)

The MONTH register is an 8-bit register that takes a value of 1 to 12 (decimal) and indicates the count value of months. It counts up when the day counter overflows.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (fRTC) later. Even if the day count register overflows while this register is being written, this register ignores the overflow and is set to the value written. Set a decimal value of 01 to 12 to this register in BCD code. **If a value outside the range is set, the register**.

#### value returns to the normal value after 1 period.

The MONTH register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 01H.

#### Correct:

(10) Month count register (MONTH)

The MONTH register is an 8-bit register that takes a value of 1 to 12 (decimal) and indicates the count value of months. It counts up when the day counter overflows.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (frc) later. Even if the day count register overflows while this register is being written, this register ignores the overflow and is set to the value written. Set a decimal value of 01 to 12 to this register in BCD code.

The MONTH register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 01H.

#### Incorrect description of year count register (YEAR) in real-time clock deleted (page 444)

Incorrect:

(11) Year count register (YEAR)

The YEAR register is an 8-bit register that takes a value of 0 to 99 (decimal) and indicates the count value of years. It counts up when the month count register (MONTH) overflows.

Values 00, 04, 08, ..., 92, and 96 indicate a leap year.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (frc) later. Even if the MONTH register overflows while this register is being written, this register ignores the overflow and is set to the value written. Set a decimal value of 00 to 99 to this register in BCD code. If a value outside the range is set, the register value returns to the normal value after 1 period.

The YEAR register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

Correct:

(11) Year count register (YEAR)

The YEAR register is an 8-bit register that takes a value of 0 to 99 (decimal) and indicates the count value of years. It counts up when the month count register (MONTH) overflows.

Values 00, 04, 08, ..., 92, and 96 indicate a leap year.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (frtc) later. Even if the

MONTH register overflows while this register is being written, this register ignores the overflow and is set to the value written. Set a decimal value of 00 to 99 to this register in BCD code.

The YEAR register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

#### 3. Caution of interval timer control register (ITMC) in 12-bit interval timer added (page 460)

Incorrect:

(3) Interval timer control register (ITMC)

#### (Omitted)

Cautions 1. Before changing the RINTE bit from 1 to 0, use the interrupt mask flag register to disable the INTIT interrupt servicing. When the operation starts (from 0 to 1) again, clear the ITIF flag, and then enable the interrupt servicing.

- 2. The value read from the RINTE bit is applied one count clock cycle after setting the RINTE bit.

- 3. Only change the setting of the ITCMP11 to ITCMP0 bits when RINTE = 0. However, it is possible to change the settings of the ITCMP11 to ITCMP0 bits at the same time as when changing RINTE from 0 to 1 or 1 to 0.

Correct:

(3) Interval timer control register (ITMC)

#### (Omitted)

- Cautions 1. Before changing the RINTE bit from 1 to 0, use the interrupt mask flag register to disable the INTIT interrupt servicing. When the operation starts (from 0 to 1) again, clear the ITIF flag, and then enable the interrupt servicing.

- 2. The value read from the RINTE bit is applied one count clock cycle after setting the RINTE bit.

- 3. When setting the RINTE bit after returned from standby mode and entering standby mode again, confirm that the written value of the RINTE bit is reflected, or wait that more than one clock of the count clock has elapsed after returned from standby mode. Then enter standby mode.

- 4. Only change the setting of the ITCMP11 to ITCMP0 bits when RINTE = 0. However, it is possible to change the settings of the ITCMP11 to ITCMP0 bits at the same time as when changing RINTE from 0 to 1 or 1 to 0.

#### 4. Added Explanations of timing chart when A/D voltage comparator is used (page 483)

```

Incorrect:

```

Figure 11-4. Timing Chart When A/D Voltage Comparator Is Used

Note (Omitted)

Note 1. (Omitted)

#### 2. The following time is the maximum amount of time necessary to start conversion.

|     | ADMC | )   | Conversion                  | Conversion Start Time                                   | (Number of fclk Clocks)    |

|-----|------|-----|-----------------------------|---------------------------------------------------------|----------------------------|

| FR2 | FR1  | FR0 | Clock<br>(f <sub>AD</sub> ) | Software trigger mode/<br>Hardware trigger no wait mode | Hardware trigger wait mode |

| 0   | 0    | 0   | fськ/ <b>64</b>             | 63                                                      |                            |

| 0   | 0    | 1   | fclк/ <b>32</b>             | 31                                                      |                            |

| 0   | 1    | 0   | fclк/16                     | 15                                                      |                            |

| 0   | 1    | 1   | fськ/8                      | 7                                                       |                            |

| 1   | 0    | 0   | fськ/6                      | 5                                                       | 1                          |

| 1   | 0    | 1   | fclк/5                      | 4                                                       |                            |

| 1   | 1    | 0   | fськ/4                      | 3                                                       |                            |

| 1   | 1    | 1   | fськ/2                      | 1                                                       |                            |

Remark fclk: CPU/peripheral hardware clock frequency

# 5. <u>Incorrect descriptions of Table 11-3 A/D Conversion Time Selection (6/8) to (8/8) when there</u> is stabilization wait time (pages 489 to 491)

Incorrect:

#### Table 11-3. A/D Conversion Time Selection (6/8)

#### (6) 2.7 V $\leq$ VDD < 3.6 V

#### When there is stabilization wait time (hardware trigger wait mode)

| A/D | Convert | er Mode<br>ADM0) | e Registe | er O |         |                       | Сс            | onversion Ti          | me Selectic        | n                     |                       | (fAD)                     |

|-----|---------|------------------|-----------|------|---------|-----------------------|---------------|-----------------------|--------------------|-----------------------|-----------------------|---------------------------|

| FR2 | FR1     | FR0              | LV1       | LV0  | Mode    | fclk =                | fclk =        | fclk =                | fclk =             | fclk =                | fclk =                | Conversion<br>Clock (fAD) |

|     |         |                  |           |      |         | 1 MHz                 | 2 MHz         | 4 MHz                 | 8 MHz              | 16 MHz                | 32 MHz                | 0 0                       |

| 0   | 0       | 0                |           |      |         |                       |               | Setting               | Setting            | Setting<br>prohibited | 54 μs                 | fclк/64                   |

| 0   | 0       | 1                |           |      |         |                       |               | prohibited            | prohibited         | 54 μs                 | 27 μs                 | fclк/32                   |

| 0   | 1       | 0                |           |      |         | Setting               | Setting       |                       | 54 μs              | 27 μs                 | 13.5 μ <b>s</b>       | fclк/16                   |

| 0   | 1       | 1                | _         | 0    | Normal  | prohibited            | prohibited    | 54 μs                 | 27 μs              | 13.5 μs               | 6.75 μs               | fclк/8                    |

| 1   | 0       | 0                | 0         | 0    | 1       | 40.5                  | 40.5 μs       | 20.25 μs              | 10.125 μs          | 5.0625 μs             | fclк/6                |                           |

| 1   | 0       | 1                |           |      |         |                       |               | 33.75 μ <b>s</b>      | 16.875 μs          | 8.4375 μs             |                       | fclк/5                    |

| 1   | 1       | 0                |           |      |         |                       | 54 μs         | 27 μs                 | 13.5 μs            | 6.75 μs               | Setting               | fclк/4                    |

| 1   | 1       | 1                |           |      |         | 54 μs                 | 27 μs         | 13.5 μs               | 6.75 μs            | Setting<br>prohibited | prohibited            | fclк/2                    |

| 0   | 0       | 0                |           |      |         |                       |               |                       | Setting            | Setting<br>prohibited | 50 μs                 | fclк/64                   |

| 0   | 0       | 1                |           |      |         |                       |               | Setting               | prohibited         | prombiled<br>50 μs    | 25 μs                 | fclк/32                   |

| 0   | 1       | 0                |           |      |         | 0                     | Setting       | prohibited            | 50 μs              | 25 μs                 | 12.5 μs               | fclк/16                   |

| 0   | 1       | 1                |           |      | Normal  | Setting<br>prohibited | prohibited    | 50 µs                 | 25 μs              | 12.5 μs               | 6.25 μs               | fclк/8                    |

| 1   | 0       | 0                | 0         | 1    | 2       | profilbited           |               | 37.5 μs               | 18.75 μs           | 9.375 μs              | 4.6875 <i>μ</i> s     | fськ/6                    |

| 1   | 0       | 1                |           |      |         |                       |               | 31.25 μs              | 15.625 μs          | 7.8125 μs             |                       | fclк/5                    |

| 1   | 1       | 0                |           |      |         |                       | 50 μs         | 25 μs                 | 12.5 μs            | 6.25 μs               | Setting               | fськ/4                    |

| 1   | 1       | 1                |           |      |         | 50 μs                 | 25 μs         | 12.5 μs               | 6.25 μs            | Setting<br>prohibited | prohibited            | fськ/2                    |

| 0   | 0       | 0                |           |      |         |                       |               | Setting               | Setting            | Setting<br>prohibited | <u>54</u> _μs         | fc∟к/64                   |

| 0   | 0       | 1                |           |      |         |                       |               | prohibited            | prohibited         | 54_μs                 | 27_µs                 | fclк/32                   |

| 0   | 1       | 0                |           |      |         | Setting               | Setting       | 54                    | <u>54</u> μs       | <u>27</u> _μs         |                       | fclк/16                   |

| 0   | 1       | 1                | 1         | 0    | Low-    | prohibited            | prohibited    | <u>54</u> μs          | <u>27</u> _μs      |                       |                       | fclк/8                    |

| 1   | 0       | 0                |           | 0    | Voltage |                       |               | <u>40.5</u> μs        |                    |                       | 0.111                 | fclк/6                    |

| 1   | 0       | 1                |           |      | 1       |                       |               | <u>33.75</u> .μs      | Setting            | Setting               | Setting<br>prohibited | fс∟к/5                    |

| 1   | 1       | 0                |           |      |         |                       | <u>54</u> _μs | 27_µs                 | prohibited         | prohibited            |                       | fclк/4                    |

| 1   | 1       | 1                |           |      |         | 54.µs                 | 27_µs         | Setting prohibited    |                    |                       |                       | fclк/2                    |

| 0   | 0       | 0                |           |      |         |                       |               | Setting               | Setting            | Setting<br>prohibited | <u>50</u> _μs         | fclк/64                   |

| 0   | 0       | 1                | 1         |      |         |                       |               | prohibited            | prohibited         | <u>50</u> μs          | <u>25</u> μs          | fclк/32                   |

| 0   | 1       | 0                |           |      |         | Cotting               | Setting       |                       | <u>50</u> μs       | <u>25</u> μs          |                       | fclк/16                   |

| 0   | 1       | 1                | 4         | 1 1  | Low-    | Setting<br>prohibited | prohibited    | <u>50</u> μs          | <u>25</u> μs       |                       | 1                     | fськ/8                    |

| 1   | 0       | 0                |           |      | Voltage |                       |               | <u>37.5</u> μs        |                    |                       |                       | fclк/6                    |

| 1   | 0       | 1                |           | 2    |         |                       | 31.25 μs      |                       | Setting            | Setting prohibited    | fclĸ/5                |                           |

| 1   | 1       | 0                |           |      |         |                       | <u>50</u> μs  | <u>25</u> μs          | Setting prohibited | prohibited            | Promoted              | fськ/4                    |

| 1   | 1       | 1                |           |      |         | 50 μs                 | 25 µs         | Setting<br>prohibited |                    |                       |                       | fськ/ <b>2</b>            |

Incorrect:

#### Table 11-3. A/D Conversion Time Selection (7/8)

#### (7) 1.8 V $\leq$ VDD < 2.7 V

#### When there is stabilization wait time (hardware trigger wait mode)

| A/E | D Conver | rter Mode<br>(ADM0) | -   | er O |           |                 | C               | onversion T           | ime Selectio       | on                                    |                  | sion<br>(AD)              |  |        |

|-----|----------|---------------------|-----|------|-----------|-----------------|-----------------|-----------------------|--------------------|---------------------------------------|------------------|---------------------------|--|--------|

| FR2 | FR1      | FR0                 | LV1 | LV0  | Mode      | fclk =<br>1 MHz | fclk =<br>2 MHz | fclk =<br>4 MHz       | fclk =<br>8 MHz    | fclk =<br>16 MHz<br><sub>(Note)</sub> | fclk =<br>32 MHz | Conversion<br>Clock (fAD) |  |        |

| 0   | 0        | 0                   |     |      |           |                 |                 |                       |                    |                                       |                  | fclк/64                   |  |        |

| 0   | 0        | 1                   |     |      |           |                 |                 |                       |                    |                                       |                  | fclк/32                   |  |        |

| 0   | 1        | 0                   |     |      |           |                 |                 |                       |                    |                                       |                  | fcьк/16                   |  |        |

| 0   | 1        | 1                   |     | 0    | Normal    | Setting         | Setting         | Setting               | Setting            | Setting                               | Setting          | fclк/8                    |  |        |

| 1   | 0        | 0                   | 0   | 0    | 1         | prohibited      | prohibited      | prohibited            | prohibited         | prohibited                            | prohibited       | fськ/6                    |  |        |

| 1   | 0        | 1                   |     |      |           |                 |                 |                       |                    |                                       |                  | fськ/5                    |  |        |

| 1   | 1        | 0                   |     |      |           |                 |                 |                       |                    |                                       |                  |                           |  | fськ/4 |

| 1   | 1        | 1                   |     |      |           |                 |                 |                       |                    |                                       |                  | fclк/2                    |  |        |

| 0   | 0        | 0                   |     |      |           | Setting         | Setting         | Setting               | Setting            | Setting                               | Setting          | fclк/64                   |  |        |

| 0   | 0        | 1                   |     |      |           | prohibited      | prohibited      | prohibited            | prohibited         | prohibited                            | prohibited       | fclк/32                   |  |        |

| 0   | 1        | 0                   |     |      |           |                 |                 |                       |                    |                                       |                  | fclк/16                   |  |        |

| 0   | 1        | 1                   |     |      | Normal    |                 |                 |                       |                    |                                       |                  | fclк/8                    |  |        |

| 1   | 0        | 0                   | 0   | 1    | 2         |                 |                 |                       |                    |                                       |                  | fclк/6                    |  |        |

| 1   | 0        | 1                   |     |      |           |                 |                 |                       |                    |                                       |                  | fclk/5                    |  |        |

| 1   | 1        | 0                   |     |      |           |                 |                 |                       |                    |                                       |                  | fськ/4                    |  |        |

| 1   | 1        | 1                   |     |      |           |                 |                 |                       |                    |                                       |                  | fclк/2                    |  |        |

| 0   | 0        | 0                   |     |      |           |                 |                 | Setting               | Setting            | Setting<br>prohibited                 | <u>54</u> .μs    | fclк/64                   |  |        |

| 0   | 0        | 1                   |     |      |           |                 |                 | prohibited            | prohibited         | <u>54</u> μs                          | <u>27</u> _μs    | fclк/32                   |  |        |

| 0   | 1        | 0                   |     |      |           | Setting         | Setting         |                       | 54 µs              | 27.µs                                 |                  | fcьк/16                   |  |        |

| 0   | 1        | 1                   | 1   | 0    | Low-      | prohibited      | prohibited      | 54 μs                 | <u>27 µs</u>       |                                       |                  | fclк/8                    |  |        |

| 1   | 0        | 0                   |     | 0    | Voltage 1 |                 |                 | 40.5 μs               |                    |                                       | Setting          | fськ/6                    |  |        |

| 1   | 0        | 1                   |     |      |           |                 |                 | <u>33.75</u> μs       | Setting            | Setting                               | prohibited       | fс∟к/5                    |  |        |

| 1   | 1        | 0                   |     |      |           |                 | <u>54</u> μs    | <u>27.</u> µs         | prohibited         | prohibited                            | prombited        | fclк/4                    |  |        |

| 1   | 1        | 1                   |     |      |           | <u>54</u> _μs   | 27_µs           | Setting prohibited    |                    |                                       |                  | fськ/2                    |  |        |

| 0   | 0        | 0                   |     |      |           |                 |                 | Setting               | Setting            | Setting prohibited                    | <u>50</u> μs     | fc∟к/64                   |  |        |

| 0   | 0        | 1                   |     |      |           |                 |                 | prohibited            | prohibited         | 50 μs                                 | 25_µs            | fclк/ <b>32</b>           |  |        |

| 0   | 1        | 0                   |     |      |           | Setting         | Setting         |                       | <u>50</u> μs       | <u>25</u> μs                          |                  | fclк/16                   |  |        |

| 0   | 1        | 1                   | 4   | 1 1  | Low-      | prohibited      | prohibited      | 50 μs                 | <u>25</u> μs       |                                       |                  | fclк/8                    |  |        |

| 1   | 0        | 0                   |     |      | Voltage 2 |                 |                 | <u>37.5</u> μs        |                    |                                       | Sotting          | fськ/6                    |  |        |

| 1   | 0        | 1                   |     |      |           |                 |                 | <u>31.25 μ</u> s      | Sotting            | Setting<br>prohibited                 |                  | fськ/5                    |  |        |

| 1   | 1        | 0                   |     |      |           |                 | <u>50</u> μs    | <u>25</u> μs          | Setting prohibited |                                       |                  | fськ/4                    |  |        |

| 1   | 1        | 1                   |     |      |           | <u>50</u> _μs   | <b>25</b> μs    | Setting<br>prohibited | Promoted           |                                       |                  | fclк/2                    |  |        |

Note (Omitted)

Incorrect:

#### Table 11-3. A/D Conversion Time Selection (8/8)

#### (8) 1.6 V $\leq$ VDD < 1.8 V

#### When there is stabilization wait time (hardware trigger wait mode)

| A/D | Convert | er Mode<br>(ADM0) | e Regist | er 0 |           |                       | Co              | onversion Ti    | me Selectio           | n                            |                  | lon<br>AD)                |         |   |   |   |   |            |            |            |            |            |            |        |

|-----|---------|-------------------|----------|------|-----------|-----------------------|-----------------|-----------------|-----------------------|------------------------------|------------------|---------------------------|---------|---|---|---|---|------------|------------|------------|------------|------------|------------|--------|

| FR2 | FR1     | FR0               | LV1      | LV0  | Mode      | fclk =<br>1 MHz       | fclk =<br>2 MHz | fclk=<br>4 MHz  | fclk =<br>8 MHz       | fCLK =<br>16 MHz<br>(Note 2) | fclk =<br>32 MHz | Conversion<br>Clock (fAD) |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 0       | 0                 |          |      |           |                       |                 |                 |                       |                              |                  | fclк/64                   |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 0       | 1                 |          |      |           |                       |                 |                 |                       |                              |                  | fclк/32                   |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 1       | 0                 |          |      |           |                       |                 |                 |                       |                              |                  | fclк/16                   |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 1       | 1                 | 0        | 0    | Normal    | Setting               | Setting         | Setting         | Setting               | Setting                      | Setting          | fськ/8                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 0       | 0                 | 0        | 0    | 1         | prohibited            | prohibited      | prohibited      | prohibited            | prohibited                   | prohibited       | fclк/6                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 0       | 1                 |          |      |           |                       |                 |                 |                       |                              |                  | fс∟к/5                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 1       | 0                 |          |      |           |                       |                 |                 |                       |                              |                  | fськ/4                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 1       | 1                 |          |      |           |                       |                 |                 |                       |                              |                  | fclк/2                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 0       | 0                 |          |      |           |                       |                 |                 |                       |                              |                  | fclк/64                   |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 0       | 1                 |          |      |           |                       |                 |                 |                       |                              |                  | fclк/32                   |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 1       | 0                 |          |      |           |                       |                 |                 |                       |                              |                  | fclк/16                   |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 1       | 1                 |          |      | Normal    | Setting               | Setting         | Setting         | Setting               | Setting                      | Setting          | fclк/8                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 0       | 0                 | 0        | 1    | 2         | 2                     | 2               | 2               | 2                     | 2                            | 2                | 2                         | 2       | 2 | 2 | 2 | 2 | prohibited | prohibited | prohibited | prohibited | prohibited | prohibited | fclк/6 |

| 1   | 0       | 1                 |          |      |           |                       |                 |                 |                       |                              |                  | fськ/5                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 1       | 0                 |          |      |           |                       |                 |                 |                       |                              |                  | fськ/4                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 1       | 1                 |          |      |           |                       |                 |                 |                       |                              |                  | fclк/2                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 0       | 0                 |          |      |           |                       | Setting         | Setting         | Setting<br>prohibited | 108 <i>µ</i> s               |                  | fc⊥к/64                   |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 0       | 1                 |          |      |           | Setting               | prohibited      | prohibited      | 108. <i>µ</i> s       |                              |                  | fclк/32                   |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 1       | 0                 |          |      |           |                       | prohibited      |                 | 108. <i>µ</i> s       |                              |                  |                           | fclк/16 |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 1       | 1                 |          |      | Low-      |                       | 108 <i>µ</i> s  |                 |                       |                              | Setting          | fclк/8                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 0       | 0                 | 1        | 0    | Voltage 1 |                       | 81. <i>µ</i> s  |                 | o #*                  | Setting                      | prohibited       | fськ/6                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 0       | 1                 |          |      |           | 135.µs                |                 | Setting         | Setting prohibited    | prohibited                   |                  | fclк/5                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 1       | 0                 |          |      |           | 108.µs                | Setting         | prohibited      | promotied             |                              |                  | fclк/4                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 1       | 1                 |          |      |           | Setting prohibited    | prohibited      |                 |                       |                              |                  | fclк/2                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 0       | 0                 |          |      |           |                       | Setting         | Setting         | Setting prohibited    | 100. <i>µ</i> s              |                  | fс∟к/64                   |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 0       | 1                 |          |      |           | Setting               | prohibited      | prohibited      | 100 <i>.µ</i> s       |                              |                  | fclк/32                   |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 1       | 0                 |          |      |           | prohibited            |                 | 100. <i>µ</i> s |                       |                              |                  | fclк/16                   |         |   |   |   |   |            |            |            |            |            |            |        |

| 0   | 1       | 1                 | 1        | 1    |           |                       | 100. <i>µ</i> s |                 |                       |                              | Setting          | fclк/8                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 0       | 0                 |          |      | Voltage 2 |                       | -               |                 | Setting               | Setting                      | prohibited       | fclк/6                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 0       | 1                 |          |      |           | 125.µs                | Setting         | Setting         | prohibited            | prohibited                   |                  | fськ/5                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 1       | 0                 |          |      |           | 100. <i>µ</i> s       | prohibited      | prohibited      |                       |                              |                  | fськ/4                    |         |   |   |   |   |            |            |            |            |            |            |        |

| 1   | 1       | 1                 |          |      |           | Setting<br>prohibited |                 |                 |                       |                              |                  | fclк/2                    |         |   |   |   |   |            |            |            |            |            |            |        |

Note (Omitted)

RENESAS

Correct:

#### Table 11-3. A/D Conversion Time Selection (6/8)

#### (6) 2.7 V $\leq$ VDD < 3.6 V

#### When there is stabilization wait time (hardware trigger wait mode)

| A/D | Converte<br>( | er Mode<br>ADM0) | e Registe | er O |              |                              | Со         | onversion T           | ime Selectio          | n                     |                       | rsion<br>(fAD)                        |

|-----|---------------|------------------|-----------|------|--------------|------------------------------|------------|-----------------------|-----------------------|-----------------------|-----------------------|---------------------------------------|

| FR2 | FR1           | FR0              | LV1       | LV0  | Mode         | fclk =                       | fclk =     | fclk =                | fclk =                | fclk =                | fclk =                | Conversion<br>Clock (f <sup>AD)</sup> |

|     |               |                  |           |      |              | 1 MHz                        | 2 MHz      | 4 MHz                 | 8 MHz                 | 16 MHz                | 32 MHz                | 0                                     |

| 0   | 0             | 0                |           |      |              |                              |            | Setting               | Setting<br>prohibited | Setting<br>prohibited | 54 μs                 | fс∟к/64                               |

| 0   | 0             | 1                |           |      |              | Normal Setting prohibited 54 | o          | prohibited            | -                     | 54 μs                 | 27 μs                 | fclк/32                               |

| 0   | 1             | 0                |           |      |              |                              | Setting    |                       | 54 μs                 | 27 μs                 | 13.5 μs               | fclк/16                               |

| 0   | 1             | 1                | 0         | 0    |              |                              | 54 μs      | 27 μs                 | 13.5 μs               | 6.75 μs               | fclк/8                |                                       |

| 1   | 0             | 0                | U         | U    | 1            |                              |            | 40.5 μs               | 20.25 μs              | 10.125 μs             | 5.0625 μs             | fськ/6                                |

| 1   | 0             | 1                |           |      |              |                              |            | 33.75 μs              | 16.875 μs             | 8.4375 μs             |                       | fс∟к/5                                |

| 1   | 1             | 0                |           |      |              |                              | 54 μs      | 27 μs                 | 13.5 μs               | 6.75 μs               | Setting               | fськ/4                                |

| 1   | 1             | 1                |           |      |              | 54 μs                        | 27 μs      | 13.5 μs               | 6.75 μs               | Setting<br>prohibited | prohibited            | fс∟к/2                                |

| 0   | 0             | 0                |           |      |              |                              |            |                       | Setting               | Setting<br>prohibited | 50 μs                 | fclк/64                               |

| 0   | 0             | 1                |           |      |              |                              |            | Setting               | prohibited            | 50 μs                 | 25 μs                 | fclк/32                               |

| 0   | 1             | 0                |           |      |              | Setting                      | Setting    | prohibited            | 50 μs                 | 25 μs                 | 12.5 μs               | fclк/16                               |

| 0   | 1             | 1                | •         |      | Normal       | prohibited                   | prohibited | 50 μs                 | 25 μs                 | 12.5 μs               | 6.25 μs               | fclк/8                                |

| 1   | 0             | 0                | 0         | 1    | 2            | promotion                    |            | 37.5 μs               | 18.75 μs              | 9.375 μs              | 4.6875 <i>μ</i> s     | fськ/6                                |

| 1   | 0             | 1                |           |      |              |                              |            | 31.25 μs              | 15.625 μs             | 7.8125 μs             | Setting               | fськ/5                                |

| 1   | 1             | 0                |           |      |              |                              | 50 μs      | 25 μs                 | 12.5 μs               | 6.25 μs               |                       | fськ/4                                |

| 1   | 1             | 1                |           |      |              | 50 μs                        | 25 μs      | 12.5 μs               | 6.25 μs               | Setting prohibited    | prohibited            | fс∟к/2                                |

| 0   | 0             | 0                |           |      |              |                              |            | Setting               | Setting               | Setting prohibited    | 42 µs                 | fclк/64                               |

| 0   | 0             | 1                |           |      |              |                              | Setting    | prohibited            | prohibited            | 42 µs                 | 21 μs                 | fclк/32                               |

| 0   | 1             | 0                |           |      |              | Setting                      |            |                       | 42 μs                 | 21 μs                 |                       | fclк/16                               |

| 0   | 1             | 1                |           |      | Low-         | prohibited                   | prohibited | 42 μs                 | 21 μs                 |                       |                       | fclк/8                                |

| 1   | 0             | 0                | 1         | 0    | Voltage      |                              |            | 31.5 μs               |                       |                       |                       | fськ/6                                |

| 1   | 0             | 1                |           |      | 1            |                              |            | 26.25 μs              |                       | Setting               | Setting<br>prohibited | fськ/5                                |

| 1   | 1             | 0                |           |      |              |                              | 42 μs      | 21 μs                 | Setting<br>prohibited | prohibited            | prombiled             | fськ/4                                |

| 1   | 1             | 1                |           |      |              | 42 µs                        | 21 μs      | Setting<br>prohibited |                       |                       |                       | fclk/2                                |

| 0   | 0             | 0                |           |      |              |                              |            |                       | Setting               | Setting<br>prohibited | 38 µs                 | fclк/64                               |

| 0   | 0             | 1                |           |      |              |                              |            | Setting<br>prohibited | prohibited            | 38 μs                 | 19 µs                 | fclк/32                               |

| 0   | 1             | 0                |           |      |              | 0                            | Setting    | promotou              | 38 μs                 | 19 μs                 |                       | fclк/16                               |

| 0   | 1             | 1                |           | 1    | Low-         | Setting<br>prohibited        | prohibited | 38 µs                 | 19 μs                 |                       | -                     | fськ/8                                |

| 1   | 0             | 0                | 1         |      | Voltage<br>2 |                              |            | 28.5 μs               |                       |                       | Cotting               | fськ/6                                |

| 1   | 0             | 1                |           |      | 2            |                              |            | 23.7 <u>5</u> µs      | us Setting            | Setting               | Setting<br>prohibited | fськ/5                                |

| 1   | 1             | 0                |           |      |              |                              | 38 μs      | 19 μs                 | Setting prohibited    | prohibited            | prombled              | fс∟к/4                                |

| 1   | 1             | 1                |           |      |              | 38 µs                        | 19 μs      | Setting<br>prohibited |                       |                       |                       | fс∟к/2                                |

Correct:

#### Table 11-3. A/D Conversion Time Selection (7/8)

#### (7) 1.8 V $\leq$ VDD < 2.7 V

#### When there is stabilization wait time (hardware trigger wait mode)

| A/D Co | onverter N | Mode Re | gister 0 ( | ADM0) |             |                    | C          | Conversion <sup>·</sup> | Time Select           | ion                    |                       | ×               |        |

|--------|------------|---------|------------|-------|-------------|--------------------|------------|-------------------------|-----------------------|------------------------|-----------------------|-----------------|--------|

| FR2    | FR1        | FR0     | LV1        | LV0   | Mode        | fclk =             | fclk =     | fclk =                  | fclk =                | fclk =                 | fclk =                | on<br>Clock     |        |

| FR2    | FRI        | FRU     | LVI        | LVU   |             | 1 MHz              | 2 MHz      | 4 MHz                   | 8 MHz                 | 16 MHz <sup>Note</sup> | 32 MHz                | 0               |        |

| x      | x          | x       | 0          | 0     | Normal<br>1 |                    |            | Setting                 | prohibited            |                        |                       | -               |        |

| x      | x          | x       | 0          | 1     | Normal<br>2 | Setting prohibited |            |                         |                       |                        | -                     |                 |        |

| 0      | 0          | 0       |            |       |             |                    |            | Setting                 | Setting               | Setting<br>prohibited  | 42 μs                 | fclк/64         |        |

| 0      | 0          | 1       |            |       |             |                    |            | prohibited              | prohibited            | 42 μs                  | 21 μs                 | fclк/32         |        |

| 0      | 1          | 0       |            |       |             | Setting            | Setting    | -                       | 42 μs                 | 21 μs                  |                       | fclк/16         |        |

| 0      | 1          | 1       |            | •     |             |                    | prohibited | prohibited              | 42 μs                 | 21 μs                  |                       |                 | fськ/8 |

| 1      | 0          | 0       | 1          | 0     |             | -                  |            | 31.5 μs                 |                       | c                      | Setting               | fclк/6          |        |

| 1      | 0          | 1       |            |       |             |                    |            | 26.25 μs                | 0 - #1                | Setting                | Setting<br>prohibited | fс∟к/5          |        |

| 1      | 1          | 0       |            |       |             |                    | 42 μs      | 21 μs                   | Setting<br>prohibited | prohibited             | profibiled            | fс∟к/4          |        |

| 1      | 1          | 1       |            |       |             | 42 μs              | 21 µs      | Setting prohibited      | promoteu              |                        |                       | fськ/2          |        |

| 0      | 0          | 0       |            |       |             |                    |            | Setting                 | Setting               | Setting prohibited     | 38 μ <b>s</b>         | fс⊥к/ <b>64</b> |        |

| 0      | 0          | 1       |            |       |             |                    |            | prohibited              | prohibited            | 38 μs                  | 19 μs                 | fclк/32         |        |

| 0      | 1          | 0       |            |       |             | Setting            | Setting    |                         | 38 µs                 | 19 μs                  |                       | fськ/16         |        |

| 0      | 1          | 1       | 1          | 1     | Low-        | prohibited         | prohibited | 38 µs                   | 19 μs                 |                        |                       | fclк/8          |        |

| 1      | 0          | 0       | 1          | 1     | Voltage 2   | -                  |            | 28.5 μs                 |                       |                        | Sotting               | fськ/6          |        |

| 1      | 0          | 1       |            |       |             |                    |            | 28.75 μs                | Cotting               | Setting                | Setting<br>prohibited | fclк/5          |        |

| 1      | 1          | 0       |            |       |             |                    | 38 μs      | 19 μs                   | Setting<br>prohibited | prohibited             | prohibited            | fclк/4          |        |

| 1      | 1          | 1       |            |       |             | 38 μs              | 19 µs      | Setting prohibited      | promoted              |                        |                       | fськ/2          |        |

Note (Omitted)

Correct:

#### Table 11-3. A/D Conversion Time Selection (8/8)

#### (8) 1.6 V $\leq$ VDD < 1.8 V

#### When there is stabilization wait time (hardware trigger wait mode)

| A/D | Convert | er Mode<br>(ADM0) | e Regist | er 0 |                   |                       | Co                    | onversion Ti       | me Selectio        | n                          |                  | sion<br>(fAD)             |

|-----|---------|-------------------|----------|------|-------------------|-----------------------|-----------------------|--------------------|--------------------|----------------------------|------------------|---------------------------|

| FR2 | FR1     | FR0               | LV1      | LV0  | Mode              | fc∟ĸ =<br>1 MHz       | fclk =<br>2 MHz       | fclк=<br>4 MHz     | fclk=<br>8 MHz     | fCLK =<br>16 MHz<br>Note 2 | fclк =<br>32 MHz | Conversion<br>Clock (fAD) |

| x   | x       | x                 | 0        | 0    | Normal<br>1       | Setting<br>prohibited | _                     | x                  | x                  | x                          | 0                | 0                         |

| x   | x       | x                 | 0        | 1    | Normal<br>2       | Setting<br>prohibited | _                     | x                  | x                  | x                          | 0                | 1                         |

| 0   | 0       | 0                 |          |      |                   |                       | Setting               | Setting            | Setting prohibited | 84 <i>μ</i> s              |                  | fськ/64                   |

| 0   | 0       | 1                 |          |      |                   | Setting               | prohibited            | prohibited         | 84 <i>μ</i> s      |                            |                  | fclк/32                   |

| 0   | 1       | 0                 |          |      |                   | prohibited            |                       | 84 <i>µ</i> s      |                    |                            |                  | fclк/16                   |

| 0   | 1       | 1                 |          | 0    | Low-<br>Voltage 1 |                       | 84 <i>μ</i> s         |                    |                    |                            | Setting          | fclk/8                    |

| 1   | 0       | 0                 | 1        | 0    |                   |                       | 63 <i>μ</i> s         |                    | 0                  | Setting                    | prohibited       | fclк/6                    |

| 1   | 0       | 1                 |          |      |                   |                       | 105 <i>µ</i> s        |                    | Setting            | Setting prohibited         | prohibited       |                           |

| 1   | 1       | 0                 |          |      |                   | 84 <i>μ</i> s         | Setting<br>prohibited | prohibited         | prombiled          |                            |                  | fськ/4                    |

| 1   | 1       | 1                 |          |      |                   | Setting<br>prohibited |                       |                    |                    |                            |                  | fclк/2                    |

| 0   | 0       | 0                 |          |      |                   |                       | Setting               | Setting            | Setting prohibited | 76 <i>μ</i> s              |                  | fclк/64                   |

| 0   | 0       | 1                 |          |      |                   | Setting               | prohibited            | prohibited         | 76 <i>µ</i> s      |                            |                  | fclк/32                   |

| 0   | 1       | 0                 |          |      |                   | prohibited            |                       | 76 <i>μ</i> s      |                    |                            |                  | fclк/16                   |

| 0   | 1       | 1                 | 1        | 1    | Low-              |                       | 76 <i>μ</i> s         |                    |                    |                            | Setting          | fclk/8                    |

| 1   | 0       | 0                 |          |      | Voltage 2         |                       |                       |                    | Setting            | Setting                    | prohibited       | fськ/6                    |

| 1   | 0       | 1                 |          |      | 99<br>70<br>Se    | 95 <i>μ</i> s         | Sotting               | Setting            | Ŭ                  | prohibited                 |                  | fс∟к/5                    |