# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                                 | Document<br>No.         | TN-78K-A011A/E                                             | Rev. | 1.00 |          |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------|------|------|----------|

| Title                 | Correction for Incorrect Description Notice<br>78K0R/Lx3-M Descriptions in the User's Mar<br>Hardware Rev. 1.00 Changed | Information<br>Category | Technical Notification                                     |      |      |          |

|                       |                                                                                                                         |                         |                                                            |      |      |          |

| Applicable<br>Product |                                                                                                                         |                         | Reference 78K0R/Lx3-M User's<br>Document (R01UH0182EJ0100) |      |      | lardware |

This document describes misstatements found in the 78K0R/Lx3-M User's Manual: Hardware Rev. 1.00 (R01UH0182EJ0100)

**Corrections**

| Applicable Item                                                                                               | Applicable<br>Page | Contents                          |

|---------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------|

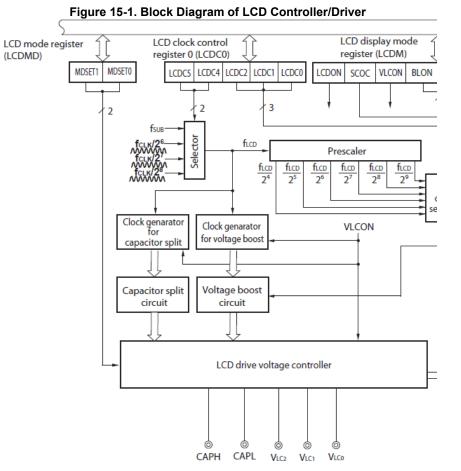

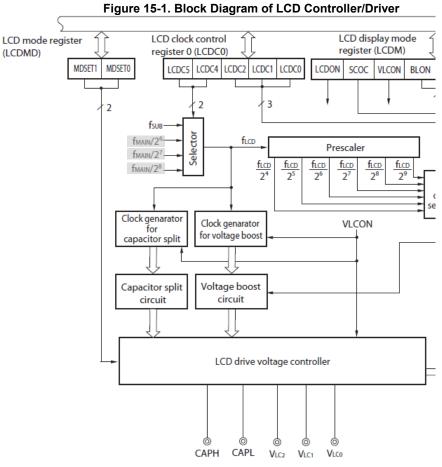

| 15.2 Configuration of LCD Controller/Driver<br>Figure 15-1. Block Diagram of LCD Controller/Driver            | Page 619           | Incorrect descriptions<br>revised |

| 15.3 Registers Controlling LCD Controller/Driver<br>Figure 15-4. Format of LCD Clock Control Register (LCDC0) | Page 622           | Incorrect descriptions<br>revised |

## Document Improvement

The above corrections will be made for the next revision of the User's Manual: Hardware.

# RENESAS TECHNICAL UPDATE TN-78K-A011A/E

|     |                                                                                                                | Corrections and Applicable Items |                 |                             |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------|-----------------------------|--|--|--|--|

| No. | No. Document No. English                                                                                       |                                  | R01UH0182EJ0100 | document for<br>corrections |  |  |  |  |

| 1   | 15.2 Configuration of LCD Controller/Driver<br>Figure 15-1. Block Diagram of LCD Controller/Driver<br>Page 619 |                                  |                 |                             |  |  |  |  |

| 2   | 15.3 Re<br>Figure 2                                                                                            | Page 4                           |                 |                             |  |  |  |  |

Incorrect: Bold with underline; Correct: Gray hatched

# **Revision History**

78K0R/Lx3 Correction for incorrect description notice

| Document Number | Issue Date   | Description                                      |

|-----------------|--------------|--------------------------------------------------|

| TN-78K-A011A/E  | Feb. 1, 2017 | First edition issued                             |

|                 |              | Corrections No.1 to No.2 revised (this document) |

## 1. <u>15.2 Configuration of LCD Controller/Driver</u> <u>Figure 15-1. Block Diagram of LCD Controller/Driver (Page 619)</u>

#### Incorrect:

Date: Feb. 1, 2017

Correct:

# 2. <u>15.3 Registers Controlling LCD Controller/Driver</u> <u>Figure 15-4. Format of LCD Clock Control Register (LCDC0) (Page 622)</u>

### Incorrect:

Figure 15-4. Format of LCD Clock Control Register (LCDC0)

$\label{eq:Address} Address: FFF42 \ H \quad After \ reset: 00H \quad R/W$

| Symbol | 7 | 6 | 5      | 4      | 3 | 2      | 1      | 0      |

|--------|---|---|--------|--------|---|--------|--------|--------|

| LCDC0  | 0 | 0 | LCDC05 | LCDC04 | 0 | LCDC02 | LCDC01 | LCDC00 |

| LCDC0 | 5 LCDC04 | LCD source clock (fLCD) selection |

|-------|----------|-----------------------------------|

| 0     | 0        | fsuв                              |

| 0     | 1        | fclk/26                           |

| 1     | 0        | fclk/27                           |

| 1     | 1        | fclk/2 <sup>8</sup>               |

| LCDC02 | LCDC01       | LCDC00 | LCD clock (LCDCL) selection |

|--------|--------------|--------|-----------------------------|

| 0      | 0            | 0      | fLCD/24                     |

| 0      | 0            | 1      | fLCD/2 <sup>5</sup>         |

| 0      | 1            | 0      | fLCD/2 <sup>6</sup>         |

| 0      | 1            | 1      | flcd/2 <sup>7</sup>         |

| 1      | 0            | 0      | fLCD/2 <sup>8</sup>         |

| 1      | 0            | 1      | fLCD/29                     |

| Ot     | her than abo | ve     | Setting prohibited          |

Cautions 1. Bits 3, 6, and 7 must be set to 0.

2. Set the LCD clock (LCDCL) to no more than 512 Hz when the internal voltage boost method has been set.

Remark fcLK: CPU/Peripheral hardware clock frequency fsub: Subsystem clock frequency Date: Feb. 1, 2017

#### Correct:

Figure 15-4. Format of LCD Clock Control Register (LCDC0)

Address : FFF42 H After reset : 00H R/W

| Symbol | 7 | 6 | 5      | 4      | 3 | 2      | 1      | 0      |

|--------|---|---|--------|--------|---|--------|--------|--------|

| LCDC0  | 0 | 0 | LCDC05 | LCDC04 | 0 | LCDC02 | LCDC01 | LCDC00 |

| LCDC05 | LCDC04 | LCD source clock (fLCD) selection |

|--------|--------|-----------------------------------|

| 0      | 0      | fsuв                              |

| 0      | 1      | fmain/2 <sup>6</sup>              |

| 1      | 0      | fmain/2 <sup>7</sup>              |

| 1      | 1      | fmain/2 <sup>8</sup>              |

| LCDC02 | LCDC01       | LCDC00 | LCD clock (LCDCL) selection |

|--------|--------------|--------|-----------------------------|

| 0      | 0            | 0      | flcd/24                     |

| 0      | 0            | 1      | fLCD/2 <sup>5</sup>         |

| 0      | 1            | 0      | fLCD/2 <sup>6</sup>         |

| 0      | 1            | 1      | flcd/2 <sup>7</sup>         |

| 1      | 0            | 0      | fLCD/2 <sup>8</sup>         |

| 1      | 0            | 1      | fLCD/29                     |

| Ot     | her than abo | ve     | Setting prohibited          |

#### Cautions 1. Bits 3, 6, and 7 must be set to 0.

2. Set the LCD clock (LCDCL) to no more than 512 Hz when the internal voltage boost method has been set.

Remark fMAIN: Main system clock frequency fsub: Subsystem clock frequency