# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

発行日: 2008年06月10日

# **RENESAS TECHNICAL UPDATE**

〒100-0004 東京都千代田区大手町 2-6-2 日本ビル 株式会社 ルネサス テクノロジ

問合せ窓口 http://japan.renesas.com/inquiry

E-mail: csc@renesas.com

| 製   | 品分類    | 分類 MPU&MCU 発行番号 TI |        | TN-H8*-A | 387A/J                                   | Rev. | 第1版   |

|-----|--------|--------------------|--------|----------|------------------------------------------|------|-------|

| 題名  |        |                    |        | 情報分類     | 技術資料                                     |      |       |

| 適   |        |                    | 対象ロット等 |          |                                          | 0    |       |

| 用製品 | H8SX/1 | 663 グループ           | 全ロット   | 関連資料     | H8SX/1663 グルー<br>ュアル<br>(RJJ09B0319-0100 |      | ウェアマニ |

H8SX/1663 グループのハードウェアマニュアルにおいて誤記がありましたので、ご案内申し上げます。

# <誤記訂正内容>

## 1. 概要

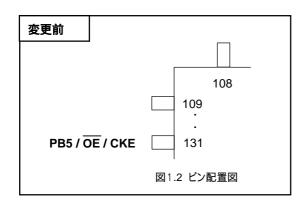

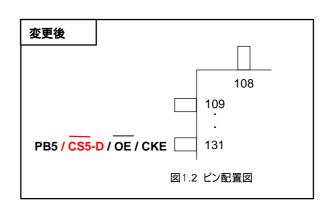

(1) 頁 1-3 「図 1.2 ピン配置図」において、131pin の機能を以下のように訂正します。

(2) 頁 1-8 「表 1.1 動作モード別ピン配置一覧」において、ピン番号 131 を以下のように訂正します。 〔変更前〕

| ピン番号 | 端子                    | 端子名 |  |  |  |  |  |

|------|-----------------------|-----|--|--|--|--|--|

|      | モード 2、6、7 モード 4、5     |     |  |  |  |  |  |

| 131  | PB5/OE/CKE PB5/OE/CKE |     |  |  |  |  |  |

# 〔変更後〕

| ピン番号 | 端子名               |                    |  |  |  |

|------|-------------------|--------------------|--|--|--|

|      | モード 2、6、7         | モード 4、5            |  |  |  |

| 131  | PB5/CS5 -D/OE/CKE | PB5/CS5 -D /OE/CKE |  |  |  |

(3) 頁 1-12 「表 1.2 端子機能」を、以下のように訂正します。

〔変更前〕

| 分類   | 記号                | ピン番号     | 入出力 | 機能             |

|------|-------------------|----------|-----|----------------|

|      |                   | FP-144LV |     |                |

| バス制御 | CS0               | 144      | 出力  | エリア7~0の選択信号です。 |

|      | CS1               | 1        |     |                |

|      | CS2-A/CS2-B       | 2/1      |     |                |

|      | CS3-A             | 3        |     |                |

|      | CS4-A/CS4-B       | 144/130  |     |                |

|      | CS5-A/CS5-B       | 1/144    |     |                |

|      | CS6-A/CS6-B/CS6-D | 2/1/132  |     |                |

|      | CS7-A/CS7-B       | 3/1      |     |                |

#### 〔変更後〕

| 分類   | 記号                | ピン番号                    | 入出力 | 機能               |

|------|-------------------|-------------------------|-----|------------------|

|      |                   | FP-144LV                |     |                  |

| バス制御 | CS0               | 144                     | 出力  | エリア 7~0 の選択信号です。 |

|      | CS1               | 1                       |     |                  |

|      | CS2-A/CS2-B       | 2/1                     |     |                  |

|      | CS3-A             | 3                       |     |                  |

|      | CS4-A/CS4-B       | 144/130                 |     |                  |

|      | CS5-A/CS5-B/CS5-D | 1/144 <mark>/131</mark> |     |                  |

|      | CS6-A/CS6-B/CS6-D | 2/1/132                 |     |                  |

|      | CS7-A/CS7-B       | 3/1                     |     |                  |

# 2. 割り込みコントローラ

(1) 頁 5-11 ISR の IRQ15F ビットを以下のように訂正します。

〔変更前〕IRQ15(15 ビット)は、リード/ライト可能になっている。

IRQ ステータスレジスタ(ISR)

| ビット  | 15     | 14  | 13  | 12  | 11     | 10     | 9      | 8      |

|------|--------|-----|-----|-----|--------|--------|--------|--------|

| ビット名 | IRQ15F | -   | -   | -   | IRQ11F | IRQ10F | IRQ9F  | IRQ8F  |

| 初期値: | 0      | 0   | 0   | 0   | 0      | 0      | 0      | 0      |

| R/W  | R/W    | R/W | R/W | R/W | R/(W)* | R/(W)* | R/(W)* | R/(W)* |

【変更後】IRQ15(15 ビット)は、リード可能、ライトはフラグをクリアするための 0 ライトのみ可能です。 IRQ ステータスレジスタ(ISR)

| ビット  | 15                       | 14  | 13  | 12  | 11     | 10     | 9      | 8      |

|------|--------------------------|-----|-----|-----|--------|--------|--------|--------|

| ビット名 | IRQ15F                   | -   | -   | -   | IRQ11F | IRQ10F | IRQ9F  | IRQ8F  |

| 初期値: | 0                        | 0   | 0   | 0   | 0      | 0      | 0      | 0      |

| R/W  | R/ <b>(</b> W <b>)</b> * | R/W | R/W | R/W | R/(W)* | R/(W)* | R/(W)* | R/(W)* |

# 3. I/O ポート

(1) 頁 9-7 「表 9.2 各ポートのレジスタ構成」において、ポート B の端子数を以下のように訂正します。

## 〔変更前〕

表 9.2 各ポートのレジスタ構成

| ポート  | 端子数 | レジスタ                    |  |  |  |   |   |

|------|-----|-------------------------|--|--|--|---|---|

|      |     | DDR DR PORT ICR PCR ODR |  |  |  |   |   |

| ポートB | 4   |                         |  |  |  | - | - |

## 〔変更後〕

表 9.2 各ポートのレジスタ構成

| ポート  | 端子数 |                         | レジスタ |  |  |   |   |  |

|------|-----|-------------------------|------|--|--|---|---|--|

|      |     | DDR DR PORT ICR PCR ODR |      |  |  |   |   |  |

| ポートB | 8   |                         |      |  |  | - | - |  |

(2) 頁 9-41 「表 9.5 各ポートの出力信号有効設定一覧」を、以下のように訂正します。

# 〔変更前〕

表 9.5 各ポートの出力信号有効設定一覧 (該当箇所のみ抜粋)

| Po | ort | 出力設定<br>信号名 | 出力信号名 | 信号選択レジスタの設定  | 各内部モジュールの設定                                    |

|----|-----|-------------|-------|--------------|------------------------------------------------|

| РВ | 3   | CAC_OE      | CAS   |              | SYSCR.EXPE=1,DRAMCR.DRAME=1,<br>DRAMCR.DTYPE=1 |

|    |     | CS3A_OE     | CS3   | PFCR2.CS3S=0 | SYSCR.EXPE=1,PFCR0.CS3E=1                      |

|    | 0   | CS4_OE      | CS4   |              | SYSCR.EXPE=1,PFCR0.CS4E=1                      |

## 〔変更後〕

# 表 9.5 各ポートの出力信号有効設定一覧 (該当箇所のみ抜粋)

| Po | ort | 出力設定<br>信号名 | 出力信号名 | 信号選択レジスタの設定        | 各内部モジュールの設定                                    |

|----|-----|-------------|-------|--------------------|------------------------------------------------|

| PB | 3   | CAS_OE      | CAS   |                    | SYSCR.EXPE=1,DRAMCR.DRAME=1,<br>DRAMCR.DTYPE=1 |

|    |     | CS3A_OE     | CS3   | 【削除】               | SYSCR.EXPE=1,PFCR0.CS3E=1                      |

|    | 0   | CS4A_OE     | CS4   | PFCR1.CS4S[A,B]=00 | SYSCR.EXPE=1,PFCR0.CS4E=1                      |

(3) 頁 9-42 「表 9.5 各ポートの出力信号有効設定一覧」において、「各内部モジュールの設定 ( PE7 ~ PE0 )」を以下のように訂正します。

発行日: 2008年06月10日

# 〔変更前〕

表 9.5 各ポートの出力信号有効設定一覧

| Po | ort | 出力設定<br>信号名 | 出力信号名 | 信号選択レジ<br>スタの設定 | 各内部モジュールの設定                 |

|----|-----|-------------|-------|-----------------|-----------------------------|

| PE | 7   | A15_OE      | A15   |                 | SYSCR.EXPE=1,PDDDR.PE7DDR=1 |

|    | 6   | A14_OE      | A14   |                 | SYSCR.EXPE=1,PDDDR.PE6DDR=1 |

|    | 5   | A13_OE      | A13   |                 | SYSCR.EXPE=1,PDDDR.PE5DDR=1 |

|    | 4   | A12_OE      | A12   |                 | SYSCR.EXPE=1,PDDDR.PE4DDR=1 |

|    | 3   | A11_OE      | A11   |                 | SYSCR.EXPE=1,PDDDR.PE3DDR=1 |

|    | 2   | A10_OE      | A10   |                 | SYSCR.EXPE=1,PDDDR.PE2DDR=1 |

|    | 1   | A9_OE       | A9    |                 | SYSCR.EXPE=1,PDDDR.PE1DDR=1 |

|    | 0   | A8_OE       | A8    |                 | SYSCR.EXPE=1,PDDDR.PE0DDR=1 |

# 〔変更後〕

表 9.5 各ポートの出力信号有効設定一覧

| Po | ort | 出力設定<br>信号名 | 出力信号名 | 信号選択レジ<br>スタの設定 | 各内部モジュールの設定                 |

|----|-----|-------------|-------|-----------------|-----------------------------|

| PE | 7   | A15_OE      | A15   |                 | SYSCR.EXPE=1,PEDDR.PE7DDR=1 |

|    | 6   | A14_OE      | A14   |                 | SYSCR.EXPE=1,PEDDR.PE6DDR=1 |

|    | 5   | A13_OE      | A13   |                 | SYSCR.EXPE=1,PEDDR.PE5DDR=1 |

|    | 4   | A12_OE      | A12   |                 | SYSCR.EXPE=1,PEDDR.PE4DDR=1 |

|    | 3   | A11_OE      | A11   |                 | SYSCR.EXPE=1,PEDDR.PE3DDR=1 |

|    | 2   | A10_OE      | A10   |                 | SYSCR.EXPE=1,PEDDR.PE2DDR=1 |

|    | 1   | A9_OE       | A9    |                 | SYSCR.EXPE=1,PEDDR.PE1DDR=1 |

|    | 0   | A8_OE       | A8    |                 | SYSCR.EXPE=1,PEDDR.PE0DDR=1 |

(4) 頁 9-45 PFCR1 のビット 1、0 の説明を以下のように訂正します。

〔変更前〕

ポートファンクションコントロールレジスタ 1(PFCR1)

| ビット | ビット名   | 初期値 | R/W | 説明                                 |

|-----|--------|-----|-----|------------------------------------|

| 7   | CS7SA* | 0   | R/W | ~ 説明省略(変更なし) ~                     |

| 6   | CS7SB* | 0   | R/W |                                    |

| 5   | CS6SA* | 0   | R/W |                                    |

| 4   | CS6SB* | 0   | R/W |                                    |

| 3   | CS5SA* | 0   | R/W |                                    |

| 2   | CS5SB* | 0   | R/W |                                    |

| 1   | CS4SA* | 0   | R/W | CS4 出力端子セレクト                       |

| 0   | CS4SB* | 0   | R/W | CS4 出力許可時(CS4E=1) CS4 の出力端子を選択します。 |

|     |        |     |     | 00:PB1 を CS4-A 出力端子として設定           |

|     |        |     |     | 01:PB0 を CS4-B 出力端子として設定           |

|     |        |     |     | 10:(設定禁止)                          |

|     |        |     |     | 11 : ( 設定禁止 )                      |

# 〔変更後〕

ポートファンクションコントロールレジスタ 1(PFCR1)

| ビット | ビット名   | 初期値 | R/W | 説明                                   |

|-----|--------|-----|-----|--------------------------------------|

| 7   | CS7SA* | 0   | R/W | ~ 説明省略(変更なし) ~                       |

| 6   | CS7SB* | 0   | R/W |                                      |

| 5   | CS6SA* | 0   | R/W |                                      |

| 4   | CS6SB* | 0   | R/W |                                      |

| 3   | CS5SA* | 0   | R/W |                                      |

| 2   | CS5SB* | 0   | R/W |                                      |

| 1   | CS4SA* | 0   | R/W | CS4 出力端子セレクト                         |

| 0   | CS4SB* | 0   | R/W | CS4 出力許可時(CS4E=1) CS4 の出力端子を選択します。   |

|     |        |     |     | <br>00: <b>PB0</b> を CS4-A 出力端子として設定 |

|     |        |     |     | <br>01: <b>PB4</b> を CS4-B 出力端子として設定 |

|     |        |     |     | 10 : ( 設定禁止 )                        |

|     |        |     |     | 11:(設定禁止)                            |

# 4. ウォッチドックタイマ

(1) 頁 14-5 RSTCSR の WOVF ビットクリア条件を、以下のように訂正します。

# 〔変更前〕

| ビット | ビット名 | 初期値 | R/W  | 説明                                                                                                                                                                                                                                                         |

|-----|------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | WOVF | 0   | R/VV | ウォッチドッグタイマオーバフローフラグ<br>ウォッチドッグタイマモードで、TCNT がオーバフローするとセットされます。<br>インターバルタイマモードではセットされません。0ライトのみ可能です。<br>[セット条件]<br>ウォッチドッグタイマモードでTCNT がオーバフロー(H'FF H'00)したとき<br>[クリア条件]<br>1 の状態をリードした後、0 をライトしたとき<br>(割り込みを使用しCPU によってクリアする場合、0 ライト後に必ずフラグを<br>リードしてください。) |

| 6   | RSTE | 0   | R/W  | ~ 説明省略(変更なし) ~                                                                                                                                                                                                                                             |

| 5   | -    | 0   | R/W  |                                                                                                                                                                                                                                                            |

| 4~0 | -    | 1   | R    |                                                                                                                                                                                                                                                            |

## 〔変更後〕

| ビット | ビット名 | 初期値 | R/W  | 説明                                                                                                                                                                                     |

|-----|------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | WOVF | 0   | TVVV | ウォッチドッグタイマオーバフローフラグ ウォッチドッグタイマモードで、TCNT がオーバフローするとセットされます。 インターバルタイマモードではセットされません。0ライトのみ可能です。 [セット条件] ウォッチドッグタイマモードでTCNT がオーバフロー(H'FF H'00)したとき [クリア条件] 1 の状態をリードした後、0 をライトしたとき 【以下削除】 |

| 6   | RSTE | 0   | R/W  | ~説明省略(変更なし)~                                                                                                                                                                           |

| 5   | -    | 0   | R/W  |                                                                                                                                                                                        |

| 4~0 | -    | 1   | R    |                                                                                                                                                                                        |

# 5. シリアルコミュニケーションインタフェース

(1) 頁 15-16 シリアルステータスレジスタ(SSR)のビット名を以下のように訂正します。

#### 〔変更前〕

シリアルステータスレジスタ(SSR)

・SCMR の SMIF=0 のとき

| ビット  | 7      | 6      | 5      | 4      | 3      | 2    | 1   | 0    |

|------|--------|--------|--------|--------|--------|------|-----|------|

| ビット名 | TDRE   | RDRF   | ORER   | FRE    | PER    | TEND | MPB | MPBT |

| 初期値: | 1      | 0      | 0      | 0      | 0      | 1    | 0   | 0    |

| R/W  | R/(W)* | R/(W)* | R/(W)* | R/(W)* | R/(W)* | R    | R   | R/W  |

## 〔変更後〕

シリアルステータスレジスタ(SSR)

・SCMR の SMIF=0 のとき

| ビット  | 7      | 6      | 5      | 4      | 3      | 2    | 1   | 0    |

|------|--------|--------|--------|--------|--------|------|-----|------|

| ビット名 | TDRE   | RDRF   | ORER   | FER    | PER    | TEND | MPB | MPBT |

| 初期値: | 1      | 0      | 0      | 0      | 0      | 1    | 0   | 0    |

| R/W  | R/(W)* | R/(W)* | R/(W)* | R/(W)* | R/(W)* | R    | R   | R/W  |

(2) 頁 15-23 「表 15.3 BRR の設定値 N とビットレート B の関係 ( 調歩同期式、ABCS ビット=0 時/ BRR の設定値 )」を以下のように訂正します。

# 〔変更前〕

表 15.3 BRR の設定値 N とビットレート B の関係

| モード   | ABCS<br>ビット | BRR の設定値                                                    | 誤差           |

|-------|-------------|-------------------------------------------------------------|--------------|

| 調歩同期式 | 0           | $B = \frac{P \times 10^6}{64 \times 2^{2n-1} \times B} - 1$ | ~説明省略(変更なし)~ |

|       | 1           | $B = \frac{P \times 10^6}{32 \times 2^{2n-1} \times B} - 1$ |              |

# 〔変更後〕

表 15.3 BRR の設定値 N とビットレート B の関係

| モード   | ABCS<br>ビット | BRR の設定値                                                    | 誤差           |

|-------|-------------|-------------------------------------------------------------|--------------|

| 調歩同期式 | 0           | $N = \frac{P \times 10^6}{64 \times 2^{2n-1} \times B} - 1$ | ~説明省略(変更なし)~ |

|       | 1           | $N = \frac{P \times 10^6}{32 \times 2^{2n-1} \times B} - 1$ |              |

# 6. クロック発振器

(1) 頁 22-5 SUBCKCR のビット 0 のビット名を以下のように訂正します。

#### 〔変更前〕

サブクロックコントロールレジスタ(SUBCKCR)

| ビット  | 7   | 6   | 5   | 4   | 3   | 2     | 1       | 0     |

|------|-----|-----|-----|-----|-----|-------|---------|-------|

| ビット名 | -   | -   | -   | -   | -   | EXSTP | WAKE32K | CS32K |

| 初期値: | 0   | 0   | 0   | 0   | 0   | 0     | 0       | 0     |

| R/W  | R/W | R/W | R/W | R/W | R/W | R/W   | R/W     | R/W   |

#### 〔変更後〕

サブクロックコントロールレジスタ(SUBCKCR)

| ビット  | 7   | 6   | 5   | 4   | 3   | 2     | 1       | 0     |

|------|-----|-----|-----|-----|-----|-------|---------|-------|

| ビット名 | -   | -   | -   | -   | -   | EXSTP | WAKE32K | CK32K |

| 初期値: | 0   | 0   | 0   | 0   | 0   | 0     | 0       | 0     |

| R/W  | R/W | R/W | R/W | R/W | R/W | R/W   | R/W     | R/W   |

# 7. 低消費電力

(1) 頁 23-2 「表 23.1 動作状態」の注釈 4 を以下のように訂正します。

#### 〔変更前〕

\*4 MSTPCRA の MSTPA9、8 ビットの設定により、動作/停止を選択することができます。 ただし、動作を選択した場合でも、端子からの出力はできません。

# 〔変更後〕

\*4 MSTPCRA の MSTPA9、8 ビットの設定により、動作/停止を選択することができます。

# 【以下削除】