# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

発行日: 2009年03月11日

# RENESAS TECHNICAL UPDATE

〒100-0004 東京都千代田区大手町 2-6-2 日本ビル 株式会社 ルネサス テクノロジ

問合せ窓口 http://japan.renesas.com/inquiry E-mail: csc@renesas.com

| 製  | 品分類    | MPU&MCU        | 発行番号   | TN-H8*-A408A/J |                                                   | Rev. | 第1版 |

|----|--------|----------------|--------|----------------|---------------------------------------------------|------|-----|

| 題名 |        |                |        |                | 技術資料                                              |      |     |

| 適  |        |                | 対象ロット等 |                | H8SX/1663<br>グループハードウェアマニュアル<br>(RJJ09B0319-0100) |      |     |

| 田  | H8SX/1 | H8SX/1663 グループ | 全ロット   | 関連資料           |                                                   |      | アル  |

H8SX/1663 グループハードウェアマニュアルにおいて誤記がありましたので、ご案内申し上げます。

#### <誤記訂正内容>

#### 5.割り込みコントローラ

(1) 頁 5-28「5.6.5 割り込みによる DTC、DMAC の起動」の記述から、DTCERF、DTCERG、DTCERH を削除します。

#### 〔変更前〕

#### (1) 割り込み要因の選択

DMAC の各チャネルの起動要因は、DMRSR により選択します。選択した起動要因は、選択回路を経由して DMAC に入力されます。内蔵モジュール割り込みによる転送が有効になるように設定(DMDR のビット設定: DTF1=1、DTF0=0、DTE=1) DMDR の DTA ビットが 1 にセットされていると、その DMAC の起動要因になった割り込み要因は DMAC が管理することになり、DTC の起動要因および CPU の割り込み要因になりません。 DMAC に管理されている割り込み以外の割り込み要因は、DTC の DTCERA ~ DTCERH の DTCE ビットにより、DTC 起動要因とするか、CPU 割り込み要因とするかを選択します。

(省略 ~変更無し~)

(2) 優先順位判定

(省略 ~変更無し~)

(3) 動作順序

(省略 ~変更無し~)

表 5.6 に、DMAC の DMDR の DTA ビット、DTC の DTCERA ~ DTCERH の DTCE ビット、および MRB の DISEL ビットの設定による割り込み要因の選択と割り込み要因クリア制御を示します。

# 〔変更後〕

#### (1) 割り込み要因の選択

DMAC の各チャネルの起動要因は、DMRSR により選択します。選択した起動要因は、選択回路を経由して DMAC に入力されます。内蔵モジュール割り込みによる転送が有効になるように設定(DMDR のビット設定: DTF1=1、DTF0=0、DTE=1)、DMDR の DTA ビットが 1 にセットされていると、その DMAC の起動要因になった割り込み要因は DMAC が管理することになり、DTC の起動要因および CPU の割り込み要因になりません。 DMAC に管理されている割り込み以外の割り込み要因は、DTC の DTCERA ~ DTCERE の DTCE ビットにより、DTC 起動要因とするか、CPU 割り込み要因とするかを選択します。

(省略 ~変更無し~)

(2) 優先順位判定

(省略 ~変更無し~)

(3) 動作順序

(省略 ~変更無し~)

表 5.6 に、DMAC の DMDR の DTA ビット、DTC の DTCERA ~ **DTCERE** の DTCE ビット、および MRB の DISEL ビットの設定による割り込み要因の選択と割り込み要因クリア制御を示します。

8.データトランスファコントローラ(DTC)

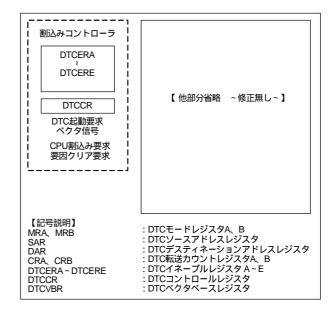

(1) 頁 8-2 「図 8.1 DTC のブロック図」内の DTCER の記述を以下のように訂正します。

〔変更前〕図 8.1 DTC のブロック図

〔 変更後〕図 8.1 DTC のブロック図

発行日: 2009年03月11日

(2) 頁 8-3 「8.2 レジスタの説明」の DTC イネーブルレジスタの記述から、DTCERG、DTCERH を削除します。〔変更前〕

・DTC イネーブルレジスタ A~E、G、H (DTCERA~DTCERE、DTCERG、DTCERH)

#### 〔変更後〕

- ・DTC イネーブルレジスタ A~E ( DTCERA~DTCERE )

- (3) 頁 8-7 DTC イネーブルレジスタの説明から、DTCERG、DTCERH を削除します。

#### 〔変更前〕

8.2.7 DTC イネーブルレジスタ A~E、G、H

(DTCERA ~ DTCERE, DTCERG, DTCERH)

DTCER は、DTC を起動する割り込み要因を選択するためのレジスタで、DTCERA~DTCERE、G、H があります。 【以下省略】

#### 〔変更後〕

8.2.7 DTC イネーブルレジスタ A~E

(DTCERA ~ DTCERE)

DTCER は、DTC を起動する割り込み要因を選択するためのレジスタで、DTCERA ~ DTCERE があります。 【以下省略】

## <u>9. I/Oポート</u>

(1) 頁 9-40 「表 9.5 各ポートの出力信号有効設定一覧」の PA1、PB6 の記述を以下のように訂正します。

#### 〔変更前〕

| Port |   | 出力設定<br>信号名  | 出力<br>信号名    | 信号選択<br>レジスタの設定    | 各内部モジュールの設定                                        |

|------|---|--------------|--------------|--------------------|----------------------------------------------------|

| PA   | 1 | BACK_OE      | BACK_OE BACK |                    | SYSCR.EXPE=1,BCR1.BRLE=1                           |

|      |   | (RD/WR)_OE   | RD/WR        |                    | SYSCR.EXPE=1,PFCR2.REWRE=1、または<br>SRAMCR.BCSELn=1  |

| PB   | 6 | (RD/WR)-B_OE | RD/WR        | PFCR2.RDWRS=1      | SYSCR.EXPE=1,PFCR2.REWRE=1 または、<br>SRAMCR.BCSELn=1 |

|      |   | CS6D_OE      | CS6          | PFCR1.CS6S[A,B]=11 | SYSCR.EXPE=1,PFCR0.CS6E=1                          |

#### 〔変更後〕

| Port |   | 出力設定<br>信号名  | 出力<br>信号名 | 信号選択<br>レジスタの設定    | 各内部モジュールの設定                                         |

|------|---|--------------|-----------|--------------------|-----------------------------------------------------|

| PA   | 1 | BACK_OE      | BACK      |                    | SYSCR.EXPE=1,BCR1.BRLE=1                            |

|      |   | (RD/WR)-A_OE | RD/WR     | PFCR2.RDWRS=0      | SYSCR.EXPE=1,PFCR2.RDWRE=1 または、<br>SRAMCR.BCSELn=1  |

| PB   | 6 | (RD/WR)-B_OE | RD/WR     | PFCR2.RDWRS=1      | SYSCR.EXPE=1,PFCR2.RDWRE =1 または、<br>SRAMCR.BCSELn=1 |

|      |   | CS6D_OE      | CS6       | PFCR1.CS6S[A,B]=11 | SYSCR.EXPE=1,PFCR0.CS6E=1                           |

## 12. 8ビットタイマ(TMR)

(1) 頁 12-24 「12.7.2 A/D 変換器の起動」の説明を以下のように訂正します。

#### 〔変更前〕

TMR\_0 のコンペアマッチ A のみ、A/D 変換器を起動することができます。\*

TMR\_0 のコンペアマッチ A の発生により、TCSR\_0 の CMFA フラグが 1 にセットされたとき、ADTE ビットが 1 にセットされていれば、A/D 変換器に対して A/D 変換の開始を要求します。この時 A/D 変換器側で、8 ビットタイマの変換トリガが選択されていれば、A/D 変換が開始されます。

【注】 \* ユニット 0、1 のみ可能です。

#### 〔変更後〕

TMR\_0、TMR\_2 のコンペアマッチ A のみ、A/D 変換器を起動することができます。\*

コンペアマッチ A の発生により、TCSR の CMFA フラグが 1 にセットされたとき、ADTE ビットが 1 にセットされていれば、A/D 変換器に対して A/D 変換の開始を要求します。この時 A/D 変換器側で、8 ビットタイマの変換トリガが選択されていれば、A/D 変換が開始されます。

【注】 \* ユニット 0、1 のみ可能です。

発行日: 2009年03月11日

# <u>24.レジスター覧</u>

(1) 頁 24-9 「24.1 レジスタアドレス一覧」 の DTCER の記述から、DTCERG、DTCERH を削除します。

# 〔変更前〕

| レジスタ名称          | 略称     | ビット数 | アドレス    | モジュール | データ<br>バス幅 | アクセス<br>ステート数 |  |  |  |  |

|-----------------|--------|------|---------|-------|------------|---------------|--|--|--|--|

| ~ 説明省略(変更なし) ~  |        |      |         |       |            |               |  |  |  |  |

| DTC イネーブルレジスタ E | DTCERE | 16   | H'FFF28 | INTC  | 16         | 2Ιφ /3Ιφ      |  |  |  |  |

| DTC イネーブルレジスタ G | DTCERG | 16   | H'FFF2C | INTC  | 16         | 21 /31        |  |  |  |  |

| DTC イネーブルレジスタ H | DTCERH | 16   | H'FFF2E | INTC  | 16         | 21 /31        |  |  |  |  |

| DTC コントロールレジスタ  | DTCCR  | 8    | H'FFF30 | INTC  | 16         | 2Ιφ /3Ιφ      |  |  |  |  |

| ~ 説明省略(変更なし) ~  |        |      |         |       |            |               |  |  |  |  |

## 〔変更後〕

| レジスタ名称          | 略称           | ビット数 | アドレス    | モジュール | データ<br>バス幅 | アクセス<br>ステート数 |  |  |  |  |  |

|-----------------|--------------|------|---------|-------|------------|---------------|--|--|--|--|--|

|                 | ~説明省略(変更なし)~ |      |         |       |            |               |  |  |  |  |  |

| DTC イネーブルレジスタ E | DTCERE       | 16   | H'FFF28 | INTC  | 16         | 2Ιφ/3Ιφ       |  |  |  |  |  |

| DTC コントロールレジスタ  | DTCCR        | 8    | H'FFF30 | INTC  | 16         | 2Ιφ/3Ιφ       |  |  |  |  |  |

| ~説明省略(変更なし)~    |              |      |         |       |            |               |  |  |  |  |  |

(2) 頁 24-25 「24.2 レジスタビット一覧」 の INTC モジュールの記述から、DTCERG、DTCERH を削除します。

# 〔変更前〕

| レジスタ    | ビット            | ビット            | ビット        | ビット        | ビット        | ビット        | ビット       | ビット       | モジュール   |  |  |  |

|---------|----------------|----------------|------------|------------|------------|------------|-----------|-----------|---------|--|--|--|

| 略称      | 31/23/15/7     | 30/22/14/6     | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1 | 24/16/8/0 |         |  |  |  |

|         |                | ~ 説明省略(変更なし) ~ |            |            |            |            |           |           |         |  |  |  |

| DTCERA~ |                |                |            | ~説明省略(3    | 变更なし) ~    |            |           |           | INTC    |  |  |  |

| DTCERD  |                |                |            |            |            |            |           |           |         |  |  |  |

| DTCERE  | _              | -              | DTCEE13    | DTCEE12    | -          | _          | _         | -         |         |  |  |  |

|         | _              | -              | -          | -          | -          | -          | _         | -         |         |  |  |  |

| DTCERG  |                |                |            |            | DTCEG11    | DTCEG10    |           |           | _       |  |  |  |

|         | DTCEG7         | DTCEG6         |            |            |            |            |           |           | _       |  |  |  |

| DTCERH  | DTCEH15        | DTCEH14        |            |            |            |            |           |           |         |  |  |  |

|         |                |                |            |            |            |            |           |           |         |  |  |  |

| DTCCR   | -              | -              | -          | RRS        | RCHNE      | -          | -         | ERR       |         |  |  |  |

| INTCR~  | ~ 説明省略(変更なし) ~ |                |            |            |            |            |           |           |         |  |  |  |

| ISR     |                |                |            |            |            |            |           |           |         |  |  |  |

|         | -              | -              | -          | ~説明省略(変    | 变更なし) ~    | -          |           |           | I/O ポート |  |  |  |

# 〔変更後〕

| レジスタ    | ビット            | ビット        | ビット        | ビット        | ビット        | ビット        | ビット       | ビット       | モジュール   |  |

|---------|----------------|------------|------------|------------|------------|------------|-----------|-----------|---------|--|

| 略称      | 31/23/15/7     | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1 | 24/16/8/0 |         |  |

|         | ~ 説明省略(変更なし) ~ |            |            |            |            |            |           |           |         |  |

| DTCERA~ | ~ 説明省略(変更なし) ~ |            |            |            |            |            |           |           |         |  |

| DTCERD  |                |            |            |            |            |            |           |           |         |  |

| DTCERE  | _              | _          | DTCEE13    | DTCEE12    | -          | _          | _         | -         |         |  |

|         | -              | -          | -          | -          | -          | -          | -         | -         |         |  |

| DTCCR   | -              | -          | -          | RRS        | RCHNE      | -          | _         | ERR       | -       |  |

| INTCR ~ |                |            |            | ~説明省略(変    | 変更なし) ~    |            |           |           |         |  |

| ISR     |                |            |            |            |            |            |           |           |         |  |

|         |                |            |            | ~説明省略(変    | 变更なし) ~    |            |           |           | I/O ポート |  |

発行日: 2009年03月11日

(3) 頁 24-37 「24.3 各動作モードにおけるレジスタの状態」 の INTC モジュールの記述から、DTCERG、DTCERH を削除

# 〔変更前〕

します。

| レジスタ    | リセット | モジュール          | スリープ | 全モジュール      | ソフトウェア | ハードウェア | モジュール   |  |  |  |

|---------|------|----------------|------|-------------|--------|--------|---------|--|--|--|

| 略称      |      | ストップ           | モード  | クロック        | スタンバイ  | スタンバイ  |         |  |  |  |

|         |      | 状態             |      | ストップモード     | モード    | モード    |         |  |  |  |

|         |      |                | ~ 説  | 明省略(変更なし) ~ |        |        | TPU_5   |  |  |  |

| DTCERA~ |      |                | ~ 説  | 明省略(変更なし) ~ |        |        | INTC    |  |  |  |

| DTCERD  |      |                |      |             |        |        |         |  |  |  |

| DTCERE  | 初期化  | -              | -    | -           | -      | 初期化    |         |  |  |  |

| DTCERG  | 初期化  |                |      |             |        | 初期化    | _       |  |  |  |

| DTCERH  | 初期化  |                |      |             |        | 初期化    | _       |  |  |  |

| DTCCR   | 初期化  | _              | -    | _           | _      | 初期化    | _       |  |  |  |

| INTCR ~ |      | ~ 説明省略(変更なし) ~ |      |             |        |        |         |  |  |  |

| ISR     |      |                |      |             |        |        |         |  |  |  |

|         |      |                | ~ 説  | 明省略(変更なし) ~ |        |        | I/O ポート |  |  |  |

# 〔変更後〕

| レジスタ    | リセット                 | モジュール          | スリープ | 全モジュール     | ソフトウェア | ハードウェア | モジュール   |  |  |  |

|---------|----------------------|----------------|------|------------|--------|--------|---------|--|--|--|

| 略称      |                      | ストップ           | モード  | クロックストップ   | スタンバイ  | スタンバイ  |         |  |  |  |

|         |                      | 状態             |      | モード        | モード    | モード    |         |  |  |  |

|         | ~ 説明省略(変更なし) ~       |                |      |            |        |        |         |  |  |  |

| DTCERA~ |                      | ~ 説明省略(変更なし) ~ |      |            |        |        |         |  |  |  |

| DTCERD  |                      |                |      |            |        |        | _       |  |  |  |

| DTCERE  | 初期化                  | -              | -    | -          | -      | 初期化    |         |  |  |  |

| DTCCR   | 初期化                  | -              | -    | -          | -      | 初期化    |         |  |  |  |

| INTCR ~ | INTCR~ ~ 説明省略(変更なし)~ |                |      |            |        |        |         |  |  |  |

| ISR     |                      |                |      |            |        |        |         |  |  |  |

|         |                      |                | ~ 説  | 明省略(変更なし)~ |        |        | I/O ポート |  |  |  |

発行日: 2009年03月11日