# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

Date: Feb.26.2004

# **RENESAS TECHNICAL UPDATE**

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Renesas Technology Corp.

| Product<br>Category   | MPU&MCU                                                                      | Document No.            | TN-H8*-263A/EA                        |                                                            | Rev. | 1.0 |

|-----------------------|------------------------------------------------------------------------------|-------------------------|---------------------------------------|------------------------------------------------------------|------|-----|

| Title                 | Correction of Errors Concerning the I<br>the SCI in the H8S/2168 Group and H | Information<br>Category | Correction or Supplement of Documents |                                                            |      |     |

| Applicable<br>Product | 7700 04 60 7700 04 67                                                        | Lot No.                 | Deferre                               | H8S/2168 Group Hardware Manual<br>REJ09B0078-0200Z Rev.2.0 |      |     |

|                       | H8S/2168, H8S/2167,<br>H8S/2166, and H8S/2158                                | All                     | Reference<br>Document                 | H8S/2158 Hardware Manual<br>ADE-602-255A Rev.2.0           |      |     |

Thank you for your consistent patronage of Renesas semiconductor products.

We would like to inform you of the correction of errors concerning the IrDA function of the serial communication interface (SCI, IrDA, and CRC) in the H8S/2168 Group Hardware Manual and H8S/2158 Hardware Manual as shown below.

The descriptions of the phase inversion function of the IrDA in the serial communication interface (SCI, IrDA, and CRC) are deleted.

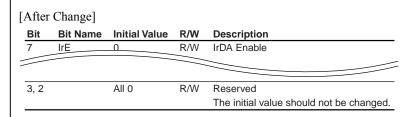

**Correction 1:** Section 14.3.10, Serial Interface Control Register (SCICR), in the H8S/2168 Group Hardware Manual [Before Change]

| Bit | Bit Name | Initial Value | R/W | Description                                                |

|-----|----------|---------------|-----|------------------------------------------------------------|

| 7   | IrF      | 0             | P/W | IrDA Enable                                                |

|     |          |               |     |                                                            |

| 3   | IrTxINV  | 0             | R/W | IrTx Data Invert                                           |

|     |          |               |     | Specifies the inversion of the logic level of the output   |

|     |          |               |     | from IrTxD. When the inversion is specified, IrCKS2 to     |

|     |          |               |     | IrCKS0 specify the low-level width, not the high-level     |

|     |          |               |     | width.                                                     |

|     |          |               |     | 0: Transmit data is output from IrTxD as it is             |

|     |          |               |     | 1: Transmit data is inverted before being output from      |

|     |          |               |     | IrTxD                                                      |

| 2   | IrRxINV  | 0             | R/W | IrRx Data Invert                                           |

|     |          |               |     | Specifies the inversion of the logic level of the input to |

|     |          |               |     | IrRxD. When the inversion is specified, IrCKS2 to          |

|     |          |               |     | IrCKS0 specify the low-level width, not the high-level     |

|     |          |               |     | width.                                                     |

|     |          |               |     | 0: Input to IrRxD is used as receive data as it is         |

|     |          |               |     | 1: Input to IrRxD is inverted before being used as         |

|     |          |               |     | receive data                                               |

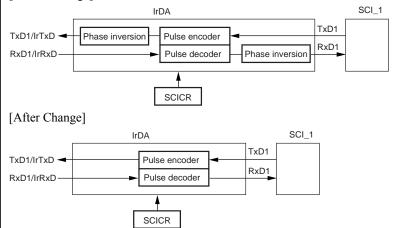

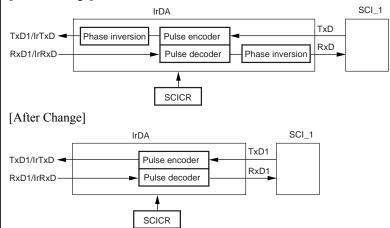

**Correction 2:** Figure 14.36, IrDA Block Diagram, in the H8S/2168 Group Hardware Manual [Before Change]

Correction 3: Transmission in section 14.8, IrDA Operation, in the H8S/2168 Group Hardware Manual

#### [Before Change]

For serial data of level 0, a high-level pulse having a width of 3/16 of the bit rate (1-bit interval) is output (initial setting).

The high-level pulse can be selected using the IrCKS2 to IrCKS0 bits in SCICR. The output waveform can also be inverted using the IrTxINV bit in SCICR.

The high-level pulse width is defined...

#### [After Change]

For serial data of level 0, a high-level pulse having a width of 3/16 of the bit rate (1-bit interval) is output (initial setting).

The high-level pulse can be selected using the IrCKS2 to IrCKS0 bits in SCICR.

The high-level pulse width is defined...

## Correction 4: Reception in section 14.8, IrDA Operation, in the H8S/2168 Group Hardware Manual

## [Before Change]

During reception, IR frames are converted to UART frames using the IrDA interface before inputting to SCI\_1. Here, the input waveform can also be inverted using the IrRxINV bit in SCICR.

Data of level 0 is output each time...

Date: Feb.26.2004

[After Change]

During reception, IR frames are converted to UART frames using the IrDA interface before inputting to SCI\_1. Data of level 0 is output each time...

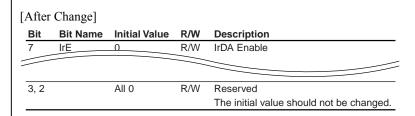

**Correction 5:** Section 24.2, Register Bits, in the H8S/2168 Group Hardware Manual [Before Change]

Register

| Abbreviation                             | n Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1 | Bit 0 | Module |

|------------------------------------------|---------|--------|--------|--------|---------|---------|-------|-------|--------|

| SCICR                                    | IrE     | IrCKS2 | IrCKS1 | IrCKS0 | IrTxINV | IrRxINV | _     | _     | SCI_1  |

| [After Change<br>Register<br>Abbreviatio | -       | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1 | Bit 0 | Module |

| SCICR                                    | IrE     | IrCKS2 | IrCKS1 | IrCKS0 | _       | _       | _     | _     | SCI_1  |

**Correction 6:** Section 16.3.10, Serial Interface Control Register (SCICR), in the H8S/2158 Hardware Manual [Before Change]

| Bit | Bit Name | Initial Value | R/W  | Description                                                |

|-----|----------|---------------|------|------------------------------------------------------------|

| 7   | IrF      | ^             | D/\/ | IrDA Enable                                                |

|     |          |               |      |                                                            |

| 3   | IrTxINV  | 0             | R/W  | IrTx Data Invert                                           |

|     |          |               |      | Specifies the inversion of the logic level of the output   |

|     |          |               |      | from IrTxD. When the inversion is specified, IrCKS2 to     |

|     |          |               |      | IrCKS0 specify the low-level width, not the high-level     |

|     |          |               |      | width.                                                     |

|     |          |               |      | 0: Transmit data is output from IrTxD as it is             |

|     |          |               |      | 1: Transmit data is inverted before being output from      |

|     |          |               |      | IrTxD                                                      |

| 2   | IrRxINV  | 0             | R/W  | IrRx Data Invert                                           |

|     |          |               |      | Specifies the inversion of the logic level of the input to |

|     |          |               |      | IrRxD. When the inversion is specified, IrCKS2 to          |

|     |          |               |      | IrCKS0 specify the low-level width, not the high-level     |

|     |          |               |      | width.                                                     |

|     |          |               |      | 0: Input to IrRxD is used as receive data as it is         |

|     |          |               |      | 1: Input to IrRxD is inverted before being used as         |

|     |          |               |      | receive data                                               |

Date: Feb.26.2004

**Correction 7:** Figure 16.36, IrDA Block Diagram, in the H8S/2158 Hardware Manual [Before Change]

Correction 8: Transmission in section 16.8, IrDA Operation, in the H8S/2158 Hardware Manual

[Before Change]

For serial data of level 0, a high-level pulse having a width of 3/16 of the bit rate (1-bit interval) is output (initial setting).

The high-level pulse can be selected using the IrCKS2 to IrCKS0 bits in SCICR. The output waveform can also be inverted using the IrTxINV bit in SCICR.

The high-level pulse width is defined...

[After Change]

For serial data of level 0, a high-level pulse having a width of 3/16 of the bit rate (1-bit interval) is output (initial setting).

The high-level pulse can be selected using the IrCKS2 to IrCKS0 bits in SCICR.

The high-level pulse width is defined...

Correction 9: Reception in section 16.8, IrDA Operation, in the H8S/2158 Hardware Manual

[Before Change]

During reception, IR frames are converted to UART frames using the IrDA interface before inputting to SCI\_1. Here, the input waveform can also be inverted using the IrRxINV bit in SCICR.

Data of level 0 is output each time...

Date: Feb.26.2004

Date: Feb.26.2004

[After Change]

$During\ reception, IR\ frames\ are\ converted\ to\ UART\ frames\ using\ the\ IrDA\ interface\ before\ inputting\ to\ SCI\_1.$

Data of level 0 is output each time...

Correction 10: Section 28.2, Register Bits, in the H8S/2158 Hardware Manual

[Before Change]

| Red | ais | ter |

|-----|-----|-----|

| 1/6 | чы  | LCI |

| Abbreviation Bit 7                     |     | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1 | Bit 0 | Module |

|----------------------------------------|-----|--------|--------|--------|---------|---------|-------|-------|--------|

| SCICR                                  | IrE | IrCKS2 | IrCKS1 | IrCKS0 | IrTxINV | IrRxINV | _     | _     | SCI_1  |

| [After Chang<br>Register<br>Abbreviati |     | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1 | Bit 0 | Module |

| SCICR                                  | IrE | IrCKS2 | IrCKS1 | IrCKS0 | _       | _       | _     | _     | SCI_1  |