Date: May. 16, 2013

## RENESAS TECHNICAL UPDATE

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                                              |         | Document<br>No.         | TN-RX*-A063A/E                                                                        | Rev. | 1.00         |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------|---------------------------------------------------------------------------------------|------|--------------|

| Title                 | Change in the RX63N group and RX631 Group User's Manual concerning the sub-clock oscillator of the 64pin products of the RX631 group |         | Information<br>Category | Technical Notification                                                                |      |              |

| Applicable<br>Product | RX631 Group<br>(R5F5631PCDFM, R5F5631PDDFM,<br>R5F5631NCDFM, R5F5631NDDFM,<br>R5F5631MCDFM, R5F5631MDDFM)                            | Lot No. |                         | RX63N Group, RX631 Group User's<br>Manual: Hardware<br>Rev. 1.60<br>(R01UH0041EJ0160) |      | ser's        |

|                       |                                                                                                                                      | All     | Reference<br>Document   |                                                                                       |      | <b>56. 5</b> |

This technical update is inform you that some description about the sub-clock oscillator of 64pin products have been added to the User's Manual of the RX63N group and RX631 group, Hardware version Rev.1.60, as indicated below.

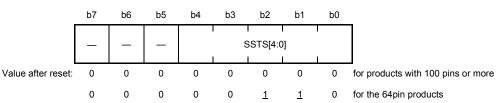

- 1. The following description about how to specify the initial value and sub-clock oscillator wait time select bit (SSTS[4:0] bits) of the 64pin products has been added the chapter of "11.2.8 Sub-Clock Oscillator Wait Control Register (SOSCWTCR)." The portion added is identified by underlining.

- · Initial value of the sub-clock oscillator wait control register (SOSCWTCR)

Address(es): 0008 00A3h

· How to specify the sub-clock oscillator wait time select bit (SSTS[4:0] bits) of the 64pin products

For the 64pin products, set the SSTS[4:0] bits so that the waiting time is at least as long as the sub-clock oscillator stabilization time (tSUBOSC).

Exampmle: When oscillation is at 32.768kHz and crystal resonator is to be used after 2s (=2000ms) of stabilization time

To satisfy the relation waiting time ≥tSUBOSC × fSUB = 2000[ms] × 32.768[kHz] = 65536[cycles], set the SSTS[4:0]

bits to 01100b (65536 cycles).

2. The description about calculating the sub-clock oscillation stabilization wait time (tSUBOSCWT) of the 64pin products has been added to the section of "Table 50.12 Clock Timing (Sub-Clock Related)" as indicated below. The portion added is identified by underlining.

For the 64pin products, the number of cycles n selected by the value of the SOSCWTCR.SSTS[4:0] bits determines the sub-clock oscillation stabilization waiting time in accord with the formula below.