Date: Feb. 28, 2017

# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                      |            | Document<br>No.         | TN-RZ*-A023A/E                                         | Rev.      | 1.00   |  |  |

|-----------------------|----------------------------------------------|------------|-------------------------|--------------------------------------------------------|-----------|--------|--|--|

| Title                 | Additional explanation for EthernetAVB of RZ | //G Series | Information<br>Category | Technical Notification                                 |           |        |  |  |

|                       |                                              | Lot No.    |                         |                                                        |           |        |  |  |

| Applicable<br>Product | RZ/G Series<br>RZ/G1H, M, N and E            | All lots   | Reference<br>Document   | RZ/G Series User's Ma<br>Rev.1.00<br>(R01UH0543EJ0100) | anual: Ha | rdware |  |  |

There is a following additional explanation about the RZ/G series products.

#### [Summary]

RZ/G Series User's manual: hardware correction for EthernetAVB.

Since some registers and bits used in the sample driver are not disclosed in the user's manual, add those information to the manual additionally.

#### [Products]

RZ/G1H, M, N and E

#### [Note]

There is no specification change (Definition is cleared).

[Additional Explanation]

(Following gray highlighted parts (abcd) are corrected or newly added.)

Section 37A EthernetAVB

## 37A.2 Register Descriptions

- Table 37A.4 Configuration of E-MAC-related Registers

Current (from):

RZ/G Series Products

| Name                                             | Abbreviation | R/W | Address     | Initial Value | Access<br>Size | RZ/G1H    | RZ/G1M    | RZ/G1N    | RZ/G1E   |

|--------------------------------------------------|--------------|-----|-------------|---------------|----------------|-----------|-----------|-----------|----------|

| E-MAC mode register                              | ECMR         | R/W | H'E680 0500 | H'0000 0000   | 32             | $\sqrt{}$ | $\sqrt{}$ | V         | V        |

| Receive frame length register                    | RFLR         | R/W | H'E680 0508 | H'0000 0000   | 32             | <b>V</b>  | <b>V</b>  | <b>V</b>  | √        |

| E-MAC status register                            | ECSR         | R/W | H'E680 0510 | H'0000 0000   | 32             | <b>V</b>  | <b>V</b>  | <b>V</b>  | √        |

| E-MAC interrupt permission register              | ECSIPR       | R/W | H'E680 0518 | H'0000 0000   | 32             | 1         | 1         | <b>V</b>  | <b>V</b> |

| PHY interface register                           | PIR          | R/W | H'E680 0520 | H'0000 0000   | 32             | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | V        |

| PHY Status Register                              | PSR          | R   | H'E680 0528 | H'0000 0000   | 32             | $\sqrt{}$ | $\sqrt{}$ | <b>V</b>  | 1        |

| PHY_INT Polarity Register                        | PIPR         | R/W | H'E680 052C | H'0000 0000   | 32             | $\sqrt{}$ | $\sqrt{}$ | <b>V</b>  | √        |

| Manual PAUSE frame register                      | MPR          | R/W | H'E680 0558 | H'0000 0000   | 32             | $\sqrt{}$ | $\sqrt{}$ | <b>V</b>  | √        |

| PAUSE frame transmit counter                     | PFTCR        | R   | H'E680 055C | H'0000 0000   | 32             | <b>V</b>  | <b>V</b>  | <b>V</b>  | √        |

| PAUSE frame receive counter                      | PFRCR        | R   | H'E680 0560 | H'0000 0000   | 32             | $\sqrt{}$ | $\sqrt{}$ | <b>V</b>  | 1        |

| EthernetAVB Mode Register                        | GECMR        | R/W | H'E680 05B0 | H'0000 0000   | 32             | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | V        |

| E-MAC address high register                      | MAHR         | R/W | H'E680 05C0 | H'0000 0000   | 32             | $\sqrt{}$ | $\sqrt{}$ | <b>V</b>  | 1        |

| E-MAC address low register                       | MALR         | R/W | H'E680 05C8 | H'0000 0000   | 32             | $\sqrt{}$ | $\sqrt{}$ | <b>V</b>  | √        |

| CRC error frame receive counter register         | CEFCR        | R/W | H'E680 0740 | H'0000 0000   | 32             | <b>V</b>  | <b>V</b>  | <b>V</b>  | <b>V</b> |

| Frame receive error counter register             | FRECR        | R/W | H'E680 0748 | H'0000 0000   | 32             | <b>V</b>  | <b>V</b>  | <b>V</b>  | <b>√</b> |

| Too-short frame receive counter register         | TSFRCR       | R/W | H'E680 0750 | H'0000 0000   | 32             | <b>V</b>  | <b>V</b>  | <b>V</b>  | <b>V</b> |

| Too-long frame receive counter register          | TLFRCR       | R/W | H'E680 0758 | H'0000 0000   | 32             | <b>V</b>  | <b>V</b>  | <b>V</b>  | <b>√</b> |

| Residual-bit frame receive counter register      | RFCR         | R/W | H'E680 0760 | H'0000 0000   | 32             | √         | √         | <b>V</b>  | <b>V</b> |

| Multicast address frame receive counter register | MAFCR        | R/W | H'E680 0778 | H'0000 0000   | 32             | √         | √         | <b>V</b>  | <b>√</b> |

Correction (to):

RZ/G Series Products

|                                     |              |     |             |               | Access | G1H       | G1M       | G1N       | G1E   |

|-------------------------------------|--------------|-----|-------------|---------------|--------|-----------|-----------|-----------|-------|

| Name                                | Abbreviation | R/W | Address     | Initial Value | Size   | RZ/G1     | RZ/G1     | RZ/G1     | RZ/G1 |

| E-MAC mode register                 | ECMR         | R/W | H'E680 0500 | H'0000 0000   | 32     | $\sqrt{}$ | $\sqrt{}$ | $\sqrt{}$ | √     |

| Receive frame length register       | RFLR         | R/W | H'E680 0508 | H'0000 0000   | 32     | √         | <b>V</b>  | <b>V</b>  | √     |

| E-MAC status register               | ECSR         | R/W | H'E680 0510 | H'0000 0000   | 32     | √         | <b>V</b>  | <b>V</b>  | √     |

| E-MAC interrupt permission register | ECSIPR       | R/W | H'E680 0518 | H'0000 0000   | 32     | 1         | √         | √         | V     |

| PHY interface register              | PIR          | R/W | H'E680 0520 | H'0000 0000   | 32     | <b>V</b>  | <b>V</b>  | <b>V</b>  | √     |

| PHY Status Register                 | PSR          | R   | H'E680 0528 | H'0000 0000   | 32     | √         | <b>V</b>  | <b>V</b>  | √     |

#### RZ/G Series Products

| Name                                             | Abbreviation | R/W | Address     | Initial Value | Access<br>Size | RZ/G1H    | RZ/G1M   | RZ/G1N   | RZ/G1E       |

|--------------------------------------------------|--------------|-----|-------------|---------------|----------------|-----------|----------|----------|--------------|

| PHY_INT Polarity Register                        | PIPR         | R/W | H'E680 052C | H'0000 0000   | 32             | $\sqrt{}$ | <b>V</b> | <b>V</b> | √            |

| Manual PAUSE frame register                      | MPR          | R/W | H'E680 0558 | H'0000 0000   | 32             | $\sqrt{}$ | <b>V</b> | 1        | √            |

| PAUSE frame transmit counter                     | PFTCR        | R   | H'E680 055C | H'0000 0000   | 32             | $\sqrt{}$ | <b>V</b> | 1        | √            |

| PAUSE frame receive counter                      | PFRCR        | R   | H'E680 0560 | H'0000 0000   | 32             | <b>V</b>  | <b>V</b> | 1        | √            |

| EthernetAVB Mode Register                        | GECMR        | R/W | H'E680 05B0 | H'0000 0000   | 32             | <b>V</b>  | <b>V</b> | 1        | √            |

| E-MAC address high register                      | MAHR         | R/W | H'E680 05C0 | H'0000 0000   | 32             | <b>V</b>  | <b>V</b> | 1        | √            |

| E-MAC address low register                       | MALR         | R/W | H'E680 05C8 | H'0000 0000   | 32             | √         | <b>V</b> | <b>V</b> | √            |

| Transmit retry over counter register             | TROCR        | R/W | H'E680 0700 | H'0000 0000   | 32             | V         | V        | V        | $\checkmark$ |

| CRC error frame receive counter register         | CEFCR        | R/W | H'E680 0740 | H'0000 0000   | 32             | <b>V</b>  | <b>V</b> | √        | √            |

| Frame receive error counter register             | FRECR        | R/W | H'E680 0748 | H'0000 0000   | 32             | 1         | 1        | <b>V</b> | √            |

| Too-short frame receive counter register         | TSFRCR       | R/W | H'E680 0750 | H'0000 0000   | 32             | <b>V</b>  | <b>V</b> | <b>V</b> | √            |

| Too-long frame receive counter register          | TLFRCR       | R/W | H'E680 0758 | H'0000 0000   | 32             | <b>V</b>  | <b>V</b> | <b>V</b> | √            |

| Residual-bit frame receive counter register      | RFCR         | R/W | H'E680 0760 | H'0000 0000   | 32             | √         | √        | √        | √            |

| Multicast address frame receive counter register | MAFCR        | R/W | H'E680 0778 | H'0000 0000   | 32             | √         | √        | <b>V</b> | √            |

#### Section number

Current (from):

- 37A.2.61 CRC Error Frame Receive Counter Register (CEFCR)

- 37A.2.62 Frame Receive Error Counter Register (FRECR)

- 37A.2.63 Too-Short Frame Receive Counter Register (TSFRCR)

- 37A.2.64 Too-Long Frame Receive Counter Register (TLFRCR)

- 37A.2.65 Residual-Bit Frame Receive Counter Register (RFCR)

- 37A.2.66 Multicast Address Frame Receive Counter Register (MAFCR)

#### Correction (to):

- 37A.2.61 Transmit retry over counter register (TROCR) -> new chapter; description at end of this document

- 37A.2.62 CRC Error Frame Receive Counter Register (CEFCR)

- 37A.2.63 Frame Receive Error Counter Register (FRECR)

- 37A.2.64 Too-Short Frame Receive Counter Register (TSFRCR)

- 37A.2.65 Too-Long Frame Receive Counter Register (TLFRCR)

- 37A.2.66 Residual-Bit Frame Receive Counter Register (RFCR)

- 37A.2.67 Multicast Address Frame Receive Counter Register (MAFCR)

#### **Description for updated registers**

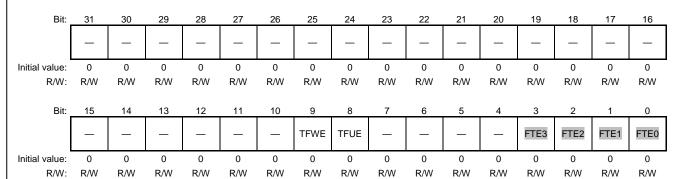

37A.2.37 Transmit Interrupt Control Register (TIC)

### Current (from):

| Bit:           | 31  | 30  | 29  | 28  | 27  | 26  | 25   | 24   | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|----------------|-----|-----|-----|-----|-----|-----|------|------|-----|-----|-----|-----|-----|-----|-----|-----|

|                | _   | _   | _   | _   | _   |     | _    |      | _   | _   | _   | _   | _   | -   | -   | -   |

| Initial value: | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W:           | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

|                |     |     |     |     |     |     |      |      |     |     |     |     |     |     |     |     |

| Bit:           | 15  | 14  | 13  | 12  | 11  | 10  | 9    | 8    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|                | _   | _   | _   | _   | _   | _   | TFWE | TFUE | _   | _   | _   | _   | _   | _   | _   | _   |

| Initial value: | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W:           | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Bit      | Bit Name | Initial Value | R/W | Description                                                                                                 |

|----------|----------|---------------|-----|-------------------------------------------------------------------------------------------------------------|

| 31 to 10 | _        | All 0         | R/W | Reserved                                                                                                    |

|          |          |               |     | These bits are read as 0. The write value should be 0.                                                      |

| 9        | TFWE     | 0             | R/W | Time Stamp FIFO Warning Interrupt Enable                                                                    |

|          |          |               |     | When the time-stamp FIFO reaches the warning level while the interrupt is enabled, the interrupt is issued. |

|          |          |               |     | 0: Disabled                                                                                                 |

|          |          |               |     | 1: Enabled                                                                                                  |

| 8        | TFUE     | 0             | R/W | Time Stamp FIFO Update Interrupt Enable                                                                     |

|          |          |               |     | When the time-stamp FIFO is updated while the interrupt is enabled, the interrupt is issued.                |

|          |          |               |     | 0: Disabled                                                                                                 |

|          |          |               |     | 1: Enabled                                                                                                  |

| 7 to 0   | _        | All 0         | R/W | Reserved                                                                                                    |

|          |          |               |     | These bits are read as 0. The write value should be 0.                                                      |

#### Correction (to):

| Bit      | Bit Name | Initial Value | R/W | Description                                                                                                 |

|----------|----------|---------------|-----|-------------------------------------------------------------------------------------------------------------|

| 31 to 10 | _        | All 0         | R/W | Reserved                                                                                                    |

|          |          |               |     | These bits are read as 0. The write value should be 0.                                                      |

| 9        | TFWE     | 0             | R/W | Time Stamp FIFO Warning Interrupt Enable                                                                    |

|          |          |               |     | When the time-stamp FIFO reaches the warning level while the interrupt is enabled, the interrupt is issued. |

|          |          |               |     | 0: Disabled                                                                                                 |

|          |          |               |     | 1: Enabled                                                                                                  |

| Bit    | Bit Name | Initial Value | R/W | Description                                                                                  |

|--------|----------|---------------|-----|----------------------------------------------------------------------------------------------|

| 8      | TFUE     | 0             | R/W | Time Stamp FIFO Update Interrupt Enable                                                      |

|        |          |               |     | When the time-stamp FIFO is updated while the interrupt is enabled, the interrupt is issued. |

|        |          |               |     | 0: Disabled                                                                                  |

|        |          |               |     | 1: Enabled                                                                                   |

| 7 to 4 | _        | All 0         | R/W | Reserved                                                                                     |

|        |          |               |     | These bits are read as 0. The write value should be 0.                                       |

| 3      | FTE3     | 0             | R/W | Frame Transmitted interrupt Enable 3                                                         |

|        |          |               |     | While this bit is 1b an interrupt will be generated when <b>TIS.FTF3</b> is 1b.              |

|        |          |               |     | 0: Disabled                                                                                  |

|        |          |               |     | 1: Enabled                                                                                   |

| 2      | FTE2     | 0             | R/W | Frame Transmitted interrupt Enable 2                                                         |

|        |          |               |     | While this bit is 1b an interrupt will be generated when <b>TIS.FTF2</b> is 1b.              |

|        |          |               |     | 0: Disabled                                                                                  |

|        |          |               |     | 1: Enabled                                                                                   |

| 1      | FTE1     | 0             | R/W | Frame Transmitted interrupt Enable 1                                                         |

|        |          |               |     | While this bit is 1b an interrupt will be generated when <b>TIS.FTF1</b> is 1b.              |

|        |          |               |     | 0: Disabled                                                                                  |

|        |          |               |     | 1: Enabled                                                                                   |

| 0      | FTE0     | 0             | R/W | Frame Transmitted interrupt Enable 0                                                         |

|        |          |               |     | While this bit is 1b an interrupt will be generated when <b>TIS.FTF0</b> is 1b.              |

|        |          |               |     | 0: Disabled                                                                                  |

|        |          |               |     | 1: Enabled                                                                                   |

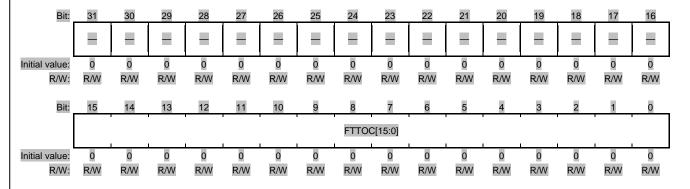

## 37A.2.38 Transmit Interrupt Status Register (TIS)

## Current (from):

| Bit:           | 31  | 30  | 29  | 28  | 27  | 26  | 25   | 24   | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|----------------|-----|-----|-----|-----|-----|-----|------|------|-----|-----|-----|-----|-----|-----|-----|-----|

|                | l   |     | l   | _   |     | l   | _    |      | l   | _   | l   | l   |     | l   | l   | _   |

| Initial value: | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W:           | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

|                |     |     |     |     |     |     |      |      |     |     |     |     |     |     |     |     |

| Bit:           | 15  | 14  | 13  | 12  | 11  | 10  | 9    | 8    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|                |     |     | l   | _   |     | l   | TFWF | TFUF | l   |     | l   | l   |     | l   | l   | _   |

| Initial value: | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W:           | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

|                |     |     |     |     |     |     |      |      |     |     |     |     |     |     |     |     |

| l | Bit      | Bit Name | Initial Value | R/W | Description                                            |

|---|----------|----------|---------------|-----|--------------------------------------------------------|

| l | 31 to 10 | _        | All 0         | R/W | Reserved                                               |

|   |          |          |               |     | These bits are read as 0. The write value should be 0. |

| Bit                           | Bit          | Name                | In                  | itial Va | llue     | R/W      | Desc                                                                                                                                                | cription                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                              |                                                         |                                              |                                          |                                        |                                          |                                            |                     |

|-------------------------------|--------------|---------------------|---------------------|----------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------|----------------------------------------------|------------------------------------------|----------------------------------------|------------------------------------------|--------------------------------------------|---------------------|

| 9                             | TFV          | ۷F                  | 0                   |          |          | R/W      | Time                                                                                                                                                | Stamp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FIFO                                           | Warnin                                                  | g Interr                                     | upt Sta                                  | atus                                   |                                          |                                            |                     |

|                               |              |                     |                     |          |          |          |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | cates the warning                              |                                                         |                                              | ission t                                 | ime-sta                                | amp FIF                                  | O has                                      |                     |

|                               |              |                     |                     |          |          |          | Only                                                                                                                                                | 0 can l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | oe writt                                       | en to th                                                | ne bit.                                      |                                          |                                        |                                          |                                            |                     |

|                               |              |                     |                     |          |          |          | [Con                                                                                                                                                | ditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | for Cha                                        | anging]                                                 |                                              |                                          |                                        |                                          |                                            |                     |

|                               |              |                     |                     |          |          |          |                                                                                                                                                     | mode<br>trans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | and w                                          | hen the<br>figurati                                     | e time s<br>on con                           | stamp F<br>trol reg                      | TIFO er<br>ister (T                    | nable bi<br>CCR.T                        | not oper<br>t in the<br>FEN) is            | 0.                  |

|                               |              |                     |                     |          |          |          | <ul> <li>The bit is set to 1 after a frame including DESC<br/>has been transmitted and one entry has already<br/>in the time-stamp FIFO.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |                                                         |                                              |                                          |                                        |                                          |                                            |                     |

|                               |              |                     |                     |          |          |          | 0: Th                                                                                                                                               | e inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | rupt is r                                      | not pen                                                 | ding.                                        |                                          |                                        |                                          |                                            |                     |

|                               |              |                     |                     |          |          |          | 1: The time-stamp FIFO has reached the warning level.                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |                                                         |                                              |                                          |                                        |                                          |                                            |                     |

| 8                             | TFL          | JF                  | 0                   |          |          | R/W      | Time Stamp FIFO Update Interrupt Status                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |                                                         |                                              |                                          |                                        |                                          |                                            |                     |

|                               |              |                     |                     |          |          |          |                                                                                                                                                     | This bit indicates that the transmission time-stamp FIFO has beer updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                |                                                         |                                              |                                          |                                        |                                          |                                            | been                |

|                               |              |                     |                     |          |          |          | Only                                                                                                                                                | 0 can l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | oe writt                                       | en to th                                                | ne bit.                                      |                                          |                                        |                                          |                                            |                     |

|                               |              |                     |                     |          |          |          | [Con                                                                                                                                                | ditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | for Cha                                        | anging]                                                 |                                              |                                          |                                        |                                          |                                            |                     |

|                               |              |                     |                     |          |          |          | _                                                                                                                                                   | configure is writed configure in the configure is configure in the configure in the configure is configure in the configure in the configure in the configure is configure in the configure in the configure in the configure is configure in the configuration in the con | guration<br>tten to t<br>guration<br>pit is se | n contro<br>the time<br>n contro<br>t to 1 w<br>N) is 1 | ol registe stampol registry then the after a | ter (TC<br>o FIFO<br>ter (TC<br>e time s | CR.TFI<br>release<br>CR.TFI<br>stamp F | EN) is (<br>e bit in t<br>R).<br>FIFO er | the trar ), and v the tran hable bi CR.TSF | /hen /<br>smit<br>t |

|                               |              |                     |                     |          |          |          | 0: Th                                                                                                                                               | e interi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | upt is r                                       | not pen                                                 | ding.                                        |                                          |                                        |                                          |                                            |                     |

|                               |              |                     |                     |          |          |          | 1: Th                                                                                                                                               | e time-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | stamp                                          | FIFO h                                                  | as bee                                       | n upda                                   | ted.                                   |                                          |                                            |                     |

| 7 to 0                        | _            |                     | Α                   | II O     |          | R/W      | Rese                                                                                                                                                | erved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                |                                                         |                                              |                                          |                                        |                                          |                                            |                     |

|                               |              |                     |                     |          |          |          | Thes                                                                                                                                                | e bits a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | are read                                       | d as 0.                                                 | The wr                                       | ite valu                                 | e shou                                 | ld be 0                                  | •                                          |                     |

| Correction<br>Bit:            | (to):        | 30                  | 29                  | 28       | 27       | 26       | 25                                                                                                                                                  | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23                                             | 22                                                      | 21                                           | 20                                       | 19                                     | 18                                       | 17                                         | 16                  |

|                               | _            | _                   | _                   | _        | _        | _        | _                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                              | _                                                       | _                                            | _                                        | _                                      | _                                        | _                                          | _                   |

|                               |              | 0                   | 0                   | 0        | 0        | 0        | 0                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                              | 0                                                       | 0                                            | 0                                        | 0                                      | 0                                        | 0                                          | 0                   |