発行日: 2013年6月20日

# **RENESAS TECHNICAL UPDATE**

〒211-8668 神奈川県川崎市中原区下沼部 1753 ルネサス エレクトロニクス株式会社

問合せ窓口 http://japan.renesas.com/contact/

E-mail: csc@renesas.com

| 製品分類 |      | MPU & MCU                                         | 発行番号   | TN-SH7-A861A/J |      | Rev. | 第1版 |

|------|------|---------------------------------------------------|--------|----------------|------|------|-----|

| 題名   |      | テートコントローラ(BSC)の MPX-I/O イン<br>ト拡張/ネゲート拡張サイクル説明の追加 | 情報分類   | 技術情報           |      |      |     |

| 適    |      |                                                   | 対象ロット等 |                |      |      |     |

| 用製品  | 下記参照 |                                                   | 全ロット   | 関連資料           | 下記参照 |      |     |

上記適用製品に内蔵されているバスステートコントローラ (BSC) の MPX-I/O インタフェースにおいて、アサート拡張サイクルおよびネゲート拡張サイクルの説明の追加がございますので連絡いたします。

以下、#は章番号、\$\$/mmは図番号を示し、各製品グループとの対応は下表になります。

| グループ                      | 章番号(#) | 図番号(\$\$)            | 図番号(mm) |

|---------------------------|--------|----------------------|---------|

| SH7206                    | 8      | 図 8.12、図 8.13、図 8.14 | 8.12    |

| SH7203                    | 9      | 図 9.11、図 9.12、図 9.13 | 9.11    |

| SH7263                    | 9      | 図 9.11、図 9.12、図 9.13 | 9.11    |

| SH7262, SH7264            | 9      | 図 9.11 ~ 図 9.13      | 9.11    |

| SH7211                    | 8      | 図 8.10 ~ 図 8.12      | 8.10    |

| SH7214, SH7216            | 9      | 図 9.11 ~ 図 9.13      | 9.11    |

| SH7231                    | 10     | 図 10.11 ~ 図 10.13    | 10.11   |

| SH7239, SH7237            | 9      | 図 9.10~図 9.12        | 9.10    |

| SH7285, SH7286,<br>SH7243 | 9      | 図 9.11 ~ 図 9.13      | 9.11    |

### 1. レジスタ説明の変更

#.4.3 CSn 空間ウェイトコントロールレジスタ (CSnWCR)

- (1) 通常空間、バイト選択付き SRAM、MPX-I/O

- · CS5WCR

| ビット   | ビット名      | 初期値    | R/W  | Bt 明                                                                   |

|-------|-----------|--------|------|------------------------------------------------------------------------|

|       |           | 107018 | 1011 |                                                                        |

| 12、11 | SW[1:0]   | 00     | R/W  | アドレス、CS5 アサート→ RD、WEn アサート遅延サイクル数                                      |

|       |           |        |      | 本ビットは、エリア5を通常空間、パイト選択付きSRAMに設定した                                       |

|       |           |        |      | 場合、アドレス、CS5アサートからRD、WEnアサートまでの遅延<br> サイクル数を指定します。                      |

|       |           |        |      | エリア5を MPX-I/Oに設定した場合、アドレスサイクル(Ta3)終了                                   |

|       |           |        |      | から、RD、WEnアサートまでの遅延サイクル数を指定します。<br>  00:0.5 サイクル                        |

|       |           |        |      |                                                                        |

|       |           |        |      | 01:1.5 サイクル                                                            |

|       |           |        |      | 10:2.5 サイクル                                                            |

|       |           |        |      | 11:3.5 サイクル                                                            |

| 4 0   | 1,0454.03 |        | 5    | THE THE ALL I WAS A STREET LINES AND A STREET                          |

| 1, 0  | HW[1:0]   | 00     | R/W  | RD、WEn ネゲート→ アドレス、CS5 ネゲート遅延サイクル数                                      |

|       |           |        |      | 本ビットは、エリア5を通常空間、バイト選択付きSRAMに設定した<br> 場合、 RD、WEnネゲートから、アドレス、CS5ネゲートまでの遅 |

|       |           |        |      | 延サイクル数を指定します。                                                          |

|       |           |        |      | エリア5を MPX-1/0に設定した場合、 RD、WEnネゲートから、<br>CS5ネゲートまでの遅延サイクル数を指定します。        |

|       |           |        |      | 00:0.5 サイクル                                                            |

|       |           |        |      | 01:1.5 サイクル                                                            |

|       |           |        |      | 10:25サイクル                                                              |

## 2. 動作説明への追加

#.5.5 MPX-I/O インタフェース

データサイクルは、通常空間アクセスと同一のサイクルとなります。

11:3.5 サイクル

SW[1:0]の遅延サイクルは、 $Ta3 \ge T1$ サイクルの間に挿入されます。HW[1:0]の遅延サイクルは T2サイクルの後に付加されます。

タイミングチャートを \$\$ に示します。

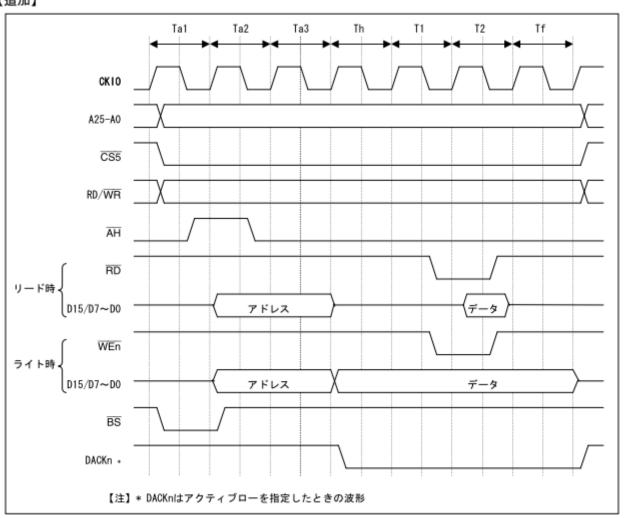

# 【追加】

mm (2) MPX空間アクセスタイミング (アドレスサイクルノーウェイト、アサート拡張サイクル1.5、データサイクルノーウェイト、ネゲート拡張サイクル1.5)

### 適用製品および関連資料

| グループ                   | 関連資料                                          | Rev.     | 管理番号            |

|------------------------|-----------------------------------------------|----------|-----------------|

| SH7206                 | SH7206 グループユーザーズマニュアル ハードウェア編                 | Rev.4.00 | R01UM0283JJ0400 |

| SH7203                 | SH7203 グループハードウェアマニュアル                        | Rev.3.00 | RJJ09B0341-0300 |

| SH7263                 | SH7263 グループハードウェアマニュアル                        | Rev.3.00 | RJJ09B0284-0300 |

| SH7262, SH7264         | SH7262 グループ、SH7264 グループ<br>ユーザーズマニュアル ハードウェア編 | Rev.3.00 | R01UH0134JJ0300 |

| SH7211                 | SH7211 グループハードウェアマニュアル                        | Rev.3.00 | RJJ09B0338-0300 |

| SH7214、SH7216          | SH7214 グループ、SH7216 グループユーザーズマニュアル ハードウェア編)    | Rev.3.00 | R01UH0230JJ0300 |

| SH7231                 | SH7231 グループ ユーザーズマニュアル ハードウェア編                | Rev.2.00 | R01UH0073JJ0200 |

| SH7239, SH7237         | SH7239 グループ、SH7237 グループユーザーズマニュアル ハードウェア編     | Rev.1.00 | R01UH0086JJ0100 |

| SH7285, SH7286, SH7243 | SH7280 グループ、SH7243 グループユーザーズマニュアル ハードウェア編     | Rev.3.00 | R01UH0229JJ0300 |

以上

発行日: 2013年6月20日