# intersil

# ISL72814SEH, ISL73814SEH

Total Dose Test Report

## Introduction

This report documents the results of low and high dose rate total dose testing of the <u>ISL72814SEH</u> and <u>ISL73814SEH</u> 16-channel current drivers. The results also include post-irradiation high temperature biased annealing. The tests were conducted to provide an assessment of the total dose hardness of the parts and to determine any dose rate, bias or anneal sensitivity. Parts were irradiated under bias and with all pins grounded at Low Dose Rate (LDR) to 100krad(Si) and at High Dose Rate (HDR) to 150krad(Si). Both irradiations were followed by high temperature biased anneal. The ISL72814SEH is rated at 100krad(Si) at HDR (50 - 300rad(Si)/s) and at 75krad(Si) at LDR (0.01rad(Si)/s) and is acceptance tested on a wafer-by-wafer basis to the SMD limits. The ISL73814SEH is rated at 75krad(Si) at LDR (0.01rad(Si)/s) and is acceptance tested on a wafer-by-wafer basis to the SMD limits.

## **Part Description**

The ISL72814SEH and ISL73814SEH (ISL7x814SEH) are radiation hardened, high-voltage, high-current, driver circuit ICs fabricated using the Renesas proprietary PR40 Silicon-On-Insulator (SOI) process technology to mitigate single event effects. The devices integrate 16 driver channels that feature a high-voltage (42V), high-current (700mA) open-emitter PNP output stage.

To further reduce solution size, the ISL7x814SEH integrates a 4-bit, 16-channel decoder with Enable. This conveniently allows you to select 1 of 16 available driver channels or disable all channels. The inputs to the decoder are TTL and CMOS compatible to allow an easy interface to FPGAs and microprocessors.

The ISL7x814SEH devices operate across the military temperature range from -55°C to +125°C and are available in a 28 Ld hermetically sealed Ceramic Dual Flatpack (CDFP) package or die.

#### **Related Literature**

For a full list of related documents, visit our website:

• ISL72814SEH, ISL73814SEH device pages

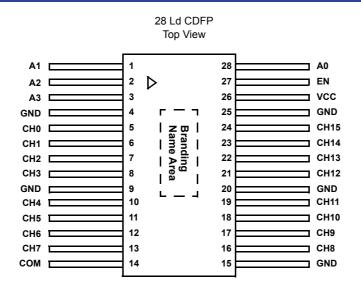

Note: The ESD triangular mark is indicative of Pin #1. It is a part of the device marking and is placed on the lid in the quadrant where Pin #1 is located.

#### Figure 1. ISL7x814SEH Pinout Configuration

| Table 1. | ISL7x814SEH Pin Descriptions |

|----------|------------------------------|

|----------|------------------------------|

| Pin Number                  | Pin Name    | Description                                                                                                                                                                                                                                                          |

|-----------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-3, 28                     | Ax          | Address lines for the decoder.                                                                                                                                                                                                                                       |

| 4, 9, 15, 20, 25            | GND         | Supply and output driver ground. Connect this pin to the PCB ground plane.                                                                                                                                                                                           |

| 5-8, 10-13, 16-19,<br>21-24 | CHx         | Channels 0 through 15 open emitter PNP outputs.                                                                                                                                                                                                                      |

| 14                          | СОМ         | ESD Clamp rail. It can be used to terminate inductances connected to the CHx pins and should be tied to the highest relay coil supply rail in the system. When not switching inductive loads, tie it to the supply rail of the CHx channel with the highest voltage. |

| 26                          | VCC         | Bias supply for the decoder and the level shift circuit. Connect to a voltage between 3V to 13.2V.                                                                                                                                                                   |

| 27                          | EN          | Active high enable input to the decoder.                                                                                                                                                                                                                             |

| -                           | Package lid | Internally connected to GND (Pin 15).                                                                                                                                                                                                                                |

## 1. Test Description

#### 1.1 Irradiation Facilities

High Dose Rate (HDR) testing was performed at 187.16rad(Si)/s using a Gammacell 220 industry standard irradiator located in the Renesas facility in Palm Bay, Florida. Low Dose Rate (LDR) testing was performed at 0.01rad(Si)/s using the Renesas Palm Bay Hopewell Designs N40 panoramic irradiator. The LDR irradiator uses PbAI spectrum hardening filters to shield the test board and devices under test against low energy secondary gamma radiation. Half of the samples were biased and half had all pins grounded during irradiation. Samples from both dose rates underwent post-irradiation anneal at +100°C for 168 hours in a small temperature chamber.

#### 1.2 Test Fixturing

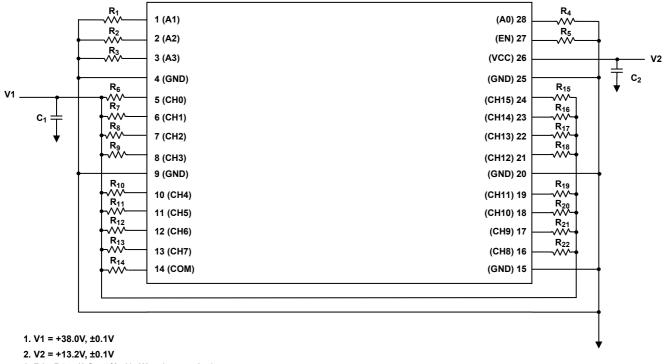

<u>Figure 2</u> shows the configuration used for biased irradiation at both dose rates and the biased anneal. Note that the part is biased at  $V_{CC}$  = 13.2V with the channels biased at 38V.

3. R1 - R5 = 1kΩ, ±5%, 1/4 Watt (per socket) 4. R6 - R22 = 38k, ±5%, 1/4 Watt

5. Socket is 28 Ld Pin Flatpack (Sensata 628-0282315)

#### Figure 2. ISL7x814SEH TID Bias Schematic

#### 1.3 Characterization Equipment and Procedures

All electrical testing was performed at room temperature outside the irradiator using production Automated Test Equipment (ATE) with data-logging at each downpoint.

#### 1.4 Experimental Matrix

Irradiation was performed in accordance with the guidelines of MIL-STD-883 Test Method 1019. The experimental matrix consisted of 10 samples irradiated at LDR under bias and 10 samples irradiated at LDR with all pins grounded; and 6 samples irradiated at HDR under bias and 6 samples irradiated at HDR with all pins grounded. All 20 LDR samples underwent biased anneal samples. Due to board size limitations, only six samples from the HDR matrix could be annealed at a time, so four biased and two unbiased samples were randomly chosen to include in the biased anneal. Three control units were used for both types of irradiation.

The ISL7x814SEH samples were from wafer lots XCT0D and XCP6D. All samples were packaged in the 28 Ld ceramic flatpack package (package code K28.A). Samples were processed through the standard burn-in cycle before irradiation.

#### 1.5 Downpoints

Downpoints for the LDR tests were 0, 10, 30, 50, 75, and 100krad(Si). Downpoints for the HDR tests were 0, 30, 50, 100, and 150krad(Si). Both exposures were followed by a 168 hour +100°C anneal under bias.

# 2. Test Results

## 2.1 Attributes Data

Total dose testing of the ISL7x814SEH is complete. All tested parameters passed the SMD limits. <u>Table 2</u> summarizes the results.

| Table 2. ISL7x814SEH Total Dose Test | Attributes Data |

|--------------------------------------|-----------------|

|--------------------------------------|-----------------|

|                       |                               |             |                 | _                      |      |

|-----------------------|-------------------------------|-------------|-----------------|------------------------|------|

| Dose Rate (rad(Si)/s) | Bias                          | Sample Size | Downpoint       | Pass ( <u>Note 1</u> ) | Fail |

| 0.01                  | Biased<br>( <u>Figure 2</u> ) | 10          | Pre-irradiation | 10                     | 0-   |

|                       | ( <u>rigure z</u> )           |             | 10krad(Si)      | 10                     | 0    |

|                       |                               |             | 30krad(Si)      | 10                     | 0    |

|                       |                               |             | 50krad(Si)      | 10                     | 0    |

|                       |                               |             | 75krad(Si)      | 10                     | 0    |

|                       |                               |             | 100krad(Si)     | 10                     | 0    |

|                       |                               |             | Anneal          | 10                     | 0    |

| 0.01                  | Grounded                      | 10          | Pre-irradiation | 10                     |      |

|                       |                               |             | 10krad(Si)      | 10                     | 0    |

|                       |                               |             | 30krad(Si)      | 10                     | 0    |

|                       |                               |             | 50krad(Si)      | 10                     | 0    |

|                       |                               |             | 75krad(Si)      | 10                     | 0    |

|                       |                               |             | 100krad(Si)     | 10                     | 0    |

|                       |                               |             | Anneal          | 10                     | 0    |

| 187.16                | Biased<br>( <u>Figure 2</u> ) | 6           | Pre-irradiation | 6                      |      |

|                       |                               |             | 30krad(Si)      | 6                      | 0    |

|                       |                               |             | 50krad(Si)      | 6                      | 0    |

|                       |                               |             | 100krad(Si)     | 6                      | 0    |

|                       |                               |             | 150krad(Si)     | 6                      | 0    |

|                       |                               |             | Anneal          | 4                      | 0    |

| 187.16                | Grounded                      | 6           | Pre-irradiation | 6                      |      |

|                       |                               |             | 30krad(Si)      | 6                      | 0    |

|                       |                               |             | 50krad(Si)      | 6                      | 0    |

|                       |                               |             | 100krad(Si)     | 6                      | 0    |

|                       |                               |             | 150krad(Si)     | 6                      | 0    |

|                       |                               |             | Anneal          | 2                      | 0    |

Note:

1. 'Pass' indicates a sample that passes all SMD limits.

## 2.2 Key Parameter Listing

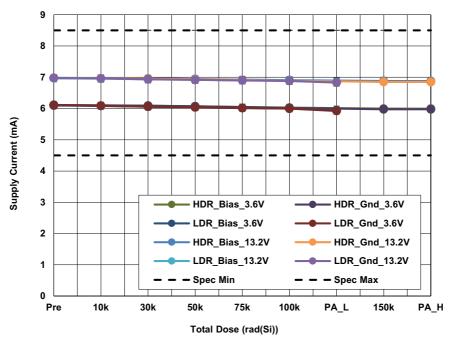

<u>Table 3</u> lists the SMD parameters that are considered indicative of part performance. These parameters are plotted in <u>Figures 3</u> through <u>20</u>. All limits are taken from the ISL7x814SEH SMD; see the SMD <u>59102-18221</u> for further detail on test conditions.

| Figure    | Parameter                                                                            | Symbol               | Limit (Low) | Limit (High) | Unit |

|-----------|--------------------------------------------------------------------------------------|----------------------|-------------|--------------|------|

| <u>3</u>  | Supply current                                                                       | I <sub>CC</sub>      | 4.5         | 8.5          | mA   |

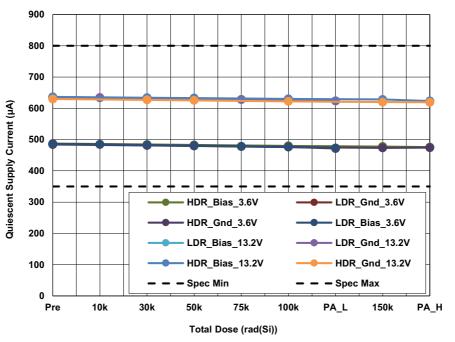

| <u>4</u>  | Quiescent supply current                                                             | I <sub>CCQ</sub>     | 350         | 800          | μA   |

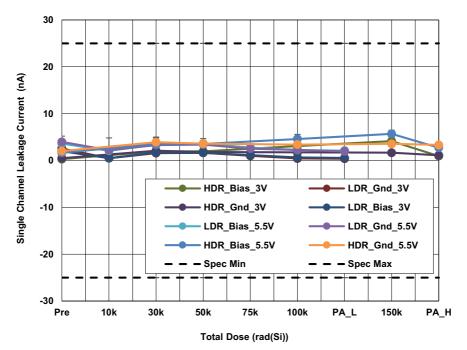

| <u>5</u>  | Single channel leakage current                                                       | I <sub>CHLK</sub>    | -25         | 25           | nA   |

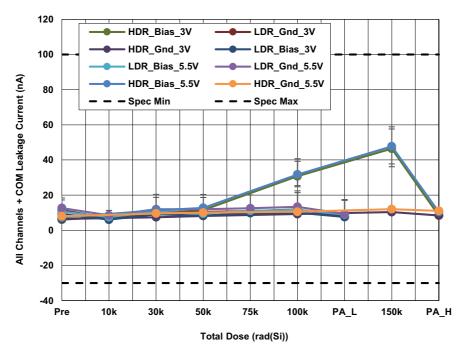

| <u>6</u>  | All channels + COM leakage current                                                   | I <sub>TOTCHLK</sub> | -30         | 100          | nA   |

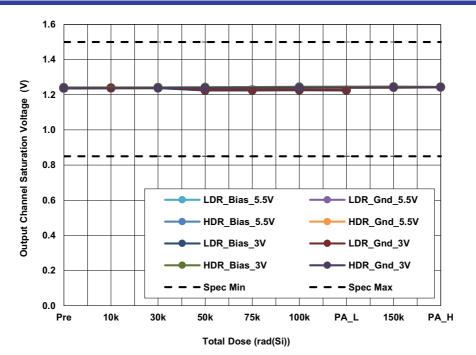

| <u>7</u>  | Output channel saturation voltage (I <sub>CHx</sub> = 700mA)                         | V <sub>CH(SAT)</sub> | 0.85        | 1.5          | V    |

| <u>8</u>  | Output channel saturation voltage (I <sub>CHx</sub> = 600mA)                         |                      | 0.8         | 1.4          |      |

| <u>9</u>  | Output channel saturation voltage (I <sub>CHx</sub> = 500mA)                         |                      | 0.65        | 1.35         |      |

| <u>10</u> | Output channel saturation voltage (I <sub>CHx</sub> = 350mA)                         |                      | 0.6         | 1.3          |      |

| <u>11</u> | Output channel saturation voltage (I <sub>CHx</sub> = 200mA)                         |                      | 0.5         | 1.2          |      |

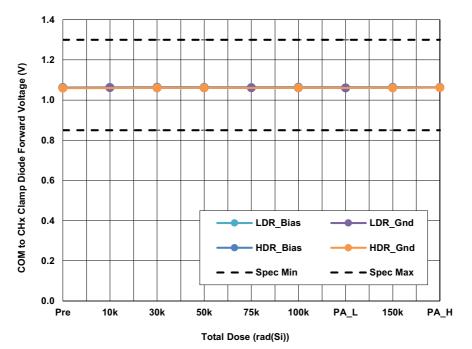

| <u>12</u> | COM to CHx Inductive kickback clamp diode forward voltage (I <sub>CHx</sub> = 200mA) | V <sub>F</sub>       | 0.85        | 1.3          | V    |

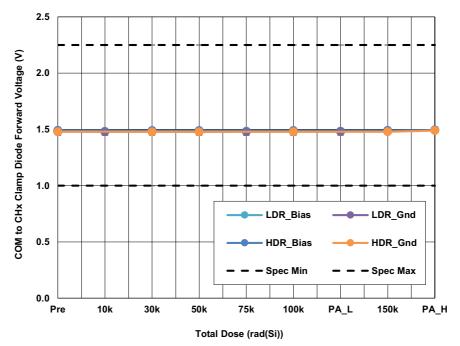

| <u>13</u> | COM to CHx Inductive kickback clamp diode forward voltage (I <sub>CHx</sub> = 700mA) |                      | 1.0         | 2.25         |      |

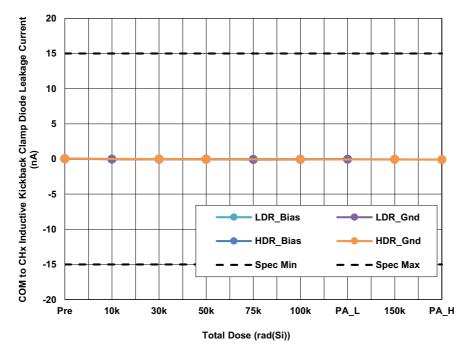

| <u>14</u> | COM to CHx inductive kickback clamp diode leakage current                            | I <sub>R</sub>       | -15         | 15           | nA   |

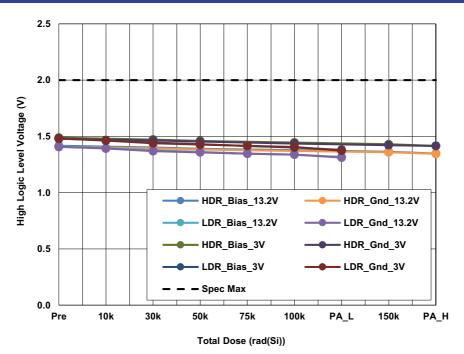

| <u>15</u> | High logic level voltage                                                             | V <sub>IH</sub>      | 2           | -            | V    |

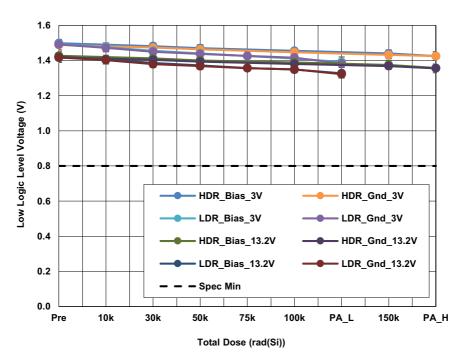

| <u>16</u> | Low logic level voltage                                                              | V <sub>IL</sub>      | -           | 0.8          | V    |

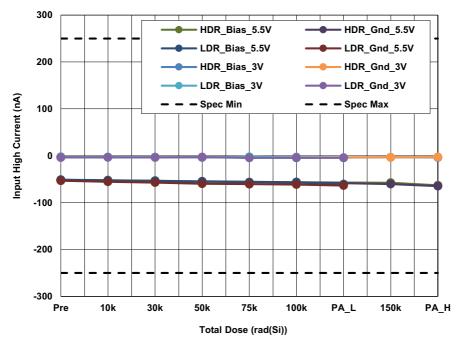

| <u>17</u> | Input high current                                                                   | I <sub>IH</sub>      | -250        | 250          | nA   |

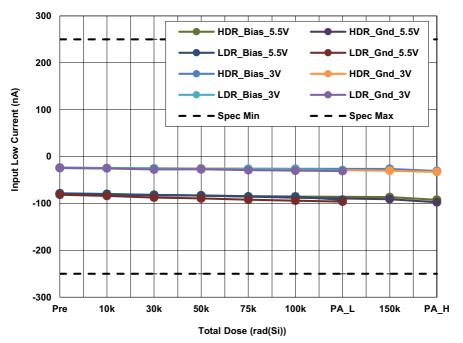

| <u>18</u> | Input low current                                                                    | I <sub>IL</sub>      | -250        | 250          | nA   |

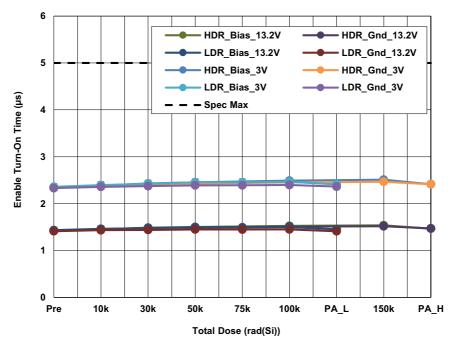

| <u>19</u> | Enable Turn-On Time                                                                  | t <sub>EN</sub>      | -           | 5            | μs   |

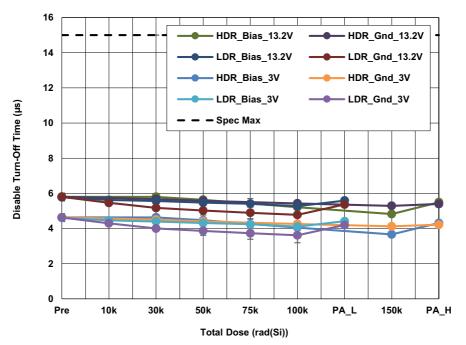

| <u>20</u> | Disable Turn-Off Time                                                                | t <sub>DIS</sub>     | -           | 15           | μs   |

| Table 3. | ISL7x814SEH SMD To | otal Dose Parameters | $(T_A = +25^{\circ}C)$ |

|----------|--------------------|----------------------|------------------------|

|----------|--------------------|----------------------|------------------------|

## 2.3 Key Parameter Variables Data

The plots in Figures 3 through 20 illustrate the TID response of the SMD parameters outlined in Key Parameter Listing. The plots show the average tested values of the parameters as a function of total dose for each of the irradiation conditions, biased and grounded, at LDR and HDR. For example, the legend HDR\_Bias indicates the average HDR response for biased parts. On the x-axis, along with the total dose, PA\_L and PA\_H represent the post-anneal LDR and HDR points, respectively. The plots also include error bars at each downpoint that represent the minimum and maximum measured values of the samples, although in some plots the error bars might not be visible due to their values compared to the scale of the graph.

Figure 4. ISL7x814SEH quiescent supply current ( $I_{CCQ}$ ) at  $V_{CC}$  = 3.6V and 13.2V, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are 350µA minimum and 800µA maximum.

Figure 5. ISL7x814SEH single channel leakage current ( $I_{CHLK}$ ) at  $V_{CC}$  = 3V and 5.5V, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are -25nA minimum and 25nA maximum.

Figure 6. ISL7x814SEH all channels + COM leakage current ( $I_{TOTCHLK}$ ) at  $V_{CC}$  = 3V and 5.5V, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are -30nA minimum and 100nA maximum.

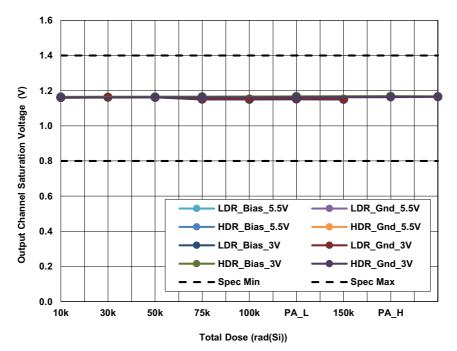

Figure 7. ISL7x814SEH output channel saturation voltage ( $V_{CH(Sat)}$ ) at  $V_{CC}$  = 3V and 5.5V, with  $I_{CHx}$  = 700mA, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are 0.85V minimum and 1.50V maximum.

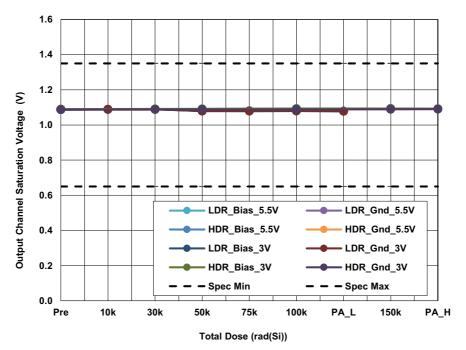

Figure 8. ISL7x814SEH output channel saturation voltage ( $V_{CH(Sat)}$ ) at  $V_{CC}$  = 3V and 5.5V, with  $I_{CHx}$  = 600mA, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are 0.80V minimum and 1.40V maximum.

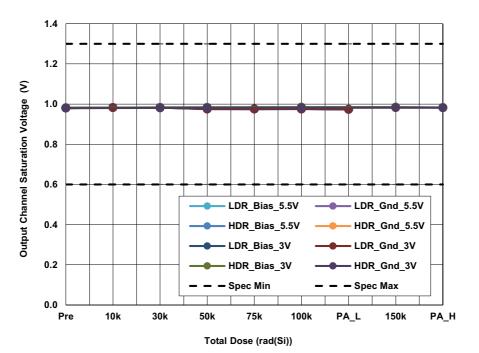

Figure 9. ISL7x814SEH output channel saturation voltage ( $V_{CH(Sat)}$ ), at  $V_{CC}$  = 3V and 5.5V, with  $I_{CHx}$  = 500mA, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are 0.65V minimum and 1.35V maximum.

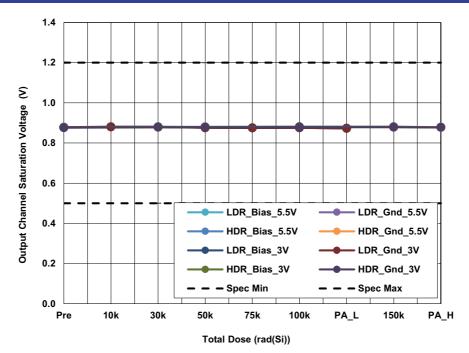

Figure 10. ISL7x814SEH output channel saturation voltage ( $V_{CH(Sat)}$ ), at  $V_{CC}$  = 3V and 5.5V, with  $I_{CHx}$  = 350mA, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are 0.60V minimum and 1.30V maximum.

Figure 11. ISL7x814SEH output channel saturation voltage ( $V_{CH(Sat)}$ ), at  $V_{CC}$  = 3V and 5.5V, with  $I_{CHx}$  = 200mA, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are 0.50V minimum and 1.20V maximum.

Figure 12. ISL7x814SEH COM to CHx clamp diode forward voltage ( $V_F$ ), with  $I_{CHx}$  = 200mA, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are 0.85V minimum and 1.30V maximum.

Figure 13. ISL7x814SEH COM to CHx clamp diode forward voltage ( $V_F$ ) with  $I_{CHx}$  = 700mA, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are 1.0V minimum and 2.25V maximum.

Figure 14. ISL7x814SEH COM to CHx inductive kickback clamp diode leakage current ( $I_R$ ) as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are -15nA minimum and 15nA maximum.

Figure 15. ISL7x814SEH high logic level voltage ( $V_{IH}$ ) at  $V_{CC}$  = 3V and 13.2V, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limit is 2.0V minimum.

Figure 16. ISL7x814SEH low logic level voltage ( $V_{IL}$ ) at  $V_{CC}$  = 3V and 13.2V, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limit is 0.8V maximum.

Figure 17. ISL7x814SEH input high current ( $I_{IH}$ ) at  $V_{CC}$  = 3V and 5.5V, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are -250nA minimum and 250nA maximum.

Figure 18. ISL7x814SEH input low current ( $I_{IL}$ ), at  $V_{CC}$  = 3V and 5.5V, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limits are -250nA minimum and 250nA maximum.

Figure 19. ISL7x814SEH enable turn-on time ( $t_{EN}$ ) at V<sub>CC</sub> = 3V and 13.2V, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limit is 5µs maximum.

Figure 20. ISL7x814SEH disable turn-off time ( $t_{DIS}$ ), at V<sub>CC</sub> = 3V and 13.2V, as a function of total dose irradiation at LDR and at HDR for biased and grounded configurations. The error bars (if visible) represent the minimum and maximum measured values. The post-irradiation SMD limit is 15µs maximum.

# 3. Discussion and Conclusion

We report the results of LDR and HDR total dose tests of the ISL7x814SEH 16 Channel Current Driver. Both irradiations were followed by a 168-hour anneal at +100°C under bias. All tested SMD parameters passed at all downpoints. No dose rate, bias, or anneal sensitivity was observed, although, as can be seen in Figure 6 on page 7, the total off-channel leakage current does increase after 50krad(Si) for the biased samples. However, the 150krad(Si) value is well below the 100nA limit and it returns to normal after the anneal. <u>"Attributes Data" on page 4</u> summarizes the attributes data for the test. <u>"Key Parameter Listing" on page 5</u> reviews the SMD parameters for the part. Finally <u>"Key Parameter Variables Data" on page 5</u> provides plots of the total dose response for the selected parameters.

# 4. Revision History

| Rev. | Date     | Description     |

|------|----------|-----------------|

| 0.00 | Mar.8.19 | Initial release |

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction prevention, appropriate treatment for aging design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas

- Electronics products. (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="http://www.renesas.com/contact/">www.renesas.com/contact/</a>