# intersil

## TEST REPORT

ISL71841SEH

Single Event Effects (SEE) Testing

#### TR007 Rev 0.00 June 12, 2015

#### Introduction

The intense proton and heavy ion environment encountered in space applications can cause a variety of Single Event Effects (SEE) in electronic circuitry, including Single Event Upset (SEU), Single Event Transient (SET), Single Event Functional Interrupt (SEFI), Single Event Gate Rupture (SEGR), and Single Event Burnout (SEB). SEE can lead to system-level performance issues including disruption, degradation and destruction. For predictable and reliable space system operation, individual electronic components should be characterized to determine their SEE response. This report discusses the results of SEE testing performed on the Intersil ISL71841SEH 32:1 analog multiplexer (MUX) designed for space applications.

## **Product Description**

The ISL71841SEHVF is a 32:1 analog multiplexer (MUX) that operates with supply voltages from  $\pm 10.8V$  to  $\pm 16.5V$  and input overvoltage capability to  $\pm 35V$ . The part is also "cold spare" capable; i.e., inputs of an unpowered part do not leak more than 1µA to  $\pm 35V$ . The ISL71841SEHVF is fabricated in a proprietary Intersil bonded wafer SOI BiCMOS process. The ISL71841SEHVF is a 32-Channel version of the ISL71840SEHVF, 16:1 analog MUX.

## **Product Documentation**

For more information about the ISL71841SEH, refer to the following documentation.

- Datasheets:

- <u>ISL71840SEH</u>, "Radiation Hardened 30V 16-Channel Analog Multiplexer"

- ISL71841SEH, "Radiation Hardened 30V 32-Channel Analog Multiplexer"

- Standard Microcircuit Drawing (SMD):

- <u>5962-15219</u> (ISL71840SEH)

- <u>5962-15220</u> (ISL72841SEH)

- Test Reports:

- TR004, "ISL71840SEH Single Event Effects (SEE) Testing of the ISL71840SEH 16:1 30V Mux"

## **SEE Test Objectives**

The ISL71841SEH was tested to determine its susceptibility to destructive single event effects (SEGR and SEB, collectively referred to by SEB herein) and to characterize its Single Event Transient (SET) behavior over various conditions and ion Linear Energy Transfer (LET) levels. The ISL71841SEH parts tested came from lot J67669.1, wafer #5 manufactured on Intersil's proprietary P6SOI process.

### **SEE Test Facility**

Testing was performed at the Texas A&M University (TAMU) Cyclotron Institute heavy ion facility. This facility is coupled to a K500 super-conducting cyclotron, which is capable of generating a wide range of test particles with the various energy, flux and fluence levels needed for advanced radiation testing. Details on the test facility can be found on the <u>TAMU</u> <u>Cyclotron website</u>. Testing was carried out on March 20, 2015 and May 30, 2015.

## **SEE Test Setup**

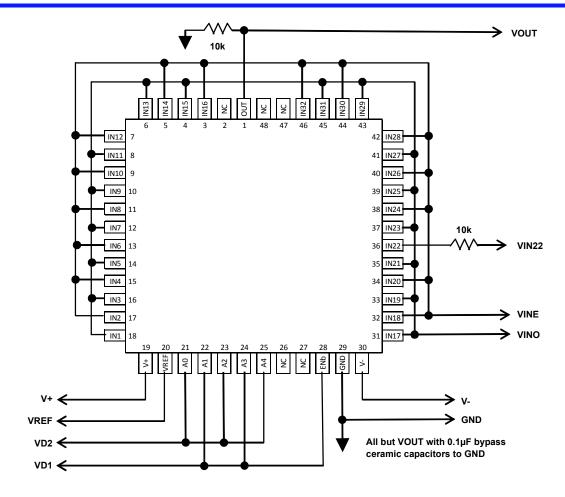

SEE testing is carried out with the sample in an active configuration. A schematic of the ISL71841SEH SEE test fixture is shown in Figure 1 on page 2. The test circuit is configured to accept variable supply voltages and two groupings of input voltages. The addressing of input IN22 is accomplished with VD1 low and VD2 high. With both VD1 and VD2 high the switches are all disabled. The output is set to half of VIN22-GND by a resistor divider formed from VIN22 to GND through VOUT. Of the remaining inputs, the odd numbered ones are connected to VINO and the even numbered ones are connected to VINE.

ISL71841SEH samples in standard ceramic flatpack packages without lids were assembled on boards that allowed two parts to be irradiated at one time. A 20-foot coaxial cable was used to connect the test fixture to a switch box in the control room which contained all of the monitoring equipment. The switch box allowed the two test circuits to be controlled and monitored remotely.

Digital multimeters were used to monitor pertinent voltages and currents. LeCroy waveRunner 4-Channel digital oscilloscopes were used to capture and store SET traces at VOUT that exceeded the oscilloscope's ±20mV AC trigger setting.

#### **SEE Damage (SEB) Testing**

For the destructive SEE (SEB) tests, conditions were selected to maximize the electrical and thermal stresses on the Device Under Test (DUT), thus insuring worst-case conditions. Two SEB tests were run with the conditions listed in Table 1. The supply voltages were set to the part's absolute maximum rating of  $\pm 20V$ . The input voltages were varied between  $\pm 17V$ , and  $\pm 35V$  to stress the switches at relevant conditions. Case temperature was maintained at  $\pm 125^{\circ}C \pm 10^{\circ}C$  by controlling the current flowing into a resistive heater bonded to the underside of the board. Four DUTs were irradiated with 2.954GeV Au ions at normal incidence resulting in a surface LET =  $86.4MeV \cdot cm^2/mg$ . The normal range into silicon for these Au ions after 30mm of air is about

118µm with a Bragg peak range of 53µm. More details can be found on the TAMU Cyclotron website. These conditions guaranteed ions transited all active device volume in this SOI process (about 10µm depth). Each irradiation was to a fluence of  $5x10^{6}$ ions/cm<sup>2</sup>. The currents into each of the voltage supplies was measured before and after each irradiation to look for changes indicative of permanent damage to the part.

As none of the supply currents reported in <u>Table 2</u> changed by more than measurement repeatability it is inferred that they indicate no damage occurred due to the exposure to the ions. Based on this, it is concluded that the part is immune to destructive SEE effects under the conditions tested in <u>Table 1</u>.

## TABLE 1. SEB CONDITIONS FOR TESTING THE ISL71841SEH. IRRADIATION WAS WITH 2.954 GeV Au AT 0° INCIDENCE FOR LET = 86.4MeV • cm<sup>2</sup>/mg TO A FLUENCE OF 5x10<sup>6</sup> lons/cm<sup>2</sup>.

|        |                                            |                           | -         |             |             |              |             |            |            |

|--------|--------------------------------------------|---------------------------|-----------|-------------|-------------|--------------|-------------|------------|------------|

|        | EFFECTIVE LET<br>(MeV-cm <sup>2</sup> /mg) | T <sub>CASE</sub><br>(°C) | V±<br>(V) | VINO<br>(V) | VINE<br>(V) | VIN22<br>(V) | VREF<br>(V) | VD1<br>(V) | VD2<br>(V) |

| Test 1 | 86.4 at 0°                                 | +125                      | ±20       | +17         | -17         | 0            | 20          | 0          | 20         |

| Test 2 | 86.4 at 0°                                 | +125                      | ±20       | +35         | -35         | 0            | 20          | 0          | 20         |

## TABLE 2. SEB MONITOR PARAMETERS FOR TESTING AT LET 0° = 86.4MeV • cm<sup>2</sup>/mg AND TCASE = +125°C. EACH IRRADIATION WAS TO A FLUENCE OF 5x106ions/cm<sup>2</sup>.

|      | MONITORED PAR            | AMETER | l+<br>(μΑ) | -<br>(μΑ) | IINO<br>(nA) | liNE<br>(nA) | IREF<br>(μA) | ID2<br>(nA) |

|------|--------------------------|--------|------------|-----------|--------------|--------------|--------------|-------------|

| DUT1 | T1 Test 1                | Pre    | 336        | 336       | 17           | 21           | 170          | 12          |

|      | -                        | Post   | 320        | 320       | 18           | 21           | 171          | 12          |

|      | Test 2                   | Pre    | 281        | 281       | 67           | 72           | 171          | 12          |

|      |                          | Post   | 281        | 281       | 63           | 74           | 171          | 12          |

| DUT2 | Test 1                   | Pre    | 310        | 310       | 10           | 20           | 168          | 14          |

|      | -                        | Post   | 310        | 310       | 11           | 22           | 168          | 14          |

| Test | Test 2                   | Pre    | 280        | 280       | 64           | 59           | 169          | 14          |

|      |                          | Post   | 280        | 280       | 64           | 64           | 169          | 14          |

| DUT3 | Test 1 ( <u>Note 1</u> ) | Pre    | 299        | 303       | 91           | 170          | 164          | 43          |

|      | -                        | Post   | 301        | 300       | 90           | 180          | 165          | 41          |

|      | Test 2                   | Pre    | 281        | 282       | 81           | 119          | 169          | 12          |

|      | -                        | Post   | 282        | 282       | 80           | 120          | 169          | 12          |

| DUT4 | Test 1 ( <u>Note 1</u> ) | Pre    | 303        | 302       | 75           | 51           | 165          | 61          |

|      |                          | Post   | 303        | 303       | 88           | 48           | 165          | 65          |

|      | Test 2                   | Pre    | 290        | 290       | 18           | 141          | 171          | 11          |

|      |                          | Post   | 291        | 291       | 18           | 122          | 172          | 11          |

NOTE:

1. Units tested in march 2015; other units tested in May 2015.

#### SET Testing of ISL71841SEH 32:1 Analog MUX

SET testing was done on four samples of the ISL71841SEH. Testing started with normal incidence gold (Au) at LET = 86.4MeV  $\cdot$  cm<sup>2</sup>/mg and with the SET detection threshold set to ±20mV deviation on V<sub>OUT</sub>. Three separate conditions, as shown in <u>Table 3</u>, were applied to each of the four parts tested. Tests 1 and 2 looked for SET on V<sub>OUT</sub> with IN22 selected, while Test 3 looked at V<sub>OUT</sub> with all switches disabled. Addressing inputs were put at the respective VIL and VIH levels to test for addressing upsets.

The first test, Test 1, tests the part operating at the bottom of the recommended supply voltage range,  $\pm 10.8$ V. The second test exercises the part at the maximum of the supply voltage range,  $\pm 16.5$ V. In both cases the VREF is set to the minimum of the recommended operating range of 4.5V to minimize the noise margin in the addressing circuits. The lower noise margins makes the addressing most susceptible to a SEE leading to an address change SET.

<u>Table 4</u> summarizes the SET counts for each test by DUT and then reports the nominal SET cross section for the complement of all four DUTs. The cross sections reported are the nominal found by dividing the event counts by the total fluence generating those counts.

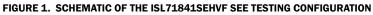

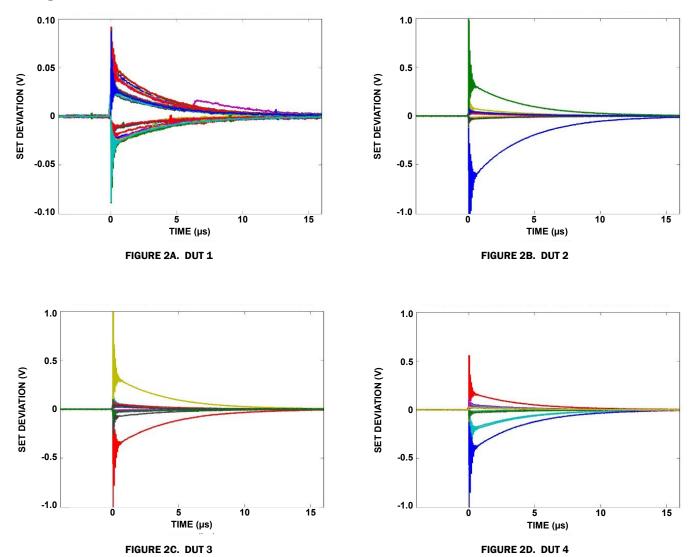

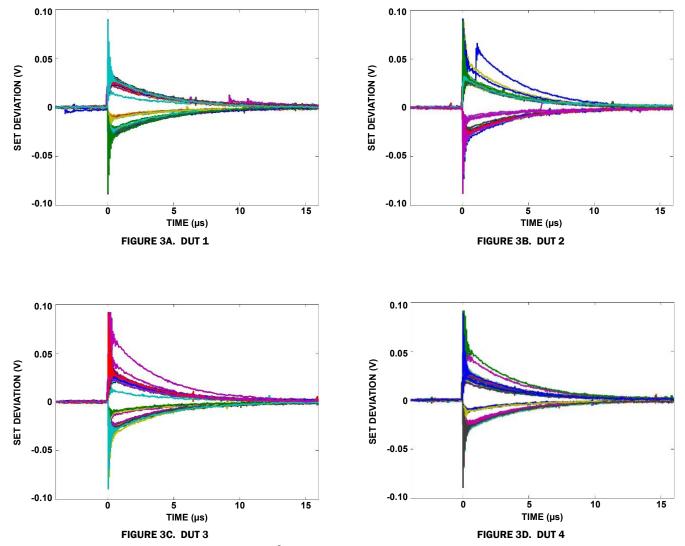

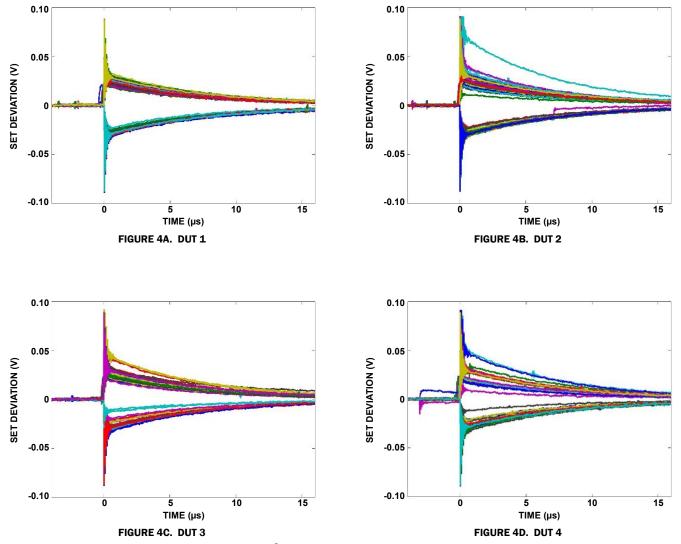

Post processing of the captured SET oscilloscope traces generated the composite plots in Figures 2, 3, and 4 for the LET = 86.4MeV • cm<sup>2</sup>/mg case. These plots show the composite of the 20 largest and 20 longest for each sense (positive and negative) of the extreme deviation so they reflect the worst 80 SET's observed in the run. Figures 2 and 3 show the SET with IN22 selected and connected to GND through both ends with 10k $\Omega$  resistors. Figure 4 shows the VOUT SET with all switches disabled.

In Figure 2 the vast bulk of the SET are less than 100mV, but for DUT2, 3, and 4 a handful of SET approaching 1V were recorded. In all cases the SET decayed away in about 15 $\mu$ s. These larger SET were not repeated under the conditions of Test 2 and Test 3 represented in Figures 3 and 4.

|        | V±<br>(V) | VREF<br>(V) | VD1<br>(V) | VD2<br>(V) | VINO<br>(V) | VINE<br>(V) | VIN22<br>(V) |

|--------|-----------|-------------|------------|------------|-------------|-------------|--------------|

| Test 1 | ±10.8     | 4.5         | 0.8        | 2.0        | +10.8       | -10.8       | 0            |

| Test 2 | ±16.5     | 4.5         | 0.8        | 2.0        | +16.5       | -16.5       | 0            |

| Test 3 | ±16.5     | 4.5         | 2.0        | 2.0        | +16.5       | -16.5       | 0            |

#### TABLE 3. THE ISL71841SEH SET TESTING CONDITIONS

TABLE 4.  $\pm 20$ mV SET COUNTS ON V<sub>OUT</sub> FOR TESTING OF THE ISL71841SEH. LET WAS 86.4MeV • cm<sup>2</sup>/mg AND FLUENCE OF 4x10<sup>6</sup>lons/cm<sup>2</sup> PER RUN

| TEST<br>CONFIGURATIONS | DUT1<br>±20mV<br>EVENT COUNTS | DUT2<br>±20mV<br>Event counts | DUT3<br>±20mV<br>EVENT COUNTS | DUT4<br>±20mV<br>EVENT COUNTS | TOTAL ±20mV<br>SET CROSS SECTION<br>(cm <sup>2</sup> ) |

|------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|--------------------------------------------------------|

| Test 1                 | 1584                          | 1564                          | 1865                          | 1712                          | 4.2E-04                                                |

| Test 2                 | 1739                          | 1606                          | 1913                          | 1738                          | 4.4E-04                                                |

| Test 3                 | 1643                          | 1801                          | 1915                          | 1681                          | 4.4E-04                                                |

#### **Composite Plots**

FIGURE 2. Composite plots of extreme SET for LET = 86.4MeV • cm<sup>2</sup>/mg for DUT 1 through 4 and Test 1, ±10.8V supplies and IN22 selected. Each run was to 4.0x10<sup>6</sup> ions/cm<sup>2</sup>. Post processing selected the 20 largest and longest SET with both positive and negative deviations; not all of 80 such plots were unique.

#### **Composite Plots** (Continued)

FIGURE 3. Composite plot of SET for LET = 86.4MeV • cm<sup>2</sup>/mg for DUT 1 through 4 and Test 2, ±16.5V supplies with IN22 selected. Each run was to 4.0x10<sup>6</sup>ions/cm<sup>2</sup>. Post processing selected the 20 largest and longest SET in both positive and negative deviations; not all of the 80 such plots were unique.

#### **Composite Plots** (Continued)

FIGURE 4. Composite plot of SET for LET = 86.4MeV • cm<sup>2</sup>/mg for DUT 1 through 4 and Test 3, ±16.5V supplies and switches disabled. Each run was to 4.0x10<sup>6</sup>ions/cm<sup>2</sup>. Post processing selected the 20 largest and longest SET in both positive and negative deviations; not all of the 80 such plots were unique.

#### **Discussion and Conclusions**

#### **SEL and SEB**

Testing with normal incidence Au at LET = 86.4 MeV • cm<sup>2</sup>/mg did not result in any indications of SEB or SEGR at applied voltages up to the absolute maximum rating of ±20V for supplies and ±35V for inputs. The 2.954GeV Au had a range into silicon of 117µm and a Bragg range of 53µm putting the Bragg peak well into the inactive handle wafer of the SOI part. Functionality and operational currents monitored did not change as a result of the irradiations carried out at a case temperature of +125°C ±10°C. A minimal interpretation of the possible SEB/SEGR cross section is less than 1.5x10<sup>-7</sup>cm<sup>2</sup> to a 95% confidence at LET = 86.4MeV • cm<sup>2</sup>/mg at normal incidence for the input voltage conditions of  $\pm 17V$  and  $\pm 35V$ . In the total testing the SEB/SEGR possible cross section is less than 7.5x10<sup>-8</sup>cm<sup>2</sup> at 95% confidence. This is all tantamount to saying that under normal operating conditions the ISL71841SEH is not susceptible to SEB or SEGR failures at up to normal incidence of LET = 86.4MeV  $\cdot$  cm<sup>2</sup>/mg.

#### **SET Results**

In SET testing no indication of an addressing upset was noted. However, SET testing did result in events exceeding the  $\pm 20$ mV detection threshold. The total cross section indicated by the SET capture counts topped out at  $4.4 \times 10^{-4}$  cm<sup>2</sup> at LET = 86.4MeV • cm<sup>2</sup>/mg. The number of SET  $\pm 20$ mV captures was weakly dependent on supply voltage with  $\pm 10.8$ V yielding slightly fewer captured SET than with  $\pm 16.5$ V. It appears the SET result from instantaneous coupling of the output to the supply rails. With a few exception at  $\pm 10.8$ V supplies all the SET captured were within  $\pm 100$ mV deviation.

The observed output SET had decay times of about 15µs. This is likely set by the capacitive loading on V<sub>OUT</sub> (about 700pF from the cabling) and the resistance setting the nominal voltage (5k $\Omega$ ). Thus, the predicted 3.5µs time constant is consistent with that observed. This is important since the application will determine this decay constant and hence the SET duration.

The SET study described here utilized a nominal V<sub>OUT</sub> of OV so that the rails were equally far from the nominal output voltage. It should be expected that as the nominal V<sub>OUT</sub> moves toward a supply rail the SET toward that rail voltage would diminish in magnitude while those toward the opposite rail would increase in magnitude. Thus, the worst case SET for a nominal output near a supply rail could be 2x the magnitudes recorded here.

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard" Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances; machine tools; personal electronic equipment: industrial robots: etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics oroducts outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Plea e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### SALES OFFICES

#### **Renesas Electronics Corporation**

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Miliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tei: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tei: +822-558-3737, Fax: +822-558-5338