# 4-Channel, 6Gbps SAS, SATA Signal Repeater

ANALOG & RE | INTERFACE & CONNECTIVITY | CLOCKS & TIMING | MEMORY & LOGIC | TOUCH & USER INTERFACE | VIDEO & DISPLAY | AUDIO

#### **FEATURES**

- Compensates for cable and PCB trace attenuation and ISI jitter

- Programmable receiver equalization up to 30db

- Programmable de-emphasis up to -8.5dB

- Recovers data stream even when the differential signal eye is completely closed due to trace attenuation and ISI jitter

- Full SAS / SATA protocol and Out-of-Band (OOB) support

- Configurable via external pins, while extended programming ranges are available via I<sup>2</sup>C interface

- Supports automatic download of configuration from external EEPROM with a single or multiple repeaters on I<sup>2</sup>C bus

- Leading edge power minimization in active and shutdown modes

- No external bias resistors or reference clocks required

- Channel mux mode, demux mode, 1 to 2 channels multicast, and Z-switch function mode

- Packages available:

- Option A Package: 100-ball FPBGA (9x9mm)

- Option B Package: 36-QFN (4x7.5mm)

#### **Benefits**

- Extends maximum cable length to over 10 meters and trace length over 65 inches in SAS / SATA applications

- Speeds up design time by eliminating signal integrity issues

- Minimizes BER, improving system performance and reliability

#### **Applications**

- Blade servers, rack servers

- SAS, SATA instrumentation

- Storage systems

- Cabled SAS or SATA devices

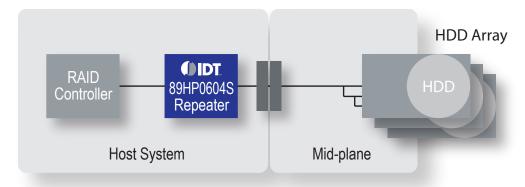

## **Device Overview**

The IDT 89HP0604S is a 1.5Gbps to 6Gbps Repeater IC featuring IDT EyeBoost™ technology that compensates for cable and board trace attenuations and ISI jitter, thereby extending connection reach. The 89HP0604S contains four half-duplex data lanes. Each channel consists of an input equalizer and amplifier, signal detection with glitch filter, as well as programmable output swing, slew rate, and de-emphasis with delay control. Since all of these features are user programmable, they allow for application specific optimization.

Besides the per channel programmable features, the 89HP0604S provides global programmable settings-termination resistance values and transfer modes.

The 89HP0604S, with its many programmable receiver and transmitter features, is ideal for the needs of SAS / SATA applications.

All modes of active data transfer are designed with minimized power consumption. Also, a wide selection of power reducing modes allows the user to eliminate power of unused blocks. In full shutdown mode, the part consumes less than 40mW in worst case environmental conditions.

## 89HP0604S SAS, SATA Compliance

The device was designed to provide end users with features needed to comply with SAS or SATA system application requirements:

- SAS, SATA Out-of-Band (OOB) Support

- Jitter, eye opening, and all other AC and DC specifications

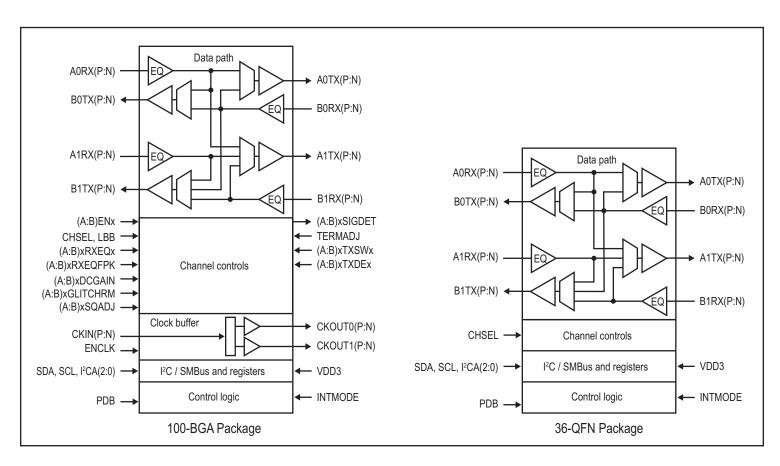

## 89HP0604S Package Options

The 89HP0604S is offered with two package options as shown in following diagram. The 100-pin BGA package provides extensive pin configuration input and status output features in addition to  $l^2C$  configuration. The 36-QFN package option requires the  $l^2C$  slave or local EEPROM for optimized configuration and status reporting.

IDT | THE ANALOG + DIGITAL COMPANY 89HP0604S PRODUCT BRIEF

MANAGEMENT | ANALOG & RF | INTERFACE & CONNECTIVITY | CLOCKS & TIMING | MEMORY & LOGIC | TOUCH & USER INTERFACE | VIDEO & DISPLAY | AUDIO

# 89HP0604S Block Diagram

The 89HP0604S contains four high speed channels. Each channel can routed to different outputs. Depending on user configuration via mode selections, input traffic can be muxed, demuxed, or looped back. To facilitate buffering of system clocks, the repeater provides 1:2 clock buffer as shown in the diagram below. Powerdown (PDB) and channel enable input pins (A0EN, etc.) are provided for easy state and channel control. Status output pins are available for monitoring critical states, such as the detection of high speed input signals (A0SIGDET, etc.).

Each channel's configuration and performance can be optimized via programming pins or via the I<sup>2</sup>C interface (SCL, SDA, A0-A2). The programming option allows the user to optimize the repeater's performance in a wide range of applications, making it an ideal solution for most applications requiring cancellation of trace or cable attenuation and ISI jitter.

89HP0604S Block Diagram

# Discover what IDT know-how can do for you: www.IDT.com/go/SIP

DSCLAMER Integrated Device Technology, Inc. (IDI) and its subsidiariers reserve the right to modify the products and/very specification description. All information in this document, including descriptions of product realtures and performance, is subject to chief to the secretary or product as well described in a such reservation of the described products are determined in the includence are described in the intellectual property right and are not supraemented to perform the same way when installed in austomer products. In the intellectual property right and in the intellectual property right are not intellectual property right are no

Appendix or significantly affect on relievant or sharp or content of the Control of the Control

PB\_89HP0604S\_REV100511