# RENESAS

# **TECHNICAL BRIEF**

## **Full-Duplex Transceivers**

Transmitting Full-Duplex Data over a Single Twisted Pair Cable

TB510 Rev.0.00 Nov 2, 2017

## Abstract

This document describes the concept and design of transmitting full-duplex data over a single Unshielded Twisted Pair (UTP) cable. The interface connection is a 350ft point-to-point data link using the <u>ISL32705E</u> isolated full-duplex transceivers as signal sources at both cable ends. One transceiver transmits data at rate of 2Mbps, the other at 4Mbps.

## Contents

| 1. | Introduction                               | 2 |

|----|--------------------------------------------|---|

| 2. | Bus Node Design                            | 3 |

| 3. | Driver Output Parameters, $R_O$ and $V_0$  | 3 |

| 4. | Current Limiting Resistors, R <sub>S</sub> | 4 |

| 5. | Line Termination                           | 4 |

| 6. | 4-to-2 Wire Conversion                     | 4 |

| 7. | Application Example                        | 6 |

| 8. | Conclusion                                 | 7 |

| 9. | Revision History                           | 8 |

# **List of Figures**

| Figure 1. | Full-Duplex Interface Requires Twice the Cabling Effort of a Half-Duplex Interface   | 2 |

|-----------|--------------------------------------------------------------------------------------|---|

| Figure 2. | Full-Duplex Transmission over Single Twisted Pair Requiring 4-to-2 Wire Conversion   | 2 |

| Figure 3. | Three Main Aspects of the Bus Node Design                                            | 3 |

| Figure 4. | Determining the Driver Output Characteristics with $R_0 = 50\Omega$ and $V_0 = 4.5V$ | 3 |

| Figure 5. | Single-Ended, Point-to-Point Data Link                                               | 4 |

| Figure 6. | $V_{B1} = V_{D1} \times G_1 + V_{D2} \times G_2$                                     | 4 |

| Figure 7. | Voltage Dividers Enable the Summation of Voltages                                    | 5 |

| Figure 8. | Full-Duplex Transmission of 2Mbps Data at Node 1 and 4Mbps Data at Node 2            | 6 |

| Figure 9. | Full-Duplex 2Mbps and 4Mbps Data Correctly Decoded                                   | 6 |

|           |                                                                                      |   |

## 1. Introduction

Higher data throughput, shorter response time, and lower installation costs are the key drivers behind the ongoing improvement efforts in industrial network design. For these reasons, allowing the immediate and continuous exchange of binary data has made the full-duplex bus the preferred interface choice in point-to-point connections. Unlike the half-duplex interface, which transmits or receives data one direction at a time, the full-duplex interface does both simultaneously. This promptness however, comes at the expense of increased cabling effort and installation cost (Figure 1).

Figure 1. Full-Duplex Interface Requires Twice the Cabling Effort of a Half-Duplex Interface

To counteract this drawback, the world of RS-485 users is seeing a new type of interface emerging that allows for full-duplex data transmission over a single twisted-pair cable.

Violating one of RS-485's fundamental principles of avoiding bus contention at all times, this point-to-point interface relies on bus contention by keeping two full-duplex transceivers permanently enabled.

To enhance interface noise immunity, the transceivers are galvanically isolated. This isolation keeps the bus free from common-mode noise, ensuring reliable data transmission in electrical noisy environments with common-mode voltages of up to  $\pm 600$ V.

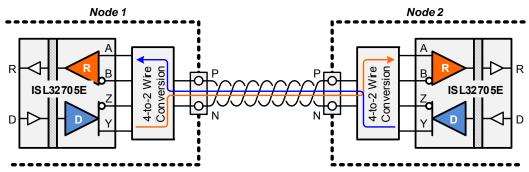

Full-duplex communication over a single signal pair requires 4-to-2 wire conversions between the transceivers and the bus cable to distinguish the incoming (receive) data from the outgoing (transmit) data (Figure 2).

Figure 2. Full-Duplex Transmission over Single Twisted Pair Requiring 4-to-2 Wire Conversion

The design of a 4-to-2 wire converter can be tricky. Although there are circuits available for solving the data separation digitally, their high component count and complicated PCB layout can result in expensive designs. This approach also has a major drawback: the circuits work only in a low-noise lab environment. In addition, exposing the circuits to high common-mode voltages causes them to cease operation.

To provide designers with a robust high-speed solution that transmits 4Mbps over 350ft cable length while tolerating high common-mode voltages, this document discusses the design of a bus node, made up of an isolated full-duplex transceiver and six resistors, performing current limiting, line termination, and 4-to-2 wire conversion.

### 2. Bus Node Design

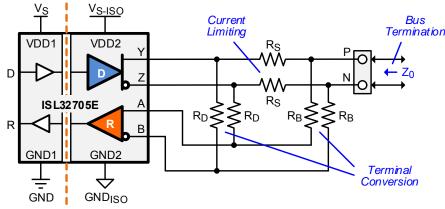

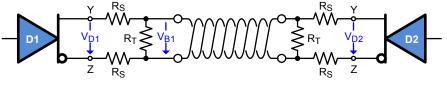

There are three main aspects to consider during the bus node design (Figure 3):

- Current limiting: Because both transceivers are consistently active, bus contention occurs, causing the flow of large differential currents. In addition, large ground potential differences between the transceiver grounds also cause large common-mode currents to flow. To prevent the drivers from overloading and eventually experiencing thermal shut down, current limiting resistors (R<sub>S</sub>) must be placed into a driver's output path.

- Bus node termination: Preventing signal reflections on the line, the bus node impedance must match the characteristic impedance of the bus cable. This is accomplished with the termination resistor,  $R_{T}$ .

- 4-to-2 wire conversion: Resistive voltage dividers consisting of the bus resistors ( $R_B$ ), the driver output resistors ( $R_D$ ), and the receiver input impedance ( $R_{IN}$ ) extract the receive signal from the full-duplex data on the bus.

Figure 3. Three Main Aspects of the Bus Node Design

# 3. Driver Output Parameters, R<sub>O</sub> and V<sub>0</sub>

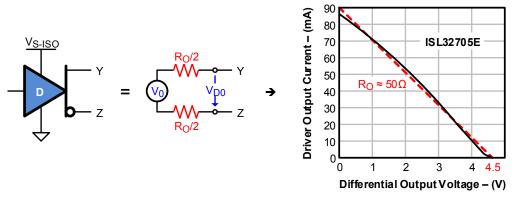

Because both drivers are always active, their output impedance ( $R_O$ ) and differential electromotive force ( $V_0$ ) affect the calculation of all resistor values as well as the voltage relations on the bus. The parameters are quickly determined by drawing a straight, best-fit line through the driver's V-I characteristic, provided in the <u>ISL32705E</u> data sheet. For the transceiver in <u>Figure 4</u>, these parameters are  $V_0 = 4.5V$  and  $R_O = V_0/I_O = 50\Omega$ .

Figure 4. Determining the Driver Output Characteristics with  $R_0 = 50\Omega$  and  $V_0 = 4.5V$

## 4. Current Limiting Resistors, R<sub>S</sub>

The value of  $R_S$  is calculated so that the two driver output currents are limited to normal operating values at the maximum voltage difference. For example, if both driver outputs are of opposite polarity, the typical voltage difference between them is 3.3V. Limiting the output current to about 30mA requires a total resistance of  $3.3V/30mA = 110\Omega$  and  $55\Omega$  for each  $R_S$ . Using the closest standard value easily available, each  $R_S$  becomes 60.4 $\Omega$ .

Figure 5. Single-Ended, Point-to-Point Data Link

#### 5. Line Termination

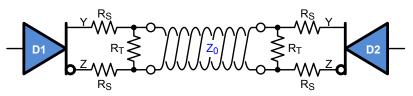

To prevent signal reflections on the bus, the input impedance of a bus node must match the characteristic cable impedance,  $Z_0$ . In this case, it means the combined impedance of the termination resistor ( $R_T$ ) in parallel to the series circuit of the two  $R_S$  resistors and the driver output impedance ( $R_O$ ) should equal  $Z_0$ .

(EQ. 1)  $R_T || (2R_S + R_O) = Z_0$

Because  $R_T$  is the only option to tune the bus node impedance towards  $Z_0$ , we solve (EQ. 1) for  $R_T$ :

(EQ. 2)

$$R_{T} = \frac{(2R_{S} + R_{O}) \cdot Z_{0}}{2R_{S} + R_{O} - Z_{0}}$$

Inserting the values  $R_S = 60.4\Omega$ ,  $R_O = 50\Omega$ , and  $Z_0 = 100\Omega$  (for Cat-5 cable) yields 241 $\Omega$ , and choosing the next higher value from the E-96 series of standard resistor values makes  $R_T = 243\Omega$ .

#### 6. 4-to-2 Wire Conversion

The 4-to-2 wire converter enables a bus node to extract the output signal of the opposite bus node from the full-duplex signal on the bus. It does so by subtracting its own driver output from the bus voltage. Focusing on node 1 (Figure 6), we establish the equation for the bus voltage  $V_{B1}$  with  $G_1$  and  $G_2$  as the generic gain coefficients:

(EQ. 3)

$$V_{B1} = V_{D1} \cdot G_1 + V_{D2} \cdot G_2$$

Solving for the  $V_{D2}$  component gives us the attenuated output of bus node 2:

(EQ. 4)

$$V_{D2} = \frac{V_{B1} - V_{D1} \cdot G_1}{G_2}$$

Circuit-wise, (EQ. 4) can be resolved with multiple difference amplifiers. With each amplifier stage requiring four gain resistors, the component count increases significantly, making this solution an expensive and complex design.

Figure 6.  $V_{B1} = V_{D1} \times G_1 + V_{D2} \times G_2$

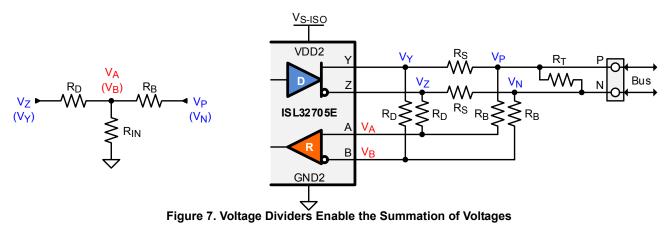

However, if we split  $V_{D1}$  and  $V_{B1}$  into their individual line voltages ( $V_{D1} = V_Y - V_Z$ ,  $V_{B1} = V_P - V_N$ ) and add them through resistive voltage dividers (see Figure 7), we can define the voltages at the summing points as the receiver input voltages,  $V_A$  and  $V_B$ :

(EQ. 5)

$$V_A = \frac{V_P}{G_{V1}} + \frac{V_Z}{G_{V2}}$$

$V_{\rm B} = \frac{V_{\rm N}}{G_{\rm V1}} + \frac{V_{\rm Y}}{G_{\rm V2}}$

where  $G_{V1}$  and  $G_{V2}$  are the generic gain factors of the voltage dividers.

Then, building the difference  $V_A$  -  $V_B$  gives the actual receiver input voltage:

(EQ. 7)

$$V_{AB} = \frac{V_{B1}}{G_{V1}} - \frac{V_{D1}}{G_{V2}} = \frac{V_{B1} \cdot G_{V2} - V_{D1} \cdot G_{V1}}{G_{V1} \cdot G_{V2}}$$

Comparing the gain coefficients in (EQ. 4) with those in (EQ. 5) results in  $G_1 = G_{V1}$ ,  $G_2 = G_{V1} \cdot G_{V2}$ , and  $G_{V2} = 1$ , which proves the validity of the voltage divider concept.

For practical applications, the receiver input impedance ( $R_{IN}$ ) must be considered, because it causes a reduction in gain factors. To minimize the impact of  $R_{IN}$ , it is recommended to make the value of  $R_B$  smaller than 0.1  $R_{IN}$ , but larger than 1k $\Omega$  to maintain low differential bus loading:

(EQ. 8)

$$0.1R_{\rm IN} \ge R_{\rm B} \ge 1k\Omega$$

The ratio of  $R_B/R_D$  should match the ratio of  $V_{B1}/V_{D1}$ , aka  $G_1$ , thus demanding that  $R_D = R_B/G_1$ . However,  $G_1$  is a nonlinear function of L (the length of the bus cable),  $R_S$ ,  $R_T$ , and  $Z_0$ , resulting in a complex algebraic expression. To simplify, (EQ. 7) presents the final equation to calculate  $R_D$ :

(EQ. 9)

$$R_D = R_B \left( 1 + \frac{2R_S}{R_T || (0.056 \cdot L + Z_0)} \right)$$

where L is the cable length in ft.

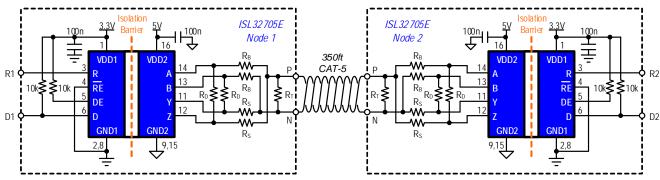

# 7. Application Example

<u>Figures 8</u> and <u>9</u> show the design and scope shot of a 4Mbps high-speed full-duplex data link over 350ft Cat-5 cable. Each bus node includes an isolated 4Mbps full-duplex transceiver and a resistor network of  $R_S = 60.4\Omega$ ,  $R_D = 2.49k\Omega$ ,  $R_B = 1k\Omega$ , and  $R_T = 243\Omega$ .

Figure 8. Full-Duplex Transmission of 2Mbps Data at Node 1 and 4Mbps Data at Node 2

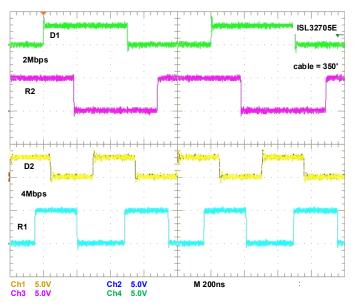

The driver inputs are fed with logic signals of different data rates. D1 receives a 2Mbps signal and D2 receives a 4Mbps signal at a random phase shift. Figure 9 shows that the receiver output of node 2 (R2) correctly displays the input data of D1, and vice versa, R1 displays the input data of D2.

Figure 9. Full-Duplex 2Mbps and 4Mbps Data Correctly Decoded

#### 8. Conclusion

Transmitting full-duplex data over a single twisted pair cable is made possible through 4-to-2 wire converters, which connect the 4-pin bus I/O of full-duplex transceivers to two bus cable conductors. To maintain a simple and inexpensive bus node design, voltage dividers are used to extract the receive signal from the full-duplex mix on the bus. Although this document describes a high-speed data link using the isolated full-duplex transceiver <u>ISL32705E</u>, Renesas provides a wide range of full-duplex transceivers for various data rates, output drives, and common-mode voltages.

## 9. Revision History

| Rev. | Date        | Description     |

|------|-------------|-----------------|

| 0.00 | Nov 2, 2017 | Initial release |

© Copyright Intersil Americas LLC 2017. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the document is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com