# **Quick Start**

DEMO9910HW Demonstration Board for ADC1207S080

Rev. 2.0 — 2 July 2012

**Quick Start**

# Document information Info Content Keywords DEMO9910HW, PCB1337-1, Demonstration board, ADC, Converter, ADC1207S080 Abstract This document describes how to use the demonstration board DEMO9910HW for the analog-to-digital converter ADC1207S080.

Overview

#### **Revision history**

| Rev | Date     | Description      |

|-----|----------|------------------|

| 2.0 | 20120702 | Rebranded.       |

| 0.1 | 20080610 | Initial version. |

# 1. Quick start

#### 1.1 Setup overview

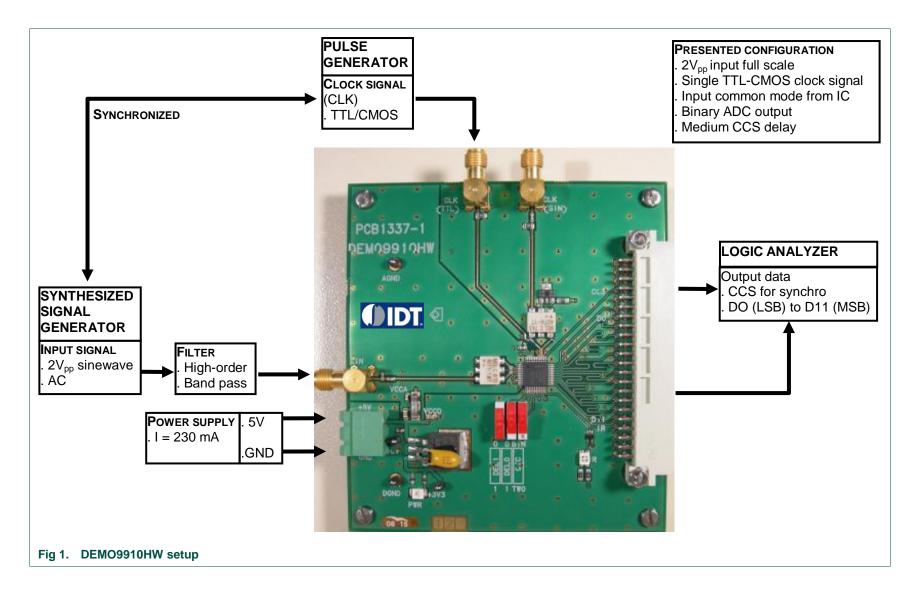

Figure Fig 1 presents the connections to measure DEMO9910HW.

#### 1.2 Power supply

The board is powered with a single 5  $V_{DC}$  power supply. A power supply regulator is used to supply all the 3.3 V circuitry on the board.

#### Table 1.General power supply

| Name | Function                                                | Vie |

|------|---------------------------------------------------------|-----|

| J5   | +5V green connector – Power supply 5 $V_{DC}$ / 230 mA. |     |

| D2   | PWR green light – It indicates the good supply plugging | -   |

| TM1  | DGND test point – Digital ground                        | -   |

| TM2  | AGND test point – Analog ground                         | -   |

| TB1  | +3V3 test point – Output stage power supply             | -   |

| TB2  | +5V test point – ADC core power supply                  | -   |

|      |                                                         |     |

### 1.3 Input signals (IN, CLK)

The input clock signal can be either a sinewave or a TTL-CMOS signal. The selection is made with 2 soldered straps on the board.

TB1

To ensure a good evaluation of the device, the input signal and the input clock must be synchronized together.

Moreover, the input frequency (Fi, MHz) and the clock frequency (Fclk, Msps) should follow the formula:

,where M is an odd number of period and N is the number of samples.

#### Table 2. Input signals

| Name | Function                                                                                           | View       |

|------|----------------------------------------------------------------------------------------------------|------------|

| J3   | IN connector – Analog input signal (50 $\Omega$ matching)                                          |            |

| J4   | CLK (TTL) connector – Single clock input signal (50 $\Omega$ matching)                             |            |

| J2   | CLK (SIN) connector – Clock input signal (50 $\Omega$ matching) for differential sinewave drive.   |            |

| ST1  | Strap – Selection between J4 (single clock drive) or the transformer (differential clock drive).   | J3 ST1 ST2 |

| ST2  | Strap – Selection between DGND (single clock drive) or the transformer (differential clock drive). |            |

# 1.4 Output signals (D0 to D11, IR, CCS)

The digital output signal is available in binary or 2's complement format.

A Complete Conversion Signal (CCS) is provided by the device for the datas acquisition and its delay is referenced to the middle of the active data.

#### Table 3. Output signals

| Name  | Functio                                                                                                     | 'n        |                    |              |  |

|-------|-------------------------------------------------------------------------------------------------------------|-----------|--------------------|--------------|--|

| J1    | Array connector – ADC digital output(D0 to D11), In ran<br>signal (IR) and Complete Conversion Signal (CCS) |           |                    |              |  |

| D1    | IR green light – It indicates that the analog input signal in the full scale range                          |           |                    |              |  |

| S1    | OTC sw                                                                                                      | ritch – O | utput format selec | tion         |  |

|       | Binary                                                                                                      |           | 2's o              | complement   |  |

| S2,S3 | DELO, D                                                                                                     | DEL1 swi  | itches – CCS dela  | ay selection |  |

|       | DEL1                                                                                                        | DEL0      | CCS delay          | Switches     |  |

|       | 0                                                                                                           | 0         | High<br>impedance  |              |  |

|       | 0                                                                                                           | 1         | 0.3 ns             |              |  |

|       | 1                                                                                                           | 0         | 1.3 ns             |              |  |

|       | 1                                                                                                           | 1         | 2.3 ns             |              |  |

# 2. Example

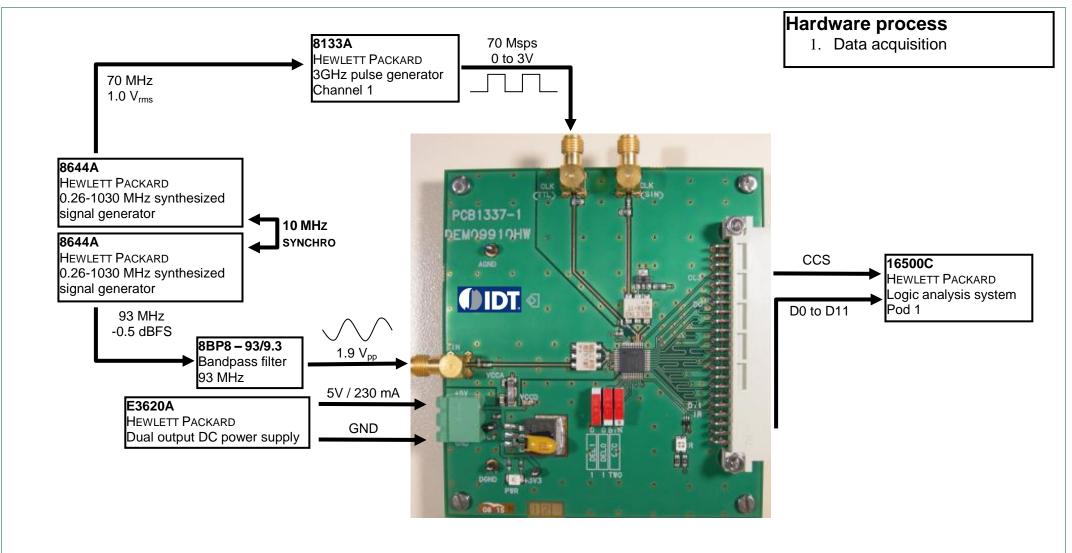

## 2.1 Setup example

Fig 2. ADC1207S080 hardware setup