# IDT<sup>™</sup> Interprise<sup>™</sup> 79RC32438 Integrated Communications Processor

# **User Reference Manual**

May 2005

6024 Silver Creek Valley Road, San Jose, California 95138 Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775 Printed in U.S.A. ©2005 Integrated Device Technology, Inc.

#### GENERAL DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### CODE DISCLAIMER

Code examples provided by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of the code examples below is completely at your own risk. IDT MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICU-LAR PURPOSE, OR NON-INFRINGEMENT. FURTHER, IDT MAKES NO REPRESENTATIONS OR WARRANTIES AS TO THE TRUTH, ACCURACY OR COMPLETENESS OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR THAT IS CONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, INDIRECT, PUNITIVE OR SPECIAL DAMAGES, HOWEVER THEY MAY ARISE, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES. The code examples also may be subject to United States export control laws and may be subject to the export or import laws of other countries and it is your responsibility to comply with any applicable laws or regulations.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

The IDT logo is a registered trademark of Integrated Device Technology, Inc. IDT, Interprise, RISController, RISCore, RC3041, RC3052, RC3081, RC32134, RC32332, RC32334, RC32336, RC32355, RC32355, RC32356, RC32364, RC32104, RC400, RC4640, RC64145, RC4650, RC5000, RC64474, RC64475 are trademarks of Integrated Device Technology, Inc.

Powering What's Next and Enabling A Digitally Connected World are service marks of Integrated Device Technology, Inc. Q, QSI, SynchroSwitch and Turboclock are registered trademarks of Quality Semiconductor, a wholly-owned subsidiary of Integrated Device Technology, Inc.

# **About This Manual**

Notes

#### Introduction

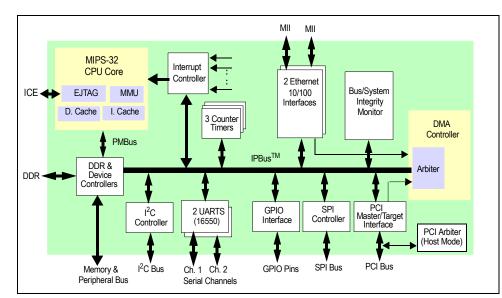

This user reference manual includes hardware and software information on the RC32438, a high performance integrated processor that combines a high performance 32-bit CPU core with system logic to provide direct connection to boot memory, main memory, I/O, and PCI. It also includes on-chip peripherals such as DMA channels, reset circuitry, interrupts, timers, and UARTs. Each chapter is designed to cover the following topics:

- High level feature summary of the specific module

- Summary of the register set associates with a specific module

- Outline of the operation of the module

- Detailed register description.

#### **Finding Additional Information**

Information not included in this manual such as mechanicals, package pin-outs, and electrical characteristics can be found in the data sheet for this device, which is available from the IDT website (www.idt.com) as well as through your local IDT sales representative.

## **Content Summary**

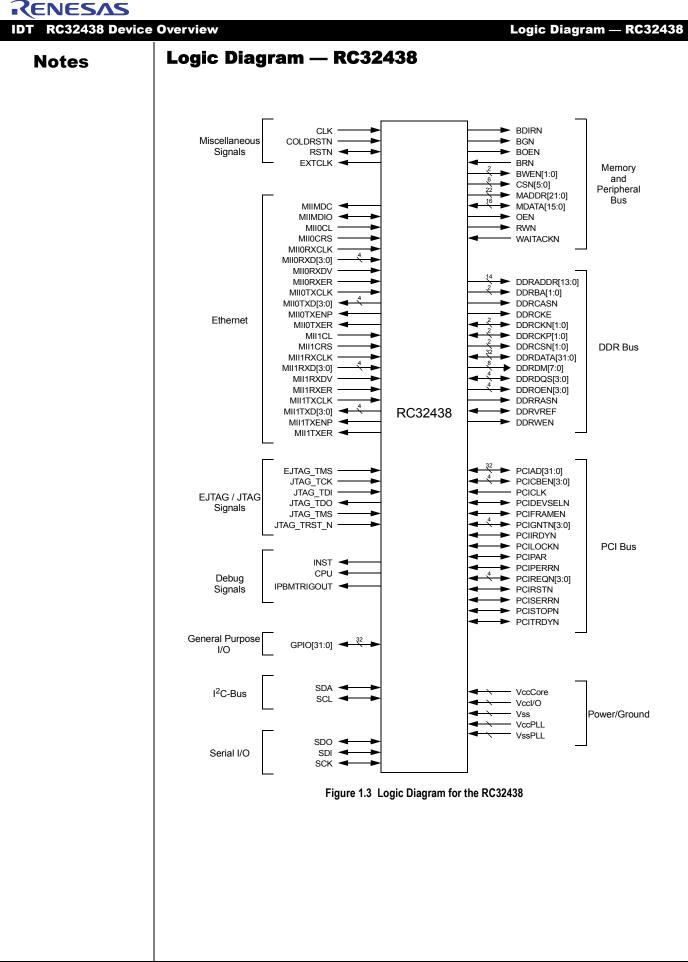

Chapter 1, "RC32438 Device Overview," provides a complete introduction to the performance capabilities of the RC32438. Included in this chapter is a summary of features for the device as well as a system block diagram and internal register maps.

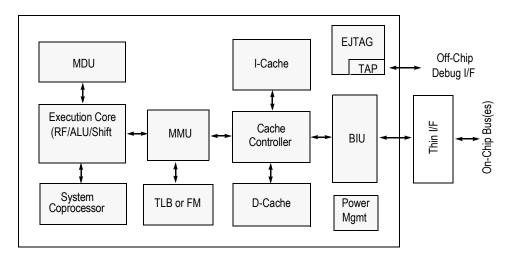

**Chapter 2**, **"MIPS32 4Kc Processor Core**," provides basic information on the architecture and operation of the 4Kc<sup>™</sup> processor core from MIPS® Technologies as it applies to the RC32438.

**Chapter 3, "Clocking and Initialization,"** discusses the reset initialization sequence required by the RC32438 and provides information on boot vector settings and clock signals.

Chapter 4, "System Integrity Functions," discusses system integrity functions, including the registers that log system activity and that can be used to indicate the source of hardware or software errors.

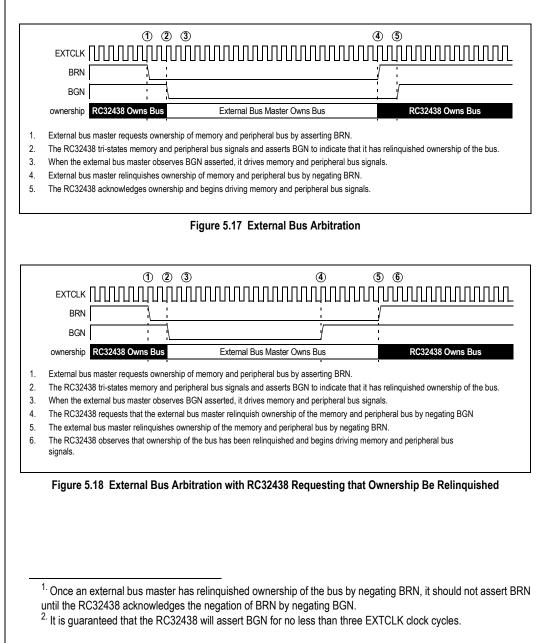

Chapter 5, "Bus Arbitration," describes the internal arbitration mechanism used among the various on-chip modules. The chapter also describes the bus protocol used by an external bus master to gain ownership of the memory and peripheral bus.

Chapter 6, "Device Controller," describes the operation of the device controller, including registers and device transactions, which provides a glueless interface to SRAMs, ROMs/PROMs/EEPROMs, dual port memories, and other devices.

Chapter 7, "Double Data Rate (DDR) Controller," describes the features, functions, and operation of the DDR Controller, including a description of the registers.

Chapter 8, "Interrupt Controller," provides information about the interrupt controller and interrupt source descriptions.

Chapter 9, "DMA Controller," describes the DMA controller, channels, descriptors, registers, transactions, and operations.

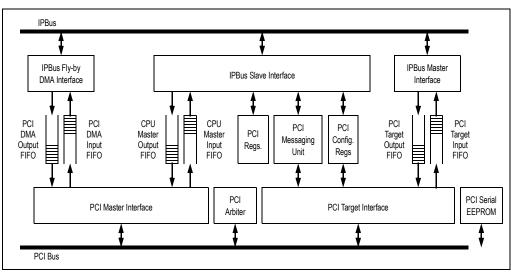

Chapter 10, "PCI Bus Interface," describes the features, functions, and operations of the PCI bus interface on the RC32438.

**Chapter 11, "Ethernet Interfaces,"** discusses the two Ethernet interfaces on the RC32438 which can be used in applications such as SOHO routers or high speed modems for PCs.

| RENESAS               |  |

|-----------------------|--|

| IDT About This Manual |  |

#### Notes

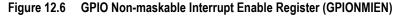

**Chapter 12, "General Purpose I/O Controller,"** describes this controller and how it is configured to operate as a general purpose I/O or as an alternate function.

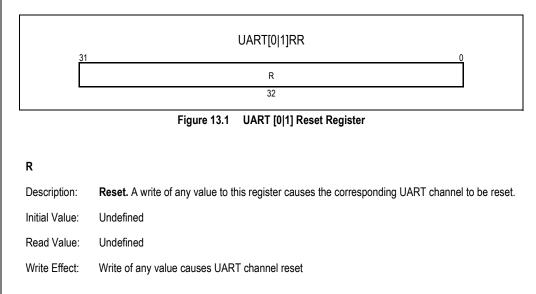

Chapter 13, "UART Controller," provides information about the two separate UARTs within the RC32438, including the UART registers.

Chapter 14, "Counter Timers," describes the three general purpose 32-bit counter/timers on the RC32438.

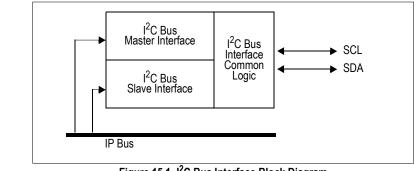

**Chapter 15, "I<sup>2</sup>C Bus Interface,"** describes the standard I<sup>2</sup>C bus interface, supporting both master and slave operations, that is implemented on the RC32438.

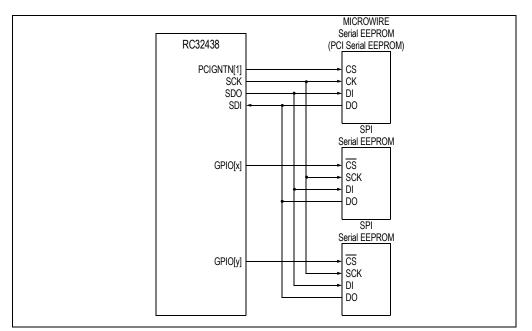

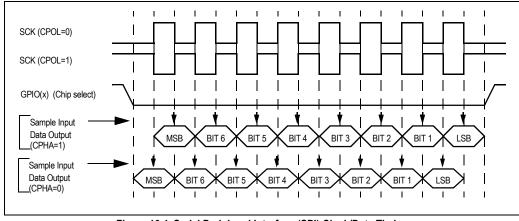

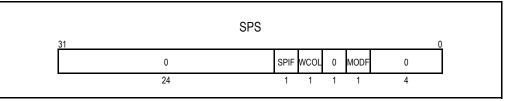

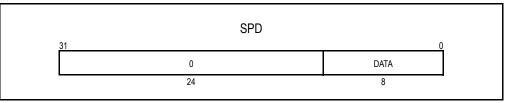

Chapter 16, "Serial Peripheral Interface," describes the SPI master interface which uses three signals to connect to low-cost SPI peripherals and memory.

Chapter 17, "On-Chip Memory," describes the operation and support provided by on-chip memory for memory read and write operations on the RC32438.

**Chapter 18, "Debugging and Performance Monitoring,"** discusses the three different debugging features available on the RC32438: IPBus Monitor, Event Monitor, and Debug Pins.

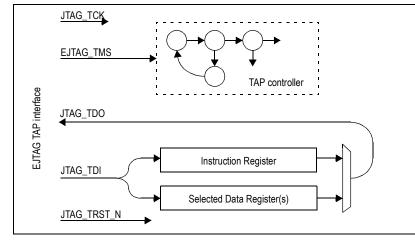

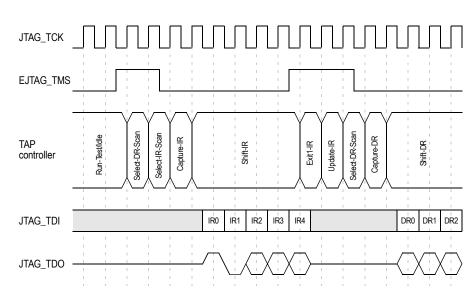

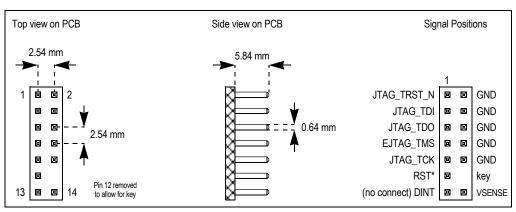

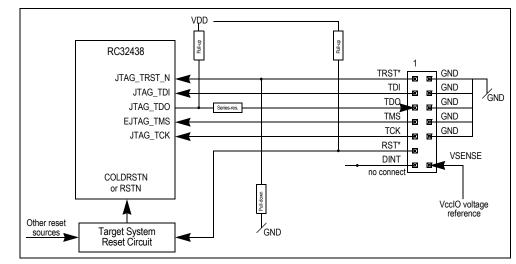

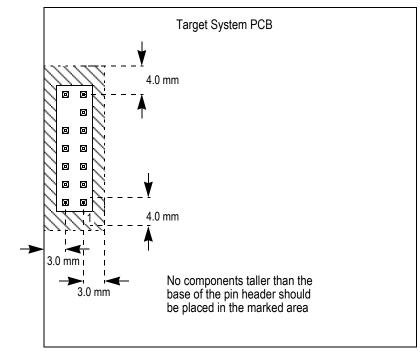

**Chapter 19, "JTAG Boundary Scan,"** discusses an enhanced JTAG interface, including a system logic TAP controller, signal definitions, a test data register, an instruction register, and usage considerations.

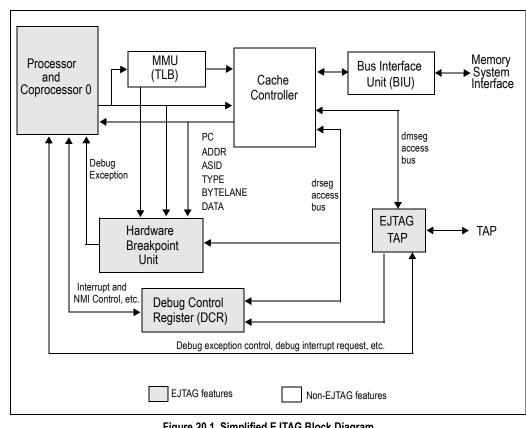

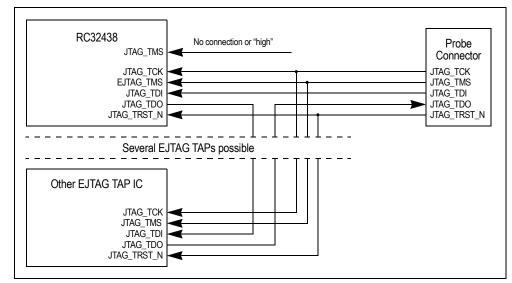

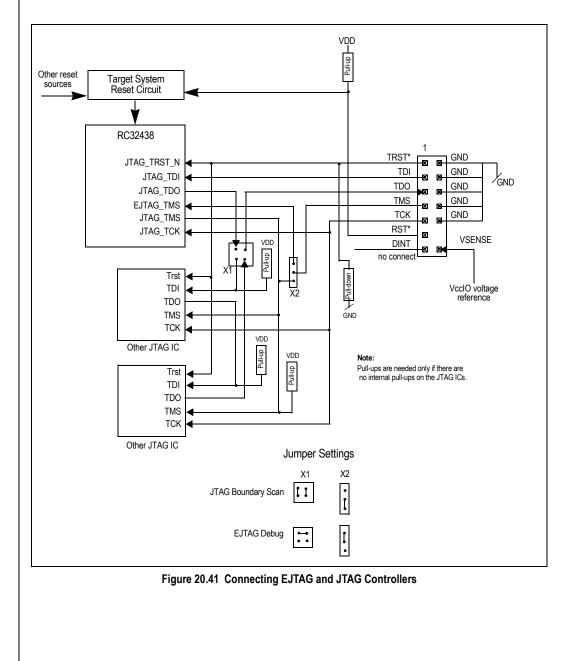

**Chapter 20, "EJTAG System,"** describes the EJTAG's features, its Debug Control Register, TAP registers, EJTAG Probe, hardware breakpoints, and other related topics.

Appendix A, "4Kc Processor Core Instructions," contains additional information about the 4Kc processor core instruction set.

#### **Documentation Conventions and Definitions**

Throughout this manual the following conventions and terms are used:

- To avoid confusion when dealing with a mixture of "active-low" and "active-high" signals, the terms assertion and negation are used. The term assert or assertion is used to indicate that a signal is active or true, independent of whether that level is represented by a high or low voltage. The term negate or negation is used to indicate that a signal is inactive or false.

- To define the active polarity of a signal, a suffix will be used. Signals ending with an 'N' should be interpreted as being active, or asserted, when at a logic zero (low) level. All other signals (including clocks, buses and select lines) will be interpreted as being active, or asserted, when at a logic one (high) level.

- To define buses, the most significant bit (MSB) will be on the left and least significant bit (LSB) will be on the right. No leading zeros will be included.

- To represent numerical values, either decimal, binary, or hexadecimal formats will be used. The binary format is as follows: 0bDDD, where "D" represents either 0 or 1; the hexadecimal format is as follows: 0xDD, where "D" represents the hexadecimal digit(s); otherwise, it is decimal.

- Unless otherwise denoted, a byte will refer to an 8-bit quantity. A halfword will refer to a 16-bit quantity. A triple-byte will refer to a 24-bit quantity. A word will refer to a 32-bit quantity, and a double or double word will refer to a 64-bit quantity.

- A bit is set when its value is 0b1. A bit is cleared when its value is 0b0.

- The compressed notation ABC[x|y|z]D refers to ABCxD, ABCyD, and ABCzD.

- The compressed notation ABC[x..y]D refers to ABCxD, ABC(x+1)D, ABC(x+2)D, ... ABCyD.

- In words, bit 31 is always the most significant bit and bit 0 is the least significant bit. In halfwords, bit 15 is always the most significant bit and bit 0 is the least significant bit. In bytes, bit 7 is always the most significant bit and bit 0 is the least significant bit.

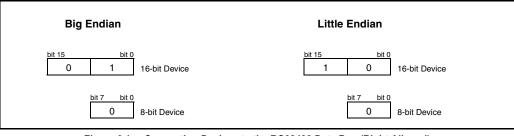

- The ordering of bytes within words is referred to as either "big endian" or "little endian." Big endian systems label byte zero as the most significant (leftmost) byte of a word. Little endian systems label byte zero as the least significant (rightmost) byte of a word.

| 1  | I Signal Terminolo                                                                                                           |

|----|------------------------------------------------------------------------------------------------------------------------------|

| es |                                                                                                                              |

|    | bit 31 bit 0                                                                                                                 |

|    | 0 1 2 3                                                                                                                      |

|    | Address of Bytes within Words: Big Endian                                                                                    |

|    |                                                                                                                              |

|    | bit 31 bit 0                                                                                                                 |

|    | 3 2 1 0                                                                                                                      |

|    | Address of Bytes within Words: Little Endian                                                                                 |

|    |                                                                                                                              |

|    | Figure 1 Example of Byte Ordering for "Big Endian" or "Little Endian" System Definition                                      |

|    | A read-only: register, bit, or field is one which can be read but not modified                                               |

|    | <ul> <li>A sticky bit is a bit that remains set after being set by hardware until a zero is written to it. Writir</li> </ul> |

|    | one to a sticky has no effect on its value.                                                                                  |

|    | ◆ A zero field in a register, denoted as "0" in register figures, must be written with a value of zero                       |

|    | returns a value of zero when read.                                                                                           |

|    |                                                                                                                              |

|    | Signal Terminology                                                                                                           |

|    | Throughout this manual, when describing signal transitions, the following terminology is used:                               |

|    | <ul> <li>Rising edge indicates a low-to-high (0 to 1) transition.</li> </ul>                                                 |

|    | <ul> <li>Falling edge indicates a high-to-low (1 to 0) transition.</li> </ul>                                                |

|    |                                                                                                                              |

|    | These terms are illustrated in Figure 2.                                                                                     |

|    | These terms are illustrated in Figure 2.                                                                                     |

|    | These terms are illustrated in Figure 2.                                                                                     |

|    |                                                                                                                              |

|    | single clock cycle                                                                                                           |

|    | single clock cycle                                                                                                           |

|    | single clock cycle<br>1 2 3 4<br>high-to-low                                                                                 |

|    |                                                                                                                              |

|    | high-to-low<br>transition                                                                                                    |

|    | high-to-low<br>transition                                                                                                    |

|    | high-to-low<br>transition                                                                                                    |

|    | high-to-low<br>transition                                                                                                    |

|    | single clock cycle<br>1 2 3 4<br>high-to-low<br>transition<br>low-to-high<br>transition                                      |

January 16, 2003: SCL pin under I<sup>2</sup>C in Table 1.1 was changed from pull-down to pull-up.

**February 5, 2003**: Changed DDRDM[7:0] pins from input/output to output only in Chapter 1. Revised description for EJTAG/JTAG pins in Table 1.2. Revised Chapter 20, EJTAG System.

March 7, 2003: Added Table 3.4, Pin State During Reset, in Chapter 3.

**April 11, 2003**: In Chapter 1, Table 1.2, the description for PCIREQN[3:0] should read that [3:1] in both host and satellite modes are unused and driven high, instead of low. Also in Chapter 1, added the address for DDRRDC register to Table 1.4. In Chapter 7, added the same DDRRDC address to Table 7.1 and revised the DDR Initialization program example.

#### Notes

**May 5, 2003**: In Chapter 10, PCI Serial EEPROM Interface section, revised 1st paragraph as follows: changed register addresses from 0x80 to 0x40, added sentence "The interface only supports 93C46-compatible serial EEPROMs," and added sentence "Only EEPROMs which are 2048 bits in size should be used." In the second paragraph, the following sentence was deleted, "EEPROM addresses which are greater than or equal to 0x40 in EEPROMs whose size is greater than 1024 bits may be used to store application specific information." Also in Chapter 10, Disabled Mode section, second paragraph, revised 1st sentence as follows: "When the PCI bus interface is disabled, all of the PCI pins are tri-stated, except PCIGNTN[3:1], and thus should be held at a valid logic level on the board." Also added that PCIGNTN[3:1] signals are driven high. In Chapter 16, Function Overview, added clarification on PCI serial EEPROM mode of operation.

May 21, 2003: In Chapter 11, Address Recognition Logic section, the 2nd through the 4th paragraphs on page 11-8 were revised.

**July 11, 2003**: Removed references to IPBus Monitor feature. In Chapter 5, deleted Enable Eager Prefetching bit from IPBus Arbiter Control Register in the IPBus Registers section. In Chapter 10, revised description for EN bit in PCI Control Register, Changed Byte Swapping bit in PCI Local Address Control register to Force Endianess, added "byte and halfword target IO transactions are not supported" to Target I/O Read and Target I/O Write sections, and changed DMA limitations to "32KB minus 8 bytes" for channels 8 and 9. In Chapter 11, removed table associated with MII Management Command Register. In Chapter 16, added information in the Functional Overview section. In Chapter 17, revised first 4 paragraphs of Theory of Operation section.

**July 28, 2003**: In Chapter 11, changed the First Descriptor bit in Figure 11.10 to Reserved and deleted information about FD in 2 sections: Ethernet Input DMA Operations and Ethernet Output DMA Operations.

**November 21, 2003**: In Chapter 10, changed the description of the IGM bit on page 10-6, the CWE bit on page 10-8, and the CLS bit on page 10-52.

**March 10, 2004**: In Chapter 2, references to the RP bit were deleted. In the Target I/O Read and Target I/O Write sections of Chapter 10, the following sentences were removed "The RC32438 PCI I/O interface is a 32-bit interface. Byte and halfword Target I/O transactions are not supported." In fact, the RC32438 does support PCI Target I/O transactions of byte and half word size. In Chapter 11, changed the description of the PEN bit on page 11-15.

May 11, 2005: In Table 10.6: switched Chapter 8 and Chapter 9 headings only - not the values in the columns; also, switched Yes and No for these two headings in the Memory Read Multiple row.

# **Table of Contents**

Notes

## About This Manual Introduction ......i Content Summary ......i Documentation Conventions and Definitions.....ii Signal Terminology...... iii Revision History.....iii 1 RC32438 Device Overview System Block Diagram ......1-2 Feature List Summary ......1-2 Logic Diagram — RC32438......1-7 Default Memory Map ......1-20 RC32438 Internal Register Map .....1-21 2 MIPS32 4Kc Processor Core Introduction ......2-1 Functional Overview 2-1 Functional Overview ......2-3 Slip Conditions ......2-17

| S | Exceptions                                  |      |

|---|---------------------------------------------|------|

|   | Exception Conditions                        |      |

|   | Exception Priority                          |      |

|   | General Exception Processing                |      |

|   | Debug Exception Processing                  |      |

|   | Exceptions                                  |      |

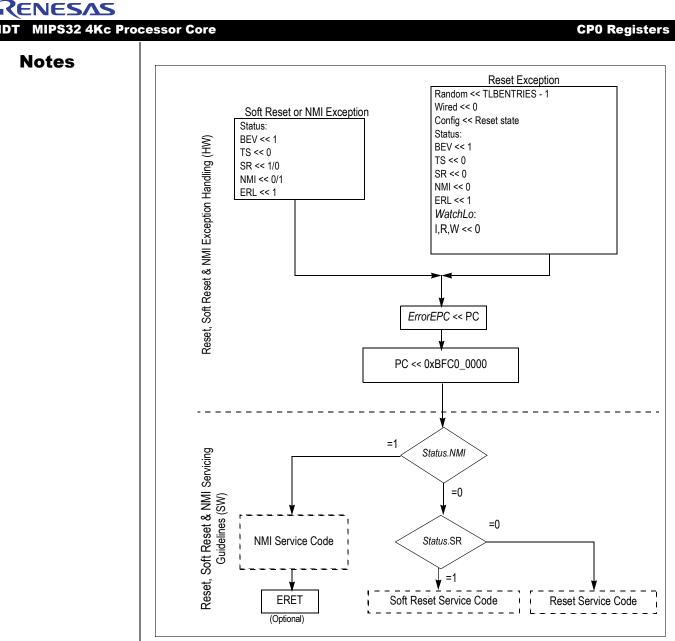

|   | Exception Handling and Servicing Flowcharts |      |

|   | CP0 Registers                               |      |

|   | CP0 Register Summary                        |      |

|   | CP0 Registers                               |      |

|   | Hardware and Software Initialization        | 2-79 |

|   | Hardware Initialized Processor State        | 2-79 |

|   | Software Initialized Processor State        | 2-80 |

|   | Caches                                      |      |

|   | Cache Protocols                             | 2-81 |

|   | Instruction Cache                           | 2-82 |

|   | Data Cache                                  | 2-82 |

|   | Memory Coherence Issues                     | 2-83 |

|   | Power Management                            |      |

|   | Instruction-Controlled Power Management     | 2-83 |

|   | Instruction Set                             |      |

|   | Load and Store Instructions                 |      |

|   | Computational Instructions                  |      |

|   | Control Instructions                        |      |

|   | Coprocessor Instructions                    |      |

|   | Enhancements to the MIPS Architecture       |      |

|   | Processor Core Instructions                 | 2-87 |

| 3 | Clocking and Initialization                 |      |

|   | Introduction                                | 3-1  |

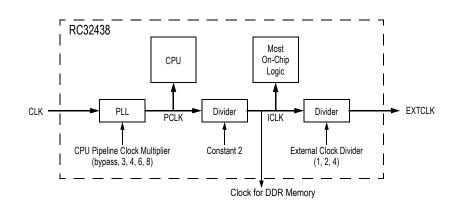

|   | Block Diagram                               |      |

|   | Clocking Overview                           |      |

|   | Reset Register Description                  |      |

|   | Reset and Initialization                    |      |

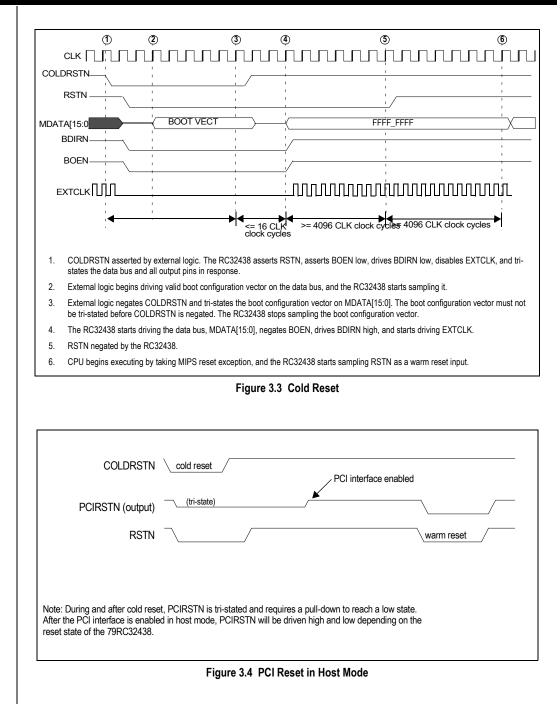

|   | Cold Reset                                  |      |

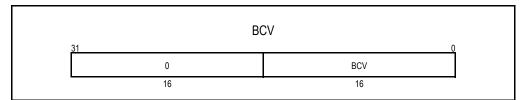

|   | Boot Configuration Vector                   |      |

|   | Reset/Initialization Registers              |      |

|   | Boot Configuration Vector Register          |      |

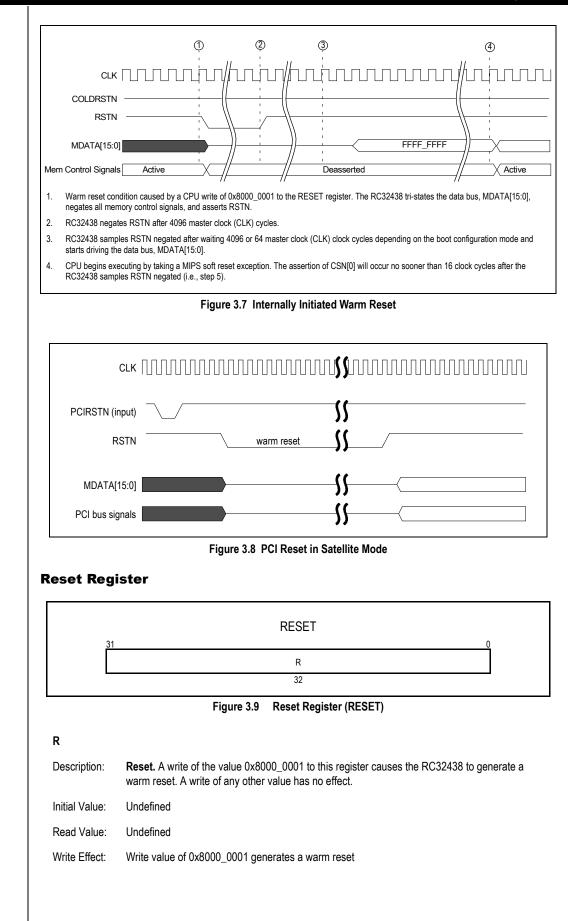

|   | Warm Reset                                  |      |

|   | Reset Register                              |      |

|   | Pin State During Reset                      | 3-9  |

|   | System Integrity Functions                  |      |

| 4 |                                             |      |

| 4 | Introduction                                | 4-1  |

| 4 |                                             |      |

| 4 | Introduction                                | 4-1  |

| ENESAS<br>Table of Cont | ents                                                                                             |    |

|-------------------------|--------------------------------------------------------------------------------------------------|----|

|                         | System Integrity Registers                                                                       | 4- |

| Notes                   | Error Control and Status Register                                                                |    |

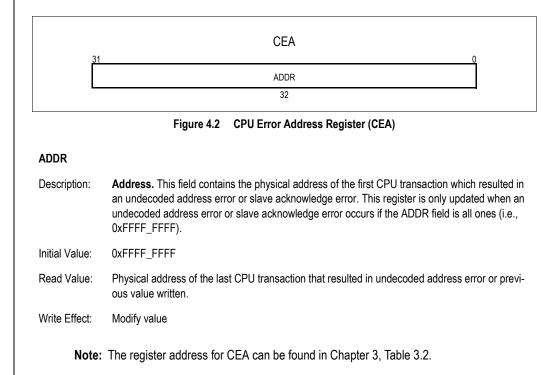

|                         | CPU Error Address Register                                                                       |    |

|                         | Address Space Monitor                                                                            |    |

|                         | Watchdog Timer                                                                                   |    |

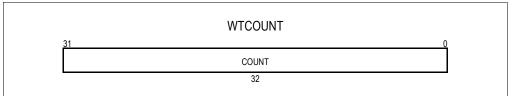

|                         | Watchdog Timer Count Register                                                                    |    |

|                         | Watchdog Timer Compare Register                                                                  |    |

|                         | Watchdog Timer Control Register                                                                  |    |

|                         | IPBus Slave Acknowledge Errors                                                                   | 4- |

|                         | 5 Bus Arbitration                                                                                |    |

|                         | Introduction                                                                                     | 5- |

|                         | Functional Overview                                                                              | -  |

|                         | IPBus Register Description                                                                       |    |

|                         |                                                                                                  |    |

|                         | PMBus Arbitration Register Description                                                           |    |

|                         | Theory of Operation                                                                              |    |

|                         | Example IPBus Arbiter Configurations                                                             |    |

|                         | IPBus Registers                                                                                  |    |

|                         | IPBus Arbiter Control Register                                                                   |    |

|                         | IPBus Arbiter Priority Configuration Register<br>IPBus Arbiter Bus Master Configuration Register |    |

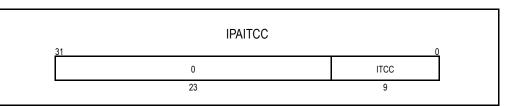

|                         | IPBus Idle Transaction Cycle Count Register                                                      |    |

|                         | PMBus Arbitration                                                                                |    |

|                         | IPBus Idle                                                                                       |    |

|                         | IPBus Active                                                                                     |    |

|                         | Sneak Transactions.                                                                              |    |

|                         | Bus Parking                                                                                      | -  |

|                         | PMBus Registers                                                                                  |    |

|                         | PMBus Arbiter Processor Priority Register                                                        |    |

|                         | PMBus Arbiter Sneak Access Control Register                                                      |    |

|                         | Memory and Peripheral Bus Arbitration                                                            |    |

|                         |                                                                                                  |    |

|                         | 6 Device Controller<br>Introduction                                                              | 6- |

|                         | Features                                                                                         | 6- |

|                         | Device Controller Register Description                                                           | 6- |

|                         | Theory of Operation                                                                              |    |

|                         | Device Control Registers                                                                         |    |

|                         | Device [05] Base Register                                                                        |    |

|                         | Device [05] Mask Register                                                                        |    |

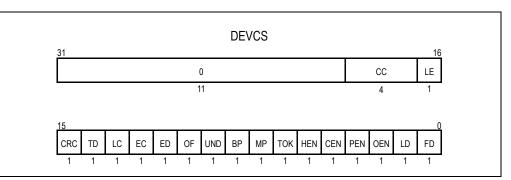

|                         | Device [05] Control Register                                                                     |    |

|                         | Device [05] Timing Control Register                                                              |    |

|                         | Memory And Peripheral Bus Transaction Timer                                                      |    |

|                         | Bus Transaction Timer Control and Status Register                                                |    |

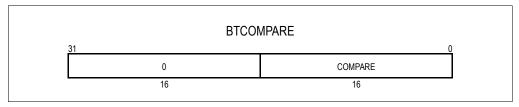

|                         | Bus Transaction Timer Compare Register                                                           |    |

|                         | Bus Transaction Timer Address Register                                                           |    |

|                         |                                                                                                  |    |

| ENESAS          |                                                     |     |

|-----------------|-----------------------------------------------------|-----|

| T Table of Cont | tents                                               |     |

| Notes           | Burst Device Read Transaction                       |     |

|                 | Device Write Transaction                            | 6-  |

|                 | Burst Device Write Transaction                      | 6-  |

|                 | Decoupled CPU Device Transactions                   | 6-  |

|                 | Device Decoupled Access Control and Status Register |     |

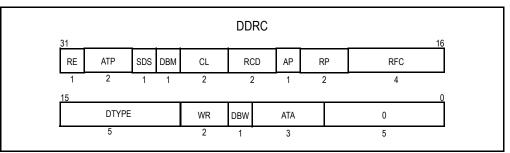

|                 | Device Decoupled Access Address Register            |     |

|                 | Device Decoupled Access Data Register               | 6-2 |

|                 | 7 DDR Controller                                    |     |

|                 | Introduction                                        | 7   |

|                 | Features                                            | 7   |

|                 | Additional Resources                                | 7   |

|                 | DDR Controller Register Description                 |     |

|                 | Theory of Operation                                 |     |

|                 | DDR Address Multiplexing Scheme                     |     |

|                 | DDR Command Encoding                                |     |

|                 | DDR Registers                                       |     |

|                 | DDR Control Register                                |     |

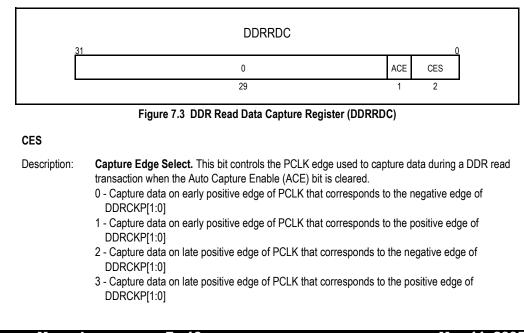

|                 | DDR Read Data Capture Register                      |     |

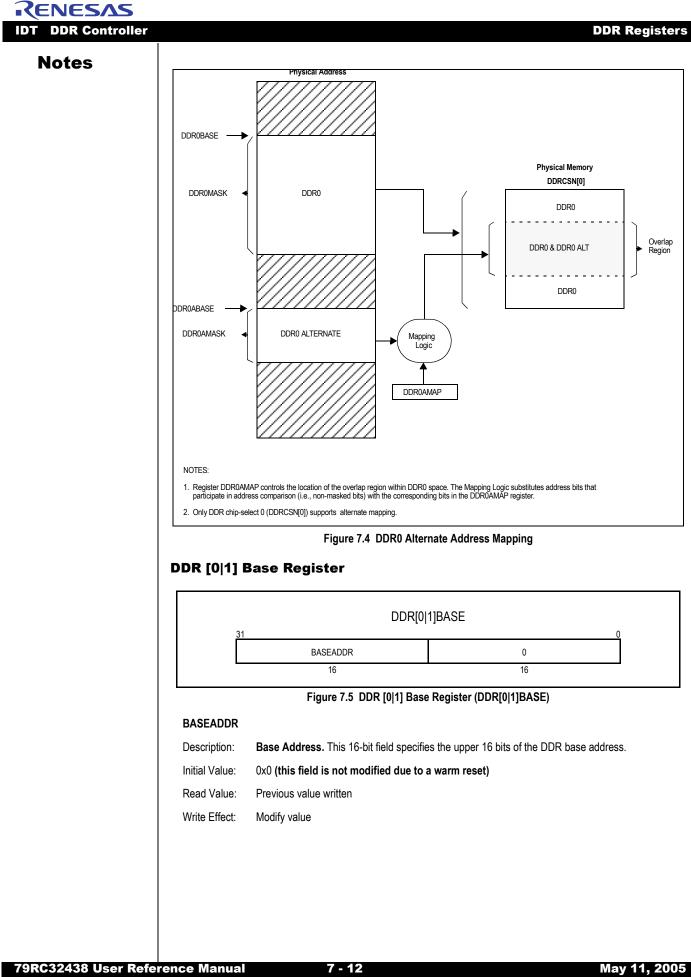

|                 | DDR Address Mapping                                 |     |

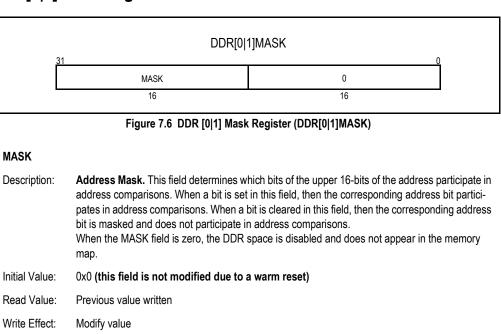

|                 | DDR [0 1] Base Register                             |     |

|                 | DDR [0 1] Mask Register                             |     |

|                 | DDR 0 Alternate Base Register                       | 7-  |

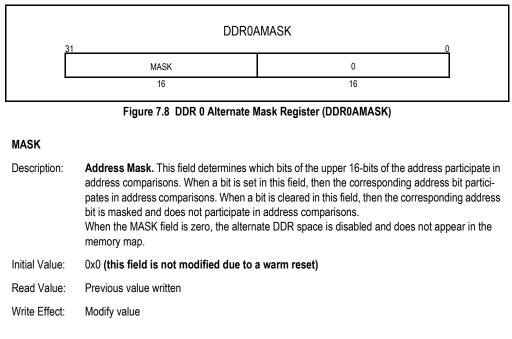

|                 | DDR 0 Alternate Mask Register                       | 7-  |

|                 | DDR 0 Alternate Mapping Register                    | 7-  |

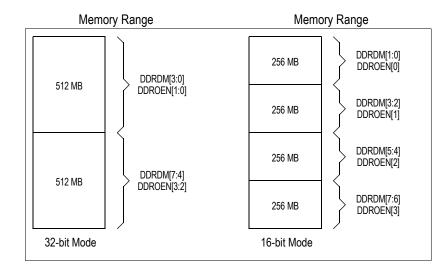

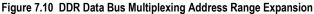

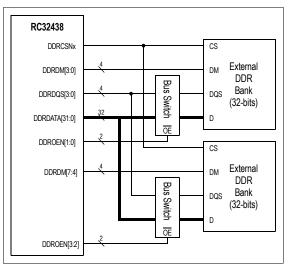

|                 | DDR Data Bus Multiplexing                           | 7-  |

|                 | DDR Initialization                                  | 7-  |

|                 | DDR Custom Transaction Register                     | 7-  |

|                 | DDR Refresh Timer                                   | 7-  |

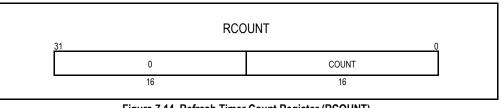

|                 | Refresh Timer Count Register                        | 7-  |

|                 | Refresh Timer Compare Register                      |     |

|                 | Refresh Timer Control Register                      | 7-  |

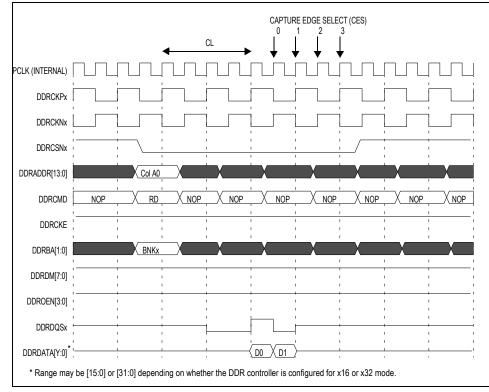

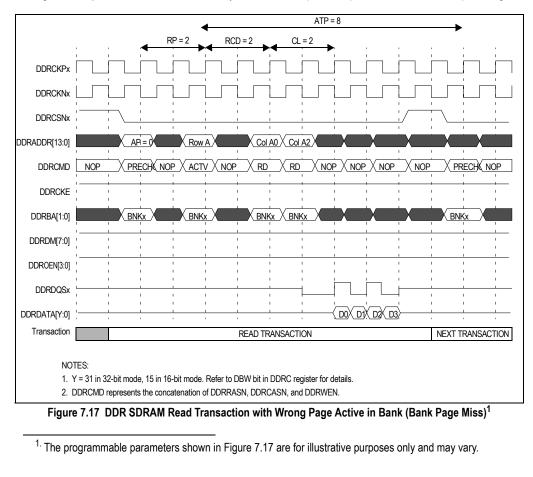

|                 | DDR Read Transaction                                | 7-2 |

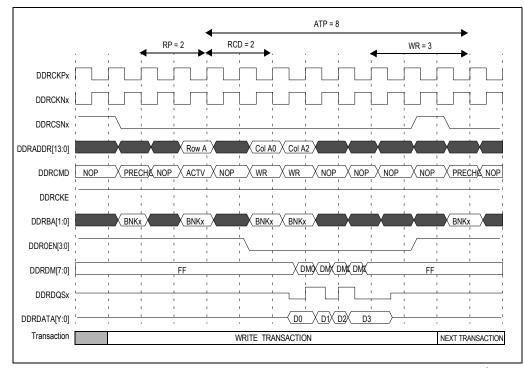

|                 | DDR Write Transaction                               | 7-2 |

|                 | DDR Refresh Transaction                             | 7-1 |

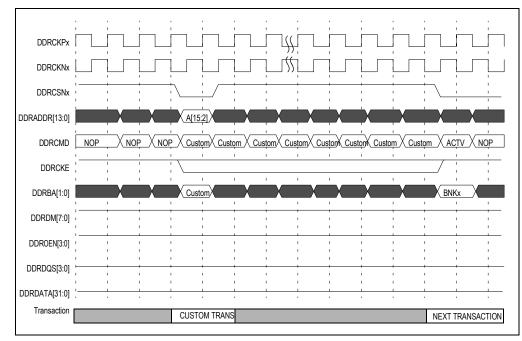

|                 | DDR Custom Transaction                              |     |

|                 | Example of DDR SDRAM Initialization                 |     |

|                 | 8 Interrupt Controller                              |     |

|                 | Introduction                                        | 8   |

|                 | Features                                            |     |

|                 |                                                     |     |

|                 | Block Diagram                                       |     |

|                 | Interrupt Controller Register Description           |     |

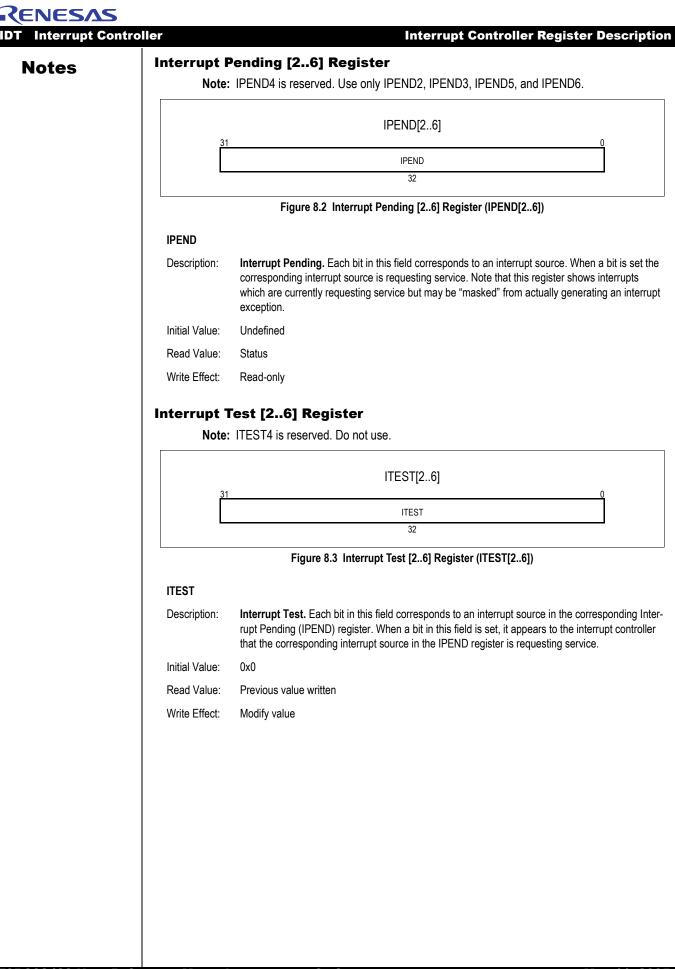

|                 | Interrupt Pending [26] Register                     |     |

|                 | Interrupt Test [2.6] Register                       |     |

|                 | Interrupt Mask [26] Register                        | ð   |

|      | Non-Maskable Interrupts                                                     | 8.6   |

|------|-----------------------------------------------------------------------------|-------|

| otes | Non-Maskable Interrupt Pin Status Register                                  |       |

|      | 9 DMA Controller                                                            |       |

|      | Introduction                                                                |       |

|      | Features                                                                    |       |

|      | DMA Registers                                                               |       |

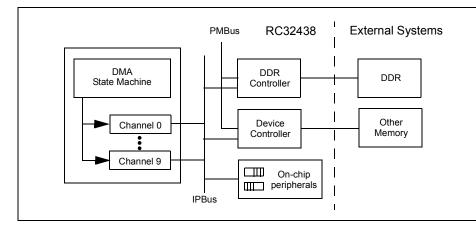

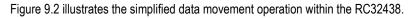

|      | Data Flow within the RC32438                                                |       |

|      | The IPBus™                                                                  |       |

|      | 4Kc Core as Bus Master                                                      |       |

|      | DMA Controller                                                              |       |

|      | No Alignment Restrictions                                                   |       |

|      | Data Flow Using the DMA Controller                                          |       |

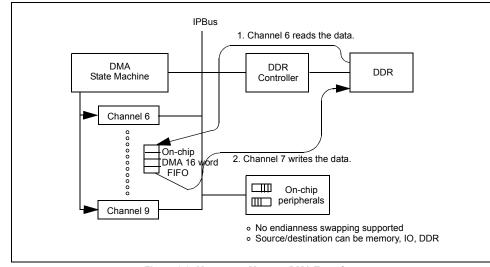

|      | Memory-to-Memory Transfer                                                   |       |

|      | DMA Channels                                                                |       |

|      | Internal DMA Operation                                                      |       |

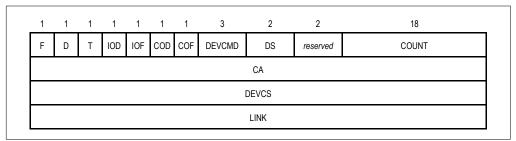

|      | DMA Descriptor Register                                                     |       |

|      | DMA Registers                                                               | 9-9   |

|      | DMA Stopping Conditions                                                     | 9-9   |

|      | DMA Request Event                                                           |       |

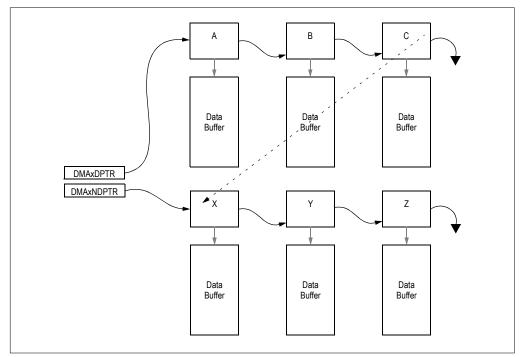

|      | DMA Descriptor List and Chaining                                            |       |

|      | DMA [09] Control Register                                                   |       |

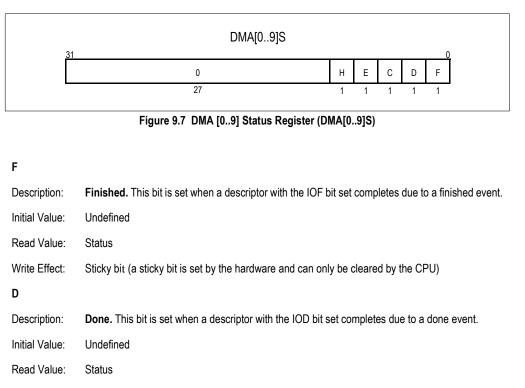

|      | DMA [09] Status Register                                                    |       |

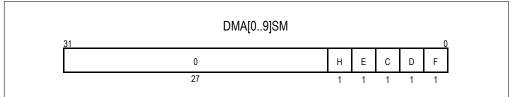

|      | DMA [09] Status Mask Register                                               |       |

|      | DMA [09] Descriptor Pointer Register                                        |       |

|      | DMA [09] Next Descriptor Pointer Register                                   |       |

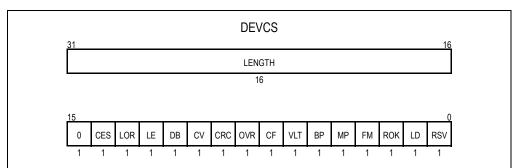

|      | External DMA Operations<br>Device Control and Status Field for External DMA |       |

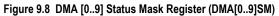

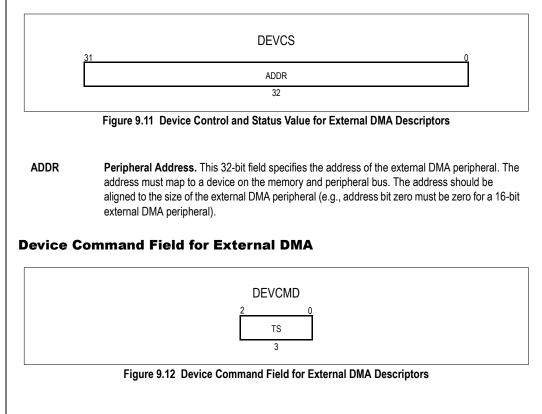

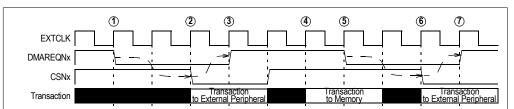

|      | Device Control and Status Field for External DMA                            |       |

|      |                                                                             |       |

|      | Memory to Memory DMA Operations<br>Examples                                 |       |

|      |                                                                             |       |

|      | 10 PCI Bus Interface Introduction                                           | 10.1  |

|      |                                                                             |       |

|      | Features                                                                    |       |

|      | Use of Decoupled PCI Transactions                                           |       |

|      | IPBus Access                                                                |       |

|      | PCI Register Description                                                    |       |

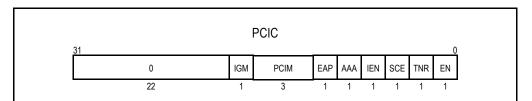

|      | PCI Control Register                                                        |       |

|      | PCI Status Register                                                         |       |

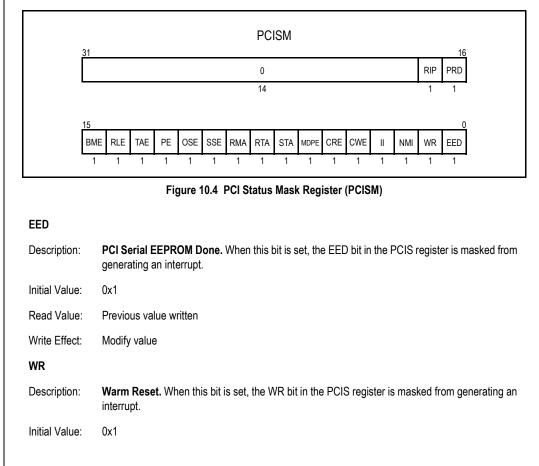

|      | PCI Status Mask Register                                                    |       |

|      | Reset                                                                       |       |

|      | Disabled Mode                                                               |       |

|      | PCI Host Mode                                                               |       |

|      | Reset and Initialization                                                    |       |

|      | Bus Arbitration                                                             | 10.14 |

| Notes | PCI Satellite Mode<br>Reset and Initialization    |      |

|-------|---------------------------------------------------|------|

|       | Bus Arbitration                                   |      |

|       |                                                   |      |

|       | Interrupts<br>PCI Serial EEPROM Interface         |      |

|       |                                                   |      |

|       | PCI Transactions                                  |      |

|       | Endianness and PCI Swapping                       |      |

|       | PCI Master                                        | 10-1 |

|       | Master I/O Read                                   | 10-1 |

|       | Master I/O Write                                  |      |

|       | Master Memory Read                                |      |

|       | Master Memory Write                               |      |

|       | Master Configuration Read                         |      |

|       | Master Configuration Write                        |      |

|       | Master Memory Read Line                           |      |

|       | Master Error Handling                             |      |

|       | PCI Configuration Address Register                |      |

|       | PCI Configuration Data Register                   |      |

|       | PCI Local Base Address [0 1 2 3] Register         |      |

|       | PCI Local Base Address [0 1 2 3] Control          |      |

|       | PCI Local Base Address [0 1 2 3] Mapping Register |      |

|       | Decoupled PCI Master Transactions                 |      |

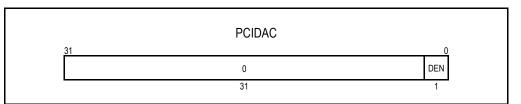

|       | PCI Decoupled Access Control Register             |      |

|       | PCI Decoupled Access Status Register              |      |

|       | PCI Decoupled Access Status Mask Register         |      |

|       | PCI Decoupled Access Data Register                |      |

|       | PCI Master—PCI to Memory DMA (DMA Channel 8)      |      |

|       | Channel 8 Memory Read                             |      |

|       | Channel 8 Memory Read Multiple                    |      |

|       | Channel 8 Memory Read Line                        |      |

|       | Channel 8 I/O Read                                |      |

|       | Channel 8 Error Handling                          |      |

|       | PCI DMA Channel 8 Configuration Register          |      |

|       | PCI Master — Memory to PCI DMA (DMA Channel 9)    |      |

|       | Channel 9 Memory Write                            |      |

|       | Channel 9 Memory Write and Invalidate             |      |

|       | Channel 9 I/O Write                               |      |

|       | Channel 9 Error Handling                          |      |

|       | PCI DMA Channel 9 Configuration Register          |      |

|       | PCI Target                                        |      |

|       | Target I/O Read                                   |      |

|       | Target I/O Write                                  |      |

|       | Target Memory Read                                |      |

|       | Target Memory Write                               |      |

|       | Target Configuration Read                         |      |

|       | Target Configuration Write                        |      |

|       | Target Memory Read Multiple                       |      |

|       | Target Memory Read Line                           |      |

|       | Target Memory Write and Invalidate                |      |

|       | Target Error Handling                             |      |

| Table of Conte |                                                                        |          |

|----------------|------------------------------------------------------------------------|----------|

| Notes          | PCI Target Control Register                                            |          |

| NULES          | Transaction Ordering                                                   |          |

|                | PCI Messaging Unit                                                     |          |

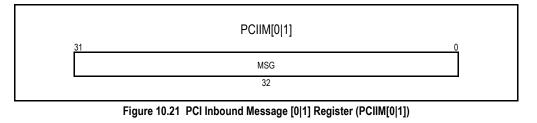

|                | PCI Inbound Message [0 1] Register                                     |          |

|                | PCI Outbound Message [0 1] Register                                    |          |

|                | PCI Inbound Doorbell Register                                          |          |

|                | PCI Inbound Interrupt Cause Register                                   |          |

|                | PCI Inbound Interrupt Mask Register                                    |          |

|                | PCI Outbound Doorbell Register                                         |          |

|                | PCI Outbound Interrupt Cause Register                                  |          |

|                | PCI Outbound Interrupt Mask Register                                   |          |

|                | PCI Configuration Registers                                            |          |

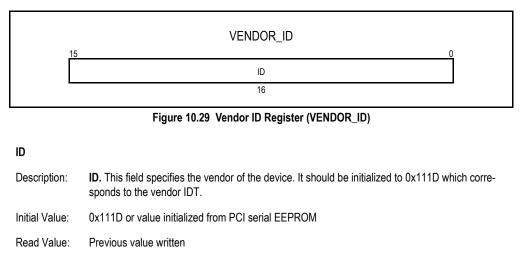

|                | Vendor ID Register                                                     |          |

|                | Device ID Register                                                     |          |

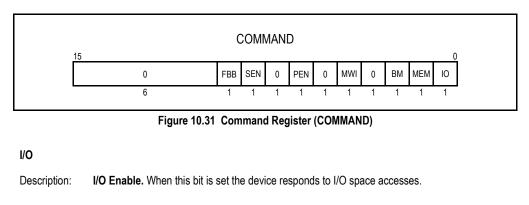

|                | Command Register                                                       |          |

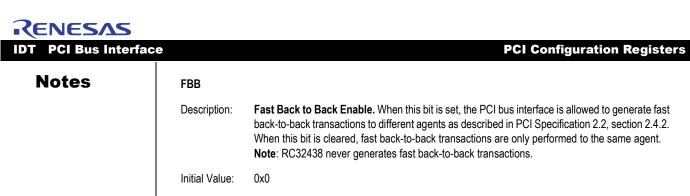

|                | Status Register                                                        |          |

|                | Device Revision ID Register                                            | 10       |

|                | Class Code Register                                                    | 10       |

|                | Cache Line Size Register                                               | 10       |

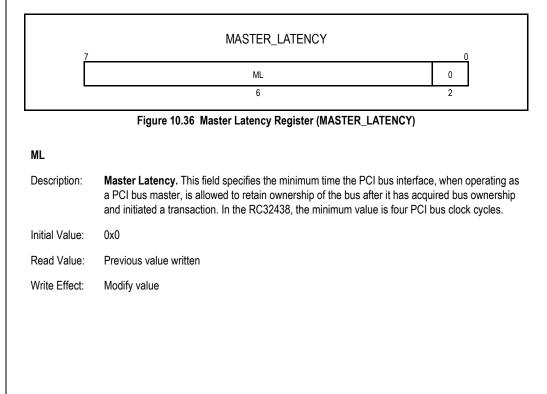

|                | Master Latency Register                                                |          |

|                | Header Type Register                                                   |          |

|                | BIST Register                                                          |          |

|                | PCI Base Address [0 1 2 3] Register                                    |          |

|                | Subsystem Vendor ID                                                    |          |

|                | Subsystem ID Register                                                  |          |

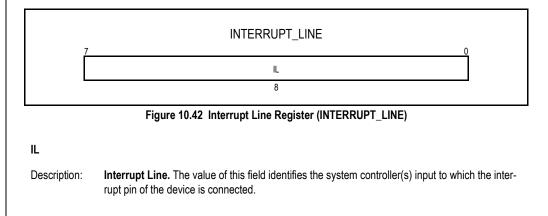

|                | Interrupt Line Register                                                |          |

|                | Interrupt Pin Register                                                 |          |

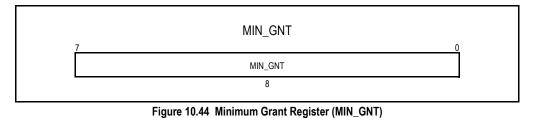

|                | Minimum Grant Register                                                 |          |

|                | Maximum Latency Register                                               |          |

|                | Target Ready Time-out Register                                         |          |

|                | Retry Limit Register                                                   | IU       |

|                | PCI Base Address [0]1 2 3] Control                                     |          |

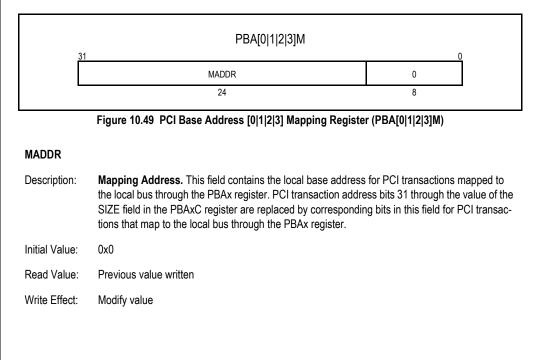

|                | PCI Base Address [0 1 2 3] Mapping Register<br>PCI Management Register |          |

|                | 11 Ethernet Interfaces                                                 |          |

|                | Introduction                                                           |          |

|                | Features                                                               |          |

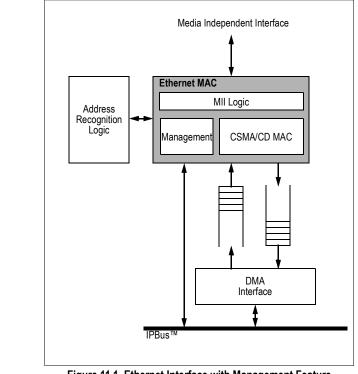

|                | Block Diagram                                                          |          |

|                |                                                                        |          |

|                | Functional Overview                                                    |          |

|                | Input and Output FIFOs                                                 | ······ ′ |

|                | Ethernet Register Description                                          |          |

|                | Ethernet Interface Control Register                                    | ······ ′ |

|                | Ethernet FIFO Transmit Threshold Register                              | 1        |

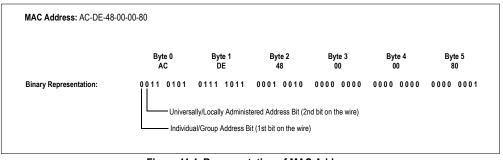

|                | Address Recognition Logic                                              | ·····    |

|                | Ethernet Address Recognition Control Register                          |          |

|                | Ethernet Hash Table [0 1] Register                                     |          |

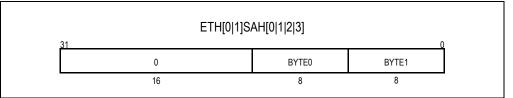

|                | Ethernet Station Address [0 1 2 3] Low Register                        |          |

|                | Ethernet Station Address [0 1 2 3] High Register                       |          |

| <b>RENESAS</b> | nts                                                 |       |

|----------------|-----------------------------------------------------|-------|

| Notes          | DMA Interface                                       |       |

| NULES          | Ethernet Input DMA Operations                       | 11-12 |

|                | Ethernet Output DMA Operations                      | 11-14 |

|                | Ethernet Statistics                                 | 11-16 |

|                | Ethernet Receive Byte Count Register                | 11-16 |

|                | Ethernet Receive Packet Count Register              | 11-17 |

|                | Ethernet Receive Undersized Packet Count Register   | 11-17 |

|                | Ethernet Receive Fragment Count Register            | 11-18 |

|                | Ethernet Transmit Byte Count Register               | 11-18 |

|                | PAUSE Control Frames                                | 11-18 |

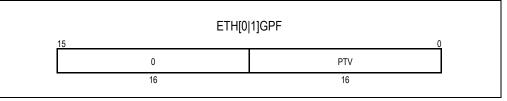

|                | Ethernet Generate Pause Frame Register              | 11-19 |

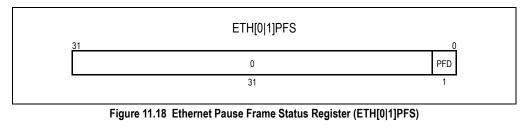

|                | Ethernet Pause Frame Status Register                | 11-19 |

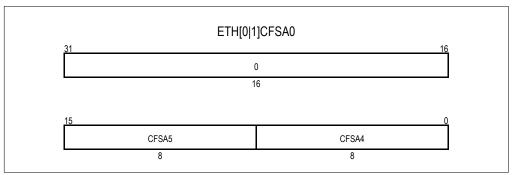

|                | Ethernet Control Frame Station Address 0 Register   | 11-20 |

|                | Ethernet Control Frame Station Address 1 Register   | 11-21 |

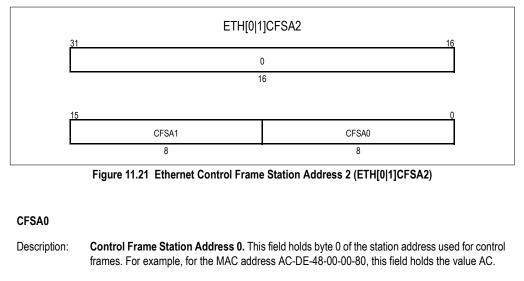

|                | Ethernet Control Frame Station Address 2 Register   | 11-21 |

|                | Ethernet Medium Access Controller (MAC)             | 11-22 |

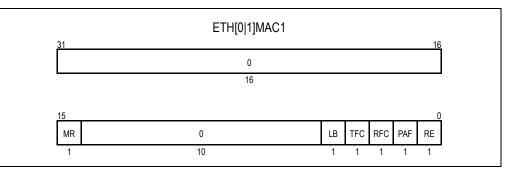

|                | Ethernet MAC Configuration Register #1              | 11-22 |

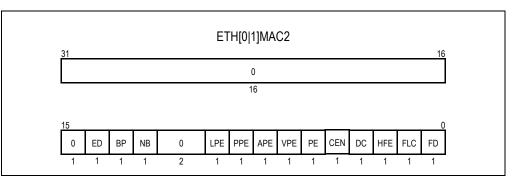

|                | Ethernet MAC Configuration Register #2              | 11-23 |

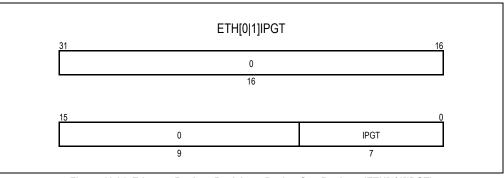

|                | Ethernet Back-to-Back Inter-Packet Gap Register     | 11-27 |

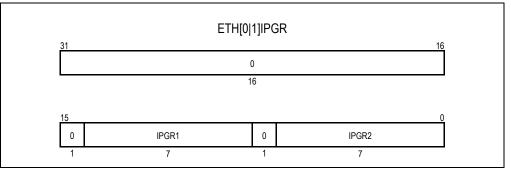

|                | Ethernet Non Back-to-Back Inter-Packet Gap Register | 11-27 |

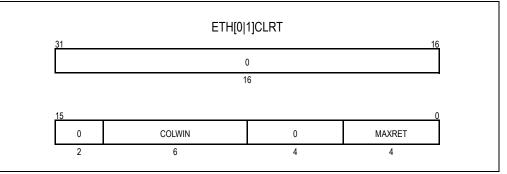

|                | Ethernet Collision Window and Retry Register        | 11-28 |

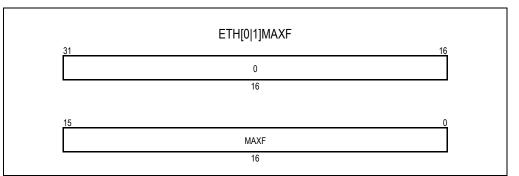

|                | Ethernet Maximum Frame Length Register              | 11-29 |

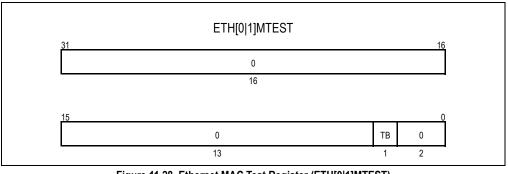

|                | Ethernet MAC Test Register                          | 11-29 |

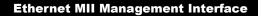

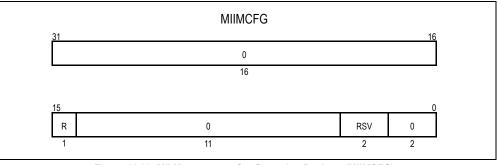

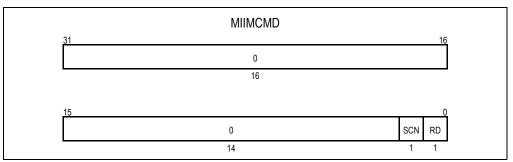

|                | Ethernet MII Management Interface                   | 11-30 |

|                | MII Management Configuration Register               | 11-30 |

|                | MII Management Command Register                     | 11-31 |

|                | MII Management Address Register                     |       |

|                | MII Management Write Data Register                  |       |

|                | MII Management Read Data Register                   |       |

|                | MII Management Indicators Register                  | 11-33 |

|                | Ethernet Clock Prescalar                            | 11-34 |

|                | Programming Example                                 | 11-34 |

|                | 12 General Purpose I/O Controller                   |       |

|                | Introduction                                        |       |

|                | Functional Overview                                 | 12-1  |

|                | Theory of Operation                                 |       |

|                | GPIO Pin Configured As Input                        |       |

|                | GPIO Pin Configured As Output                       |       |

|                | GPIO Pin Configured As an Alternate Function        |       |

|                | GPIO Pins As Interrupt Sources                      |       |

|                | GPIO Pins As Non-maskable Interrupt Sources         |       |

|                | General Purpose I/O Register Description            |       |

|                | GPIO Function Register                              |       |

|                | GPIO Function Register                              |       |

|                | GPIO Data Register                                  |       |

|                | GPIO Data Register                                  |       |

|                | GPIO Interrupt Status Register                      |       |

|                |                                                     |       |

|       | 42 LIADT Constraller                                      |     |

|-------|-----------------------------------------------------------|-----|

| Notes | 13 UART Controller                                        | 40  |

|       | Introduction                                              |     |

|       | Features                                                  |     |

|       | Functional Overview                                       |     |

|       | UART Register Description                                 | 13  |

|       | Baud Rate Selection                                       | 13  |

|       | UART Interrupts                                           |     |

|       | UART Channel Reset                                        | 13  |

|       | UART Registers                                            |     |

|       | Reset Register                                            |     |

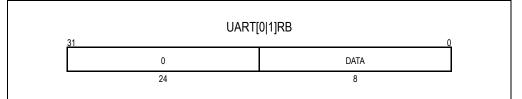

|       | Receive Buffer Register                                   | 13  |

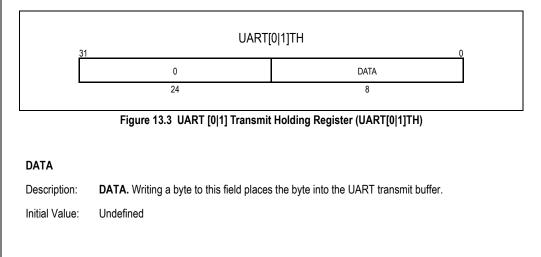

|       | Transmit Holding Register                                 |     |

|       | Interrupt Enable Register                                 | 13  |

|       | Interrupt Identification Register                         |     |

|       | FIFO Control Register                                     |     |

|       | Line Control Register                                     |     |

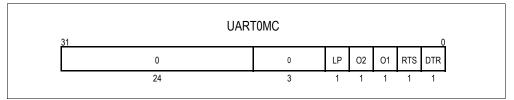

|       | Modem Control Register                                    |     |

|       | Line Status Register                                      |     |

|       | Modem Status Register                                     |     |

|       | Scratch Register                                          |     |

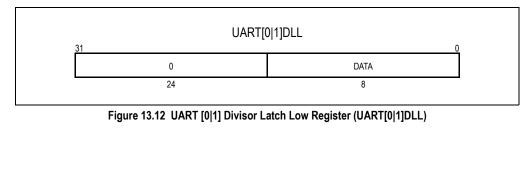

|       | Divisor Latch Low Register<br>Divisor Latch High Register |     |

|       |                                                           |     |

|       | 14 Counter/Timers                                         |     |

|       | Functional Overview                                       |     |

|       | Counter/Timers Register Description                       | 14  |

|       | Theory of Operation                                       |     |

|       | Counter Timer [0 1 2] Count Register                      |     |

|       | Counter Timer [0 1 2] Compare Register                    |     |

|       | Counter Timer [0 1 2] Control Register                    | 14  |

|       | 15 I2C Bus Interface                                      |     |

|       | Introduction                                              | 15  |

|       | Features                                                  | 15  |

|       | Block Diagram                                             |     |

|       | Functional Overview and Theory of Operation               |     |

|       | I2C Register Description                                  |     |

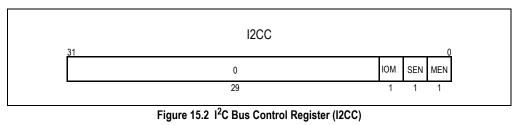

|       | I <sup>2</sup> C Bus Control Register                     |     |

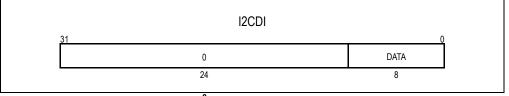

|       | I2C Bus Data Input Register                               |     |

|       | I2C Bus Data Input Register                               |     |

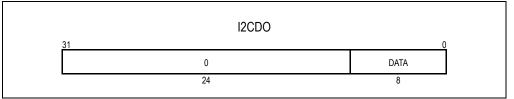

|       | I2C Bus Data Output Negister                              |     |

|       |                                                           |     |

|       | I2C Bus Master Interface                                  |     |

|       | Example I2C Bus Transactions                              |     |

|       | I2C Bus Master Command Register                           |     |

|       | I2C Bus Master Status Register                            |     |

|       | I2C Bus Master Status Mask Register                       | 1 - |

| le of Conten |                                              |       |

|--------------|----------------------------------------------|-------|

| es           | Example of I2C Bus Transaction               |       |

|              | I2C Bus Slave Status Register                |       |

|              | I2C Bus Slave Status Mask Register           |       |

|              | I2C Bus Slave Address Register               |       |

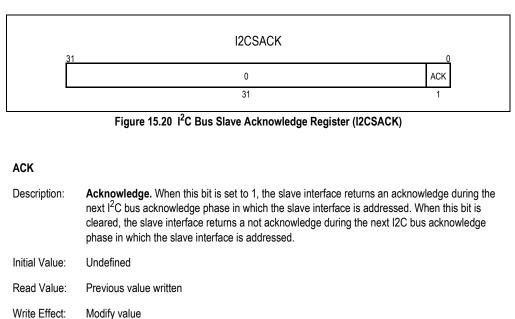

|              | I2C Bus Slave Acknowledge Register           |       |

|              | Programming Example                          |       |

|              | 16 Serial Peripheral Interface               |       |

|              | Introduction                                 |       |

|              | Block Diagram                                |       |

|              | SPI Register Description                     |       |

|              | Functional Overview                          |       |

|              | PCI Serial EEPROM Mode (Microwire)           |       |

|              | SPI Interface Mode                           |       |

|              | SPI Clock Prescalar                          |       |

|              | Clock Prescalar Register                     |       |

|              | SPI Control Register                         |       |

|              | SPI Status Register                          |       |

|              | SPI Data Register                            |       |

|              | SPI Setup                                    |       |

|              | Serial Bit I/O Pins                          |       |

|              | Serial I/O Function Register                 |       |

|              | Serial I/O Configuration Register            |       |

|              | Serial I/O Data Register                     |       |

|              | Master Programming Example                   |       |

|              | SPI Initialization                           |       |

|              | 17 On-Chip Memory                            |       |

|              |                                              | 47 4  |

|              |                                              |       |

|              | Theory of Operation                          |       |

|              | On-chip Memory Base Register                 |       |

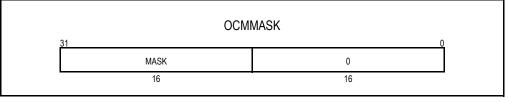

|              | On-chip Memory Mask Register                 |       |

|              | 18 Debugging and Performance Monitoring      |       |

|              | Introduction                                 |       |

|              | Features                                     |       |

|              | Debug and Performance Register Description   |       |

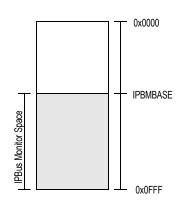

|              | IPBus Monitor                                |       |

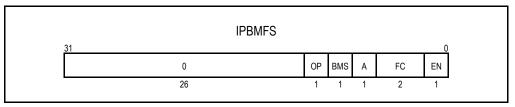

|              | IPBus Monitor Registers                      |       |

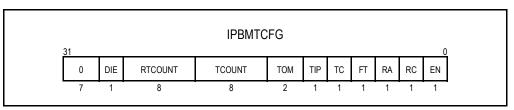

|              | IPBus Monitor Trigger Configuration Register |       |

|              | IPBus Monitor Trigger Select Register        |       |

|              | IPBus Monitor Manual Trigger Register        |       |

|              | IPBus Monitor Trigger Condition 0 Register   |       |

|              | IPBus Monitor Trigger Condition of Register  |       |

|              | IPBus Monitor Trigger Condition 7 Register   |       |

|              |                                              |       |

|              | IPBus Monitor Trigger Condition 3 Register   | 18-10 |

| IPBus Monitor Filter Control 0 Register |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| C C                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Event Monitor 0 Compare Register        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Debug Pins                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

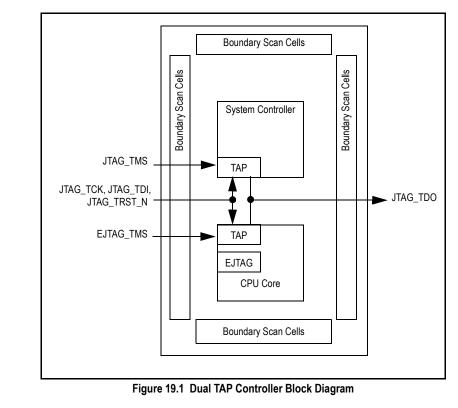

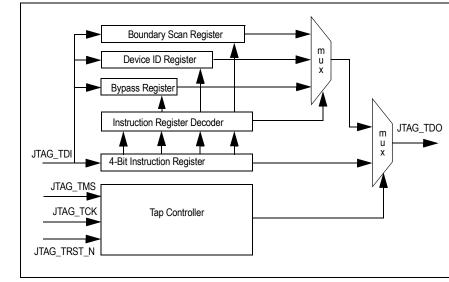

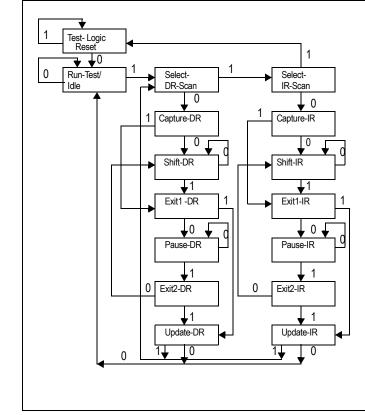

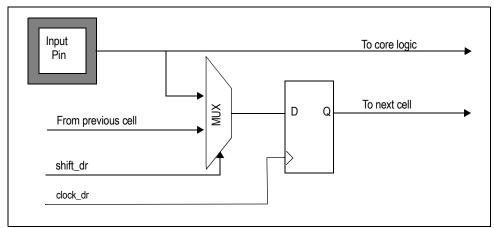

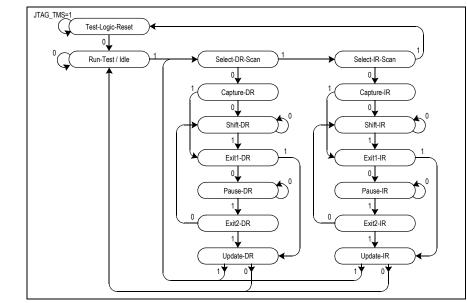

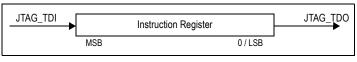

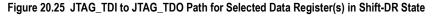

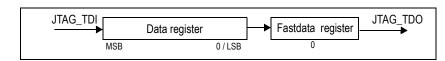

| 19 JTAG Boundary Scan                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| System Logic TAP Controller Overview    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Signal Definitions                      | 19-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Test Data Register (DR)                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| - · · ·                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| • • • •                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Usage Considerations                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20 EJTAG System                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Introduction                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

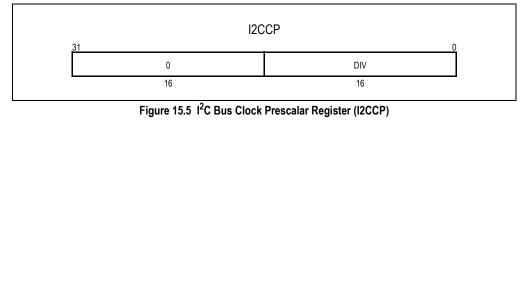

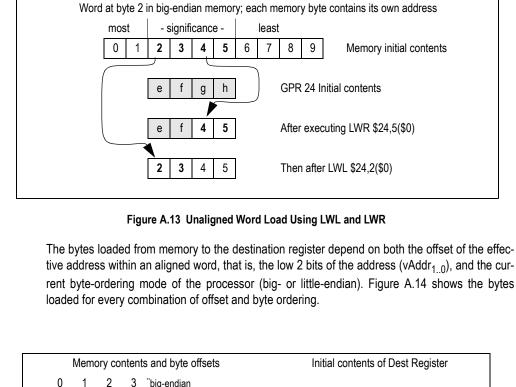

| Functional Description                  | 20-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |