## **ZSPM4121 Evaluation Kit Description**

#### Restrictions:

IDT's ZSPM4121 Evaluation Kit is designed for evaluation of the ZSPM4121, laboratory setup, and module development only. This kit must not be used for module production and production test setups

IDT shall not be liable for any damages arising out of defects resulting from (i) delivered hardware (ii) non-observance of instructions contained in this manual, or (iii) misuse, abuse, use under abnormal conditions or alteration by anyone other than IDT. To the extent permitted by law, IDT hereby expressly disclaims and User expressly waives any and all warranties, whether express, implied, or statutory, including, without limitation, implied warranties of merchantability and of fitness for a particular purpose, statutory warranty of non-infringement and any other warranty that may arise by reason of usage of trade, custom, or course of dealing.

## **Contents**

| Kit Contents               | 2                                                                                                                                                               |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction               | 2                                                                                                                                                               |

|                            |                                                                                                                                                                 |

|                            |                                                                                                                                                                 |

|                            |                                                                                                                                                                 |

| Evaluation Board Schematic | 4                                                                                                                                                               |

|                            |                                                                                                                                                                 |

|                            |                                                                                                                                                                 |

| Document Revision History  | 6                                                                                                                                                               |

|                            | Kit Contents Introduction Connectors Probe and Test Points Setup Evaluation Board Schematic Evaluation Board Layout Related Documents Document Revision History |

### 1 Kit Contents

- ZSPM4121 Evaluation Board

- Kit Documentation

### 2 Introduction

The ZSPM4121 Evaluation Board is a compact system intended to facilitate measuring the performance and operating characteristics of the ZSPM4121 Under-Voltage Load Switch. The board contains a number of test points to allow evaluating the functions of the ZSPM4121 (see Figure 2.1 and section 4). It has a solid ground plane.

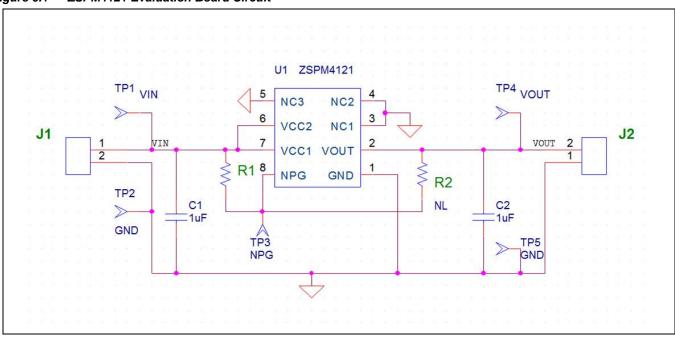

Note: The default part number for the ZSPM4121 Under-Voltage Load Switch (U1 in the schematic in Figure 6.1) is ZSPM4121AI1 Wxx, where xx refers to the factory-configured voltage threshold which is determined by the version of the ZSPM4121 Evaluation Board ordered. Contact IDT for available board versions.

Note: The default configuration of the Evaluation Board is with the NPG pin pulled up to Vin via R1 and therefore R2 is unpopulated (NL designation in the schematic in Figure 6.1). If the application requires that NPG be pulled up to Vout, remove R1 and install R2.

Test Point TP1 (Vin) Test Point TP4 (Vout) (Kelvin connection for accurate voltage measurements) (Kelvin connection for accurate voltage measurements) J1 Vin+ Supply J2 Vout+ Input Post **Output Post** J1 Supply GND J2 GND Input Post **Output Post** ZSPM4121 Pin 1 Test Point TP5 Test Point TP2

Figure 2.1 ZSPM4121 Evaluation Board Connections

(GND for Vout Measurements)

Test Point TP3

(NPG output pin; low="Power Good")

(GND for Vin Measurements)

#### 3 Connectors

The board contains the following connectors to external signals and supplies (see Figure 2.1):

**J1:** Screw terminal connection for Vin supply (Vin+ and GND)

**J2:** Screw terminal connection to Vout output (Vout+ and GND)

### 4 Probe and Test Points

The board contains the following test/probe points (see Figure 2.1):

**TP1/Vin:** Kelvin measurement test point for Vin main input **TP4/Vout:** Kelvin measurement test point for Vout output

TP3/NPG: Measurement point for the ZSPM4121's open-drain N-channel NPG output pin 8 (low indicates

"Power Good")

**TP2/GND:** Test point for ground; recommended ground for accurate measurements for Vin **TP5/GND:** Test point for ground; recommended ground for accurate measurements for Vout

## 5 Setup

Connect the input voltage supply for the ZSPM4121 at the J1 screw terminal with the leads connected shown in Figure 2.1.

The output of the Evaluation Board can be measured at the J2 screw terminal.

Recommendation: Use J1 and J2 only for power connections. Use test points TP1 (Vin) and TP4 (Vout) as Kelvin connections for accurate voltage measurements (see Figure 2.1).

## 6 Evaluation Board Schematic

Figure 6.1 ZSPM4121 Evaluation Board Circuit

Table 6.1 ZSPM4121 Evaluation Board Bill of Materials (BOM)

| QTY | Reference | Description                     | Manufacturer | Manufacturer P/N | Digikey P/N         |

|-----|-----------|---------------------------------|--------------|------------------|---------------------|

| 1   | U1        | ZSPM4121                        | IDT          | ZSPM4121AI1Wxx*  | N/A                 |

| 2   | C1        | CAP CER 1UF 25V<br>10% X5R 0603 | TDK          | C1608X5R1E105K   | 445-5146-2-ND       |

|     | C2        | CAP CER 1UF 25V<br>10% X5R 0603 | TDK          | C1608X5R1E105K   | 445-5146-2-ND       |

| 1   | R1        | RES 1K OHM 1/10W<br>5% 0603 SMD | Stackpole    | RMCF0603JT1K00   | RMCF0603JT1K00CT-ND |

| 0   | R2        | Do not populate                 |              |                  |                     |

| 5   | TP1       | Test Point                      | Keystone     | 5001K-ND         | 5001                |

|     | TP2       | Test Point                      | Keystone     | 5001K-ND         | 5001                |

|     | TP3       | Test Point                      | Keystone     | 5001K-ND         | 5001                |

|     | TP4       | Test Point                      | Keystone     | 5001K-ND         | 5001                |

|     | TP5       | Test Point                      | Keystone     | 5001K-ND         | 5001                |

<sup>\*</sup> xx refers to the factory-configured voltage threshold, which is determined by the version of the ZSPM4121 Evaluation Board ordered. Contact IDT for available board versions.

| QTY | Reference | Description                      | Manufacturer            | Manufacturer P/N | Digikey P/N |

|-----|-----------|----------------------------------|-------------------------|------------------|-------------|

| 2   | J1, J2    | TERMINAL BLOCK<br>3.5MM 2POS PCB | On Shore Technology Inc | ED555/2DS        | ED1514-ND   |

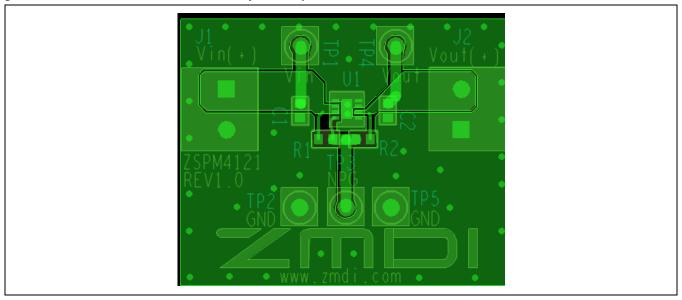

# 7 Evaluation Board Layout

Figure 7.1 ZSPM4121 Evaluation Board Layout – Top View

## **8 Related Documents**

| File Name              |

|------------------------|

| ZSPM4121 Data Sheet    |

| ZSPM4121 Feature Sheet |

Visit <a href="https://www.IDT.com/ZSPM4121">www.IDT.com/ZSPM4121</a> or contact your nearest sales office for the latest version of these documents.

# 9 Document Revision History

| Revision | Date              | Description              |

|----------|-------------------|--------------------------|

| 1.00     | November 14, 2012 | First release.           |

|          | April 14, 2016    | Changed to IDT branding. |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.