## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# R0P3219TR001MRK

## General Infomation Manual Renesas M32192 µT-Engine Board Set

#### Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/ or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

## Preface

Thank you very much for purchasing the R0P3219TR001MRK (hereafter, M32192  $\mu$ T-Engine), the  $\mu$ T-Engine board set incorporating the Renesas M32192.

The M32192  $\mu$ T-Engine is a board set for software evaluation that incorporates the 32-bit microcontroller M32192 made by Renesas Technology. This product is manufactured to  $\mu$ T-Engine specification.

This manual describes mainly specifications of the M32192  $\mu$ T-Engine and how to set it up. For information on the software supplied with it, please refer to on-line manuals for each product. The latest versions of the related documents are available from the Renesas Technology Corp Web site (http://www.renesas.com/).

The contents of the package of this product are listed in "1.3 Package Components" so refer to the list for confirmation. If there is anything you have noticed about the product, please contact your local distributor.

## Important

Before using this product, be sure to read the user's manual (this user's manual) carefully. Keep this user's manual, and refer to this when you have questions about this product.

#### About this product:

The term "this product" referred to herein means the product manufactured by Renesas Technology Corporation. It does not include the user systems and host machines of the customers.

#### Purpose of use of this product:

This product is a device to support the development of a system that uses the M32R Family M32R/ECU Series M32192 of Renesas 32-bit single-chip MCUs. It provides support for system development in both software and hardware. Be sure to use this product correctly according to said purpose of use. Please avoid using this product for other than its intended purpose of use.

#### For those who use this product:

This product can only be used by those who have carefully read the user's manual and know how to use it. Use of this product requires the basic knowledge of electric circuits, logical circuits, and MCUs.

#### When using this product:

- (1) This product is a development supporting unit for use in your program development and evaluation stages. In mass-producing your program you have finished developing, be sure to make a judgment on your own risk that it can be put to practical use by performing integration test, evaluation, or some experiment else.

- (2) In no event shall Renesas Solutions Corp. be liable for any consequence arising from the use of this product.

- (3) Renesas Solutions Corp. strives to renovate or provide a workaround for product malfunction at some charge or without charge. However, this does not necessarily mean that Renesas Solutions Corp. guarantees the renovation or the provision under any circumstances.

- (4) This product has been developed by assuming its use for program development and evaluation in laboratories. Therefore, it does not fall under the application of Electrical Appliance and Material Safety Law and protection against electromagnetic interference when used in Japan.

- (5) Renesas Solutions Corp. cannot predict all possible situations or possible cases of misuse where a potential danger exists. Therefore, the warnings written in this user's manual and the warning labels attached to this product do not necessarily cover all of such possible situations or cases. Please be sure to use this product correctly and safely on your own responsibility.

- (6) This product is designed for use in program development and evaluation stages. It cannot be embedded in your product for mass-production purposes.

- (7) Even if this product has a deficiency in its internal microcomputer, it will not be replaced with a product which has had the microcomputer deficiencies corrected.

- (8) No parts incorporated in this product may be dismantled for diverted use in other products.

- (9) The software stored in the ROM of this product may not be copied, in whole or part, for use in other hardware.

- (10) The CF and MMC cannot be guaranteed to be capable of operating in all devices.

- (11) The LAN interface cannot be guaranteed to be connectable to all pieces of equipment.

#### Usage restrictions:

This product has been developed as a means of supporting system development by users. Therefore, do not use it as a device used for equipment-embedded applications. Also, do not use it for developing the systems or equipment used for the following purposes either:

- (1) Transportation and vehicular

- (2) Medical (equipment where human life is concerned)

- (3) Aerospace

- (4) Nuclear power control

- (5) Undersea repeater

If you are considering the use of this product for one of the above purposes, please be sure to consult your local distributor.

#### About product changes:

We are constantly making efforts to improve the design and performance of this product. Therefore, the specification or design of this product or its user's manual may be changed without prior notice.

#### About the rights:

- (1) We assume no responsibility for any damage or infringement on patent rights or any other rights arising from the use of any information, products or circuits presented in this user's manual.

- (2) The information or data in this user's manual does not implicitly or otherwise grant a license for patent rights or any other rights belonging to us or third parties.

- (3) This user's manual and this product are copyrighted, with all rights reserved by us. This user's manual may not be copied, duplicated or reproduced, in whole or part, without prior written consent of us.

#### About diagrams:

The diagrams in this user's manual may not all represent exactly the actual object.

- \* CompactFlash <sup>™</sup> is a trademark of SanDisk Corporation.

- \* MultiMediaCard <sup>™</sup> is a trademark of Infineon Technologies AG.

### Precautions for Safety

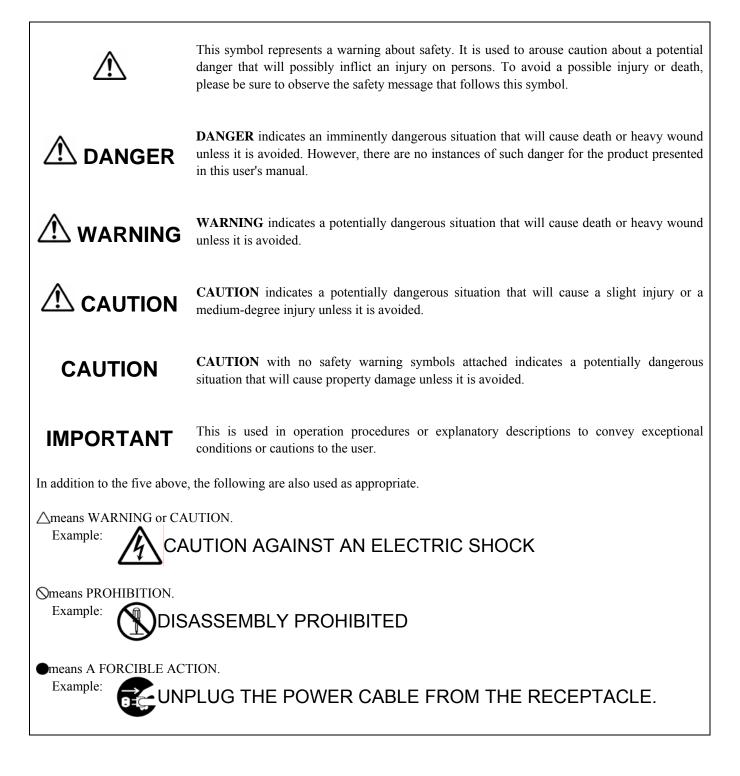

#### **Definitions of Signal Words**

In both the user's manual and on the product itself, several icons are used to insure proper handling of this product and also to prevent injuries to you or other persons, or damage to your properties.

This chapter describes the precautions which should be taken in order to use this product safely and properly. Be sure to read this chapter before using this product.

| Cautions for AC Adapter:                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • Before installing this equipment or connecting it to other equipment, disconnect the AC power cable from its outlet to prevent injury or accident.                                              |

| • The DC plug on the included AC adapter has the below polarity.                                                                                                                                  |

|                                                                                                                                                                                                   |

| About the Power-on Sequence:                                                                                                                                                                      |

| • Once the power is turned off, wait for about 10 seconds before turning it back on again.                                                                                                        |

| About Handling of the Product:                                                                                                                                                                    |

| • Handle the product with caution, taking care not to apply strong mechanical shock to the product by dropping or letting it fall down.                                                           |

| • Do not touch the communication interface connector pins or other connector pins directly with your hand. Static electricity from your body may break down the internal circuit of the product.  |

| • Do not pull the product by the cable connecting to a board in it. Do not hold down a board while you pull the other end of it. The cable may break.                                             |

| • Do not use inch-sized screws for the product. All of the screws used in it are the ISO type (metric size). When replacing screws, be sure to use the same type of screw that is currently used. |

## **User Registration**

When you've purchased the product, please be sure to make an entry on user registry of Renesas. For information on our policy concerning the protection of personal information, please refer to the Renesas Technology Corp. Homepage.

URL: http://www.renesas.com/

The information we receive via the User Registration Form aids us greatly in our customer support activities. We provide Renesas Technology and related companies, distributors, etc., with essential user information (electronically or on paper) that will further help them provide customer support.

If you do not wish to have your user information provided to other related companies, please contact us to let us know. Note, however, this will limit our ability to provide complete product support.

If your name is not registered, you will not be eligible to receive notification of fault information or other maintenance services. So please be sure to register your name with Renesas.

For user registration, please contact your local distributor.

#### Contents

| 1. Overview       11         1.1 Product Outline       11         1.2 System Configuration       11         1.3 Package Components       12         1.4 External Specifications       13         1.5 Functional Blocks       15         1.6 Address Map       16         2. Functional Specifications       17         2.1 The CPU       17         2.2 Memory       21         2.3 Control PLD       21         2.4 CompactFlash Interface       21         2.5 MINC Card Interface       22         2.7 Debug Serial Interface       22         2.8 Real-Interface       22         2.9 Prover Supply Circuit       23         2.1 Reset Module       24         2.1 Scanto Connector       26         2.1 S CAN Communication Connector       26 <t< th=""><th></th><th>Page</th></t<>                                            |                                | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|

| 1 2 System Configuration       11         1 3 Package Components       12         1 4 External Specifications       13         1 5 Functional Blocks       15         1 6 Address Map       16         2. Functional Specifications       17         2.1 The CPU       17         2.1 The CPU       17         2.1 The CPU       17         2.3 Control PLD       21         2.4 CompactHash Interface       21         2.5 MMC Interface       21         2.6 ETRON Card Interface       22         2.7 Debug Serial Interface       22         2.8 Power Supply Circuit       22         2.9 Power Supply Circuit       23         2.1 Dickok Module       23         2.1 IN Switch Module       24         2.1 Stension CAN Signal Connector       24         2.1 S ACmers Board Connector       26         2.1 B XIT Switch Module       27         2.1 Particle Interface       27         2.1 Particle Interface       27         2.1 S XIT Switch Module       24         2.1 S XIT Switch Module       24         2.1 S XIT Switch Module       25         2.1 S XIT Switch Module       26         2.                                                                           | 1. Overview                    | 11   |

| 1.3 Package Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.1 Product Outline            | 11   |

| 1 4 External Specifications       .13         1.5 Functional Blocks       .15         1.6 Address Map       .16         2. Functional Specifications       .17         2.1 The CPU       .17         2.2 Memory       .21         2.3 Control PLD       .21         2.4 CompactFlash Interface       .21         2.5 MMC Interface       .21         2.6 TRON Card Interface       .22         2.7 Debug Serial Interface       .22         2.8 Real-time Clock       .22         2.9 Power Supply Circuit       .23         2.10 Clock Module       .23         2.11 Reset Module       .24         2.12 INT Switch Module       .24         2.13 Extension CAN Signal Connector       .26         2.14 Extension CAN Signal Connector       .26         2.15 CAN Communication Connector       .26         2.16 AR Camera Board Connector       .26         2.17 LAN Interface       .27         2.18 SD Interface       .27         2.19 Parallel Interface       .28         3.17 Lock Controller (CPC)       .36         3.18 Accease Timing       .30         3.19 Accease Timing       .31         3.19 Accease Timing       .31<                                                 |                                |      |

| 1.5 Functional Blocks       .15         1.6 Address Map       .16         2. Functional Specifications       .17         2.1 The CPU       .17         2.1 The CPU       .17         2.2 Memory       .21         2.3 Control PLD       .21         2.4 CompactFlash Interface       .21         2.5 MMC Interface       .21         2.5 MMC Interface       .22         2.7 Debug Serial Interface       .22         2.8 Real-time Clock Module       .22         2.9 Power Supply Circuit       .23         2.10 Clock Module       .23         2.11 Reset Module       .24         2.12 INT Switch Module       .24         2.13 Extension Bus Connector       .26         2.14 Extension CAN Signal Connector       .26         2.15 CAN Communication Connector       .26         2.16 CAN Communication Connector       .26         2.14 Extension Dus Connector       .26         2.15 CAN Communication Connector       .26         2.16 Can Communication Connector       .26         2.15 Can Communication Connector       .26         2.15 Can Communication Connector       .26         2.16 Can Communication Connector       .26                                          | •                              |      |

| 1.6 Address Map       16         2. Functional Specifications       17         2.1 The CPU       17         2.3 Control PLD       21         2.4 CompactFlash Interface       21         2.5 MMC Interface       21         2.6 TRON Card Interface       22         2.7 Debug Serial Interface       22         2.7 Debug Serial Interface       22         2.8 Real-time Clock       22         2.9 Power Supply Circuit       23         2.10 Clock Module       23         2.11 Reset Module       24         2.12 INT Switch Module       24         2.13 Extension Bus Connector       24         2.14 Extension CAN Signal Connector       26         2.15 CAN Communication Connector       26         2.16 AR Camera Board Connector       26         2.17 LAN Interface       27         2.19 Parallel Interface       27         2.19 Parallel Interface       29         3.1 Function Pins.       29         3.1 Function Pins.       29         3.1 Function Pins.       29         3.2 A CompactFlash Controller (CFC)       31         3.4 CompactFlash Controller (CCC)       37         3.5 MutiMedicadra Controller (MMCC)                                             |                                |      |

| 2. Functional Specifications       17         2.1 The CPU       17         2.2 Memory       21         2.3 Control PLD       21         2.4 CompactFlash Interface       21         2.5 MMC Interface       21         2.6 eTRON Card Interface       22         2.7 Debug Serial Interface       22         2.8 Real-time Clock       22         2.9 Power Supply Circuit       23         2.10 Clock Module       24         2.11 Reset Module       24         2.12 Stension Bus Connector       24         2.13 Extension Bus Connector       26         2.16 CAR Communication Connector       26         2.16 AR Communication Connector       26         2.16 AR Communication Connector       26         2.16 AR Communication Connector       26         2.17 LAN Interface       27         2.18 Sol Interface       27         2.19 Parallel Interface       28         3.1 Function Pins       29         3.1 Function Pins       29         3.1 Function Pins       29         3.2 Access Timing       30         3.3 Access Timing       30         3.4 CompactFlash Controller (CC)       38                                                                              |                                |      |

| 2.1 The CPU       17         2.2 Memory       21         2.3 Control PLD       21         2.4 CompactFlash Interface       21         2.5 MMC Interface       21         2.6 ETRON Card Interface       22         2.7 Debug Serial Interface       22         2.8 Real-time Clock       22         2.9 Power Supply Circuit       23         2.10 Clock Module       24         2.11 Reset Module       24         2.12 INT Switch Module       24         2.13 Extension Bus Connector       26         2.14 Extension CAN Signal Connector       26         2.15 CAN Communication Connector       26         2.16 AR Camera Board Connector       26         3.7 Functional Description of the Control PLD       29         3.1 Function Pins       29         3.1 Function Pins Controller (CCC)                                        | •                              |      |

| 22 Memory.       21         23 Control PLD       21         24 CompactFlash Interface       21         25 MMC Interface       21         25 MMC Interface       22         27 Debug Serial Interface       22         27 Debug Serial Interface       22         28 Real-time Clock       22         29 Power Supply Circuit       23         210 Clock Module       23         211 Reset Module       24         212 INT Switch Module       24         213 Extension Bus Connector       24         214 Extension CAN Signal Connector       25         215 GAN Communication Connector       26         216 AR Camera Board Connector       26         217 LAN Interface       27         218 SDI Interface       27         219 Parallel Interface       27         219 Parallel Interface       27         219 Parallel Interface       29         31 Functional Description of the Control PLD       29         32 Internal Register Address Map       30         33 A Coress Timing       31         34 CompactFlash Controller (MCC)       36         35 S MultiMediaCard Controller (MCC)       36         36 Interrupt Controller (CFC)                                        |                                |      |

| 2.3 Control PLD       21         2.4 CompactFlash Interface       21         2.5 MMC Interface       21         2.6 TRON Card Interface       22         2.7 Debug Serial Interface       22         2.8 Real-time Clock       22         2.9 Power Supply Circuit       23         2.10 Clock Module       23         2.11 Reset Module       24         2.12 INT Switch Module       24         2.13 Extension Bus Connector       24         2.14 Extension CAN Signal Connector       26         2.16 CAN Communication Connector       26         2.16 CAR Camera Board Connector       26         2.16 CAR Camera Board Connector       26         2.16 CAR Camera Board Connector       26         2.17 LAN Interface       27         2.18 SDI Interface       27         2.19 Parallel Interface       28         3. Functional Description of the Control PLD       29         3.1 Function Pins       29         3.2 Internal Register Address Map       30         3.3 Access Timing       32         3.4 CompactFlash Controller (CFC)       32         3.5 MultiMediaCard Controller (MCC)       38         3.6 Interrupt Controller (CC)       37     <                   |                                |      |

| 2.4 CompactFlash Interface       21         2.5 MMC Interface       21         2.6 RFRON Card Interface       22         2.7 Debug Serial Interface       22         2.8 Real-time Clock       22         2.9 Power Supply Circuit       23         2.10 Clock Module       23         2.11 Reset Module       23         2.12 INT Switch Module       24         2.13 Extension Bus Connector       24         2.14 Extension CAN Signal Connector       26         2.15 CAN Communication Connector       26         2.16 AR Camera Board Connector       26         2.17 LAN Interface       27         2.18 SDI Interface       27         2.19 Parallel Interface       28         3. Functional Description of the Control PLD       29         3.1 Function Pins       29         3.2 Internal Register Address Map       30         3.3 Access Timing       31         3.4 CompactFlash Controller (MCC)       35         3.5 MultiMediaCard Controller (MCC)       36         3.6 Interrupt Controller (ICU)       47         3.7 I/O Controller (ICU)       47         3.8 CRC Calculation Circuit (CRCC)       37         3.9 Real Time Clock Controller (RTCC)               | ,                              |      |

| 2.5 MMC Interface       21         2.6 eTRON Card Interface       22         2.7 Debug Serial Interface       22         2.8 Real-time Clock       22         2.8 Real-time Clock       22         2.9 Power Supply Circuit       23         2.10 Clock Module       23         2.11 Reset Module       24         2.12 INT Switch Module       24         2.13 Extension Bus Connector       24         2.14 Extension CAN Signal Connector       26         2.15 CAN Communication Connector       26         2.16 AC Camera Board Connector       26         2.16 AC Camera Board Connector       26         2.17 LAN Interface       27         2.18 SDI Interface       27         2.19 Parallel Interface       28         3. Functional Description of the Control PLD       29         3.1 Function Pins       29         3.2 Internal Register Address Map       30         3.3 Access Timing       31         3.4 CompactFlash Controller (CFC)       32         3.5 MultiMediaCard Controller (MMCC)       38         3.6 Interrupt Controller (ICC)       35         3.5 Generation Board       37         3.6 Interrupt Controller (RTCC)       36 </td <td></td> <td></td> |                                |      |

| 2.6 eTRON Card Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                              |      |

| 2.7 Debug Serial Interface       22         2.8 Real-time Clock       22         2.9 Power Supply Circuit       23         2.10 Clock Module       23         2.11 Reset Module       24         2.12 IN Switch Module       24         2.13 Extension Bus Connector       24         2.14 Extension CAN Signal Connector       26         2.15 CAN Communication Connector       26         2.16 CAN Communication Connector       26         2.16 CAN Communication Connector       26         2.15 CAN Communication Connector       26         2.16 CAN Communication Connector       26         2.17 LAN Interface       27         2.18 SDI Interface       27         2.19 Parallel Interface       28         3. Functional Description of the Control PLD       29         3.1 Function Pins       29         3.1 Function Pins       29         3.1 Function Pins       30         3.3 Access Timing       30         3.4 CompactFlash Controller (CFC)       32         3.5 MultiMediaCard Controller (MMCC)       38         3.6 Interrupt Controller (CC)       57         3.10 eTRON Card Controller (ETC)       37         3.11 System Configuration Data (SYSC)          |                                |      |

| 2.8 Real-time Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                |      |

| 2.9 Power Supply Circuit       23         2.10 Clock Module       23         2.11 Reset Module       24         2.12 INT Switch Module       24         2.13 Extension Bus Connector       24         2.14 Extension CAN Signal Connector       24         2.15 CAN Communication Connector       26         2.16 AR Camera Board Connector       26         2.17 LAN Interface       27         2.18 SDI Interface       27         2.19 Parallel Interface       28         3. Functional Description of the Control PLD       29         3.1 Function Pins       29         3.2 Internal Register Address Map.       30         3.3 Access Timing       30         3.4 CompactFlash Controller (CFC)       32         3.5 MultiMediaCard Controller (MMCC)       38         3.6 Interrupt Controller (ICC)       37         3.7 I/O Controller (ICC)       55         3.8 CRC Calculation Circuit (CRCC)       61         3.9 Real Time Clock Controller (ETC)       33         3.1 I System Configuration Data (SYSC)       42         4. LAN Extension Board       87         4. DUtine of the LAN Extension Board Space       88         4.4 Outline of the PLD       89         < | -                              |      |

| 2.10 Clock Module       23         2.11 Reset Module       24         2.12 INT Switch Module       24         2.13 Extension Bus Connector       24         2.14 Extension CAN Signal Connector       25         2.15 CAN Communication Connector       26         2.16 AR Camera Board Connector       26         2.16 AR Camera Board Connector       26         2.17 LAN Interface       27         2.18 SDI Interface       27         2.19 Parallel Interface       28         3. Functional Description of the Control PLD       29         3.1 Function Pins       29         3.2 Internal Register Address Map       30         3.3 Access Timing       31         3.4 CompactFlash Controller (CFC)       32         3.5 MultiMediaCard Controller (MMCC)       38         3.6 Interrupt Controller (ICU)       47         3.7 I/O Controller (ICU)       47         3.8 CRC Calculation Circuit (CRCC)       61         3.9 Real Time Clock Controller (RTCC)       61         3.9 Real Time Clock Controller (RTCC)       61         3.1 System Configuration Data (SYSC)       85         4. LAN Extension Board       87         4.1 Extension Board       87         4     |                                |      |

| 2.11 Reset Module.242.12 INT Switch Module.242.13 Extension Bus Connector.242.14 Extension CAN Signal Connector.252.15 CAN Communication Connector.262.16 AR Camera Board Connector.262.17 LAN Interface.272.18 SDI Interface.272.19 Parallel Interface.272.19 Parallel Interface.283. Functional Description of the Control PLD.293.1 Function Pins.293.2 Internal Register Address Map.303.3 Access Timing.303.4 CompactFlash Controller (CFC).323.5 MultiMediaCard Controller (MMCC).383.6 Interrupt Controller (ICU).473.7 I/O Controller (ICU).473.1 1 System Configuration Data (SYSC).613.9 Real Time Clock Controller (RTCC).733.11 System Configuration Data (SYSC).854. LAN Extension Board.874.2 Functional Blocks.874.3 Mapping of the LAN Extension Board Space.884.4 Outline of the PLD.884.5 DIO.895. Extension Board Space.915.1 Outline of the Extension Board.915.2 Extension Bus Signal Assignments.935.4 EXREADY# Input.976. Mechanical Specifications.996.1 External View of the Board.996.1 External View of the Board.99                                                                                                                                          |                                |      |

| 2.12 INT Switch Module242.13 Extension Bus Connector242.14 Extension CAN Signal Connector252.15 CAN Communication Connector262.16 AR Camera Board Connector262.17 LAN Interface272.18 SDI Interface272.19 Parallel Interface283. Functional Description of the Control PLD293.1 Function Pins293.2 Internal Register Address Map303.3 Access Timing313.4 CompactFlash Controller (CFC)323.5 MutliMediaCard Controller (MMCC)383.6 Interrupt Controller (ICC)553.8 CRC Calculation Circuit (CRCC)613.9 Real Time Clock Controller (RTCC)673.10 eTRON Card Controller (ETC)733.11 System Configuration Data (SYSC)854. LAN Extension Board874.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD895. Extension Bus Connector915.1 Outline of the PLD896. Extension Bus Signal Assignments935.4 EXREADY# Input976. Mechanical Specifications996.1 External View of the Board996.1 External View of the Board99                                                                                                                                                                                                                                       |                                |      |

| 2.13 Extension Bus Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                |      |

| 2.14 Extension CAN Signal Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                |      |

| 2.15 CAN Communication Connector262.16 AR Camera Board Connector262.17 LAN Interface272.18 SDI Interface272.19 Parallel Interface283. Functional Description of the Control PLD293.1 Function Pins293.2 Internal Register Address Map303.3 Access Timing313.4 CompactFlash Controller (CFC)323.5 MultilMediaCard Controller (MMCC)383.6 Interrupt Controller (ICU)473.7 I/O Controller (ICU)473.7 I/O Controller (ICC)553.8 CRC Calculation Circuit (CRCC)613.9 Real Time Clock Controller (RTCC)613.9 Real Time Clock Controller (ETC)733.11 System Configuration Data (SYSC)854. LAN Extension Board874.1 External Specifications874.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD884.5 DIO895. Extension Board Specifications915.1 Outline of the Extension Board915.1 Extension Bus Connectors915.1 External View of the Board996.1 External View of the Board996.1 External View of the Board99                                                                                   |                                |      |

| 2.16 AR Camera Board Connector262.17 LAN Interface.272.18 SDI Interface.272.19 Parallel Interface.283. Functional Description of the Control PLD293.1 Function Pins.293.2 Internal Register Address Map303.3 Access Timing313.4 CompactFlash Controller (CFC).323.5 MultiMediaCard Controller (CFC).383.6 Interrupt Controller (ICU)473.7 I/O Controller (ICU)473.8 CRC Calculation Circuit (CRCC).613.9 Real Time Clock Controller (ETC).673.10 eTRON Card Controller (ETC).733.11 System Configuration Data (SYSC).854. LAN Extension Board874.1 External Specifications874.2 Functional Blocks884.4 Outline of the PLD884.5 DIO.895. Extension Board Space.884.4 Outline of the PLD884.5 DIO.895. Extension Board Space.915.1 Outline of the Extension Board915.1 Outline of the Extension Board915.1 Outline of the Extension Board915.1 Attension Board Space834.5 DIO.896.1 External View of the Board996.1 External View of the Board996.1 External View of the Board996.1 External View of the Board99                                                                                                                                                                           |                                |      |

| 2.17 LAN Interface272.18 SDI Interface272.19 Parallel Interface283. Functional Description of the Control PLD293.1 Function Pins293.2 Internal Register Address Map303.3 Access Timing313.4 CompactFlash Controller (CFC)323.5 MultiMediaCard Controller (MMCC)383.6 Interrupt Controller (ICU)473.7 I/O Controller (ICC)553.8 CRC Calculation Circuit (CRCC)613.9 Real Time Clock Controller (RTCC)673.10 eTRON Card Controller (RTCC)673.11 System Configuration Data (SYSC)854. LAN Extension Board874.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD884.5 DIO895. Extension Bus Connectors915.1 Outline of the Extension Board915.1 Outline of the Extension Board915.1 Extension Bus Connectors915.2 Extension Bus Connectors915.3 Extension Bus Connectors915.4 EXREADY# Input936.1 External View of the Board996.1 External View of the Board99                                                                                                                                                                                                                                                                                        |                                |      |

| 2.18 SDI Interface.272.19 Parallel Interface.283. Functional Description of the Control PLD293.1 Function Pins.293.2 Internal Register Address Map.303.3 Access Timing313.4 CompactFlash Controller (CFC).323.5 MultiMediaCard Controller (MMCC)383.6 Interrupt Controller (ICU)473.7 I/O Controller (ICU)473.8 CRC Calculation Circuit (CRCC)613.9 Real Time Clock Controller (RTCC)673.11 System Configuration Data (SYSC)854. LAN Extension Board874.1 External Specifications874.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD884.5 DIO895. Extension Board Space915.1 Outline of the Extension Board915.2 Extension Board Space915.3 Extension Board Space915.4 EXREADY# Input976. Mechanical Specifications996.1 External View of the Board99                                                                                                                                                                                                                                                                                                                                                                                          |                                |      |

| 2.19 Parallel Interface.283. Functional Description of the Control PLD293.1 Function Pins293.2 Internal Register Address Map303.3 Access Timing313.4 CompactFlash Controller (CFC)323.5 MultiMediaCard Controller (MMCC)383.6 Interrupt Controller (ICU)473.7 I/O Controller (ICC)553.8 CRC Calculation Circuit (CRCC)613.9 Real Time Clock Controller (RTCC)673.10 eTRON Card Controller (ETC)733.11 System Configuration Data (SYSC)854. LAN Extension Board874.1 External Specifications874.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD884.5 DIO895. Extension Board Specifications915.1 Outline of the Extension Board915.2 Extension Bus Connectors915.4 EXREADY# Input976. Mechanical Specifications996.1 External View of the Board99                                                                                                                                                                                                                                                                                                                                                                                               |                                |      |

| 3. Functional Description of the Control PLD       29         3.1 Function Pins       29         3.2 Internal Register Address Map       30         3.3 Access Timing       31         3.4 CompactFlash Controller (CFC)       32         3.5 MultiMediaCard Controller (MMCC)       38         3.6 Interrupt Controller (ICU)       47         3.7 I/O Controller (ICC)       55         3.8 CRC Calculation Circuit (CRCC)       61         3.9 Real Time Clock Controller (RTCC)       67         3.10 eTRON Card Controller (ETC)       73         3.11 System Configuration Data (SYSC)       85         4. LAN Extension Board       87         4.1 External Specifications       87         4.2 Functional Blocks       87         4.3 Mapping of the LAN Extension Board Space       88         4.4 Outline of the PLD       88         4.5 DIO       89         5. Extension Board Specifications       91         5.1 Outline of the Extension Board       91         5.2 Extension Bus Signal Assignments       93         5.4 EXREADY# Input       97         6.1 Mechanical Specifications       99         6.1 External View of the Board       99                         |                                |      |

| 3.1 Function Pins293.2 Internal Register Address Map303.3 Access Timing313.4 CompactFlash Controller (CFC)323.5 MultiMediaCard Controller (MMCC)383.6 Interrupt Controller (ICU)473.7 I/O Controller (ICC)553.8 CRC Calculation Circuit (CRCC)613.9 Real Time Clock Controller (RTCC)673.10 eTRON Card Controller (ETC)733.11 System Configuration Data (SYSC)854. LAN Extension Board874.1 External Specifications874.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD884.5 DIO895. Extension Board Space915.1 Outline of the Extension Board915.1 Outline of the Extension Board915.2 Extension Bus Signal Assignments935.4 EXREADY# Input976. Mechanical Specifications996.1 External View of the Board996.1 External View of the Board99                                                                                                                                                                            |                                |      |

| 3.2 Internal Register Address Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                              |      |

| 3.3 Access Timing313.4 CompactFlash Controller (CFC)323.5 MultiMediaCard Controller (MMCC)383.6 Interrupt Controller (ICU)473.7 I/O Controller (IOC)553.8 CRC Calculation Circuit (CRCC)613.9 Real Time Clock Controller (RTCC)673.10 eTRON Card Controller (RTCC)733.11 System Configuration Data (SYSC)854. LAN Extension Board874.1 External Specifications874.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD884.5 DIO895. Extension Board Specifications915.1 Outline of the Extension Board915.2 Extension Bus Connectors915.3 Extension Bus Signal Assignments935.4 EXREADY# Input976. Mechanical Specifications996.1 External View of the Board99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                |      |

| 3.4 CompactFlash Controller (CFC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |      |

| 3.5 MultiMediaCard Controller (IMCC)383.6 Interrupt Controller (ICU)473.7 I/O Controller (IOC)553.8 CRC Calculation Circuit (CRCC)613.9 Real Time Clock Controller (RTCC)673.10 eTRON Card Controller (ETC)733.11 System Configuration Data (SYSC)854. LAN Extension Board874.1 External Specifications874.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD884.5 DIO895. Extension Bus Connectors915.1 Outline of the Extension Board915.2 Extension Bus Signal Assignments935.4 EXREADY# Input976. Mechanical Specifications996.1 External View of the Board99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                              |      |

| 3.6 Interrupt Controller (ICU)       47         3.7 I/O Controller (IOC)       55         3.8 CRC Calculation Circuit (CRCC)       61         3.9 Real Time Clock Controller (RTCC)       67         3.10 eTRON Card Controller (ETC)       73         3.11 System Configuration Data (SYSC)       85         4. LAN Extension Board       87         4.1 External Specifications       87         4.2 Functional Blocks       87         4.3 Mapping of the LAN Extension Board Space       88         4.4 Outline of the PLD       88         4.5 DIO       89         5. Extension Board Specifications       91         5.1 Outline of the Extension Board       91         5.2 Extension Bus Connectors       91         5.3 Extension Bus Signal Assignments       93         5.4 EXREADY# Input       97         6. Mechanical Specifications       99         6.1 External View of the Board       99                                                                                                                                                                                                                                                                            |                                |      |

| 3.7 I/O Controller (IOC)553.8 CRC Calculation Circuit (CRCC)613.9 Real Time Clock Controller (RTCC)673.10 eTRON Card Controller (ETC)733.11 System Configuration Data (SYSC)854. LAN Extension Board874.1 External Specifications874.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD884.5 DIO895. Extension Board Specifications915.1 Outline of the Extension Board915.2 Extension Bus Connectors915.3 Extension Bus Signal Assignments935.4 EXREADY# Input976. Mechanical Specifications996.1 External View of the Board99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |      |

| 3.8 CRC Calculation Circuit (CRCC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                |      |

| 3.9 Real Time Clock Controller (RTCC)673.10 eTRON Card Controller (ETC)733.11 System Configuration Data (SYSC)854. LAN Extension Board874.1 External Specifications874.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD884.5 DIO895. Extension Board Specifications915.1 Outline of the Extension Board915.2 Extension Bus Connectors915.3 Extension Bus Signal Assignments935.4 EXREADY# Input976. Mechanical Specifications996.1 External View of the Board99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                |      |

| 3.10 eTRON Card Controller (ETC)733.11 System Configuration Data (SYSC)854. LAN Extension Board874.1 External Specifications874.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD884.5 DIO895. Extension Board Specifications915.1 Outline of the Extension Board915.2 Extension Bus Connectors915.3 Extension Bus Signal Assignments935.4 EXREADY# Input976. Mechanical Specifications996.1 External View of the Board99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |      |

| 3.11 System Configuration Data (SYSC)854. LAN Extension Board874.1 External Specifications874.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD884.5 DIO895. Extension Board Specifications915.1 Outline of the Extension Board915.2 Extension Bus Connectors915.3 Extension Bus Signal Assignments935.4 EXREADY# Input976. Mechanical Specifications996.1 External View of the Board99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                |      |

| 4. LAN Extension Board       87         4.1 External Specifications       87         4.2 Functional Blocks       87         4.3 Mapping of the LAN Extension Board Space       88         4.4 Outline of the PLD       88         4.5 DIO       89         5. Extension Board Specifications       91         5.1 Outline of the Extension Board       91         5.2 Extension Bus Connectors       91         5.3 Extension Bus Signal Assignments       93         5.4 EXREADY# Input       97         6. Mechanical Specifications       99         6.1 External View of the Board       99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                |      |

| 4.1 External Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                |      |

| 4.2 Functional Blocks874.3 Mapping of the LAN Extension Board Space884.4 Outline of the PLD884.5 DIO895. Extension Board Specifications915.1 Outline of the Extension Board915.2 Extension Bus Connectors915.3 Extension Bus Signal Assignments935.4 EXREADY# Input976. Mechanical Specifications996.1 External View of the Board99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                |      |

| 4.3 Mapping of the LAN Extension Board Space       .88         4.4 Outline of the PLD       .88         4.5 DIO       .89         5. Extension Board Specifications       .91         5.1 Outline of the Extension Board       .91         5.2 Extension Bus Connectors       .91         5.3 Extension Bus Signal Assignments       .93         5.4 EXREADY# Input       .97         6. Mechanical Specifications       .99         6.1 External View of the Board       .99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |      |

| 4.4 Outline of the PLD       .88         4.5 DIO       .89         5. Extension Board Specifications       .91         5.1 Outline of the Extension Board       .91         5.2 Extension Bus Connectors       .91         5.3 Extension Bus Signal Assignments       .93         5.4 EXREADY# Input       .97         6. Mechanical Specifications       .99         6.1 External View of the Board       .99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                |      |

| 4.5 DIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                |      |

| 5. Extension Board Specifications       .91         5.1 Outline of the Extension Board       .91         5.2 Extension Bus Connectors       .91         5.3 Extension Bus Signal Assignments       .93         5.4 EXREADY# Input       .97         6. Mechanical Specifications       .99         6.1 External View of the Board       .99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                |      |

| 5.1 Outline of the Extension Board.       .91         5.2 Extension Bus Connectors       .91         5.3 Extension Bus Signal Assignments       .93         5.4 EXREADY# Input       .97         6. Mechanical Specifications       .99         6.1 External View of the Board       .99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                |      |

| 5.2 Extension Bus Connectors       .91         5.3 Extension Bus Signal Assignments       .93         5.4 EXREADY# Input       .97         6. Mechanical Specifications       .99         6.1 External View of the Board       .99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                |      |

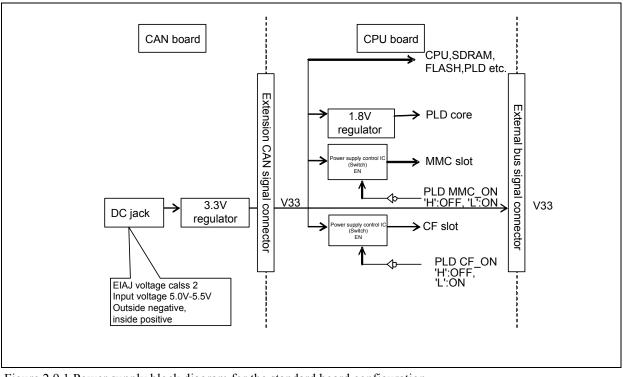

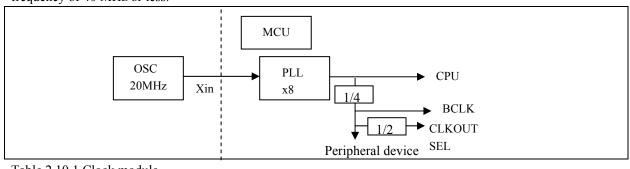

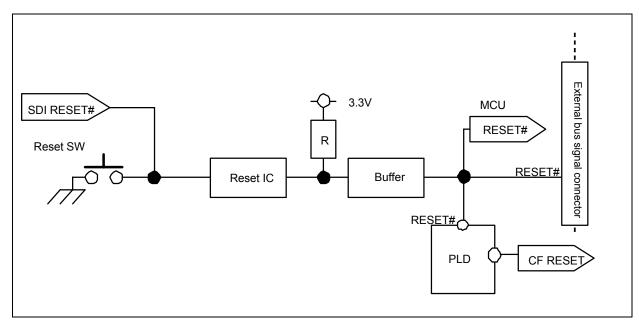

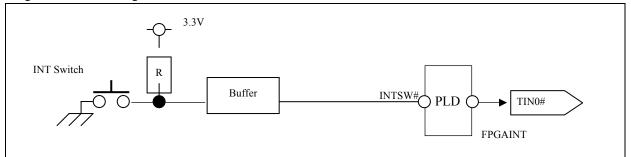

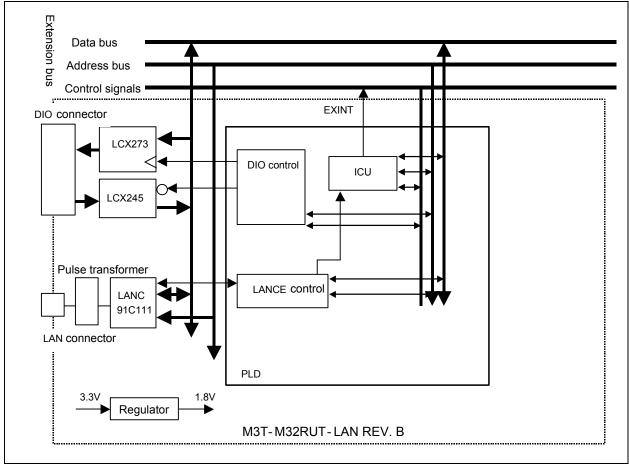

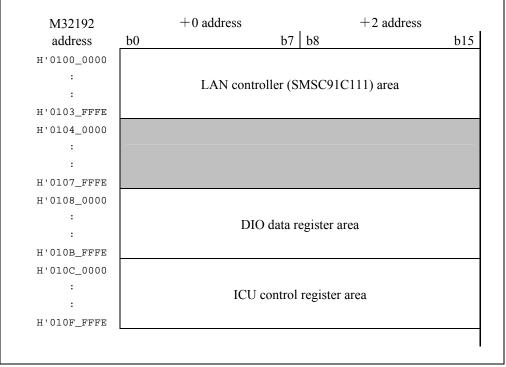

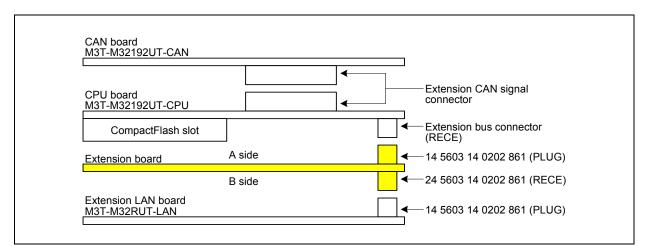

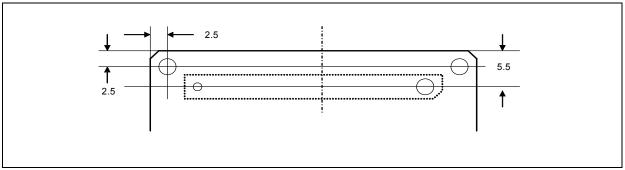

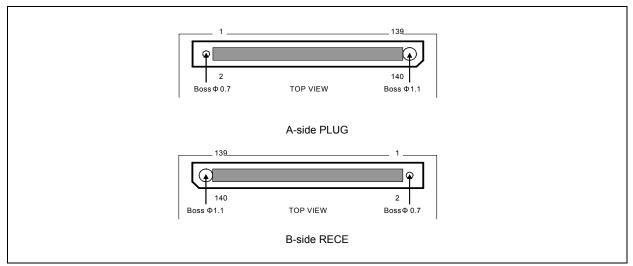

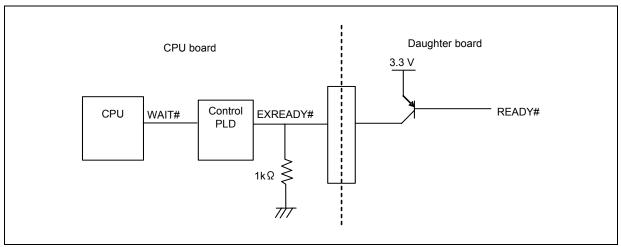

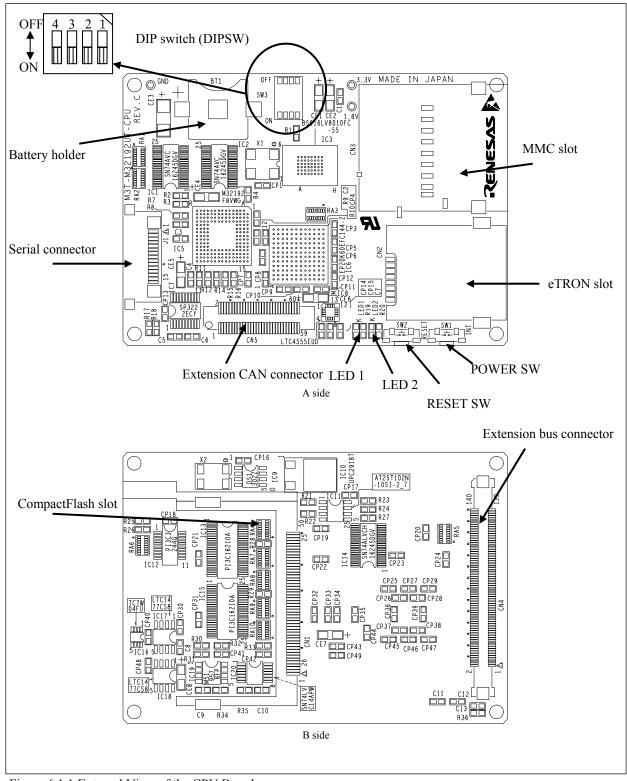

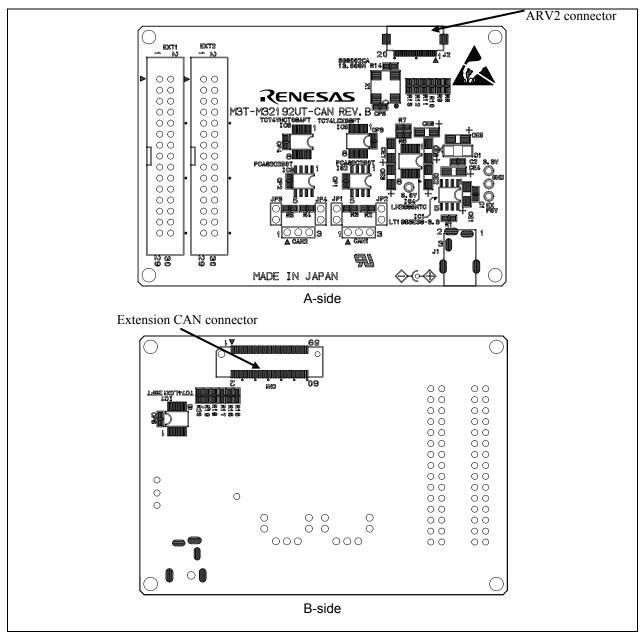

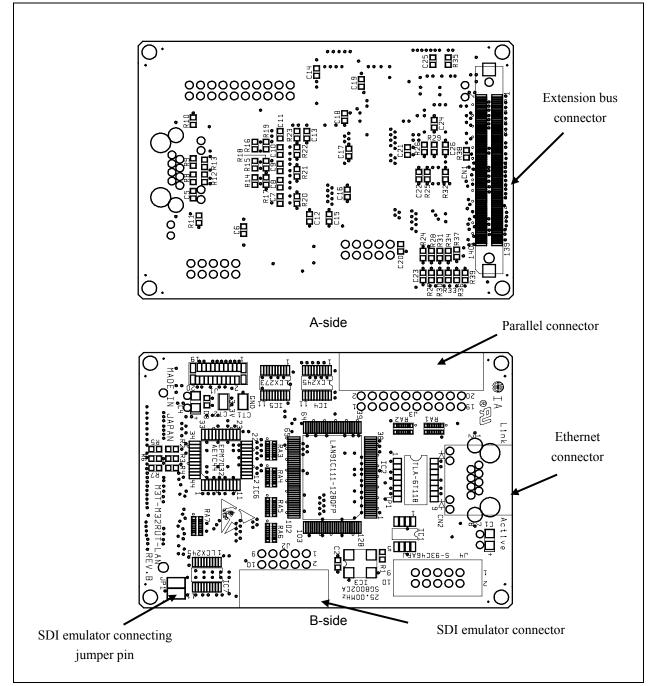

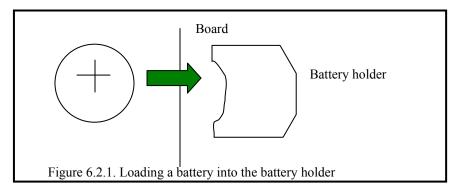

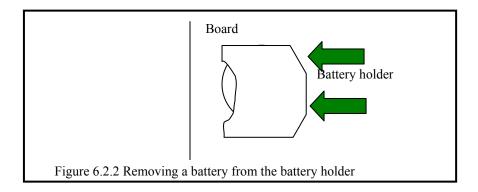

| 5.3 Extension Bus Signal Assignments       .93         5.4 EXREADY# Input       .97         6. Mechanical Specifications       .99         6.1 External View of the Board       .99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                |      |