# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# ユーザーズ・マニュアル

# μPD789104,789114,789124, 789134**サブシリーズ**

8ビット・シングルチップ・マイクロコンピュータ

| μPD789101  | μPD789121  |

|------------|------------|

| μPD789102  | μPD789122  |

| μPD789104  | μPD789124  |

| μPD789111  | μPD789131  |

| μPD789112  | μPD789132  |

| μPD789114  | μPD789134  |

| μPD78F9116 | μPD78F9136 |

[メ モ]

### 目次要約

第1章 概 説(μPD789104, 789114サブシリーズ) ... 23

第2章 概 説 (μ PD789124, 789134**サブ**シリーズ) ... 31

第3章 端子機能 ... 39

第4章 CPUアーキテクチャ ... 47

第5章 ポート機能 ... 73

第6章 クロック発生回路 (μ PD789104, 789114サブシリーズ) ... 89

第7章 クロック発生回路(μ PD789124, 789134サブシリーズ) ... 97

**第8章** 16**ビット・タイマ・カウンタ** ... 105

第9章 8ピット・タイマ/イベント・カウンタ ... 117

第10章 ウォッチドッグ・タイマ ... 131

第11章 8ビットA/Dコンバータ (μPD789104, 789124サブシリーズ) ... 137

第12章 10**ピット**A/D**コンバータ (**μ PD789114, 789134**サブシリーズ)** ... 151

**第13章 シリアル・インタフェース20 ... 165**

第14章 乗算器 ... 201

第15章 割り込み機能 ... 205

第16章 スタンバイ機能 ... 219

第17章 リセット機能 ... 227

第18章 μ PD78F9116, 78F9136 ... 231

**第**19**章 マスク・オプション(マスク**ROM**製品)** ... 239

第20章 命令セットの概要 ... 241

付録A 開発ツール ... 253

付録B 組み込み用ソフトウエア ... 259

付録C レジスタ索引 ... 261

付録D 改版履歴 ... 265

### CMOSデバイスの一般的注意事項

#### 静電気対策 (MOS全般)

#### 注意 MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、NECが出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また,MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 未使用入力の処理 (CMOS特有)

#### 注意 CMOSデバイスの入力レベルは固定してください。

バイポーラやNMOSのデバイスと異なり、CMOSデバイスの入力に何も接続しない状態で動作させると、ノイズなどに起因する中間レベル入力が生じ、内部で貫通電流が流れて誤動作を引き起こす恐れがあります。プルアップかプルダウンによって入力レベルを固定してください。また、未使用端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してV∞またはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については、その内容を守ってください。

#### 初期化以前の状態 (MOS全般)

#### 注意 電源投入時, MOSデバイスの初期状態は不定です。

分子レベルのイオン注入量等で特性が決定するため,初期状態は製造工程の管理外です。電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は,まずリセット動作を実行してください。

#### EEPROMは,日本電気株式会社の商標です。

WindowsおよびWindows NTは、米国Microsoft Corporationの米国およびその他の国における登録商標または商標です。

PC/ATは,米国IBM社の商標です。

HP9000シリーズ700, HP-UXは,米国ヒューレット・パッカード社の商標です。

SPARCstationは,米国SPARC International, Inc.の商標です。

Solaris, SunOSは,米国サン・マイクロシステムズ社の商標です。

OSF/Motifは, Open Software Foundation, Inc.の商標です。

NEWS, NEWS-OSは, ソニー株式会社の商標です。

TRONは, The Realtime Operating system Nucleusの略称です。

ITRONは, Industrial TRONの略称です。

本製品のうち,外国為替および外国貿易管理法の規定により規制貨物等(または役務)に該当するものについては,日本国外に輸出する際に,同法に基づき日本国政府の輸出許可が必要です。

非該当品: μ PD78F9116, 78F9136

ユーザ判定品: μ PD789101, 789102, 789104

$\mu$  PD789111, 789112, 789114  $\mu$  PD789121, 789122, 789124  $\mu$  PD789131, 789132, 789134

- 本資料の内容は予告なく変更することがありますので,最新のものであることをご確認の上ご使用ください。

- 文書による当社の承諾なしに本資料の転載複製を禁じます。

- 本資料に記載された製品の使用もしくは本資料に記載の情報の使用に際して,当社は当社もしくは第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。上記使用に 起因する第三者所有の権利にかかわる問題が発生した場合,当社はその責を負うものではありませんの でご了承ください。

- 本資料に記載された回路,ソフトウエア,及びこれらに付随する情報は,半導体製品の動作例,応用例を説明するためのものです。従って,これら回路・ソフトウエア・情報をお客様の機器に使用される場合には,お客様の責任において機器設計をしてください。これらの使用に起因するお客様もしくは第三者の損害に対して,当社は一切その責を負いません。

- 当社は品質,信頼性の向上に努めていますが,半導体製品はある確率で故障が発生します。当社半導体製品の故障により結果として,人身事故,火災事故,社会的な損害等を生じさせない冗長設計,延焼対策設計,誤動作防止設計等安全設計に十分ご注意願います。

- 当社は、当社製品の品質水準を「標準水準」、「特別水準」およびお客様に品質保証プログラムを指定して頂く「特定水準」に分類しております。また、各品質水準は以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認の上ご使用願います。

標準水準:コンピュータ,OA機器,通信機器,計測機器,AV機器,家電,工作機械,パーソナル機器,産業用ロボット

特別水準:輸送機器(自動車,列車,船舶等),交通用信号機器,防災/防犯装置,各種安全装置, 生命維持を直接の目的としない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート / データ・ブック等の資料で,特に品質水準の表示がない場合は標準水準製品であることを表します。当社製品を上記の「標準水準」の用途以外でご使用をお考えのお客様は,必ず事前に当社販売窓口までご相談頂きますようお願い致します。

M7 98.8

### 本版で改訂された主な箇所

| 箇 所      | 内 容                                                                            |

|----------|--------------------------------------------------------------------------------|

| 全 般      | 28ピン・プラスチック・シュリンクDIPを削除                                                        |

|          | 30ピン・プラスチック・シュリンクDIPを計画中として追加                                                  |

|          | マスクROM製品,μ PD78F9116を開発中から開発済みに変更                                              |

|          | パッケージにMC-5A4タイプを追加                                                             |

|          | 電源電圧(MIN.)を1.8 V 2.7 Vに変更                                                      |

| p.44     | 表3 - 1 <b>各端子の入出力回路タイプと未使用端子の処理</b> で未使用時の推奨接続方法を変更                            |

| p.81     | 5. 2. 4 <b>ポート</b> 5で入力端子として使用する場合の注意事項を追加                                     |

| p.97-103 | 第7章 <b>クロック発生回路(</b> μ PD789124, 789134 <b>サブシリーズ)</b> でシステム・クロックの発振周          |

|          | 波数を2.0~4.0 MHzに変更                                                              |

| p.112    | 8. 4. 1 <b>タイマ割り込みとしての動作</b> でCR20の書き換えに対する注意事項を追加                             |

| p.119    | 9.2(1)8ビット・コンペア・レジスタ80(CR80)でCR80の書き換えに対する注意事項を追加                              |

| p.122    | 9.4.1 インターバル・タイマとしての動作に操作方法の説明文を追加                                             |

| p.124    | 9.4.2 外部イベント・カウンタとしての動作に操作方法の説明文を追加                                            |

| p.125    | 9.4.3 方形波出力としての動作に操作方法の説明文を追加                                                  |

| p.127    | 9. 4. 4 PWM <b>出力としての動作</b> に操作方法の説明文を追加                                       |

| p.173    | 13.3(3)アシンクロナス・シリアル・インタフェース・ステータス・レジスタ20(ASIS20)で                              |

|          | 1ビット・メモリ操作命令が可能に変更                                                             |

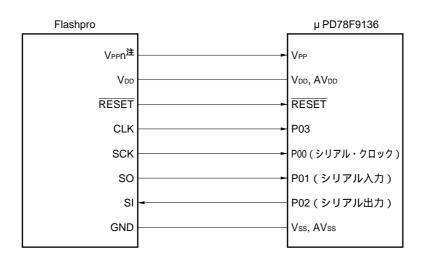

| p.235    | 18. 1. 3 <b>(</b> b <b>)</b> $\mu$ PD78F9136 <b>と</b> Flashpro <b>の接続例</b> を追加 |

| p.237    | 18. 1. 4 Flashpro (PG-FP3 <b>)での設定例</b> を追加                                    |

| p.253    | 付録A 開発ツール                                                                      |

|          | 全面改訂:IE-78K0S-NSに対応                                                            |

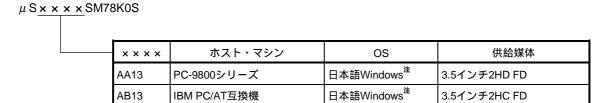

| p.259    | 付録B 組み込み用ソフトウエアでMX78K0Sのオーダ名称を追加                                               |

| p.265    | <b>付録</b> D <b>改版履歴</b> を追加                                                    |

本文欄外の★印は,本版で改訂された主な箇所を示しています。

巻末にアンケート・コーナを設けております。このドキュメントに対するご意見を お気軽にお寄せください。

### はじめに

**対象者** このマニュアルはμ PD789104, 789114, 789124, 789134サブシリーズの機能を理解し, その応用システムや応用プログラムを設計, 開発するユーザのエンジニアを対象としています。

対象製品は,次に示すサブシリーズの各製品です。

・ $\mu$  PD789104サブシリーズ:  $\mu$  PD789101, 789102, 789104

・ $\mu$  PD789114サブシリーズ:  $\mu$  PD789111, 789112, 789114, 78F9116

・ $\mu$  PD789124サブシリーズ:  $\mu$  PD789121, 789122, 789124

・ $\mu$  PD789134サブシリーズ:  $\mu$  PD789131, 789132, 789134, 78F9136

このマニュアルでは特にことわりがない限り全製品を代表して $\mu$  PD789134**サブシリーズ**と記載しております。

システム・クロックの発振周波数は,セラミック / クリスタル発振 ( $\mu$  PD789104, 789114サブシリーズ)を $f_{\rm K}$ , RC発振 ( $\mu$  PD789124, 789134サブシリーズ)を $f_{\rm CC}$ としています。

**目 的** このマニュアルは,次の構成に示す機能をユーザに理解していただくことを目的としています。

構 成 μPD789104, 789114, 789124, 789134サブシリーズのマニュアルは, このマニュアルと命令編 (78K/0Sシリーズ共通)の2冊に分かれています。

μ PD789104, 789114, 789124, 789134サブシリーズ ユーザーズ・マニュアル

端子機能

内部ブロック機能

割り込み

その他の内蔵周辺機能

78K/0Sシリーズ ユーザーズ・マニュアル 命令編

CPU機能

命令セット

命令の説明

**読み方** このマニュアルを読むにあたっては、電気、論理回路、マイクロコンピュータの一般知識を必要とします。

一通りの機能を理解しようとするとき

目次に従って読んでください。

レジスタ・フォーマットの見方

ビット番号を で囲んでいるものは、そのビット名称がアセンブラでは予約語に、Cコンパイラではfrbit.hというヘッダ・ファイルで定義済みとなっているものです。

レジスタ名が分かっていてレジスタの詳細を確認するとき

付録C レジスタ索引を利用してください。

78K/OSシリーズの命令機能の詳細を知りたいとき

別冊の78K/OSシリーズ ユーザーズ・マニュアル 命令編 (U11047J) を参照してください。

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記 : <u>×××</u>(端子,信号名称に上線)

注:本文中につけた注の説明

注意: 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数…××××または××××B

10進数...×××× 16進数...××××H

**関連資料** 関連資料は暫定版の場合がありますが、この資料では「暫定」の表示をしておりません。あらかじめ ご了承ください。

#### デバイスの関連資料

| 資料 名                                                 | 資料      | 番号      |

|------------------------------------------------------|---------|---------|

|                                                      | 和文      | 英文      |

| μ PD789101, 789102, 789104 ペーパ・マシン                   | U12815J | U12815E |

| μ PD789111, 789112, 789114 ペーパ・マシン                   | U13013J | U13013E |

| μ PD789121, 789122, 789124 ペーパ・マシン                   | U13025J | U13025E |

| μ PD789131, 789132, 789134 ペーパ・マシン                   | U13015J | U13015E |

| μ PD78F9116 ペーパ・マシン                                  | U13037J | U13037E |

| μ PD78F9136 ペーパ・マシン                                  | U13036J | U13036E |

| μ PD789104, 789114, 789124, 789134サブシリーズ ユーザーズ・マニュアル | このマニュアル | U13045E |

| 78K/OSシリーズ ユーザーズ・マニュアル 命令編                           | U11047J | U11047E |

#### 開発ツールの資料 (ユーザーズ・マニュアル)

| 資 料 名                         |             | 資料番号    |         |

|-------------------------------|-------------|---------|---------|

|                               |             | 和文      | 英文      |

| RA78KOS アセンブラ・パッケージ           | 操作編         | U11622J | U11622E |

|                               | アセンブリ言語編    | U11599J | U11599E |

|                               | 構造化アセンブリ言語編 | U11623J | U11623E |

| CC78K0S Cコンパイラ                | 操作編         | U11816J | U11816E |

|                               | 言語編         | U11817J | U11817E |

| SM78K0S システム・シミュレータ Windows™  | レファレンス編     | U11489J | U11489E |

| ベース                           |             |         |         |

| SM78Kシリーズ システム・シミュレータ         | 外部部品ユーザオープン | U10092J | U10092E |

|                               | インタフェース仕様編  |         |         |

| ID78K0S-NS統合ディバッガ Windowsベース  | レファレンス編     | U12901J | U12901E |

| IE-78KOS-NS インサーキット・エミュレータ    |             | U13549J | U13549E |

| IE-789136-NS-EM1 エミュレーション・ボード |             | 作成予定    | 作成予定    |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには必ず最新の資料をご使用ください。

#### 組み込み用ソフトウエアの資料 (ユーザーズ・マニュアル)

| 資 料 名                 |     | 資料      | 番号   |

|-----------------------|-----|---------|------|

|                       |     | 和文      | 英文   |

| 78K/0Sシリーズ用OS MX78K0S | 基礎編 | U12938J | 作成予定 |

#### その他の資料

| 資料 名                                                          | 資料      | 番号      |

|---------------------------------------------------------------|---------|---------|

|                                                               | 和文      | 英文      |

| SEMICONDUCTORS SELECTION GUIDE Products & Packages ( CD-ROM ) | X13769X |         |

| 半導体デバイス 実装マニュアル                                               | C10535J | C10535E |

| NEC半導体デバイスの品質水準                                               | C11531J | C11531E |

| NEC半導体デバイスの信頼性品質管理                                            | C10983J | C10983E |

| 静電気放電(ESD)破壊対策ガイド                                             | C11892J | C11892E |

| 半導体 品質 / 信頼性ハンドブック                                            | C12769J | -       |

| マイクロコンピュータ関連製品ガイド 社外メーカ編                                      | U11416J | -       |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには必ず最新の資料をご使用ください。

[メ モ]

# 目 次

| 第1章         | 概 説 (µ PD789104, 789114 <b>サプシリーズ)</b> 23            |

|-------------|------------------------------------------------------|

| 1 1         | <b>特 徵</b> 23                                        |

|             | 応用分野 23                                              |

|             | オーダ情報 24                                             |

|             | 端子接続図 (Top View ) 25                                 |

|             | 78K/OS <b>シリーズの展開</b> 27                             |

|             | プロック図 29                                             |

|             | 機能概要 30                                              |

|             |                                                      |

| <b>第</b> 2章 | 概 説 (μ PD789124, 789134 <b>サプシリーズ)</b> 31            |

|             |                                                      |

| 2. 1        | 特 徵 31                                               |

|             | <b>応用分野</b> 31                                       |

| 2. 3        | <b>オーダ情報</b> 32                                      |

|             | <b>端子接続図(</b> Top View <b>)</b> 33                   |

| 2. 5        | 78K/0S <b>シリーズの展開</b> 35                             |

| 2. 6        | <b>ブロック図</b> 37                                      |

| 2. 7        | 機能概要 38                                              |

| <b>第</b> 3章 | <b>端子機能</b> 39                                       |

|             |                                                      |

| 3. 1        | <b>端子機能一覧</b> 39                                     |

| 3. 2        | 端子機能の説明 41                                           |

|             | 3. 2. 1 P00-P03 ( Port0 ) 41                         |

|             | 3. 2. 2 P10, P11 ( Port1 ) 41                        |

|             | 3. 2. 3 P20-P25 ( Port2 ) 41                         |

|             | 3. 2. 4 P50-P53 ( Port 5 ) 42                        |

|             | 3. 2. 5 P60-P63 ( Port 6 ) 42                        |

|             | 3. 2. 6 RESET 42                                     |

|             | 3. 2. 7 X1, X2 (μPD789104, 789114サブシリーズ) 42          |

|             | 3. 2. 8 CL1, CL2 ( $\mu$ PD789124, 789134サブシリーズ) 42  |

|             | 3. 2. 9 AVDD 42                                      |

|             | 3. 2. 10 AVss 43                                     |

|             | 3. 2. 11 VDD 43                                      |

|             | 3. 2. 12 Vss 43                                      |

|             | 3. 2. 13 VPP ( $\mu$ PD78F9116, 78F9136の $ \mu$ ) 43 |

3.2.14 20番ピンのICO(マスクROM製品のみ) ... 43

|  | <b>*</b> | 3. 2. 15 | 10番ピン | と21番ピンのIC0 |  | 43 |

|--|----------|----------|-------|------------|--|----|

|--|----------|----------|-------|------------|--|----|

#### 3.3 端子の入出力回路と未使用端子の処理 ... 44

#### **第4章** CPU**アーキテクチャ** ... 47

| 4          | 1 | メモリ      | 」              | 47     |

|------------|---|----------|----------------|--------|

| <b>+</b> . |   | <i>_</i> | <i>,</i> — 181 | <br>41 |

- 4.1.1 内部プログラム・メモリ空間 ... 51

- 4.1.2 内部データ・メモリ(内部高速RAM)空間 ... 52

- 4.1.3 特殊機能レジスタ (SFR: Special Function Register) 領域 ... 52

- 4.1.4 データ・メモリ・アドレシング ... 53

#### 4.2 **プロセッサ・レジスタ** ... 57

- 4.2.1 制御レジスタ ... 57

- 4.2.2 汎用レジスタ ... 60

- 4.2.3 特殊機能レジスタ(SFR) ... 61

#### 4.3 命令アドレスのアドレシング ... 64

- 4.3.1 レラティブ・アドレシング ... 64

- 4.3.2 イミーディエト・アドレシング ... 65

- 4.3.3 テーブル・インダイレクト・アドレシング ... 66

- 4.3.4 レジスタ・アドレシング ... 66

#### 4.4 オペランド・アドレスのアドレシング ... 67

- 4.4.1 ダイレクト・アドレシング ... 67

- 4.4.2 ショート・ダイレクト・アドレシング ... 68

- 4.4.3 特殊機能レジスタ(SFR)アドレシング ... 69

- 4.4.4 レジスタ・アドレシング ... 70

- 4.4.5 レジスタ・インダイレクト・アドレシング ... 71

- 4.4.6 ベースト・アドレシング ... 72

- 4.4.7 スタック・アドレシング ... 72

#### 第5章 ポート機能 ... 73

- 5.1 ポートの機能 ... 73

- 5.2 ポートの構成 ... 75

- 5. 2. 1 ポート0 ... 75

- 5.2.2 ポート1 ... 76

- 5.2.3 ポート2 ... 77

- 5.2.4 ポート5 ... 81

- 5.2.5 ポート6 ... 82

#### 5.3 ポート機能を制御するレジスタ ... 83

#### 5.4 ポート機能の動作 ... 86

- 5.4.1 入出力ポートへの書き込み ... 86

- 5.4.2 入出力ポートからの読み出し ... 86

- 5.4.3 入出力ポートでの演算 ... 87

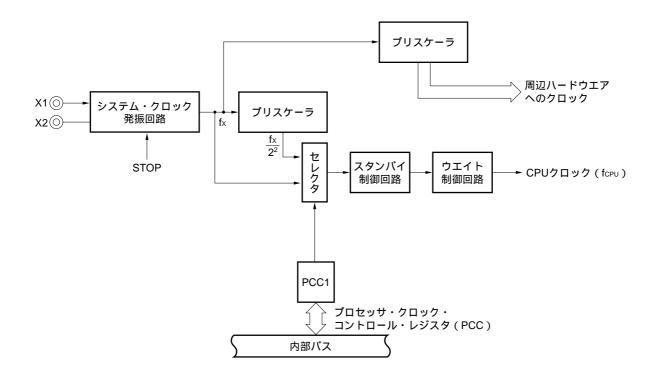

## 第6章 クロック発生回路 (μ PD789104, 789114サプシリーズ) ... 89

| 6. 1        | <b>クロック発生回路の機能</b> 89                                 |

|-------------|-------------------------------------------------------|

| 6. 2        | <b>クロック発生回路の構成</b> 89                                 |

| 6. 3        | <b>クロック発生回路を制御するレジスタ</b> 90                           |

| 6. 4        | システム・クロック発振回路 91                                      |

|             | 6. 4. 1 システム・クロック発振回路 91                              |

|             | 6. 4. 2 分周回路 94                                       |

| 6. 5        | <b>クロック発生回路の動作</b> 94                                 |

| 6. 6        | CPU <b>クロックの設定の変更</b> 95                              |

|             | 6. 6. 1 CPUクロックの切り替えに要する時間 95                         |

|             | 6. 6. 2 CPUクロックの切り替え手順 95                             |

| 第7章         | <b>クロック発生回路(</b> μ PD789124, 789134 <b>サブシリーズ)</b> 97 |

|             | , , , , , , , , , , , , , , , , , , , ,               |

| 7. 1        | <b>クロック発生回路の機能</b> 97                                 |

| 7. 2        | <b>クロック発生回路の構成</b> 97                                 |

| 7. 3        | <b>クロック発生回路を制御するレジスタ</b> 98                           |

| 7. 4        | <b>システム・クロック発振回路</b> 99                               |

|             | 7. 4. 1 システム・クロック発振回路 99                              |

|             | 7. 4. 2 分周回路 102                                      |

| 7. 5        | <b>クロック発生回路の動作</b> 102                                |

| 7. 6        | CPU <b>クロックの設定の変更</b> 103                             |

|             | 7. 6. 1 CPUクロックの切り替えに要する時間 103                        |

|             | 7. 6. 2 CPUクロックの切り替え手順 103                            |

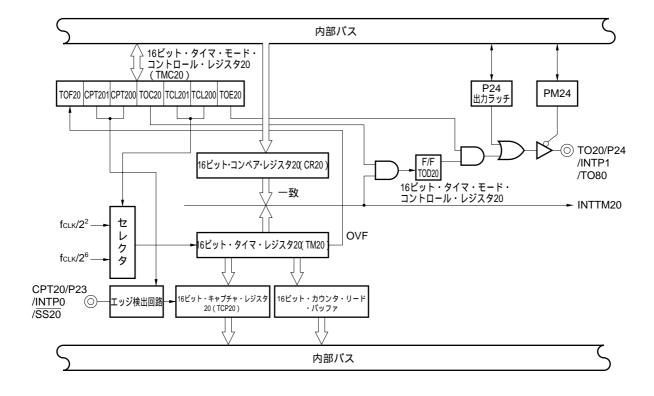

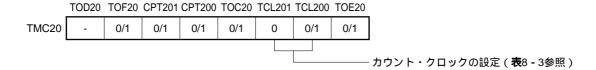

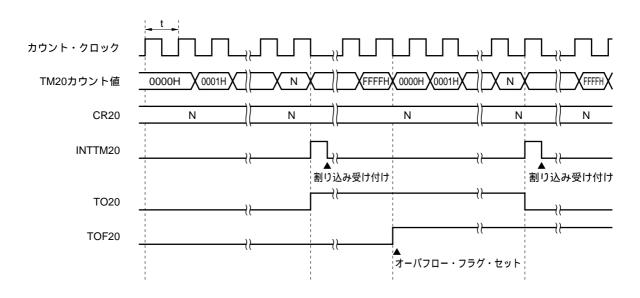

| <b>第</b> 8章 | 16 <b>ビット・タイマ・カウンタ</b> 105                            |

|             |                                                       |

| 8. 1        | 16 <b>ビット・タイマ・カウンタの機能</b> 106                         |

| 8. 2        | 16 <b>ビット・タイマ・カウンタの構成</b> 107                         |

| 8. 3        | 16 <b>ビット・タイマ・カウンタを制御するレジスタ</b> 109                   |

| 8. 4        | 16 <b>ビット・タイマ・カウンタの動作</b> 112                         |

|             | 8.4.1 タイマ割り込みとしての動作 112                               |

|             | 8.4.2 タイマ出力としての動作 114                                 |

|             | 8. 4. 3 キャプチャ動作 115                                   |

|             | 8.4.4 16ビット・タイマ・レジスタ20の読み出し 116                       |

| <b>第</b> 9章 | 8ピット・タイマ/イベント・カウンタ 117                                |

| 9. 1        | 8 <b>ビット・タイマ / イベント・カウンタの機能</b> 117                   |

| 9. 2        | 8 <b>ビット・タイマ/イベント・カウンタの構成</b> 118                     |

| 9. 3        | 8 <b>ビット・タイマ / イベント・カウンタを制御するレジスタ</b> 120             |

| 9. 4        | 8 <b>ビット・タイマ / イベント・カウンタの動作</b> 122                   |

|              | 9. 4. 2 外部イベント・カウンタとしての動作 124                                           |

|--------------|-------------------------------------------------------------------------|

|              | 9.4.3 方形波出力としての動作 125                                                   |

|              | 9.4.4 PWM出力としての動作 127                                                   |

| 9. 5         | 8 <b>ビット・タイマ / イベント・カウンタの注意事項</b> 129                                   |

| <b>第</b> 10章 | ウォッチドッグ・タイマ 131                                                         |

| 10. 1        | <b>ウォッチドッグ・タイマの機能</b> 131                                               |

| 10. 2        | <b>ウォッチドッグ・タイマの構成</b> 132                                               |

| 10. 3        | <b>ウォッチドッグ・タイマを制御するレジスタ</b> 133                                         |

| 10. 4        | <b>ウォッチドッグ・タイマの動作</b> 135                                               |

|              | 10.4.1 ウォッチドッグ・タイマとしての動作 135                                            |

|              | 10.4.2 インターバル・タイマとしての動作 136                                             |

| 第11章         | 8ピットA/Dコンパータ (μ PD789104, 789124サプシリーズ) 137                             |

| 11. 1        | 8 <b>ビット</b> A/D <b>コンバータの機能</b> 137                                    |

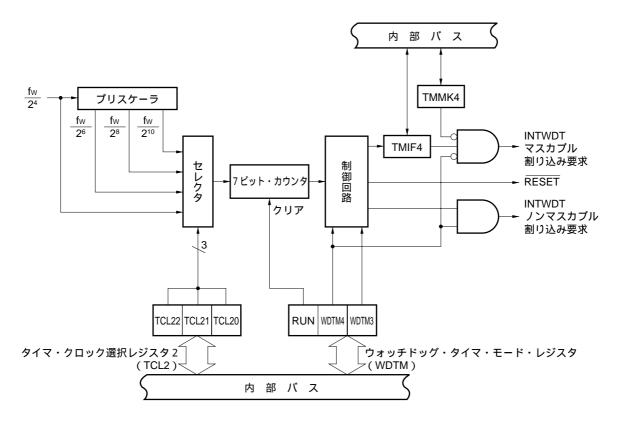

| 11. 2        | 8 <b>ビット</b> A/D <b>コンバータの構成</b> 137                                    |

| 11. 3        | 8 <b>ピット</b> A/D <b>コンバータを制御するレジスタ</b> 140                              |

| 11. 4        | 8 <b>ピット</b> A/D <b>コンバータの動作</b> 142                                    |

|              | 11. 4. 1 8ビットA/Dコンバータの基本動作 142                                          |

|              | 11. 4. 2 入力電圧と変換結果 143                                                  |

|              | 11. 4. 3 8ビットA/Dコンバータの動作モード 145                                         |

| 11. 5        | 8 <b>ピット</b> A/D <b>コンバータの注意事項</b> 146                                  |

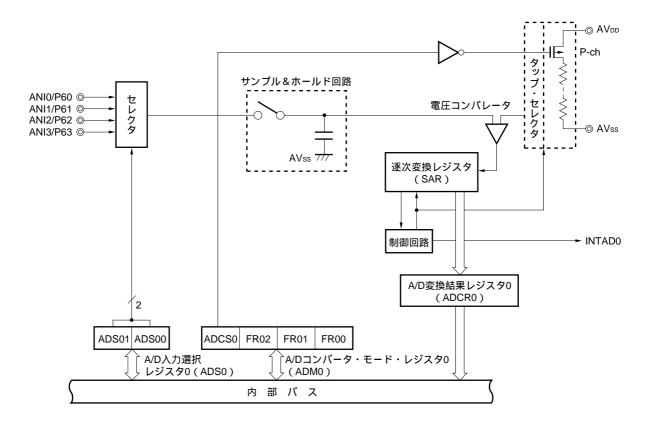

| 第12章         | 10 <b>ビット</b> A/D <b>コンバータ (</b> μ PD789114, 789134 <b>サブ</b> シリーズ) 151 |

| 12. 1        | 10 <b>ビット</b> A/D <b>コンバータの機能</b> 151                                   |

| 12. 2        | 10 <b>ビット</b> A/D <b>コンバータの構成</b> 151                                   |

| 12. 3        | 10 <b>ビット</b> A/D <b>コンバータを制御するレジスタ</b> 154                             |

| 12. 4        | 10 <b>ビット</b> A/D <b>コンパータの動作</b> 156                                   |

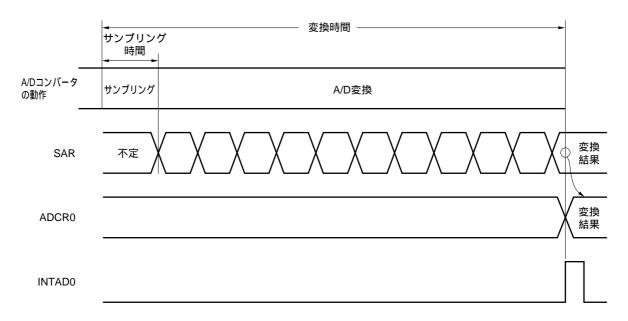

|              | 12. 4. 1 10ビットA/Dコンバータの基本動作 156                                         |

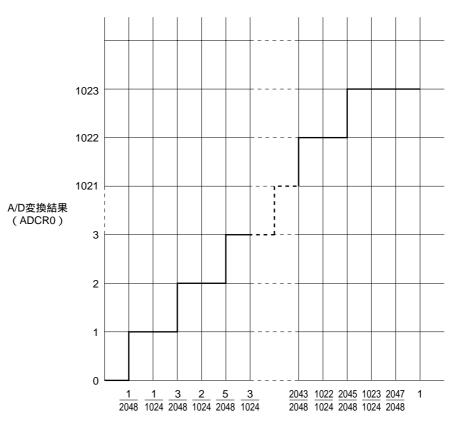

|              | 12.4.2 入力電圧と変換結果 158                                                    |

|              | 12. 4. 3 10ビットA/Dコンバータの動作モード 159                                        |

| 12. 5        | 10 <b>ビット</b> A/D <b>コンバータの注意事項</b> 160                                 |

| <b>第</b> 13章 | シリアル・インタフェース20 165                                                      |

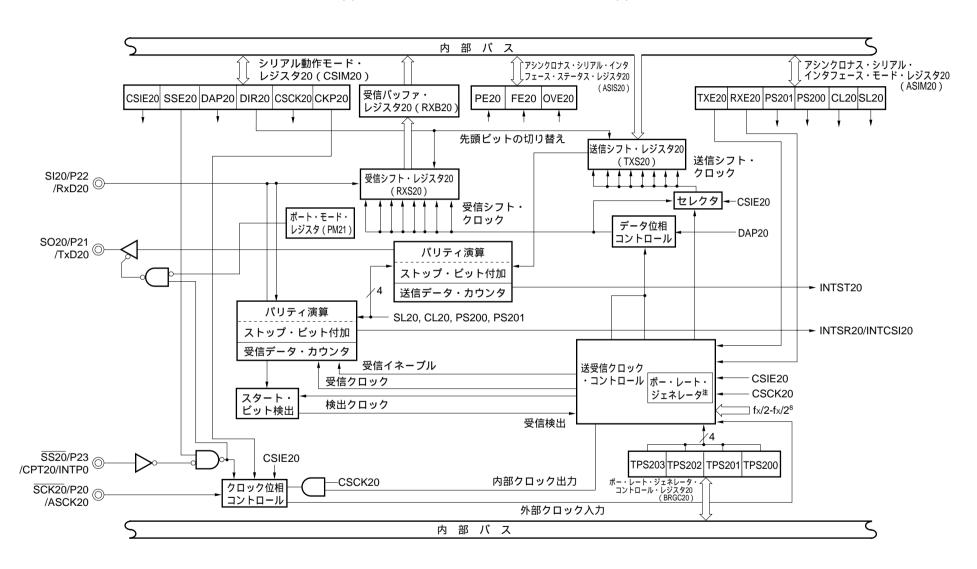

| 13. 1        | シリアル・インタフェース20 <b>の機能</b> 165                                           |

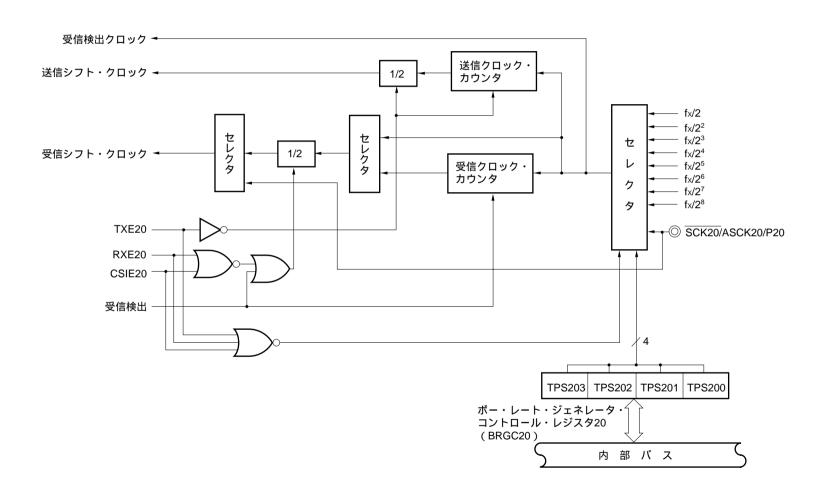

| 13. 2        | シリアル・インタフェース20 <b>の構成</b> 166                                           |

| 13. 3        | シリアル・インタフェース20 <b>を制御するレジスタ</b> 170                                     |

| 13. 4        | ・ <b>シリアル・インタフェース</b> 20 <b>の動作</b> 177                                 |

9.4.1 インターバル・タイマとしての動作 ... 122

- 13.4.1 動作停止モード ... 177

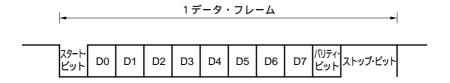

- 13.4.2 アシンクロナス・シリアル・インタフェース(UART)モード ... 179

- 13.4.3 3線式シリアルI/Oモード ... 191

#### 第14章 乗算器 ... 201

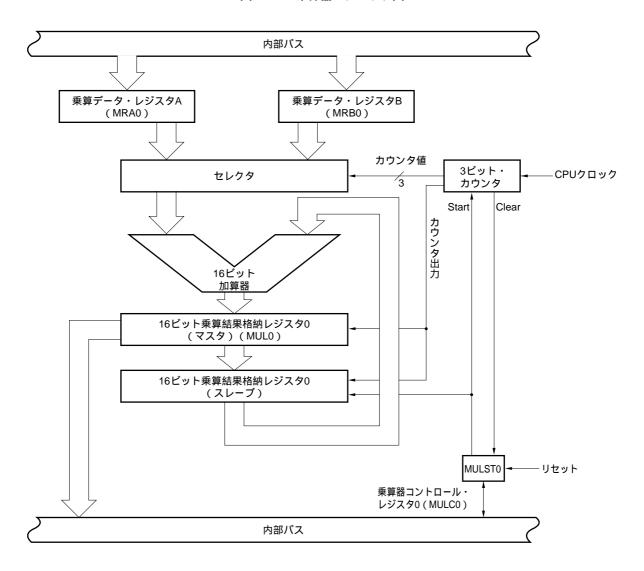

- 14.1 乗算器の機能 ... 201

- 14.2 乗算器の構成 ... 201

- 14.3 乗算器を制御するレジスタ ... 203

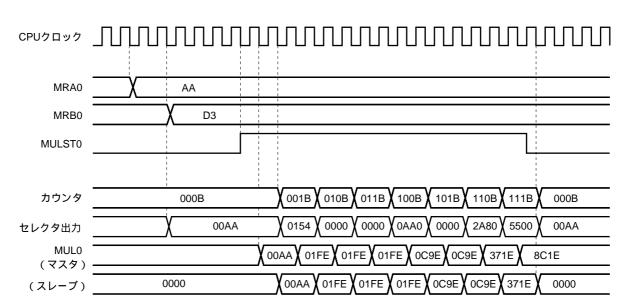

- 14.4 乗算器の動作 ... 204

#### 第15章 割り込み機能 ... 205

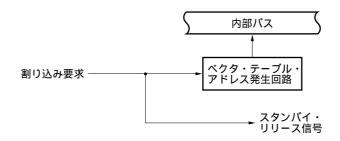

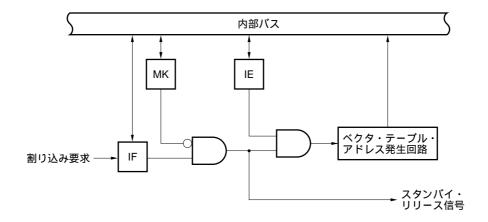

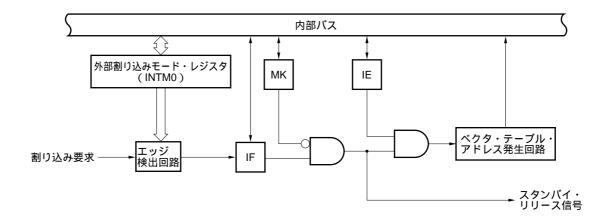

- 15.1 割り込み機能の種類 ... 205

- 15.2 割り込み要因と構成 ... 205

- 15.3 割り込み機能を制御するレジスタ ... 208

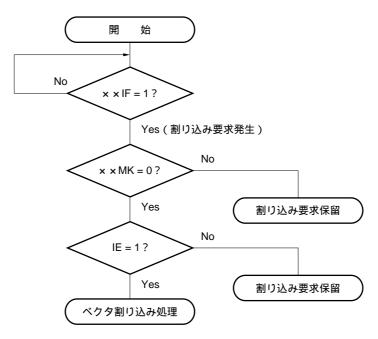

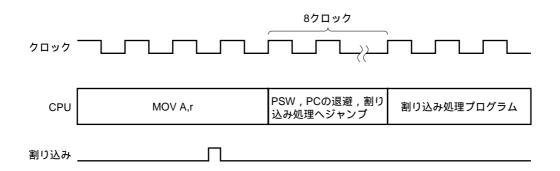

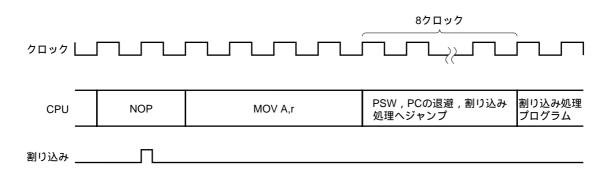

- 15.4 割り込み処理動作 ... 213

- 15. 4. 1 ノンマスカブル割り込み要求の受け付け動作 ... 213

- 15.4.2 マスカブル割り込み要求の受け付け動作 ... 215

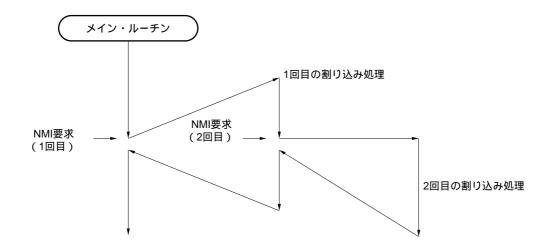

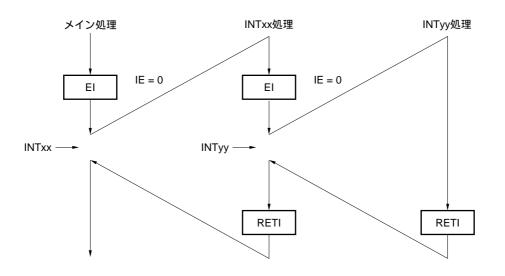

- 15.4.3 多重割り込み処理 ... 217

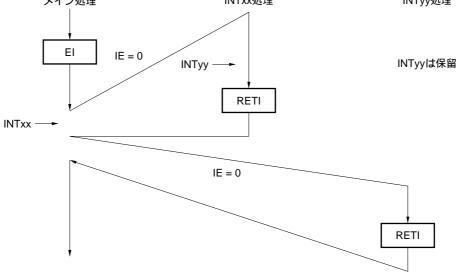

- 15.4.4 割り込み要求の保留 ... 218

#### 第16章 スタンパイ機能 ... 219

- 16.1 スタンバイ機能と構成 ... 219

- 16.1.1 スタンバイ機能 ... 219

- 16. 1. 2 スタンバイ機能を制御するレジスタ (μPD789104, 789114サブシリーズ)... 220

- 16.2 スタンバイ機能の動作 ... 221

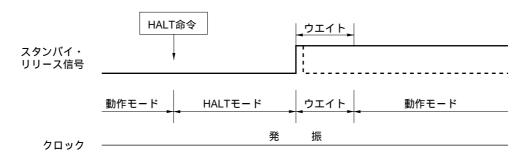

- 16.2.1 HALTモード ... 221

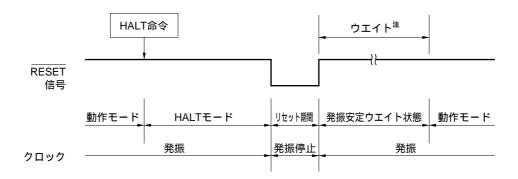

- 16.2.2 STOPモード ... 224

#### 第17章 リセット機能 ... 227

#### 第18章 μ PD78F9116, 78F9136 ... 231

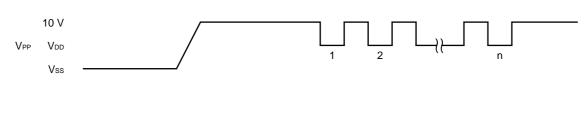

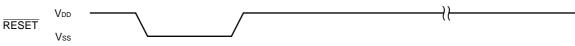

- 18.1 フラッシュ・メモリ・プログラミング ... 232

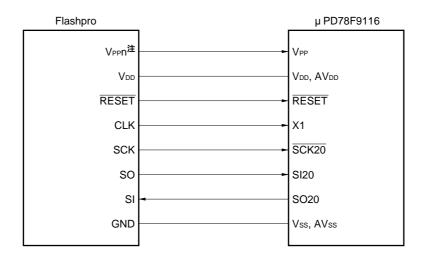

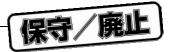

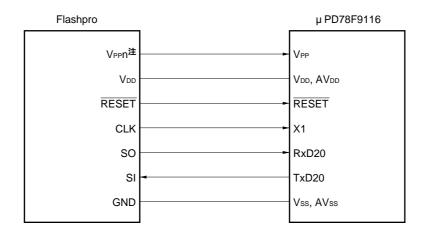

- 18.1.1 通信方式の選択 ... 232

- 18.1.2 フラッシュ・メモリ・プログラミングの機能 ... 233

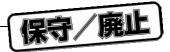

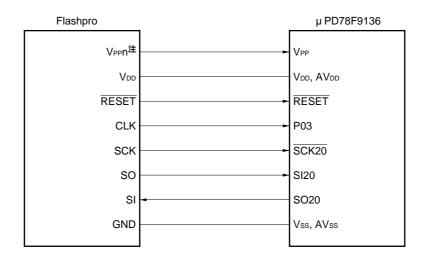

- 18.1.3 Flashpro の接続例 ... 233

- 18.1.4 Flashpro (PG-FP3)での設定例 ... 237

### 第19章 マスク・オプション (マスクROM製品) ... 239

#### 第20章 命令セットの概要 ... 241

- 20.1 オペレーション ... 241

- 20.1.1 オペランドの表現形式と記述方法 ... 241

- 20.1.2 オペレーション欄の説明 ... 242

- 20.1.3 フラグ動作欄の説明 ... 242

- 20.2 オペレーション一覧 ... 243

- 20.3 アドレシング別命令一覧 ... 249

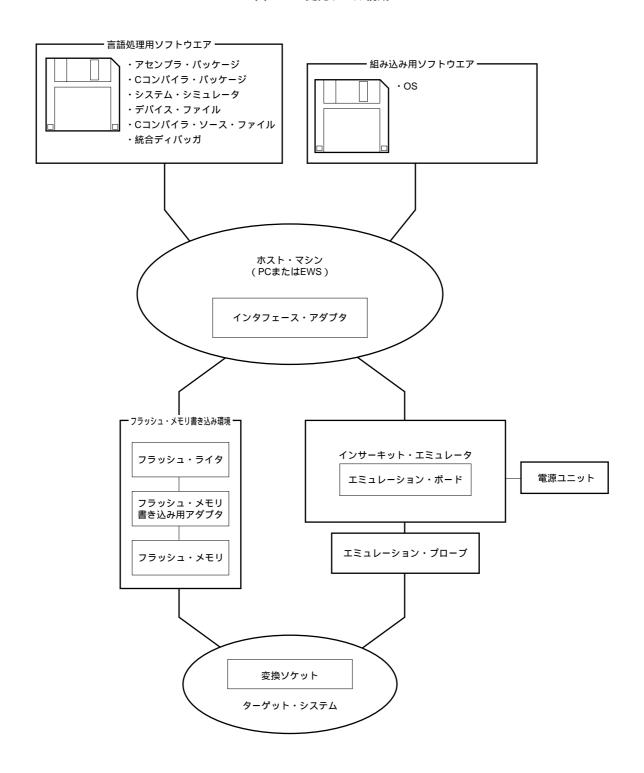

#### 付録A 開発ツール ... 253

- A. 1 **言語処理用ソフトウエア** ... 255

- A. 2 フラッシュ・メモリ書き込み用ツール ... 256

- A. 3 ディバグ用ツール ... 256

- A. 3. 1 ハードウエア ... 256

- A. 3. 2 ソフトウエア ... 257

#### 付録B 組み込み用ソフトウエア ... 259

#### 付録C レジスタ索引 ... 261

- C.1 レジスタ索引 (50音順) ... 261

- C. 2 レジスタ索引 (アルファベット順) ... 263

- ★ **付録D 改版履歴** ... 265

# 図の目次 (1/4)

| 図番号    | タイトル , ページ                                            |

|--------|-------------------------------------------------------|

| 3 - 1  | 端子の入出力回路一覧 45                                         |

|        |                                                       |

| 4 - 1  | メモリ・マップ(μPD789101, 789111, 789121, 789131) 47         |

| 4 - 2  | メモリ・マップ(μ PD789102, 789112, 789122, 789132) 48        |

| 4 - 3  | メモリ・マップ(μ PD789104, 789114, 789124, 789134) 49        |

| 4 - 4  | メモリ・マップ(μ PD78F9116, 78F9136) 50                      |

| 4 - 5  | データ・メモリのアドレシング (μPD789101, 789111, 789121, 789131) 53 |

| 4 - 6  | データ・メモリのアドレシング (μPD789102, 789112, 789122, 789132) 54 |

| 4 - 7  | データ・メモリのアドレシング (μPD789104, 789114, 789124, 789134) 55 |

| 4 - 8  | データ・メモリのアドレシング(μ PD78F9116, 78F9136) 56               |

| 4 - 9  | プログラム・カウンタの構成 57                                      |

| 4 - 10 | プログラム・ステータス・ワードの構成 57                                 |

| 4 - 11 | スタック・ポインタの構成 59                                       |

| 4 - 12 | スタック・メモリへ退避されるデータ 59                                  |

| 4 - 13 | スタック・メモリから復帰されるデータ 59                                 |

| 4 - 14 | 汎用レジスタの構成 60                                          |

|        |                                                       |

| 5 - 1  | ポートの種類 73                                             |

| 5 - 2  | P00-P03のブロック図 75                                      |

| 5 - 3  | P10, P11のブロック図 76                                     |

| 5 - 4  | P20のブロック図 77                                          |

| 5 - 5  | P21のブロック図 78                                          |

| 5 - 6  | P22, P23, P25のブロック図 79                                |

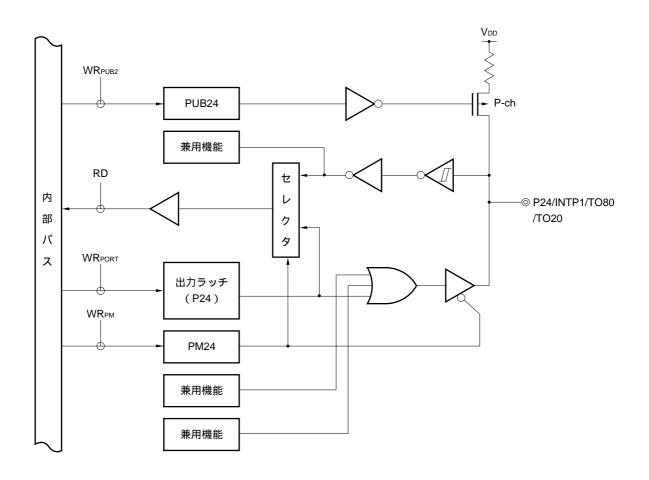

| 5 - 7  | P24のブロック図 80                                          |

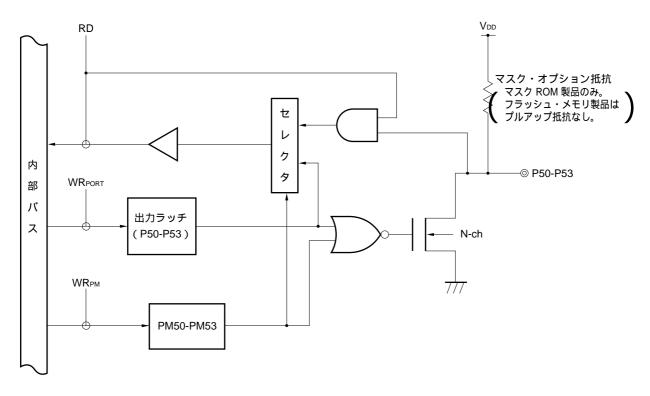

| 5 - 8  | P50-P53のブロック図 81                                      |

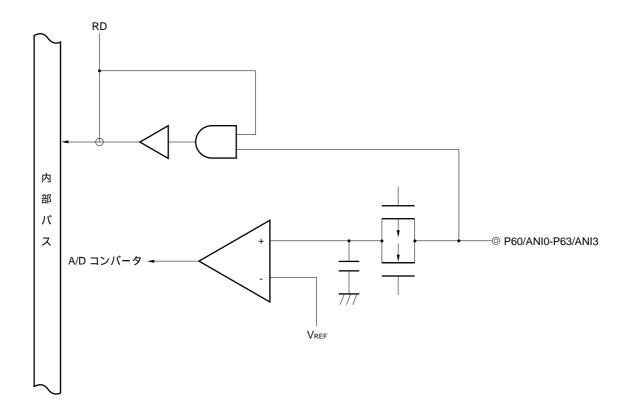

| 5 - 9  | P60-P63のブロック図 82                                      |

| 5 - 10 | ポート・モード・レジスタのフォーマット 84                                |

| 5 - 11 | プルアップ抵抗オプション・レジスタ0のフォーマット 84                          |

| 5 - 12 | プルアップ抵抗オプション・レジスタB2のフォーマット 85                         |

|        |                                                       |

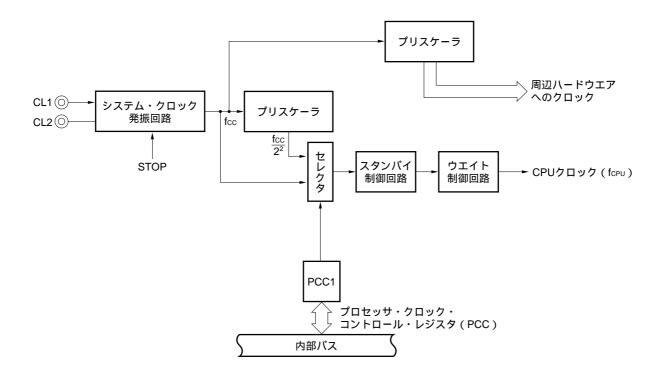

| 6 - 1  | クロック発生回路のブロック図 89                                     |

| 6 - 2  | プロセッサ・クロック・コントロール・レジスタのフォーマット 90                      |

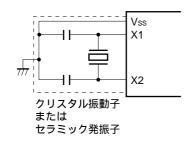

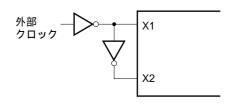

| 6 - 3  | システム・クロック発振回路の外付け回路 91                                |

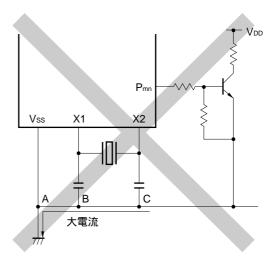

| 6 - 4  | 発振子の接続の悪い例 92                                         |

| 6 - 5  | CPUクロックの切り替え 95                                       |

|        |                                                       |

| 7 - 1  | クロック発生回路のブロック図 97                                     |

| 7 - 2  | プロセッサ・クロック・コントロール・レジスタのフォーマット 98                      |

7-3 システム・クロック発振回路の外付け回路 ... 99

# 図の目次 (2/4)

| 図番号     | タイトル , ページ                                      |

|---------|-------------------------------------------------|

| 7 - 4   | 発振子の接続の悪い例 100                                  |

| 7 - 5   | CPUクロックの切り替え 103                                |

|         |                                                 |

| 8 - 1   | 16ビット・タイマ・カウンタのブロック図 107                        |

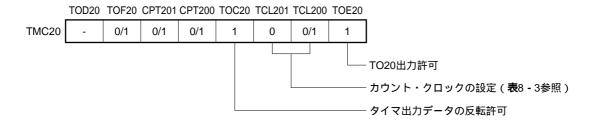

| 8 - 2   | 16ビット・タイマ・モード・コントロール・レジスタ20のフォーマット 110          |

| 8 - 3   | ポート・モード・レジスタ2のフォーマット 111                        |

| 8 - 4   | タイマ割り込み動作時の16ビット・タイマ・モード・コントロール・レジスタ20の設定内容 112 |

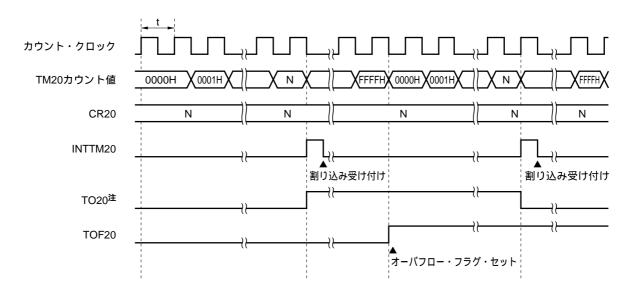

| 8 - 5   | タイマ割り込み動作のタイミング 113                             |

| 8 - 6   | タイマ出力動作時の16ビット・タイマ・モード・コントロール・レジスタ20の設定内容 114   |

| 8 - 7   | タイマ出力のタイミング 114                                 |

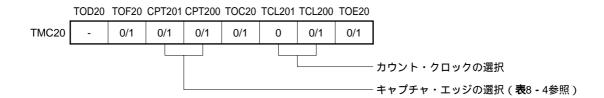

| 8 - 8   | キャプチャ動作時の16ビット・タイマ・モード・コントロール・レジスタ20の設定内容 115   |

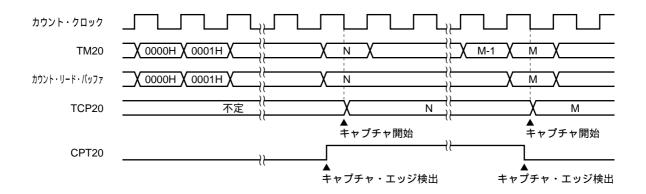

| 8 - 9   | キャプチャ動作のタイミング(CPT20端子の両エッジ指定時) 115              |

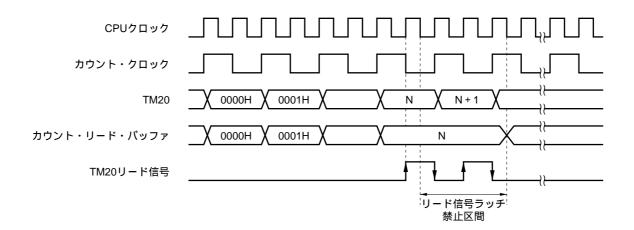

| 8 - 10  | 16ビット・タイマ・レジスタ20の読み出しのタイミング 116                 |

|         |                                                 |

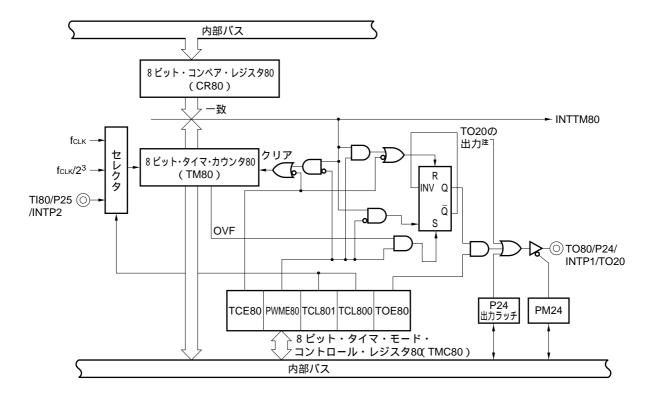

| 9 - 1   | 8ビット・タイマ / イベント・カウンタ80のブロック図 119                |

| 9 - 2   | 8ビット・タイマ・モード・コントロール・レジスタ80のフォーマット 120           |

| 9 - 3   | ポート・モード・レジスタ2のフォーマット 121                        |

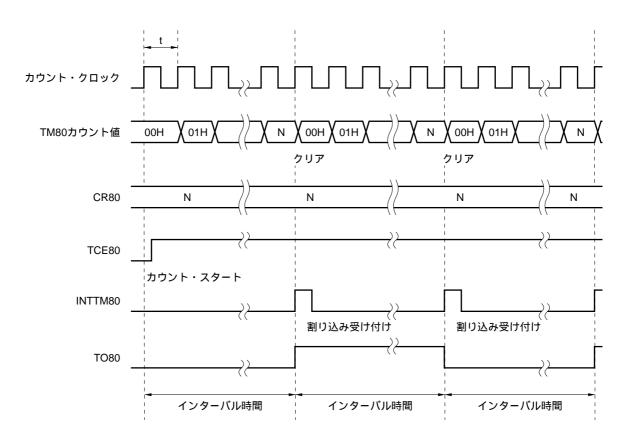

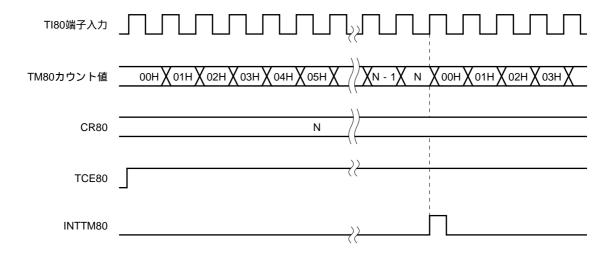

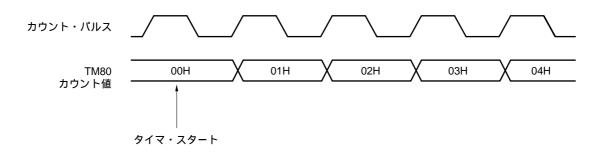

| 9 - 4   | インターバル・タイマ動作のタイミング 123                          |

| 9 - 5   | 外部イベント・カウンタ動作のタイミング(立ち上がりエッジ指定時) 124            |

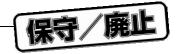

| 9 - 6   | 方形波出力のタイミング 126                                 |

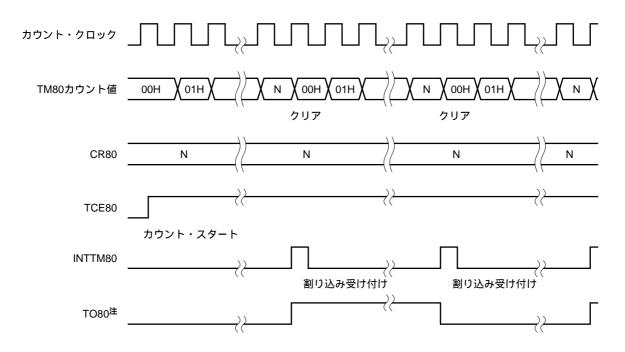

| 9 - 7   | PWM出力のタイミング 128                                 |

| 9 - 8   | 8ビット・タイマ・レジスタのスタート・タイミング 129                    |

| 9 - 9   | 外部イベント・カウンタとしての動作時のタイミング 129                    |

|         |                                                 |

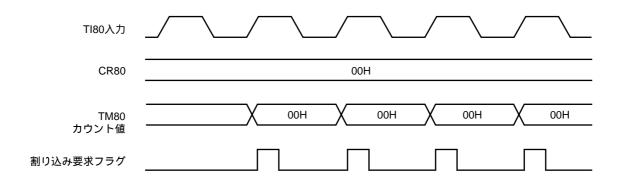

| 10 - 1  | ウォッチドッグ・タイマのブロック図 132                           |

| 10 - 2  | タイマ・クロック選択レジスタ2のフォーマット 133                      |

| 10 - 3  | ウォッチドッグ・タイマ・モード・レジスタのフォーマット 134                 |

|         |                                                 |

|         | 8ビットA/Dコンバータのブロック図 138                          |

| 11 - 2  | A/Dコンバータ・モード・レジスタ0のフォーマット 140                   |

|         | A/D入力選択レジスタ0のフォーマット 141                         |

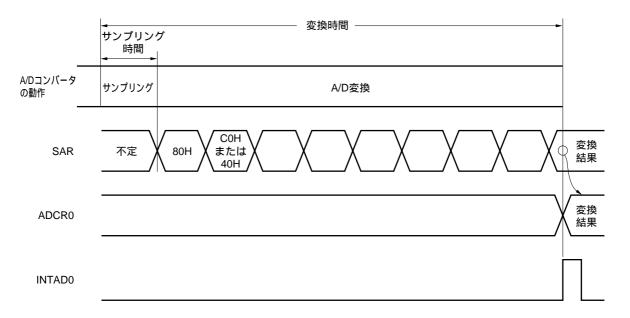

| 11 - 4  | 8ビットA/Dコンバータの基本動作 143                           |

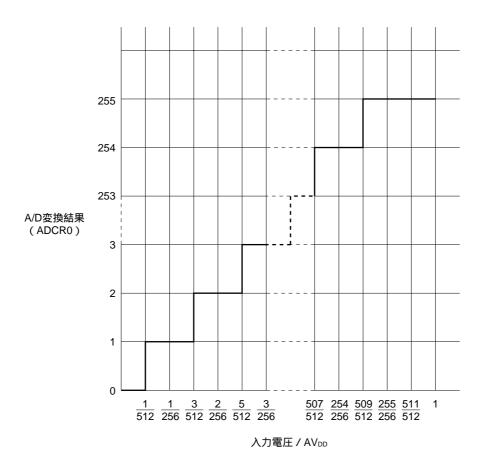

| 11 - 5  | アナログ入力電圧とA/D変換結果の関係 144                         |

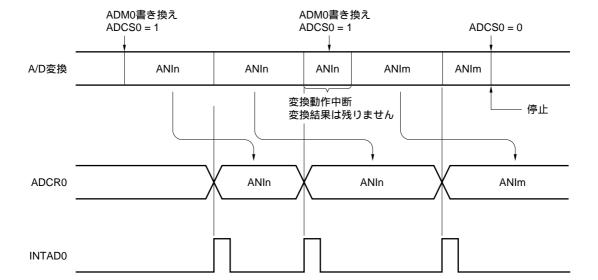

| 11 - 6  | ソフトウエア・スタートによるA/D変換動作 145                       |

| 11 - 7  | スタンバイ・モード時の消費電流を低減させる方法例 146                    |

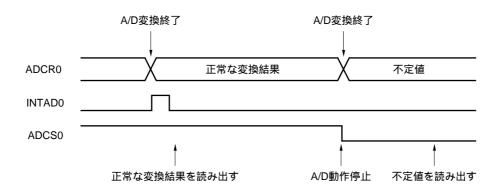

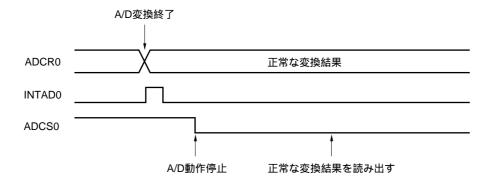

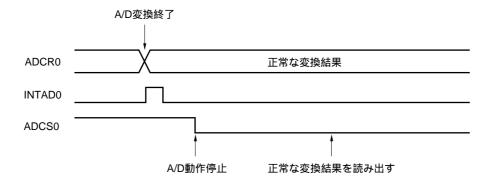

| 11 - 8  | 変換結果を読み出すタイミング(変換結果が不定値の場合) 147                 |

| 11 - 9  | 変換結果を読み出すタイミング(変換結果が正常値の場合) 147                 |

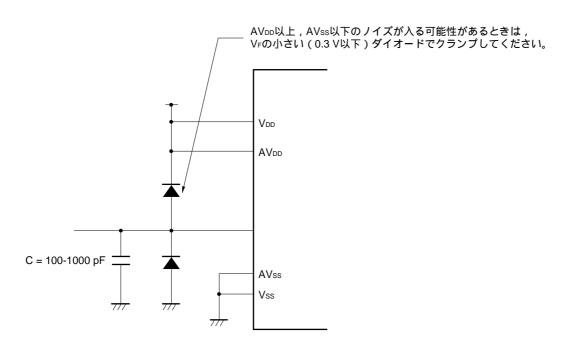

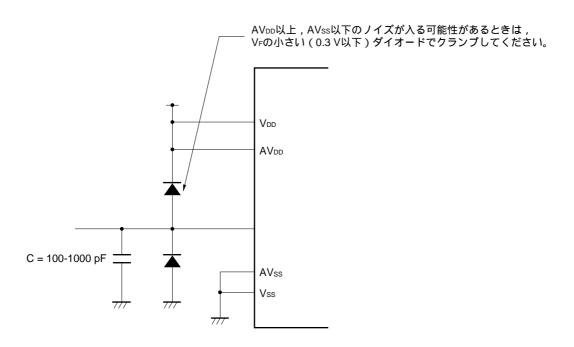

| 11 - 10 | アナログ入力端子の処理 148                                 |

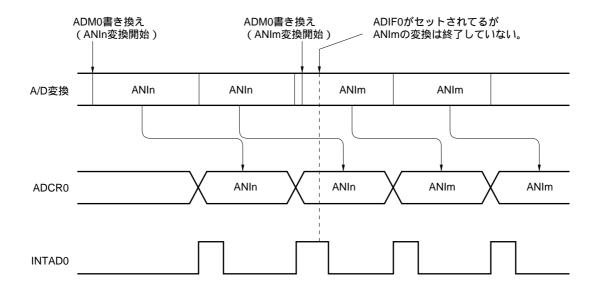

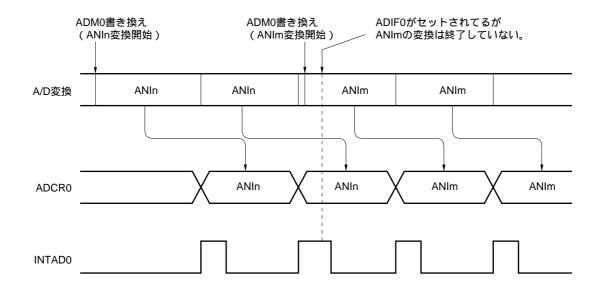

| 11 - 11 | A/D変換終了割り込み要求発生タイミング 149                        |

## 図の目次(3/4)

図番号 タイトル,ページ

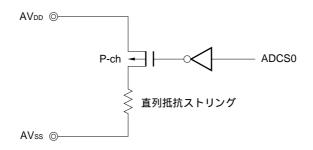

| 11 - 12 AVDD端子の: | 処理 149 |

|------------------|--------|

|------------------|--------|

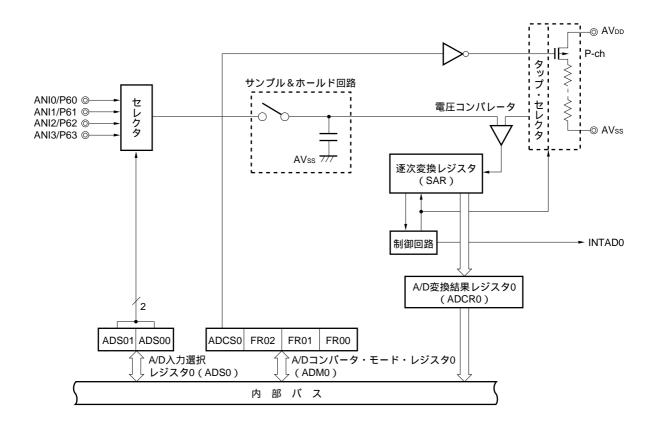

| 12 - 1 | 10ビットA/Dコンバータのブロック図 | <br>152 |

|--------|---------------------|---------|

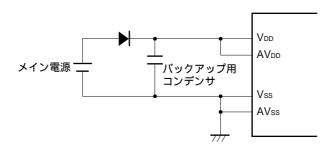

| 12 1   |                     | <br>102 |

- 12 2 A/Dコンバータ・モード・レジスタ0のフォーマット ... 154

- 12 3 A/D入力選択レジスタ0のフォーマット ... 155

- 12 4 10ビットA/Dコンバータの基本動作 ... 157

- 12 5 アナログ入力電圧とA/D変換結果の関係 ... 158

- 12 6 ソフトウエア・スタートによるA/D変換動作 ... 159

- 12 7 スタンバイ・モード時の消費電流を低減させる方法例 ... 160

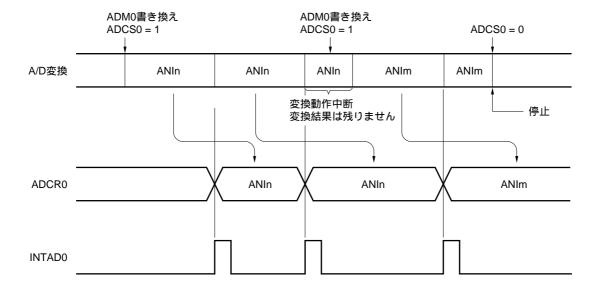

- 12-8 変換結果を読み出すタイミング(変換結果が不定値の場合) ... 161

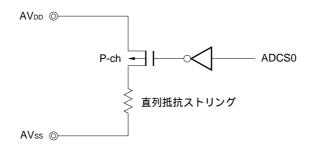

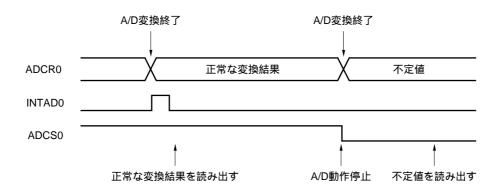

- 12 9 変換結果を読み出すタイミング(変換結果が正常値の場合) ... 161

- 12-10 アナログ入力端子の処理 ... 162

- 12 11 A/D変換終了割り込み要求発生タイミング ... 163

- 12 12 AVpp端子の処理 ... 163

- 13-1 シリアル・インタフェース20のブロック図 ... 167

- 13 2 ボー・レート・ジェネレータのブロック図 ... 168

- 13-3 シリアル動作モード・レジスタ20のフォーマット ... 170

- 13-4 アシンクロナス・シリアル・インタフェース・モード・レジスタ20のフォーマット ... 171

- 13-5 アシンクロナス・シリアル・インタフェース・ステータス・レジスタ20のフォーマット ... 173

- 13-6 ボー・レート・ジェネレータ・コントロール・レジスタ20のフォーマット ... 174

- 13 7 アシンクロナス・シリアル・インタフェースの送受信データのフォーマット ... 185

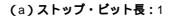

- 13-8 アシンクロナス・シリアル・インタフェース送信完了割り込みタイミング ... 187

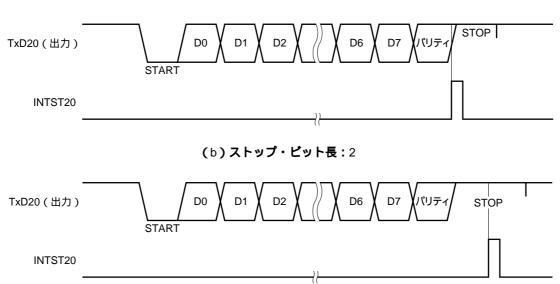

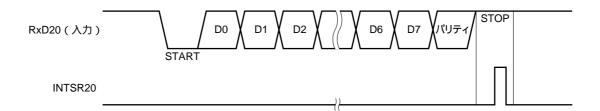

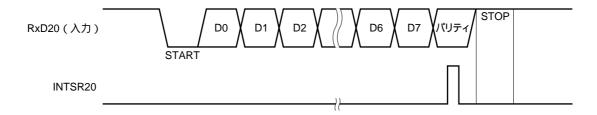

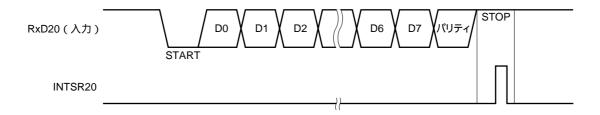

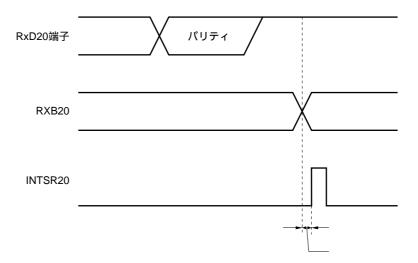

- 13 9 アシンクロナス・シリアル・インタフェース受信完了割り込みタイミング ... 188

- 13 10 受信エラー・タイミング ... 189

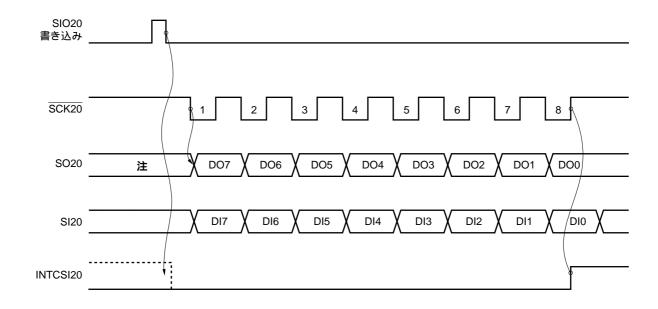

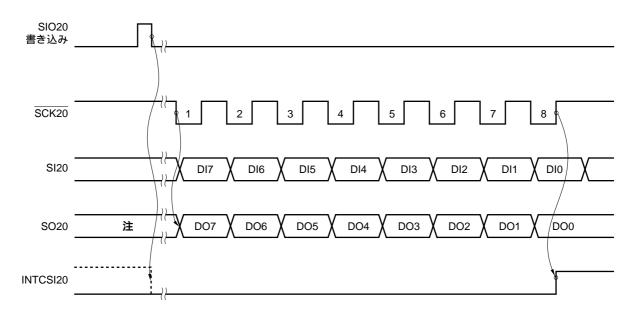

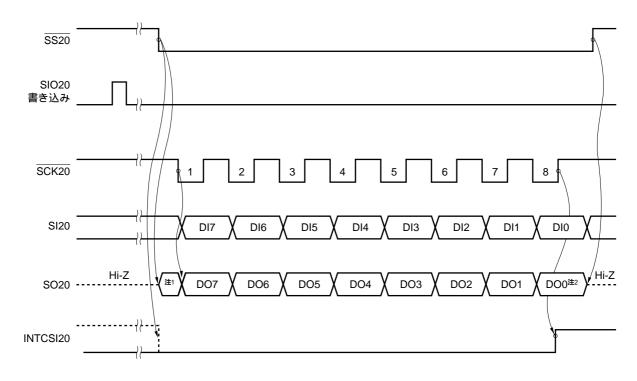

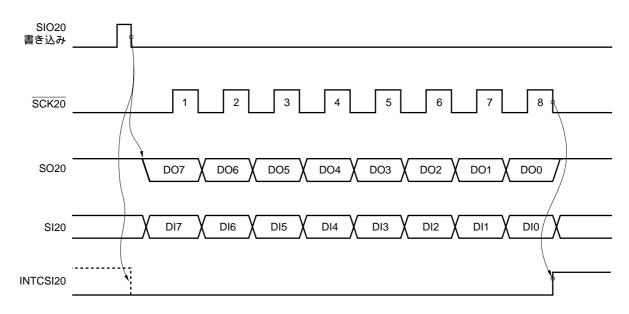

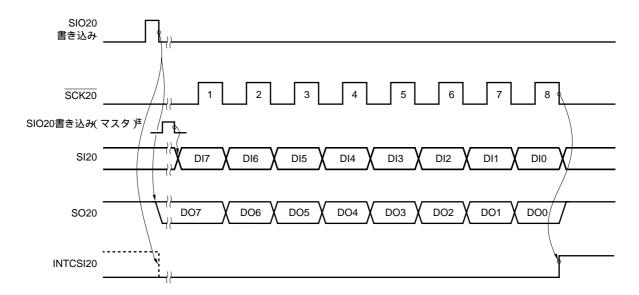

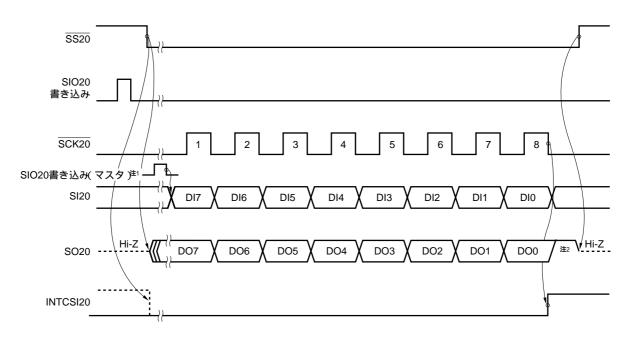

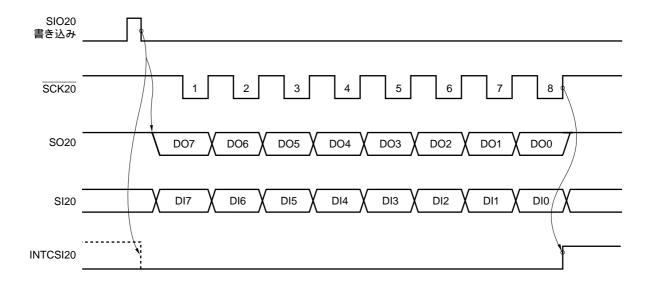

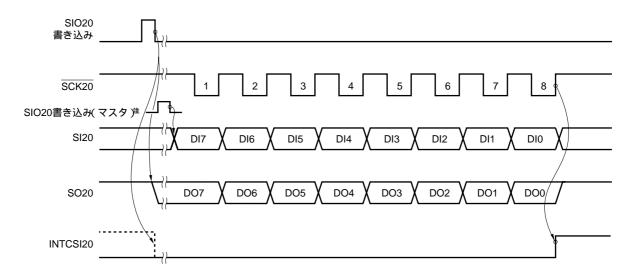

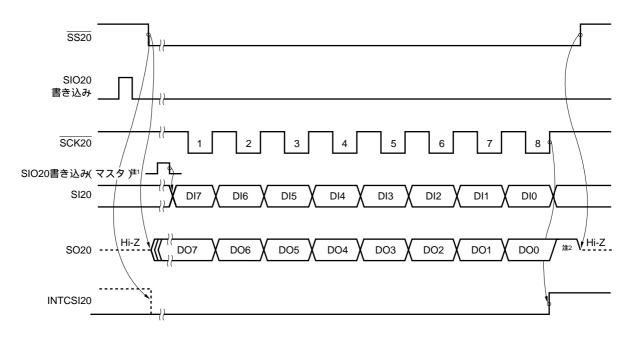

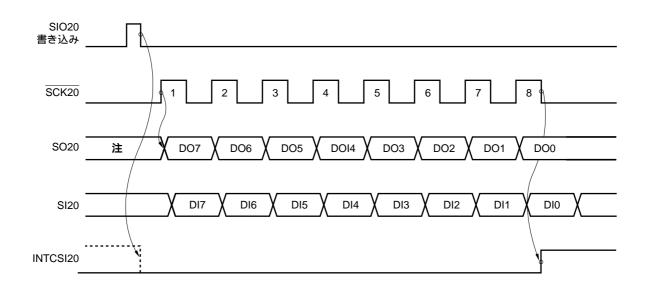

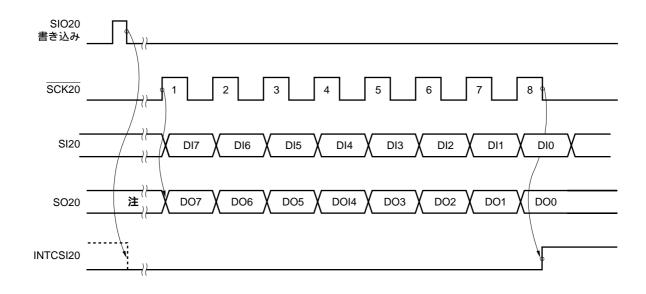

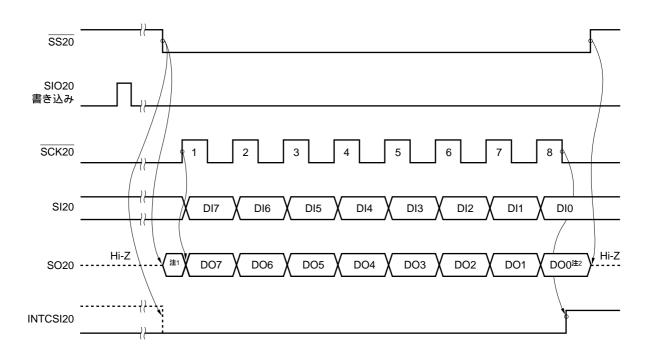

- 13 11 3線式シリアルI/Oモードのタイミング ... 194

- 14-1 乗算器のブロック図 ... 202

- 14-2 乗算器コントロール・レジスタ0のフォーマット ... 203

- 14 3 乗算器の動作タイミング(AAH×D3Hの例) ... 204

- 15-1 割り込み機能の基本構成 ... 207

- 15-2 割り込み要求フラグ・レジスタのフォーマット ... 209

- 15-3 割り込みマスク・フラグ・レジスタのフォーマット ... 210

- 15-4 外部割り込みモード・レジスタ0のフォーマット ... 211

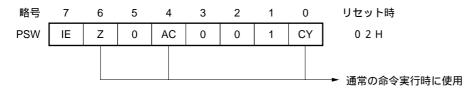

- 15-5 プログラム・ステータス・ワードの構成 ... 212

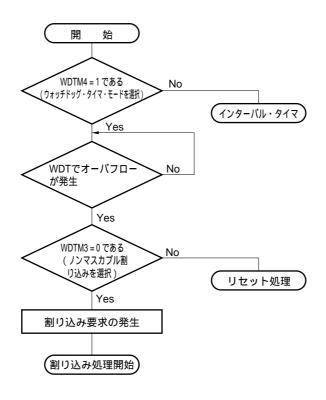

- 15-6 ノンマスカブル割り込み要求発生から受け付けまでのフロー・チャート ... 214

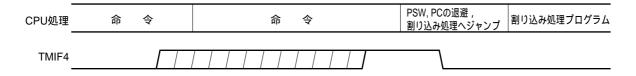

- 15-7 ノンマスカブル割り込み要求の受け付けタイミング ... 214

- 15-8 ノンマスカブル割り込み要求の受け付け動作 ... 214

# 図の目次 (4/4)

| 図番号     | タイトル , ページ                           |

|---------|--------------------------------------|

| 15 - 9  | 割り込み要求受け付け処理アルゴリズム 215               |

| 15 - 10 | 割り込み要求の受け付けタイミング(MOV A, rの例) 216     |

| 15 - 11 | 割り込み要求の受け付けタイミング                     |

|         | (命令実行中の最終クロックで割り込み要求フラグが発生したとき) 216  |

| 15 - 12 | 多重割り込みの例 217                         |

|         |                                      |

| 16 - 1  | 発振安定時間選択レジスタのフォーマット 220              |

| 16 - 2  | HALTモードの割り込み発生による解除 222              |

| 16 - 3  | HALTモードのRESET入力による解除 223             |

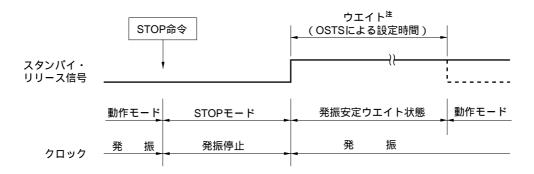

| 16 - 4  | STOPモードの割り込み発生による解除 225              |

| 16 - 5  | STOPモードのRESET入力による解除 226             |

|         |                                      |

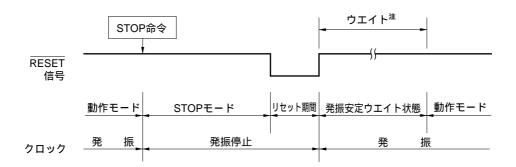

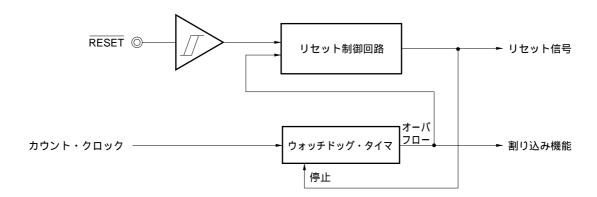

| 17 - 1  | リセット機能のブロック図 227                     |

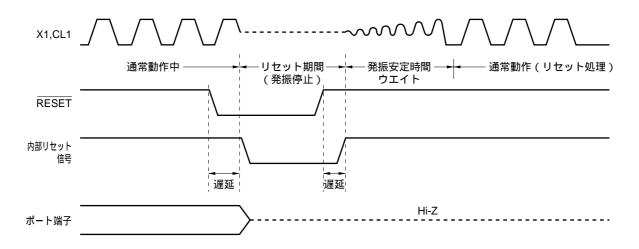

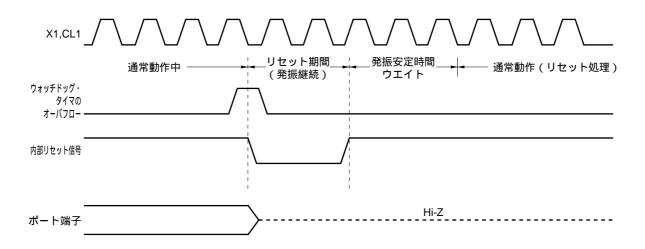

| 17 - 2  | RESET入力によるリセット・タイミング 228             |

| 17 - 3  | ウォッチドッグ・タイマのオーバフローによるリセット・タイミング 228  |

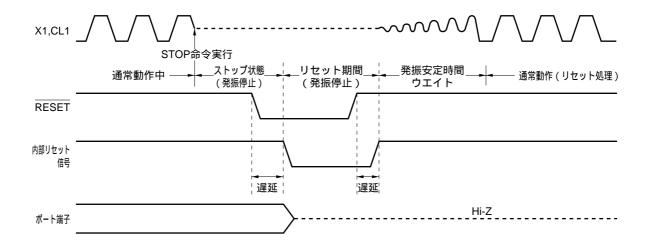

| 17 - 4  | STOPモード中のRESET入力によるリセット・タイミング 228    |

|         |                                      |

| 18 - 1  | 通信方式選択フォーマット 232                     |

| 18 - 2  | 3線式シリアルI/O方式でのFlashpro の接続例 233      |

| 18 - 3  | UART方式でのFlashpro の接続例 234            |

| 18 - 4  | 疑似3線式でのFlashpro の接続例 (P0を使用する場合) 234 |

| 18 - 5  | 3線式シリアルI/O方式でのFlashpro の接続例 235      |

| 18 - 6  | UART方式でのFlashpro の接続例 236            |

| 18 - 7  | 疑似3線式でのFlashpro の接続例 (P0を使用する場合) 236 |

|         |                                      |

A - 1 開発ツール構成 ... 254

# 表の目次 (1/2)

| 表番号    | タイトル , ページ                                                          |

|--------|---------------------------------------------------------------------|

| 3 - 1  | 各端子の入出力回路タイプと未使用端子の処理 44                                            |

| 4 - 1  | 内部ROM容量 51                                                          |

| 4 - 2  | ベクタ・テーブル 51                                                         |

| 4 - 3  | 特殊機能レジスター覧 62                                                       |

| 5 - 1  | ポートの機能 74                                                           |

| 5 - 2  | ポートの構成 75                                                           |

| 5 - 3  | 兼用機能使用時のポート・モード・レジスタ,出力ラッチの設定 83                                    |

| 6 - 1  | クロック発生回路の構成 89                                                      |

| 6 - 2  | CPUクロックの切り替えに要する最大時間 95                                             |

| 7 - 1  | クロック発生回路の構成 97                                                      |

| 7 - 2  | CPUクロックの切り替えに要する最大時間 103                                            |

| 8 - 1  | タイマの動作 105                                                          |

| 8 - 2  | 16ビット・タイマ・カウンタの構成 107                                               |

| 8 - 3  | 16ビット・タイマ・カウンタのインターバル時間 112                                         |

| 8 - 4  | キャプチャ・エッジの設定内容 115                                                  |

| 9 - 1  | 8ビット・タイマ / イベント・カウンタ80のインターバル時間 117                                 |

| 9 - 2  | 8ビット・タイマ / イベント・カウンタ80の方形波出力範囲 117                                  |

| 9 - 3  | 8ビット・タイマ / イベント・カウンタ80の構成 118                                       |

| 9 - 4  | 8ビット・タイマ / イベント・カウンタ80のインターバル時間 ( $f_X = 5.0 \text{ MHz}$ 動作時 ) 122 |

| 9 - 5  | 8ビット・タイマ / イベント・カウンタ80のインターバル時間(fcc = 4.0 MHz動作時) 122               |

| 9 - 6  | 8ビット・タイマ / イベント・カウンタ80の方形波出力範囲(fx = 5.0 MHz動作時) 125                 |

| 9 - 7  | 8ビット・タイマ / イベント・カウンタ80の方形波出力範囲(fcc = 4.0 MHz動作時) 125                |

| 10 - 1 | ウォッチドッグ・タイマの暴走検出時間 131                                              |

| 10 - 2 | インターバル時間 131                                                        |

| 10 - 3 | ウォッチドッグ・タイマの構成 132                                                  |

| 10 - 4 | ウォッチドッグ・タイマの暴走検出時間 135                                              |

| 10 - 5 | インターバル・タイマのインターバル時間 136                                             |

| 11 - 1 | 8ビットA/Dコンバータの構成 137                                                 |

| 12 - 1 | 10ビットA/Dコンバータの構成 151                                                |

# 表の目次 (2/2)

| 表番号    | タイトル , ページ                                   |

|--------|----------------------------------------------|

| 13 - 1 | シリアル・インタフェース20の構成 166                        |

| 13 - 2 | シリアル・インタフェース20の動作モードの設定一覧 172                |

| 13 - 3 | システム・クロックとボー・レートの関係例 175                     |

| 13 - 4 | ASCK20端子入力周波数とボー・レートの関係(BRGC20 = 80H設定時) 176 |

| 13 - 5 | システム・クロックとボー・レートの関係例 184                     |

| 13 - 6 | ASCK20端子入力周波数とボー・レートの関係(BRGC20 = 80H設定時) 184 |

| 13 - 7 | 受信エラーの要因 189                                 |

|        |                                              |

| 15 - 1 | 割り込み要因一覧 206                                 |

| 15 - 2 | 割り込み要求信号名に対する各種フラグ 208                       |

| 15 - 3 | マスカブル割り込み要求発生から処理までの時間 215                   |

|        |                                              |

| 16 - 1 | HALTモード時の動作状態 221                            |

| 16 - 2 | HALTモードの解除後の動作 223                           |

| 16 - 3 | STOPモード時の動作状態 224                            |

| 16 - 4 | STOPモードの解除後の動作 226                           |

|        |                                              |

| 17 - 1 | 各ハードウエアのリセット後の状態 229                         |

|        |                                              |

| 18 - 1 | フラッシュ・メモリ製品とマスクROM製品の違い 231                  |

| 18 - 2 | 通信方式一覧 232                                   |

| 18 - 3 | フラッシュ・メモリ・プログラミングの主な機能 233                   |

| 18 - 4 | PG-FP3での設定例 237                              |

|        |                                              |

| 19 - 1 | 端子のマスク・オプションの選択 239                          |

|        |                                              |

| 20 - 1 | オペランドの表現形式と記述方法 241                          |

# 第1章 概 説 (μ PD789104, 789114**サブシリーズ**)

### 1.1 特 徵

ROM, RAM容量

| 項目                 | プログラム・    | データ・メモリ |           |

|--------------------|-----------|---------|-----------|

| 品名                 |           |         | (内部高速RAM) |

| μ PD789101, 789111 | ROM       | 2 Kバイト  | 256バイト    |

| μ PD789102, 789112 |           | 4 Kバイト  |           |

| μ PD789104, 789114 |           | 8 Kバイト  |           |

| μ PD78F9116        | フラッシュ・メモリ | 16 Kバイト |           |

システム・クロック:クリスタル/セラミック発振

高速  $(0.4\,\mu\,\mathrm{s})$  と (低速1.6  $\mu\,\mathrm{s}$ ) に最小命令実行時間を変更可能  $(システム・クロック:5.0\,\mathrm{MHz}$ 動作時 )

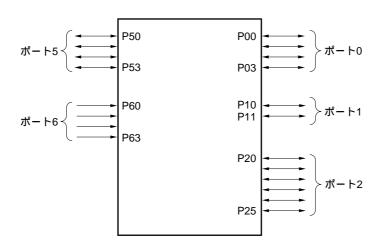

I/Oポート:20本

シリアル・インタフェース:1チャネル

3線式シリアルI/Oモード / UARTモード選択可能

8ビット分解能A/Dコンバータ:4チャネル( $\mu$  PD789104サブシリーズ) 10ビット分解能A/Dコンバータ:4チャネル( $\mu$  PD789114サブシリーズ)

タイマ:3チャネル

・16ビット・タイマ・カウンタ : 1チャネル・8ビット・タイマ / イベント・カウンタ : 1チャネル・ウォッチドッグ・タイマ : 1チャネル

乗算器内蔵:8ビット×8ビット = 16ビット

ベクタ割り込み要因:10 電源電圧:Vpp = 2.7~5.5 V

動作周囲温度: TA = -40~+85

### 1.2 応用分野

掃除機,洗濯機,冷蔵庫,バッテリ・チャージャなど

# ★ 1.3 オーダ情報

| オーダ名称                                         | パッケージ                                        | 内部ROM     |

|-----------------------------------------------|----------------------------------------------|-----------|

| $\mu$ PD789101GS- × × ×                       | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | マスクROM    |

| $\mu$ PD789101MC- $\times$ $\times$ -5A4      | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

| $\mu$ PD789102GS- x x x                       | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | "         |

| $\mu$ PD789102MC- $\times$ $\times$ -5A4      | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

| $\mu$ PD789104GS- × × ×                       | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | "         |

| $\mu$ PD789104MC- × × × -5A4                  | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

| $\mu$ PD789111GS- × × ×                       | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | "         |

| $\mu$ PD789111MC- $\times \times \times$ -5A4 | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

| $\mu$ PD789112GS- × × ×                       | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | "         |

| $\mu$ PD789112MC- $\times \times$ -5A4        | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

| $\mu$ PD789114GS- × × ×                       | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | "         |

| $\mu$ PD789114MC- × × × -5A4                  | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

| $\mu$ PD78F9116GS                             | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | フラッシュ・メモリ |

| $\mu$ PD78F9116MC-5A4                         | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

注意 上記製品のほかに30ピン・プラスチック・シュリンクDIP (オーダ名称未定)が計画中としてあります。

備考 ×××はROMコード番号です。

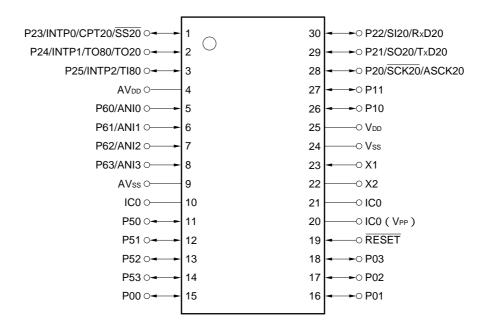

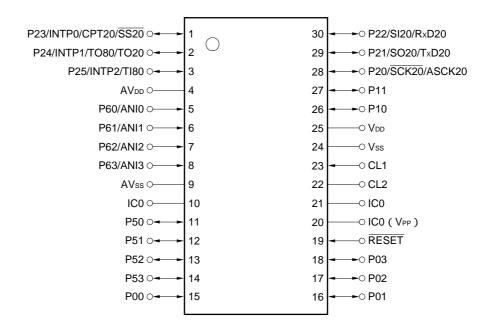

### 1.4 **端子接続図 (**Top View )

・30ピン・プラスチック・シュリンクSOP (300 mil, 樹脂厚1.7 mm)

$\begin{array}{lll} \mu \, \text{PD789101GS-} \times \times \times & \mu \, \text{PD789111GS-} \times \times \times \\ \mu \, \text{PD789102GS-} \times \times \times & \mu \, \text{PD789112GS-} \times \times \times \\ \mu \, \text{PD789104GS-} \times \times \times & \mu \, \text{PD789114GS-} \times \times \times \end{array}$

μ PD78F9116GS

★ ・30ピン・プラスチック・シュリンクSOP (300 mil, 樹脂厚1.2 mm)

μ PD789101MC- × × × -5A4 μ PD789111MC- × × × -5A4 μ PD789102MC- × × × -5A4 μ PD789104MC- × × × -5A4 μ PD789104MC- × × × -5A4 μ PD789116MC- × × × -5A4 μ PD78F9116MC- 5A4

★ 注意 上記製品のほかに30ピン・プラスチック・シュリンクDIP(オーダ名称未定)が計画中としてあります。

注意1. ICO (Internally Connected) 端子はVssに直接接続してください。

- 2. AVDD端子はVDDに接続してください。

- 3. AVss端子はVssに接続してください。

**備考** ( )内は, μ PD78F9116のとき。

ANI0-ANI3 : Analog Input RxD20 : Receive Data SCK20 ASCK20 : Asynchronous Serial Input : Serial Clock  $AV_{DD}$ : Analog Power Supply SI20 : Serial Input **AVss** : Analog Ground SO20 : Serial Output CPT20 : Capture Trigger Input **SS20** : Chip Select Input

IC0: Internally ConnectedTI80: Timer InputINTP0-INTP2: Interrupt from PeripheralsTO20, TO80: Timer OutputP00-P03: Port0TxD20: Transmit DataP10, P11: Port1VDD: Power Supply

P50-P53

: Port5

Vss

: Ground

P60-P63

: Port6

X1, X2

: Crystal 1, 2

RESET : Reset

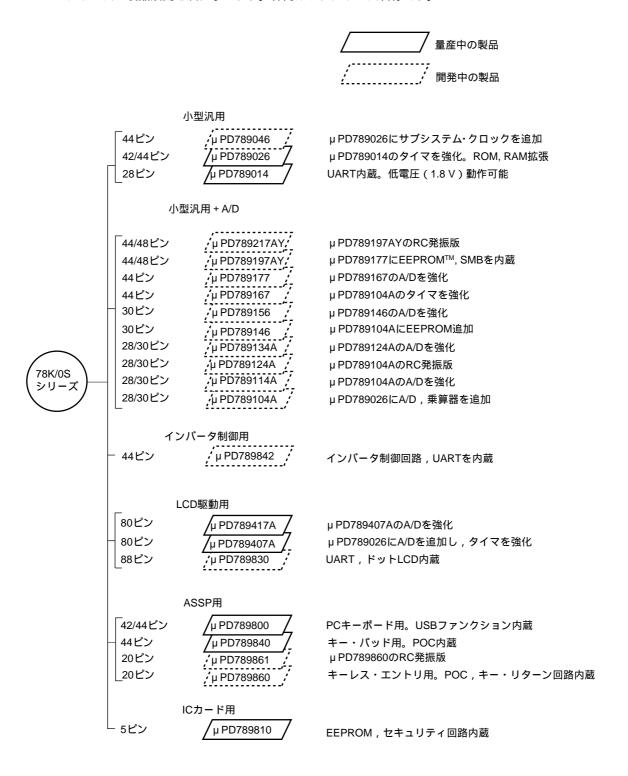

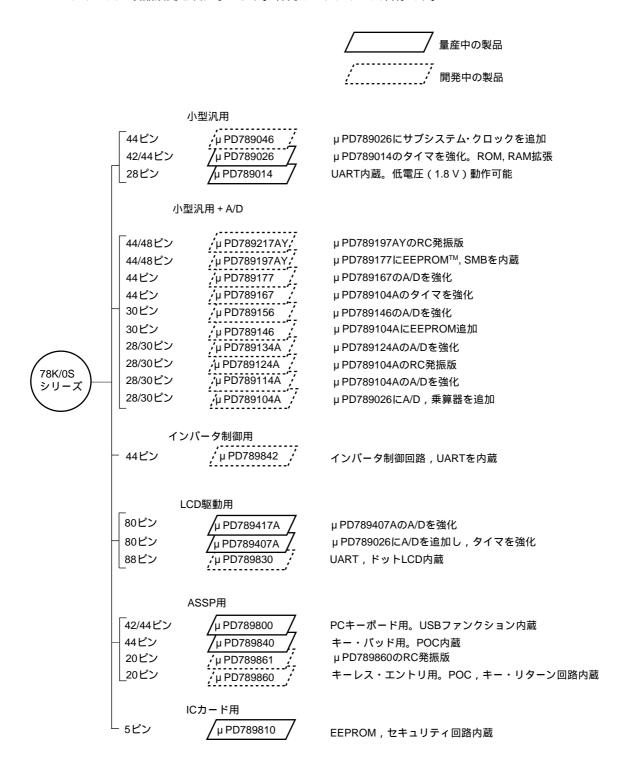

### ★ 1.5 78K/0Sシリーズの展開

78K/OSシリーズの製品展開を次に示します。枠内はサブシリーズ名称です。

#### 各サブシリーズ間の主な機能の違いを次に示します。

|            | 機能               | ROM容量     |       | タイ     | イマ   |      | 8-bit | 10-bit | シリアル・                | I/O | V <sub>DD</sub> | 備考       |

|------------|------------------|-----------|-------|--------|------|------|-------|--------|----------------------|-----|-----------------|----------|

| サブシリー      | -冱               |           | 8-bit | 16-bit | 時計   | WDT  | A/D   | A/D    | インタフェース              |     | 最小値             |          |

| 小型         | μ PD789046       | 16 K      | 1 ch  | 1 ch   | 1 ch | 1 ch | -     | -      | 1 ch ( UART : 1 ch ) | 34本 | 1.8 V           | -        |

| 汎用         | μ PD789026       | 4 K-16 K  |       |        | -    |      |       |        |                      |     |                 |          |

|            | μ PD789014       | 2 K-4 K   | 2 ch  | -      |      |      |       |        |                      | 22本 |                 |          |

| 小型         | μ PD789217AY     | 16 K-24 K | 3 ch  | 1 ch   | 1 ch | 1 ch | -     | 8 ch   | 2 ch UART : 1 ch     | 31本 | 1.8 V           | RC発振版,   |

| 汎用         |                  |           |       |        |      |      |       |        | SMB : 1 ch           |     |                 | EEPROM内蔵 |

| + A/D      | $\mu$ PD789197AY |           |       |        |      |      |       |        |                      |     |                 | EEPROM内蔵 |

|            | μ PD789177       |           |       |        |      |      |       |        | 1 ch ( UART : 1 ch ) |     |                 | -        |

|            | μ PD789167       |           |       |        |      |      | 8 ch  | -      |                      |     |                 |          |

|            | $\mu$ PD789156   | 8 K-16 K  | 1 ch  |        | -    |      | -     | 4 ch   |                      | 20本 |                 | EEPROM内蔵 |

|            | $\mu$ PD789146   |           |       |        |      |      | 4 ch  | -      |                      |     |                 |          |

|            | μ PD789134A      | 2 K-8 K   |       |        |      |      | -     | 4 ch   |                      |     |                 | RC発振版    |

|            | μ PD789124A      |           |       |        |      |      | 4 ch  | -      |                      |     |                 |          |

|            | μ PD789114A      |           |       |        |      |      | -     | 4 ch   |                      |     |                 | -        |

|            | μ PD789104A      |           |       |        |      |      | 4 ch  | -      |                      |     |                 |          |

| インバー       | μ PD789842       | 8 K-16 K  | 3 ch  | 注      | 1 ch | 1 ch | 8 ch  | -      | 1 ch ( UART : 1 ch ) | 30本 | 4.0 V           | -        |

| 夕制御        |                  |           |       |        |      |      |       |        |                      |     |                 |          |

| LCD        | μ PD789417A      | 12 K-24 K | 3 ch  | 1 ch   | 1 ch | 1 ch | -     | 7 ch   | 1 ch ( UART : 1 ch ) | 43本 | 1.8 V           | -        |

| 駆動用        | μ PD789407A      |           |       |        |      |      | 7 ch  | -      |                      |     |                 |          |

|            | μ PD789830       | 24 K      | 1 ch  |        |      |      | -     |        |                      | 30本 | 2.7 V           |          |

| ASSP       | $\mu$ PD789800   | 8 K       | 2 ch  | 1 ch   | -    | 1 ch | -     | -      | 2 ch ( USB : 1ch )   | 31本 | 4.0 V           | -        |

|            | $\mu$ PD789840   |           |       |        |      |      | 4 ch  |        | 1 ch                 | 29本 | 2.8 V           |          |

|            | $\mu$ PD789861   | 4 K       |       | -      |      |      | -     |        | -                    | 14本 | 1.8 V           | RC発振版    |

|            | μPD789860        |           |       |        |      |      |       |        |                      |     |                 | -        |

| ICカード<br>用 | μ PD789810       | 6 K       | -     | -      | -    | 1 ch | -     | -      | -                    | 1本  | 2.7 V           | EEPROM内蔵 |

注 10ビット・タイマ:1チャネル

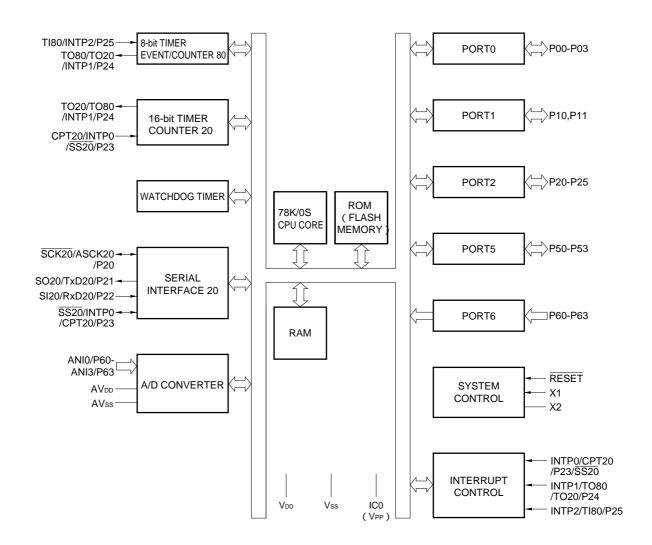

### 1.6 プロック図

備考1. 内部ROM容量は製品によって異なります。

2. ( )内は, μ PD78F9116のとき。

## 1.7 機能概要

| 項目        |         | μ PD789101                                 | μ PD789102                   | μ PD789104     | μ PD78F9116 |  |  |  |  |

|-----------|---------|--------------------------------------------|------------------------------|----------------|-------------|--|--|--|--|

|           |         | μ PD789111                                 | μ PD789112                   | $\mu$ PD789114 |             |  |  |  |  |

| 内部メモリ ROM |         | マスクROM                                     | マスクROM フラッシュ・メモ              |                |             |  |  |  |  |

|           |         | 2 Kバイト                                     | 4 Kバイト                       | 8 Kバイト         | 16 Kバイト     |  |  |  |  |

|           | 高速RAM   | 256バイト                                     | 256バイト                       |                |             |  |  |  |  |

| システム・クロ   | コック     | クリスタル / セラミッ                               | ク発振                          |                |             |  |  |  |  |

| 最小命令実行時   | 寺間      | 0.4/1.6 μs (システム                           | ・クロック:5.0 MHz動               | 作時)            |             |  |  |  |  |

| 汎用レジスタ    |         | 8ビット×8レジスタ                                 |                              |                |             |  |  |  |  |

| 命令セット     |         | ・16ビット演算                                   |                              |                |             |  |  |  |  |

|           |         | ・ビット操作(セット                                 | ・,リセット,テスト)な                 | など             |             |  |  |  |  |

| 乗算器       |         | 8ビット×8ビット=16                               | ビット                          |                |             |  |  |  |  |

| I/Oポート    |         | 合計                                         | : 20                         | 0本             |             |  |  |  |  |

|           |         | ·CMOS入力                                    | · CMOS入力 : 4本                |                |             |  |  |  |  |

|           |         | ・CMOS入出力 : 12本                             |                              |                |             |  |  |  |  |

|           |         | ・N-chオープン・ドレーン(12 V耐圧) :4本                 |                              |                |             |  |  |  |  |

| A/Dコンバータ  | 7       | 8ビット分解能×4チャネル(μ PD789104サブシリーズ)            |                              |                |             |  |  |  |  |

|           |         | 10ビット分解能×4チャネル(μ PD789114サブシリーズ)           |                              |                |             |  |  |  |  |

| シリアル・イン   | ンタフェース  | 3線式シリアルI/Oモード / UARTモード選択可能:1チャネル          |                              |                |             |  |  |  |  |

| タイマ       |         | 16ビット・タイマ : 1チャネル                          |                              |                |             |  |  |  |  |

|           |         | 8ビット・タイマ / イ                               | 8ビット・タイマ / イベント・カウンタ : 1チャネル |                |             |  |  |  |  |

|           |         | ウォッチドッグ・タイ                                 | ウォッチドッグ・タイマ : 1チャネル          |                |             |  |  |  |  |

| タイマ出力     |         | 1本                                         |                              |                |             |  |  |  |  |

| ベクタ割り     | マスカブル   | 内部:6,外部:3                                  |                              |                |             |  |  |  |  |

| 込み        | ノンマスカブル | 内部:1                                       |                              |                |             |  |  |  |  |

| 電源電圧      |         | V <sub>DD</sub> = 2.7 ~ 5.5 V              |                              |                |             |  |  |  |  |

| 動作周囲温度    |         | $T_A = -40 \sim +85$                       |                              |                |             |  |  |  |  |

| パッケージ     |         | ・30ピン・プラスチック・シュリンクDIP(計画中)                 |                              |                |             |  |  |  |  |

|           |         | ・30ピン・プラスチック・シュリンクSOP(300 mil , 樹脂厚1.7 mm) |                              |                |             |  |  |  |  |

|           |         | ・30ピン・プラスチック・シュリンクSOP(300 mil,樹脂厚1.2 mm)   |                              |                |             |  |  |  |  |

\*

# 第2章 概 説 (μ PD789124, 789134**サブシリーズ**)

### 2.1 特 徵

ROM, RAM容量

| 項目                 | プログラム・    | データ・メモリ |           |

|--------------------|-----------|---------|-----------|

| 品名                 |           |         | (内部高速RAM) |

| μ PD789121, 789131 | ROM       | 2 Kバイト  | 256バイト    |

| μ PD789122, 789132 |           | 4 Kバイト  |           |

| μ PD789124, 789134 |           | 8 Kバイト  |           |

| μ PD78F9136        | フラッシュ・メモリ | 16 Kバイト |           |

システム・クロック:RC発振

高速 ( $0.5\,\mu s$ ) と (低速 $2.0\,\mu s$ ) に最小命令実行時間を変更可能 (システム・クロック: 4.0~MHz動作時)

I/Oポート:20本

シリアル・インタフェース:1チャネル

3線式シリアルI/Oモード / UARTモード選択可能

8ビット分解能A/Dコンバータ:4チャネル( $\mu$  PD789124サブシリーズ) 10ビット分解能A/Dコンバータ:4チャネル( $\mu$  PD789134サブシリーズ)

タイマ:3チャネル

・16ビット・タイマ・カウンタ : 1チャネル・8ビット・タイマ / イベント・カウンタ : 1チャネル・ウォッチドッグ・タイマ : 1チャネル

乗算器内蔵:8ビット×8ビット = 16ビット

ベクタ割り込み要因:10 電源電圧:V<sub>DD</sub> = 2.7~5.5 V

動作周囲温度: TA = -40~+85

### 2.2 応用分野

掃除機,洗濯機,冷蔵庫,バッテリ・チャージャなど

# ★ 2.3 オーダ情報

| オーダ名称                                   | パッケージ                                        | 内部ROM     |

|-----------------------------------------|----------------------------------------------|-----------|

| $\mu$ PD789121GS- × × ×                 | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | マスクROM    |

| $\mu$ PD789121MC- × × × -5A4            | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

| $\mu$ PD789122GS- x x x                 | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | "         |

| $\mu$ PD789122MC- × × × -5A4            | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

| $\mu$ PD789124GS- × × ×                 | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | "         |

| $\mu$ PD789124MC- × × × -5A4            | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

| $\mu$ PD789131GS- × × ×                 | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | "         |

| $\mu$ PD789131MC- × × × -5A4            | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

| $\mu$ PD789132GS- × × ×                 | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | "         |

| $\mu$ PD789132MC- × × × -5A4            | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

| $\mu$ PD789134GS- × × ×                 | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | "         |

| $\mu$ PD789134MC- × × × -5A4            | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

| $\mu$ PD78F9136GS $^{	ext{	iny 2}}$     | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.7 mm ) | フラッシュ・メモリ |

| $\mu$ PD78F9136MC-5A4 $^{	ext{	iny 2}}$ | 30ピン・プラスチック・シュリンクSOP ( 300 mil , 樹脂厚1.2 mm ) | "         |

#### 注 開発中

注意 上記製品のほかに30ピン・プラスチック・シュリンクDIP (オーダ名称未定)が計画中としてあります。

備考 ×××はROMコード番号です。

### 2. 4 **端子接続図 (**Top View )

・30ピン・プラスチック・シュリンクSOP (300 mil, 樹脂厚1.7 mm)

$\mu$  PD789121GS- × × ×  $\mu$  PD789131GS- × × ×  $\mu$  PD789122GS- × × ×  $\mu$  PD789132GS- × × ×  $\mu$  PD789134GS- × × ×  $\mu$  PD789134GS- × × ×  $\mu$  PD78F9136GS<sup> $\pm$ </sup>

▶ ・30ピン・プラスチック・シュリンクSOP(300 mil, 樹脂厚1.2 mm)

μ PD789121MC- × × × -5A4 μ PD789131MC- × × × -5A4 μ PD789122MC- × × × -5A4 μ PD789132MC- × × × -5A4 μ PD789134MC- × × × -5A4 μ PD789136MC- 5A4 μ PD78F9136MC-5A4

注意 上記製品のほかに30ピン・プラスチック・シュリンクDIP (オーダ名称未定)が計画中としてあります。

#### 注 開発中

注意1. ICO (Internally Connected) 端子はVssに直接接続してください。

- 2. AVDD端子はVDDに接続してください。

- 3. AVss端子はVssに接続してください。

**備考** ( )内は, μ PD78F9136のとき。

$\bigstar$

ANI0-ANI3 : Analog Input RESET : Reset

ASCK20 : Asynchronous Serial Input RxD20 : Receive Data SCK20  $AV_{DD}$ : Analog Power Supply : Serial Clock **AVss** : Analog Ground SI20 : Serial Input CL1, CL2 : RC Oscillator SO20 : Serial Output

CPT20 : Capture Trigger Input SS20 : Chip Select Input IC0 : Internally Connected TI80 : Timer Input

INTP0-INTP2 : Interrupt from Peripherals TO20, TO80 : Timer Output P00-P03 : Port0 TxD20 : Transmit Data

P20-P25 : Port2 VPP : Programming Power Supply

$V_{DD}$

: Power Supply

P50-P53 : Port5 Vss : Ground

P60-P63 : Port6

: Port1

P10, P11

# ★ 2.5 78K/0Sシリーズの展開

78K/OSシリーズの製品展開を次に示します。枠内はサブシリーズ名称です。

## 各サブシリーズ間の主な機能の違いを次に示します。

|       | 機能               | ROM容量     |       | タイ     | イマ   |      | 8-bit | 10-bit | シリアル・                | I/O | V <sub>DD</sub> | 備考       |

|-------|------------------|-----------|-------|--------|------|------|-------|--------|----------------------|-----|-----------------|----------|

| サブシリ- | -沼               |           | 8-bit | 16-bit | 時計   | WDT  | A/D   | A/D    | インタフェース              |     | 最小値             |          |

| 小型    | μ PD789046       | 16 K      | 1 ch  | 1 ch   | 1 ch | 1 ch | -     | -      | 1 ch ( UART : 1 ch ) | 34本 | 1.8 V           | -        |

| 汎用    | μ PD789026       | 4 K-16 K  |       |        | -    |      |       |        |                      |     |                 |          |

|       | μ PD789014       | 2 K-4 K   | 2 ch  | -      |      |      |       |        |                      | 22本 |                 |          |

| 小型    | $\mu$ PD789217AY | 16 K-24 K | 3 ch  | 1 ch   | 1 ch | 1 ch | -     | 8 ch   | 2 ch UART : 1 ch     | 31本 | 1.8 V           | RC発振版,   |

| 汎用    |                  |           |       |        |      |      |       |        | SMB : 1 ch           |     |                 | EEPROM内蔵 |

| + A/D | $\mu$ PD789197AY |           |       |        |      |      |       |        |                      |     |                 | EEPROM内蔵 |

|       | μ PD789177       |           |       |        |      |      |       |        | 1 ch ( UART : 1 ch ) |     |                 | -        |

|       | μ PD789167       |           |       |        |      |      | 8 ch  | -      |                      |     |                 |          |

|       | μ PD789156       | 8 K-16 K  | 1 ch  |        | -    |      | -     | 4 ch   |                      | 20本 |                 | EEPROM内蔵 |

|       | μ PD789146       |           |       |        |      |      | 4 ch  | -      |                      |     |                 |          |

|       | μ PD789134A      | 2 K-8 K   |       |        |      |      | 1     | 4 ch   |                      |     |                 | RC発振版    |

|       | μ PD789124A      |           |       |        |      |      | 4 ch  | -      |                      |     |                 |          |

|       | μ PD789114A      |           |       |        |      |      | -     | 4 ch   |                      |     |                 | -        |

|       | μ PD789104A      |           |       |        |      |      | 4 ch  | -      |                      |     |                 |          |

| インバー  | μ PD789842       | 8 K-16 K  | 3 ch  | 注      | 1 ch | 1 ch | 8 ch  | -      | 1 ch ( UART : 1 ch ) | 30本 | 4.0 V           | -        |

| 夕制御   |                  |           |       |        |      |      |       |        |                      |     |                 |          |

| LCD   | μ PD789417A      | 12 K-24 K | 3 ch  | 1 ch   | 1 ch | 1 ch | -     | 7 ch   | 1 ch ( UART : 1 ch ) | 43本 | 1.8 V           | -        |

| 駆動用   | μ PD789407A      |           |       |        |      |      | 7 ch  | -      |                      |     |                 |          |

|       | μ PD789830       | 24 K      | 1 ch  |        |      |      | -     |        |                      | 30本 | 2.7 V           |          |

| ASSP  | μ PD789800       | 8 K       | 2 ch  | 1 ch   | -    | 1 ch | -     | -      | 2 ch ( USB : 1ch )   | 31本 | 4.0 V           | -        |

|       | μ PD789840       |           |       |        |      |      | 4 ch  |        | 1 ch                 | 29本 | 2.8 V           |          |

|       | μPD789861        | 4 K       |       | -      |      |      | -     |        | -                    | 14本 | 1.8 V           | RC発振版    |

|       | μ PD789860       |           |       |        |      |      |       |        |                      |     |                 | -        |

| ICカード | μ PD789810       | 6 K       | -     | -      | -    | 1 ch | -     | -      | -                    | 1本  | 2.7 V           | EEPROM内蔵 |

| 用     |                  |           |       |        |      |      |       |        |                      |     |                 |          |

注 10ビット・タイマ:1チャネル

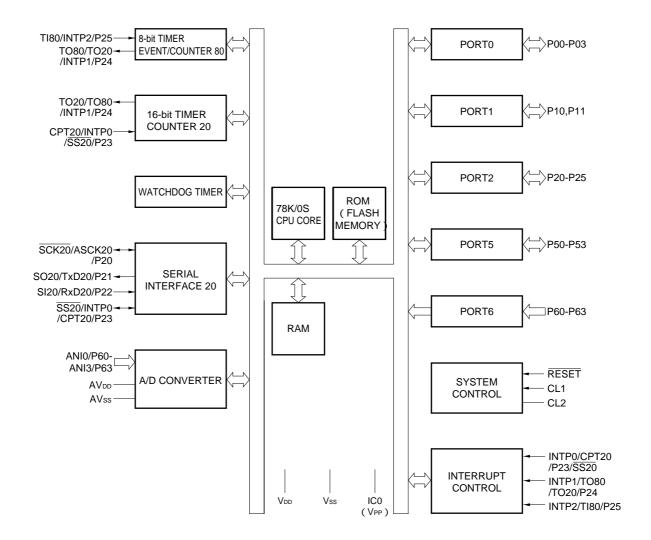

# 2.6 プロック図

備考1. 内部ROM容量は製品によって異なります。

2. ( )内は, μ PD78F9136のとき。

# 2.7 機能概要

| Iļ       | [ ]     | μ PD789121                               | μ PD789122      | μ PD789124        | μ PD78F9136 |  |  |  |  |  |

|----------|---------|------------------------------------------|-----------------|-------------------|-------------|--|--|--|--|--|

|          | T       | μ PD789131                               |                 |                   |             |  |  |  |  |  |

| 内部メモリ    | ROM     | マスクROM                                   | T               | T                 | フラッシュ・メモリ   |  |  |  |  |  |

|          |         | 2 Kバイト                                   | 4 Kバイト          | 8 Kバイト            | 16 Kバイト     |  |  |  |  |  |

|          | 高速RAM   | 256バイト                                   |                 |                   |             |  |  |  |  |  |

| システム・クロ  | コック     | RC発振                                     |                 |                   |             |  |  |  |  |  |

| 最小命令実行時  | 時間      | 0.5/2.0 μs (システム                         | ・クロック:4.0 MHz動  | 作時)               |             |  |  |  |  |  |

| 汎用レジスタ   |         | 8ビット×8レジスタ                               |                 |                   |             |  |  |  |  |  |

| 命令セット    |         | ・16ビット演算                                 |                 |                   |             |  |  |  |  |  |

|          |         | ・ビット操作(セット                               | ・, リセット , テスト)フ | など                |             |  |  |  |  |  |

| 乗算器      |         | 8ビット×8ビット=16                             | ビット             |                   |             |  |  |  |  |  |

| I/Oポート   |         | 合計                                       | : 2             | 0本                |             |  |  |  |  |  |

|          |         | ·CMOS入力                                  | : 4             | <br>本             |             |  |  |  |  |  |

|          |         | ・CMOS入出力                                 | : 1:            | 2本                |             |  |  |  |  |  |

|          |         | ・N-chオープン・ドレ                             | ノーン(12 V耐圧) :4  | 本                 |             |  |  |  |  |  |

| A/Dコンバータ | 7       | 8ビット分解能×4チャネル(μ PD789124サブシリーズ)          |                 |                   |             |  |  |  |  |  |

|          |         | 10ビット分解能×4チャネル(μ PD789134サブシリーズ)         |                 |                   |             |  |  |  |  |  |

| シリアル・イン  | ンタフェース  | 3線式シリアルI/Oモード / UARTモード選択可能:1チャネル        |                 |                   |             |  |  |  |  |  |

| タイマ      |         | 16ビット・タイマ                                | :               | 1チャネル             |             |  |  |  |  |  |

|          |         | 8ビット・タイマ / イ・                            | ベント・カウンタ :      | 1チャネル             |             |  |  |  |  |  |

|          |         | ウォッチドッグ・タイ                               | ∵マ :            | 1チャネル             |             |  |  |  |  |  |

| タイマ出力    |         | 1本                                       |                 |                   |             |  |  |  |  |  |

| ベクタ割り    | マスカブル   | 内部:6,外部:3                                |                 |                   |             |  |  |  |  |  |

| 込み       | ノンマスカブル | 内部:1                                     |                 |                   |             |  |  |  |  |  |

| 電源電圧     |         | V <sub>DD</sub> = 2.7 ~ 5.5 V            |                 |                   |             |  |  |  |  |  |

| 動作周囲温度   |         | T <sub>A</sub> = -40 ~ +85               |                 |                   |             |  |  |  |  |  |

| パッケージ    |         | ・30ピン・プラスチック・シュリンクDIP(計画中)               |                 |                   |             |  |  |  |  |  |

|          |         | ・30ピン・プラスチック・シュリンクSOP(300 mil,樹脂厚1.7 mm) |                 |                   |             |  |  |  |  |  |

|          |         | ・30ピン・プラスチッ                              | ック・シュリンクSOP (   | 300 mil,樹脂厚1.2 mr | m)          |  |  |  |  |  |

\*

$\bigstar$

# 第3章 端子機能

# 3.1 端子機能一覧

# \_\_\_\_(1) ポート端子

| 端子名称     | 入出力 | 機能                               | リセット時 | 兼用端子            |

|----------|-----|----------------------------------|-------|-----------------|

| P00-P03  | 入出力 | ポート0。                            | 入力    | -               |

|          |     | 4ビット入出力ポート。                      |       |                 |

|          |     | 1ビット単位で入力/出力の指定可能。               |       |                 |

|          |     | 入力ポートとして使用する場合 , プルアップ抵抗オプション・レ  |       |                 |

|          |     | ジスタ0(PU0)の設定により,内蔵プルアップ抵抗を使用可能。  |       |                 |

| P10, P11 | 入出力 | ポート1。                            | 入力    | -               |

|          |     | 2ビット入出力ポート。                      |       |                 |

|          |     | 1ビット単位で入力/出力の指定可能。               |       |                 |

|          |     | 入力ポートとして使用する場合 , プルアップ抵抗オプション・レ  |       |                 |

|          |     | ジスタ0(PU0)の設定により,内蔵プルアップ抵抗を使用可能。  |       |                 |

| P20      | 入出力 | ポート2。                            | 入力    | SCK20/ASCK20    |

| P21      |     | 6ビット入出力ポート。                      |       | SO20/TxD20      |

| P22      |     | 1ビット単位で入力/出力の指定可能。               |       | SI20/RxD20      |

| P23      |     | プルアップ抵抗オプション・レジスタB2(PUB2)の設定により, |       | INTP0/CPT20     |

|          |     | 内蔵プルアップ抵抗を使用可能。                  |       | /SS20           |

| P24      |     |                                  |       | INTP1/TO80/TO20 |

| P25      |     |                                  |       | INTP2/TI80      |

| P50-P53  | 入出力 | ポート5。                            | 入力    | -               |

|          |     | 4ビットN-chオープン・ドレーン入出力ポート。         |       |                 |

|          |     | 1ビット単位で入力 / 出力の指定可能。             |       |                 |

|          |     | マスクROM製品は,マスク・オプションにより,プルアップ抵    |       |                 |

|          |     | 抗の内蔵を指定可能。                       |       |                 |

| P60-P63  | 入力  | ポート6。                            | 入力    | ANI0-ANI3       |

|          |     | 4ビット入力専用ポート。                     |       |                 |

## (2) ポート以外の端子

| 端子名称            | 入出力 | 機能                                       | リセット時 | 兼用端子            |

|-----------------|-----|------------------------------------------|-------|-----------------|

| INTP0           | 入力  | 有効エッジ(立ち上がり,立ち下がり,立ち上がりおよび立ち下            | 入力    | P23/CPT20/SS20  |

| INTP1           |     | がりの両エッジ)指定可能な外部割り込み入力。                   |       | P24/TO80/TO20   |

| INTP2           |     |                                          |       | P25/TI80        |

| SI20            | 入力  | シリアル・インタフェースのシリアル・データ入力。                 | 入力    | P22/RxD20       |

| SO20            | 出力  | シリアル・インタフェースのシリアル・データ出力。                 | 入力    | P21/TxD20       |

| SCK20           | 入出力 | シリアル・インタフェースのシリアル・クロック入力/出力。             | 入力    | P20/ASCK20      |

| ASCK20          | 入力  | アシンクロナス・シリアル・インタフェース用シリアル・クロッ            | 入力    | P20/SCK20       |

|                 |     | ク入力。                                     |       |                 |

| SS20            | 入力  | シリアル・インタフェースのチップ・セレクト入力。                 | 入力    | P23/CPT20/INTP0 |

| RxD20           | 入力  | アシンクロナス・シリアル・インタフェース用シリアル・データ            | 入力    | P22/SI20        |

|                 |     | 入力。                                      |       |                 |

| TxD20           | 出力  | アシンクロナス・シリアル・インタフェース用シリアル・データ            | 入力    | P21/SO20        |

|                 |     | 出力。                                      |       |                 |

| TI80            | 入力  | 8ビット・タイマ ( TM80 ) への外部カウント・クロック入力。       | 入力    | P25/INTP2       |

| TO80            | 出力  | 8ビット・タイマ ( TM80 ) 出力。                    | 入力    | P24/INTP1/TO20  |

| TO20            | 出力  | 16ビット・タイマ ( TM20 ) 出力。                   | 入力    | P24/INTP1/TO80  |

| CPT20           | 入力  | キャプチャ・エッジ入力。                             | 入力    | P23/INTP0/SS20  |

| ANI0-ANI3       | 入力  | A/Dコンバータのアナログ入力。                         | 入力    | P60-P63         |

| AVss            | -   | A/Dコンバータのグランド電位。                         | -     | -               |

| AVDD            | -   | A/Dコンバータのアナログ電源。                         | -     | -               |

| X1              | 入力  | システム・クロック発振用クリスタル接続 ( μ PD789104, 789114 | -     | -               |

| X2              | -   | サブシリーズ)。                                 | -     | -               |

| CL1             | 入力  | システム・クロック発振用抵抗(R), コンデンサ(C)              | -     | -               |

| CL2             | -   | 接続(μ PD789124, 789134サブシリーズ)。            | -     | -               |

| RESET           | 入力  | システム・リセット入力。                             | 入力    | -               |

| V <sub>DD</sub> | -   | 正電源。                                     | -     | -               |

| Vss             | -   | グランド電位。                                  | -     |                 |

| IC0             | -   | 内部接続されています。Vssに直接接続してください。               | -     | -               |

| V <sub>PP</sub> | -   | フラッシュ・メモリ・プログラミング・モード設定。                 | -     | -               |

|                 |     | プログラム書き込み / ベリファイ時の高電圧印加。                |       |                 |

|                 |     | 通常モード時は,Vssに直接接続してください。                  |       |                 |

# 3.2 端子機能の説明

### 3. 2. 1 P00-P03 (Port0)

4ビットの入出力ポートです。ポート・モード・レジスタ0(PM0)により1ビット単位で入力ポートまたは出力ポートに指定できます。入力ポートとして使用する場合,プルアップ抵抗オプション・レジスタ0(PU0)により,内蔵プルアップ抵抗を使用できます。

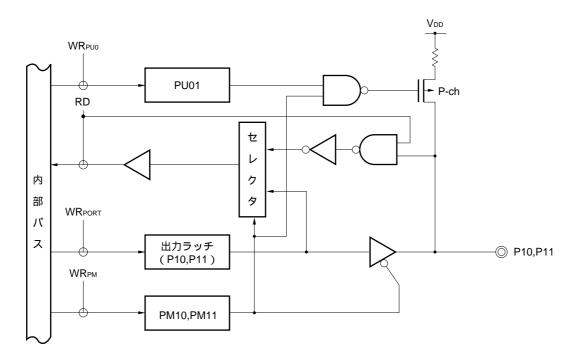

#### 3. 2. 2 P10, P11 (Port1)

2ビットの入出力ポートです。ポート・モード・レジスタ1 (PM1)により1ビット単位で入力ポートまたは出力ポートに指定できます。入力ポートとして使用する場合,プルアップ抵抗オプション・レジスタ0 (PU0)により,内蔵プルアップ抵抗を使用できます。

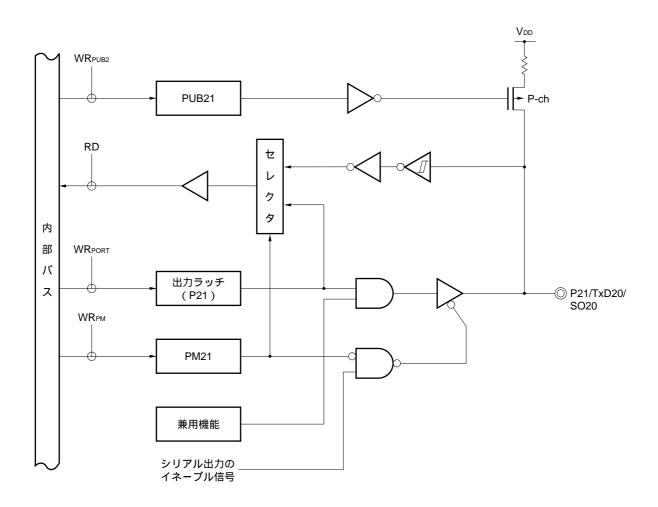

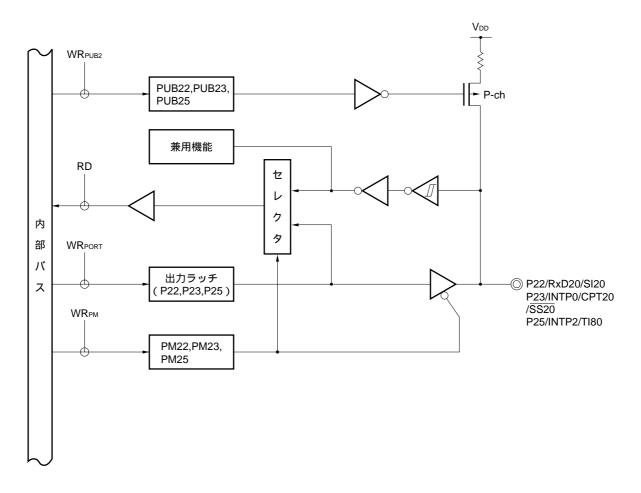

### 3. 2. 3 P20-P25 (Port2)

6ビット入出力ポートです。入出力ポートのほかにタイマの入出力,外部割り込み入力,シリアル・インタフェースのデータ入出力,クロック入出力機能があります。

1ビット単位で次のような動作モードを指定できます。

#### (1) ポート・モード

6ビットの入出力ポートとして機能します。ポート・モード・レジスタ2 (PM2)により,1ビット単位で入力ポートまたは出力ポートに指定できます。ポート・モード・レジスタ2 (PM2)にかかわらず,1ビット単位で,プルアップ抵抗オプション・レジスタB2 (PUB2)により内蔵プルアップ抵抗を使用できます。

#### (2) コントロール・モード

タイマの入出力,外部割り込み入力,シリアル・インタフェースのデータ入出力,クロック入出力として機能します。

#### (a) TI80

8ビット・タイマ/イベント・カウンタ80への外部クロック入力端子です。

#### (b) TO20, TO80

16ビット・タイマ,8ビット・タイマ出力端子です。

#### (c) CPT20

キャプチャ・エッジ入力端子です。

#### (d) INTP0-INTP2

有効エッジ(立ち上がりエッジ,立ち下がりエッジ,立ち上がりおよび立ち下がりエッジの両エッジ)指定可能な外部割り込み入力端子です。

#### (e) SI20, SO20

シリアル・インタフェースのシリアル・データの入出力端子です。

(f) SCK20

シリアル・インタフェースのシリアル・クロックの入出力端子です。

(g) SS20

シリアル・インタフェースのチップ・セレクト入力端子です。

(h) RxD20, TxD20

アシンクロナス・シリアル・インタフェース用シリアル・データ入出力端子です。

(i) ASCK20

アシンクロナス・シリアル・インタフェース用シリアル・クロック入力端子です。

注意 シリアル・インタフェースの端子として使用する場合は,その機能に応じて入出力および 出力ラッチの設定が必要となります。設定方法については表13 - 2 シリアル・インタフェース20の動作モードの設定一覧を参照してください。

#### 3. 2. 4 P50-P53 (Port 5)

4ビットのN-chオープン・ドレーン入出力ポートです。ポート・モード・レジスタ5 (PM5) により1ビット 単位で入力または出力ポートに指定できます。マスクROM製品は,マスク・オプションにより,プルアップ抵 抗の内蔵を指定可能です。

3. 2. 5 P60-P63 (Port 6)

4ビット入力専用ポートです。汎用入力ポートのほかに,A/Dコンバータ入力機能があります。

(1)ポート・モード

4ビットの入力専用ポートとして機能します。

(2) コントロール・モード

A/Dコンバータのアナログ入力(ANIO-ANI3)として機能します。

3. 2. 6 RESET

ロウ・レベル・アクティブのシステム・リセット入力端子です。

3. 2. 7 X1, X2 (μ PD789104, 789114サプシリーズ)

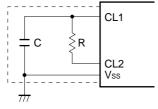

システム・クロック発振用クリスタル振動子接続端子です。 外部クロックを供給するときは,X1に入力し,X2にその反転信号を入力してください。

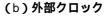

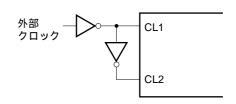

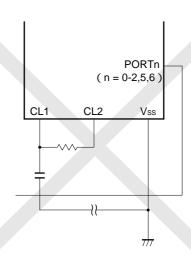

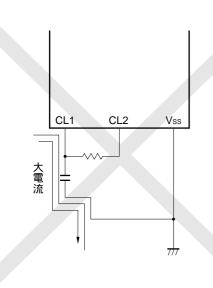

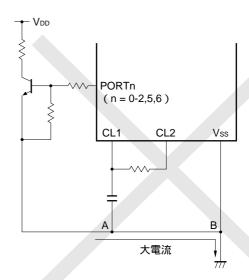

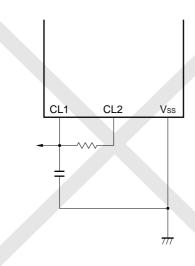

3. 2. 8 CL1, CL2 (μ PD789124, 789134サプシリーズ)

システム・クロック発振用抵抗(R), コンデンサ(C)接続端子です。

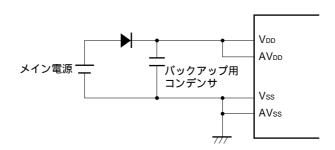

3. 2. 9 AVDD

A/Dコンバータのアナログ電源端子です。A/Dコンバータを使用しないときでも,常にVpp端子と同電位で使用してください。

## 3. 2. 10 AVss

A/Dコンバータのグランド電位端子です。A/Dコンバータを使用しないときでも,常にVss端子と同電位で使用してください。

#### 3. 2. 11 VDD

正電源供給端子です。

#### 3, 2, 12 Vss

グランド電位端子です。

## 3. 2. 13 VPP ( µ PD78F9116, 78F9136**のみ** )

フラッシュ・メモリ・プログラミング・モード設定およびプログラム書き込み / ベリファイ時の高電圧印加端子です。

通常動作モード時はVssに直接接続してください。

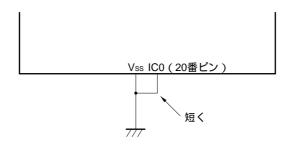

## 3. 2. 14 20番ピンのIC0 (マスクROM製品のみ)

20番ピンのIC0 (Internally Connected) 端子 (1.4 **端子接続図 (**Top View**)**, 2.4 **端子接続図 (**Top View**)** 参照)は,当社出荷時に $\mu$  PD789134を検査するためのテスト・モードに設定するための端子です。通常動作時には,IC0端子をVss端子に直接接続し,その配線長を極力短くしてください。

ICO端子とVss端子間の配線の引き回しが長い場合や、ICO端子に外来ノイズが加わった場合などで、ICO端子とVss端子間に電位差が生じたときには、お客様のプログラムが正常に動作しないことがあります。

#### IC0端子をVss端子に直接接続してください。

## ★ 3. 2. 15 10番ピンと21番ピンのIC0

10番ピンと21番ピンのICO(1.4 **端子接続図(**Top View**),**2.4 **端子接続図(**Top View**)**参照)は内部接続されています。

IC0端子はVssに直接接続してください。

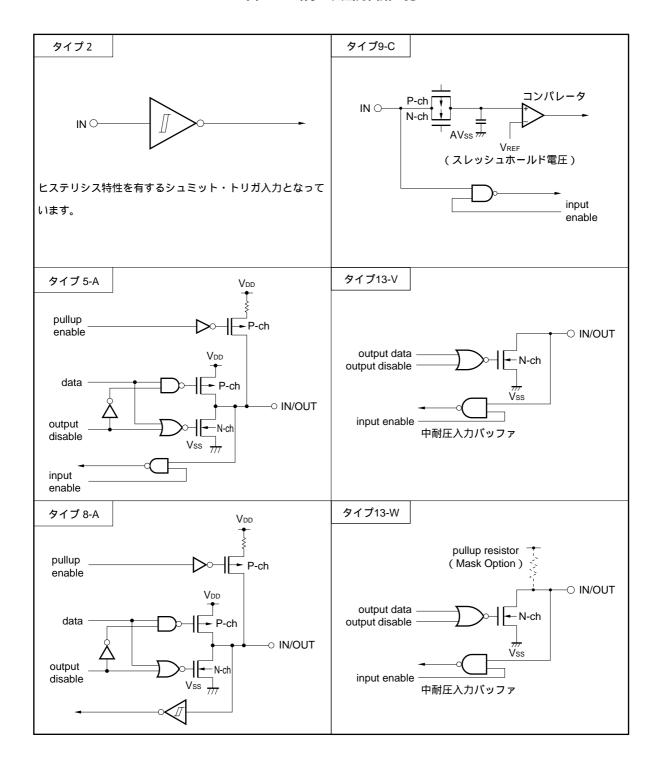

# 3.3 端子の入出力回路と未使用端子の処理

各端子の入出力回路タイプと,未使用端子の処理を表3-1に示します。 また,各タイプの入出力回路の構成は,図3-1を参照してください。

#### 表3 - 1 各端子の入出力回路タイプと未使用端子の処理

| 端子名                      | 入出力回路タイプ | 入出力 | 未使用時の推奨接続方法                  |

|--------------------------|----------|-----|------------------------------|

| P00-P03                  | 5-A      | 入出力 | 入力時:個別に抵抗を介して,VpoまたはVssに接続して |

| P10, P11                 |          |     | ください。                        |

| P20/SCK20/ASCK20         | 8-A      |     | 出力時:オープンにしてください。             |

| P21/SO20/TxD20           |          |     |                              |

| P22/SI20/RxD20           |          |     |                              |

| P23/INTP0/CPT20/SS20     |          |     |                              |

| P24/INTP1/TO80/TO20      |          |     |                              |

| P25/INTP2/TI80           |          |     |                              |

| P50-P53 (マスクROM製品)       | 13-W     |     | 入力時:個別に抵抗を介して,V∞に接続してください。   |

| P50-P53                  | 13-V     |     | 出力時:オープンにしてください。             |

| ( μ PD78F9116, 78F9136 ) |          |     |                              |

| P60/ANI0-P63/ANI3        | 9-C      | 入力  | VppまたはVssに直接接続してください。        |

| AVDD                     | -        | -   | Vddに接続してください。                |

| AVss                     |          |     | Vssに接続してください。                |

| RESET                    | 2        | 入力  | -                            |

| IC0                      | -        | -   | Vssに直接接続してください。              |

#### 図3-1 端子の入出力回路一覧

[メ モ]

# 第4章 CPUアーキテクチャ

# 4.1 メモリ空間

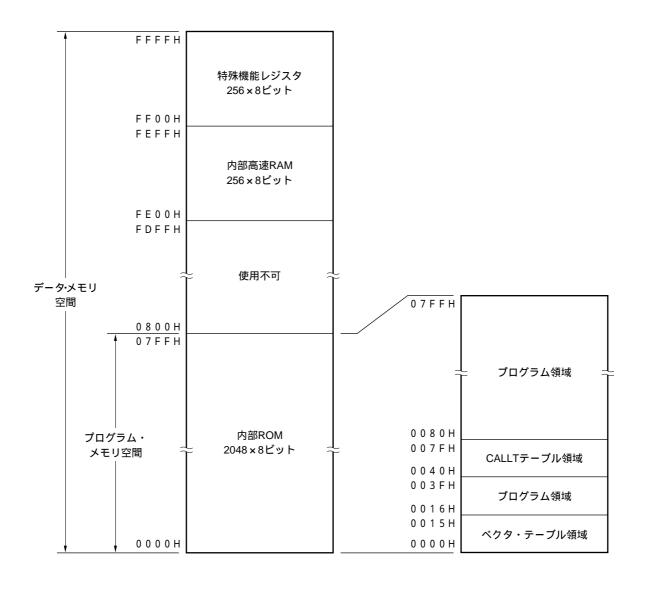

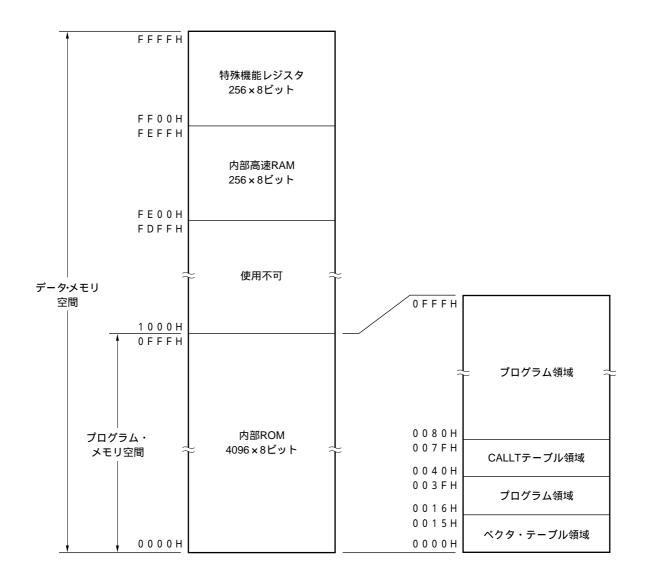

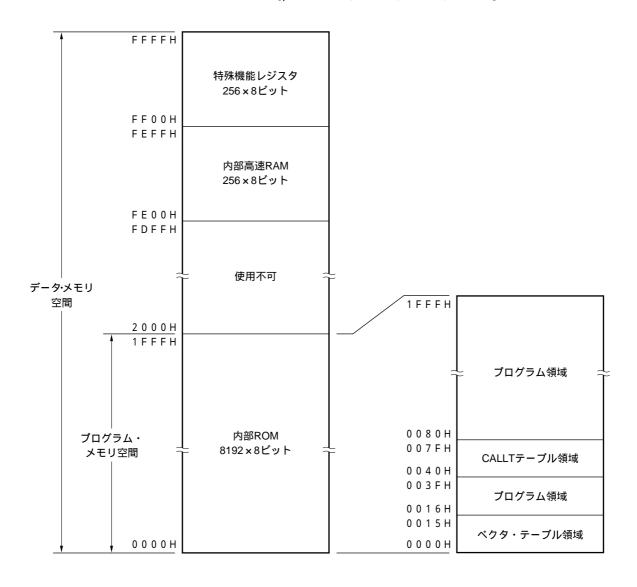

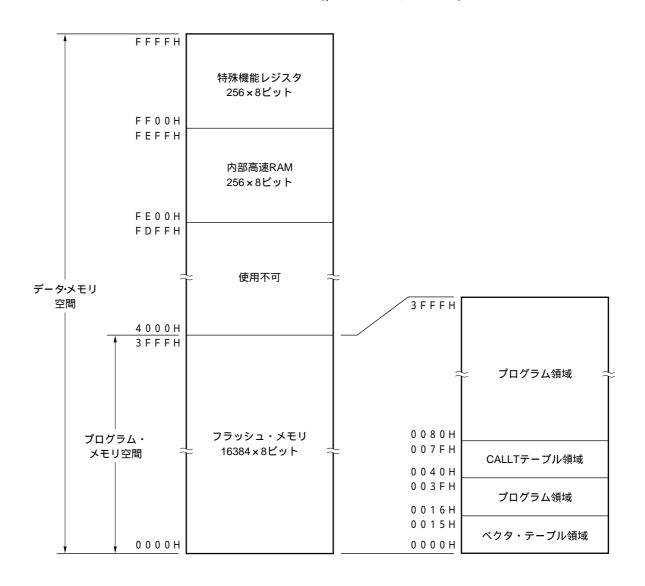

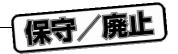

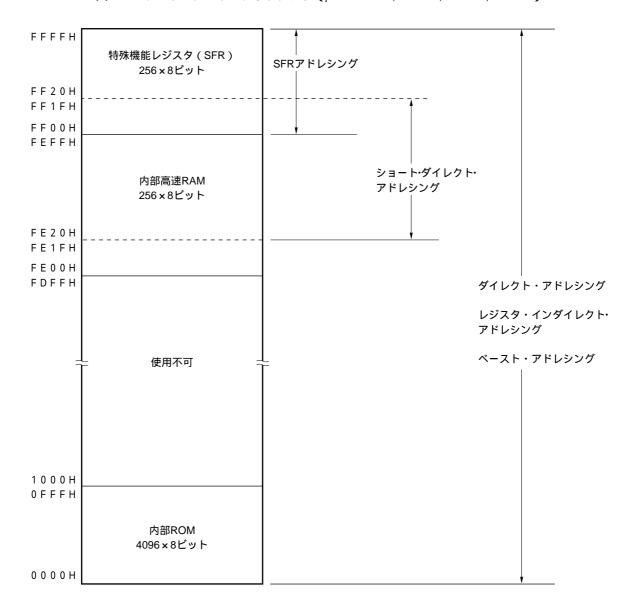

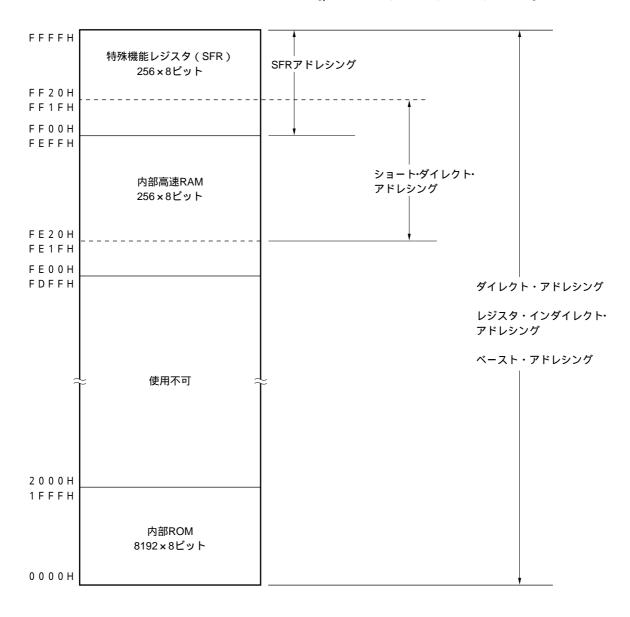

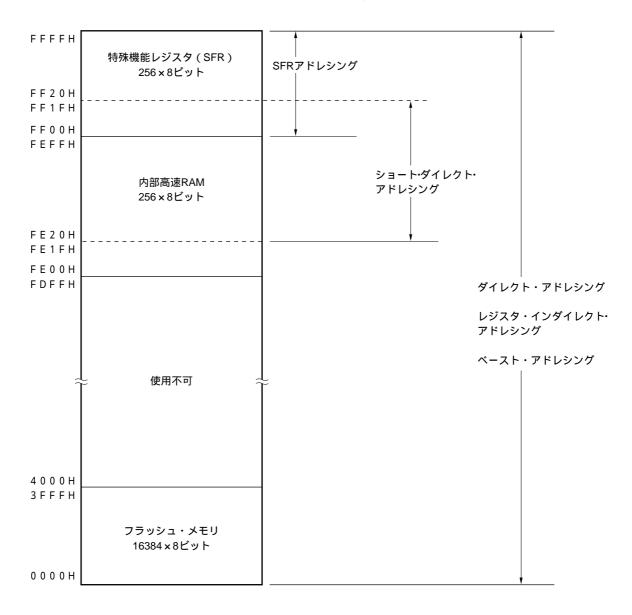

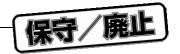

$\mu$  PD789134サブシリーズは,64 Kバイトのメモリ空間をアクセスできます。図4 - 1から図4 - 4に,メモリ・マップを示します。

**図**4 - 1 メモリ・マップ (  $\mu$  PD789101, 789111, 789121, 789131 )

#### **図**4 - 2 メモリ・マップ (µ PD789102, 789112, 789122, 789132)

### 図4 - 3 メモリ・マップ (µ PD789104, 789114, 789124, 789134)

# 図4 - 4 メモリ・マップ (μ PD78F9116, 78F9136)

# 4.1.1 内部プログラム・メモリ空間

内部プログラム・メモリ空間には,プログラムおよびテーブル・データなどを格納します。通常,プログラム・カウンタ(PC)でアドレスします。

$\mu$  PD789134サブシリーズでは , 各製品ごとに次の容量の内部ROM (またはフラッシュ・メモリ ) を内蔵しています。

品 名 内部ROM 構造 容量

μ PD789101, 789111, 789121, 789131 マスクROM 2048 × 8ビット

μ PD789102, 789112, 789132 4096 × 8ビット

μ PD789104, 789114, 789124, 789134 8192 × 8ビット

μ PD78F9116, 78F9136 フラッシュ・メモリ 16384 × 8ビット

表4 - 1 内部ROM容量

内部プログラム・メモリ空間には,次に示す領域を割り付けています。

#### (1)ベクタ・テーブル領域

0000H-0015Hの22バイトの領域はベクタ・テーブル領域として予約されています。ベクタ・テーブル領域には,RESET入力,各割り込み要求発生により分岐するときのプログラム・スタート・アドレスを格納しておきます。16ビット・アドレスのうち下位8ビットが偶数アドレスに,上位8ビットが奇数アドレスに格納されます。

| ベクタ・テーブル・アドレス | 割り込み要求  | ベクタ・テーブル・アドレス | 割り込み要求           |

|---------------|---------|---------------|------------------|

| 0000H         | RESET入力 | 000CH         | INTSR20/INTCSI20 |

| 0 0 0 4 H     | INTWDT  | 000EH         | INTST20          |

| 0006H         | INTP0   | 0010H         | INTTM80          |

| 0008H         | INTP1   | 0 0 1 2 H     | INTTM20          |

| 0 0 0 A H     | INTP2   | 0 0 1 4 H     | INTAD0           |

表4-2 ベクタ・テーブル

#### (2) CALLT命令テーブル領域

0040H-007FHの64バイトの領域には,1バイト・コール命令(CALLT)のサブルーチン・エントリ・アドレスを格納することができます。

# 4. 1. 2 内部データ・メモリ (内部高速RAM)空間

$\mu$  PD789134サブシリーズの製品は , 256バイトの内部高速RAMを内蔵しています。 内部高速RAMはスタックとしても使用します。

# 4.1.3 特殊機能レジスタ (SFR: Special Function Register) 領域

FF00H-FFFFHの領域には,オン・チップ周辺ハードウエアの特殊機能レジスタ(SFR)が割り付けられています(表4-3参照)。

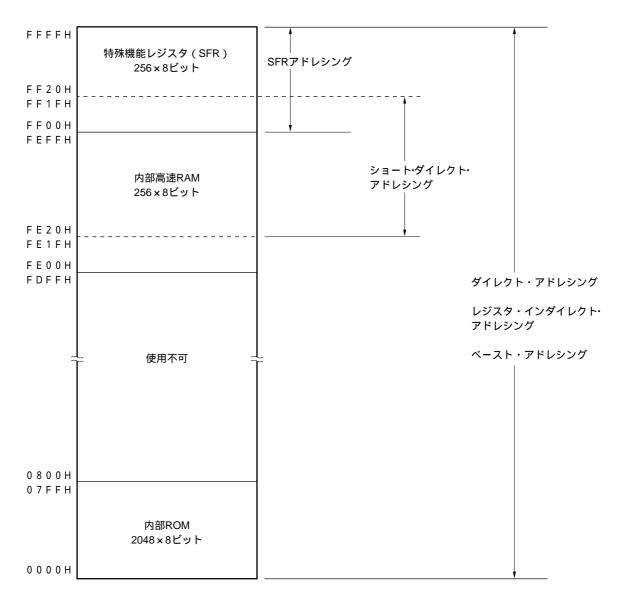

## 4.1.4 データ・メモリ・アドレシング

$\mu$  PD789134サブシリーズは,メモリの操作性などを考慮した豊富なアドレシング・モードを備えています。特にデータ・メモリを内蔵している領域 (FE00H-FEFFH) では,特殊機能レジスタ (SFR) など,それぞれの持つ機能にあわせて特有のアドレシングが可能です。図4 - 5から図4 - 8にデータ・メモリのアドレシングを示します。

図4 - 5 データ・メモリのアドレシング (µPD789101, 789111, 789121, 789131)

## 図4 - 6 データ・メモリのアドレシング (µPD789102, 789112, 789122, 789132)

# 図4 - 7 データ・メモリのアドレシング (µPD789104, 789114, 789124, 789134)

## 図4 - 8 データ・メモリのアドレシング (µPD78F9116, 78F9136)

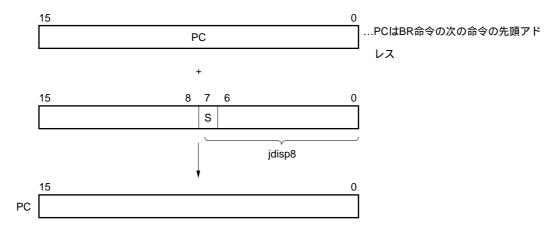

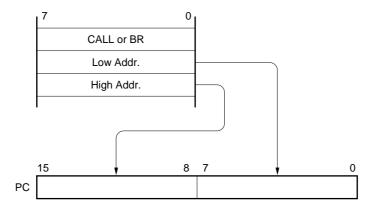

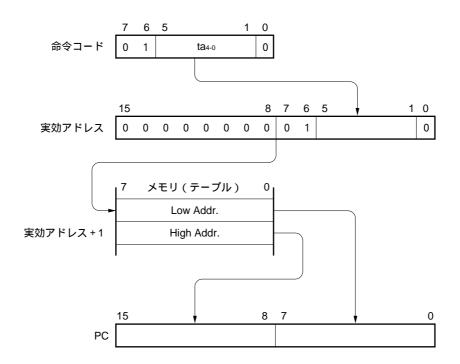

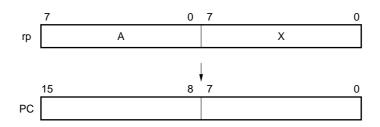

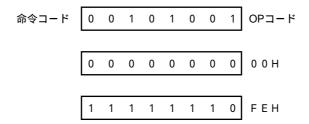

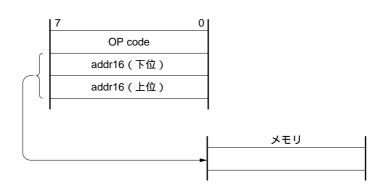

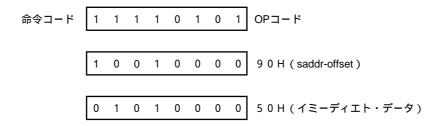

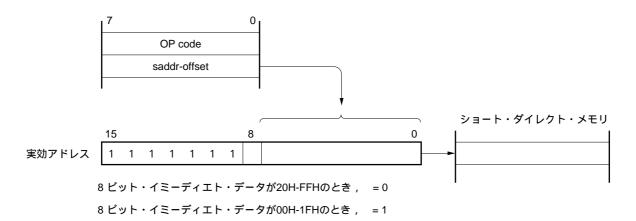

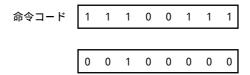

# 4.2 プロセッサ・レジスタ