### カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# ユーザーズ・マニュアル

# μPD78014H サブシリーズ

8 ビット・シングルチップ・マイクロコンピュータ

μPD78011H

μPD78011H(A)

μPD78012H

μPD78012H(A)

μPD78013H

μPD78013H(A)

μPD78014H(A)

μPD78P018F

μPD78P018F(A)

資料番号 U12220JJ2V0UM00 (第 2 版 ) 発行年月 November 1997 N

# 目次要約

| <b>弗</b>  草          | 大                               |

|----------------------|---------------------------------|

| 第2章                  | <b>端子機能</b> 45                  |

| 第3章                  | CPU <b>アーキテクチャ</b> 59           |

| 第4章                  | <b>ポート機能</b> 91                 |

| 第5章                  | <b>クロック発生回路</b> 113             |

| 第6章                  | 16 <b>ピット・タイマ/イベント・カウンタ</b> 129 |

| 第7章                  | 8 ビット・タイマ / イベント・カウンタ 157       |

| 第8章                  | <b>時計用タイマ</b> 179               |

| 第9章                  | <b>ウォッチドッグ・タイマ</b> 187          |

| 第10章                 | <b>クロック出力制御回路</b> 195           |

| 第11章                 | <b>ブザー出力制御回路</b> 199            |

| 第12章                 | A/D <b>コンバータ</b> 203            |

| <b>第</b> 13 <b>章</b> | <b>シリアル・インタフェース・チャネル0</b> 219   |

| 第14章                 | シリアル・インタフェース・チャネル1 273          |

| <b>第</b> 15 <b>章</b> | <b>割り込み機能とテスト機能</b> 319         |

| 第16章                 | <b>外部デバイス拡張機能</b> 345           |

| 第17章                 | スタンバイ機能 357                     |

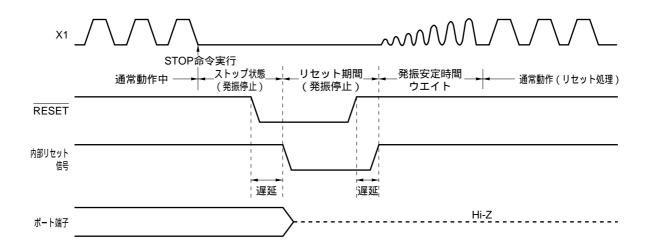

| 第18章                 | リセット機能 367                      |

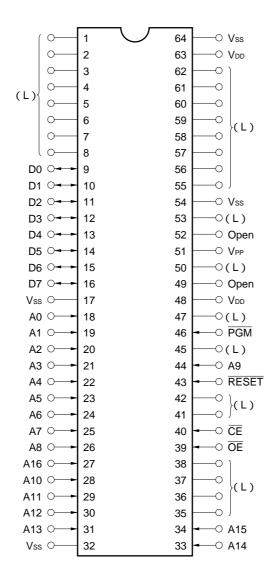

| 第19章                 | μPD78P018F <b>の概要</b> 371       |

| 第20章                 | <b>命令セットの概要</b> 399             |

| 付 釤                  | <b>.</b> 415                    |

#### - CMOS**デバイスの一般的注意事**項

#### 静電気対策 (MOS全般)

#### 注意 MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、NECが出荷梱包に使用している導電性のトレーやマガジン・ケース,または導電性の緩衝材,金属ケースなどを利用し,組み立て工程にはアースを施してください。プラスチック板上に放置したり,端子を触ったりしないでください。

また,MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 未使用入力の処理 (CMOS特有)

#### 注意 CMOSデバイスの入力レベルは固定してください。

バイポーラやNMOSのデバイスと異なり、CMOSデバイスの入力に何も接続しない状態で動作させると、ノイズなどに起因する中間レベル入力が生じ、内部で貫通電流が流れて誤動作を引き起こす恐れがあります。プルアップかプルダウンによって入力レベルを固定してください。また、未使用端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVooまたはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については,その内容を守ってください。

#### 初期化以前の状態 (MOS全般)

#### 注意 電源投入時, MOSデバイスの初期状態は不定です。

分子レベルのイオン注入量等で特性が決定するため,初期状態は製造工程の管理外です。電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は,まずリセット動作を実行してください。

#### FIPは,日本電気株式会社の登録商標です。

IEBus , QTOPは日本電気株式会社の商標です。

MS-DOS, WindowsおよびWindowsNTは,米国Microsoft Corporationの米国およびその他の国における登録商標または商標です。

IBM DOS, PC/AT, PC DOSは, 米国IBM社の商標です。

HP9000シリーズ700, HP-UXは,米国ヒューレット・パッカード社の商標です。

SPARCstationは,米国SPARC International, Inc.の商標です。

SunOSは,米国サン・マイクロシステムズ社の商標です。

イーサネットは,米国ゼロックス社の商標です。

NEWS, NEWS-OSは, ソニー株式会社の商標です。

OSF/Motifは, Open Software Foundation, Inc.の商標です。

TRONは, The Realtime Operating system Nucleusの略称です。

ITRONは, Industrial TRONの略称です。

本製品のうち,外国為替および外国貿易管理法の規定により戦略物資等(または役務)に該当するものについては,日本国外に輸出する際に,同法に基づき日本国政府の輸出許可が必要です。

非 該 当 品 : μPD78P018FDW, 78P018FKK-S

ユーザ判定品 : μ PD78011HCW-×××, 78011HGC-×××-AB8, 78011HGK-×××-8A8,

μPD78011HCW(A) × × × , 78011HGQ(A) × × ×-AB8 , 78011HGK(A) × × ×-8A8

μ PD78012HCW- x x x , 78012HGC- x x x - AB8 , 78012HGK- x x x - 8A8 ,

μ PD78012HCW( A ) × × × , 78012HGQ( A ) × × ×-AB8 , 78012HGK( A ) × × ×-8A8

$\mu$  PD78013HCW-  $\times$   $\times$   $\times$  , 78013HGC-  $\times$   $\times$   $\times$  -AB8 , 78013HGK-  $\times$   $\times$   $\times$  -8A8 ,

μ PD78013HCW( A ) × × × , 78013HGQ( A ) × × × -AB8 , 78013HGK( A ) × × × -8A8

μ PD78014HCW- x x x , 78014HGC- x x x - AB8 , 78014HGK- x x x - 8A8 ,

$\mu$  PD78014HCW( A )  $\times$   $\times$   $\times$  , 78014HGC( A )  $\times$   $\times$  -AB8 , 78014HGK( A )  $\times$   $\times$  -8A8

μ PD78P018FCW , 78P018FGC-AB8 , 78P018FGK-8A8

μ PD78P018FCW( A ) , 78P018FGC( A ) AB8

本資料に掲載の応用回路および回路定数は、例示的に示したものであり、量産設計を対象とするものではありません。

#### 本資料の内容は、後日変更する場合があります。

文書による当社の承諾なしに本資料の転載複製を禁じます。

本資料に記載された製品の使用もしくは本資料に記載の情報の使用に際して,当社は当社もしくは第三者の知的所有権その他の権利に対する保証または実施権の許諾を行うものではありません。上記使用に起因する第三者所有の権利にかかわる問題が発生した場合,当社はその責を負うものではありませんのでご了承ください。

当社は品質,信頼性の向上に努めていますが,半導体製品はある確率で故障が発生します。当社半導体製品の故障により結果として,人身事故,火災事故,社会的な損害等を生じさせない冗長設計,延焼対策設計,誤動作防止設計等安全設計に十分ご注意願います。

当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定して頂く「特定水準」に分類しております。また,各品質水準は以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認の上ご使用願います。

標準水準:コンピュータ,OA機器,通信機器,計測機器,AV機器,家電,工作機械,パーソナル機器,産業用ロボット

特別水準:輸送機器(自動車,列車,船舶等),交通用信号機器,防災/防犯装置,各種安全装置, 生命維持を直接の目的としない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート / データ・ブック等の資料で,特に品質水準の表示がない場合は標準水準製品であることを表します。当社製品を上記の「標準水準」の用途以外でご使用をお考えのお客様は,必ず事前に当社販売窓口までご相談頂きますようお願い致します。

この製品は耐放射線設計をしておりません。

M7 94.11

### 本版で改訂された主な箇所

| 箇 所        | 内容                                                                    |

|------------|-----------------------------------------------------------------------|

|            | 次のポートのブロック図を変更                                                        |

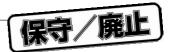

| p.98       | ・図4 - 6 P20, P21, P23-P26のプロック図                                       |

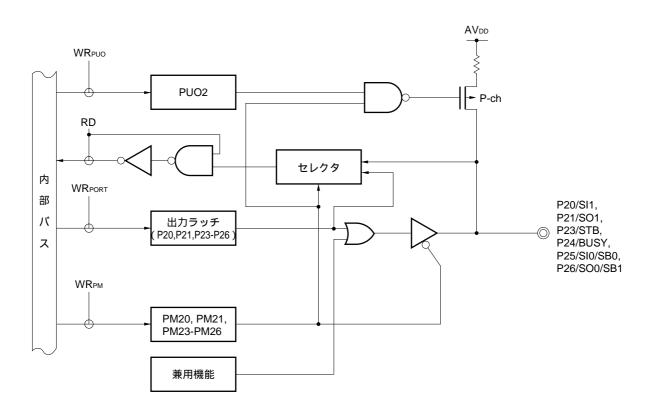

| p.99       | ・図4 - 7 P22, P27のプロック図                                                |

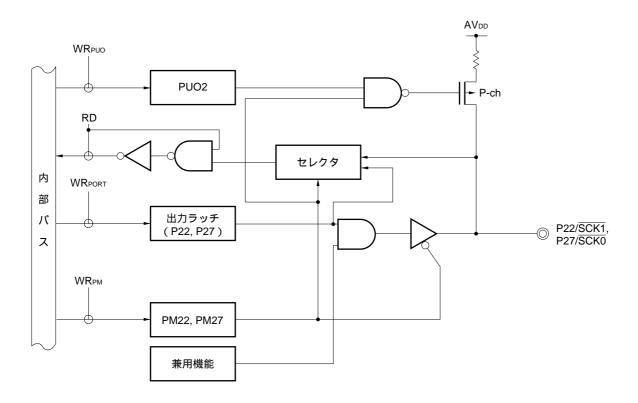

| p.100      | ・ <b>図4-8</b> P30-P37 <b>のプロック図</b>                                   |

| p.117      | 表 5 - 2 CPU <b>クロックと最小命令実行時間の関係</b> を追加                               |

| p.171, 175 | <b>図7</b> -10, <b>図7</b> -13 <b>方形波出力動作のタイミング</b> を追加                 |

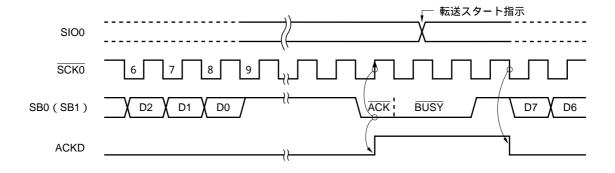

| p.228, 247 | SBIモード時にシリアル・インタフェース・チャネル 0 の動作を停止                                    |

|            | させるときの注意を追加                                                           |

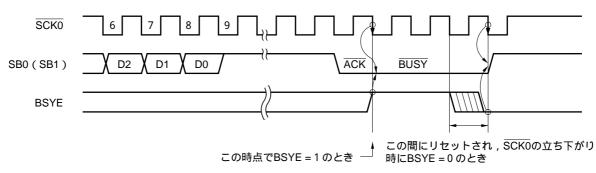

| p.230, 250 | シリアル・インタフェース・チャネル0のビジィ・モードを解除する                                       |

|            | (レディ信号を出力する)条件を変更                                                     |

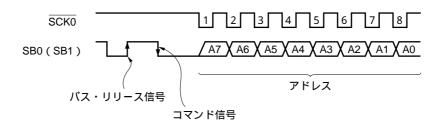

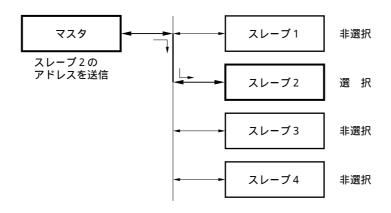

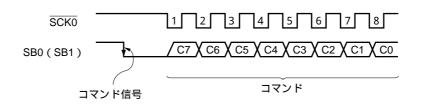

| p.241, 242 | 13. <b>4</b> . <b>3( 2 ) a )パス・リリース信号(</b> REL <b>) , ( b )コマンド信号</b> |

|            | (CMD)に配線の引き回しについての注意を追加                                               |

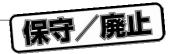

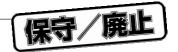

| p.417-432  | 付録B 開発ツール                                                             |

|            | 全面改訂:インサーキット・エミュレータIE-78K0-NS, IE-78001-R-A                           |

|            | に対応                                                                   |

| p.433, 434 | 付録 C 組み込み用ソフトウエア                                                      |

|            | 全面改訂:ファジィ推論開発支援システムを削除                                                |

| p.441      | <b>付録E 改版履歴</b> を追加                                                   |

本文欄外の 印は,本版で改訂された主な箇所を示しています。

巻末にアンケート・コーナを設けております。このドキュメントに対するご意見を お気軽にお寄せください。

[メ モ]

### はじめに

対象者 このマニュアルは,µPD78014Hサブシリーズの機能を理解し,その応用システムや応用プログラムを設計,開発するユーザのエンジニアを対象としています。 対象製品は,次に示すサブシリーズの各製品です。

・μ PD78014Hサブシリーズ : μ PD78011H, 78012H, 78013H, 78014H μ PD78011H( A ), 78012H( A ), 78013H( A ), 78014H( A )

- **旬** の このマニュアルは,次の構成に示す機能をユーザに理解していただくことを目的としています。

- 構 成 μ PD78014Hサブシリーズのマニュアルは,このマニュアルと命令編(78K/0シリーズ共通)の2 冊に分かれています。

μ PD78014Hサブシリーズ ユーザーズ・マニュアル (このマニュアル)

端子機能

内部ブロック機能

割り込み

その他の内蔵周辺機能 u PD78P018F<sup>注</sup>の概要 78K/0シリーズ ユーザーズ・マニュアル 命令編

CPU機能

命令セット

命令の説明

- 注 μPD78011H, 78012H, 78013H, 78014HのPROM内蔵品として,μPD78P018Fを,μPD78011H(A), 78012H(A), 78013H(A), 78014H(A)のPROM内蔵品として,μPD78P018F(A)を使用します。

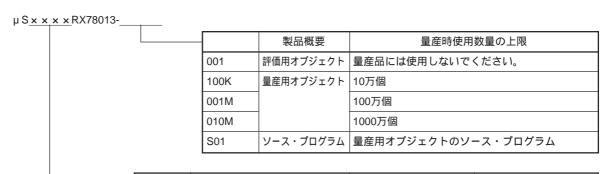

- 注意  $\mu$  PD78P018Fのうち ,  $\mu$  PD78P018FDW , 78P018FKK-Sは , お客様の装置の量産製品 に使用されることを意図した信頼性を保持しておりません。実験または機能評価用にのみ ご使用ください。

読み方 このマニュアルを読むにあたっては、電気、論理回路、マイクロコンピュータの一般知識を必要とします。

μ PD78011H( A ), 78012H( A ), 78013H( A ), 78014H( A ), 78P018F( A )のマニュアルと してお使いになる方へ

μ PD78011H, 78012H, 78013H, 78014H, 78P018Fとμ PD78011H(A), 78012H(A), 78013H(A), 78014H(A), 78P018F(A)は 品質水準のみが異なります。(A)品については 品名を次のように読み替えてください。

μ PD78011H μ PD78011H( A ) μ PD78012H μ PD78012H( A ) μ PD78013H μ PD78013H( A ) μ PD78014H μ PD78014H( A ) μ PD78P018F μ PD78P018F( A )

μPD78P018Fのマニュアルとしてお使いになる方へ

**1**.12  $\mu$ PD78014H**サブシリーズと** $\mu$ PD78P018F**との違い**で  $\mu$ PD78014Hサブシリーズとの機能の違いを確認してください。また,第19章  $\mu$ PD78P018F**の概要**に, $\mu$ PD78P018Fのみ有効な機能についてまとめてありますのでお読みください。なお,このマニュアルでは, $\mu$ PD78P018Fのみ有効な機能については, $\mu$ PD78014Hサブシリーズでは使用できないため,詳細には記述してありません。

一通りの機能を理解しようとするとき

目次に従って読んでください。

レジスタ・フォーマットの見方

ビット番号を で囲んでいるものは、そのビット名称がRA78K/0では予約語に、CC78K/0ではsfrbit.hというヘッダ・ファイルで定義済みとなっているものです。

レジスタ名が分かっていて、レジスタの詳細を確認するとき

付録 D レジスタ索引を利用してください。

μPD78014Hサブシリーズの命令機能の詳細を知りたいとき

別冊の78K/0**シリーズ ユーザーズ・マニュアル 命令編 (**U12326J**)** を参照してください。

μ PD78014Hサブシリーズの電気的特性を知りたいとき

別冊のデータ・シートを参照してください。

μPD78014Hサブシリーズの各種機能の応用例を知りたいとき

別冊のアプリケーション・ノートを参照してください。

注意 このマニュアル中の使用例は,一般電子機器用の『標準』品質水準用に作成してあります。 『標準』品質水準を要求する用途にこのマニュアル中の使用例を使用する場合は,実際に 使用する各部品および回路について,その品質水準についてご検討のうえご使用ください。

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記: ×××(端子, 信号名称に上線)

注:本文中に付けた注の説明

注意: 気を付けて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数…××××または××××B

10進数...×××× 16進数...××××H

#### 関連資料

関連資料は暫定版の場合がありますが,この資料では「暫定」の表示をしておりません。あらかじめご了承ください。

#### デバイスの関連資料

|   |                                                       |         | 番 号     |

|---|-------------------------------------------------------|---------|---------|

|   |                                                       | 和文      | 英文      |

|   | μPD78011H, 78012H, 78013H, 78014H データ・シート             | U11898J | U11898E |

| * | μPD78011H(Α), 78012H(Α), 78013H(Α), 78014H(Α) データ・シート | U12174J | U12174E |

|   | μPD78P018F データ・シート                                    | U10955J | U10955E |

|   | μPD78P018F(A) データ・シート                                 | U12132J | U12132E |

|   | μPD78014Hサブシリーズ ユーザーズ・マニュアル                           | このマニュアル | U12220E |

|   | 78K/0シリーズ ユーザーズ・マニュアル 命令編                             | U12326J | U12326E |

|   | 78K/0シリーズ インストラクション活用表                                | U10903J | -       |

|   | 78K/0シリーズ インストラクション・セット                               | U10904J | -       |

| * | 78K/0シリーズ アプリケーション・ノート 基礎編( )                         | U12704J | U12704E |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには必ず最新の資料をご使用ください。

#### 開発ツールの関連資料 (ユーザーズ・マニュアル)

| 資料名                            | ,                     | 資料       | 番号       |

|--------------------------------|-----------------------|----------|----------|

|                                |                       | 和文       | 英文       |

| RA78K0 アセンブラ・パッケージ             | 操作編                   | U11802J  | U11802E  |

|                                | アセンブリ言語編              | U11801J  | U11801E  |

|                                | 構造化アセンブリ言語編           | U11789J  | U11789E  |

| RA78Kシリーズ 構造化アセンブラ・プリプロ        | lセッサ                  | U12323J  | EEU-1402 |

| CC78K0 Cコンパイラ                  | 操作編                   | U11517J  | U11517E  |

|                                | 言語編                   | U11518J  | U11518E  |

| CC78K/0 Cコンパイラ アプリケーション・ノート    | プログラミング・ノウハウ編         | U13034J  | EEA-1208 |

| CC78Kシリーズ ライブラリ・ソース・ファイ        | , JV                  | U12322J  | -        |

| PG-1500 PROMプログラマ              |                       | U11940J  | U11940E  |

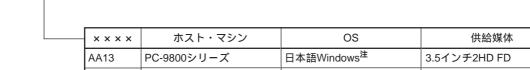

| PG-1500コントローラ PC-9800シリーズ(M    | S-DOS™)ベース            | EEU-704  | EEU-1291 |

| PG-1500コントローラ IBM PCシリーズ(PC    | DOS™)ベース              | EEU-5008 | U10540E  |

| IE-78K0-NS                     |                       | 作成予定     | 作成予定     |

| IE-78001-R-A                   |                       | 作成予定     | 作成予定     |

| IE-78018-NS-EM1                |                       | 作成予定     | 作成予定     |

| IE-78K0-R-EX1                  |                       | 作成予定     | 作成予定     |

| IE-78014-R-EM-A                |                       | EEU-962  | U10418E  |

| EP-78240                       |                       | EEU-986  | U10332E  |

| EP-78012GK-R                   |                       | EEU-5012 | EEU-1538 |

| SM78K0 システム・シミュレータ Windows™ベース | レファレンス編               | U10181J  | U10181E  |

| SM78Kシリーズ システム・シミュレータ          | 外部部品ユーザオープンインタフェース仕様編 | U10092J  | U10092E  |

| ID78K0 統合ディバッガ EWSベース          | レファレンス編               | U11151J  | -        |

| ID78K0 統合ディバッガ PCベース           | レファレンス編               | U11539J  | U11539E  |

| ID78K0 統合ディバッガ Windowsベース      | ガイド編                  | U11649J  | U11649E  |

| ID78K0-NS 統合ディバッガ PCベース        | レファレンス編               | U12900J  | 作成予定     |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには必ず最新の資料をご使用ください。

#### 組み込み用ソフトウエアの関連資料 (ユーザーズ・マニュアル)

| 資料名                 |         | 資料番号    |         |

|---------------------|---------|---------|---------|

|                     |         | 和文      | 英文      |

| 78K/0シリーズ リアルタイムOS  | 基礎編     | U11537J | U11537E |

|                     | インストール編 | U11536J | U11536E |

| 78K/0シリーズ用OS MX78K0 | 基礎編     | U12257J | U12257E |

#### その他の関連資料

|   | 資 料 名                    | 資料      | 番号      |

|---|--------------------------|---------|---------|

|   |                          | 和文      | 英文      |

|   | IC PACKAGE MANUAL        | C10943X |         |

|   | 半導体デバイス 実装マニュアル          | C10535J | C10535E |

|   | NEC半導体デバイスの品質水準          | C11531J | C11531E |

|   | NEC半導体デバイスの信頼性品質管理       | C10983J | C10983E |

| * | 静電気放電(ESD)破壊対策ガイド        | C11892J | C11892E |

| * | 半導体品質 / 信頼性ハンドブック        | C12769J | -       |

|   | マイクロコンピュータ関連製品ガイド 社外メーカ編 | U11416J | -       |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには必ず最新の資料をご使用ください。

[メ モ]

# 目 次

| 第 1        | 草            | <b>概 記</b> 31                                      |

|------------|--------------|----------------------------------------------------|

| ,          | 1.1          | 特 徵 31                                             |

| •          | 1.2          | <b>応用分野</b> 32                                     |

| •          | 1.3          | <b>オーダ情報</b> 33                                    |

| •          | 1 . 4        | <b>品質水準</b> 34                                     |

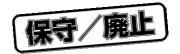

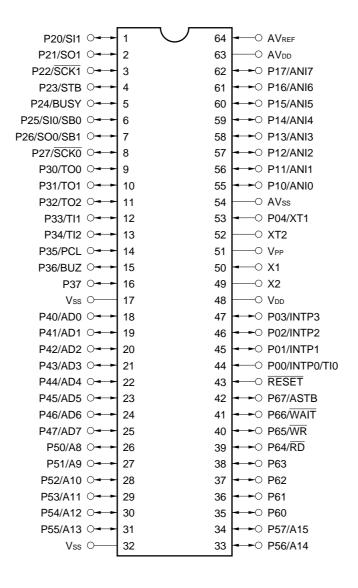

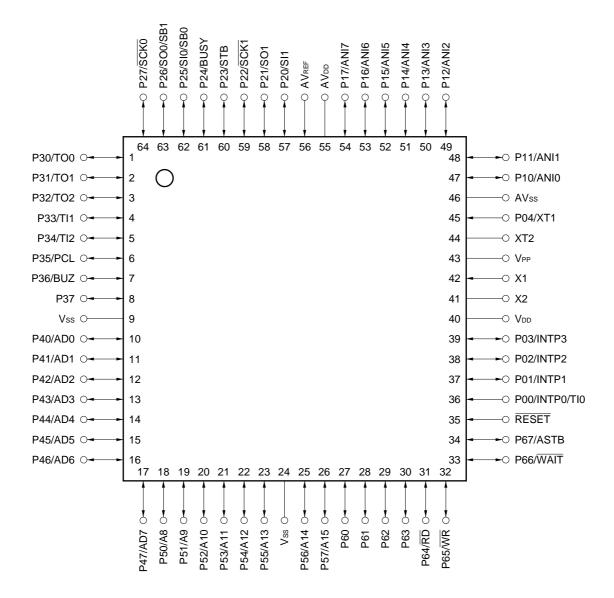

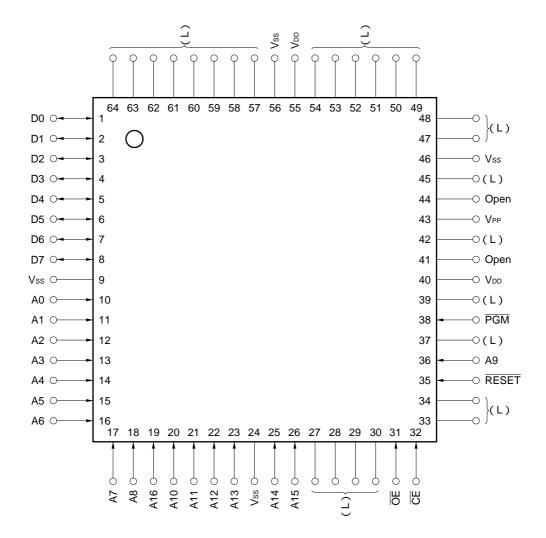

| •          | 1 . 5        | <b>端子接続図(</b> Top View <b>)</b> 35                 |

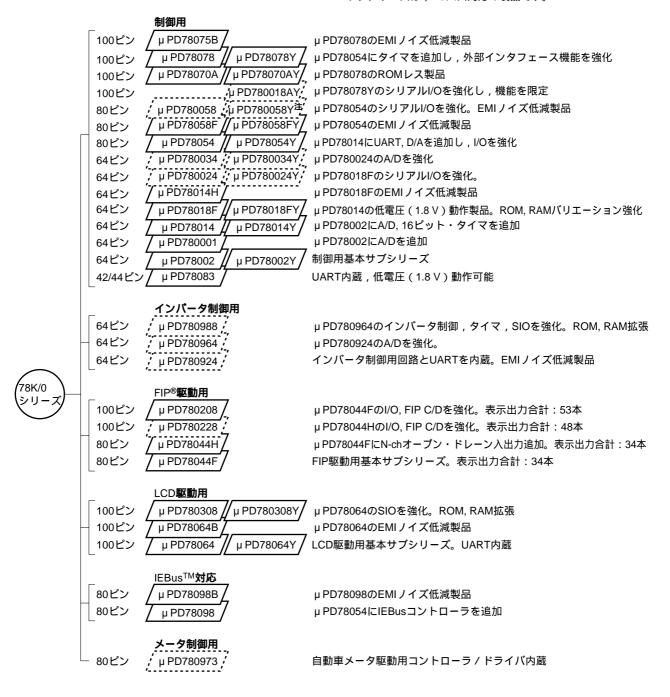

| •          | 1 . 6        | 78K/0 <b>シリーズの展開</b> 38                            |

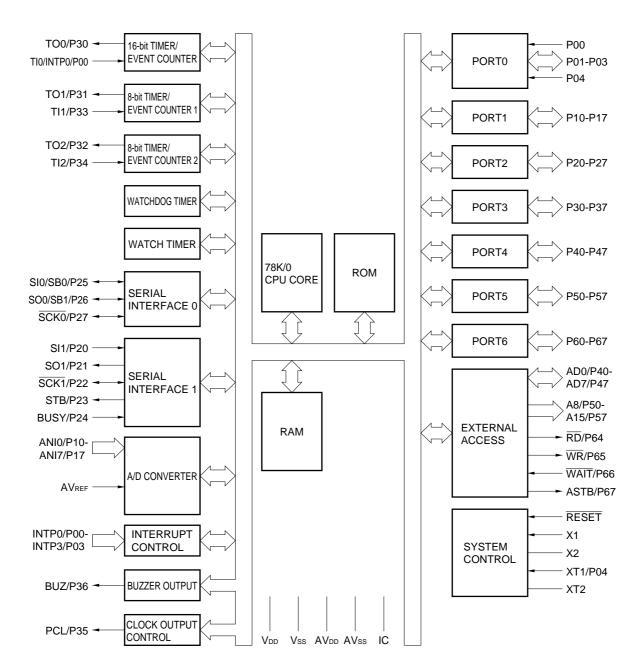

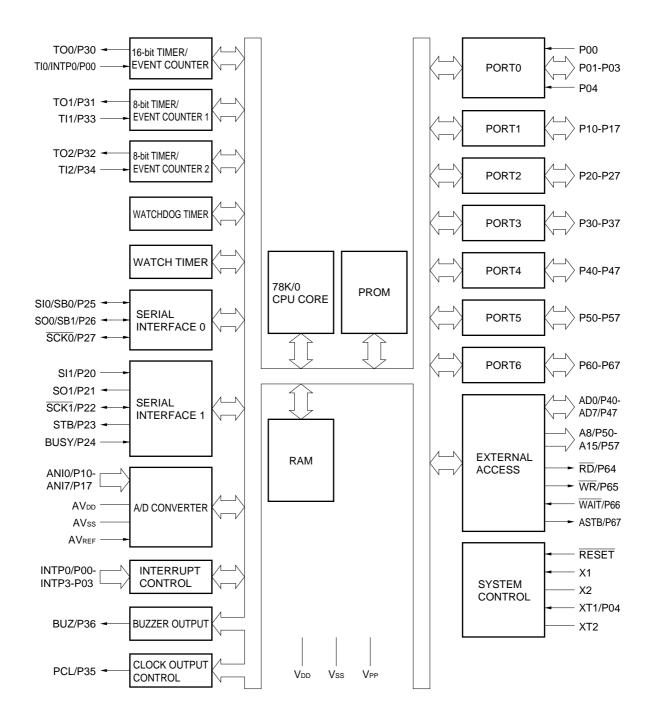

| •          | 1 . 7        | <b>プロック図</b> 40                                    |

| •          | 1 . 8        | <b>機能概要</b> 41                                     |

| •          | 1 . 9        | <b>標準品と特別品の違い</b> 42                               |

|            |              | マスク・オプションについて 42                                   |

|            |              | $\mu$ PD78018Fサブシリーズと $\mu$ PD78014Hサブシリーズとの違い 43  |

| •          | <b>1</b> .12 | μPD78014H <b>サブシリーズと</b> μPD78P018F <b>との違い</b> 43 |

| <b>44</b>  |              |                                                    |

| <b>弗</b> ∠ | 早            | <b>端子機能</b> 45                                     |

| ;          | 2.1          | <b>端子機能一覧</b> 45                                   |

|            |              | <b>端子機能の説明</b> … 49                                |

|            |              | 2.2.1 P00-P04 (Port0) 49                           |

|            |              | 2.2.2 P10-P17 (Port1) 49                           |

|            |              | 2.2.3 P20-P27 (Port2) 50                           |

|            |              | 2.2.4 P30-P37 (Port3) 51                           |

|            |              | 2.2.5 P40-P47 (Port4) 51                           |

|            |              | 2.2.6 P50-P57 (Port5) 52                           |

|            |              | 2.2.7 P60-P67 (Port6) 52                           |

|            |              | 2.2.8 AVREF 52                                     |

|            |              | 2.2.9 AVDD 53                                      |

|            |              | 2.2.10 AVss 53                                     |

|            |              | 2.2.11 RESET 53                                    |

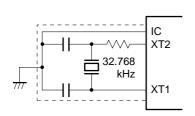

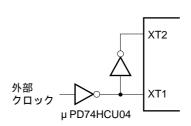

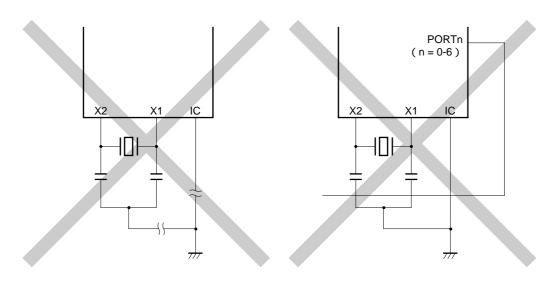

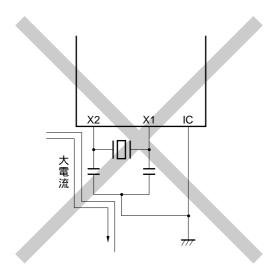

|            |              | 2.2.12 X1, X2 53                                   |

|            |              | 2.2.13 XT1, XT2 53                                 |

|            |              | 2.2.14 VDD 53                                      |

|            |              | 2.2.15 Vss 53                                      |

|            |              | 2.2.16 IC 53                                       |

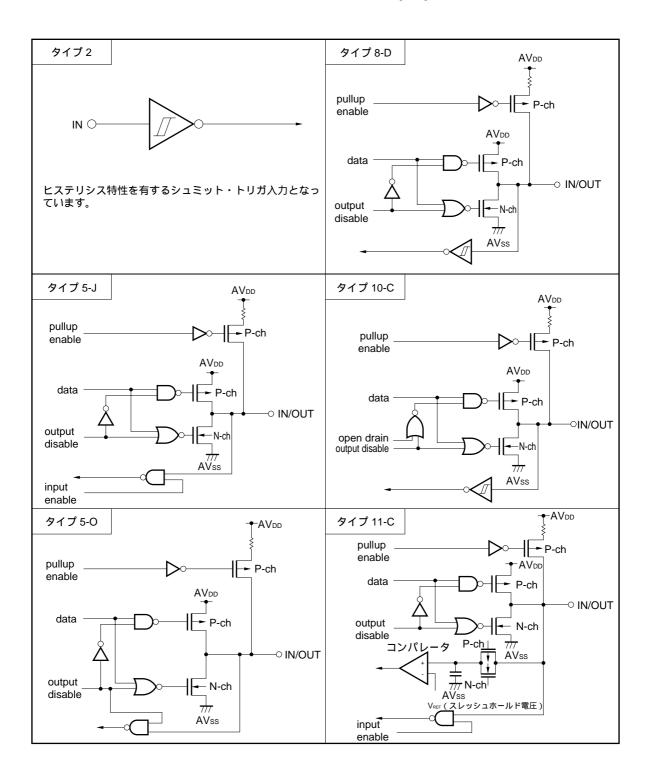

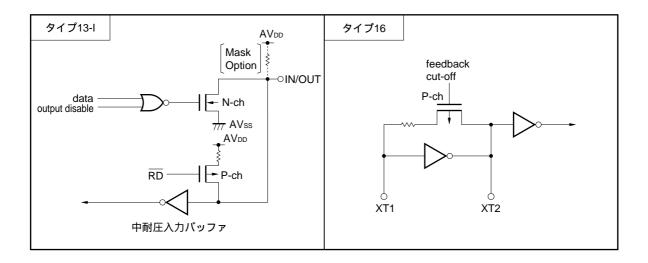

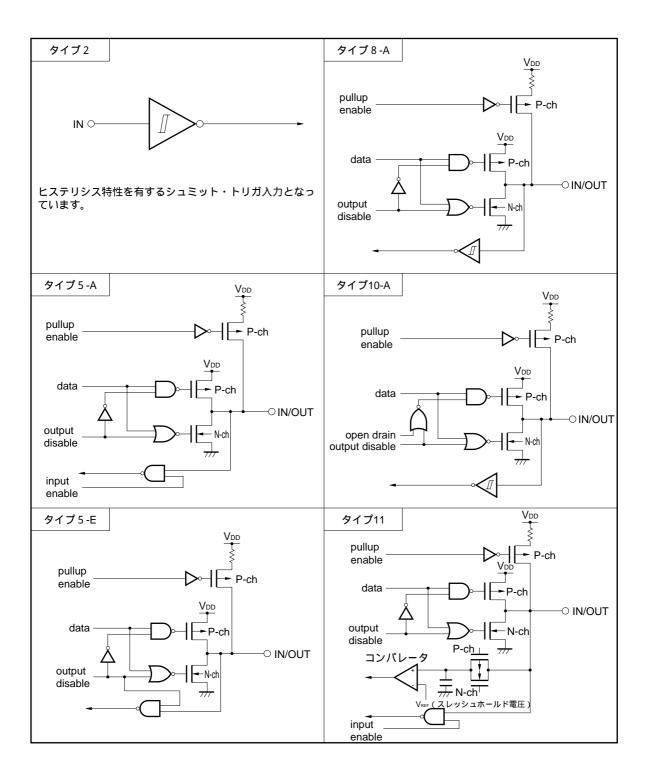

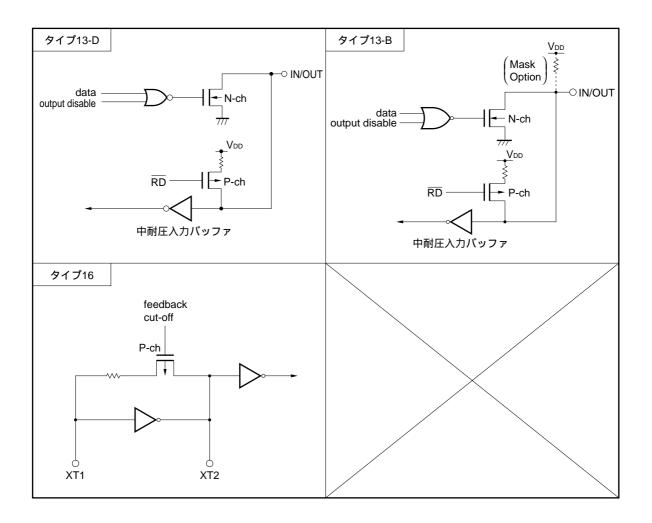

|            | 2.3          | <b>端子の入出力回路と未使用端子の処理</b> 54                        |

| 第3         | 章            | CPU <b>アーキテクチャ</b> 59                              |

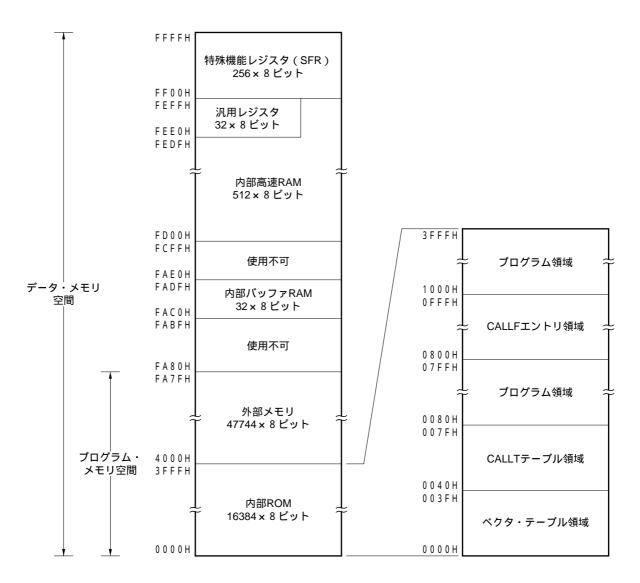

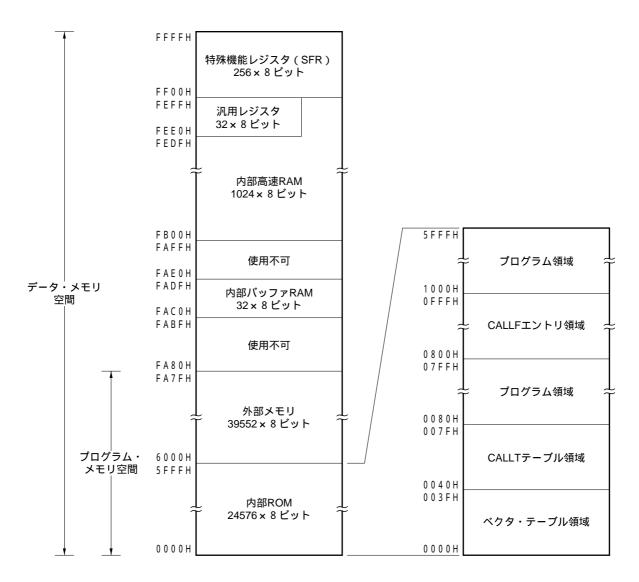

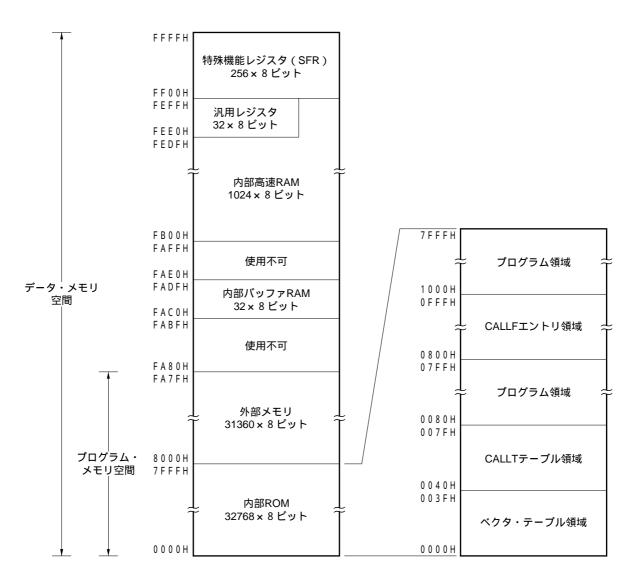

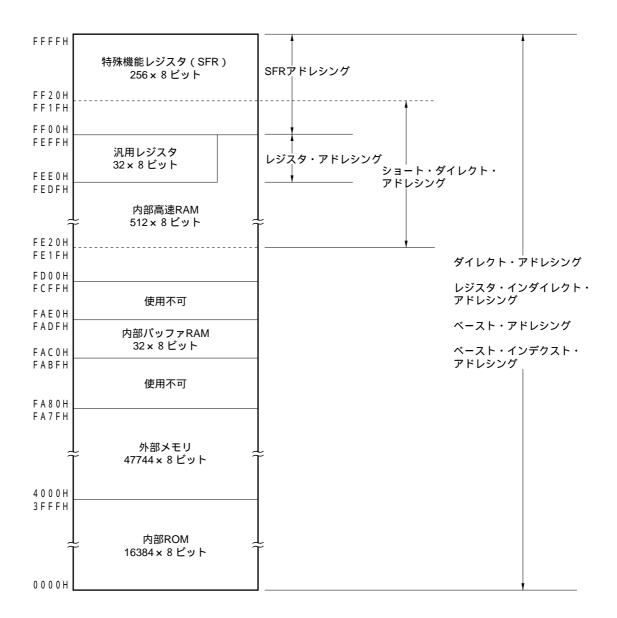

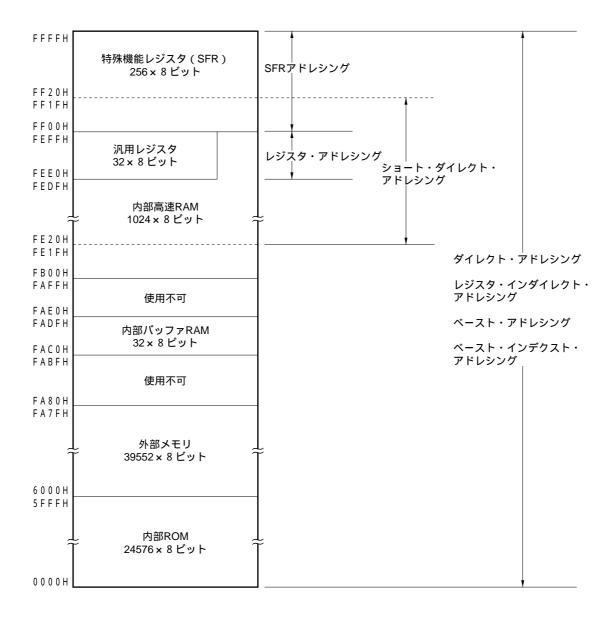

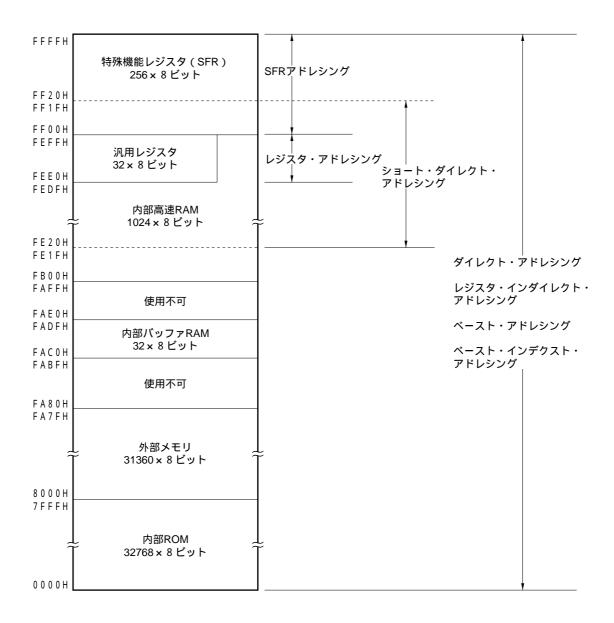

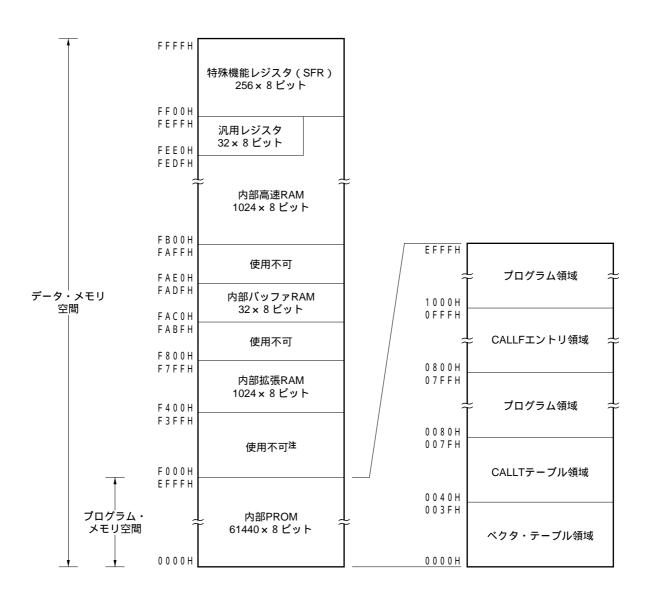

| ;          | 3 . 1        | <b>メモリ空間</b> 59                                    |

|            |              | 3.1.1 内部プログラム・メモリ空間 63                             |

|            |              | 3.1.2 内部データ・メモリ空間 64                               |

|            |              | 3.1.3 特殊機能レジスタ (SFR: Special Function Register)    |

領域 ... 64

|                                                       | 3.1.4 外部メモリ空間 64                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

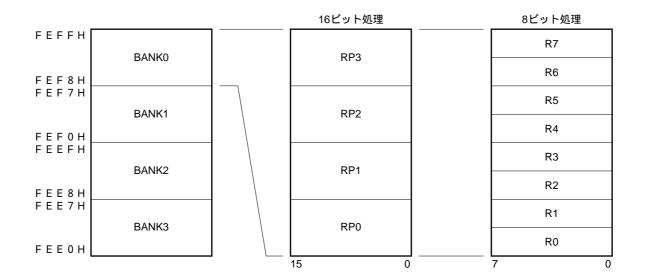

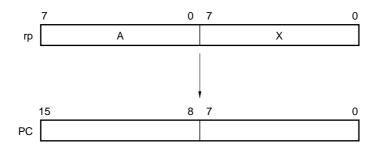

| 3.2                                                   | プロセッサ・レジスタ 65                                                                                                                                                                                                                                                                                                                      |

|                                                       | 3.2.1 制御レジスタ 65                                                                                                                                                                                                                                                                                                                    |

|                                                       | 3.2.2 汎用レジスタ 68                                                                                                                                                                                                                                                                                                                    |

|                                                       | 3.2.3 特殊機能レジスタ (SFR: Special Function Register) 70                                                                                                                                                                                                                                                                                 |

| 3.3                                                   | <b>命令アドレスのアドレシング</b> 73                                                                                                                                                                                                                                                                                                            |

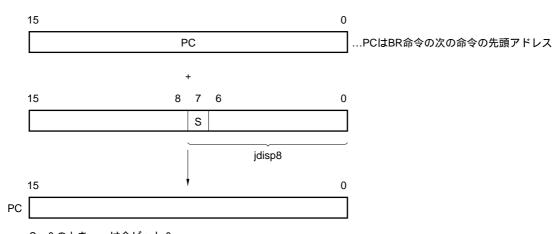

|                                                       | 3.3.1 レラティブ・アドレシング 73                                                                                                                                                                                                                                                                                                              |

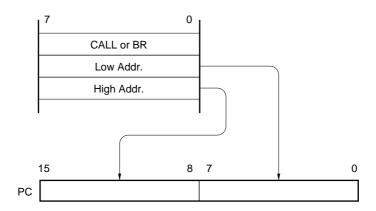

|                                                       | 3.3.2 イミーディエト・アドレシング 74                                                                                                                                                                                                                                                                                                            |

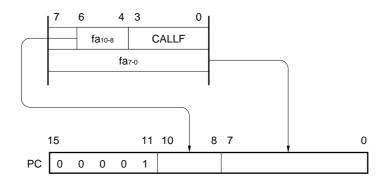

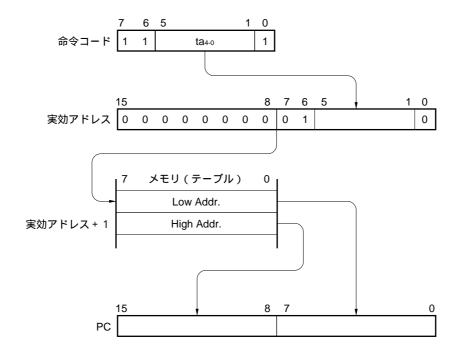

|                                                       | 3.3.3 テーブル・インダイレクト・アドレシング 75                                                                                                                                                                                                                                                                                                       |

|                                                       | 3.3.4 レジスタ・アドレシング 76                                                                                                                                                                                                                                                                                                               |

| 3.4                                                   | オペランド・アドレスのアドレシング 77                                                                                                                                                                                                                                                                                                               |

|                                                       | 3.4.1 データ・メモリ・アドレシング 77                                                                                                                                                                                                                                                                                                            |

|                                                       | 3.4.2 インプライド・アドレシング 81                                                                                                                                                                                                                                                                                                             |

|                                                       | 3.4.3 レジスタ・アドレシング 82                                                                                                                                                                                                                                                                                                               |

|                                                       | 3.4.4 ダイレクト・アドレシング 83                                                                                                                                                                                                                                                                                                              |

|                                                       | 3.4.5 ショート・ダイレクト・アドレシング 84                                                                                                                                                                                                                                                                                                         |

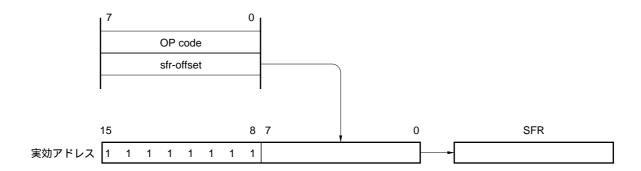

|                                                       | 3.4.6 特殊機能レジスタ (SFR) アドレシング 86                                                                                                                                                                                                                                                                                                     |

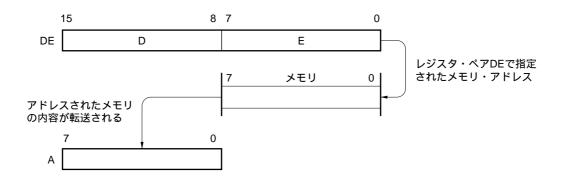

|                                                       | 3.4.7 レジスタ・インダイレクト・アドレシング 87                                                                                                                                                                                                                                                                                                       |

|                                                       | 3.4.8 ベースト・アドレシング 88                                                                                                                                                                                                                                                                                                               |

|                                                       | 3.4.9 ベースト・インデクスト・アドレシング 89                                                                                                                                                                                                                                                                                                        |

|                                                       | 3.4.10 スタック・アドレシング 89                                                                                                                                                                                                                                                                                                              |

|                                                       |                                                                                                                                                                                                                                                                                                                                    |

| 第4章                                                   | <b>ポート機能</b> 91                                                                                                                                                                                                                                                                                                                    |

|                                                       |                                                                                                                                                                                                                                                                                                                                    |

|                                                       |                                                                                                                                                                                                                                                                                                                                    |

|                                                       | ポートの機能 91                                                                                                                                                                                                                                                                                                                          |

|                                                       | <b>ポートの構成</b> 94                                                                                                                                                                                                                                                                                                                   |

|                                                       | ポートの構成 94<br>4.2.1 ポート0 95                                                                                                                                                                                                                                                                                                         |

|                                                       | ポートの構成 94<br>4.2.1 ポート0 95<br>4.2.2 ポート1 97                                                                                                                                                                                                                                                                                        |

|                                                       | ポートの構成 94<br>4.2.1 ポート0 95<br>4.2.2 ポート1 97<br>4.2.3 ポート2 98                                                                                                                                                                                                                                                                       |

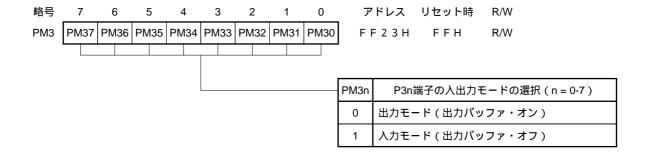

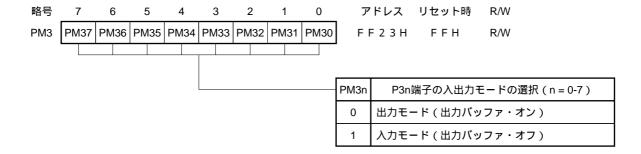

|                                                       | ポートの構成 94<br>4.2.1 ポート0 95<br>4.2.2 ポート1 97<br>4.2.3 ポート2 98<br>4.2.4 ポート3 100                                                                                                                                                                                                                                                     |

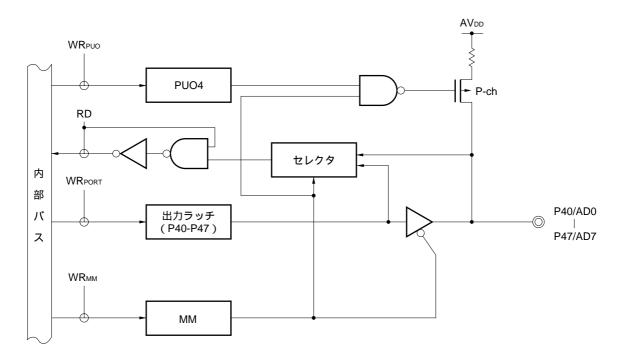

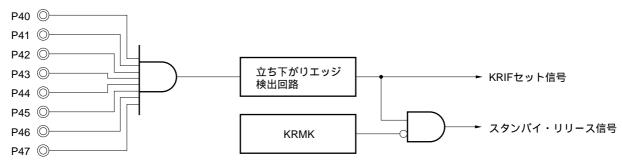

|                                                       | ポートの構成 94<br>4.2.1 ポート0 95<br>4.2.2 ポート1 97<br>4.2.3 ポート2 98<br>4.2.4 ポート3 100<br>4.2.5 ポート4 101                                                                                                                                                                                                                                   |

|                                                       | ポートの構成 94<br>4.2.1 ポート0 95<br>4.2.2 ポート1 97<br>4.2.3 ポート2 98<br>4.2.4 ポート3 100<br>4.2.5 ポート4 101<br>4.2.6 ポート5 102                                                                                                                                                                                                                 |

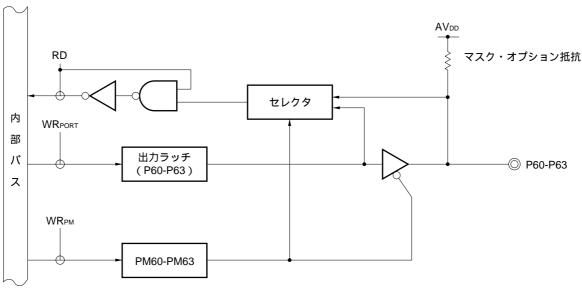

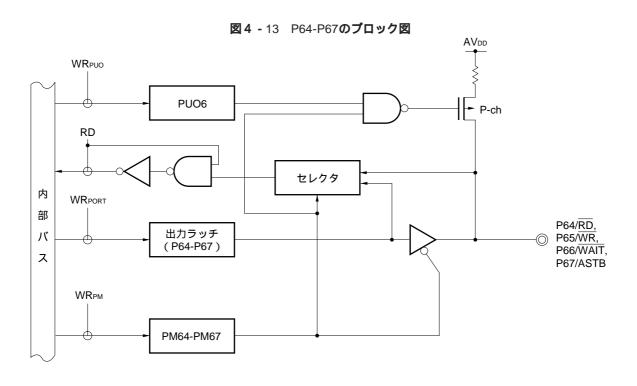

| 4.2                                                   | ポートの構成 94 4.2.1 ポート0 95 4.2.2 ポート1 97 4.2.3 ポート2 98 4.2.4 ポート3 100 4.2.5 ポート4 101 4.2.6 ポート5 102 4.2.7 ポート6 103                                                                                                                                                                                                                    |

| 4.2                                                   | ポートの構成 94 4.2.1 ポート0 95 4.2.2 ポート1 97 4.2.3 ポート2 98 4.2.4 ポート3 100 4.2.5 ポート4 101 4.2.6 ポート5 102 4.2.7 ポート6 103 ポート機能を制御するレジスタ 105                                                                                                                                                                                                 |

| 4.2                                                   | ポートの構成 94 4.2.1 ポート0 95 4.2.2 ポート1 97 4.2.3 ポート2 98 4.2.4 ポート3 100 4.2.5 ポート4 101 4.2.6 ポート5 102 4.2.7 ポート6 103 ポート機能を制御するレジスタ 105 ポート機能の動作 111                                                                                                                                                                                    |

| 4.2                                                   | ポートの構成 94 4.2.1 ポート0 95 4.2.2 ポート1 97 4.2.3 ポート2 98 4.2.4 ポート3 100 4.2.5 ポート4 101 4.2.6 ポート5 102 4.2.7 ポート6 103 ポート機能を制御するレジスタ 105 ポート機能の動作 111 4.4.1 入出力ポートへの書き込み 111                                                                                                                                                             |

| 4.2                                                   | ポートの構成 94 4.2.1 ポート0 95 4.2.2 ポート1 97 4.2.3 ポート2 98 4.2.4 ポート3 100 4.2.5 ポート4 101 4.2.6 ポート5 102 4.2.7 ポート6 103 ポート機能を制御するレジスタ 105 ポート機能の動作 111 4.4.1 入出力ポートへの書き込み 111 4.4.2 入出力ポートからの読み出し 111                                                                                                                                     |

| 4.2<br>4.3<br>4.4                                     | ポートの構成 94 4.2.1 ポート0 95 4.2.2 ポート1 97 4.2.3 ポート2 98 4.2.4 ポート3 100 4.2.5 ポート4 101 4.2.6 ポート5 102 4.2.7 ポート6 103 ポート機能を制御するレジスタ 105 ボート機能の動作 111 4.4.1 入出力ポートへの書き込み 111 4.4.2 入出力ポートからの読み出し 111 4.4.3 入出力ポートでの演算 112                                                                                                                |

| 4.2<br>4.3<br>4.4                                     | ポートの構成 94 4.2.1 ポート0 95 4.2.2 ポート1 97 4.2.3 ポート2 98 4.2.4 ポート3 100 4.2.5 ポート4 101 4.2.6 ポート5 102 4.2.7 ポート6 103 ポート機能を制御するレジスタ 105 ポート機能の動作 111 4.4.1 入出力ポートへの書き込み 111 4.4.2 入出力ポートからの読み出し 111                                                                                                                                     |

| 4.2<br>4.3<br>4.4                                     | ポートの構成 94 4.2.1 ポート0 95 4.2.2 ポート1 97 4.2.3 ポート2 98 4.2.4 ポート3 100 4.2.5 ポート4 101 4.2.6 ポート5 102 4.2.7 ポート6 103 ポート機能を制御するレジスタ 105 ボート機能の動作 111 4.4.1 入出力ポートへの書き込み 111 4.4.2 入出力ポートからの読み出し 111 4.4.3 入出力ポートでの演算 112                                                                                                                |

| 4.2<br>4.3<br>4.4                                     | ポートの構成 … 94 4.2.1 ポート0 … 95 4.2.2 ポート1 … 97 4.2.3 ポート2 … 98 4.2.4 ポート3 … 100 4.2.5 ポート4 … 101 4.2.6 ポート5 … 102 4.2.7 ポート6 … 103 ポート機能を制御するレジスタ … 105 ポート機能の動作 … 111 4.4.1 入出力ポートへの書き込み … 111 4.4.2 入出力ポートからの読み出し … 111 4.4.3 入出力ポートでの演算 … 112 マスク・オプション … 112                                                                      |

| 4.2<br>4.3<br>4.4<br>4.5<br>第 <b>5章</b>               | ポートの構成 … 94 4.2.1 ポート0 … 95 4.2.2 ポート1 … 97 4.2.3 ポート2 … 98 4.2.4 ポート3 … 100 4.2.5 ポート4 … 101 4.2.6 ポート5 … 102 4.2.7 ポート6 … 103 ポート機能を制御するレジスタ … 105 ポート機能の動作 … 111 4.4.1 入出力ポートへの書き込み … 111 4.4.2 入出力ポートからの読み出し … 111 4.4.3 入出力ポートでの演算 … 112 マスク・オプション … 112                                                                      |

| 4.2<br>4.3<br>4.4<br>4.5<br>第5章<br>5.1                | ポートの構成 … 94 4.2.1 ポート0 … 95 4.2.2 ポート1 … 97 4.2.3 ポート2 … 98 4.2.4 ポート3 … 100 4.2.5 ポート4 … 101 4.2.6 ポート5 … 102 4.2.7 ポート6 … 103 ボート機能を制御するレジスタ … 105 ボート機能の動作 … 111 4.4.1 入出力ポートへの書き込み … 111 4.4.2 入出力ポートからの読み出し … 111 4.4.3 入出力ポートでの演算 … 112 マスク・オプション … 112                                                                      |

| 4.2<br>4.3<br>4.4<br>4.5<br>第 <b>5章</b><br>5.1<br>5.2 | ポートの構成 … 94 4.2.1 ポート0 … 95 4.2.2 ポート1 … 97 4.2.3 ポート2 … 98 4.2.4 ポート3 … 100 4.2.5 ポート4 … 101 4.2.6 ポート5 … 102 4.2.7 ポート6 … 103 ポート機能を制御するレジスタ … 105 ボート機能の動作 … 111 4.4.1 入出力ポートへの書き込み … 111 4.4.2 入出力ポートからの読み出し … 111 4.4.3 入出力ポートでの演算 … 112 マスク・オプション … 112 クロック発生回路 … 113                                                       |

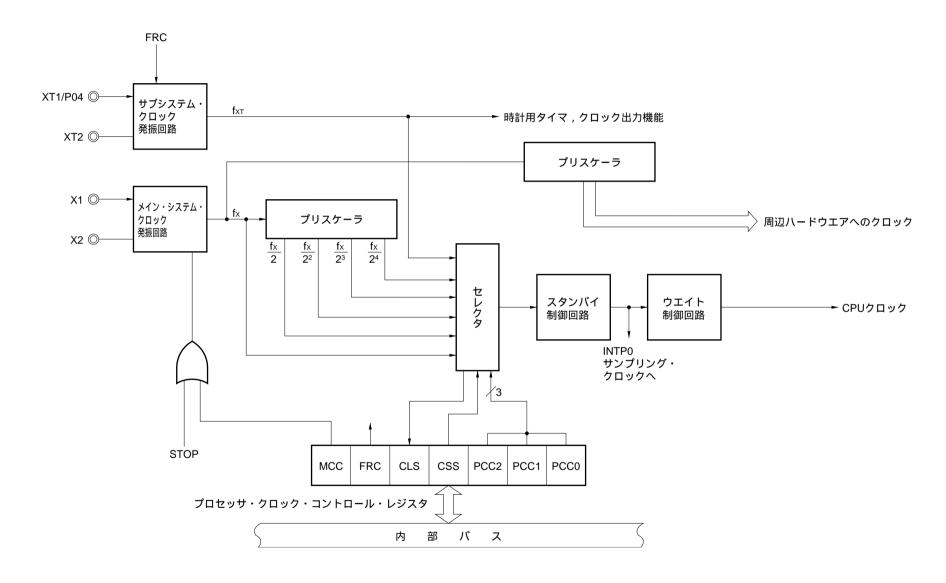

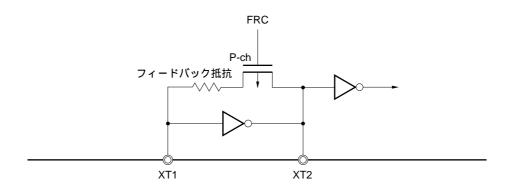

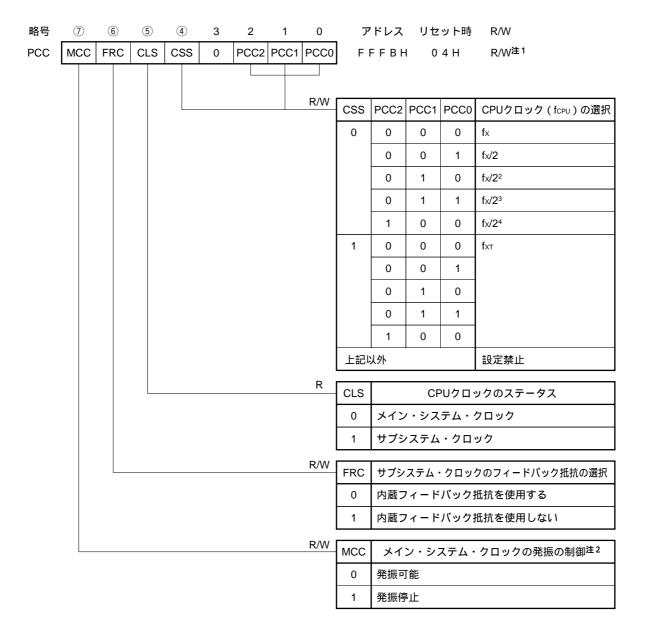

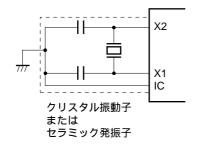

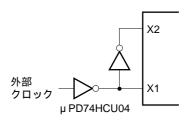

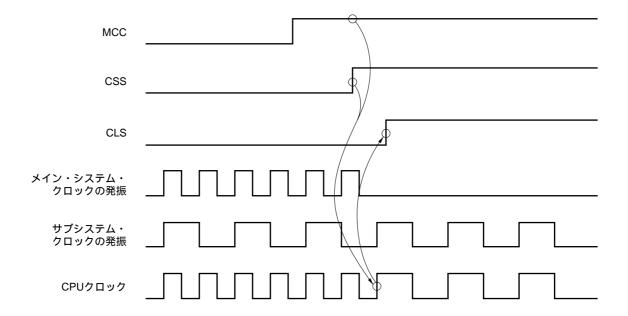

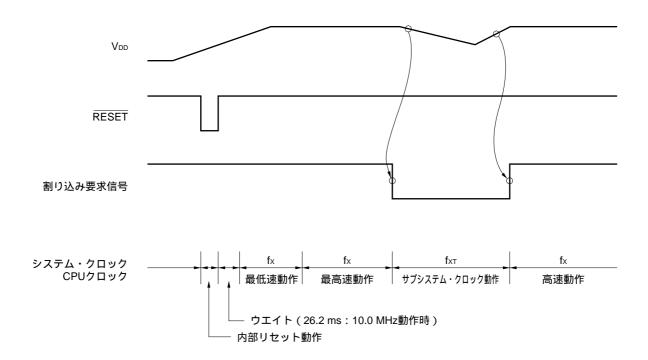

| 4.2<br>4.3<br>4.4<br>4.5<br>第5章<br>5.1<br>5.2<br>5.3  | ポートの構成 … 94 4.2.1 ポート0 … 95 4.2.2 ポート1 … 97 4.2.3 ポート2 … 98 4.2.4 ポート3 … 100 4.2.5 ポート4 … 101 4.2.6 ポート5 … 102 4.2.7 ポート6 … 103 ポート機能を制御するレジスタ … 105 ボート機能の動作 … 111 4.4.1 入出力ポートへの書き込み … 111 4.4.2 入出力ポートからの読み出し … 111 4.4.3 入出力ポートでの演算 … 112 マスク・オプション … 112 クロック発生回路 … 113 クロック発生回路の機能 … 113                                     |

| 4.2<br>4.3<br>4.4<br>4.5<br>第5章<br>5.1<br>5.2<br>5.3  | ポートの構成 … 94 4.2.1 ポート0 … 95 4.2.2 ポート1 … 97 4.2.3 ポート2 … 98 4.2.4 ポート3 … 100 4.2.5 ポート4 … 101 4.2.6 ポート5 … 102 4.2.7 ポート6 … 103 ポート機能を制御するレジスタ … 105 ポート機能の動作 … 111 4.4.1 入出力ポートへの書き込み … 111 4.4.2 入出力ポートからの読み出し … 111 4.4.3 入出力ポートでの演算 … 112 マスク・オプション … 112 クロック発生回路 … 113 クロック発生回路の機能 … 113 クロック発生回路の機能 … 113 クロック発生回路の構成 … 113 |

|                                                                    | 5.4.3 分周回路 121                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                    | 5.4.4 サブシステム・クロックを使用しない場合 121                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.5                                                                | クロック発生回路の動作 122                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                    | 5 . 5 . 1 メイン・システム・クロックの動作 123<br>5 . 5 . 2 サブシステム・クロックの動作 125                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.6                                                                | システム・クロックとCPUクロックの設定の変更 126                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                    | 5.6.1 システム・クロックとCPUクロックの                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                    | 切り替えに要する時間 126                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                    | 5.6.2 システム・クロックとCPUクロックの切り替え手順 127                                                                                                                                                                                                                                                                                                                                                                                                                    |

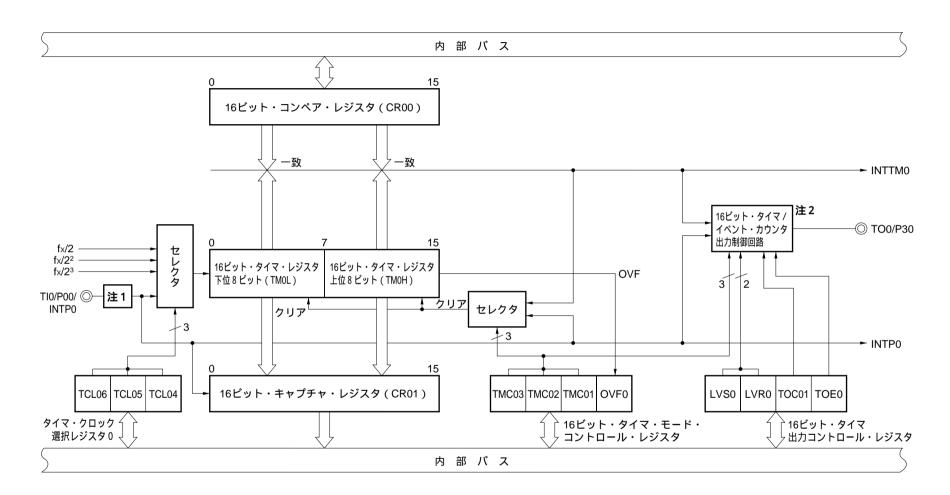

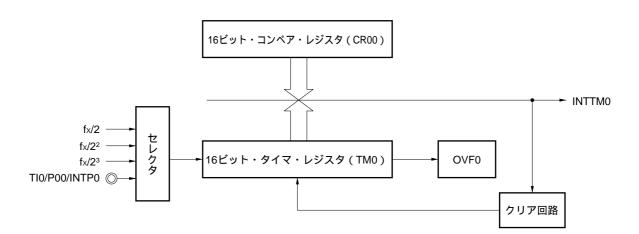

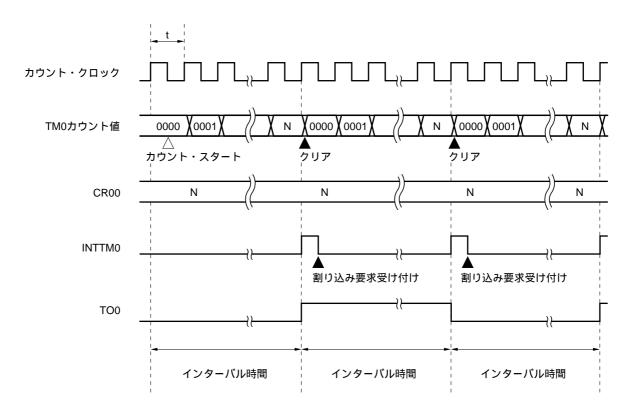

| 第6章                                                                | 16ピット・タイマ/イベント・カウンタ 129                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                    | μPD78014H <b>サブシリーズ内蔵タイマの概要</b> 129<br>16 <b>ビット・タイマ/イペント・カウンタの機能</b> 130                                                                                                                                                                                                                                                                                                                                                                             |

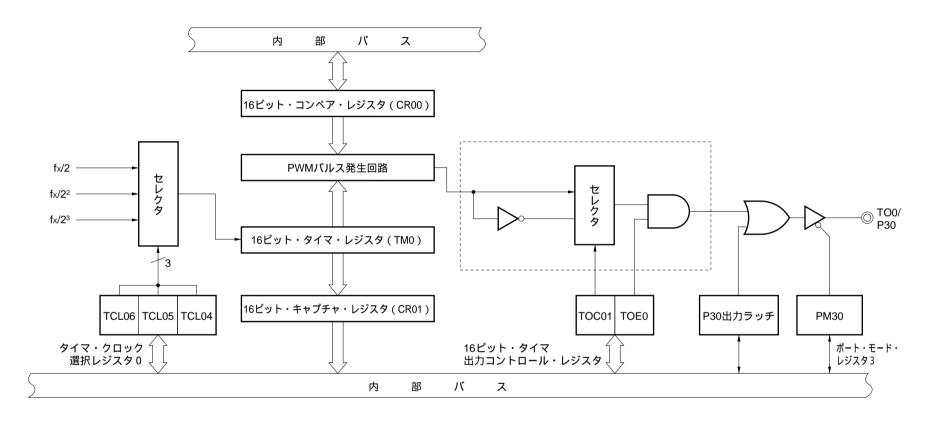

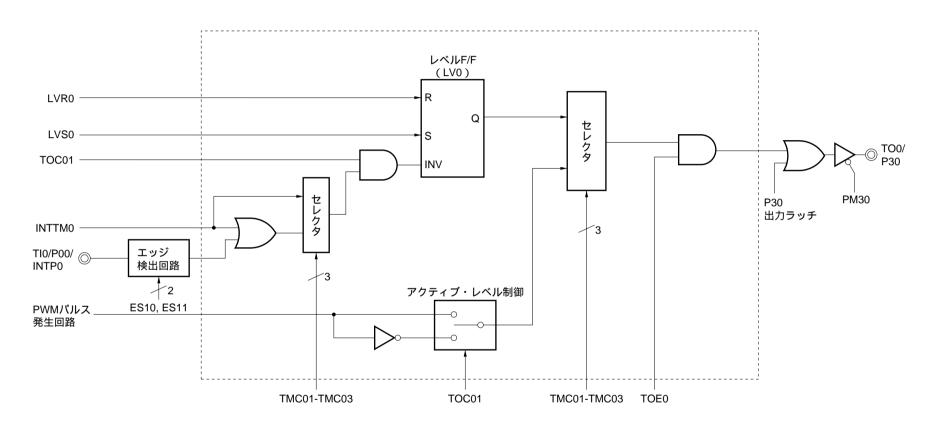

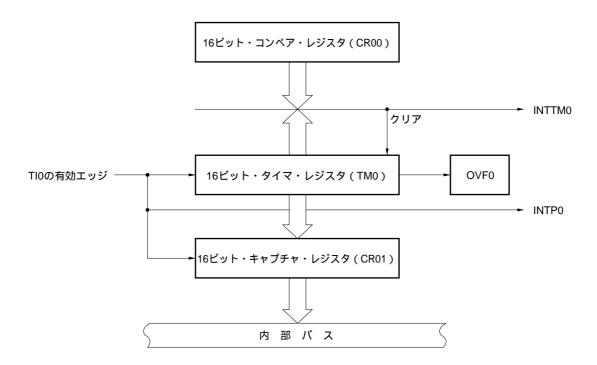

|                                                                    | 16ビット・タイマ/イベント・カウンタの構成 131                                                                                                                                                                                                                                                                                                                                                                                                                            |

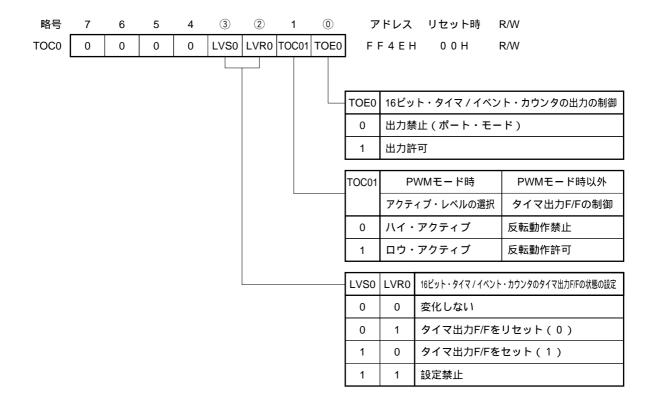

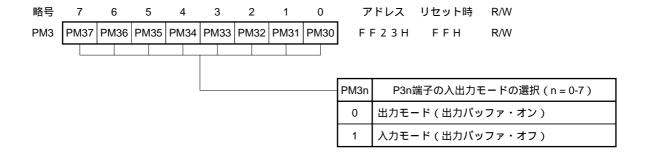

|                                                                    | 16ビット・タイマ/イベント・カウンタを制御するレジスタ 136                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.5                                                                | 16 <b>ビット・タイマ/イベント・カウンタの動作</b> 143                                                                                                                                                                                                                                                                                                                                                                                                                    |

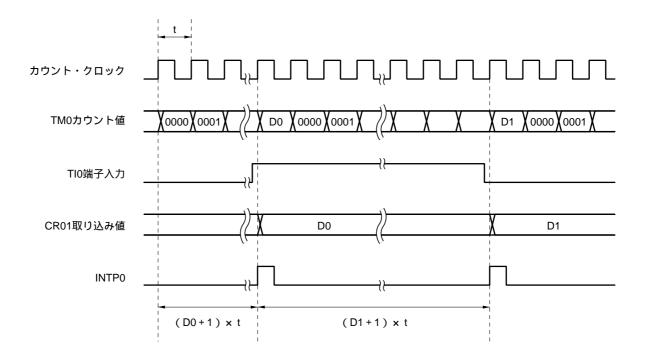

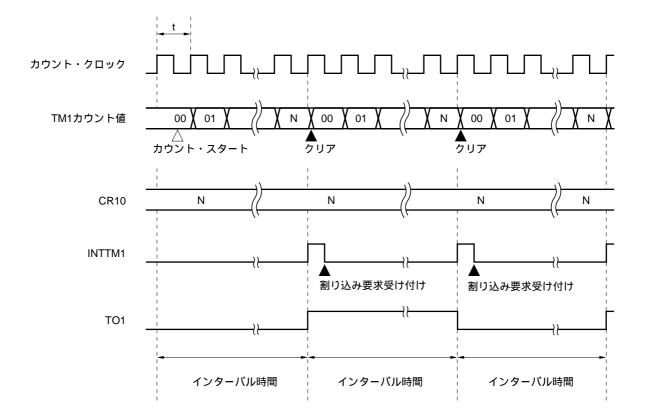

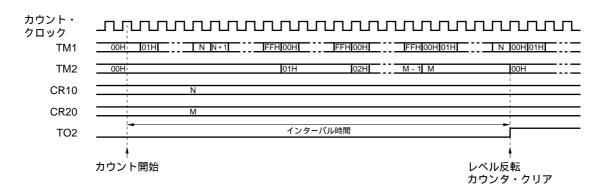

|                                                                    | 6.5.1 インターバル・タイマとしての動作 143                                                                                                                                                                                                                                                                                                                                                                                                                            |

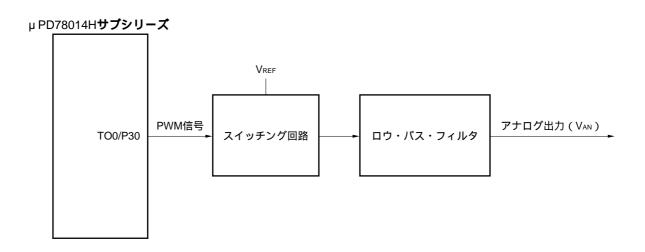

|                                                                    | 6.5.2 PWM出力としての動作 145                                                                                                                                                                                                                                                                                                                                                                                                                                 |

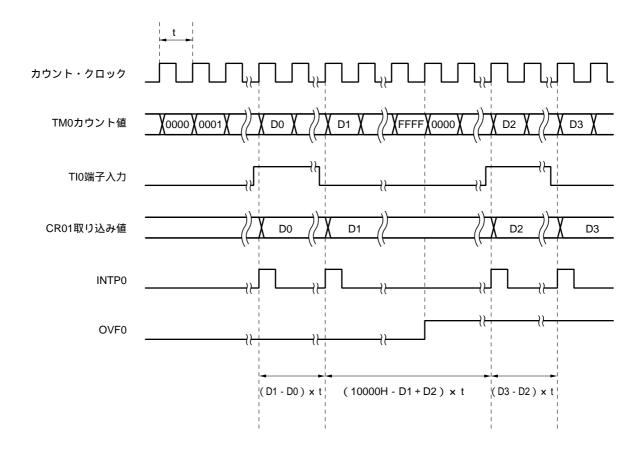

|                                                                    | 6.5.3 パルス幅測定としての動作 147                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                    | 6.5.4 外部イベント・カウンタとしての動作 150<br>6.5.5 方形波出力としての動作 152                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.6                                                                | 16 <b>ビット・タイマ/イベント・カウンタの注意事項</b> 153                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 第7章                                                                | 8 ピット・タイマ / イベント・カウンタ 157                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                    | 8 ビット・タイマ / イベント・カウンタ 157<br>8 ビット・タイマ / イベント・カウンタの機能 157<br>7.1.1 8 ビット・タイマ / イベント・カウンタ・モード 157                                                                                                                                                                                                                                                                                                                                                      |

|                                                                    | 8 ビット・タイマ / イベント・カウンタの機能 157                                                                                                                                                                                                                                                                                                                                                                                                                          |

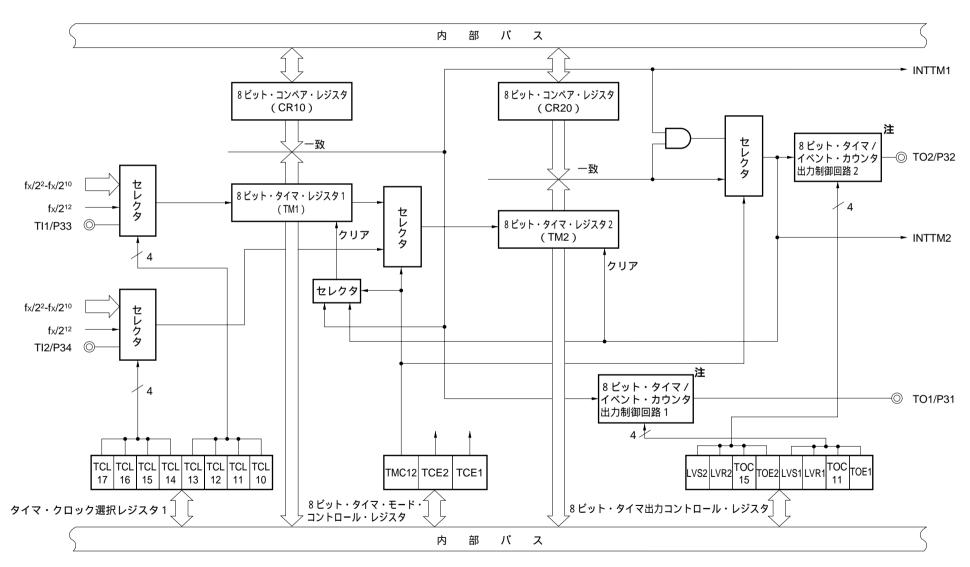

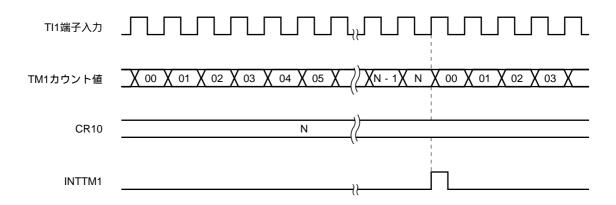

| 7.1                                                                | 8 ピット・タイマ/イベント・カウンタの機能 157<br>7.1.1 8 ビット・タイマ / イベント・カウンタ・モード 157<br>7.1.2 16ビット・タイマ / イベント・カウンタ・モード 159<br>8 ピット・タイマ / イベント・カウンタの構成 160                                                                                                                                                                                                                                                                                                              |

| 7.1<br>7.2<br>7.3                                                  | 8 ビット・タイマ/イベント・カウンタの機能 157<br>7.1.1 8 ビット・タイマ/イベント・カウンタ・モード 157<br>7.1.2 16ビット・タイマ/イベント・カウンタ・モード 159<br>8 ビット・タイマ/イベント・カウンタの構成 160<br>8 ビット・タイマ/イベント・カウンタを制御するレジスタ 163                                                                                                                                                                                                                                                                                |

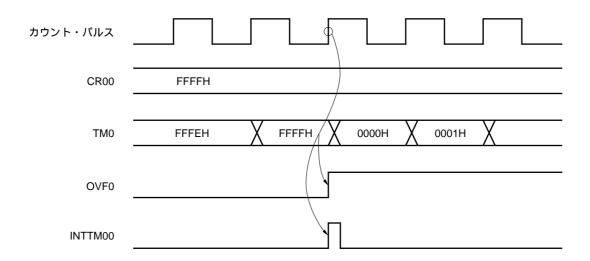

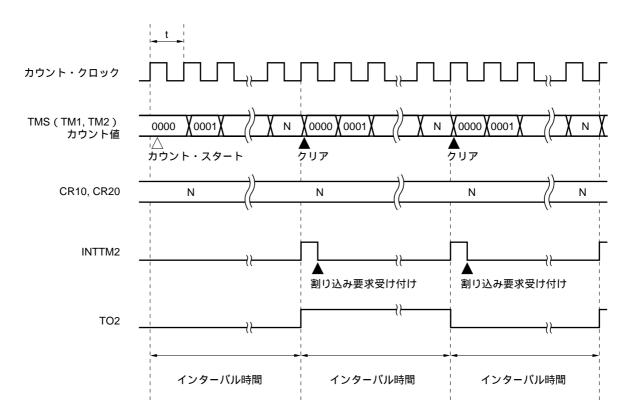

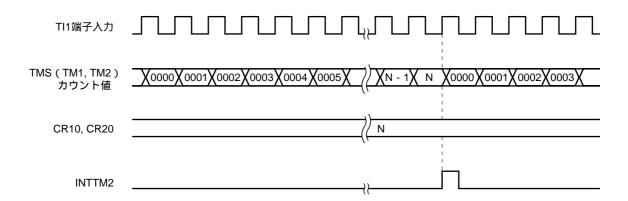

| 7.1<br>7.2<br>7.3                                                  | 8 ビット・タイマ/イベント・カウンタの機能 157 7.1.1 8 ビット・タイマ/イベント・カウンタ・モード 157 7.1.2 16ビット・タイマ/イベント・カウンタ・モード 159 8 ビット・タイマ/イベント・カウンタの構成 160 8 ビット・タイマ/イベント・カウンタを制御するレジスタ 163 8 ビット・タイマ/イベント・カウンタの動作 168                                                                                                                                                                                                                                                                 |

| 7.1<br>7.2<br>7.3                                                  | 8 ピット・タイマ/イベント・カウンタの機能 157 7.1.1 8 ビット・タイマ/イベント・カウンタ・モード 157 7.1.2 16ビット・タイマ/イベント・カウンタ・モード 159 8 ピット・タイマ/イベント・カウンタの構成 160 8 ピット・タイマ/イベント・カウンタを制御するレジスタ 163 8 ピット・タイマ/イベント・カウンタの動作 168 7.4.1 8 ビット・タイマ/イベント・カウンタ・モード 168                                                                                                                                                                                                                               |

| 7.1<br>7.2<br>7.3<br>7.4                                           | 8 ビット・タイマ/イベント・カウンタの機能 157 7.1.1 8 ビット・タイマ/イベント・カウンタ・モード 157 7.1.2 16ビット・タイマ/イベント・カウンタ・モード 159 8 ビット・タイマ/イベント・カウンタの構成 160 8 ビット・タイマ/イベント・カウンタを制御するレジスタ 163 8 ビット・タイマ/イベント・カウンタの動作 168                                                                                                                                                                                                                                                                 |

| 7.1<br>7.2<br>7.3<br>7.4                                           | 8 ビット・タイマ/イベント・カウンタの機能 … 157 7.1.1 8 ビット・タイマ/イベント・カウンタ・モード … 157 7.1.2 16ビット・タイマ/イベント・カウンタ・モード … 159 8 ビット・タイマ/イベント・カウンタの構成 … 160 8 ビット・タイマ/イベント・カウンタを制御するレジスタ … 163 8 ビット・タイマ/イベント・カウンタの動作 … 168 7.4.1 8 ビット・タイマ/イベント・カウンタ・モード … 168 7.4.2 16ビット・タイマ/イベント・カウンタ・モード … 172 8 ビット・タイマ/イベント・カウンタの注意事項 … 176                                                                                                                                              |

| 7.1<br>7.2<br>7.3<br>7.4                                           | 8 ビット・タイマ / イベント・カウンタの機能 157 7.1.1 8 ビット・タイマ / イベント・カウンタ・モード 157 7.1.2 16ビット・タイマ / イベント・カウンタ・モード 159 8 ビット・タイマ / イベント・カウンタの構成 160 8 ビット・タイマ / イベント・カウンタを制御するレジスタ 163 8 ビット・タイマ / イベント・カウンタの動作 168 7.4.1 8 ビット・タイマ / イベント・カウンタ・モード 168 7.4.2 16ビット・タイマ / イベント・カウンタ・モード 172                                                                                                                                                                             |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5                                    | 8 ビット・タイマ/イベント・カウンタの機能 … 157 7.1.1 8 ビット・タイマ/イベント・カウンタ・モード … 157 7.1.2 16ビット・タイマ/イベント・カウンタ・モード … 159 8 ビット・タイマ/イベント・カウンタの構成 … 160 8 ビット・タイマ/イベント・カウンタを制御するレジスタ … 163 8 ビット・タイマ/イベント・カウンタの動作 … 168 7.4.1 8 ビット・タイマ/イベント・カウンタ・モード … 168 7.4.2 16ビット・タイマ/イベント・カウンタ・モード … 172 8 ビット・タイマ/イベント・カウンタの注意事項 … 176                                                                                                                                              |

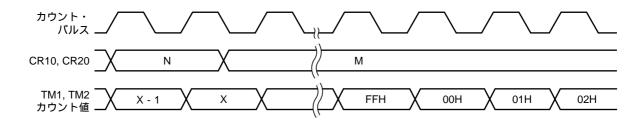

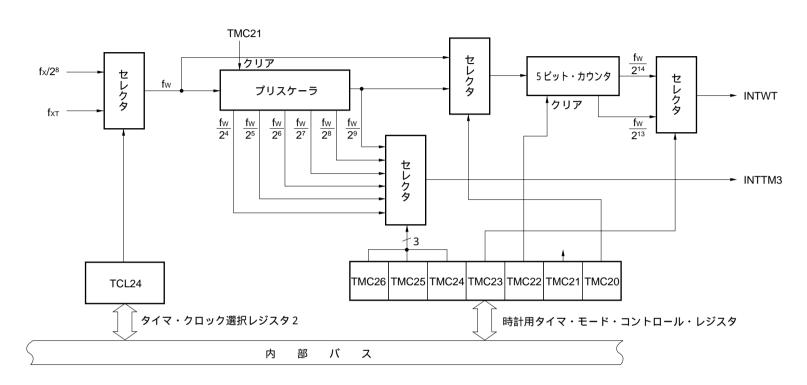

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>第8章<br>8.1<br>8.2               | 8 ピット・タイマ/イベント・カウンタの機能 … 157 7.1.1 8 ビット・タイマ/イベント・カウンタ・モード … 157 7.1.2 16 ビット・タイマ/イベント・カウンタ・モード … 159 8 ピット・タイマ/イベント・カウンタの構成 … 160 8 ピット・タイマ/イベント・カウンタを制御するレジスタ … 163 8 ピット・タイマ/イベント・カウンタの動作 … 168 7.4.1 8 ビット・タイマ/イベント・カウンタ・モード … 168 7.4.2 16 ビット・タイマ/イベント・カウンタ・モード … 172 8 ピット・タイマ/イベント・カウンタの注意事項 … 176 時計用タイマの機能 … 179 時計用タイマの機能 … 179                                                                                                            |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>第8章<br>8.1<br>8.2<br>8.3        | 8 ピット・タイマ / イベント・カウンタの機能 … 157 7.1.1 8 ビット・タイマ / イベント・カウンタ・モード … 157 7.1.2 16 ビット・タイマ / イベント・カウンタ・モード … 159 8 ピット・タイマ / イベント・カウンタの構成 … 160 8 ピット・タイマ / イベント・カウンタを制御するレジスタ … 163 8 ピット・タイマ / イベント・カウンタの動作 … 168 7.4.1 8 ビット・タイマ / イベント・カウンタ・モード … 168 7.4.2 16 ビット・タイマ / イベント・カウンタ・モード … 172 8 ピット・タイマ / イベント・カウンタの注意事項 … 176 時計用タイマの機能 … 179 時計用タイマの機能 … 179 時計用タイマの構成 … 180 時計用タイマを制御するレジスタ … 180                                                    |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>第8章<br>8.1<br>8.2<br>8.3        | 8 ビット・タイマ/イベント・カウンタの機能 … 157 7.1.1 8 ビット・タイマ/イベント・カウンタ・モード … 157 7.1.2 16ビット・タイマ/イベント・カウンタ・モード … 159 8 ビット・タイマ/イベント・カウンタの構成 … 160 8 ビット・タイマ/イベント・カウンタを制御するレジスタ … 163 8 ビット・タイマ/イベント・カウンタの動作 … 168 7.4.1 8 ビット・タイマ/イベント・カウンタ・モード … 168 7.4.2 16ビット・タイマ/イベント・カウンタ・モード … 172 8 ビット・タイマ/イベント・カウンタの注意事項 … 176 時計用タイマの機能 … 179 時計用タイマの構成 … 180 時計用タイマの構成 … 180 時計用タイマの動作 … 184                                                                              |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>第8章<br>8.1<br>8.2<br>8.3        | 8 ピット・タイマ / イベント・カウンタの機能 … 157 7.1.1 8 ビット・タイマ / イベント・カウンタ・モード … 157 7.1.2 16 ビット・タイマ / イベント・カウンタ・モード … 159 8 ピット・タイマ / イベント・カウンタの構成 … 160 8 ピット・タイマ / イベント・カウンタを制御するレジスタ … 163 8 ピット・タイマ / イベント・カウンタの動作 … 168 7.4.1 8 ビット・タイマ / イベント・カウンタ・モード … 168 7.4.2 16 ビット・タイマ / イベント・カウンタ・モード … 172 8 ピット・タイマ / イベント・カウンタ・モード … 172 8 ピット・タイマ / イベント・カウンタの注意事項 … 176 時計用タイマの機能 … 179 時計用タイマの構成 … 180 時計用タイマの動作 … 180 時計用タイマの動作 … 184 8.4.1 時計用タイマとしての動作 … 184 |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>第8章<br>8.1<br>8.2<br>8.3        | 8 ビット・タイマ/イベント・カウンタの機能 … 157 7.1.1 8 ビット・タイマ/イベント・カウンタ・モード … 157 7.1.2 16ビット・タイマ/イベント・カウンタ・モード … 159 8 ビット・タイマ/イベント・カウンタの構成 … 160 8 ビット・タイマ/イベント・カウンタを制御するレジスタ … 163 8 ビット・タイマ/イベント・カウンタの動作 … 168 7.4.1 8 ビット・タイマ/イベント・カウンタ・モード … 168 7.4.2 16ビット・タイマ/イベント・カウンタ・モード … 172 8 ビット・タイマ/イベント・カウンタの注意事項 … 176 時計用タイマの機能 … 179 時計用タイマの構成 … 180 時計用タイマの構成 … 180 時計用タイマの動作 … 184                                                                              |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>第8章<br>8.1<br>8.2<br>8.3<br>8.4 | 8 ピット・タイマ / イベント・カウンタの機能 … 157 7.1.1 8 ビット・タイマ / イベント・カウンタ・モード … 157 7.1.2 16 ビット・タイマ / イベント・カウンタ・モード … 159 8 ピット・タイマ / イベント・カウンタの構成 … 160 8 ピット・タイマ / イベント・カウンタを制御するレジスタ … 163 8 ピット・タイマ / イベント・カウンタの動作 … 168 7.4.1 8 ビット・タイマ / イベント・カウンタ・モード … 168 7.4.2 16 ビット・タイマ / イベント・カウンタ・モード … 172 8 ピット・タイマ / イベント・カウンタ・モード … 172 8 ピット・タイマ / イベント・カウンタの注意事項 … 176 時計用タイマの機能 … 179 時計用タイマの構成 … 180 時計用タイマの動作 … 180 時計用タイマの動作 … 184 8.4.1 時計用タイマとしての動作 … 184 |

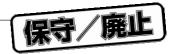

|                                                                                                    | <b>ウォッチドッグ・タイマの構成</b> 188                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.3                                                                                                | <b>ウォッチドッグ・タイマを制御するレジスタ</b> 190                                                                                                                                                                                                                    |

| 9.4                                                                                                | <b>ウォッチドッグ・タイマの動作</b> 193                                                                                                                                                                                                                          |

|                                                                                                    | 9.4.1 ウォッチドッグ・タイマとしての動作 193                                                                                                                                                                                                                        |

|                                                                                                    | 9.4.2 インターバル・タイマとしての動作 194                                                                                                                                                                                                                         |

|                                                                                                    |                                                                                                                                                                                                                                                    |

| 0章                                                                                                 | <b>クロック出力制御回路</b> 195                                                                                                                                                                                                                              |

| _                                                                                                  |                                                                                                                                                                                                                                                    |

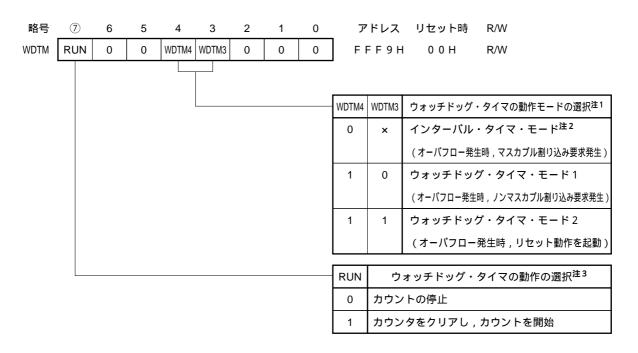

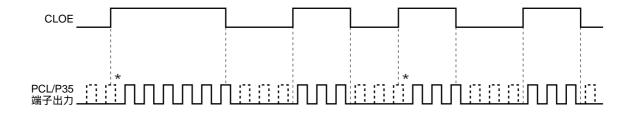

| 10. <b>1</b>                                                                                       | <b>クロック出力制御回路の機能</b> 195                                                                                                                                                                                                                           |

|                                                                                                    | クロック出力制御回路の構成 196                                                                                                                                                                                                                                  |

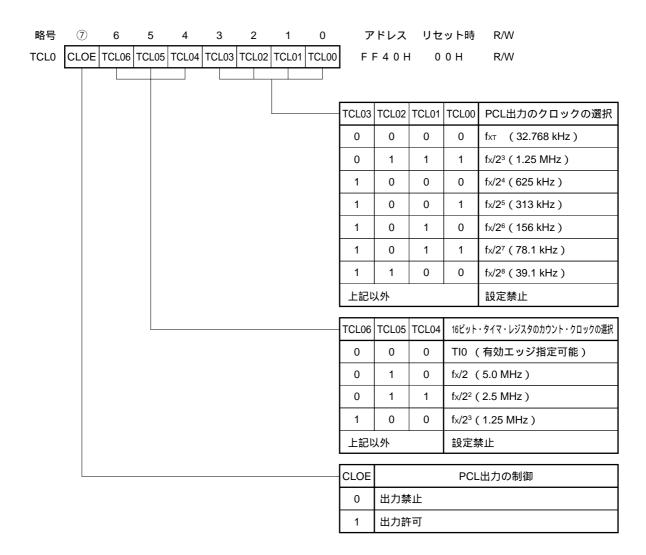

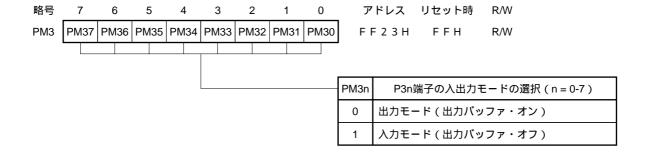

|                                                                                                    | クロック出力機能を制御するレジスタ 196                                                                                                                                                                                                                              |

|                                                                                                    |                                                                                                                                                                                                                                                    |

| 1章                                                                                                 | ブザー出力制御回路 199                                                                                                                                                                                                                                      |

|                                                                                                    | A MANAGEMENT 100                                                                                                                                                                                                                                   |

| 11 <b>1</b>                                                                                        | <b>ブザー出力制御回路の機能</b> 199                                                                                                                                                                                                                            |

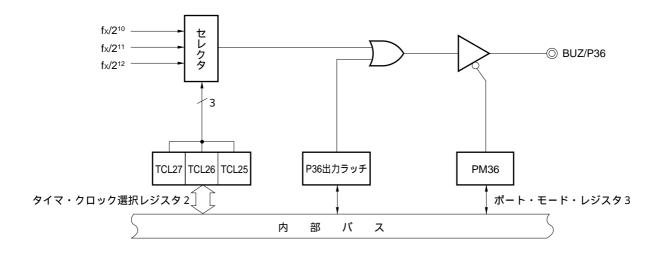

|                                                                                                    | ブザー出力制御回路の構成 199                                                                                                                                                                                                                                   |

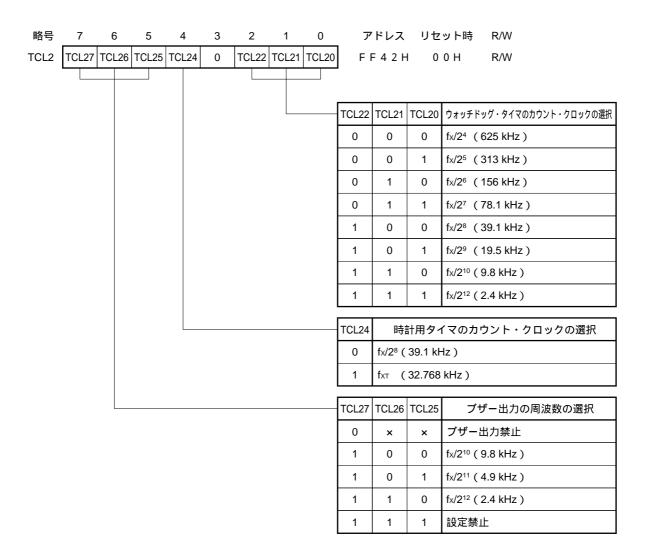

|                                                                                                    | プザー出力機能を制御するレジスタ 200                                                                                                                                                                                                                               |

| 11.3                                                                                               |                                                                                                                                                                                                                                                    |

| 2音                                                                                                 | A/D <b>コンバータ</b> 203                                                                                                                                                                                                                               |

| <b>-</b>                                                                                           | 7/D 3 / / 203                                                                                                                                                                                                                                      |

| 12 <b>1</b>                                                                                        | A/D <b>コンバータの機能</b> 203                                                                                                                                                                                                                            |

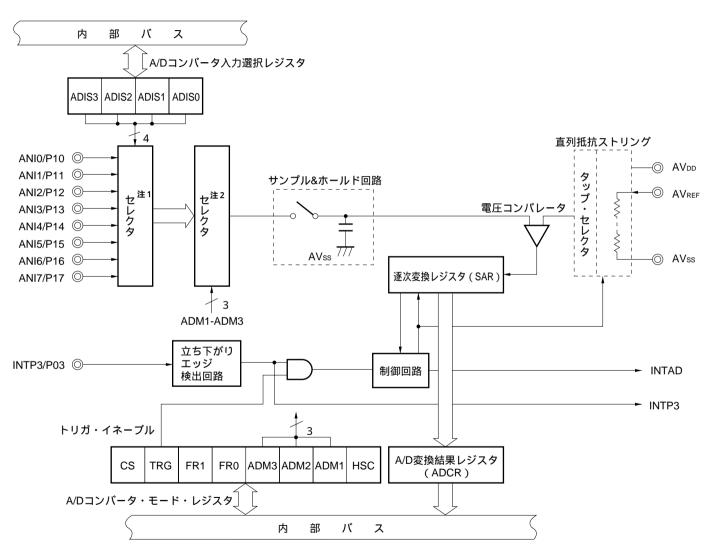

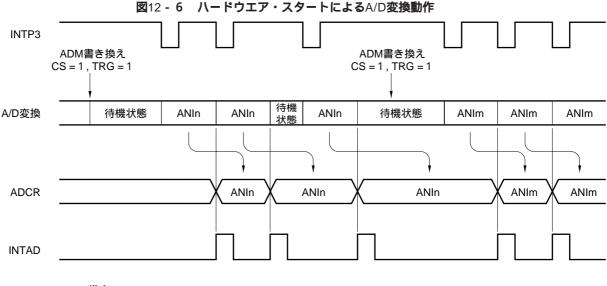

|                                                                                                    | A/D <b>コンバータの機能</b> 203<br>A/D <b>コンバータの構成</b> 203                                                                                                                                                                                                 |

|                                                                                                    |                                                                                                                                                                                                                                                    |

|                                                                                                    | A/D <b>コンパータを制御するレジスタ</b> 206                                                                                                                                                                                                                      |

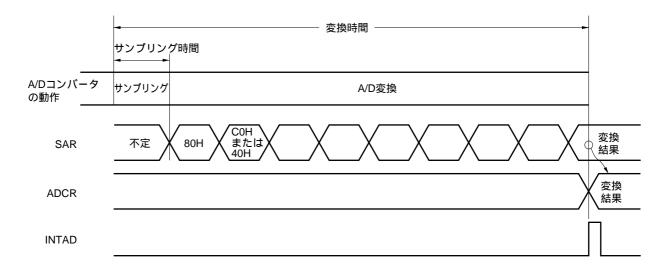

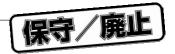

| 12. <b>4</b>                                                                                       | A/D <b>コンバータの動作</b> 209                                                                                                                                                                                                                            |

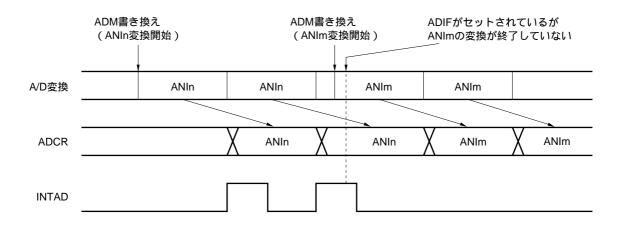

|                                                                                                    | 12.4.1 A/Dコンバータの基本動作 209                                                                                                                                                                                                                           |

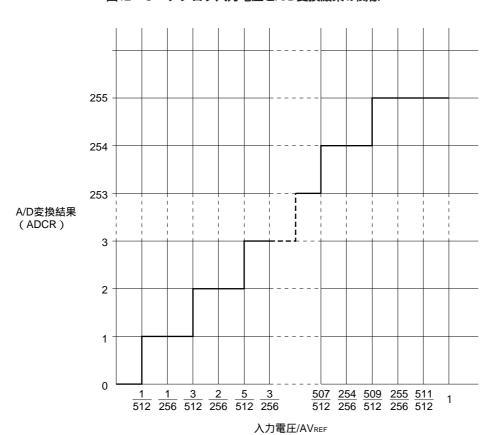

|                                                                                                    | 12.4.2 入力電圧と変換結果 211                                                                                                                                                                                                                               |

|                                                                                                    | 12.4.3 A/Dコンバータの動作モード 212                                                                                                                                                                                                                          |

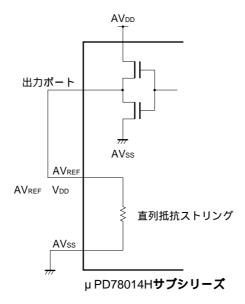

| 12. <b>5</b>                                                                                       | A/D <b>コンバータの注意事項</b> 214                                                                                                                                                                                                                          |

|                                                                                                    |                                                                                                                                                                                                                                                    |

| 3章                                                                                                 | シリアル・インタフェース・チャネル <b>0</b> 219                                                                                                                                                                                                                     |

|                                                                                                    |                                                                                                                                                                                                                                                    |

| 13 <b>1</b>                                                                                        |                                                                                                                                                                                                                                                    |

|                                                                                                    | シリアル・インタフェース・チャネル <b>0 の機能</b> 220                                                                                                                                                                                                                 |

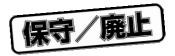

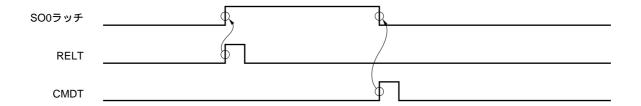

| 13. <b>2</b>                                                                                       | シリアル・インタフェース・チャネル 0 の構成 221                                                                                                                                                                                                                        |

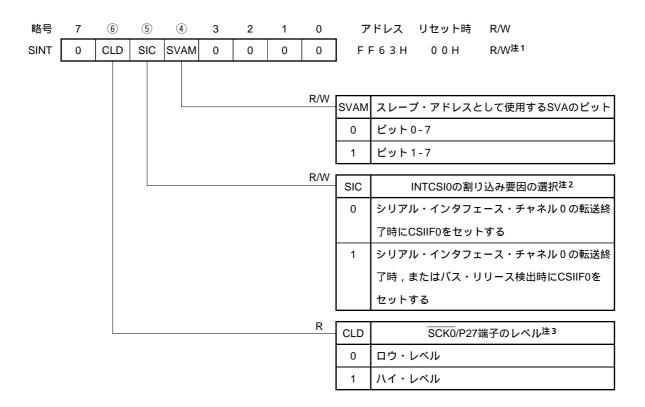

| 13. <b>2</b><br>13. <b>3</b>                                                                       | シリアル・インタフェース・チャネル 0 の構成 221<br>シリアル・インタフェース・チャネル 0 を制御するレジスタ 225                                                                                                                                                                                   |

| 13. <b>2</b><br>13. <b>3</b>                                                                       | シリアル・インタフェース・チャネル 0 の構成 221                                                                                                                                                                                                                        |

| 13. <b>2</b><br>13. <b>3</b>                                                                       | シリアル・インタフェース・チャネル 0 の構成 221<br>シリアル・インタフェース・チャネル 0 を制御するレジスタ 225                                                                                                                                                                                   |

| 13. <b>2</b><br>13. <b>3</b>                                                                       | シリアル・インタフェース・チャネル 0 の構成 221<br>シリアル・インタフェース・チャネル 0 を制御するレジスタ 225<br>シリアル・インタフェース・チャネル 0 の動作 232                                                                                                                                                    |

| 13. <b>2</b><br>13. <b>3</b>                                                                       | シリアル・インタフェース・チャネル 0 の構成221シリアル・インタフェース・チャネル 0 を制御するレジスタ225シリアル・インタフェース・チャネル 0 の動作23213.4.1動作停止モード232                                                                                                                                               |

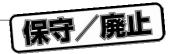

| 13. <b>2</b><br>13. <b>3</b>                                                                       | シリアル・インタフェース・チャネル 0 の構成221シリアル・インタフェース・チャネル 0 を制御するレジスタ225シリアル・インタフェース・チャネル 0 の動作23213.4.1動作停止モード23213.4.23 線式シリアルI/Oモードの動作232                                                                                                                     |

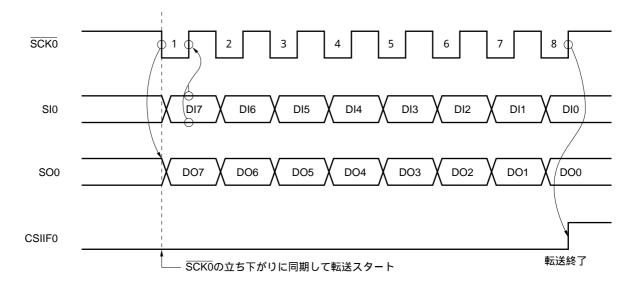

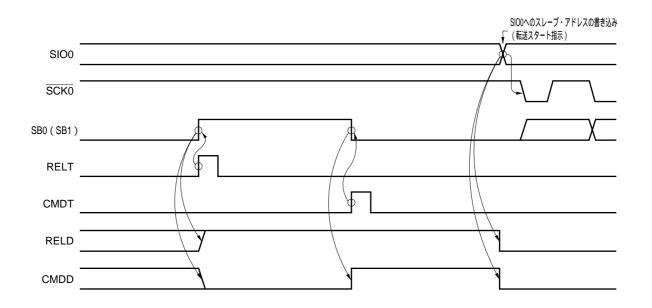

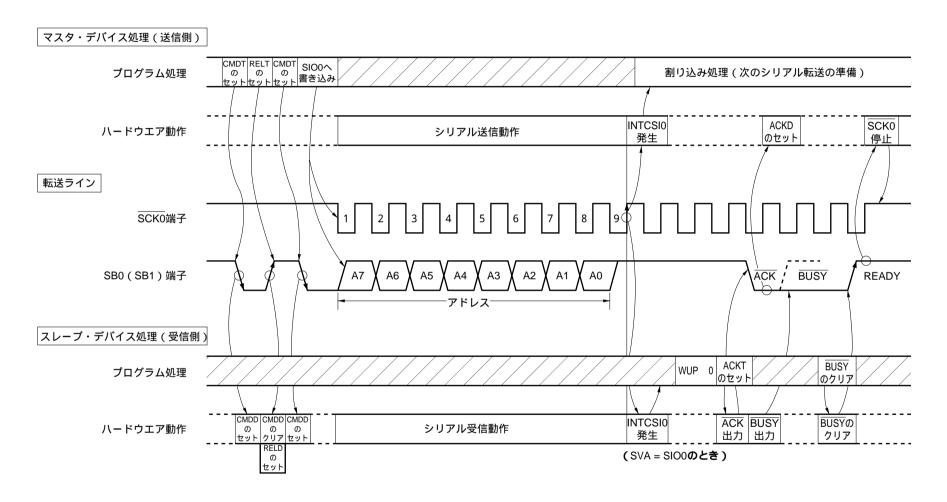

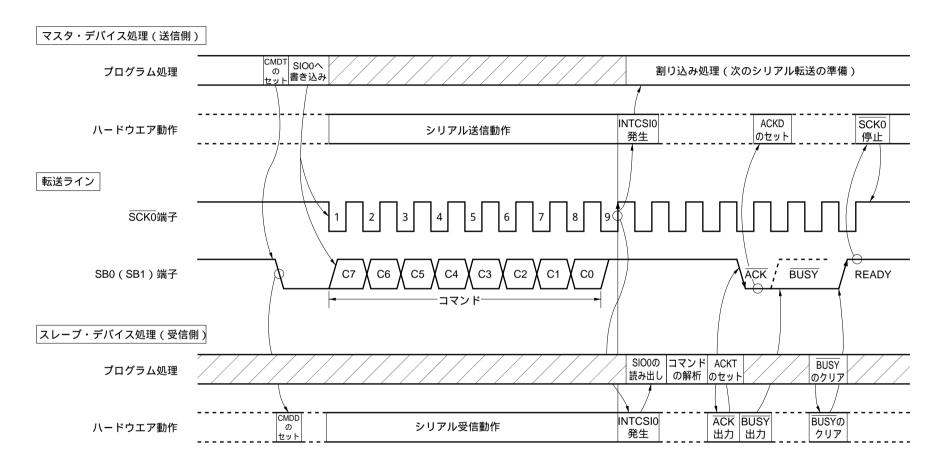

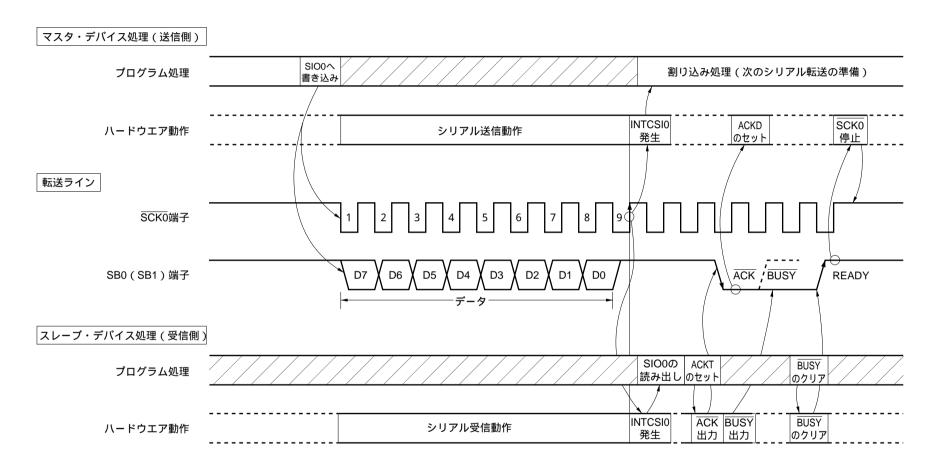

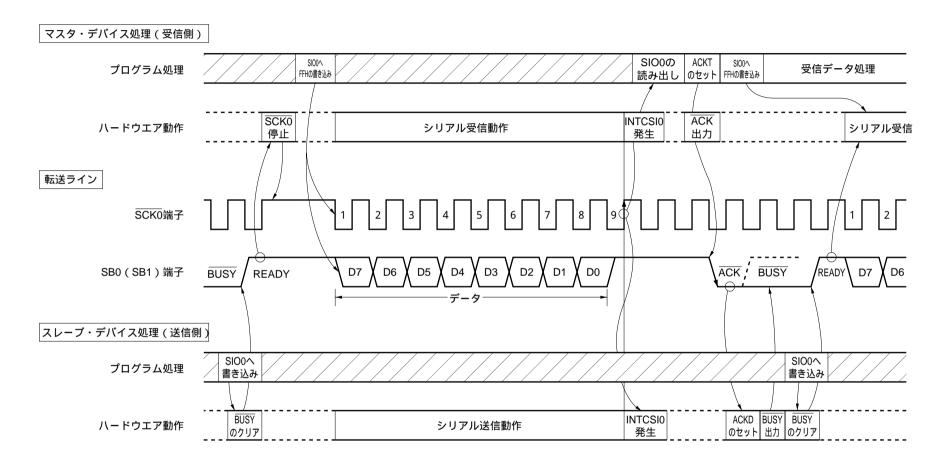

| 13. <b>2</b><br>13. <b>3</b>                                                                       | シリアル・インタフェース・チャネル 0 の構成221シリアル・インタフェース・チャネル 0 を制御するレジスタ225シリアル・インタフェース・チャネル 0 の動作23213.4.1動作停止モード23213.4.23 線式シリアルI/Oモードの動作23213.4.3SBIモードの動作237                                                                                                   |

| 13. <b>2</b><br>13. <b>3</b>                                                                       | シリアル・インタフェース・チャネル 0 の構成221シリアル・インタフェース・チャネル 0 を制御するレジスタ23213.4.1動作停止モード23213.4.23 線式シリアルI/Oモードの動作23213.4.3SBIモードの動作23713.4.42 線式シリアルI/Oモードの動作267                                                                                                   |

| 13. <b>2</b><br>13. <b>3</b><br>13. <b>4</b>                                                       | シリアル・インタフェース・チャネル 0 の構成221シリアル・インタフェース・チャネル 0 を制御するレジスタ23213.4.1動作停止モード23213.4.23 線式シリアルI/Oモードの動作23213.4.3SBIモードの動作23713.4.42 線式シリアルI/Oモードの動作267                                                                                                   |

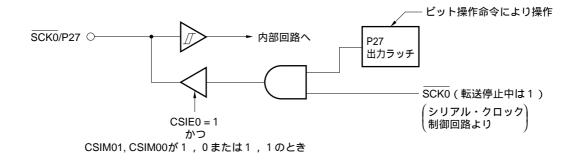

| 13. <b>2</b><br>13. <b>3</b><br>13. <b>4</b>                                                       | シリアル・インタフェース・チャネル 0 の構成221シリアル・インタフェース・チャネル 0 を制御するレジスタ225シリアル・インタフェース・チャネル 0 の動作23213.4.1動作停止モード23213.4.23 線式シリアルI/Oモードの動作23213.4.3SBIモードの動作23713.4.42 線式シリアルI/Oモードの動作26713.4.5SCKO/P27端子出力の操作272                                                 |

| 13. <b>2</b><br>13. <b>3</b><br>13. <b>4</b>                                                       | シリアル・インタフェース・チャネル 0 の構成221シリアル・インタフェース・チャネル 0 を制御するレジスタ225シリアル・インタフェース・チャネル 0 の動作23213.4.1動作停止モード23213.4.23 線式シリアルI/Oモードの動作23213.4.3SBIモードの動作23713.4.42 線式シリアルI/Oモードの動作26713.4.5SCKO/P27端子出力の操作272                                                 |

| 13. <b>2</b><br>13. <b>3</b><br>13. <b>4</b><br>4章                                                 | シリアル・インタフェース・チャネル 0 の構成221シリアル・インタフェース・チャネル 0 を制御するレジスタ225シリアル・インタフェース・チャネル 0 の動作23213.4.1動作停止モード23213.4.23 線式シリアルI/Oモードの動作23213.4.3SBIモードの動作23713.4.42 線式シリアルI/Oモードの動作26713.4.5SCKO/P27端子出力の操作272シリアル・インタフェース・チャネル1273                            |

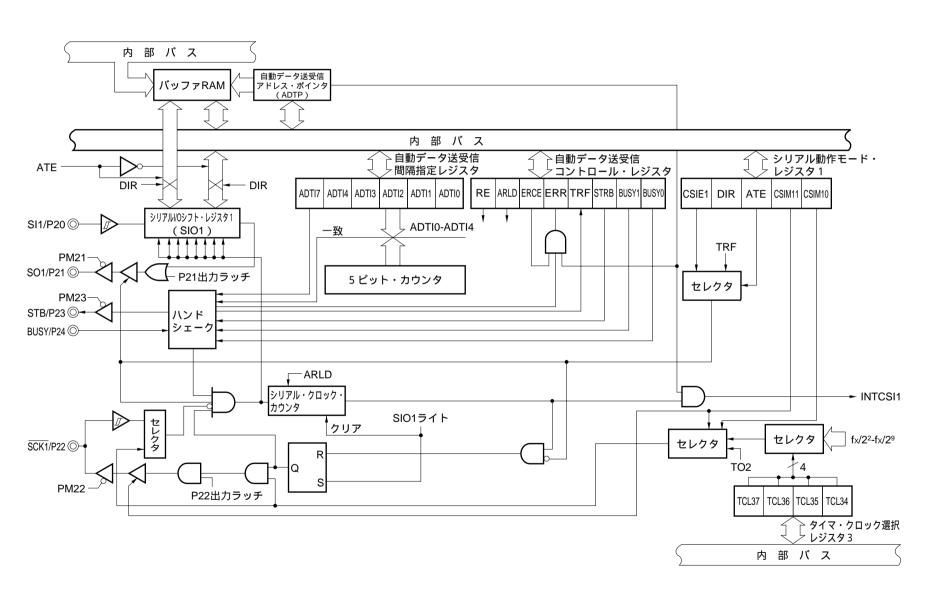

| 13. <b>2</b><br>13. <b>3</b><br>13. <b>4</b><br>4章<br>14. <b>1</b><br>14. <b>2</b>                 | シリアル・インタフェース・チャネル 0 の構成221シリアル・インタフェース・チャネル 0 を制御するレジスタ23213.4.1動作停止モード23213.4.23線式シリアルI/Oモードの動作23213.4.3SBIモードの動作23713.4.42線式シリアルI/Oモードの動作26713.4.5SCKO/P27端子出力の操作272シリアル・インタフェース・チャネル 1273シリアル・インタフェース・チャネル 1 の機能273                             |

| 13. <b>2</b><br>13. <b>3</b><br>13. <b>4</b><br>4章<br>14. <b>1</b><br>14. <b>2</b><br>14. <b>3</b> | シリアル・インタフェース・チャネル 0 の構成221シリアル・インタフェース・チャネル 0 を制御するレジスタ23213.4.1動作停止モード23213.4.23 線式シリアルI/Oモードの動作23213.4.3SBIモードの動作23713.4.42 線式シリアルI/Oモードの動作26713.4.5SCKO/P27端子出力の操作272シリアル・インタフェース・チャネル 1273シリアル・インタフェース・チャネル 1 の機能273シリアル・インタフェース・チャネル 1 の構成274 |

|                                                                                                    | 9.4<br>0章<br>10.1<br>10.2<br>10.3<br>1章<br>11.1<br>11.2<br>11.3<br>2章<br>12.1<br>12.2<br>12.3<br>12.4                                                                                                                                              |

|                                                                              | 14.4.2 3 線式シリアルI/Oモードの動作 286<br>14.4.3 自動送受信機能付き 3 線式シリアルI/Oモードの動作                                                                                                                                                                                           | 290 |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>^</b> ~~ →                                                                |                                                                                                                                                                                                                                                              |     |

| 第15草                                                                         | <b>割り込み機能とテスト機能</b> 319                                                                                                                                                                                                                                      |     |

|                                                                              | <b>割り込み機能の種類</b> 319                                                                                                                                                                                                                                         |     |

|                                                                              | 割り込み要因と構成 319                                                                                                                                                                                                                                                |     |