# RZ/N1D Group, RZ/N1S Group, RZ/N1L Group

User's Manual: System Control and Peripheral

RZ Family RZ/N Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### **Notice**

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products

and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your

product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of

these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="https://www.renesas.com/contact/">www.renesas.com/contact/</a>.

# General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

- 1. Precaution against Electrostatic Discharge (ESD)

- A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

- 2. Processing at power-on

- The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

- Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements.

Follow the guideline for input signal during power-off state as described in your product documentation.

- 4. Handling of unused pins

- Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

- 5. Clock signals

- After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

- 6. Voltage application waveform at input pin

- Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

- 7. Prohibition of access to reserved addresses

- Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

- 8. Differences between products

- Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

# How to Use This Manual

# 1. Objective and Target Users

This manual was written to explain the hardware functions and electrical characteristics of this LSI to the target users, i.e. those who will be using this LSI in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logic circuits, and microcomputers.

This manual is organized in the following items: an overview of the product, descriptions of the CPU, system control functions, and peripheral functions, electrical characteristics of the device, and usage notes.

When designing an application system that includes this LSI, take all points to note into account.

Points to note are given in their contexts and at the final part of each section, and in the section giving usage notes.

The list of revisions is a summary of major points of revision or addition for earlier versions. It does not cover all revised items. For details on the revised points, see the actual locations in the manual.

The following documents have been prepared for reference.

#### ■ Documents related to RZ/N1

| Document Name                                                                                                                    | Document Number                  |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group DATASHEET                                                                               | R01DS0323EJ****                  |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: System Introduction, Multiplexing, Electrical and Mechanical Information | R01UH0750EJ****                  |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: System Control and Peripheral                                            | R01UH0751EJ****<br>(this manual) |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: Peripherals                                                              | R01UH0752EJ****                  |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: R-IN Engine and Ethernet Peripherals                                     | R01UH0753EJ****                  |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: PWMTimer                                                                 | R01UH0913EJ****                  |

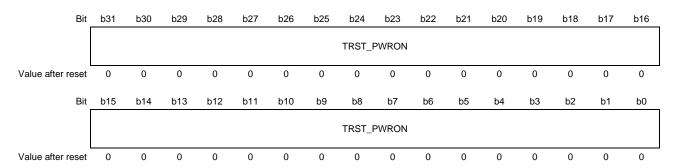

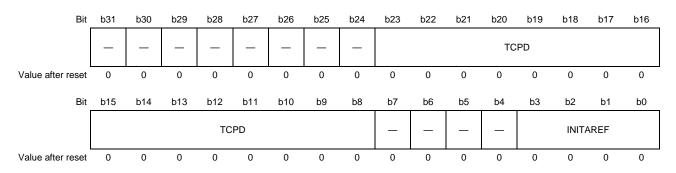

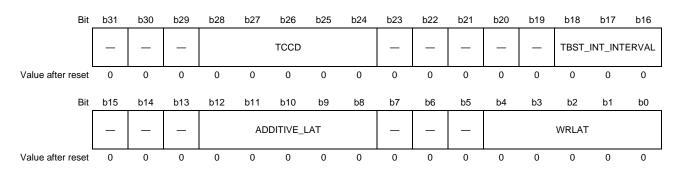

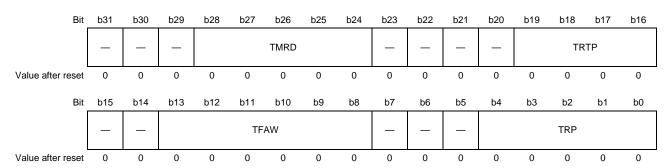

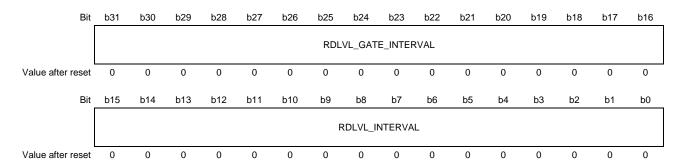

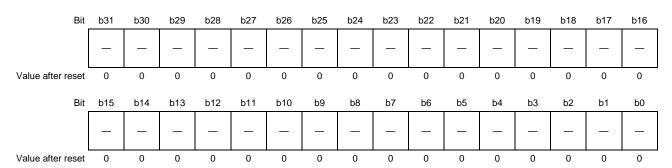

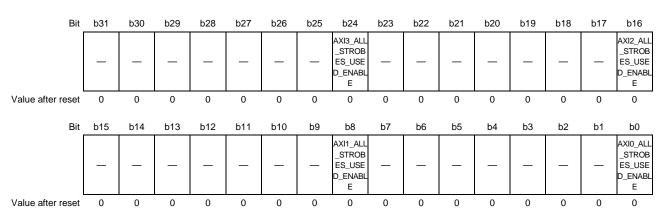

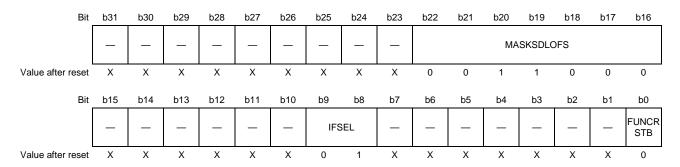

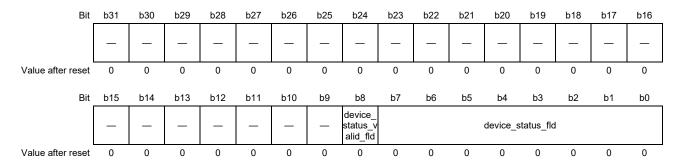

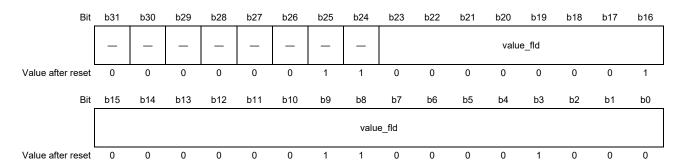

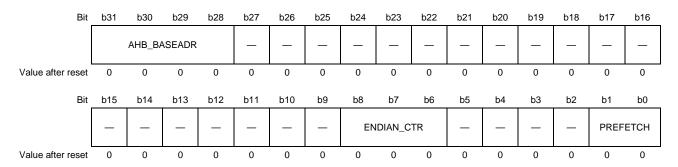

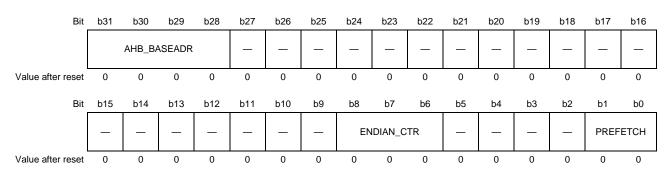

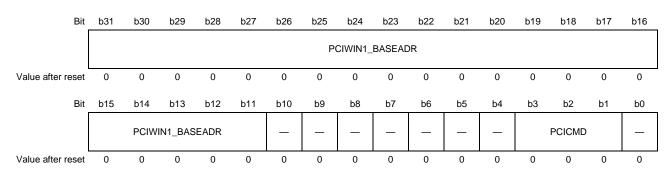

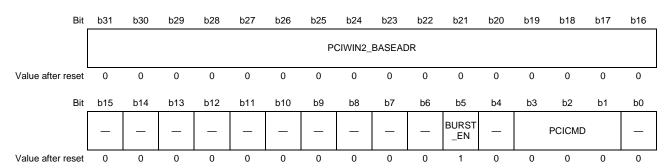

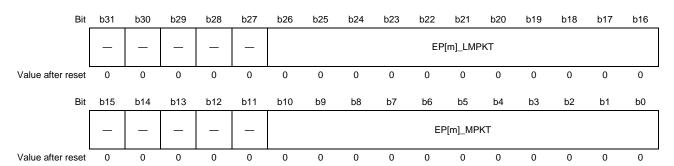

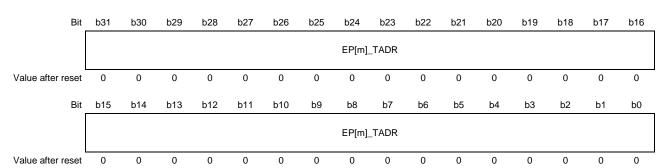

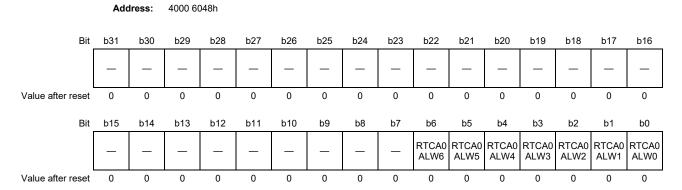

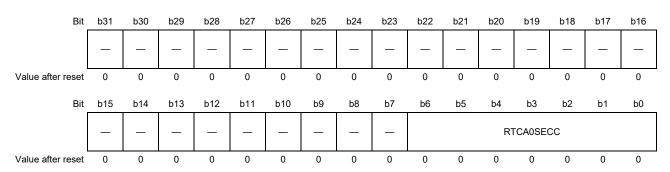

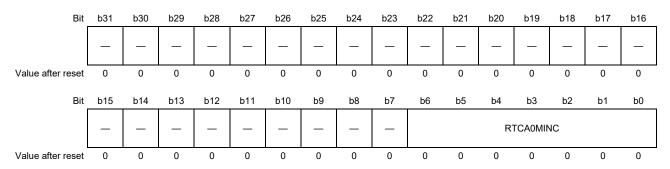

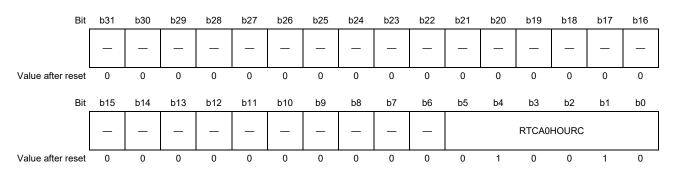

# 2. Description of Registers

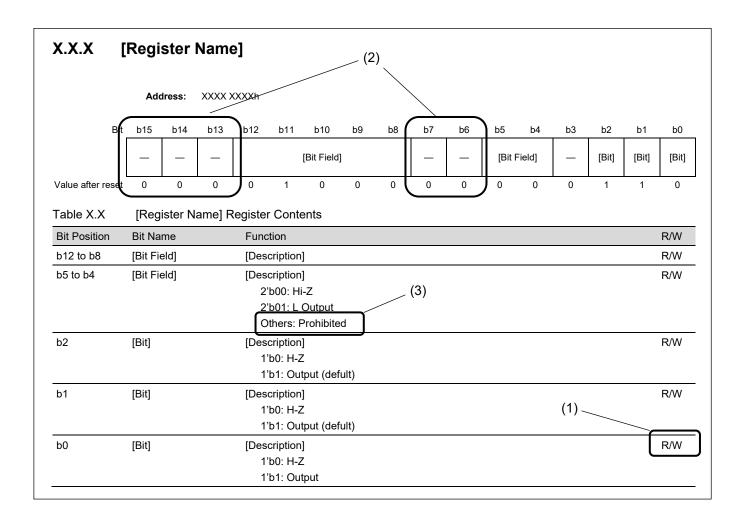

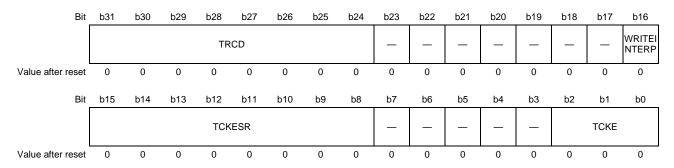

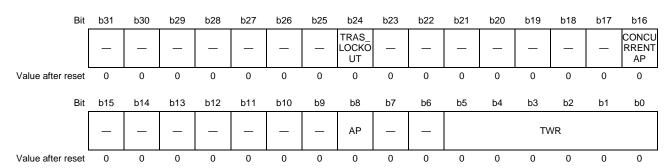

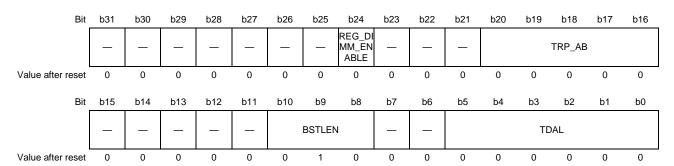

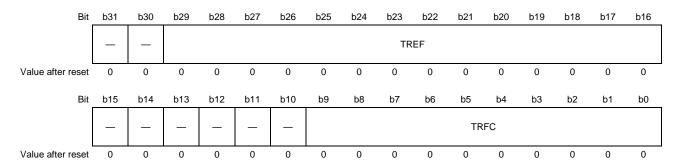

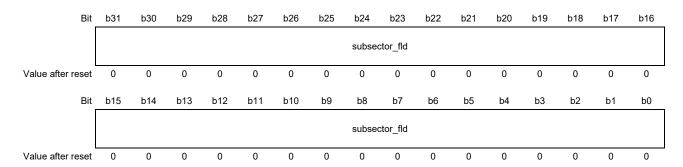

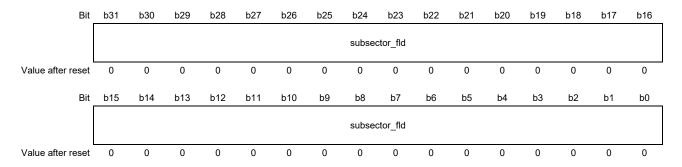

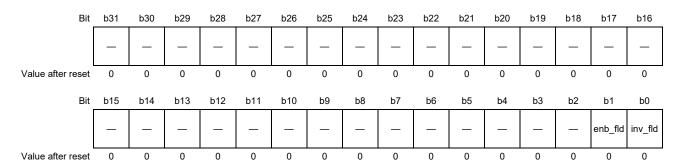

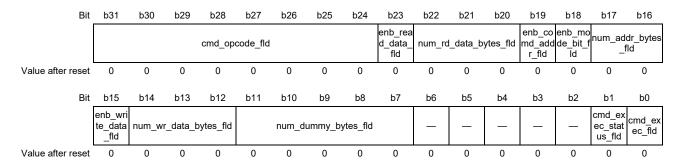

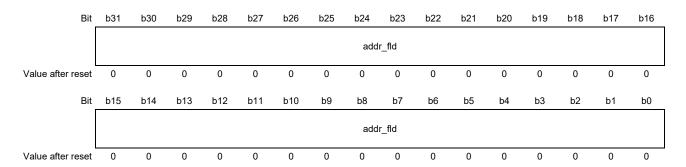

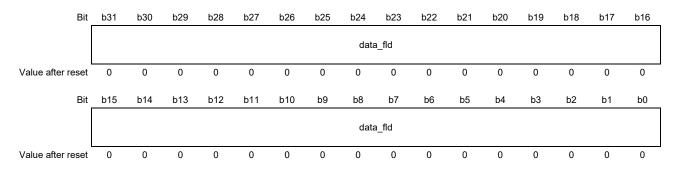

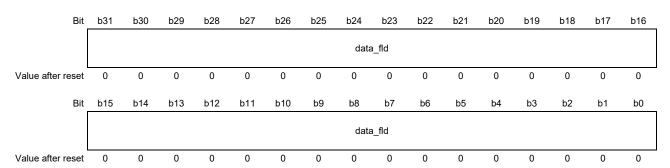

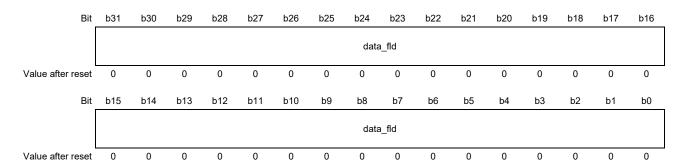

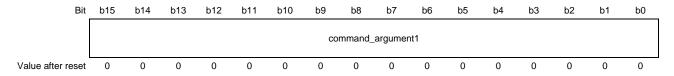

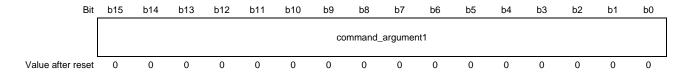

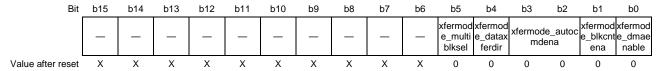

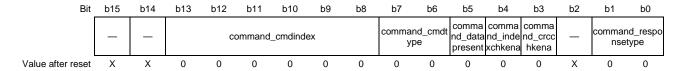

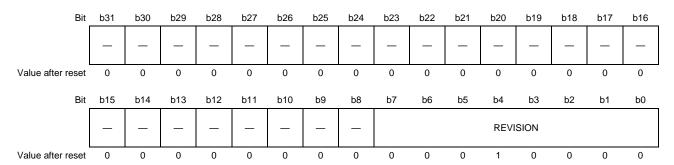

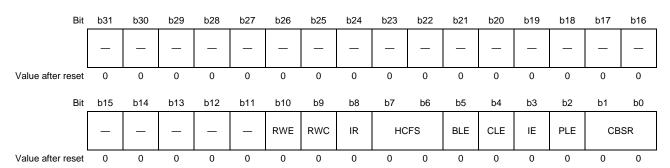

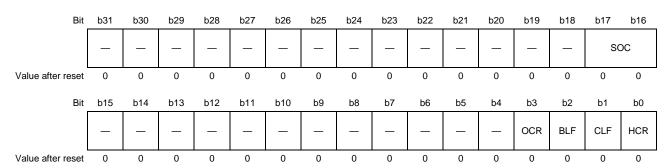

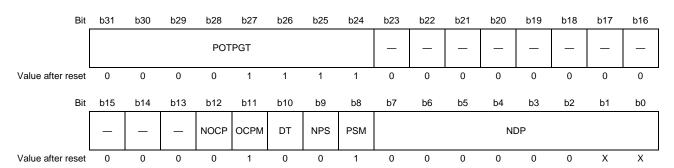

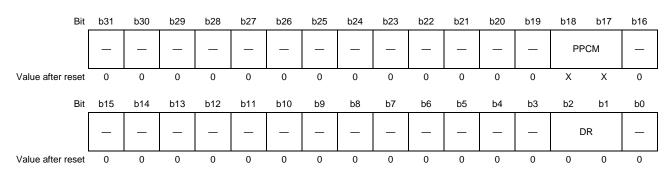

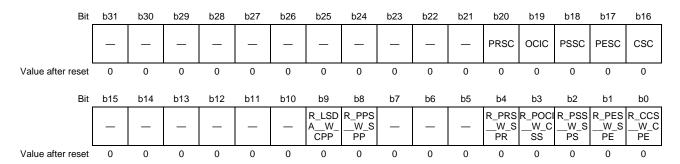

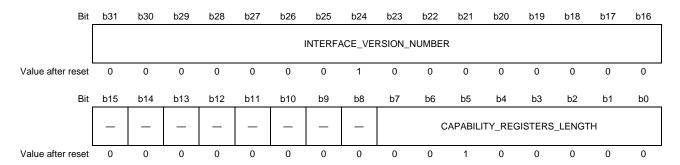

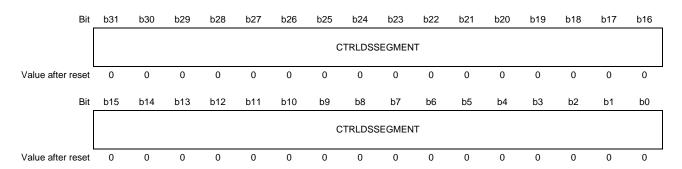

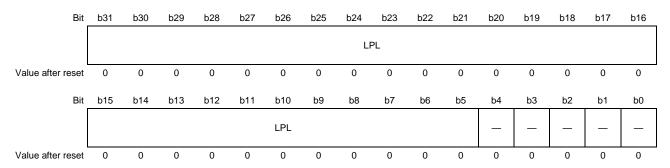

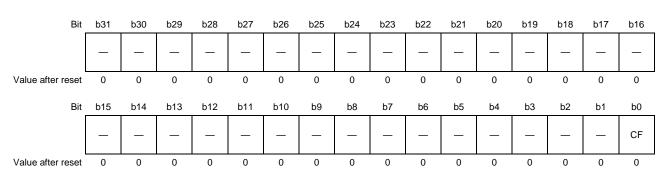

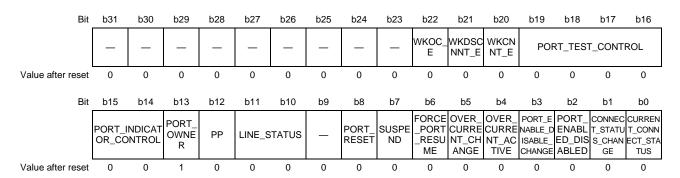

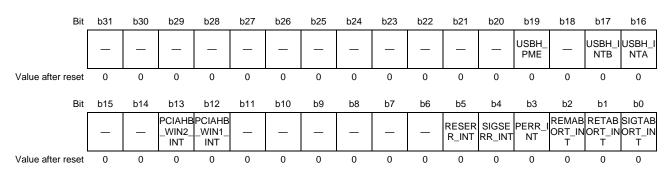

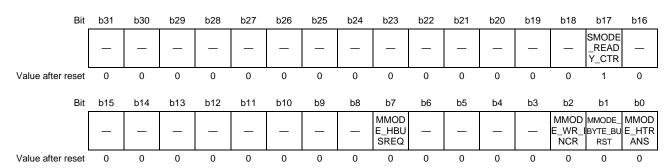

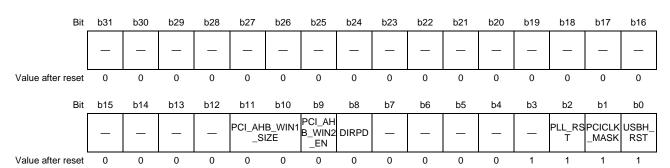

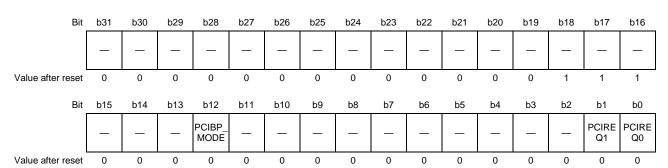

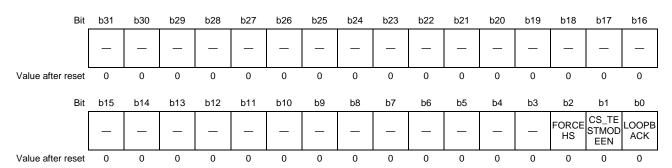

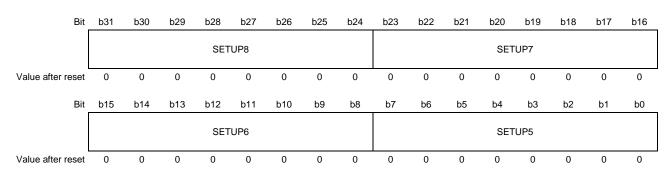

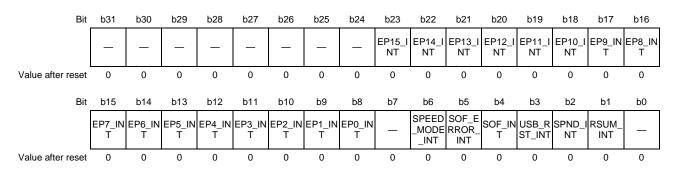

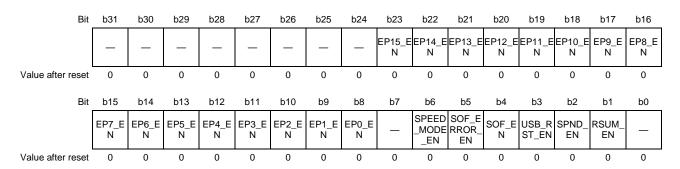

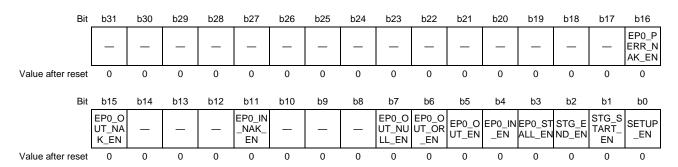

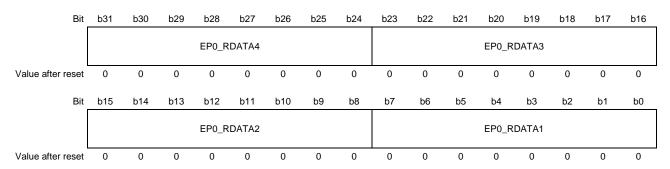

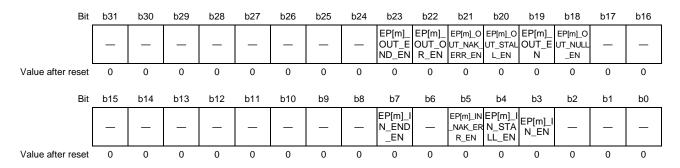

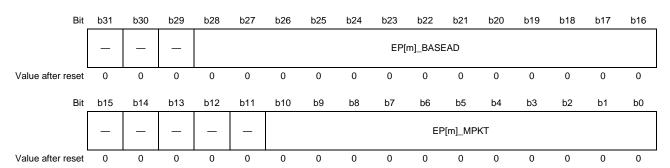

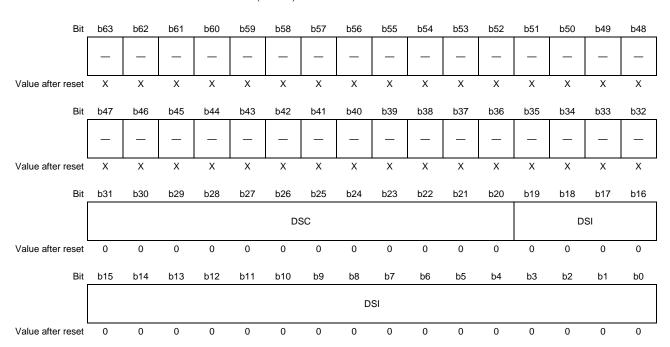

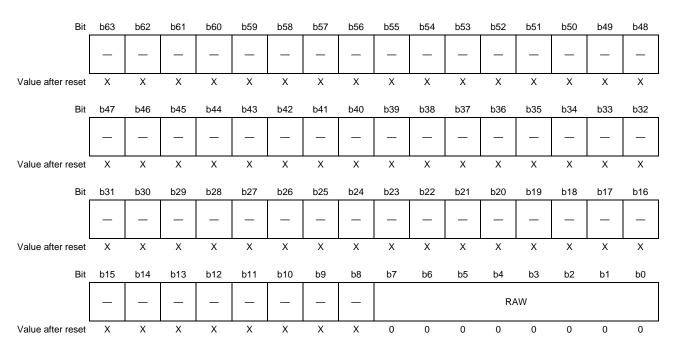

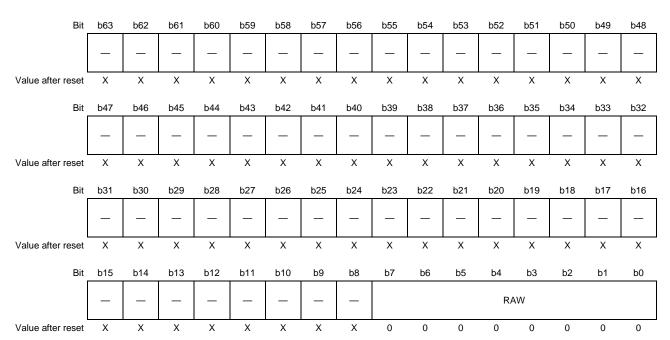

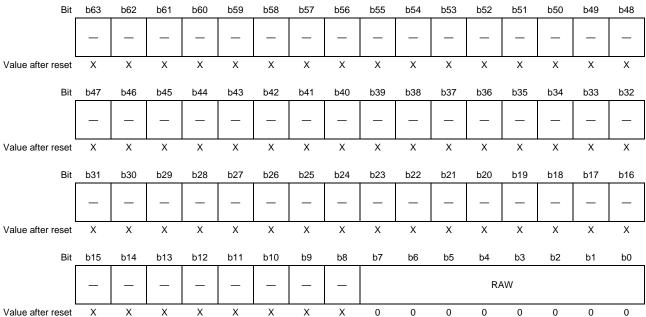

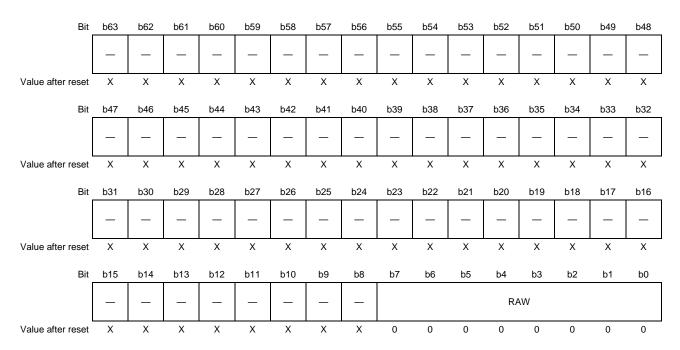

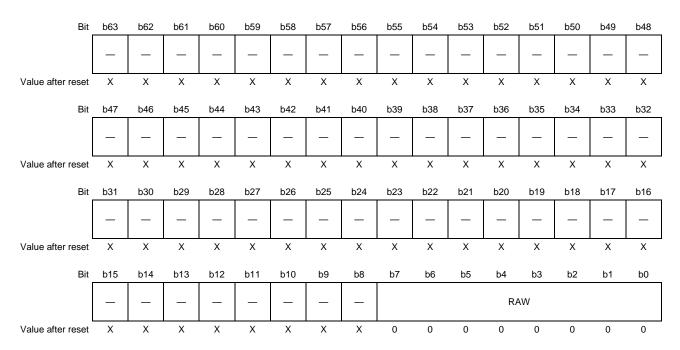

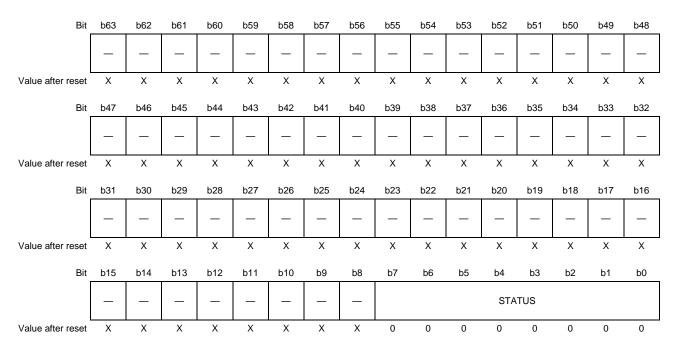

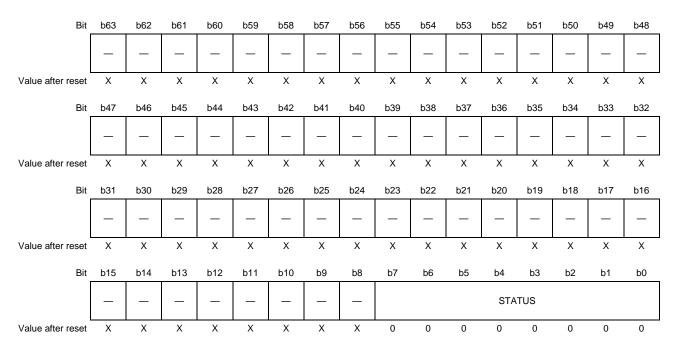

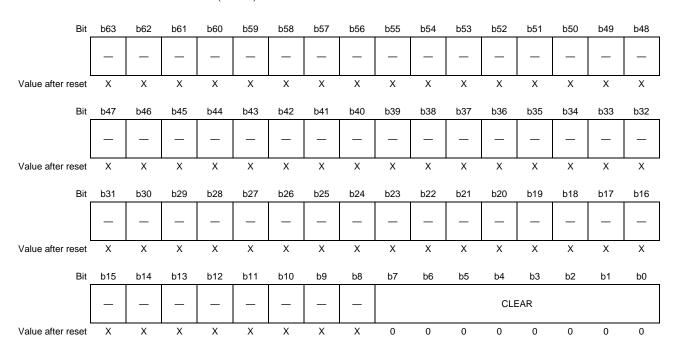

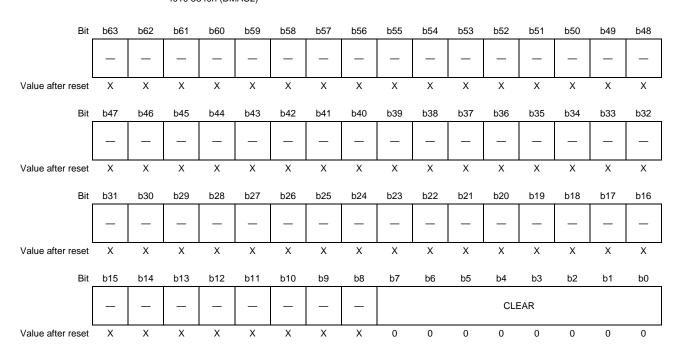

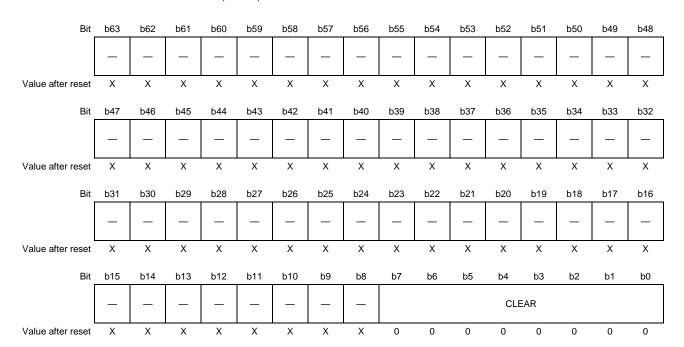

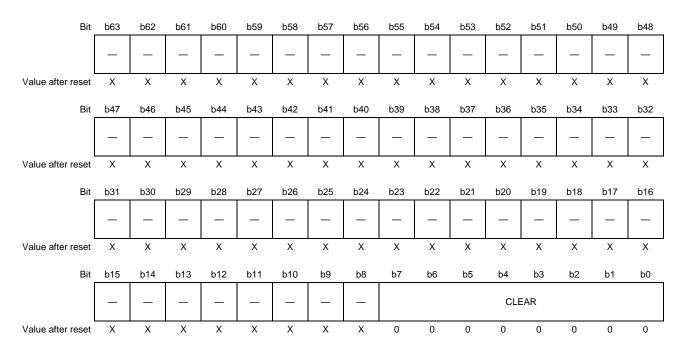

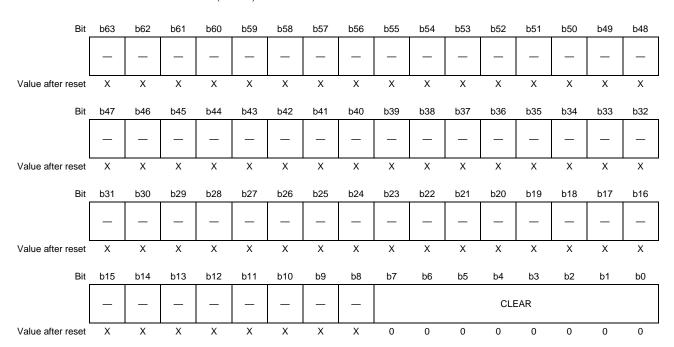

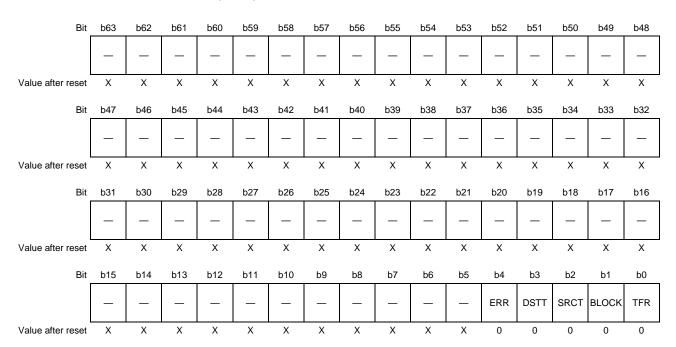

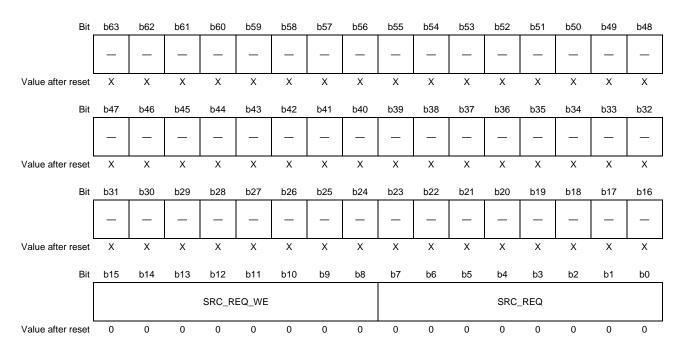

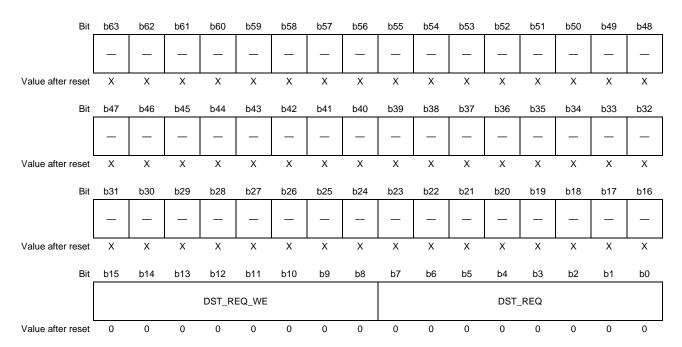

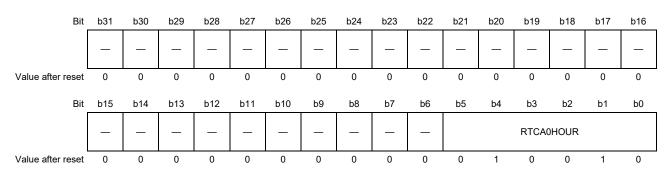

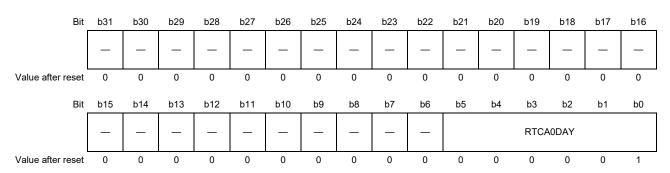

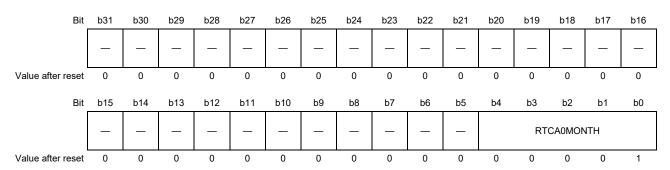

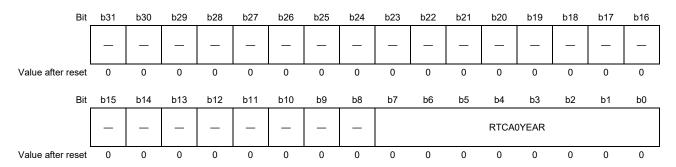

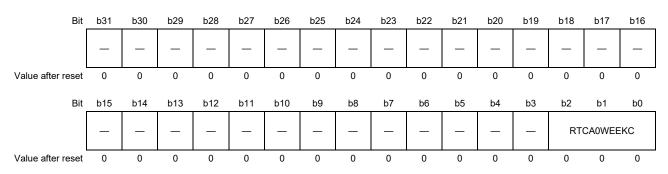

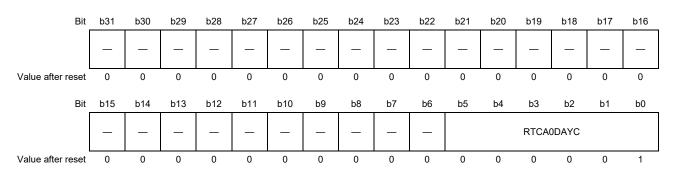

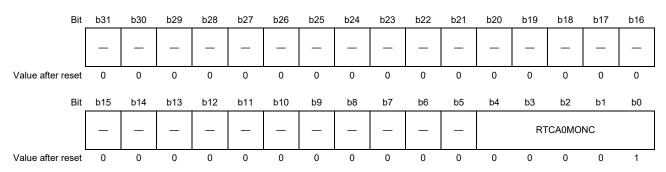

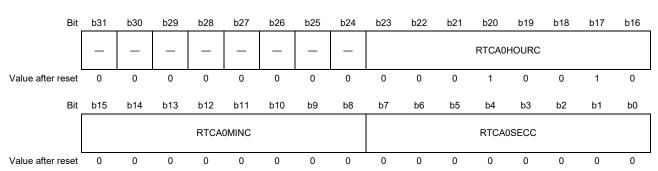

Each register description includes a bit chart, illustrating the arrangement of bits, and a table of bits, describing the meanings of the bit settings. The standard format and notation for bit charts and tables are described below.

(1) R/W: The bit or field is readable and writable.

R/(W): The bit or field is readable and writable. However, writing to this bit or field has some limitations. For details on the limitations, see the description or notes of respective registers.

R: The bit or field is readable. Writing to this bit or field has no effect.

W: The bit or field is writable. Reading to this bit or field is not guaranteed.

- (2) Reserved. Make sure to use the specified value when writing to this bit or field; otherwise, the correct operation is not guaranteed.

- (3) Setting prohibited. The correct operation is not guaranteed if such a setting is performed.

# 3. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                   |

|--------------|---------------------------------------------|

| AHB          | Arm Advanced High-performance Bus           |

| APB          | Arm Advanced Peripheral Bus                 |

| AXI          | Arm Advanced eXtensible Interface           |

| bps          | bits per second                             |

| CA7          | Arm Cortex-A7 module                        |

| CM3          | Arm Cortex-M3 module                        |

| CRC          | Cyclic Redundancy Check                     |

| DMA          | Direct Memory Access                        |

| DMAC         | Direct Memory Access Controller             |

| Hi-Z         | High Impedance                              |

| HSR          | High-availability Seamless Redundancy       |

| HW-RTOS      | Hard Ware Real Time OS                      |

| I/O          | Input/Output                                |

| INTC         | Interrupt Controller                        |

| LSB          | Least Significant Bit                       |

| MSB          | Most Significant Bit                        |

| NC           | Non-Connect                                 |

| NoC          | Network-on-Chip                             |

| PLL          | Phase Locked Loop                           |

| PWM          | Pulse Width Modulation                      |

| UART         | Universal Asynchronous Receiver/Transmitter |

| OTP          | One Time Programmable                       |

| PTP          | Precision Time Protocol                     |

| PRP          | Parallel Redundancy Protocol                |

| SoC          | System On Chip                              |

# 4. Description of the Access Size

Access size:

8 bits = Byte

16 bits = Halfword

32 bits = Word

# **Table of Contents**

| Section 1 Cl | PU                                                        | 26 |

|--------------|-----------------------------------------------------------|----|

| 1.1 Arm      | Cortex-A7                                                 | 26 |

| 1.1.1        | Overview                                                  | 26 |

| 1.1.2        | Usage Notes                                               | 27 |

| 1.2 Arm      | Cortex-M3                                                 | 28 |

| 1.2.1        | Overview                                                  | 28 |

| 1.2.2        | Signal Interface                                          | 28 |

| 1.2.3        | Usage Notes                                               | 28 |

| 1.           | 2.3.1 Restriction                                         | 28 |

| Section 2 No | etwork-On-Chip                                            | 29 |

| 2.1 Ove      | rview                                                     | 29 |

| 2.2 Fea      | tures                                                     | 29 |

| Section 3 2N | MB SRAM                                                   | 33 |

| 3.1 Ove      | rview                                                     | 33 |

| 3.2 Sigr     | nal Interfaces                                            | 33 |

| _            | ister Map                                                 |    |

| _            | ister Description                                         |    |

| 3.4.1        | RAMPCMD — RAM_SYS Protect Command Register                |    |

| 3.4.2        | RAMEDC — RAM_SYS ECC Decoder Config Register              |    |

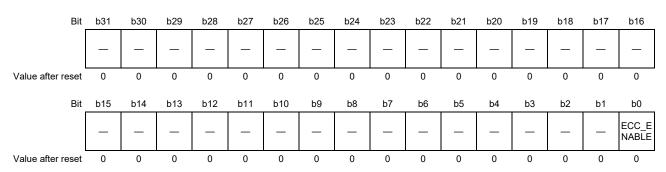

| 3.4.3        | RAMEEC — RAM_SYS ECC Encoder Config Register              |    |

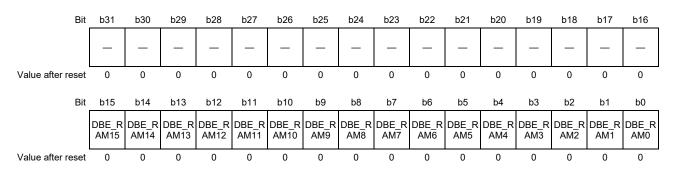

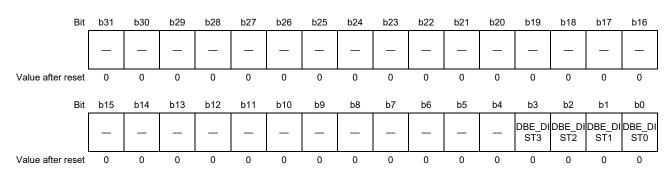

| 3.4.4        | RAMDBEST — RAM_SYS Double Bit ECC Error Status Register   | 38 |

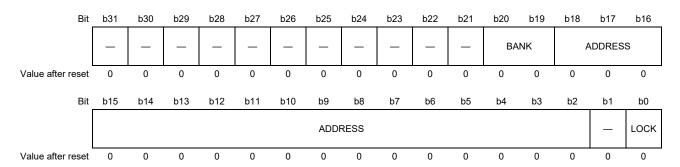

| 3.4.5        | RAMDBEAD — RAM_SYS Double Bit ECC Error Address Register  | 40 |

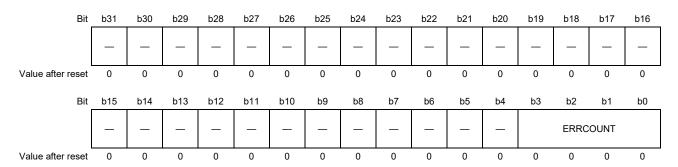

| 3.4.6        | RAMDBECNT — RAM_SYS Double Bit ECC Error Counter Register | 41 |

| 3.5 Ope      | eration                                                   | 42 |

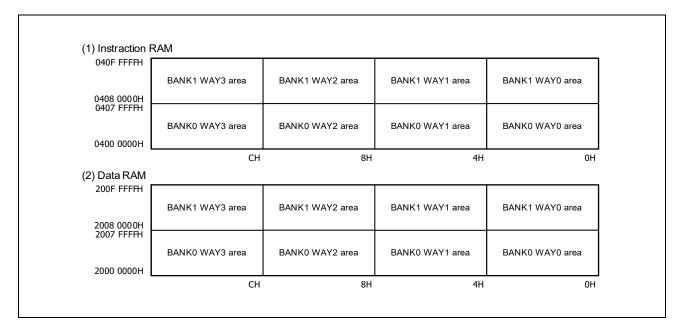

| 3.5.1        | Configuration of Memory Map                               | 42 |

| 3.5.2        | Initializing                                              | 42 |

| 3.5.3        | ECC Error Correction Function                             | 42 |

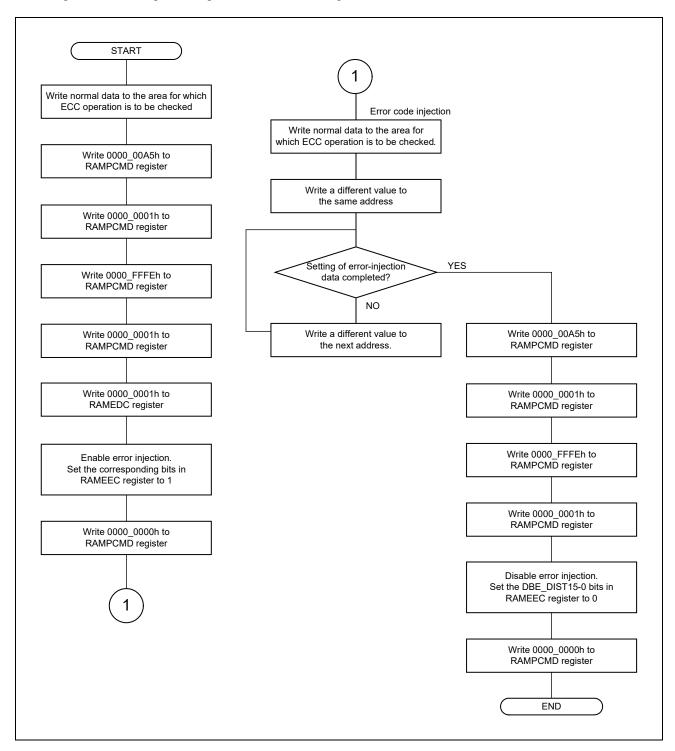

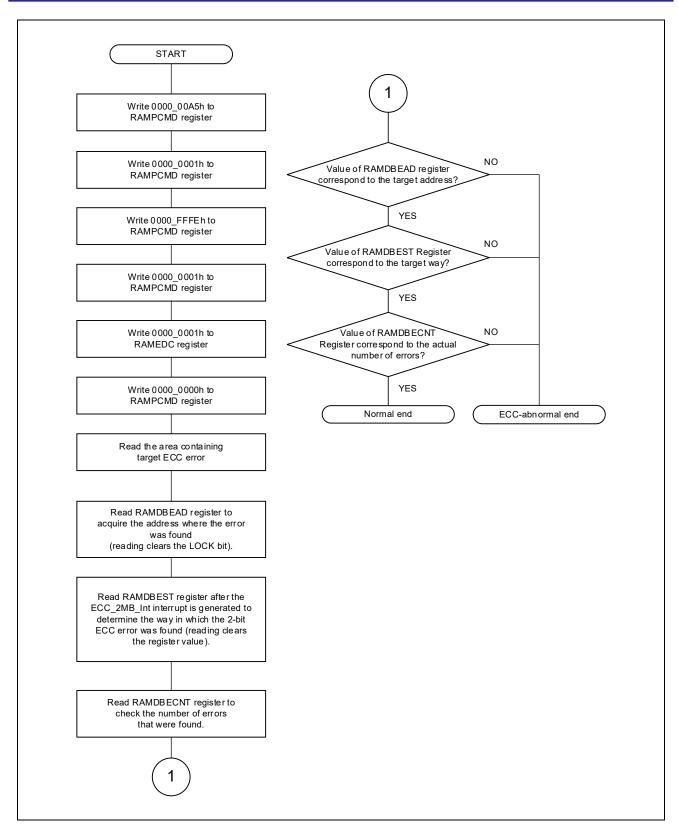

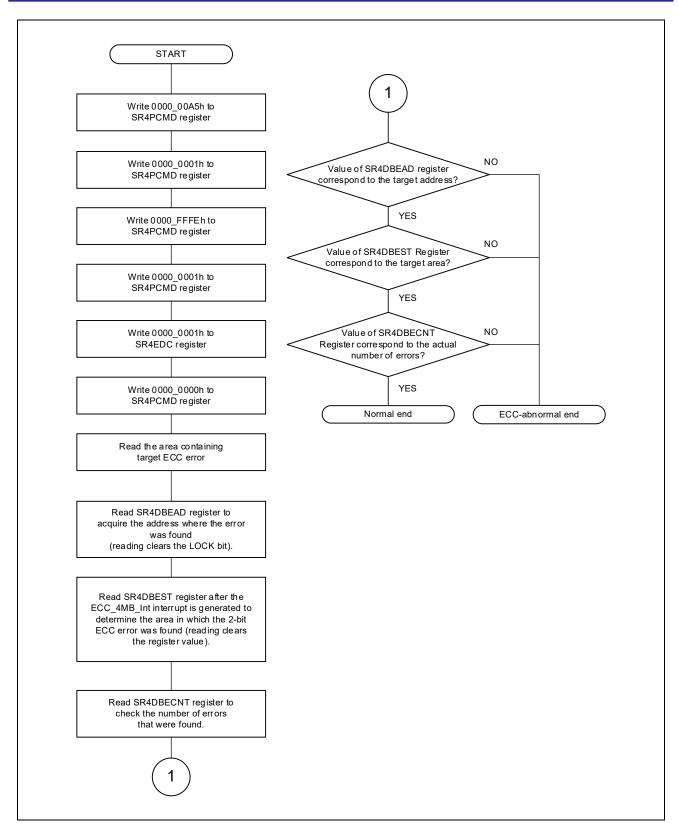

| 3.5.4        | Self-Testing of the ECC Circuit                           | 43 |

| 3.6 Usa      | ge Notes                                                  | 45 |

| 3.6.1        | Protect Command Register (RAMPCMD)                        | 45 |

| 3.6.2        | ECC Decoder Config Register (RAMEDC)                      | 45 |

| 3.6.3        | ECC Encoder Config Register (RAMEEC)                      | 46 |

| 3.6.4        | Double Bit ECC Error Status Register (RAMDBEST)           | 46 |

| 3.6.5        | Double Bit ECC Error Address Register (RAMDBEAD)          | 46 |

| 3.6.6        | Double Bit ECC Error Counter Register (RAMDBECNT)         | 46 |

| Section 4 4N | MB SRAM                                                   | 47 |

| 4.1 Ove      | rview                                                     | 47 |

| 4.2     | Signa   | al Interfaces                                              |    |  |  |  |  |

|---------|---------|------------------------------------------------------------|----|--|--|--|--|

| 4.3     | Regi    | gister Map                                                 |    |  |  |  |  |

| 4.4     | Regi    | ster Description                                           | 48 |  |  |  |  |

|         | 4.4.1   | SR4PCMD — SRAM 4MB Protect Command Register                | 48 |  |  |  |  |

|         | 4.4.2   | SR4EDC — SRAM 4MB ECC Decoder Config Register              | 48 |  |  |  |  |

|         | 4.4.3   | SR4EEC — SRAM 4MB ECC Encoder Config Register              | 49 |  |  |  |  |

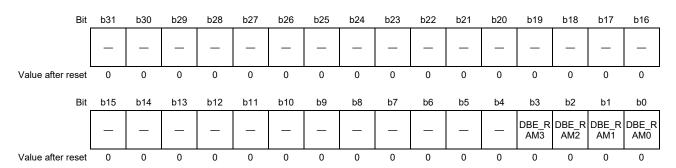

|         | 4.4.4   | SR4DBEST — SRAM 4MB Double Bit ECC Error Status Register   | 50 |  |  |  |  |

|         | 4.4.5   | SR4DBEAD — SRAM 4MB Double Bit ECC Error Address Register  | 51 |  |  |  |  |

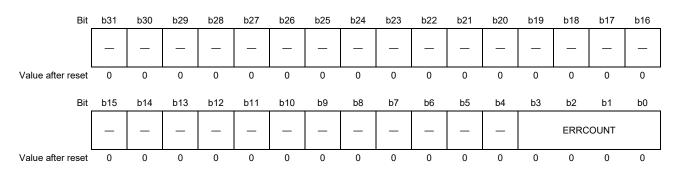

|         | 4.4.6   | SR4DBECNT — SRAM 4MB Double Bit ECC Error Counter Register | 51 |  |  |  |  |

| 4.5     | Oper    | ation                                                      | 52 |  |  |  |  |

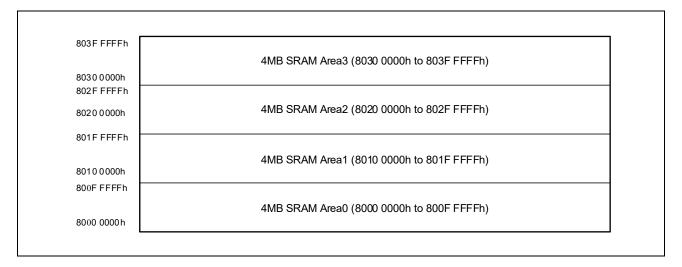

|         | 4.5.1   | Configuration of Memory Map                                | 52 |  |  |  |  |

|         | 4.5.2   | Initializing                                               | 52 |  |  |  |  |

|         | 4.5.3   | ECC Error Correction Function                              | 52 |  |  |  |  |

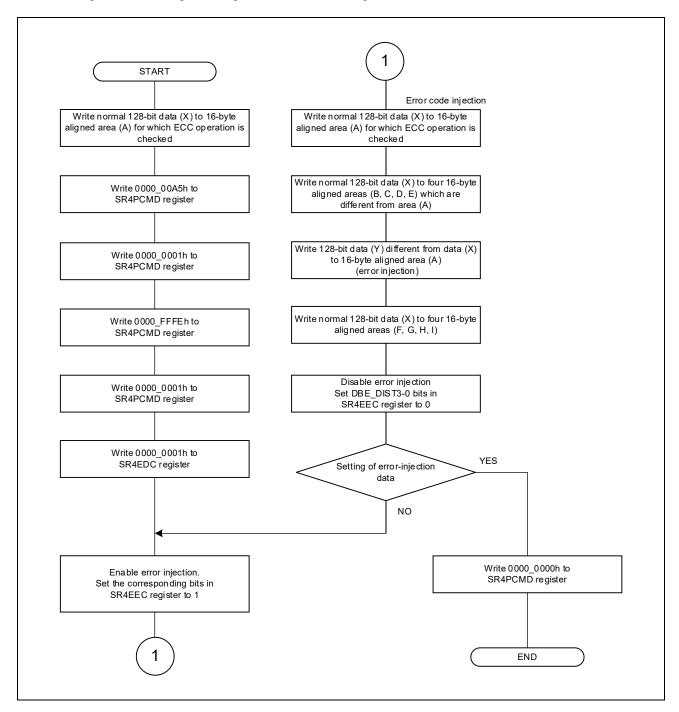

|         | 4.5.4   | Self-Testing of the ECC Circuit                            | 53 |  |  |  |  |

| 4.6     | Usag    | e Notes                                                    | 55 |  |  |  |  |

|         | 4.6.1   | SRAM 4MB Protect Command Register (SR4PCMD)                | 55 |  |  |  |  |

|         | 4.6.2   | SRAM 4MB ECC Decoder Config Register (SR4EDC)              | 55 |  |  |  |  |

|         | 4.6.3   | SRAM 4MB ECC Encoder Config Register (SR4EEC)              | 56 |  |  |  |  |

|         | 4.6.4   | SRAM 4MB Double Bit ECC Error Status Register (SR4DBEST)   | 56 |  |  |  |  |

|         | 4.6.5   | SRAM 4MB Double Bit ECC Error Address Register (SR4DBEAD)  | 56 |  |  |  |  |

|         | 4.6.6   | SRAM 4MB Double Bit ECC Error Counter Register (SR4DBECNT) | 56 |  |  |  |  |

| Sectio  | n 5 De  | bugging Interface                                          | 57 |  |  |  |  |

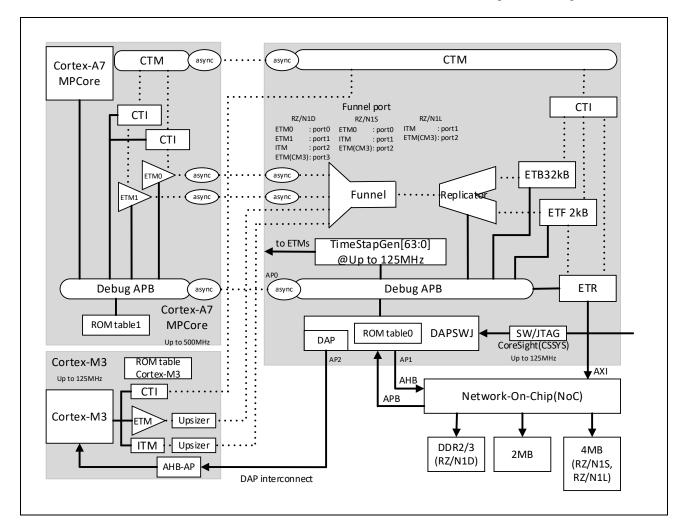

| 5.1     |         | view                                                       |    |  |  |  |  |

| 5.2     |         | 6 Interface                                                |    |  |  |  |  |

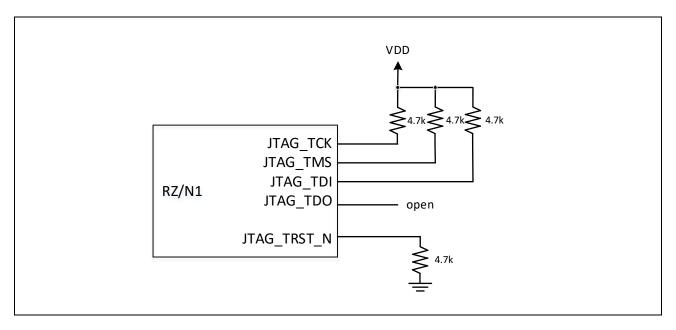

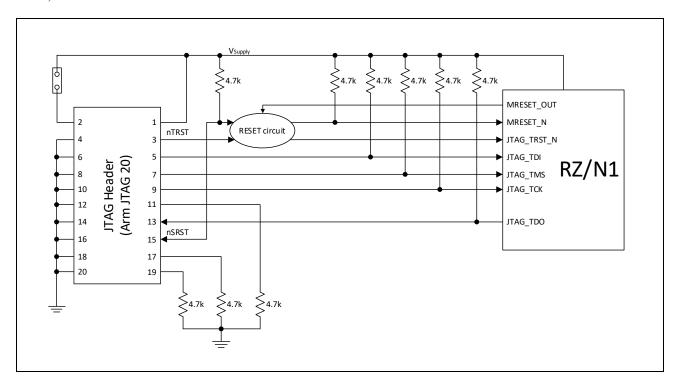

| 0.2     | 5.2.1   | Circuit Recommendation of JTAG Interface                   |    |  |  |  |  |

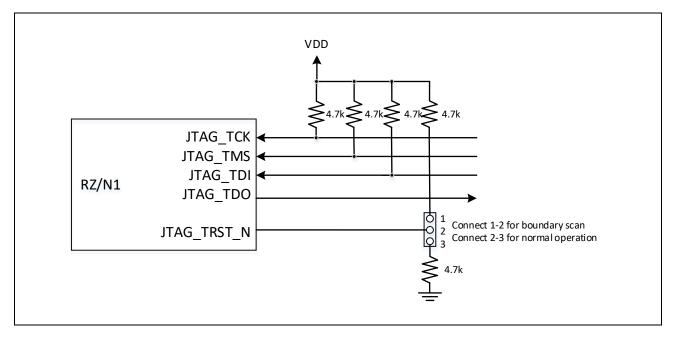

|         | 5.2.1   | Circuit Recommendation of JTAG-Debug Interface             |    |  |  |  |  |

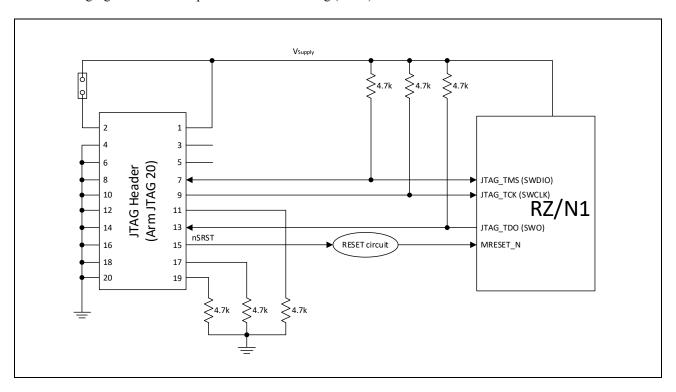

|         | 5.2.3   | Circuit Recommendation of Serial Wire Debug Interface      |    |  |  |  |  |

| 5.3     |         | t Considerations                                           |    |  |  |  |  |

| 5.5     | 5.3.1   | RZ/N1 Reset Signals                                        |    |  |  |  |  |

|         | 5.3.2   | Debugger Reset Signals                                     |    |  |  |  |  |

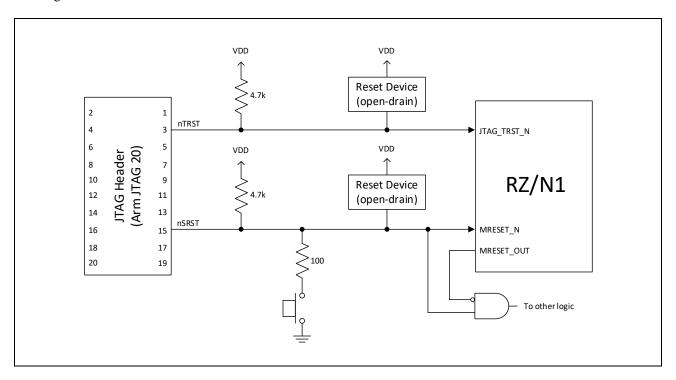

|         | 5.3.3   | Example Reset Circuit                                      |    |  |  |  |  |

|         |         | ·                                                          |    |  |  |  |  |

| Section | on 6 16 | DDR2/3 Controller                                          | 63 |  |  |  |  |

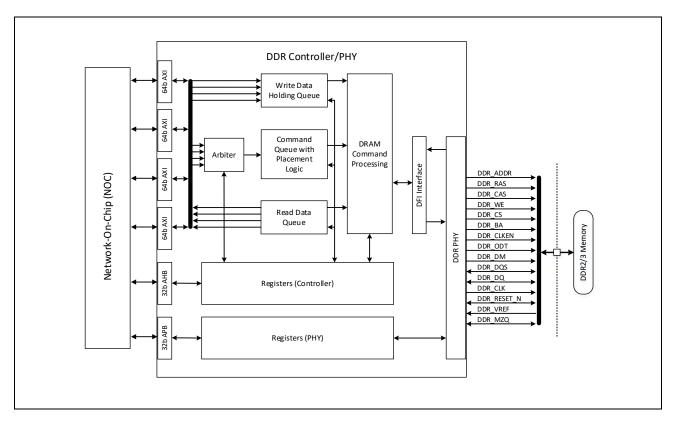

| 6.1     | Over    | view                                                       | 63 |  |  |  |  |

| 6.2     | Signa   | al Interfaces                                              | 65 |  |  |  |  |

| 6.3     | Regi    | ster Map                                                   | 66 |  |  |  |  |

|         | 6.3.1   | DDR Controller                                             | 66 |  |  |  |  |

|         | 6.3.2   | DDR PHY                                                    | 69 |  |  |  |  |

| 6.4     | Regi    | ster Description                                           | 70 |  |  |  |  |

|         | 6.4.1   | DDR Controller Register Description                        | 70 |  |  |  |  |

|         | 6.4     | .1.1 DDR_CTL_00 — DDR-Controller Status & Control 00       |    |  |  |  |  |

| 6.4.1.2  |                 |                    |             | l 01 |     |

|----------|-----------------|--------------------|-------------|------|-----|

| 6.4.1.3  | DDR_CTL_02 — DD | R-Controller Statu | ıs & Contro | l 02 | 71  |

| 6.4.1.4  | DDR_CTL_03 — DD | R-Controller Statu | ıs & Contro | l 03 | .72 |

| 6.4.1.5  |                 |                    |             | l 04 |     |

| 6.4.1.6  |                 |                    |             | l 05 |     |

| 6.4.1.7  |                 |                    |             | I 06 |     |

| 6.4.1.8  |                 |                    |             | l 07 |     |

| 6.4.1.9  |                 |                    |             | l 08 |     |

| 6.4.1.10 |                 |                    |             | l 09 |     |

| 6.4.1.11 |                 |                    |             | l 10 |     |

| 6.4.1.11 |                 |                    |             |      |     |

| -        |                 |                    |             | l 11 |     |

| 6.4.1.13 |                 |                    |             | l 12 |     |

| 6.4.1.14 |                 |                    |             | l 13 |     |

| 6.4.1.15 |                 |                    |             | l 14 |     |

| 6.4.1.16 |                 |                    |             | l 15 |     |

| 6.4.1.17 |                 |                    |             | I 16 |     |

| 6.4.1.18 |                 |                    |             | l 17 |     |

| 6.4.1.19 |                 |                    |             | l 18 |     |

| 6.4.1.20 | DDR_CTL_19 — DD | R-Controller Statu | is & Contro | l 19 | 81  |

| 6.4.1.21 | DDR_CTL_20 — DD | R-Controller Statu | is & Contro | l 20 | 81  |

| 6.4.1.22 | DDR CTL 21 — DD | R-Controller Statu | ıs & Contro | l 21 | .82 |

| 6.4.1.23 |                 |                    |             | l 22 |     |

| 6.4.1.24 |                 |                    |             | l 23 |     |

| 6.4.1.25 |                 |                    |             | l 24 |     |

| 6.4.1.26 |                 |                    |             | l 25 |     |

| 6.4.1.27 |                 |                    |             | I 26 |     |

| 6.4.1.28 |                 |                    |             | l 27 |     |

| 6.4.1.29 |                 |                    |             | l 28 |     |

| 6.4.1.30 |                 |                    |             | l 29 |     |

| 6.4.1.31 |                 |                    |             | l 30 |     |

|          |                 |                    |             | l 31 |     |

| 6.4.1.32 |                 |                    |             |      |     |

| 6.4.1.33 |                 |                    |             | l 32 |     |

| 6.4.1.34 |                 |                    |             | l 33 |     |

| 6.4.1.35 |                 |                    |             | I 34 |     |

| 6.4.1.36 |                 |                    |             | I 35 |     |

| 6.4.1.37 |                 |                    |             | I 36 |     |

| 6.4.1.38 |                 |                    |             | I 37 |     |

| 6.4.1.39 |                 |                    |             | I 38 |     |

| 6.4.1.40 |                 |                    |             | I 39 |     |

| 6.4.1.41 | DDR_CTL_40 — DD | R-Controller Statu | ıs & Contro | I 40 | 93  |

| 6.4.1.42 | DDR_CTL_41 — DD | R-Controller Statu | ıs & Contro | l 41 | 93  |

| 6.4.1.43 | DDR_CTL_42 — DD | R-Controller Statu | is & Contro | l 42 | 94  |

| 6.4.1.44 |                 |                    |             | l 43 |     |

| 6.4.1.45 |                 |                    |             | l 44 |     |

| 6.4.1.46 |                 |                    |             | l 45 |     |

| 6.4.1.47 |                 |                    |             | l 46 |     |

| 6.4.1.48 |                 |                    |             | l 47 |     |

| 6.4.1.49 |                 |                    |             | l 48 |     |

| 6.4.1.50 |                 |                    |             | l 49 |     |

|          |                 |                    |             |      |     |

| 6.4.1.51 |                 |                    |             | l 50 |     |

| 6.4.1.52 |                 |                    |             | l 51 |     |

| 6.4.1.53 | DDK_CTL_52 — DD | K-Controller Statu | is & Contro | l 52 | 100 |

| 6.4.1.55 | DDR_CTL_54 — DDR-Controller Status & Control 54                       | 102 |

|----------|-----------------------------------------------------------------------|-----|

| 6.4.1.56 | DDR_CTL_55 — DDR-Controller Status & Control 55                       |     |

| 6.4.1.57 | DDR_CTL_56 — DDR-Controller Status & Control 56                       |     |

| 6.4.1.58 | DDR_CTL_57 — DDR-Controller Status & Control 57                       |     |

| 6.4.1.59 | DDR_CTL_58 — DDR-Controller Status & Control 58                       |     |

| 6.4.1.60 | DDR_CTL_59 — DDR-Controller Status & Control 59                       |     |

| 6.4.1.61 | DDR_CTL_60 — DDR-Controller Status & Control 60                       |     |

| 6.4.1.62 | DDR_CTL_61 — DDR-Controller Status & Control 61                       |     |

| 6.4.1.63 | DDR_CTL_62 — DDR-Controller Status & Control 62                       |     |

| 6.4.1.64 | DDR CTL 63 — DDR-Controller Status & Control 63                       |     |

| 6.4.1.65 | DDR_CTL_64 — DDR-Controller Status & Control 64                       |     |

|          |                                                                       |     |

| 6.4.1.66 | DDR_CTL_65 — DDR-Controller Status & Control 65                       |     |

| 6.4.1.67 | DDR_CTL_66 — DDR-Controller Status & Control 66                       |     |

| 6.4.1.68 | DDR_CTL_67 — DDR-Controller Status & Control 67                       |     |

| 6.4.1.69 | DDR_CTL_68 — DDR-Controller Status & Control 68                       |     |

| 6.4.1.70 | DDR_CTL_69 — DDR-Controller Status & Control 69                       |     |

| 6.4.1.71 | DDR_CTL_70 — DDR-Controller Status & Control 70                       |     |

| 6.4.1.72 | DDR_CTL_71 — DDR-Controller Status & Control 71                       |     |

| 6.4.1.73 | DDR_CTL_72 — DDR-Controller Status & Control 72                       |     |

| 6.4.1.74 | DDR_CTL_73 — DDR-Controller Status & Control 73                       |     |

| 6.4.1.75 | DDR_CTL_74 — DDR-Controller Status & Control 74                       | 116 |

| 6.4.1.76 | DDR_CTL_75 — DDR-Controller Status & Control 75                       |     |

| 6.4.1.77 | DDR_CTL_76 — DDR-Controller Status & Control 76                       | 118 |

| 6.4.1.78 | DDR_CTL_77 — DDR-Controller Status & Control 77                       | 118 |

| 6.4.1.79 | DDR_CTL_78 — DDR-Controller Status & Control 78                       | 119 |

| 6.4.1.80 | DDR_CTL_79 — DDR-Controller Status & Control 79                       | 119 |

| 6.4.1.81 | DDR_CTL_80 — DDR-Controller Status & Control 80                       |     |

| 6.4.1.82 | DDR_CTL_81 — DDR-Controller Status & Control 81                       |     |

| 6.4.1.83 | DDR_CTL_82 — DDR-Controller Status & Control 82                       |     |

| 6.4.1.84 | DDR_CTL_83 — DDR-Controller Status & Control 83                       |     |

| 6.4.1.85 | DDR_CTL_84 — DDR-Controller Status & Control 84                       |     |

| 6.4.1.86 | DDR_CTL_85 — DDR-Controller Status & Control 85                       |     |

| 6.4.1.87 | DDR_CTL_86 — DDR-Controller Status & Control 86                       |     |

| 6.4.1.88 | DDR CTL 87 — DDR-Controller Status & Control 87                       |     |

| 6.4.1.89 | DDR_CTL_88 — DDR-Controller Status & Control 88                       |     |

| 6.4.1.90 | DDR_CTL_89 — DDR-Controller Status & Control 89                       |     |

| 6.4.1.91 | DDR_CTL_90 — DDR-Controller Status & Control 90                       |     |

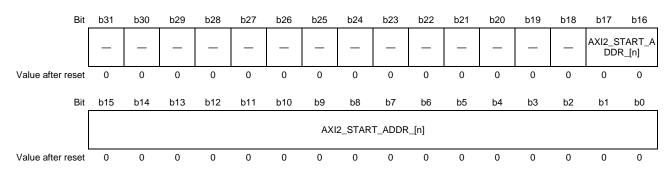

| 6.4.1.92 | DDR_CTL_[k] — Port0 Range[n] Start Address Setting Register (n = 015) | 120 |

| 0.4.1.92 | (k = 91 + n × 2)                                                      | 126 |

| 6 4 1 02 | DDR_CTL_[k] — Port0 Range[n] End Address Setting Register (n = 015)   | 120 |

| 6.4.1.93 |                                                                       | 407 |

| 0.4.4.04 | $(k = 92 + n \times 2)$                                               | 127 |

| 6.4.1.94 | DDR_CTL_[k] — Port1 Range[n] Start Address Setting Register (n = 015) | 407 |

|          | (k = 123 + n × 2)                                                     | 127 |

| 6.4.1.95 | DDR_CTL_[k] — Port1 Range[n] End Address Setting Register (n = 015)   |     |

|          | $(k = 124 + n \times 2)$                                              | 128 |

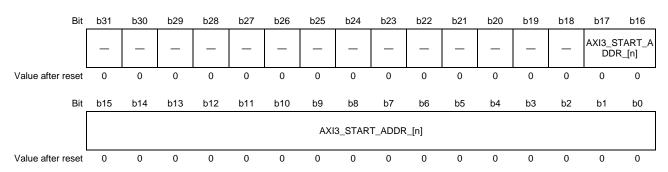

| 6.4.1.96 | DDR_CTL_[k] — Port2 Range[n] Start Address Setting Register (n = 015) |     |

|          | $(k = 155 + n \times 2)$                                              | 128 |

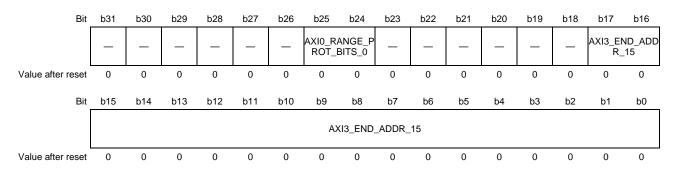

| 6.4.1.97 | DDR_CTL_[k] — Port2 Range[n] End Address Setting Register (n = 015)   |     |

|          | $(k = 156 + n \times 2)$                                              | 129 |

| 6.4.1.98 | DDR_CTL_[k] — Port3 Range[n] Start Address Setting Register (n = 015) |     |

|          | (k = 187 + n × 2)                                                     | 129 |

| 6.4.1.99 | DDR_CTL_[k] — Port3 Range[n] End Address Setting Register (n = 014)   |     |

|          | (k = 188 + n × 2)                                                     | 130 |

|          |                                                                       |     |

|           | DDR_CTL_218 — Port3 Range15 End Address Setting Register                                                                | 130 |

|-----------|-------------------------------------------------------------------------------------------------------------------------|-----|

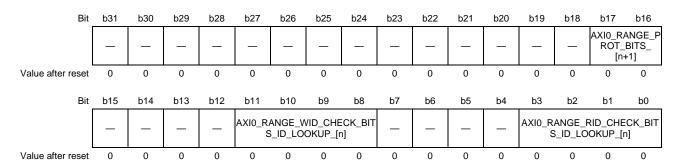

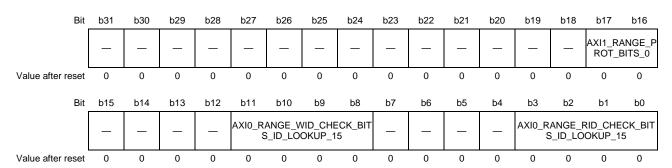

| 6.4.1.101 | DDR_CTL_[k] — Port0 Range[n] Protect Setting Register1 (n = 015)                                                        |     |

|           | $(k = 219 + n \times 2)$                                                                                                | 131 |

| 6.4.1.102 | DDR_CTL_[k] — Port0 Range[n] Protect Setting Register2 (n = 014)                                                        |     |

|           | $(k = 220 + n \times 2)$                                                                                                |     |

| 6.4.1.103 | DDR_CTL_250 — Port0 Range15 Protect Setting Register2                                                                   | 133 |

| 6.4.1.104 | DDR_CTL_[k] — Port1 Range[n] Protect Setting Register1 (n = 015)                                                        |     |

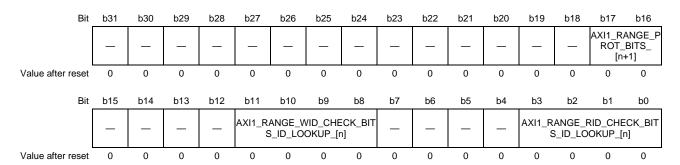

|           | $(k = 251 + n \times 2)$                                                                                                | 134 |

| 6.4.1.105 | DDR_CTL_[k] — Port1 Range[n] Protect Setting Register2 (n = 014)                                                        | 405 |

| 0.4.4.400 | $(k = 252 + n \times 2)$                                                                                                |     |

| 6.4.1.106 | DDR_CTL_282 — Port1 Range15 Protect Setting Register2                                                                   | 136 |

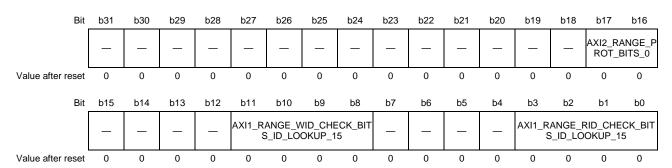

| 6.4.1.107 | DDR_CTL_[k] — Port2 Range[n] Protect Setting Register1 (n = 015)                                                        | 407 |

| 0.4.4.400 | (k = 283 + n × 2)                                                                                                       | 137 |

| 6.4.1.108 | DDR_CTL_[k] — Port2 Range[n] Protect Setting Register2 (n = 014)                                                        | 420 |

| 6 4 4 400 | (k = 284 +n × 2)                                                                                                        |     |

| 6.4.1.109 | DDR_CTL_314 — Port2 Range15 Protect Setting Register2  DDR_CTL_[k] — Port3 Range[n] Protect Setting Register1 (n = 015) | 139 |

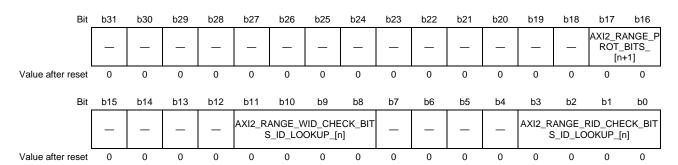

| 6.4.1.110 | (k = 315 + n × 2)                                                                                                       | 140 |

| 6.4.1.111 | DDR_CTL_[k] — Port3 Range[n] Protect Setting Register2 (n = 014)                                                        | 140 |

| 0.4.1.111 | (k = 316 + n × 2)                                                                                                       | 1/1 |

| 6.4.1.112 | DDR_CTL_346 — Port3 Range15 Protect Setting Register2                                                                   |     |

| 6.4.1.113 | DDR CTL 347 — DDR-Controller Status & Control 347                                                                       |     |

| 6.4.1.114 | DDR_CTL_348 — DDR-Controller Status & Control 348                                                                       |     |

| 6.4.1.115 | DDR_CTL_349 — DDR-Controller Status & Control 349                                                                       |     |

| 6.4.1.116 | DDR_CTL_350 — DDR-Controller Status & Control 350                                                                       |     |

| 6.4.1.117 | DDR CTL 351 — DDR-Controller Status & Control 351                                                                       |     |

| 6.4.1.118 | DDR_CTL_352 — DDR-Controller Status & Control 352                                                                       |     |

| 6.4.1.119 | DDR_CTL_353 — DDR-Controller Status & Control 353                                                                       |     |

| 6.4.1.120 | DDR_CTL_354 — DDR-Controller Status & Control 354                                                                       |     |

| 6.4.1.121 | DDR_CTL_355 — DDR-Controller Status & Control 355                                                                       |     |

| 6.4.1.122 | DDR CTL 356 — DDR-Controller Status & Control 356                                                                       |     |

| 6.4.1.123 | DDR_CTL_357 — DDR-Controller Status & Control 357                                                                       | 151 |

| 6.4.1.124 | DDR_CTL_358 — DDR-Controller Status & Control 358                                                                       | 152 |

| 6.4.1.125 | DDR_CTL_359 — DDR-Controller Status & Control 359                                                                       | 152 |

| 6.4.1.126 | DDR_CTL_360 — DDR-Controller Status & Control 360                                                                       | 153 |

| 6.4.1.127 | DDR_CTL_361 — DDR-Controller Status & Control 361                                                                       | 153 |

| 6.4.1.128 | DDR_CTL_362 — DDR-Controller Status & Control 362                                                                       | 154 |

| 6.4.1.129 | DDR_CTL_363 — DDR-Controller Status & Control 363                                                                       |     |

| 6.4.1.130 | DDR_CTL_364 — DDR-Controller Status & Control 364                                                                       |     |

| 6.4.1.131 | DDR_CTL_365 — DDR-Controller Status & Control 365                                                                       |     |

| 6.4.1.132 | DDR_CTL_366 — DDR-Controller Status & Control 366                                                                       |     |

|           | DDR_CTL_367 — DDR-Controller Status & Control 367                                                                       |     |

| 6.4.1.134 | <b>–</b> –                                                                                                              |     |

| 6.4.1.135 | DDR_CTL_369 — DDR-Controller Status & Control 369                                                                       |     |

| 6.4.1.136 | DDR_CTL_370 — DDR-Controller Status & Control 370                                                                       |     |

| 6.4.1.137 | DDR_CTL_371 — DDR-Controller Status & Control 371                                                                       |     |

| 6.4.1.138 | DDR_CTL_372 — DDR-Controller Status & Control 372                                                                       |     |

| 6.4.1.139 | DDR_CTL_373 — DDR-Controller Status & Control 373                                                                       |     |

| 6.4.1.140 | DDR_CTL_374 — DDR-Controller Status & Control 374                                                                       |     |

|           | PHY Register Description                                                                                                |     |

| 6.4.2.1   | FUNCCTRL — Function Control Register                                                                                    |     |

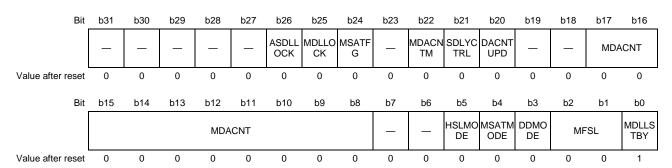

| 6.4.2.2   | DLLCTRL — MDLL Control Register                                                                                         |     |

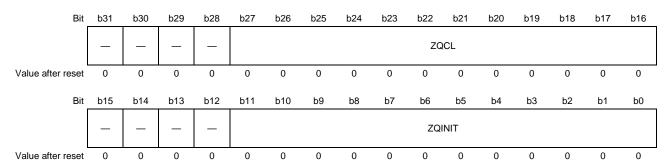

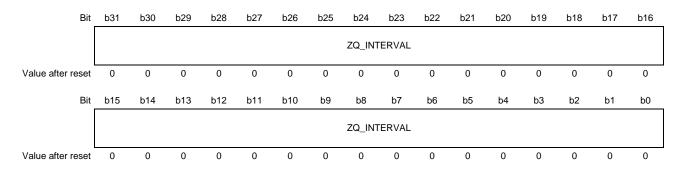

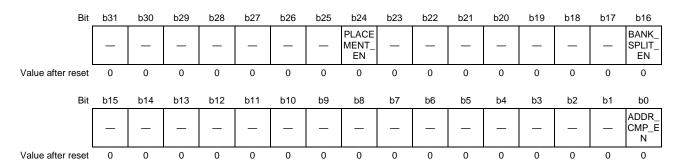

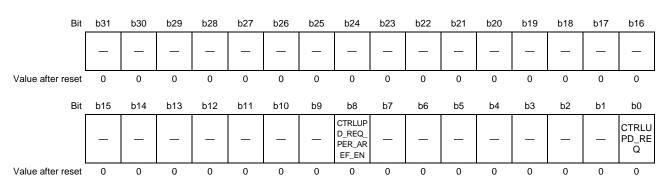

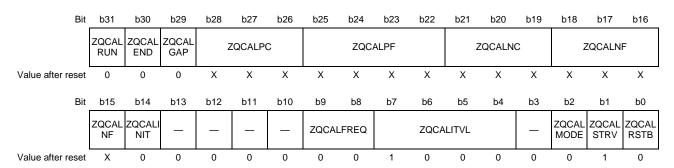

| 6.4.2.3   | ZQCALCTRL — ZQ Calibration Control Register                                                                             | 165 |

6.4

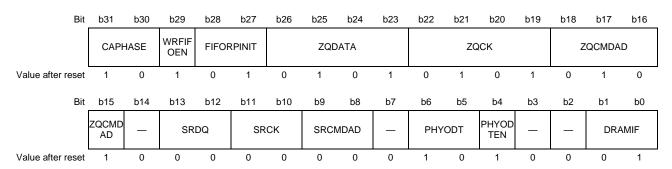

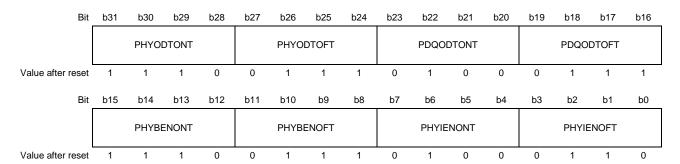

|              | 4.2.4         | ZQODTCTRL — ZQODT Control Register               |     |

|--------------|---------------|--------------------------------------------------|-----|

| 6.           | 4.2.5         | RDCTRL — Read Control Register                   |     |

|              | 4.2.6         | RDTMG — READ Timing Control Register             | 169 |

|              | 4.2.7         | FIFOINIT — FIFO Initialization Register          |     |

| 6.           | 4.2.8         | OUTCTRL — Output Control Register                |     |

| 6.           | 4.2.9         | WLCTRL1 — Write Leveling Control Register 1      | 172 |

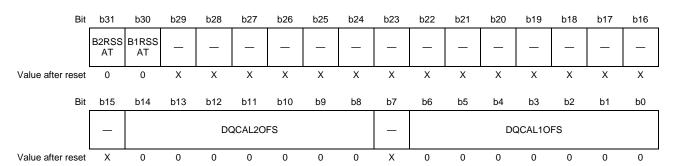

| 6.           | 4.2.10        | DQCALOFS1 — DQS Offset Setting                   | 173 |

| 6.5 Ope      | ration.       |                                                  | 174 |

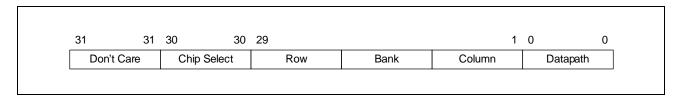

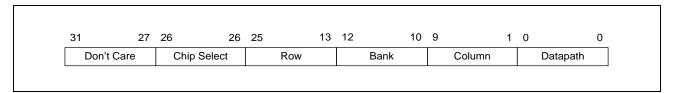

| 6.5.1        | Addı          | ress Mapping                                     | 174 |

| 6.           | 5.1.1         | DDR SDRAM Address Mapping Options                | 174 |

| 6.           | 5.1.2         | Maximum Address Space                            | 175 |

| 6.           | 5.1.3         | Memory Mapping to Address Space                  | 176 |

| 6.5.2        | AXI           | Interface Ports                                  | 177 |

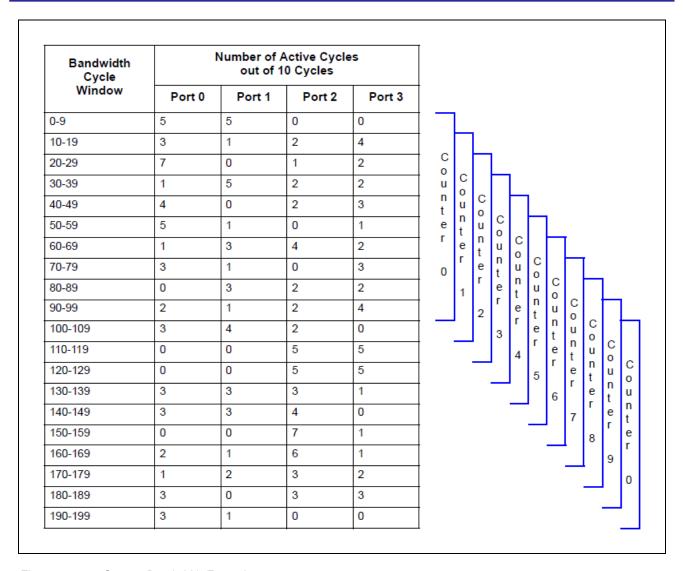

| 6.           | 5.2.1         | Arbitration Scheme                               |     |

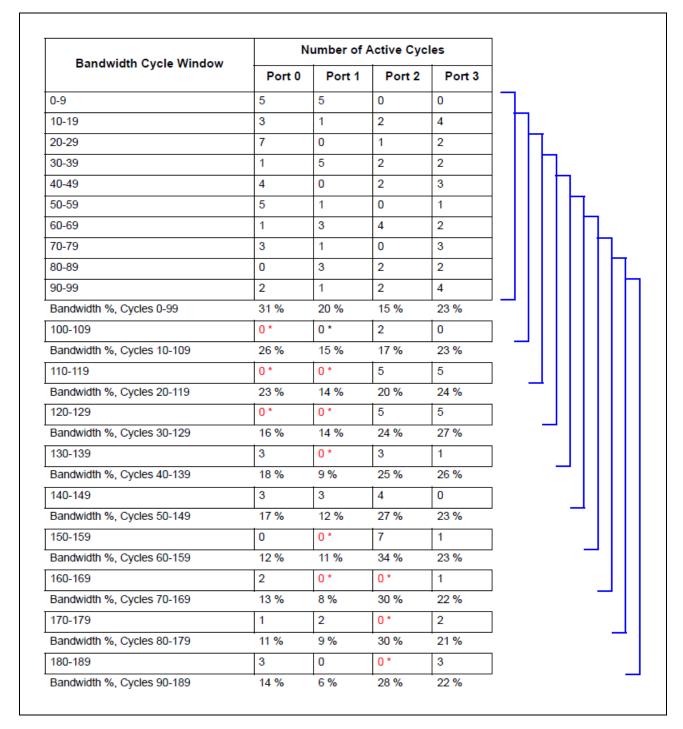

| 6.           | 5.2.2         | Understanding Round-Robin Arbitration            |     |

| 6.           | 5.2.3         | Understanding Port Priority                      |     |

| 6.           | 5.2.4         | Understanding Port Bandwidth                     |     |

| 6.           | 5.2.5         | Understanding Port Bandwidth Hold-Off            |     |

| 6.           | 5.2.6         | Understanding Port Bandwidth Overflow            |     |

| 6.           | 5.2.7         | Priority Round-Robin Arbitration Summary         |     |

| 6.           | 5.2.8         | Arbitration Examples                             |     |

| 6.           | 5.2.9         | Programming for Priority Round-Robin Arbitration | 189 |

| 6.5.3        | Port          | Protection Option                                | 190 |

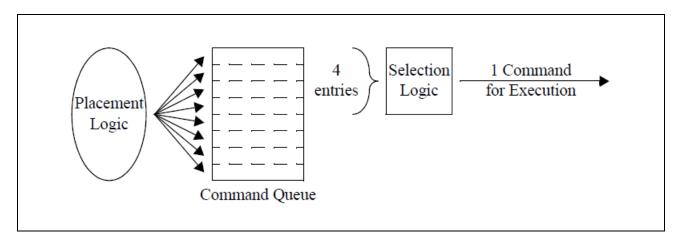

| 6.5.4        | Com           | nmand Queue with Placement Logic                 | 192 |

|              | 5.4.1         | Rules of the Placement Algorithm                 |     |

| _            | 5.4.2         | Command Execution Order After Placement          |     |

| _            | 5.4.3         | ACT Request Control                              |     |

| 6.5.5        |               | AM Command Processing                            |     |

| 6.5.6        |               | C Function                                       |     |

|              | 5.6.1         | ECC Error Types                                  |     |

|              | 5.6.2         | Features of the ECC Logic                        |     |

|              | 5.6.3         | ECC Control                                      |     |

|              | 5.6.4         | Syndromes                                        | 004 |

| 6.           | 5.6.5         | Command Processing when ECC is Enabled           |     |

| _            | 5.6.6         | ECC and Read Operations                          |     |

|              | 5.6.7         | ECC and Write Operations                         |     |

|              | 5.6.8         | Automatic ECC Corruption                         |     |

|              | 5.6.9         | Forcing an ECC Error Event                       |     |

|              | 5.6.10        | •                                                |     |

| 6.5.7        | Low           | Power Control Management                         |     |

|              | 5.7.1         | Low Power States                                 |     |

| 0.           | 5.7.2         | Management of the Low Power Control Module       |     |

|              | 5.7.3         | Software Programmable Interface                  |     |

|              | 5.7.4         | Automatic Interface                              |     |

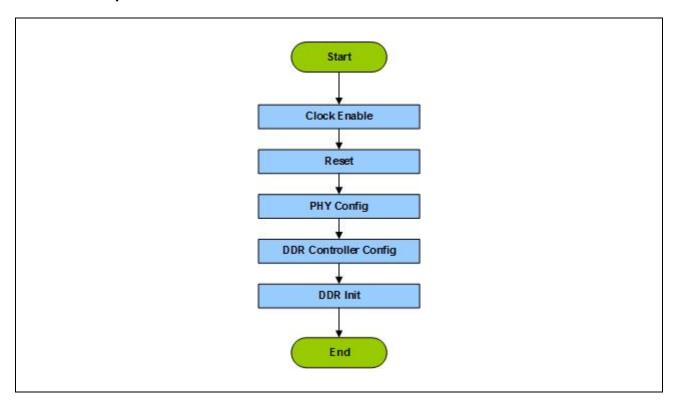

|              |               | es                                               |     |

|              | •             |                                                  |     |

| 6.6.1        |               | plified DDR Initialization                       |     |

| 6.6.2        | אטט           | R Initialization Example                         | 215 |

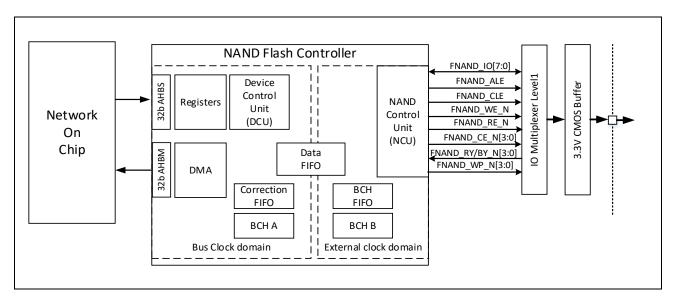

| Section 7 NA | $\Delta$ ND F | Flash Controller                                 | 218 |

|              |               |                                                  |     |

| 7.1 Ove      | ı view        |                                                  | ∠18 |

| 7.2 | Sign   | al Interfaces                                                 | 219 |

|-----|--------|---------------------------------------------------------------|-----|

| 7.3 | Regi   | ster Map                                                      | 220 |

| 7.4 | Reai   | ster Description                                              | 221 |

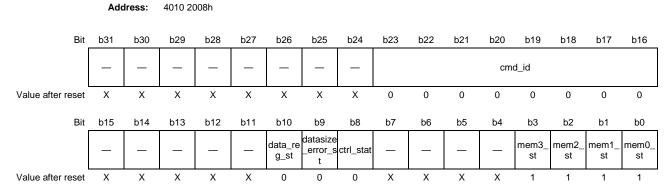

|     | 7.4.1  | COMMAND — Command Register                                    |     |

|     | 7.4.2  | CONTROL — CONTROL Register                                    |     |

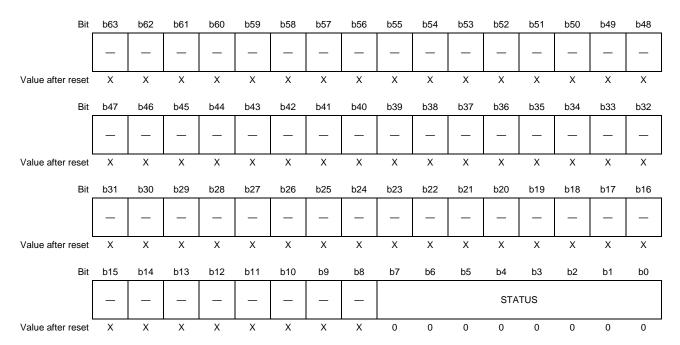

|     | 7.4.3  | STATUS — STATUS Register                                      |     |

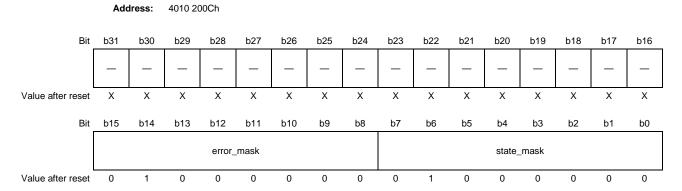

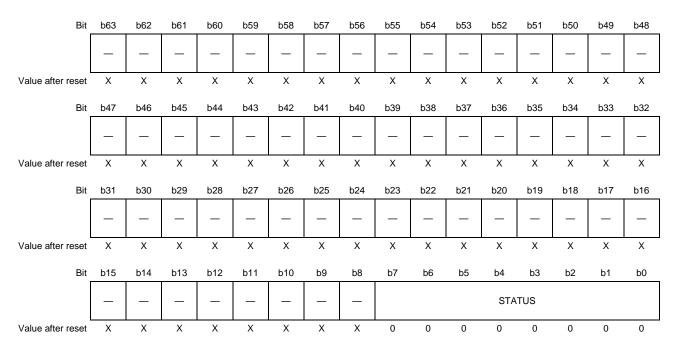

|     | 7.4.4  | STATUS MASK — STATUS MASK Register                            |     |

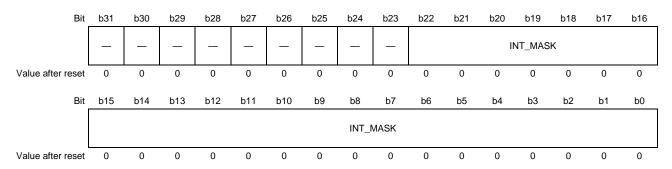

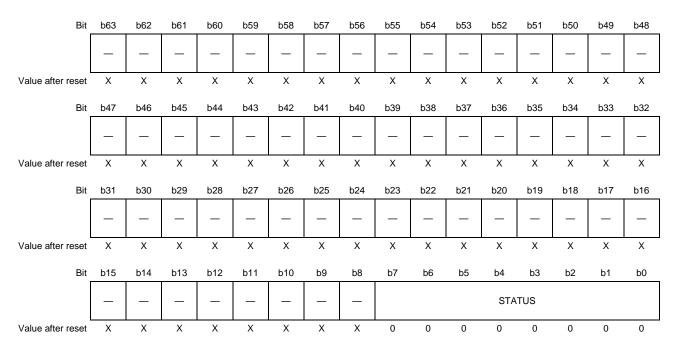

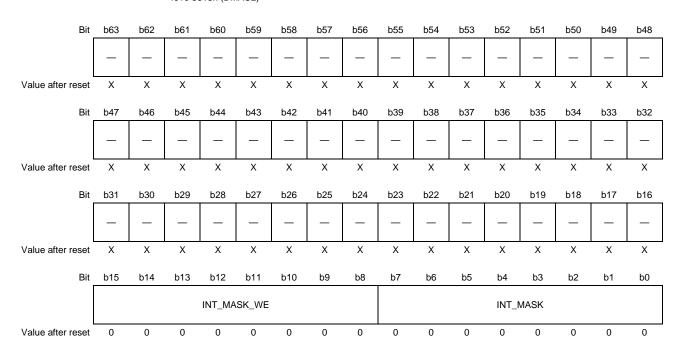

|     | 7.4.5  | INT_MASK — INT_MASK Register                                  |     |

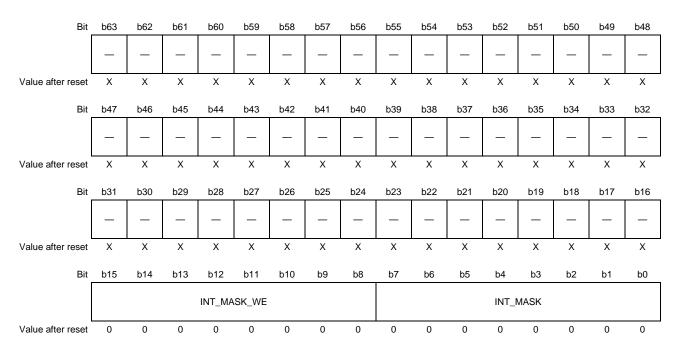

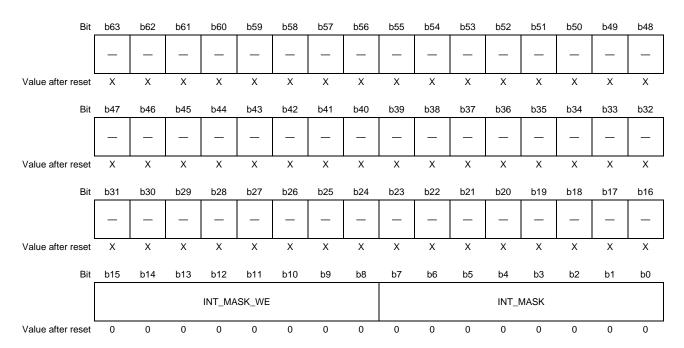

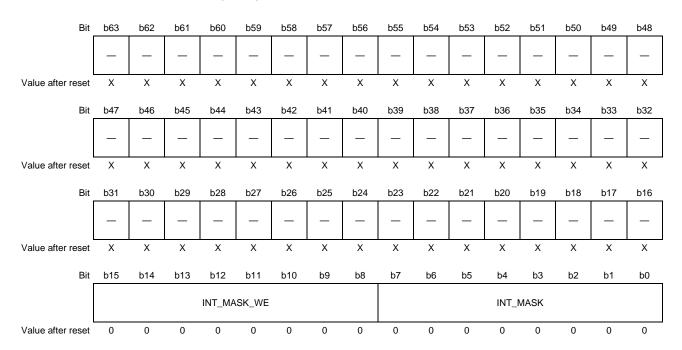

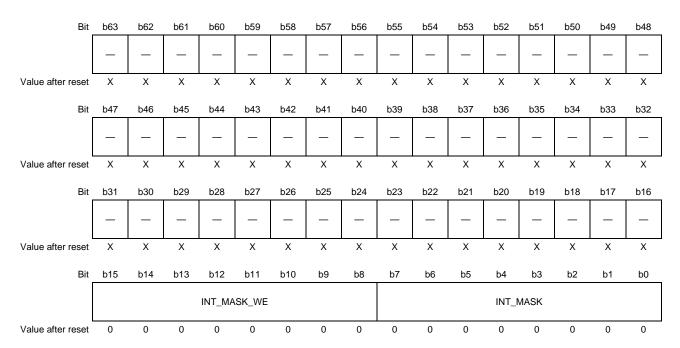

|     | 7.4.6  | INT_STATUS — INT_STATUS Register                              |     |

|     | 7.4.7  | ECC_CTRL — ECC Control Register                               |     |

|     | 7.4.8  | ECC_OFFSET — ECC Offset Register                              |     |

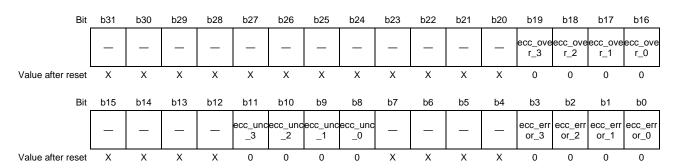

|     | 7.4.9  | ECC_STAT — ECC Status Register                                |     |

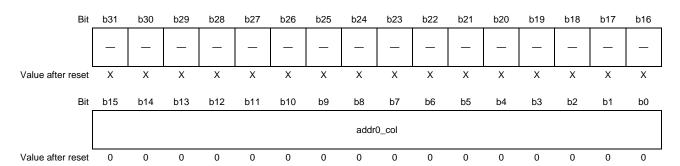

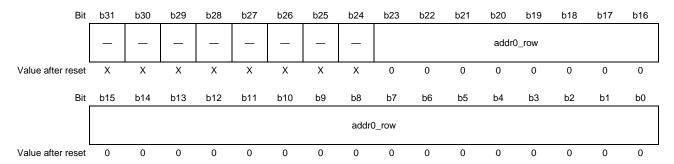

|     | 7.4.10 | ADDR0_COL — Column Address 0 Register                         | 233 |

|     | 7.4.11 | ADDR0_ROW — Row Address 0 Register                            | 233 |

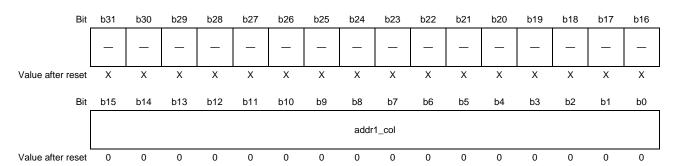

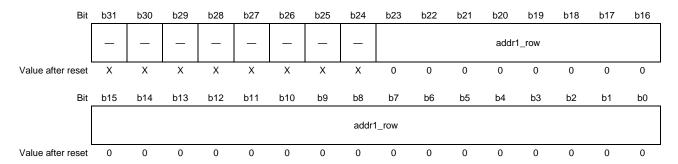

|     | 7.4.12 | ADDR1_COL — Column Address 1 Register                         | 234 |

|     | 7.4.13 | ADDR1_ROW — Row Address 1 Register                            | 234 |

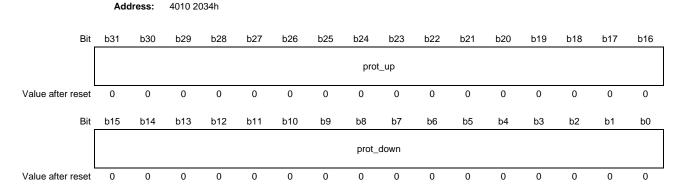

|     | 7.4.14 | PROTECT — Protect Register                                    | 235 |

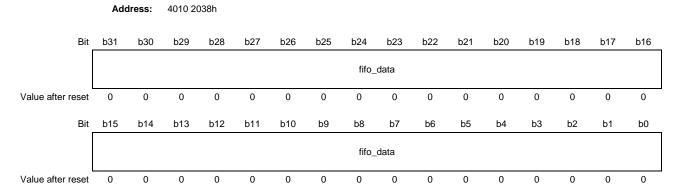

|     | 7.4.15 | FIFO_DATA — FIFO Data Register                                | 236 |

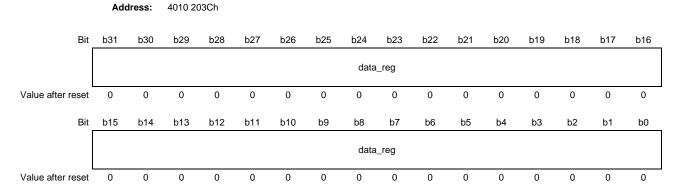

|     | 7.4.16 | DATA_REG — Data Register                                      | 236 |

|     | 7.4.17 | DATA_REG_SIZE — DATA_REG_SIZE Register                        | 237 |

|     | 7.4.18 | DEV[n]_PTR — Device [n] Remap Pointer Register (n = 03)       | 237 |

|     | 7.4.19 | DMA_ADDR — DMA Address Register                               | 238 |

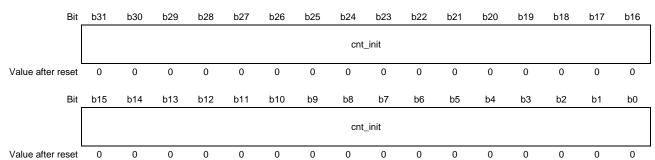

|     | 7.4.20 | DMA_CNT — DMA Counter Register                                | 238 |

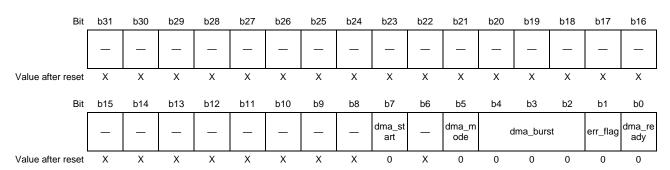

|     | 7.4.21 | DMA_CTRL — DMA Control Register                               | 239 |

|     | 7.4.22 | BBM_CTRL — BBM Control Register                               | 240 |

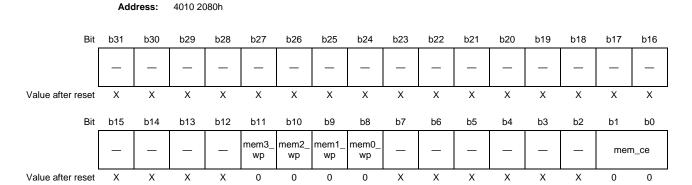

|     | 7.4.23 | MEM_CTRL — Memory Devices Control Register                    | 241 |

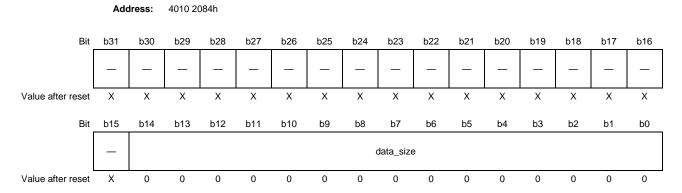

|     | 7.4.24 | DATA_SIZE — Data Size Register                                | 242 |

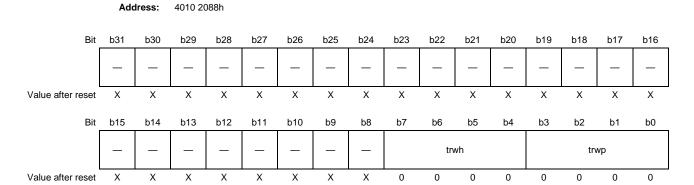

|     | 7.4.25 | TIMINGS_ASYN — Asynchronous Mode Timings Register             | 243 |

|     | 7.4.26 | TIME_SEQ_0 — Command Sequence Timing Register 0               | 244 |

|     | 7.4.27 | TIME_SEQ_1 — Command Sequence Timing Register 1               | 245 |

|     | 7.4.28 | TIME_GEN_SEQ_0 — Generic Command Sequence Register 0          | 246 |

|     | 7.4.29 | TIME_GEN_SEQ_1 — Generic Command Sequence Register 1          | 247 |

|     | 7.4.30 | TIME_GEN_SEQ_2 — Generic Command Sequence Register 2          | 248 |

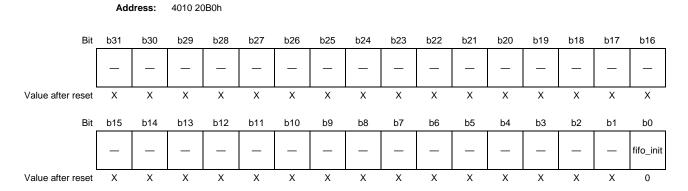

|     | 7.4.31 | FIFO_INIT — FIFO Init Register                                | 249 |

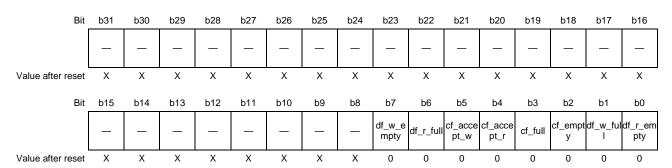

|     | 7.4.32 | FIFO_STATE — FIFO Status Register                             | 250 |

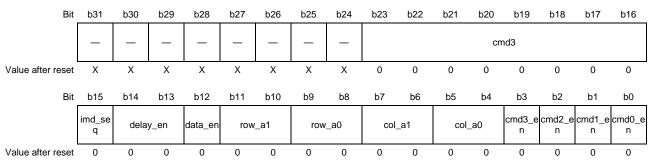

|     | 7.4.33 | GEN_SEQ_CTRL — Generic Sequence Register                      | 251 |

|     | 7.4.34 | MLUN — LUN Configuration Register                             | 253 |

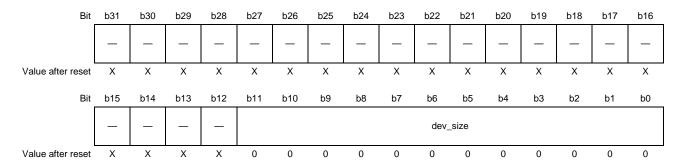

|     | 7.4.35 | DEV[n]_SIZE — Device [n] BBM Record Counter Register (n = 03) | 253 |

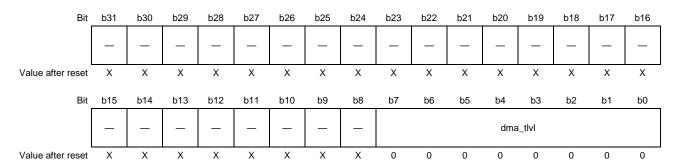

|     | 7.4.36 | DMA_TLVL — DMA Trigger Level Register                         | 254 |

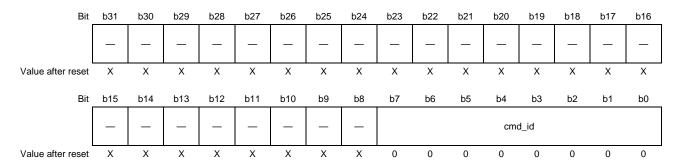

|     | 7.4.37 | CMD_MARK — CMD ID Initial Value                               | 254 |

|     | 7.4.38 | LUN_STATUS_0 — LUN Status Register                            | 255 |

|     | 7.4.39 | TIME_GEN_SEQ_3 — Generic Command Sequence Register 3          | 256 |

|     | 7.4.40 | INT STAT — Internal Status Register                           | 257 |

|     | 7.4.41 | ECC_CNT — ECC Error Counter           | 258 |

|-----|--------|---------------------------------------|-----|

|     | 7.4.42 | PARAM_REG — PARAMETER Register        | 259 |

| 7.5 | Oper   | ration                                | 261 |

|     | 7.5.1  | Programming the NAND Flash Controller | 261 |

|     | 7.5.2  | Command Generation                    | 261 |

|     | 7.5    | 5.2.1 Instruction Encoding            |     |

|     | _      | 5.2.2 Command Sequence Encoding       |     |

|     |        | 5.2.3 Sequence SEQ_0                  |     |

|     |        | 5.2.4 Sequence SEQ_1                  |     |

|     |        | 5.2.5 Sequence SEQ_2                  |     |

|     |        | 5.2.6 Sequence SEQ_3                  |     |

|     |        | 5.2.7 Sequence SEQ 4                  |     |

|     |        | 5.2.8 Sequence SEQ_5                  |     |

|     |        | 5.2.9 Sequence SEQ_6                  |     |

|     |        | 5.2.10 Sequence SEQ_7                 |     |

|     | 7.5    | 5.2.11 Sequence SEQ_8                 |     |

|     |        | 5.2.12 Sequence SEQ 9                 |     |

|     |        | 5.2.13 Sequence SEQ 10                |     |

|     |        | 5.2.14 Sequence SEQ_11                |     |

|     |        | 5.2.15 Sequence SEQ_12                |     |

|     |        | 5.2.16 Sequence SEQ_13                |     |

|     |        | 5.2.17 Sequence SEQ_14                |     |

|     |        | 5.2.18 Sequence SEQ_15                |     |

|     |        | 5.2.19 Sequence SEQ 17                |     |

|     |        | 5.2.20 Sequence SEQ_18                |     |

|     | 7.5    | 5.2.21 Sequence SEQ_19                |     |

|     | 7.5    | 5.2.22 Sequence SEQ_20                |     |

|     | 7.5    | 5.2.23 Sequence SEQ_21                |     |

|     |        | 5.2.24 Sequence SEQ 22                |     |

|     | 7.5    | 5.2.25 Sequence SEQ 23                |     |

|     | 7.5    | 5.2.26 Sequence SEQ_24                | 273 |

|     | 7.5    | 5.2.27 Sequence SEQ_25                |     |

|     | 7.5.3  | Generic Command Sequence              | 274 |

|     | 7.5.4  | Instructions                          | 278 |

|     | 7.5    | 5.4.1 Instruction Set                 |     |

|     |        | 5.4.2 Instruction Execution           |     |

|     |        | 5.4.3 RESET Command                   |     |

|     |        | 5.4.4 READ ID Command                 |     |

|     |        | 5.4.5 READ PARAMETER PAGE Command     |     |

|     |        | 5.4.6 READ UNIQUE ID Command          |     |

|     |        | 5.4.7 GET FEATURES Command            |     |

|     | 7.5    | 5.4.8 SET FEATURES Command            |     |

|     |        | 5.4.9 READ STATUS Command             |     |

|     | 7.5    | 5.4.10 DEVICE STATUS Command          |     |

|     |        | 5.4.11 VOLUME SELECT Command          |     |

|     |        | 5.4.12 SELECT LUN WITH STATUS Command |     |

|     |        | 5.4.13 LUN STATUS Command             |     |

|     |        | 5.4.14 CHANGE READ COLUMN Command     |     |

|     |        | 5.4.15 SELECT CACHE REGISTER Command  |     |

|     |        | 5.4.16 CHANGE WRITE COLUMN Command    |     |

|     |        | 5.4.17 CHANGE ROW ADDRESS Command     |     |

|     | 7.5.4                                  | 4.18    | READ PAGE Command                                              |     |

|-----|----------------------------------------|---------|----------------------------------------------------------------|-----|

|     | 7.5.4                                  | 4.19    | READ PAGE CACHE Command                                        | 287 |

|     | 7.5.4                                  | 4.20    | READ PAGE CACHE LAST Command                                   | 287 |

|     | 7.5.4                                  | 4.21    | READ MULTIPLANE Command                                        |     |

|     | 7.5.4                                  |         | QUEUE PAGE READ Command                                        |     |

|     | 7.5.4                                  |         | TWO PLANE PAGE READ Command                                    |     |

|     | 7.5.4                                  |         | PROGRAM PAGE Command                                           |     |

|     | 7.5.4                                  |         | PROGRAM PAGE IMMEDIATE Command                                 |     |

|     | 7.5.4<br>7.5.4                         |         | PROGRAM PAGE 1 CommandPROGRAM PAGE 1 Command                   |     |

|     | 7.5. <sup>2</sup><br>7.5. <sup>2</sup> |         | PROGRAM PAGE CACHE Command                                     |     |

|     | 7.5. <sup>2</sup><br>7.5. <sup>2</sup> |         | PROGRAM MULTIPLANE Command                                     |     |

|     | 7.5.4                                  |         | WRITE PAGE Command                                             |     |

|     | 7.5.4                                  |         | WRITE PAGE CACHE Command                                       |     |

|     | 7.5.4                                  |         | WRITE MULTIPLANE Command                                       |     |

|     | 7.5.4                                  |         | ERASE BLOCK Command                                            |     |

|     | 7.5.4                                  | 4.34    | ERASE MULTIPLANE Command                                       | 293 |

|     | 7.5.4                                  | 4.35    | COPYBACK READ Command                                          | 293 |

|     | 7.5.4                                  | 4.36    | COPYBACK PROGRAM Command                                       |     |

|     | 7.5.4                                  | 4.37    | COPYBACK PROGRAM 1 Command                                     |     |

|     | 7.5.4                                  |         | COPYBACK MULTIPLANE Command                                    |     |

|     | 7.5.4                                  |         | PROGRAM OTP Command                                            |     |

|     | 7.5.4                                  |         | DATA PROTECT OTP Command                                       |     |

|     | 7.5.4                                  |         | PAGE READ OTP Command                                          |     |

|     |                                        |         | .UN Work Mode                                                  |     |

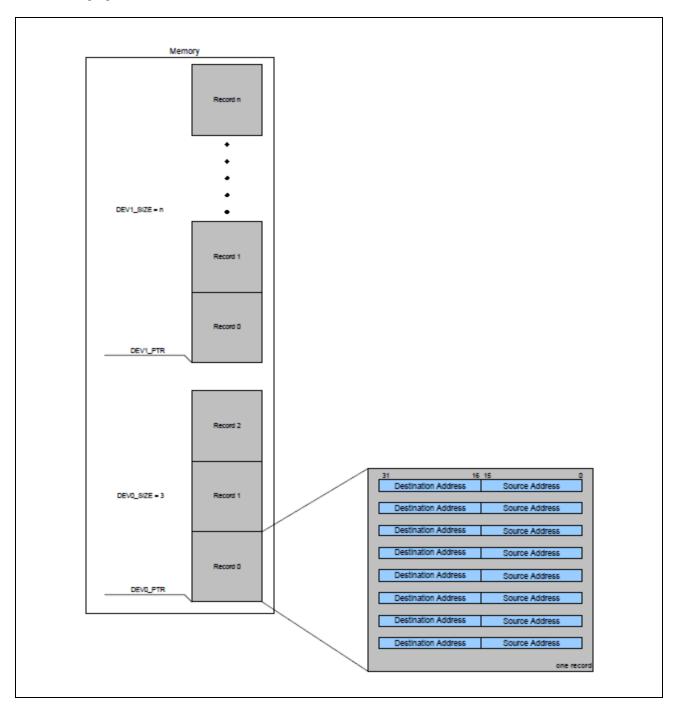

|     |                                        |         | pping Mechanism                                                |     |

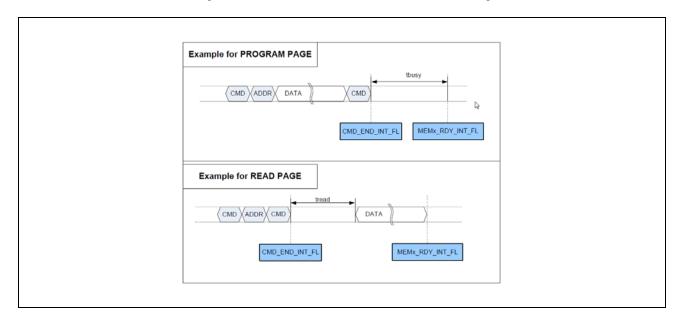

|     | 7.5.7                                  | Interru | ıpts Mechanism                                                 | 299 |

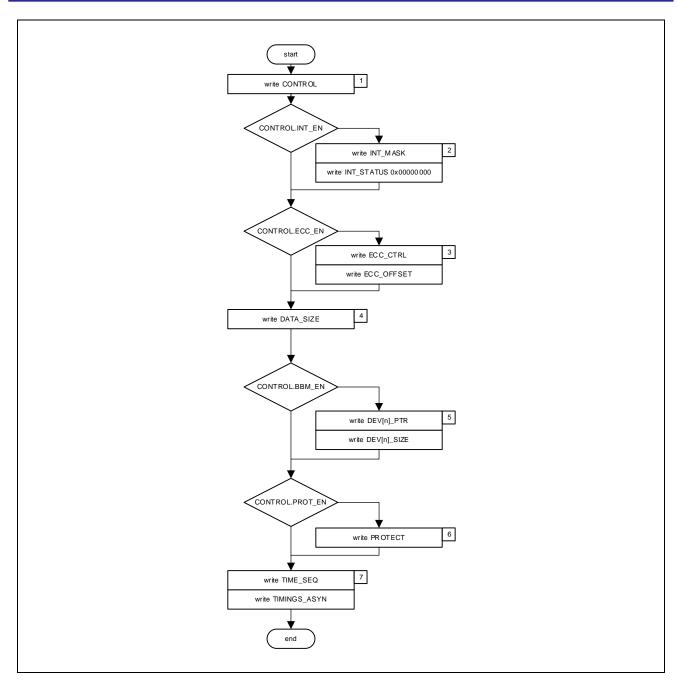

| 7.6 | Setup                                  | and Co  | onfiguration                                                   | 300 |

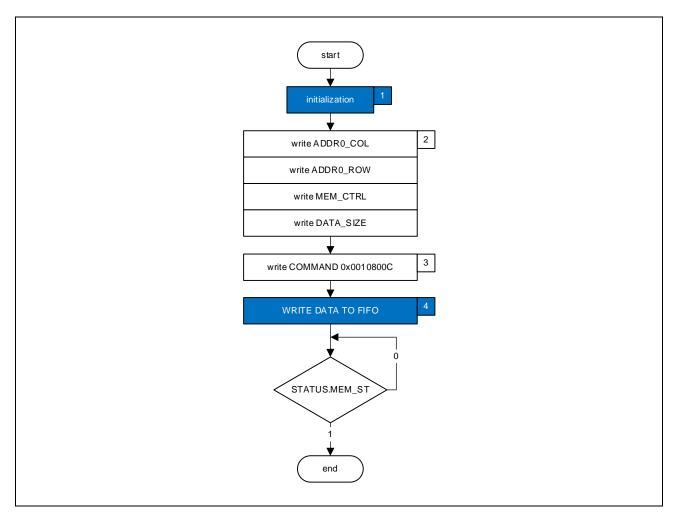

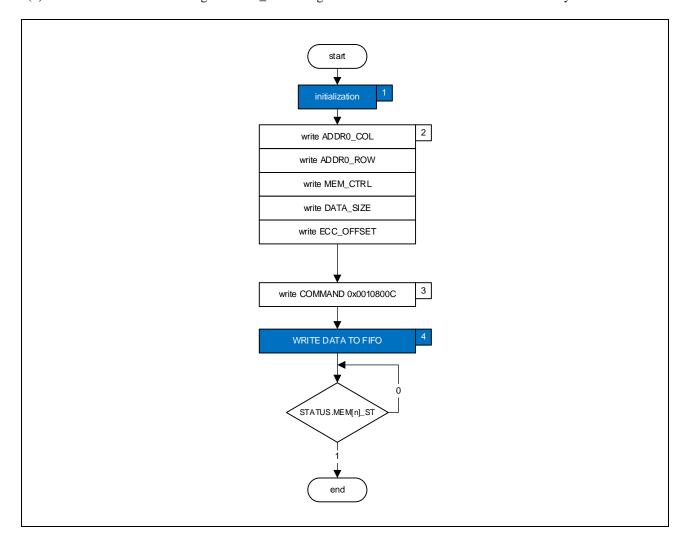

|     | 7.6.1                                  | Send I  | Data to NAND Flash via Slave Interface                         | 302 |

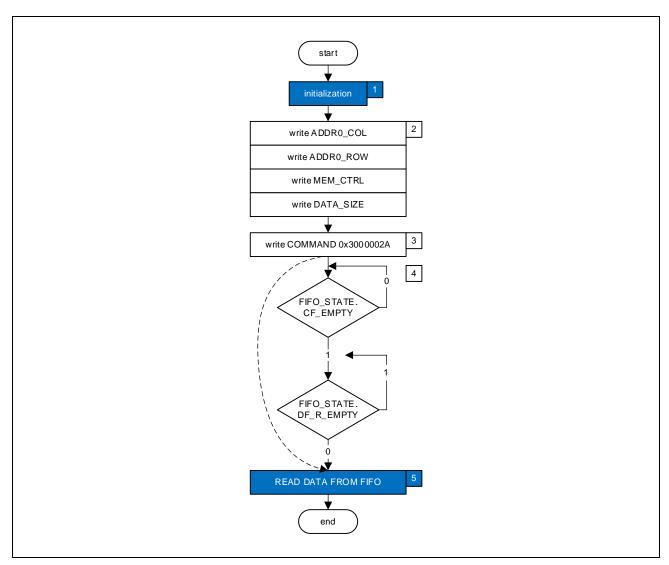

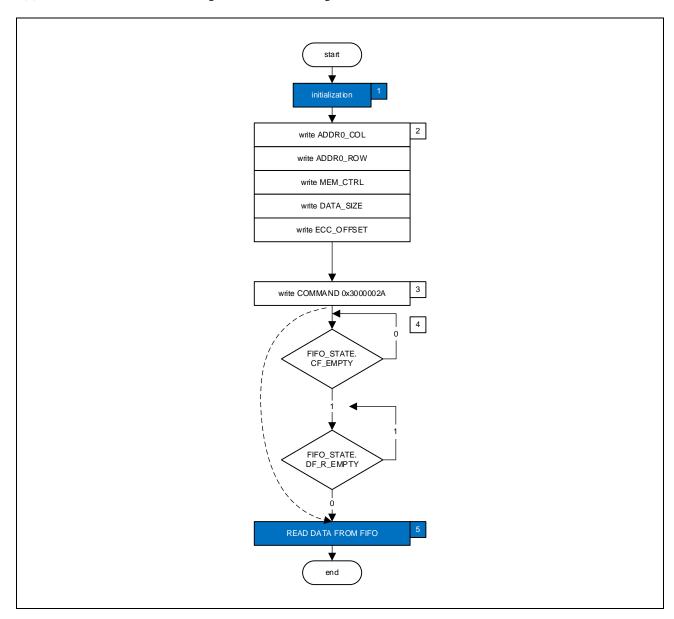

|     | 7.6.2                                  | Read I  | Data from NAND Flash via Slave Interface                       | 303 |

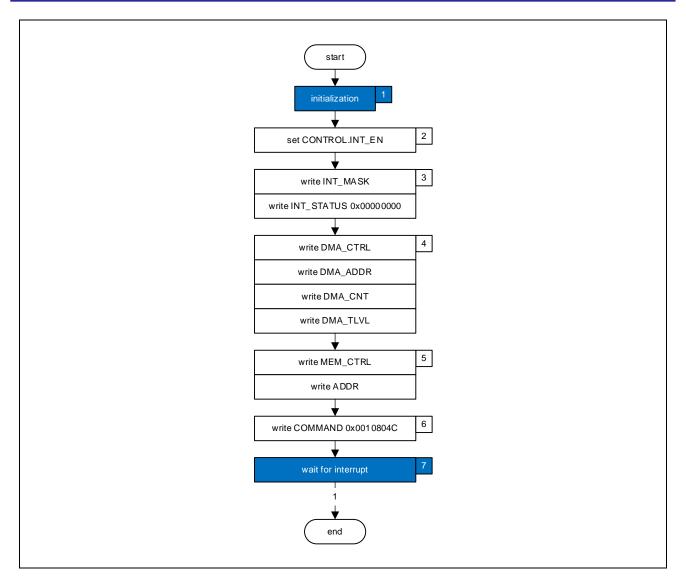

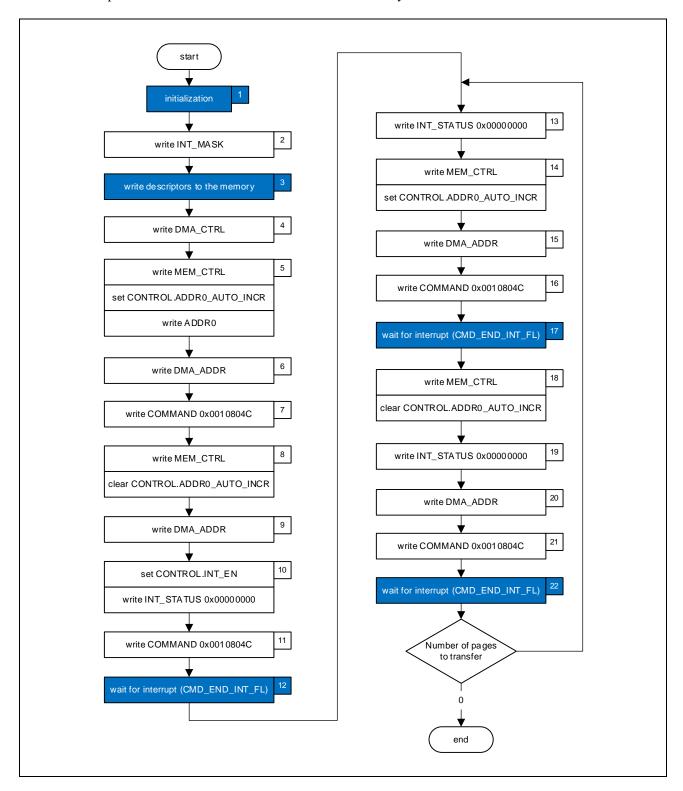

|     | 7.6.3                                  | Send I  | Data to NAND Flash via Master Interface (Using DMA)            | 304 |

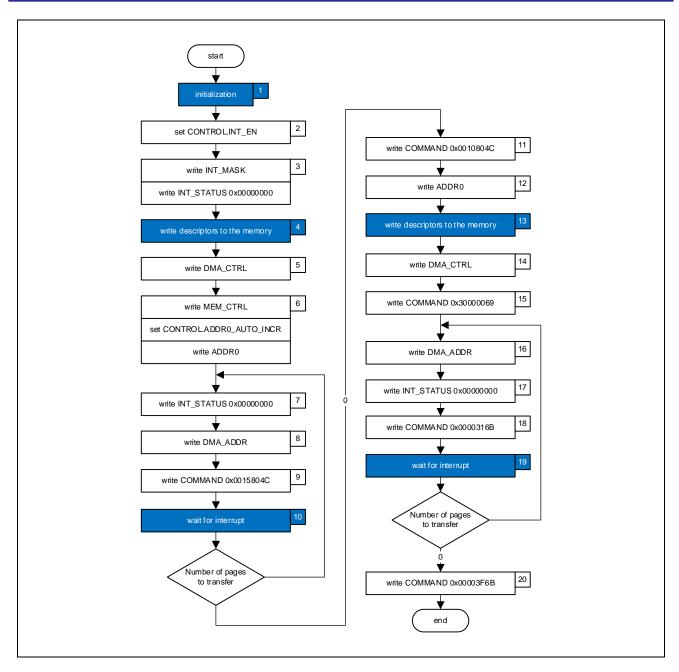

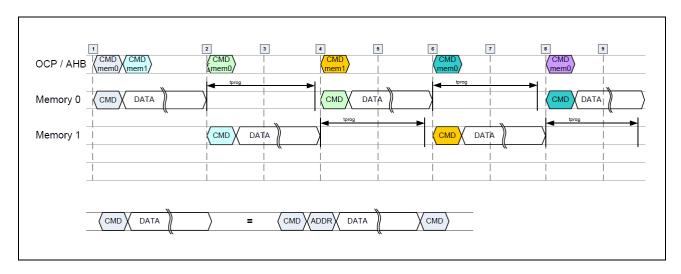

|     |                                        |         | Vriting and Reading of Several Pages from the Memory Using DMA |     |

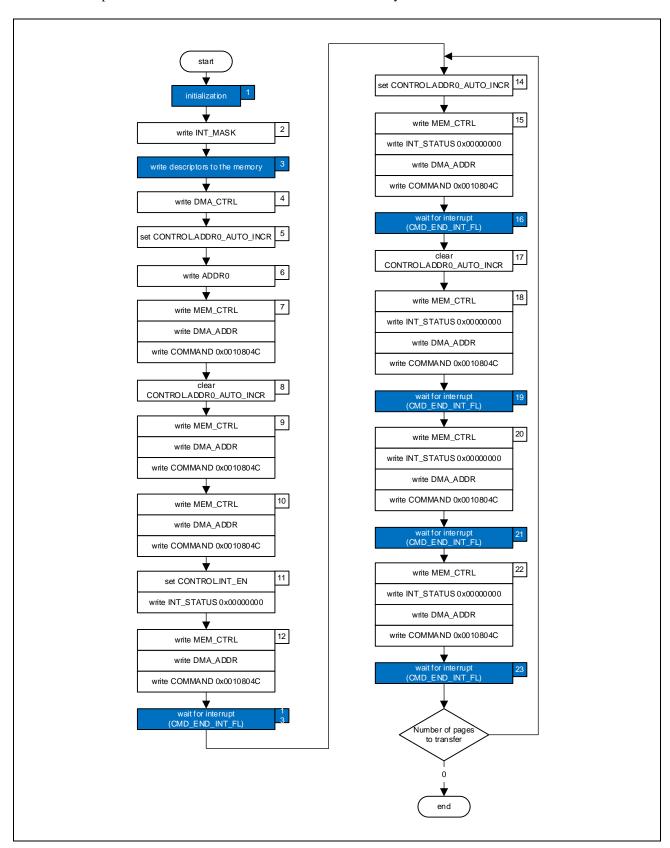

|     |                                        |         | g of Data into Two NAND Flash Memory Devices                   |     |

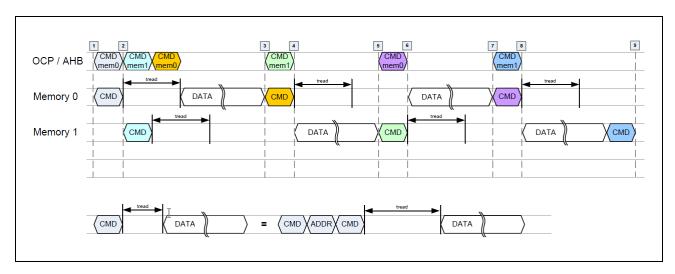

|     | 7.6.6                                  | Readir  | ng Data from Two NAND Flash Memory Devices                     | 309 |

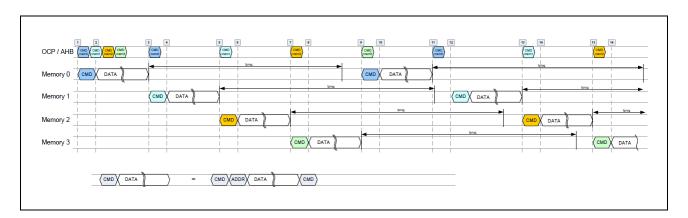

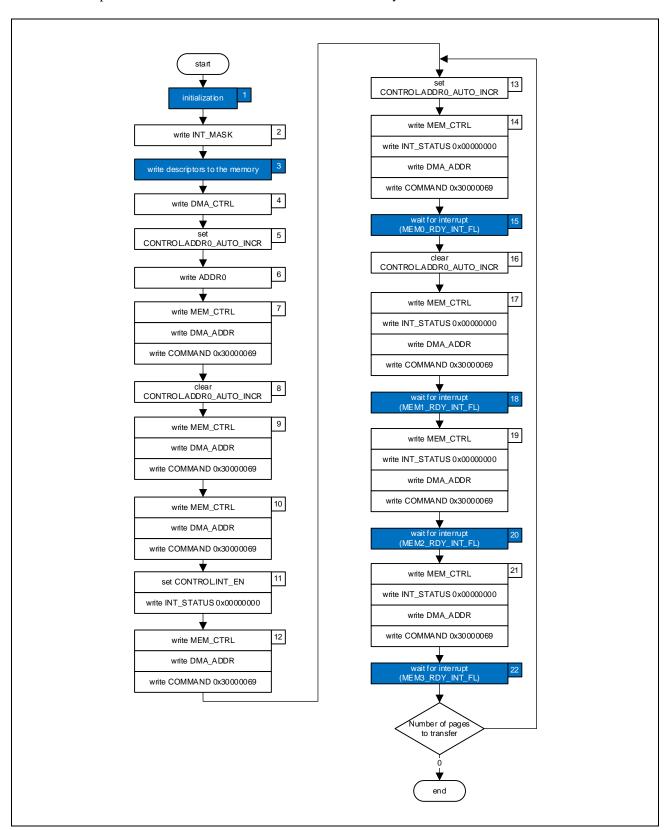

|     |                                        |         | g Data into Four NAND Flash Memory Devices                     |     |

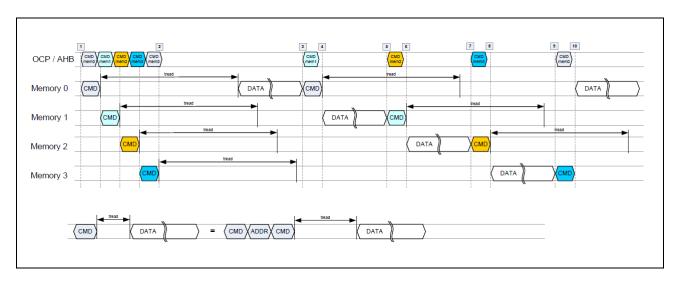

|     |                                        | -       | ng Data from Four NAND Flash Memory Devices                    |     |

|     |                                        |         | g Partial Pages                                                |     |

|     |                                        |         | ng Partial Pages                                               |     |

| 7.7 |                                        |         |                                                                |     |

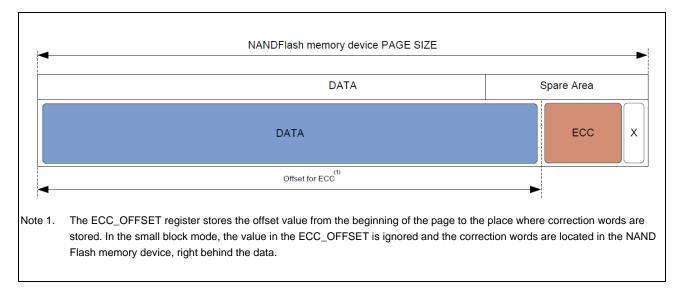

|     |                                        |         | and Data Location within the Page                              |     |

|     |                                        |         | Algorithm Implementation                                       |     |

| 7.8 |                                        |         |                                                                |     |

|     | •                                      |         |                                                                |     |

|     |                                        |         | [n]_COL and ADDR[n]_ROW Registerst Pagister (PROTECT)          |     |

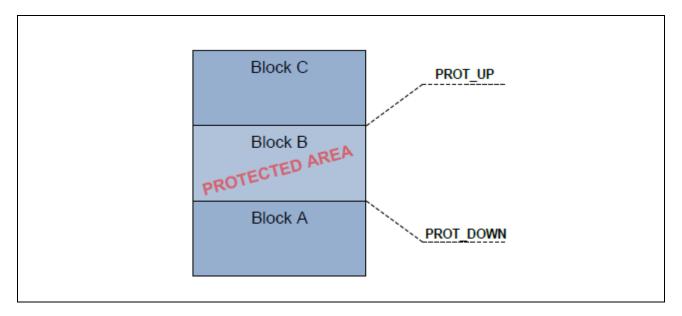

|     |                                        |         | t Register (PROTECT)                                           |     |

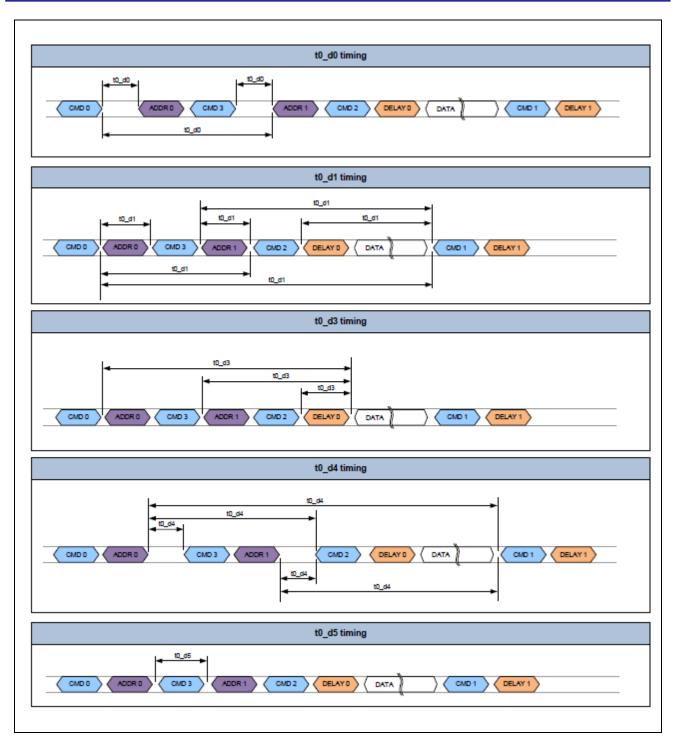

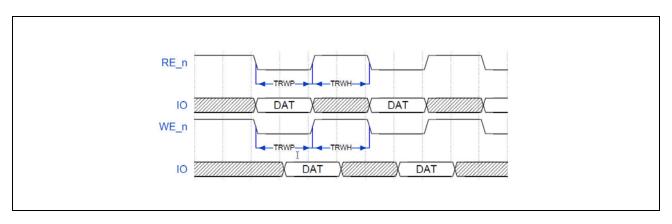

|     |                                        | -       | hronous Mode Timings Register (TIMINGS_ASYN)                   |     |

|     | 7.8.4                                  | Comm    | nand Sequence Timing Register 1 (TIME_SEQ_1)                   | 320 |

|     |                                        |         |                                                                |     |

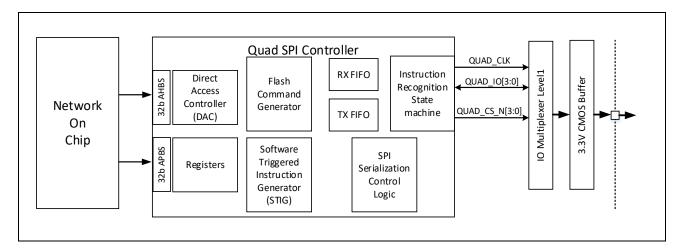

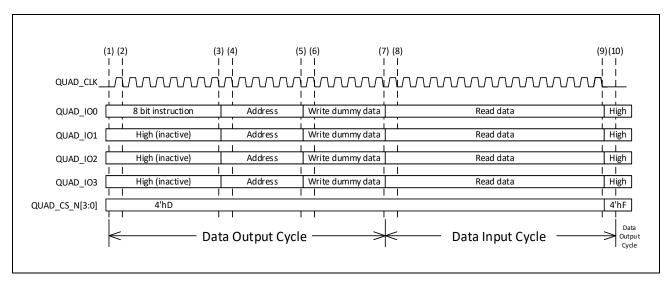

| Section 8 Quad IO SPI |               |                                                                           |     |  |  |  |  |  |

|-----------------------|---------------|---------------------------------------------------------------------------|-----|--|--|--|--|--|

| 8.1                   | Overview      |                                                                           |     |  |  |  |  |  |

| 8.2                   | Signa         | Signal interfaces                                                         |     |  |  |  |  |  |

| 8.3                   | Regis         | ter Map                                                                   | 323 |  |  |  |  |  |

| 8.4                   | Regis         | ter Description                                                           | 325 |  |  |  |  |  |

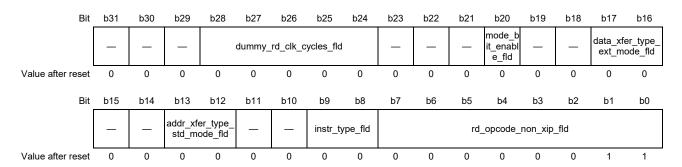

|                       | 8.4.1         | config_reg — QSPI Configuration Register                                  |     |  |  |  |  |  |

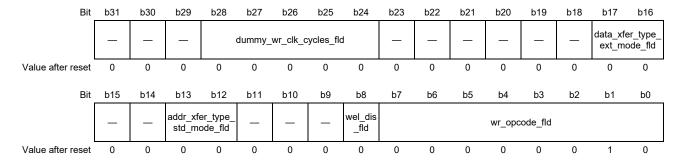

|                       | 8.4.2         | dev_instr_rd_config_reg — Device Read Instruction Configuration Register  |     |  |  |  |  |  |

|                       | 8.4.3         | dev_instr_wr_config_reg — Device Write Instruction Configuration Register |     |  |  |  |  |  |

|                       | 8.4.4         | dev_delay_reg — QSPI Device Delay Register                                |     |  |  |  |  |  |

|                       | 8.4.5         | rd_data_capture_reg — Read Data Capture Register                          | 331 |  |  |  |  |  |

|                       | 8.4.6         | dev_size_config_reg — Device Size Configuration Register                  | 332 |  |  |  |  |  |

|                       | 8.4.7         | remap_addr_reg — Remap Address Register                                   | 333 |  |  |  |  |  |

|                       | 8.4.8         | mode_bit_config_reg — Mode Bit Configuration Register                     |     |  |  |  |  |  |

|                       | 8.4.9         | tx_thresh_reg — TX Threshold Register                                     | 334 |  |  |  |  |  |

|                       | 8.4.10        | rx_thresh_reg — RX Threshold Register                                     | 334 |  |  |  |  |  |

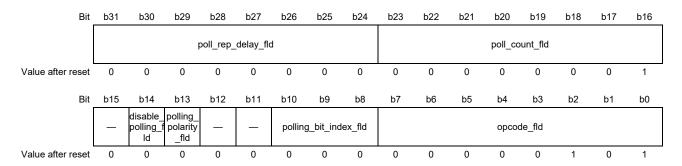

|                       | 8.4.11        | write_completion_ctrl_reg — Write Completion Control Register             | 335 |  |  |  |  |  |

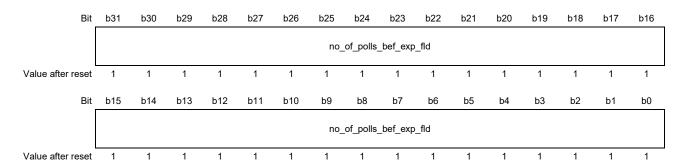

|                       | 8.4.12        | no_of_polls_bef_exp_reg — Polling Expiration Register                     | 336 |  |  |  |  |  |

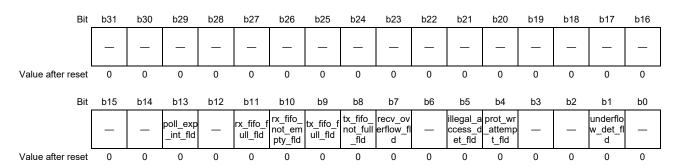

|                       | 8.4.13        | irq_status_reg — Interrupt Status Register                                | 337 |  |  |  |  |  |

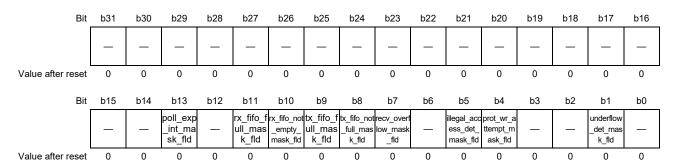

|                       | 8.4.14        | irq_mask_reg — Interrupt Mask Register                                    | 339 |  |  |  |  |  |

|                       | 8.4.15        | lower_wr_prot_reg — Lower Write Protection Register                       | 340 |  |  |  |  |  |

|                       | 8.4.16        | upper_wr_prot_reg — Upper Write Protection Register                       | 340 |  |  |  |  |  |

|                       | 8.4.17        | wr_prot_ctrl_reg — Write Protection Control Register                      | 341 |  |  |  |  |  |

|                       | 8.4.18        | flash_cmd_ctrl_reg — Flash Command Control Register                       | 342 |  |  |  |  |  |

|                       | 8.4.19        | flash_cmd_addr_reg — Flash Command Address Register                       | 344 |  |  |  |  |  |

|                       | 8.4.20        | flash_rd_data_lower_reg — Flash Command Read Data Register (Lower)        | 344 |  |  |  |  |  |

|                       | 8.4.21        | flash_rd_data_upper_reg — Flash Command Read Data Register (Upper)        | 345 |  |  |  |  |  |

|                       | 8.4.22        | flash_wr_data_lower_reg — Flash Command Write Data Register (Lower)       | 345 |  |  |  |  |  |

|                       | 8.4.23        | flash_wr_data_upper_reg — Flash Command Write Data Register (Upper)       | 346 |  |  |  |  |  |

|                       | 8.4.24        | polling_flash_status_reg — Polling Flash Status Register                  | 346 |  |  |  |  |  |

|                       | 8.4.25        | module_id_reg — Module ID Register                                        | 347 |  |  |  |  |  |

| 8.5                   | Opera         | ation                                                                     | 348 |  |  |  |  |  |

|                       | 8.5.1         | AHB Control Interface                                                     | 348 |  |  |  |  |  |

|                       | 8.5.          | , , ,                                                                     |     |  |  |  |  |  |

|                       | 8.5.          |                                                                           |     |  |  |  |  |  |

|                       | 8.5.2         | Direct Access Controller (DAC)                                            |     |  |  |  |  |  |

|                       | 8.5.3         | Software Triggered Instruction Generator (STIG)                           |     |  |  |  |  |  |

|                       | 8.5.4         | Servicing a STIG request                                                  |     |  |  |  |  |  |

|                       | 8.5.5         |                                                                           |     |  |  |  |  |  |

|                       | 8.5.6         | SPI Command Translation                                                   |     |  |  |  |  |  |

|                       | 8.5.7         | Selecting the Flash Instruction Type                                      |     |  |  |  |  |  |

|                       | 8.5.8         | APB Interface and Register Module                                         |     |  |  |  |  |  |

|                       | 8.5.9<br>8.5. | Read Data Capturing                                                       |     |  |  |  |  |  |

| 8.6    | Progr           | amming Quad SPI Controller                                                                                | 355 |

|--------|-----------------|-----------------------------------------------------------------------------------------------------------|-----|

|        | 8.6.1           | Configuring the Quad SPI Controller for use after reset                                                   | 355 |

|        | 8.6.2           | Configuring the Quad SPI Controller for optimal use                                                       | 355 |

|        | 8.6.3           | Using the Flash Command Control Register (STIG Operation)                                                 | 357 |

|        | 8.6.4           | Using SPI Legacy Mode                                                                                     | 357 |

|        | 8.6.5           | Entering and Exiting NoCMD mode                                                                           |     |

|        |                 | .5.1 Entering NoCMD mode                                                                                  |     |

|        |                 | .5.2 Exiting NoCMD mode                                                                                   |     |

| 0.7    | 8.6.6           | Using the Write Protection Registers                                                                      |     |

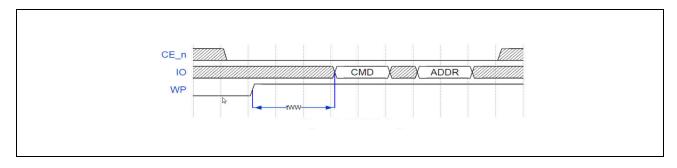

| 8.7    | _               | e Notes                                                                                                   |     |

|        | 8.7.1           | 4-byte Address Output                                                                                     |     |

|        | 8.7.2           | Write Protection Area                                                                                     |     |

|        | 8.7.3           | Automatically Polling for Write Complete                                                                  |     |

|        | 8.7.4           | Chip Select Output                                                                                        | 359 |

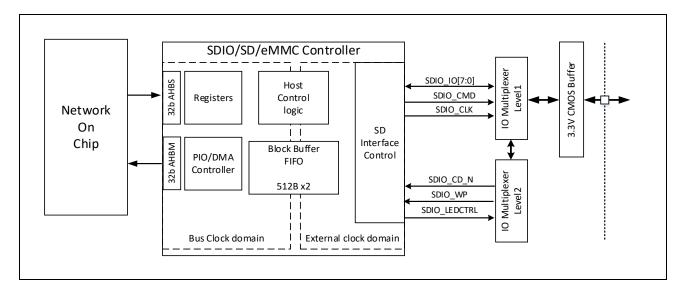

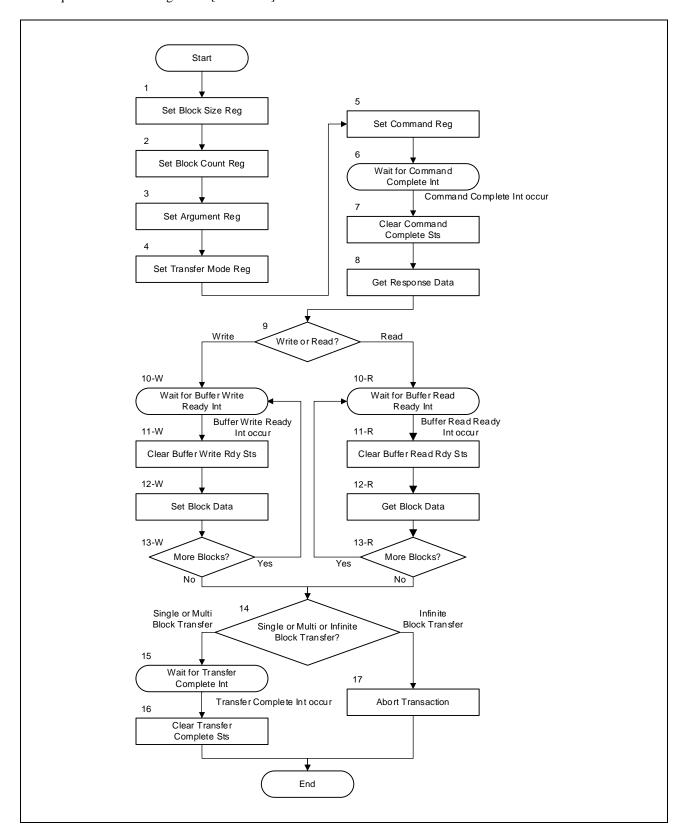

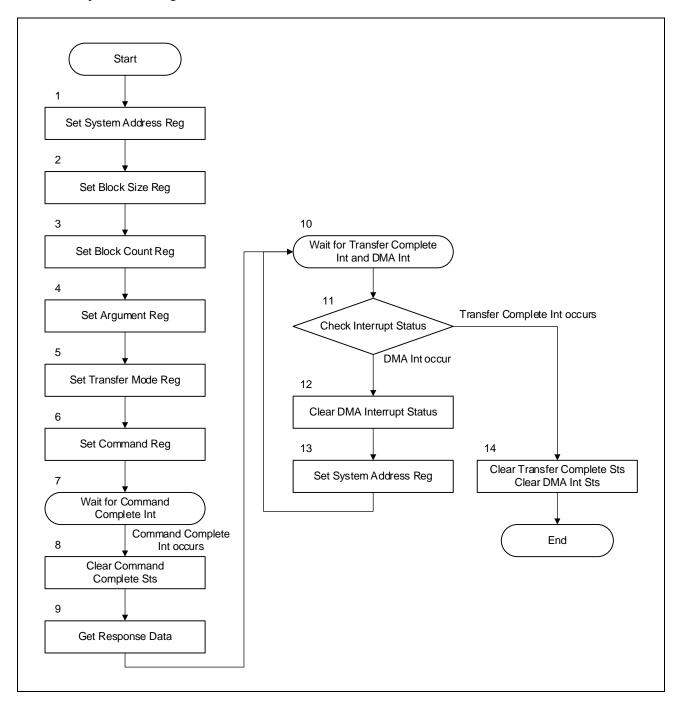

| Sectio | n 9 SD          | IO/SD/eMMC Controller                                                                                     | 360 |

| 9.1    | Overv           | /iew                                                                                                      | 360 |

| 9.2    |                 | I Interfaces                                                                                              |     |

| 9.3    | J               | ter Map                                                                                                   |     |

| 9.5    | 9.3.1           | Register Map (SDIO1)                                                                                      |     |

|        | 9.3.1           | Register Map (SDIO2)                                                                                      |     |

| 0.4    |                 | ter Description                                                                                           |     |

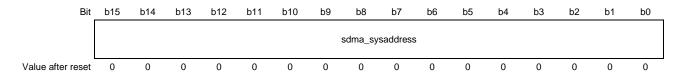

| 9.4    | 9.4.1           | ·                                                                                                         |     |

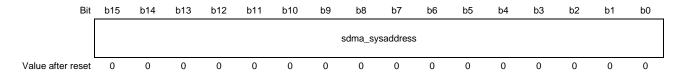

|        | 9.4.1           | reg_sdmasysaddrlo — SDMA System Address Register Lowreg_sdmasysaddrhi — SDMA System Address Register High |     |

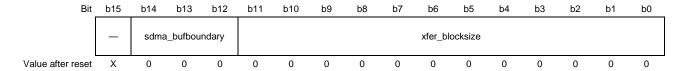

|        | 9.4.2           | ,                                                                                                         |     |

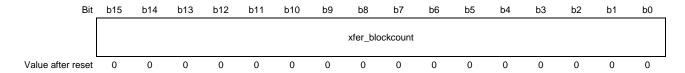

|        | 9.4.3           | reg_blocksize — Block Size Register                                                                       |     |

|        | 9.4.4           | reg_blockcount — Block Count Register                                                                     |     |

|        |                 | reg_argument1lo — Argument1 Register Low                                                                  |     |

|        | 9.4.6<br>9.4.7  | reg_argument1hi — Argument1 Register High                                                                 |     |

|        |                 | reg_transfermode — Transfer Mode Register                                                                 |     |

|        | 9.4.8           | reg_command — Command Register                                                                            |     |

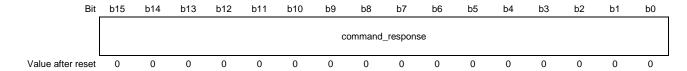

|        | 9.4.9<br>9.4.10 | reg_response[n] — Response Register [n] (n = 07)                                                          |     |

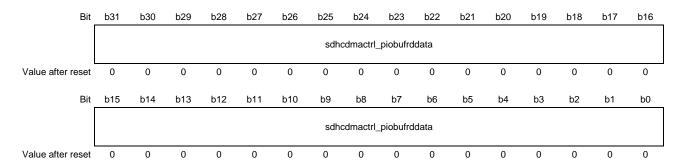

|        |                 | reg_dataport — Buffer Data Port Register                                                                  |     |

|        | 9.4.11          | reg_presentstate — Present State Register                                                                 |     |

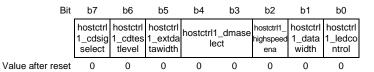

|        | 9.4.12          | reg_hostcontrol1 — Host Control 1 Register                                                                |     |

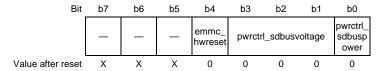

|        | 9.4.13          | reg_powercontrol — Power Control Register                                                                 |     |

|        | 9.4.14          | reg_blockgapcontrol — Block Gap Control Register                                                          |     |

|        | 9.4.15          | reg_wakeupcontrol — Wake-up Control Register                                                              |     |

|        | 9.4.16          | reg_clockcontrol — Clock Control Register                                                                 |     |

|        | 9.4.17          | reg_timeoutcontrol — Timeout Control Register                                                             |     |

|        | 9.4.18          | reg_softwarereset — Software Reset Register                                                               |     |

|        | 9.4.19          | reg_normalintrsts — Normal Interrupt Status Register                                                      |     |

|        | 9.4.20          | reg_errorintrsts — Error Interrupt Status Register                                                        |     |

|        | 9.4.21          | reg_normalintrstsena — Normal Interrupt Status Enable Register                                            | 393 |

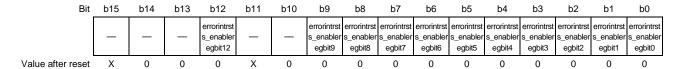

| 9.4.22       | reg_errorintrstsena — Error Interrupt Status Enable Register                         | 394 |

|--------------|--------------------------------------------------------------------------------------|-----|

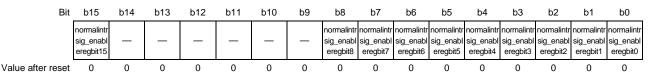

| 9.4.23       | reg_normalintrsigena — Normal Interrupt Signal Enable Register                       | 395 |

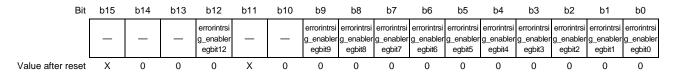

| 9.4.24       | reg_errorintrsigena — Error Interrupt Signal Enable Register                         | 396 |

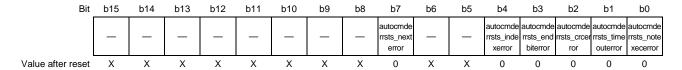

| 9.4.25       | reg_autocmderrsts — Auto CMD Error Status Register                                   | 397 |

| 9.4.26       | reg_hostcontrol2 — Host Control 2 Register                                           | 398 |

| 9.4.27       | reg_capabilities — Capabilities Register                                             | 399 |

| 9.4.28       | reg_capabilities_cont — Capabilities Register (Continue)                             | 401 |

| 9.4.29       | reg_maxcurrentcap — Maximum Current Capabilities Register                            | 402 |

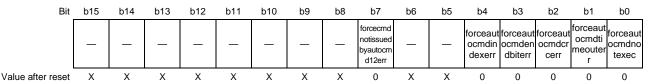

|              | reg_ForceEventforAUTOCMDErrorStatus — Force Event for Auto CMD Error Status Register | 403 |

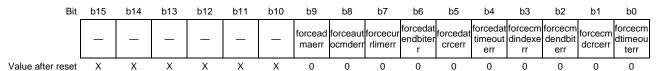

|              | reg_forceeventforerrintsts — Force Event for Error Interrupt Status Register         |     |

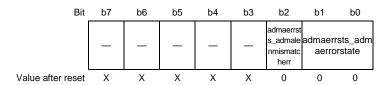

|              | reg_admaerrsts — ADMA Error Status Register                                          |     |

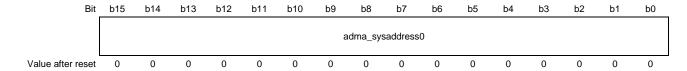

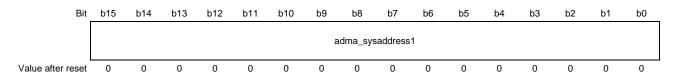

|              | reg_admasysaddr0 — ADMA System Address Register Low                                  |     |

|              | reg_admasysaddr1 — ADMA System Address Register High                                 |     |

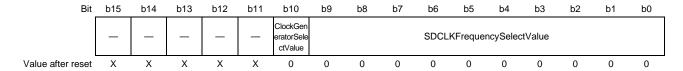

|              | reg_presetvalue0 — Preset Value Register for Initialization                          |     |

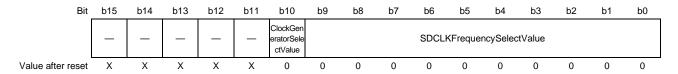

|              | reg_presetvalue1 — Preset Value Register for Default Speed                           |     |

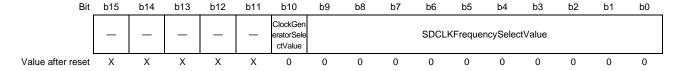

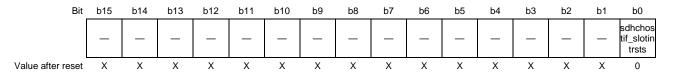

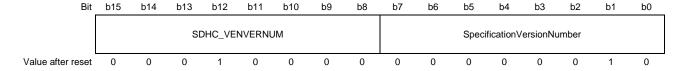

|              | reg_presetvalue2 — Preset Value Register for High Speed                              |     |