# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**User's Manual**

# **RA78K0S Series**

**Assembler Package**

**Structured Assembler Language**

ST78K0S V1.00 or Later

Document No. U11623EJ1V0UMJ1 (1st edition) Date Published January 2001 N CP(K)

© NEC Corporation 1996 Printed in Japan [MEMO]

MS-DOS and Windows are trademarks of Microsoft Corporation. IBM PC and PC DOS are trademarks of International Business Machines Corporation. HP9000 Series 700 and HP-UX are trademarks of Hewlett Packard Corporation. SPARCstation is a trademark of SPARC International, Inc. RISC NEWS and NEWS-OS are trademarks of Sony Corporation.

- The information in this document is current as of August, 1996. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

"Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

- (1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

NEC Electronics Inc. (U.S.) Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### NEC Electronics (Germany) GmbH

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

#### NEC Electronics (UK) Ltd.

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

# NEC Electronics Italiana s.r.l.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99 NEC Electronics (Germany) GmbH Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

#### NEC Electronics (France) S.A. Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

#### **NEC Electronics (France) S.A.** Madrid Office

Madrid, Spain Tel: 91-504-2787 Fax: 91-504-2860

#### **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388 NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. United Square, Singapore Tel: 65-253-8311 Fax: 65-250-3583

NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

# NEC do Brasil S.A.

Electron Devices Division Guarulhos-SP Brasil Tel: 55-11-6462-6810 Fax: 55-11-6462-6829

#### PREFACE

This manual has been written to help users obtain an accurate understanding of the coding method used for the structured assembler preprocessor (hereafter referred to as the "structured assembler") that is included in the "RA78K0S Assembler Package", i.e., the assembler package for compact, general-purpose microcontrollers in the 78K/0 Series.

This manual does not explain methods for using programs other than the structured assembler nor does it describe structured assembler operation methods.

Therefore, when writing programs, please refer to the "ASSEMBLER PACKAGE USER'S MANUAL" (ASSEMBLY LANGUAGE AND OPERATION).

#### **Target readers**

This manual was written for readers who understand the functions of compact, general-purpose microcontrollers in the 78K/0 Series.

Readers requiring a description of the functions of compact, general-purpose microcontrollers in the 78K/0 Series should refer to the target chip's User's Manual.

#### **Target chips**

This assembler can be used for all chips supported by the RA78K0S Assembler Package.

#### Composition

The composition of this manual is described below.

CHAPTER 1 GENERAL

This chapter describes the functions (the role, etc.) of the structured assembler in software development for microcontrollers.

- CHAPTER 2 SOURCE PROGRAM CODING METHODS

This chapter describes methods for source program configuration, coding syntax, and other principal rules and

conventions concerning the coding of source programs.

- CHAPTER 3 CONTROL STATEMENTS

Control statements are used to describe the "if~else~endif" indicators of the program structure. This chapter describes control statement functions and coding methods.

- CHAPTER 4 EXPRESSIONS Assignments and arithmetic operations are entered as expressions. This chapter describes expression functions and coding methods.

- CHAPTER 5 DIRECTIVES

This chapter presents use examples in describing how to write and use structured assembler directives.

- CHAPTER 6 CONTROL INSTRUCTIONS

This chapter presents use examples in describing how to write and use structured assembler control instructions.

- APPENDIX A SYNTAX LISTS

This appendix presents a structured assembler syntax list.

- APPENDIX B LISTS OF GENERATED INSTRUCTIONS This appendix presents a list of instructions generated by the structured assembler.

- APPENDIX C MAXIMUM PERFORMANCE

This appendix describes the maximum performance features of the structured assembler.

# Use

Readers who are using a structured assembler for the first time should read this manual starting from "CHAPTER

# 1 GENERAL".

Readers who already have a general knowledge of structured assemblers may skip Chapter 1. However, all readers should read section **"1.3 Before Starting Program Development"**.

# Legend

The meanings of common symbols in this manual are described below.

|          |   | Same format or pattern is repeated                                |

|----------|---|-------------------------------------------------------------------|

|          |   |                                                                   |

| []       | : | Characters enclosed in these brackets can be omitted.             |

| ΓΙ       | : | Characters enclosed in these brackets are a character string.     |

| ••       | : | Characters between single quotation marks are a character string. |

|          | : | Quotation marks indicate a location of reference.                 |

| $\Delta$ | : | Indicates one or more white-space characters or tabs.             |

| Boldface | : | Characters in boldface are as shown.                              |

|          | : | Underlining is used to indicate input character strings.          |

| :        | : | Indicates that program description is omitted                     |

| ()       | : | Characters between parentheses are a character string.            |

| CR       | : | Carriage return                                                   |

| LF       | : | Line feed                                                         |

| /        | : | Delimiter                                                         |

| α        | : | is entered as a mnemonic operand, such as a register name         |

| β        | : | is entered as a mnemonic operand, such as a register name         |

| γ        | : | is entered as a mnemonic operand, such as a register name         |

| δ        | : | is entered as a mnemonic operand, such as a register name         |

|          |   |                                                                   |

# CONTENTS

| CHAPT | ER 1 GENERAL                                                 | 1        |

|-------|--------------------------------------------------------------|----------|

| 1.1   | Overview of Structured Assembler                             | 1        |

| 1.2   | Overview of Functions                                        | 2        |

| 1.3   | Before Starting Program Development                          | 4        |

|       | 1.3.1 Maximum performance                                    | 4        |

|       | 1.3.2 Caution points                                         | 5        |

|       | 1.3.3 Environment variables                                  | 6        |

|       |                                                              | _        |

|       | ER 2 SOURCE PROGRAM CODING METHODS                           | 7        |

|       | Basic Configuration of Source Programs                       | 7        |

|       | Source Program Elements                                      | 8        |

|       | Reserved Words                                               | 11       |

|       | Label Generation Rules                                       | 13       |

|       | Size Specification                                           | 13       |

|       | Data Sizes                                                   | 14       |

|       | Comments                                                     | 15       |

|       | Tool Information                                             | 15       |

| 2.9   | Output Results of Input Source Files by Structured Assembler | 16       |

| СНАРТ | ER 3 CONTROL STATEMENTS                                      | 17       |

|       | Overview of Control Statements                               | 17       |

|       | Control Statement Characters                                 | 17       |

|       | Nesting                                                      | 18       |

|       | Register Specification                                       | 19       |

|       | Control Statement Functions                                  | 20       |

|       | Conditional Expressions                                      | 20<br>44 |

| 3.0   | -                                                            |          |

|       | 3.6.1 Comparison expressions                                 | 45       |

|       | 3.6.2 Test bit expressions                                   | 67       |

|       | 3.6.3 Logical operations                                     | 74       |

| СНАРТ | ER 4 EXPRESSIONS                                             | 81       |

| СНАРТ | ER 5 DIRECTIVES                                              | 125      |

| 5.1   | Overview of Directives                                       | 125      |

| 5.2   | Directive Functions                                          | 125      |

| СНАРТ | ER 6 CONTROL INSTRUCTIONS                                    | 122      |

|       | Overview of Control Instructions                             |          |

|       | Assembler Control Instructions                               |          |

|       | Control Instructions                                         |          |

| 0.3   |                                                              | 130      |

| APPENDIX A | SYNTAX LISTS                    | 141 |

|------------|---------------------------------|-----|

| APPENDIX B | LISTS OF GENERATED INSTRUCTIONS | 145 |

| APPENDIX C | MAXIMUM PERFORMANCE             | 155 |

# List of Figures

| Figur | e No.                         | Title | Page |   |

|-------|-------------------------------|-------|------|---|

|       |                               |       |      |   |

| 1-1.  | Structured Assembler Function |       |      | 2 |

| 1-2.  | Program Development Flowchart |       |      | 3 |

# List of Tables (1/2)

| Table | No. Title                                                                        | Page |

|-------|----------------------------------------------------------------------------------|------|

| 1-1.  | Maximum Performance of Structured Assembler                                      |      |

| 2-1.  | Structured Assembly Language Coding                                              |      |

| 2-2.  | Alphanumeric Characters                                                          |      |

| 2-3.  | Special Characters                                                               |      |

| 2-4.  | Invalid Characters                                                               |      |

| 2-5.  | Reserved Word Symbols                                                            | 11   |

| 2-6.  | Data Sizes                                                                       |      |

| 2-7.  | Output by Structured Assembler                                                   |      |

| 3-1.  | Generated Instructions for switch Statement                                      |      |

| 3-2.  | Comparison Expressions                                                           |      |

| 3-3.  | Test Bit Expressions                                                             |      |

| 3-4.  | Logical Operations                                                               |      |

| 3-5.  | Generated instructions for Comparison Instructions                               |      |

| 3-6.  | Generated Instructions (Control Statement in Lower Case Letters) for Logical AND |      |

| 3-7.  | Generated Instructions (Control Statement in Upper Case Letters) for Logical AND |      |

| 3-8.  | Generated Instructions for Logical OR                                            |      |

| 4-1.  | Assignment Statements                                                            |      |

| 4-2.  | Count Statements                                                                 |      |

| 4-3.  | Exchange Statements                                                              |      |

| 4-4.  | Bit Manipulation Statements                                                      |      |

| 4-5.  | Generated Instructions for Assignments                                           |      |

| 4-6.  | Generated Instructions for Increment Assignments                                 |      |

| 4-7.  | Generated Instructions for Decrement Assignments                                 |      |

| 4-8.  | Generated Instructions for Logical AND Assignments                               |      |

| 4-9.  | Generated Instructions for Logical OR Assignments                                | 102  |

| 4-10. | Generated Instructions for Logical XOR Assignments                               | 106  |

| 4-11. | Generated Instructions for Increment                                             | 112  |

| 4-12. | Generated Instructions for Decrement                                             | 114  |

| 4-13. | Generated Instructions for Exchange                                              | 117  |

| 4-14. | Generated Instructions for Set Bit                                               | 120  |

| 4-15. | Generated Instructions for Clear Bit                                             |      |

| 5-1.  | List of Directives                                                               | 125  |

| 6-1.  | Control Instructions that Can Be Entered Only in Module Headers                  |      |

| 6-2.  | Control Instructions that Are Recognized as the Module Body                      |      |

| 6-3.  | Control Instruction List                                                         |      |

| 6-4.  | Interpretation of Kanji Code                                                     | 139  |

# List of Tables (2/2)

| Table | e No. Title                                                                                                                                                         | Page |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|       | Control Statements<br>Conditional Expressions<br>Expressions                                                                                                        | 142  |

| -     | Directives                                                                                                                                                          |      |

| B-2.  | Generated Instructions for Comparison Expressions<br>Generated Instructions for Test Bit Expressions<br>Generated Instructions for Logic Expressions<br>Expressions |      |

| C-1.  | Maximum Performance of Structured Assembler                                                                                                                         |      |

# [MEMO]

# CHAPTER 1 GENERAL

This chapter describes the functions (the role, etc.) of the ST78K0S in software development for microcontrollers.

#### 1.1 Overview of Structured Assembler

The RA78K0S structured assembler preprocessor is a program in the "RA78K0S Assembler Package" that is used for software development of compact, general-purpose microcontrollers in the 78K/0 Series.

In this manual, the structured assembler preprocessor is abbreviated as the "structured assembler" or the "ST78K0S (structured assembler)".

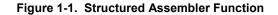

A structured assembler converts structured assembly statements such as "if~else~endif" and "for~next" into assembly language source program files. Control statements are used to enter "if~else~endif" and "for~next" descriptions.

As such, a structured assembler offers the following three advantages.

#### <1> Programs are easy to write

- Each program structure can be written as is, which facilitates the development process from design to coding.

- · There is no need to consider label names for branching.

- Transfer instructions that contain large amounts of code can be entered as assignment statements.

#### <2> Programs are easy to read.

- Program structure is easy to understand.

- · Operations and transfers between memory registers can be entered in a single statement.

- Other programmers' programs are easy to read.

- Program maintenance (revision) is easy.

#### <3> Facilitates desktop debugging

Coding can be done on a one-to-one correspondence with the detail design, thus facilitating desktop debugging.

## 1.2 Overview of Functions

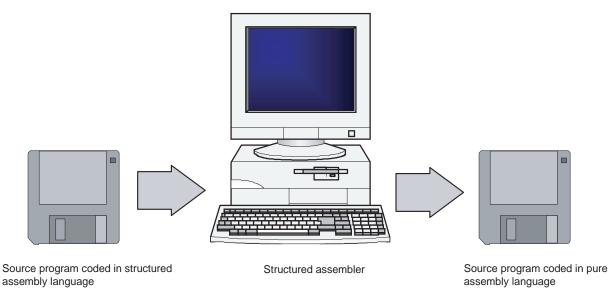

The structured assembler analyzes various control statements, expressions, and directives within a structured assembler source program that are coded according to a specific language specification and outputs an assembler source program that serves as an input source file for the assembler.

Structured statements can be output as comments and converted assembler instructions and ordinary assembly language can all be output as secondary source files.

Error messages are output when errors occur.

The main functions of the structured assembler are listed below.

- <1> Program coding is facilitated by an abundance of C-like control statements.

- <2> C-like assignment statements and assignment operators can be used in coding.

- <3> Control structures and assignment statements can be coded for bit processing.

- <4> It includes C-like symbol definition directives, conditional processing functions, and include directives.

- <5> Since it is the preprocessor that outputs assembler source programs, code optimization can be performed following conversion by the structured assembler.

- <6> A directive is provided for converting to CALLT instructions, so that routines can be registered to a CALLT table following development of a program.

- <7> Easy-to-read assembly lists can be created by changing the assembler source program output position.

Figure 1-2 shows a flowchart of program development.

Figure 1-2. Program Development Flowchart

Caution: Device files are sold separately.

# 1.3 Before Starting Program Development

The maximum performance features of the structured assembler are listed below. Be sure to refer to these values before writing programs.

#### 1.3.1 Maximum performance

The structured assembler's maximum performance values are listed below.

| Item                                                                         | Maximum value          |

|------------------------------------------------------------------------------|------------------------|

| Line length (not including LF or CR)                                         | 218 characters         |

| Number of symbols registered in #define directive (excluding reserved words) | 512 symbols            |

| Nesting levels in control statement                                          | 31 levels              |

| Nesting levels in #ifdef directive                                           | 8 levels               |

| #defcallt directives                                                         | 32                     |

| Nesting of #include directives                                               | Not supported          |

| Number of redefinitions by #define directive                                 | 31 times               |

| Number of operands assigned in a series                                      | 33 <sup>(Note 1)</sup> |

| Logical operator operands                                                    | 17 <sup>(Note 2)</sup> |

| Number of symbols defined by -D option                                       | 30                     |

# Table 1-1. Maximum Performance of Structured Assembler

**Notes 1.** The maximum value is expressed as follows.

S1=S2= ··· S32=S33

Up to 33 symbols, including 32 equal signs (=), can be inserted.

The maximum value is expressed as follows.

expression 1&&expression 2&& ... &&expression 16&&expression 17

Up to 17 expressions and 16 "&&" (or "||") signs can be inserted.

#### 1.3.2 Caution points

#### (1) Word symbols and byte symbols

The structured assembler uses the last character in each user symbol to determine whether the symbol is a word symbol or a byte symbol. The default character for word symbols is "P", and it can be changed via the -SC option.

For details of the -SC option, see the "RA78K0S Series Assembler Package Operation".

#### Example 1

| Structured assembler | Assembler |      |          |

|----------------------|-----------|------|----------|

| SYM = #3             |           | MOV  | SYM, #3  |

| SYMP = #3            |           | MOVW | SYMP, #3 |

#### Example 2 Start command for structured assembler

A>ST78K3 INPUT A -SC@

"@" is used as the character indicating a word symbol.

Input file specification

Structured assembler command name

| Structured a | issembler | Assembler |       |    |

|--------------|-----------|-----------|-------|----|

| SYMP = #     | :3        | MOV       | SYMP, | #3 |

| SYM@ = #     | 3         | MOVW      | SYM@, | #3 |

#### (2) Definition of label (symbol indicating address via assembler)

When defining labels, be sure to enter the label definition on a separate line from the structured assembler statement.

Example

| Good example |           |

|--------------|-----------|

| SYMBOL:      |           |

|              | AX = #10H |

Bad example

SYMBOL: AX = #10H

#### 1.3.3 Environment variables

LANG78K specifies the type of kanji code used for entering comments.

#### (1) Coding format

SETALANG78K = kanji code

Kanji codes

SJIS : Shift JIS code

EUC : EUC code

NONE : No kanji code processing

#### (2) Functions

- If no environment variable has been set, the kanji code specification is set according to the OS, as follows.

- MS-DOS : SJIS

- PC DOS : NONE

- SunOS : EUC

- HP-UX : SJIS

- NEWS-OS : SJIS

- The priority of kanji code specifications is as follows.

- <1> Specification by -ZS, -ZE, or -ZN option

- <2> Specification by kanji code specification control instruction (\$KANJICODE)

- <3> Specification by LANG78K environment variable

- <4> Default specification based on OS

# CHAPTER 2 SOURCE PROGRAM CODING METHODS

This chapter describes coding methods and formats for source programs.

# 2.1 Basic Configuration of Source Programs

Source programs consist of structured assembly language and (pure) assembly language. For further description of assembly language, see the "**RA78K0S Series Assembler Package Language**". Each line (between two LFs) can contain up to 218 characters.

The types of coding used in structured assembly language are listed below in **Table 2-1**. **Structured Assembly Language Coding**.

|                                     |                      | Туре                                                              | Coding                                                                                                                                           |

|-------------------------------------|----------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Structured<br>assembly<br>statement | Control<br>statement | Conditional branch                                                | if~elseif~else~endif<br>if_bit~elseif_bit~else~endif<br>switch~case~default~ends                                                                 |

| Conditio                            |                      | Conditional loop                                                  | for~next<br>while~endw<br>while_bit~endw<br>repeat~until<br>repeat~until_bit                                                                     |

|                                     |                      | Other                                                             | break, continue, goto                                                                                                                            |

|                                     | Expression           | Assignment statement<br>Count statement<br>Exchange statement     | Assignment (=), assignment plus operation (+=, etc.), shift (rotate)<br>assignment (>>=, etc.)<br>Increment (++), decrement ()<br>Exchange (<->) |

| Conditiona<br>expression            |                      | Comparison expression<br>Test bit expression<br>Logical operation | ==, !=, <, >, >=, <=<br>bit address, !bit address<br>Logical AND (&&), Logical OR (  )                                                           |

| Table 2-1. | Structured | Assembly | / Language | Codina |

|------------|------------|----------|------------|--------|

|            | onactarca  | Assembly | Language   | oounig |

Conditional expressions are entered as control statement conditions.

For details, see "3.5 Control Statement Functions".

#### (1) Control statements

Control statements include "if" and "switch~case" statements that represent conditional branches, "for~next", "while", and "repeat~until" statements that represent conditional loops, and "break", "continue", and "goto" statements that represent loop exit processing. For details, see "CHAPTER 3 CONTROL STATEMENTS".

#### (2) Expressions

Expressions include assignment statements, count statements (increment and decrement), and exchange statements. For details, see "CHAPTER 4 EXPRESSIONS".

#### 2.2 Source Program Elements

#### (1) Character set

Letters, numerals, and special characters can be used in source programs.

| Numerals |            | 0      | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9      |  |  |

|----------|------------|--------|---|---|---|---|---|---|---|---|--------|--|--|

| Letters  |            | A<br>N |   |   |   |   |   |   |   |   |        |  |  |

|          | Lower case | a<br>n |   |   |   |   |   | - |   |   | j<br>w |  |  |

#### Table 2-2. Alphanumeric Characters

In the ST78K0S, only the first character in control statements are case-sensitive. Any lower case letters that appear after the first character are converted to upper case letters. However, secondary source files are output using the case specifications in which they were entered.

| ?     Question       @     Unit price       _     Underlinin       White spa       HT     Horizonta       ,     Comma       .     Period | symbol<br>g<br>ce                     | Character used as letter         Character used as letter         Character used as letter         Delimiter symbol for phrases         Character used as white space         Delimiter symbol for operands |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Underlinin<br>White spa<br>HT Horizonta<br>, Comma                                                                                       | g                                     | Character used as letter Delimiter symbol for phrases Character used as white space                                                                                                                         |

| HT Horizonta                                                                                                                             | ice                                   | Delimiter symbol for phrases<br>Character used as white space                                                                                                                                               |

| HT Horizonta<br>, Comma                                                                                                                  |                                       | Character used as white space                                                                                                                                                                               |

| , Comma                                                                                                                                  | tab                                   |                                                                                                                                                                                                             |

| ,                                                                                                                                        |                                       | Delimiter symbol for operands                                                                                                                                                                               |

| . Period                                                                                                                                 |                                       |                                                                                                                                                                                                             |

|                                                                                                                                          |                                       | Bit position symbol for bit symbols                                                                                                                                                                         |

| " Double qu                                                                                                                              | lotation mark                         | Specification character for #INCLUDE directive's disk-type file<br>names                                                                                                                                    |

| ' Single que                                                                                                                             | otation mark                          | Symbol used to mark start and end of character constant                                                                                                                                                     |

| + Plus symb                                                                                                                              | ool                                   | Positive sign or increment operation                                                                                                                                                                        |

| – Minus syn                                                                                                                              | nbol                                  | Negative sign or decrement operation                                                                                                                                                                        |

| & Ampersar                                                                                                                               | nd                                    | Logical AND operator                                                                                                                                                                                        |

| Separator                                                                                                                                | symbol                                | Logical OR operator                                                                                                                                                                                         |

| ^ Upward a                                                                                                                               | rrow symbol                           | Exclusive OR operator                                                                                                                                                                                       |

| ( Left parer                                                                                                                             | thesis                                | Change in operation sequence or expression in control statement                                                                                                                                             |

| ) Right pare                                                                                                                             | enthesis                              |                                                                                                                                                                                                             |

| = Equal syn                                                                                                                              | nbol                                  | Assignment operator, comparison operator                                                                                                                                                                    |

| : Colon                                                                                                                                  |                                       | Delimiter symbol for labels                                                                                                                                                                                 |

| ; Semicolor                                                                                                                              | 1                                     | Comment start symbol or delimiter symbol in control statement expressions                                                                                                                                   |

| # Number s<br>musical n                                                                                                                  | ymbol or sharp symbol (in<br>otation) | First character in structured assembler directive or immediate display symbol                                                                                                                               |

| \$ Dollar sign                                                                                                                           | 1                                     | Location or counter value<br>Display symbol in control instruction                                                                                                                                          |

| ! Exclamati                                                                                                                              | on point                              | Direct addressing specification symbol, negation display symbol                                                                                                                                             |

| < Not equal                                                                                                                              | (less than) symbol                    | Comparison operator                                                                                                                                                                                         |

| > Not equal                                                                                                                              | (more than) symbol                    |                                                                                                                                                                                                             |

| \ Back slas                                                                                                                              | h                                     | Directory specification symbol                                                                                                                                                                              |

| [ Left brack                                                                                                                             | et                                    | Indirect address specification symbol                                                                                                                                                                       |

| ] Right brac                                                                                                                             | ket                                   |                                                                                                                                                                                                             |

| LF Line feed                                                                                                                             |                                       | End of line symbol                                                                                                                                                                                          |

# Table 2-3. Special Characters

An error will occur if any of the following invalid characters are entered.

#### Table 2-4. Invalid Characters

|                                 | ASCII code                                           |

|---------------------------------|------------------------------------------------------|

| Illegal characters              | 00H to 08H, 0BH, 0CH, 0EH to 1FH, 7FH                |

| Unrecognized special characters | % (25H), ' (60H), {(7BH),} (7DH), <sup>–</sup> (7EH) |

| Other characters                | 80H~0FFH                                             |

When an illegal character is entered, an error occurs and each illegal character is replaced by a period (.) when a secondary file is output.

However, invalid characters can be used in comments.

#### (2) Identifiers

Identifiers are names that are attached to numerical data, addresses, etc. Identifiers are used to make the contents of source programs easier to identify. Use #define statements to define details of identifiers (see also "**5.2 Directive Functions**").

#### (3) Symbols

The last character in the symbol name determines whether the structured assembler generates a byte access instruction or a word access instruction. The default setting is P (pair), which can be changed via the -SC option. All character strings other than reserved word symbols can be handled as user symbols. All alphanumeric characters and all other characters that can be established as English alphabet characters can be used as user symbols.

#### (4) Constants

Structured assembly language does not include any constants. However, assembly language constants can be output as is to secondary files (for details of assembly language constants, refer to the **"RA78K0S ASSEMBLER PACKAGE USER'S MANUAL ASSEMBLY LANGUAGE"**

#### (5) Expressions

Expressions are constants, special characters, and symbols that are combined using operators (for details of assembly language expressions, see the "ASSEMBLER PACKAGE USER'S MANUAL ASSEMBLY LANGUAGE".

Be sure to enclose in parentheses any symbols that are separated by white spaces within an assembly language expression.

#### Examples

- <1> Coding method for assembler

- MOV A, # (SYM AND 0FFH)

MOV A, LABEL + 1

<2> Coding method for structured assembler source program

A = # (SYM AND 0FFH)

A = (LABEL + 1)

#### 2.3 Reserved Words

The following table lists reserved words in structured assembly language. For information on instructions and sfr symbols, see the target device's User's Manual.

|                     | Reserved word                               |  |  |  |

|---------------------|---------------------------------------------|--|--|--|

| Control statements  | IF, IF_BIT, ELSEIF, ELSEIF_BIT, ELSE, ENDIF |  |  |  |

|                     | SWITCH, CASE, DEFAULT, ENDS                 |  |  |  |

|                     | FOR, NEXT                                   |  |  |  |

|                     | WHILE, WHILE_BIT, ENDW                      |  |  |  |

|                     | REPEAT, UNTIL, UNTIL_BIT                    |  |  |  |

|                     | BREAK, CONTINUE, GOTO                       |  |  |  |

| Directives          | DFINE                                       |  |  |  |

|                     | IFDEF, ELSE, ENDIF                          |  |  |  |

|                     | INCLUDE                                     |  |  |  |

|                     | DEFCALLT, ENDCALLT                          |  |  |  |

| Operators           | ++,                                         |  |  |  |

|                     | =, +=, -=, &=,  =, ^=, <<=, >>=, <->        |  |  |  |

|                     | ==, !=, <, >=, >, <=, FOREVER               |  |  |  |

| Assembler operators | MOD, NOT                                    |  |  |  |

|                     | AND, OR, XOR                                |  |  |  |

|                     | EQ, NE, GT, GE, LT, LE                      |  |  |  |

|                     | SHL, SHR                                    |  |  |  |

|                     | HIGH, LOW                                   |  |  |  |

|                     | DATAPOS, BITPOS, MASK                       |  |  |  |

#### Table 2-5. Reserved Word Symbols (1/2)

|                                | Reserved word                                       |  |  |  |  |  |

|--------------------------------|-----------------------------------------------------|--|--|--|--|--|

| Assembler control instructions | PROCESSOR, PC                                       |  |  |  |  |  |

|                                | DEBAG, NODEBAG, DEBAGA, NODEBAGA, , DG, NODG        |  |  |  |  |  |

|                                | XREF, XR, NOXREF, NOXR                              |  |  |  |  |  |

|                                | TITLE, TI                                           |  |  |  |  |  |

|                                | SYMLEN, NOSYMLEN                                    |  |  |  |  |  |

|                                | CAP, NOCAP                                          |  |  |  |  |  |

|                                | SYMLIST, NOSYMLIST                                  |  |  |  |  |  |

|                                | FORMFEED, NOFORMFEED                                |  |  |  |  |  |

|                                | WIDTH, LENGTH                                       |  |  |  |  |  |

|                                | ТАВ                                                 |  |  |  |  |  |

|                                | KANJICODE                                           |  |  |  |  |  |

|                                | IC                                                  |  |  |  |  |  |

|                                | EJECT, EJ                                           |  |  |  |  |  |

|                                | LIST, LI, NOLIST, NOLI                              |  |  |  |  |  |

|                                | GEN, NOGEN                                          |  |  |  |  |  |

|                                | COND, NOCOND                                        |  |  |  |  |  |

|                                | SUBTITLE, ST                                        |  |  |  |  |  |

|                                | SET, RESET                                          |  |  |  |  |  |

|                                | _IF, _ELSEIF,                                       |  |  |  |  |  |

| Registers                      | CY, Z                                               |  |  |  |  |  |

|                                | А                                                   |  |  |  |  |  |

|                                | R0, R1, R2, R3, R4, R5, R6, R7, X, B, C, D, E, H, L |  |  |  |  |  |

|                                | PSW                                                 |  |  |  |  |  |

|                                | AX                                                  |  |  |  |  |  |

|                                | RP0, RP1, RP2, RP3, BC, DE, HL                      |  |  |  |  |  |

|                                | SP                                                  |  |  |  |  |  |

| Other                          | DGS, DGL, TOL_INF, SJIS, EUC, NONE                  |  |  |  |  |  |

# Table 2-5. Reserved Word Symbols (2/2)

#### 2.4 Label Generation Rules

When using control statements in assembler instructions, the structured assembler generates labels for branch instructions.

Labels generated by the structured assembler have the format "?Ldddd".

The "dddd" represents a decimal value of 1 or more, output with suppression of zeros and left alignment. Therefore, do not enter any labels using this "?Ldddd" format.

#### 2.5 Size Specification

Size specifications can be made to change the data size of symbols entered in the left or right sides of an assignment expression or a conditional expression or case symbols in switch statements.

#### [Coding format]

$(\Delta size\_specification\_character\Delta)$

#### [Function]

<1> If the size character is either "B" or "b", the data size is changed to bytes.

#### [Description]

- <1> An error will occur if the size specification character is incorrect.

- <2> An error will occur if a size specification is entered in an assignment expression or a conditional expression which does not support size specifications.

- <3> If a size specification is made to a register, coding can only be done using the same specification. The data size cannot be changed. If the data size is different, an error will occur.

- <4> When specifying a user symbol, be sure to change the data size to the specified data size.

- <5> If a size specification has been entered for a direct access specification symbol or an indirect access specification symbol or for immediate data, the size specification will be ignored and the data size will not be changed.

- <6> Word access cannot be specified in size specifications.

# 2.6 Data Sizes

The structured assembler checks the data size of symbols. This is because the symbols differ according to the instruction being generated. However, the structured assembler allows the assembler to determine whether or not the symbol definitions and constants are entered correctly.

The data sizes checked by the structured assembler are listed below.

#### Table 2-6. Data Sizes

| а | CY                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b | Bit symbols (except [HL]. $\beta$ )<br>This structured assembler recognizes bit sfrs and symbols entered using the format " $\alpha$ . $\beta$ " as bit symbols.<br>Items that can be entered as " $\alpha$ " include byte user symbols, word user symbols, byte-specified user symbols, sfrs, constants, A, and PSW.<br>Items that can be entered as " $\beta$ " include byte user symbols, word user symbols, and constants. |

| С | [HL]. $\beta$<br>Items that can be entered as " $\beta$ " include byte user symbols, word user symbols, and constants.                                                                                                                                                                                                                                                                                                         |

| d | Byte user symbol                                                                                                                                                                                                                                                                                                                                                                                                               |

| е | byte-specified user symbols, sfrs that overlaps saddrp                                                                                                                                                                                                                                                                                                                                                                         |

| f | A                                                                                                                                                                                                                                                                                                                                                                                                                              |

| g | Byte registers (except A, R0, R1)                                                                                                                                                                                                                                                                                                                                                                                              |

| h | R0                                                                                                                                                                                                                                                                                                                                                                                                                             |

| i | R1                                                                                                                                                                                                                                                                                                                                                                                                                             |

| j | sfr                                                                                                                                                                                                                                                                                                                                                                                                                            |

| k | PSW                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Ι | Word user symbol                                                                                                                                                                                                                                                                                                                                                                                                               |

| m | sfrp that overlaps saddrp                                                                                                                                                                                                                                                                                                                                                                                                      |

| n | AX                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0 | Word register (except AX, RP0)                                                                                                                                                                                                                                                                                                                                                                                                 |

| р | RP0                                                                                                                                                                                                                                                                                                                                                                                                                            |

| q | sfrp                                                                                                                                                                                                                                                                                                                                                                                                                           |

| r | SP                                                                                                                                                                                                                                                                                                                                                                                                                             |

| S | Direct access specification symbols<br>These are symbols that are specified using the format "!addr".<br>Byte user symbols, word user symbols, constants, and "\$" can be entered as "addr".                                                                                                                                                                                                                                   |

| t | Indirect access specification symbols<br>These are symbols that are specified using the format "[HL]" or "[HL+byte]".<br>Byte user symbols, constants, and "\$" can be entered as "byte".                                                                                                                                                                                                                                      |

| u | Special indirect access specification symbols<br>These are symbols that are specified using the format "[DE]".                                                                                                                                                                                                                                                                                                                 |

| V | Immediate data<br>These are symbols that are specified using the format "#date".<br>Byte user symbols, word user symbols, constants, and "\$" can be entered as "date".                                                                                                                                                                                                                                                        |

#### 2.7 Comments

Any character string that appears after a semicolon (;) until the next line feed (LF) is regarded as a comment statement, which is not processed but is simply output to a secondary file. Comment statements can be entered at any position in a line of code.

However, since semicolons are used between parentheses as expression delimiters in the "for~next" syntax, the two semicolons that are entered between parentheses are not regarded as the start of a comment statement.

All of the characters listed under "2.2 (1) Character set" can be used in comments.

Processing of illegal characters does not occur when the illegal characters are included in a comment or comment statement.

# 2.8 Tool Information

The structured assembler outputs tool information.

If an input source file contains tool information that has been output by the structured assembler, the "\$" character at the start of the information is replaced with ";".

The output position is the end of the module header. The only types of statements that can be entered in module headers are assembler control instructions, comment statements, and line feeds.

#### [Output format]

\$TOL\_INF 2FH, second parameter, third parameter, 0FFFH

2FH indicates that it is tool information output by the structured assembler preprocessor.

The second parameter indicates the version number of this preprocessor.

The version number is output either as a hexadecimal value or, if the value is not converted, as the decimal number image that was shown at startup.

#### (Example)

Version number  $1.00 \rightarrow 100 H$

The third parameter is used to indicate this preprocessor's error messages.

- 0H Normal end

- 1H Fatal error, exited

- 2H Warning, exited

- 3H Fatal error and warning, exited

0FFFFH indicates language-related information. This is a fixed value for this preprocessor.

# 2.9 Output Results of Input Source Files by Structured Assembler

Input source files are output as follows by the structured assembler.

# Table 2-7. Output by Structured Assembler

| Input source program file                                                             | Secondary source program file |

|---------------------------------------------------------------------------------------|-------------------------------|

| Structured assembler control statements<br>Structured assembler expression statements | Output as comments            |

| Structured assembler directives                                                       | Not output                    |

| #INCLUDE                                                                              | Outputs include contents      |

| Source alias set by #IFDEF                                                            | Not output                    |

| Comments                                                                              | Output as comments            |

| Other lines                                                                           | Output as is                  |

# **CHAPTER 3 CONTROL STATEMENTS**

This chapter presents examples in describing control statement functions.

#### 3.1 Overview of Control Statements

Control statements are used to structurally code the flow of program control. Control statements include the followings.

- Conditional branch (IF~THEN~ELSE)

- (1) if~elseif~else~endif

- (2) if\_bit~elseif\_bit~else~endif

- (3) switch~case~default~ends

#### Conditional loop (DO~WHILE)

- (4) for~next (loop increment)

- (5) while~endw (loop condition judgment before processing)

- (6) while\_bit~endw (loop condition judgment before processing)

- (7) repeat~until (loop condition judgment after processing)

- (8) repeat~until\_bit (loop condition judgment after processing)

- (9) break (Loop block break)

- (10) continue (Loop block loop)

- (11) goto (Exit for exception handling)

#### 3.2 Control Statement Characters

The instruction generated by a control statement differs fundamentally depending on whether upper case or lower case letters are used in the control statement. For example, the different statement sizes between "if~endif" and "IF~ENDIF" can preclude direct branching via the conditional branch instruction generated by processing of the condition expression.

However, ensuring that the statement will always be branched correctly has the disadvantage of reducing the program's efficiency as an object.

As a solution to this problem, the user is able to set upper or lower case in order to improve the object efficiency rate. If there is no need to improve the object efficiency rate, the user can omit changing the character size as long as coding uses upper case letters.

Since control statements generate conditional branch instructions, be sure to specify whether or not the relative address is within 128 bytes.

In control statements, "if" and "elseif" are reserved words. The structured assembler determines whether the first character in a control statement reserved word is an upper case or lower case letter.

IF, If ... First letter is upper case, so coding is determined as upper case.

if, iF  $\cdots$  First letter is lower case, so coding is determined as lower case.

If entered in upper case … branches using a combination of conditional branch instruction and BR directive. If entered in lower case … branches directly using a conditional directive.

Paired control statements (such as "if, else,endif") can have mixed upper case and lower case letters. In other words, it is possible to enter one as "IF~else~ENDIF".

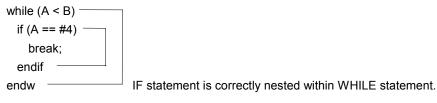

#### 3.3 Nesting

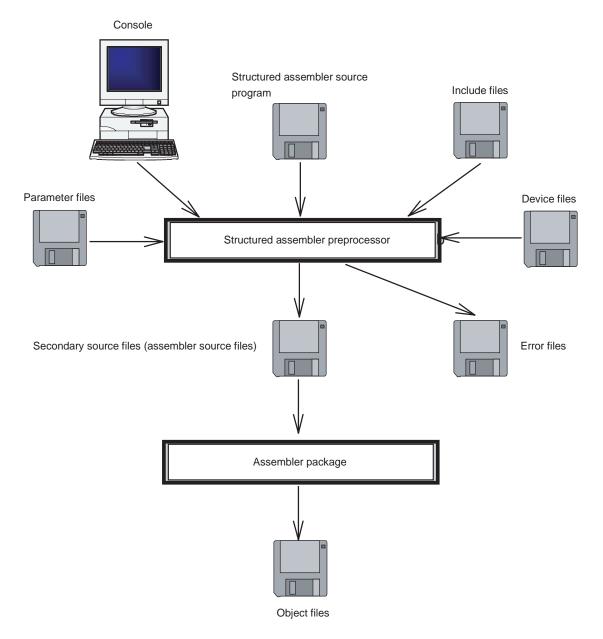

Control statements can be nested. Generally, up to 31 nesting levels are allowed. However, control statements cannot be intersected.

# (Example of incorrect coding)

# (Example of correct coding)

## 3.4 Register Specification

#### [Coding format]

$([\Delta] [=] [\Delta] \text{ register name } [\Delta])$

#### [Function]

#### <1> If a register is specified immediately after a comparison expression

After the instruction to transfer the left side to the specified register, a comparison expression is generated to compare the specified register with the right side.

#### (Example)

?L1:

```

CMP SYM1,#5;if(SYM1!=#5 && SYM2>=#0 && SYM3<#80H(A))

BZ $?L1

CMP SYM2,#0

BC $?L1

MOV A,SYM3

CMP A,#80H

BNC $?L1

;endif</pre>

```

#### <2> If a register is specified after a control statement

During the generated of each comparison expression, after the instruction for transferring the left side to the specified register is generated, a comparison expression is generated to compare the specified register with the right side.

#### (Example)

?L2:

| MOV | / A,R  | 4 ;if(H | R4!=#5 8 | && R2>=#0 | && R. | 3<#80H | ) (A) |

|-----|--------|---------|----------|-----------|-------|--------|-------|

| CMI | Р А,#  | 5       |          |           |       |        |       |

| BZ  | \$?L   | 2       |          |           |       |        |       |

| MOV | A,R    | 2       |          |           |       |        |       |

| CMI | P A,#  | 0       |          |           |       |        |       |

| BC  | \$?L   | 2       |          |           |       |        |       |

| MOV | A,R    | 3       |          |           |       |        |       |

| CMI | P A,#  | 80H     |          |           |       |        |       |

| BNG | 2 \$?L | 2       |          |           |       |        |       |

|     |        | ;end:   | if       |           |       |        |       |

#### <3> If both (a) and (b) are specified