# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**User's Manual**

# CubeSuite Ver. 1.00

# **Integrated Development Environment**

V850 Coding

Target Device V850 Microcontrollers

Document No. U19383EJ1V0UM00 (1st edition) Date Published September 2008

© NEC Electronics Corporation 2008 Printed in Japan

#### User's Manual U19383EJ1V0UM

# [MEMO]

# SUMMARY OF CONTENTS

CHAPTER 1 GENERAL ... 22

CHAPTER 2 FUNCTIONS ... 23

CHAPTER 3 COMPILER LANGUAGE SPECIFICATIONS ... 73

CHAPTER 4 ASSEMBLY LANGUAGE SPECIFICATIONS ... 192

CHAPTER 5 LINK DIRECTIVE SPECIFICATION ... 699

CHAPTER 6 FUNCTIONAL SPECIFICATION ... 721

CHAPTER 7 STARTUP ... 900

CHAPTER 8 ROMIZATION ... 923

CHAPTER 9 CROSS REFERENCE OF COMPILER AND ASSEMBLER ... 938

CHAPTER 10 CAUTIONS ... 942

APPENDIX A INDEX ... 950

All trademarks or registered trademarks in this document are the property of their respective owners.

4

- The information in this document is current as of September, 2008. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

# PREFACE

This manual describes the role of the CubeSuite integrated development environment for developing applications and systems for V850 microcontrollers and provides an outline of its features.

CubeSuite is an integrated development environment (IDE) for V850 microcontrollers, integrating the necessary tools for the development phase of software (e.g. design, implementation, and debugging) into a single platform.

By providing an integrated environment, it is possible to perform all development using just this product, without the need to use many different tools separately.

| Readers                 | This manual is intended for users who wish to understand the functions of the CubeSuite and design software and hardware application systems.                                        |                                                                                           |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Purpose                 | This manual is intended to give users an understanding of the functions of the Cubesuite to use for reference in developing the hardware or software of systems using these devices. |                                                                                           |

| Organization            | This manual can be broadly divided into the following units.                                                                                                                         |                                                                                           |

|                         | CHAPTER 1 GENERAL<br>CHAPTER 2 FUNCTIO                                                                                                                                               |                                                                                           |

|                         |                                                                                                                                                                                      | R LANGUAGE SPECIFICATIONS                                                                 |

|                         |                                                                                                                                                                                      |                                                                                           |

|                         | CHAPTER 5 LINK DIRE<br>CHAPTER 6 FUNCTIO                                                                                                                                             |                                                                                           |

|                         | CHAPTER 7 STARTUP                                                                                                                                                                    |                                                                                           |

|                         | CHAPTER 8 ROMIZATI                                                                                                                                                                   | -                                                                                         |

|                         | CHAPTER 9 CROSS RI<br>CHAPTER 10 CAUTION                                                                                                                                             | EFERENCE OF COMPILER AND ASSEMBLER                                                        |

|                         | APPENDIX A INDEX                                                                                                                                                                     |                                                                                           |

| How to Read This Manual | It is assumed that the readers of this manual have general knowledge of electricity, logic circuits, and microcontrollers.                                                           |                                                                                           |

| Conventions             | Data significance:                                                                                                                                                                   | Higher digits on the left and lower digits on the right                                   |

|                         | -                                                                                                                                                                                    | XXX (overscore over pin or signal name)<br>Footnote for item marked with Note in the text |

|                         | Note:<br>Caution:                                                                                                                                                                    | Information requiring particular attention                                                |

|                         | Remark:                                                                                                                                                                              | Supplementary information                                                                 |

|                         | Numeric representation:                                                                                                                                                              | Decimal XXXX                                                                              |

|                         |                                                                                                                                                                                      | Hexadecimal 0xXXXX                                                                        |

#### **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

| Document Name                      |             | Document No.  |

|------------------------------------|-------------|---------------|

| CubeSuite Ver.1.00                 | Start       | U19377E       |

| Integrated Development Environment | Programming | U19390E       |

| User's Manual                      | Message     | U19391E       |

|                                    | V850 Coding | This document |

|                                    | V850 Build  | U19386E       |

|                                    | V850 Debug  | U19389E       |

|                                    | V850 Design | U19380E       |

Caution The related documents listed above are subject to change without notice. Be sure to use the latest edition of each document when designing.

#### User's Manual U19383EJ1V0UM

# [MEMO

# TABLE OF CONTENTS

# CHAPTER 1 GENERAL ... 22

- 1.1 Outline ... 22

- 1.2 Special Features ... 22

# CHAPTER 2 FUNCTIONS ... 23

- 2.1 Variables (C language) ... 23

- 2.1.1 Allocating to sections accessible with short instructions ... 23

- 2.1.2 Changing allocated section ... 24

- 2.1.3 Defining variables for use during standard and interrupt processing ... 26

- 2.1.4 Defining user port ... 28

- 2.1.5 Defining const constant pointer ... 29

- 2.2 Functions ... 30

- 2.2.1 Changing area to be allocated to ... 30

- 2.2.2 Calling an away function ... 31

- 2.2.3 Embedding assembler instructions ... 32

- 2.2.4 Executing in RAM ... 32

- 2.3 Using Microcomputer Functions ... 33

- 2.3.1 Accessing peripheral I/O register with C language ... 33

- 2.3.2 Describing interrupt processing with C language ... 34

- 2.3.3 Using CPU instructions in C language ... 35

- 2.3.4 Creating a self-programming boot area ... 36

- 2.4 Variables (Assembler) ... 37

- 2.4.1 Defining variables with no initial values ... 37

- 2.4.2 Defining const constants with initial values ... 38

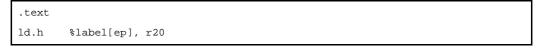

- 2.4.3 Referencing section addresses ... 39

- 2.5 Startup Routine ... 40

- 2.5.1 Secure stack area ... 40

- 2.5.2 Securing stack area and specifying allocation ... 42

- 2.5.3 Initializing RAM ... 43

- 2.5.4 Preparing function and variable access ... 44

- 2.5.5 Preparing to use code size reduction function ... 47

- 2.5.6 Ending startup routine ... 48

- 2.6 Link Directives ... 49

- 2.6.1 Adding function section allocation ... 49

- 2.6.2 Adding section allocation for variables ... 49

- 2.6.3 Distributing section allocation ... 50

- 2.7 Reducing Code size ... 52

- 2.7.1 Reducing code size (C language) ... 52

- 2.7.2 Reducing variable area with variable definition method ... 65

- 2.8 Accelerating Processing ... 68

- 2.8.1 Accelerate processing with description method ... 68

- 2.9 Compiler and Assembler Mutual References ... 70

- 2.9.1 Mutually referencing variables ... 70

- 2.9.2 Mutually referencing functions ... 72

# CHAPTER 3 COMPILER LANGUAGE SPECIFICATIONS ... 73

- 3.1 Basic Language Specifications ... 73

- 3.1.1 Processing system dependent Items ... 73

- 3.1.2 Ansi option ... 86

- 3.2 Environment During Compilation ... 87

- 3.2.1 Internal representation and value area of data ... 87

- 3.2.2 General-purpose registers ... 95

- 3.2.3 Referencing data ... 96

- 3.2.4 Software register bank ... 96

- 3.2.5 Mask register ... 98

- 3.2.6 Device file ... 101

- 3.3 Extended Language Specifications ... 103

- 3.3.1 Macro name ... 103

- 3.3.2 Keyword ... 104

- 3.3.3 #pragma directive ... 104

- 3.3.4 Using expanded specifications ... 106

- 3.3.5 Modification of C-source ... 162

- 3.4 Function Call Interface ... 163

- 3.4.1 Calling between C functions ... 163

- 3.4.2 Prologue/Epilogue processing function ... 176

- 3.4.3 far jump function ... 179

- 3.5 Expanded Function of CC78Kx ... 186

- 3.5.1 #pragma directive ... 186

- 3.5.2 Assembler control instructions ... 190

- 3.5.3 Specifying interrupt/exception handler ... 190

- 3.5.4 Expanded function not supported ... 190

- 3.6 Section Name List ... 191

#### CHAPTER 4 ASSEMBLY LANGUAGE SPECIFICATIONS ... 192

4.1 Description of Source ... 192

- 4.1.1 Description ... 192

- 4.1.2 Expression ... 202

- 4.1.3 Operators ... 205

- 4.1.4 Arithmetic operators ... 206

- 4.1.5 Shift operators ... 206

- 4.1.6 Bitwise logical operators ... 207

- 4.1.7 Comparison operators ... 207

- 4.1.8 Operation rules ... 209

- 4.1.9 Definition of absolute expression ... 210

- 4.1.10 Identifiers ... 212

- 4.1.11 Characteristics of an operand ... 212

- 4.2 Quasi Directives ... 227

- 4.2.1 Outline ... 227

- 4.2.2 Section definition quasi directives ... 228

- 4.2.3 Symbol control quasi directives ... 252

- 4.2.4 Location counter control quasi directives ... 259

- 4.2.5 Area allocation quasi directives ... 262

- 4.2.6 Program linkage quasi directives ... 271

- 4.2.7 Assembler control quasi directive ... 277

- 4.2.8 File input control quasi directives ... 282

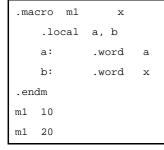

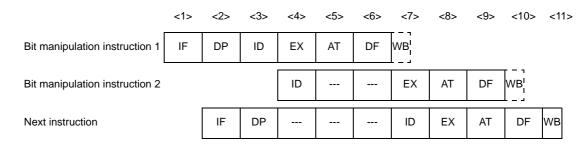

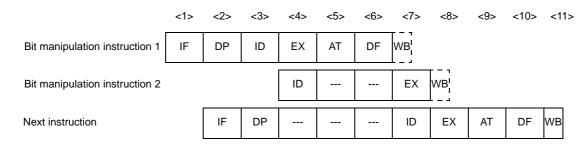

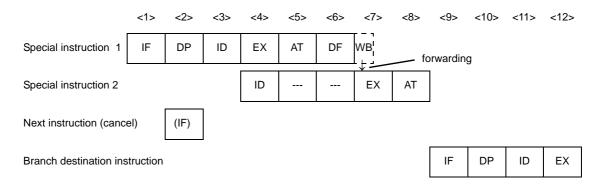

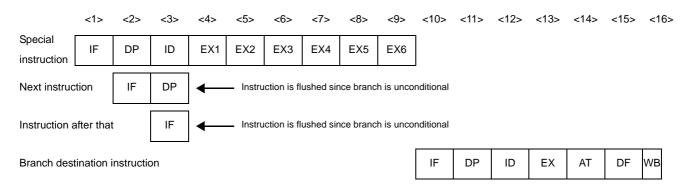

4.2.9 Repetitive assembly quasi directives ... 285 4.2.10 Conditional assembly quasi directives ... 288 4.2.11 Skip quasi directives ... 301 4.2.12 Macro quasi directives ... 306 4.3 Macro ... 311 4.3.1 Outline ... 311 4.3.2 Usage of macro ... 312 4.3.3 Symbols in macro ... 312 4.3.4 Macro operator ... 313 4.4 Reserved Words ... 314 4.5 Instructions ... 315 4.5.1 Memory space ... 315 4.5.2 Register ... 316 4.5.3 Addressing ... 353 4.5.4 Instruction set ... 361 4.5.5 Description of instructions ... 377 4.5.6 Load/Store instructions ... 378 4.5.7 Arithmetic operation instructions ... 387 4.5.8 Saturated operation instructions ... 450 4.5.9 Logical instructions ... 464 4.5.10 Branch instructions ... 510 4.5.11 Bit Manipulation instructions ... 527 4.5.12 Stack manipulation instructions ... 536 4.5.13 Special instructions ... 541 4.5.14 Pipeline (V850) ... 565 4.5.15 Pipeline (V850ES) ... 589 4.5.16 Pipeline (V850E1) ... 629 4.5.17 Pipeline (V850E2) ... 667

# CHAPTER 5 LINK DIRECTIVE SPECIFICATION ... 699

5.1 Coding Method ... 699

- 5.1.1 Characters used in link directive file ... 700

- 5.1.2 Link directive file name ... 700

- 5.1.3 Segment directive ... 701

- 5.1.4 Mapping directive ... 707

- 5.1.5 Symbol directive ... 715

- 5.2 Reserved Words ... 720

### CHAPTER 6 FUNCTIONAL SPECIFICATION ... 721

6.1 Supplied Libraries ... 721

- 6.1.1 Standard library ... 723

- 6.1.2 Mathematical library ... 729

- 6.1.3 ROMization library ... 731

- 6.2 Header Files ... 732

- 6.3 Re-entrant ... 732

- 6.4 Library Function ... 733

- 6.4.1 Functions with variable arguments ... 733

- 6.4.2 Character string functions ... 737

- 6.4.3 Memory management functions ... 755

- 6.4.4 Character conversion functions ... 763

- 6.4.5 Character classification functions ... 769

- 6.4.6 Standard I/O functions ... 782

- 6.4.7 Standard utility functions ... 814

- 6.4.8 Non-local jump functions ... 841

- 6.4.9 Mathematical functions ... 844

- 6.4.10 Copy function ... 885

- 6.5 Runtime Library ... 886

- 6.6 Library Consumption Stack List ... 888

- 6.6.1 Standard library ... 888

- 6.6.2 Mathematical library ... 898

- 6.6.3 ROMization library ... 899

# CHAPTER 7 STARTUP ... 900

- 7.1 Functional Outline ... 900

- 7.2 File Contents ... 900

- 7.3 Startup Routine ... 901

- 7.3.1 Setting RESET handler when reset is input ... 902

- 7.3.2 Setting of register mode of start up routine ... 902

- 7.3.3 Securing stack area and setting stack pointer ... 903

- 7.3.4 Securing argument area for main function ... 904

- 7.3.5 Setting text pointer (tp) ... 904

- 7.3.6 Setting global pointer (gp) ... 905

- 7.3.7 Setting element pointer (ep) ... 906

- 7.3.8 Setting mask value to mask registers (r20 and r21) ... 906

- 7.3.9 Initializing peripheral I/O registers that must be initialized before execution of main function ... 907

- 7.3.10 Initializing user target that must be initialized before execution of main function ... 908

- 7.3.11 Clearing sbss area to 0 ... 908

- 7.3.12 Clearing bss area to 0 ... 909

- 7.3.13 Clearing sebss area to 0 ... 910

- 7.3.14 Clearing tibss.byte area to 0 ... 911

- 7.3.15 Clearing tibss.word area to 0 ... 912

- 7.3.16 Clearing sibss area to 0 ... 913

- 7.3.17 Setting of CTBP value for prologue/epilogue runtime library of functions [V850E] ... 913

- 7.3.18 Setting of programmable peripheral I/O register value [V850E] ... 914

- 7.3.19 Setting r6 and r7 as argument of main function ... 915

- 7.3.20 Branching to main function (when not using real-time OS) ... 915

- 7.3.21 Branching to initialization routine of real-time OS (when using real-time OS) ... 916

- 7.4 Coding Example ... 917

# CHAPTER 8 ROMIZATION ... 923

- 8.1 Outline ... 923

- 8.2 rompsec Section ... 925

- 8.2.1 Types of sections to be packed ... 925

- 8.2.2 Size of rompsec section ... 925

- 8.2.3 rompsec section and link directive ... 926

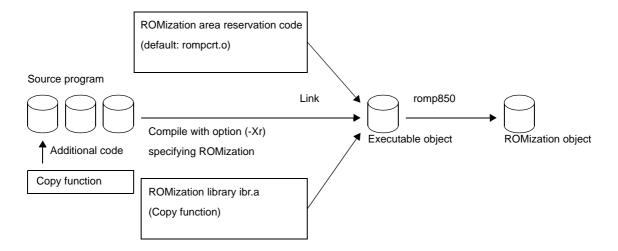

- 8.3 Creation of Object for ROMization ... 928

- 8.3.1 Creation procedure (default) ... 928

8.3.2 Creation procedure (customize) ... 930

8.4 Copy Function ... 933

### CHAPTER 9 CROSS REFERENCE OF COMPILER AND ASSEMBLER ... 938

- 9.1 Method of Accessing Arguments and Automatic Variables ... 938

- 9.2 Method of Storing Return Value ... 938

- 9.3 Calling of Assembly Language Routine from C Language ... 939

- 9.4 Calling of C Language Routine from Assembly Language ... 940

- 9.5 Reference of Argument Defined by Other Language ... 941

### CHAPTER 10 CAUTIONS ... 942

- 10.1 Delimiting Folder/Path ... 942

- **10.2 Option Specification Sequence ... 942**

- 10.3 Mixing with K&R Format in Function Declaration/Definition ... 943

- 10.4 Output of Other Than Position-Independent Codes ... 944

- 10.5 Count of Derivative Type Qualification for Type Configuration ... 944

- 10.6 Length of Identifier and Valid Number of Characters ... 944

- 10.7 Number of Times of Block Nesting ... 945

- 10.8 Number of case Labels in switch Statement ... 945

- 10.9 Floating-Point Operation Exception in Operation of Constant Expression ... 945

- 10.10 Merging Vast/Large-Quantity File ... 945

- 10.11 Optimization of Vast File ... 945

- 10.12 Library File Search by Specifying Option ... 946

- 10.13 Volatile Qualifier ... 946

- 10.14 Extra Brackets in Function Declaration ... 949

APPENDIX A INDEX ... 950

# **LIST OF FIGURES**

| Figure No. Title, Page                                                                               |

|------------------------------------------------------------------------------------------------------|

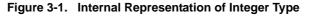

| 3-1 Internal Representation of Integer Type 87                                                       |

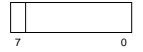

| 3-2 Internal Representation of Floating-Point Type 88                                                |

| 3-3 Internal Representation of Pointer Type 88                                                       |

| 3-4 Internal Representation of Enumerate Type 89                                                     |

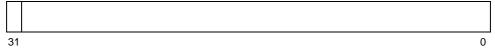

| 3-5 Internal Representation of Array Type 89                                                         |

| 3-6 Internal Representation of Structure Type 90                                                     |

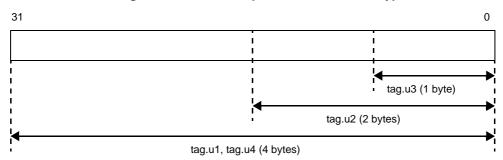

| 3-7 Internal Representation of Union Type 91                                                         |

| 3-8 Internal Representation of Bit Field 92                                                          |

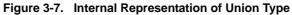

| 3-9 Register Modes and Usable Registers 97                                                           |

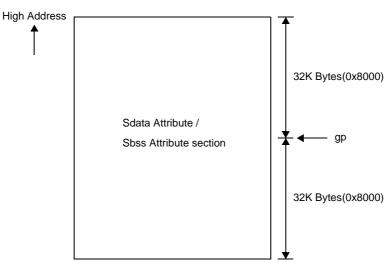

| 3-10 sdata and sbss Attribute Sections 106                                                           |

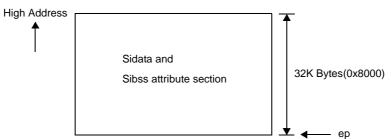

| 3-11 sidata and sibss Attribute Sections 108                                                         |

| 3-12 sdata and sbss Attribute Sections 109                                                           |

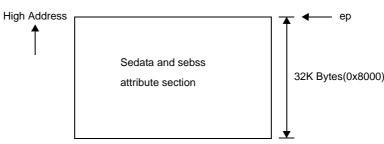

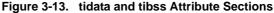

| 3-13 tidata and tibss Attribute Sections 109                                                         |

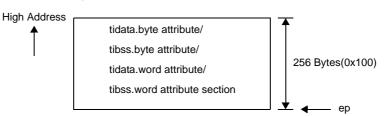

| 3-14 tidata and tibss Attribute Sections 111                                                         |

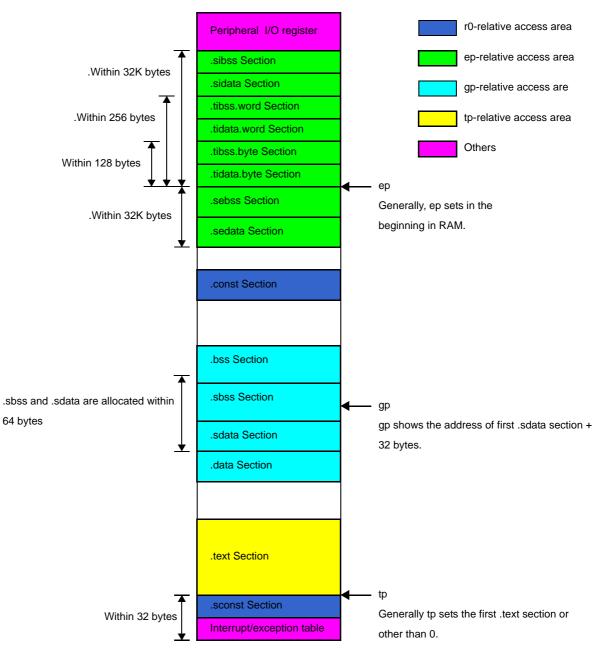

| 3-15 Image of Interrupt Handler Address 131                                                          |

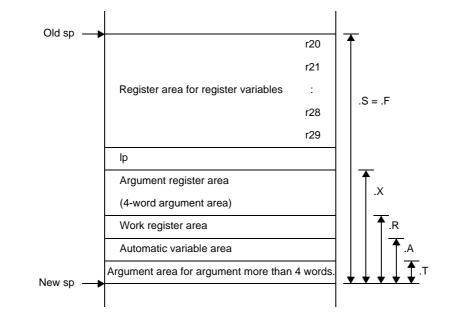

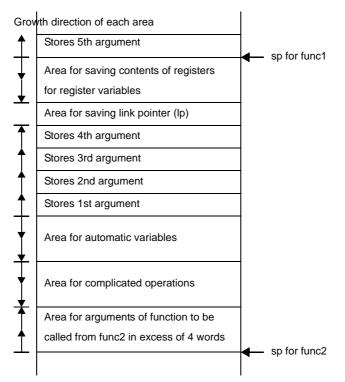

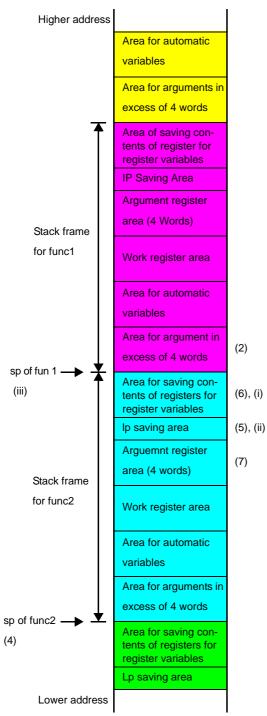

| 3-16 Stack Frame (When Argument Register Area Is Located at Center of Stack) 164                     |

| 3-17 Stack Frame (When Argument Register Area Is Located at Beginning of Stack) 164                  |

| 3-18 Generation/Disappearance of Stack Frame (When Argument Register Area Is Located at Center of    |

| Stack) 166                                                                                           |

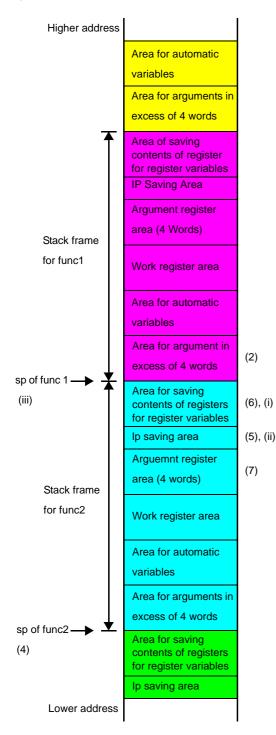

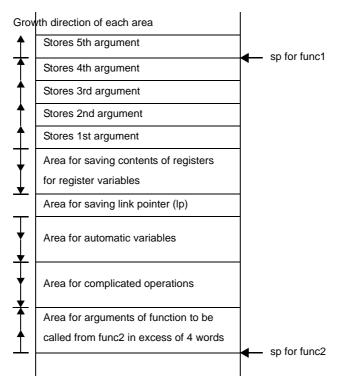

| 3-19 Stack Growth Direction of Each Area of Stack Frame 167                                          |

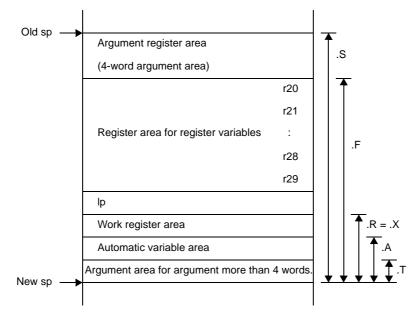

| 3-20 Generation/Disappearance of Stack Frame (When Argument Register Area Is Located at Beginning of |

| Stack) 171                                                                                           |

| 3-21 Stack Growth Direction of Each Area of Stack Frame 172                                          |

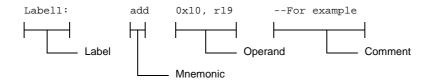

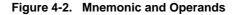

| 4-1 Organization of Assembly Language Statement 192                                                  |

| 4-2 Mnemonic and Operands 196                                                                        |

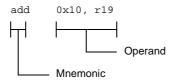

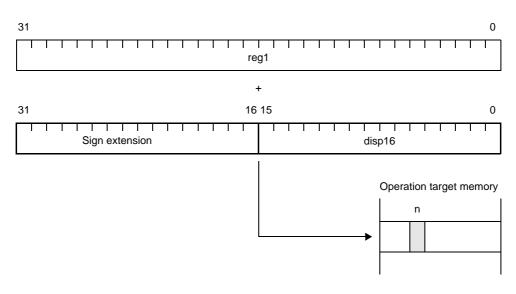

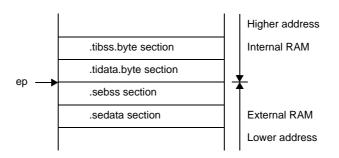

| 4-3 Memory Location Image of Internal RAM 218                                                        |

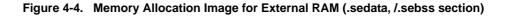

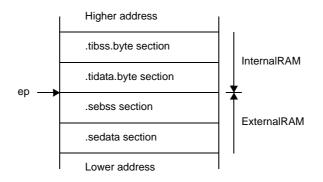

| 4-4 Memory Allocation Image for External RAM (.sedata, /.sebss section) 219                          |

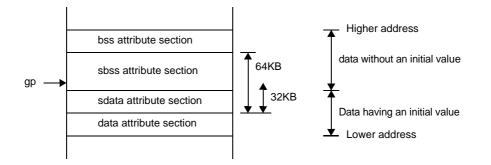

| 4-5 Memory Location Image of gp Offset Reference Section 221                                         |

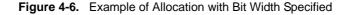

| 4-6 Example of Allocation with Bit Width Specified 263                                               |

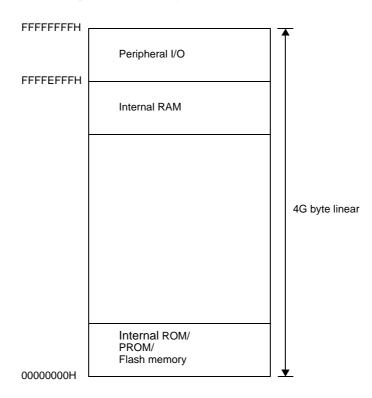

| 4-7 Memory Map of V850 Microcontroller 315                                                           |

| 4-8 Program Register 316                                                                             |

| 4-9 System Register 317                                                                              |

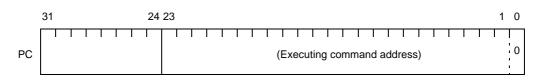

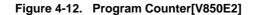

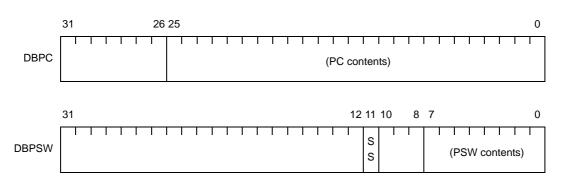

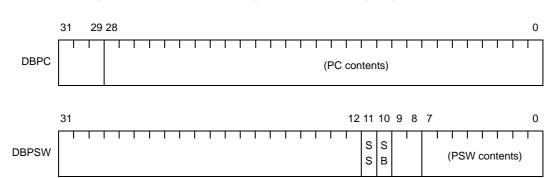

| 4-10 Program Counter [V850] 319                                                                      |

| 4-11 Program Counter[V850ES, V850E1] 319                                                             |

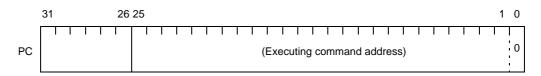

| 4-12 Program Counter[V850E2] 319                                                                     |

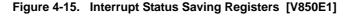

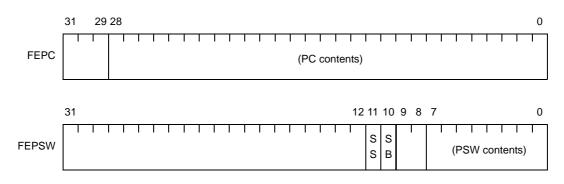

| 4-13 Interrupt Status Saving Registers [V850] 321                                                    |

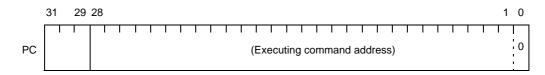

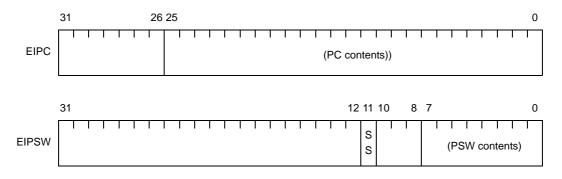

| 4-14 Interrupt Status Saving Registers [V850ES] 322                                                  |

| 4-15 Interrupt Status Saving Registers [V850E1] 322                                                  |

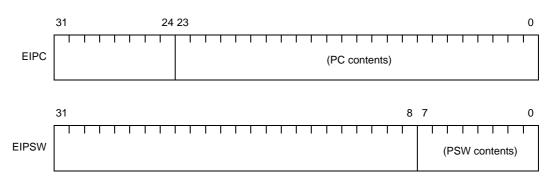

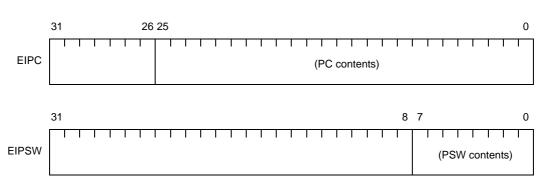

| 4-16 Interrupt Status Saving Registers [V850E2] 322                                                  |

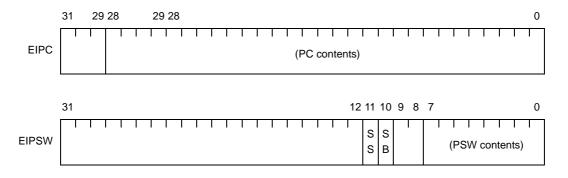

4-17 NMI Status Saving Registers [V850] ... 323

- 4-18 NMI Status Saving Registers [V850ES] ... 323

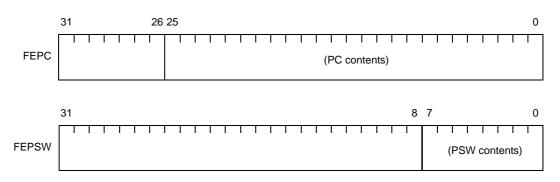

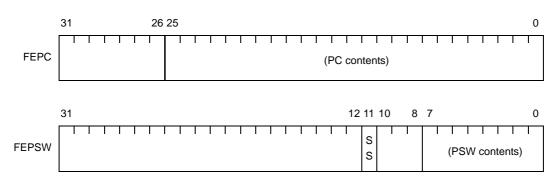

- 4-19 NMI Status Saving Registers [V850E1] ... 324

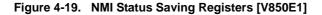

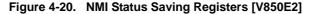

- 4-20 NMI Status Saving Registers [V850E2] ... 324

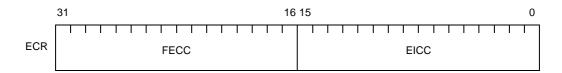

- 4-21 Exception Cause Register [V850, V850ES, V850E1, V850E2] ... 324

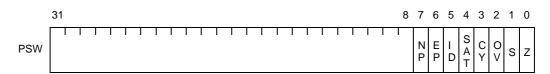

- 4-22 Program Status Word [V850, V850ES] ... 325

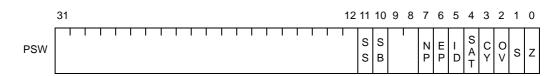

- 4-23 Program Status Word [V850E1] ... 327

- 4-24 Program Status Word [V850E2] ... 329

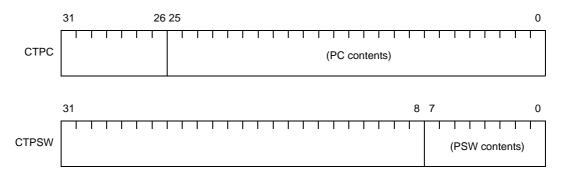

- 4-25 CALLT Caller Status Saving Registers [V850ES] ... 331

- 4-26 CALLT Caller Status Saving Registers [V850E1] ... 331

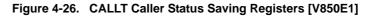

- 4-27 CALLT Caller Status Saving Registers [V850ES] ... 332

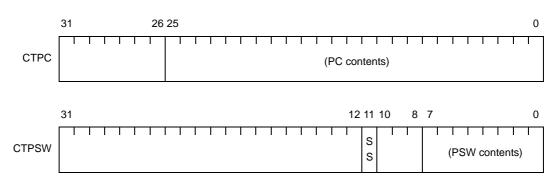

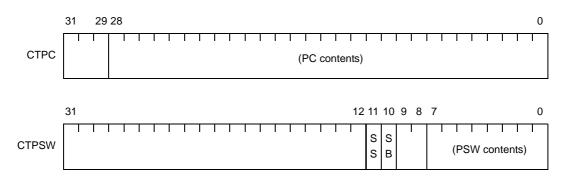

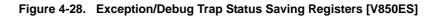

- 4-28 Exception/Debug Trap Status Saving Registers [V850ES] ... 333

- 4-29 Exception/Debug Trap Status Saving Registers [V850E1] ... 334

- 4-30 Exception/Debug Trap Status Saving Registers [V850E2] ... 334

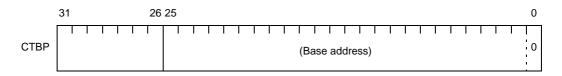

- 4-31 CALLT Base Pointer [V850ES, V850E1] ... 335

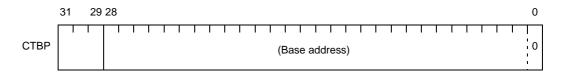

- 4-32 CALLT Base Pointer [V850E2] ... 335

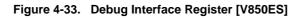

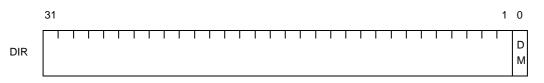

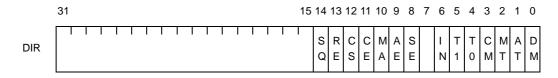

- 4-33 Debug Interface Register [V850ES] ... 336

- 4-34 Debug Interface Register [V850E1] ... 337

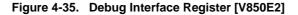

- 4-35 Debug Interface Register [V850E2] ... 339

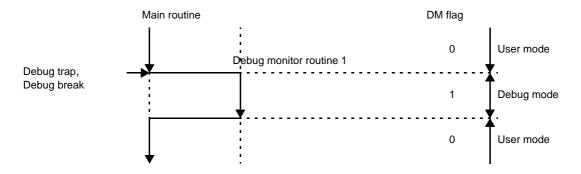

- 4-36 Breakpoint Control Registers [V850E1] ... 341

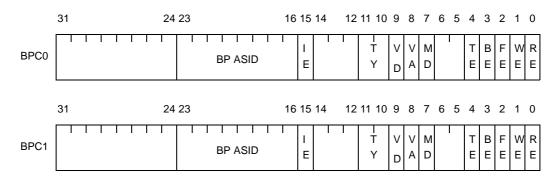

- 4-37 Breakpoint Control Register [V850E2] ... 343

- 4-38 Program ID Register [V850E1, V850E2] ... 345

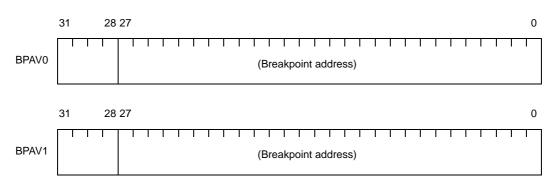

- 4-39 Breakpoint Address Setting Register [V850E1] ... 346

- 4-40 Breakpoint Address Setting Register [V850E2] ... 347

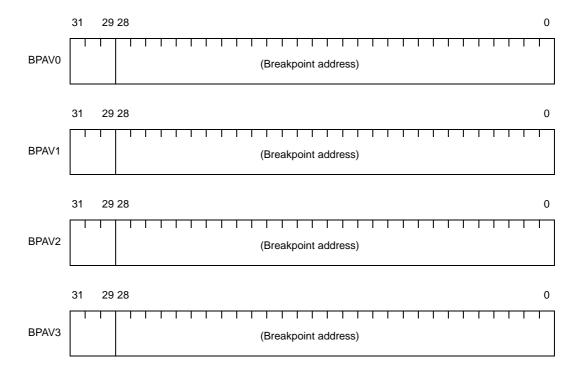

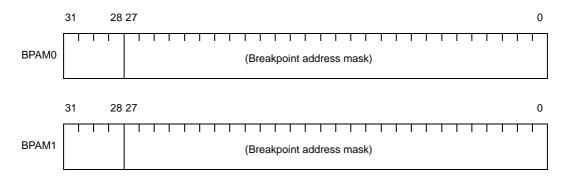

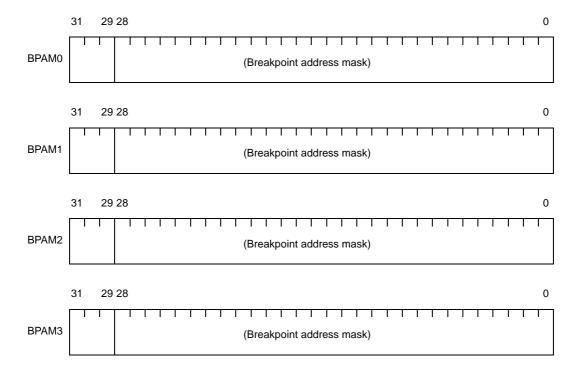

- 4-41 Breakpoint Address Mask Register [V850E1] ... 348

- 4-42 Breakpoint Address Mask Register [V850E2] ... 348

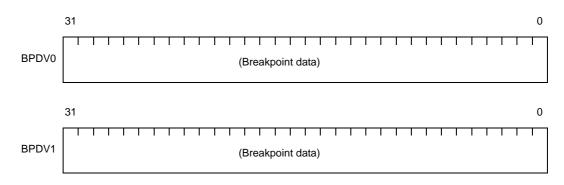

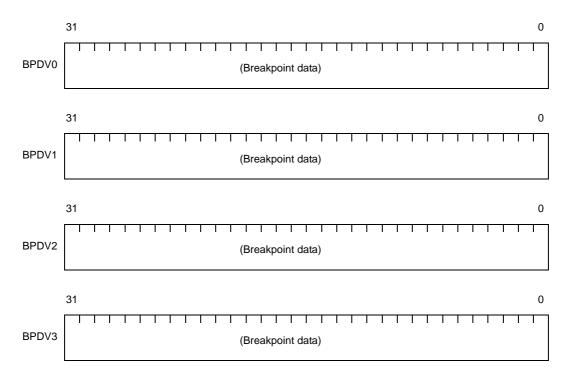

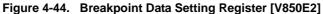

- 4-43 Breakpoint Data Setting Register [V850E1] ... 349

- 4-44 Breakpoint Data Setting Register [V850E2] ... 350

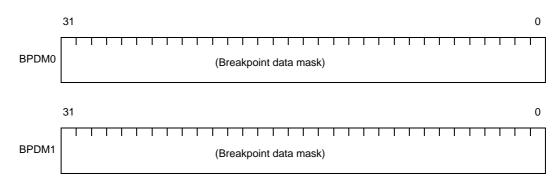

- 4-45 Breakpoint Data Mask Register [V850E1] ... 351

- 4-46 Breakpoint Data Mask Registers [V850E2] ... 352

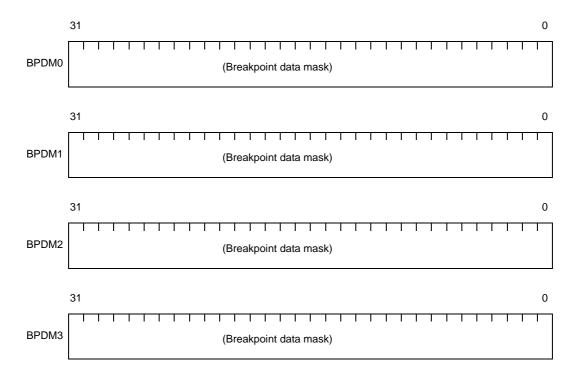

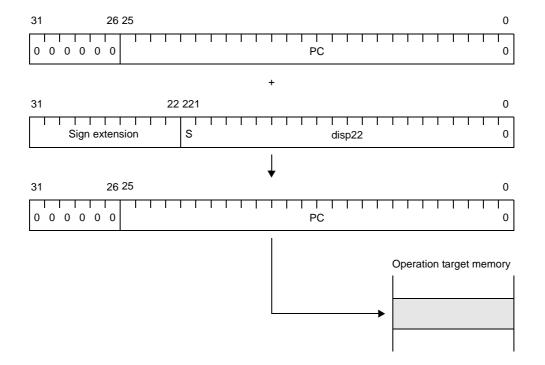

- 4-47 Relative Addressing (JR disp22/JARL disp22, reg2)[V850] ... 353

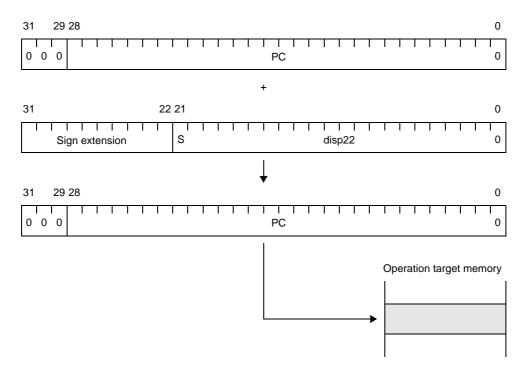

- 4-48 Relative Addressing (JR disp22/JARL disp22, reg2)[V850ES, V850E1] ... 354

- 4-49 Relative Addressing (JR disp22/JARL disp22, reg2)[V850E2] ... 354

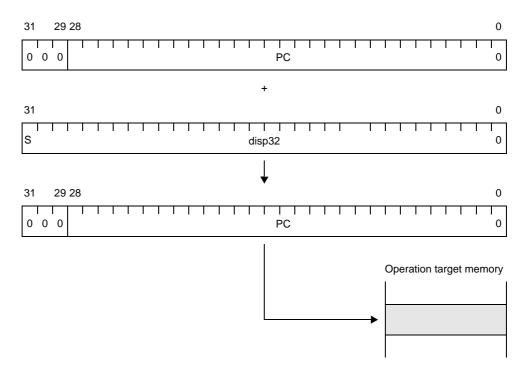

- 4-50 Relative Addressing (JR disp32/JARL disp32, reg2)[V850E2] ... 355

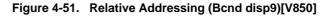

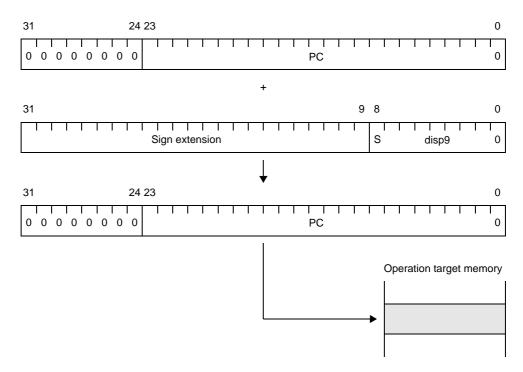

- 4-51 Relative Addressing (Bcnd disp9)[V850] ... 355

- 4-52 Relative Addressing (Bcnd disp9)[V850ES, V850E1] ... 356

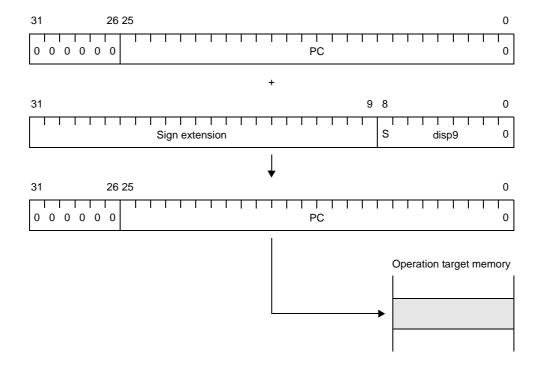

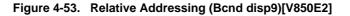

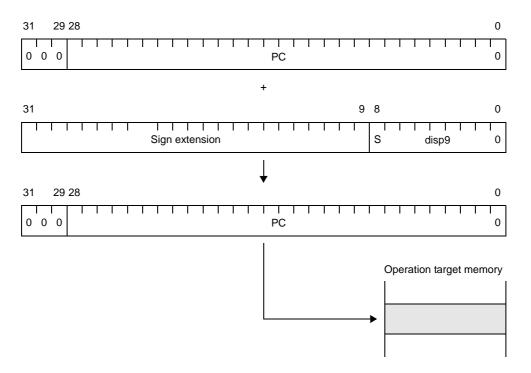

- 4-53 Relative Addressing (Bcnd disp9)[V850E2] ... 356

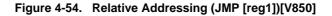

- 4-54 Relative Addressing (JMP [reg1])[V850] ... 357

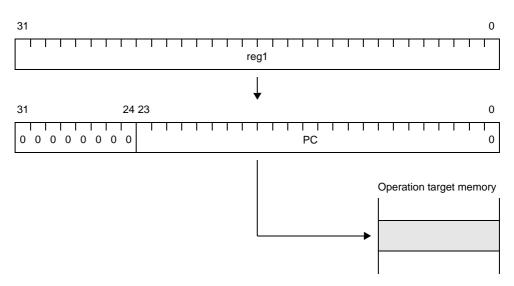

- 4-55 Register Addressing (JMP [reg1] V850ES, V850E1] ... 357

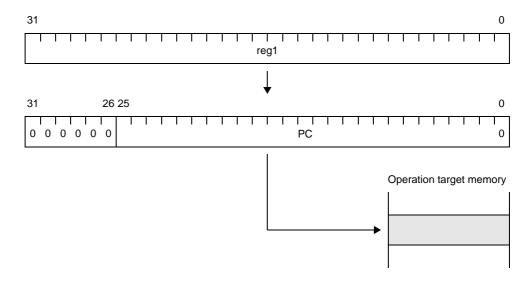

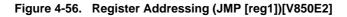

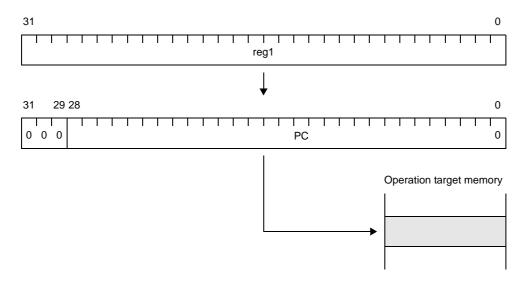

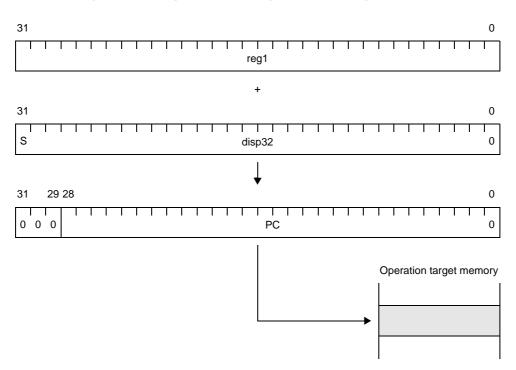

- 4-56 Register Addressing (JMP [reg1])[V850E2] ... 358

- 4-57 Register Addressing (JMP disp32[reg1])[V850E2] ... 358

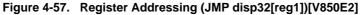

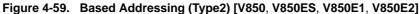

- 4-58 Based Addressing (Type1) [V850, V850ES, V850E1, V850E2] ... 359

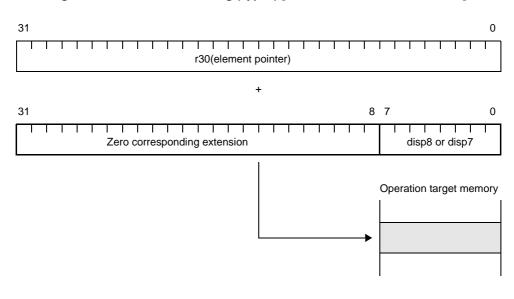

- 4-59 Based Addressing (Type2) [V850, V850ES, V850E1, V850E2] ... 360

- 4-60 Bit Addressing [V850, V850ES, V850E1, V850E2] ... 360

- 4-61 Memory Location Image of Internal RAM ... 369

- 4-62 Memory Allocation Image for External RAM (.sedata/.sebss Section) ... 369

- 4-63 Memory Location Image for gp Offset Reference Section ... 372

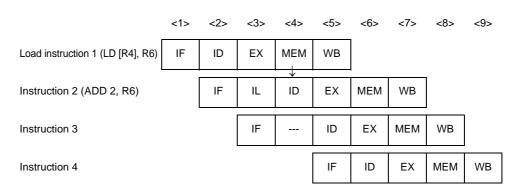

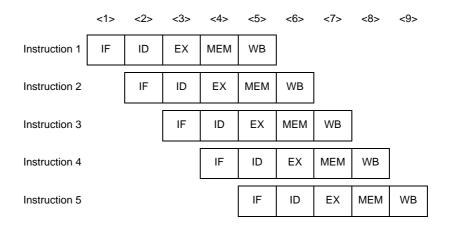

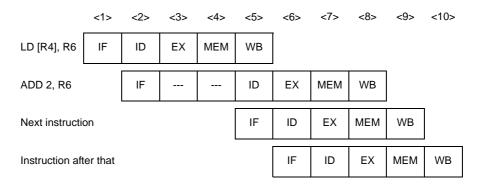

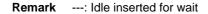

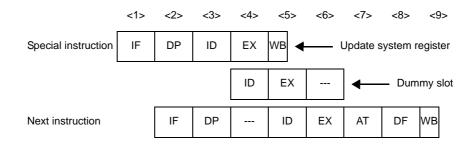

- 4-64 Example of Executing Nine Standard Instructions ... 565

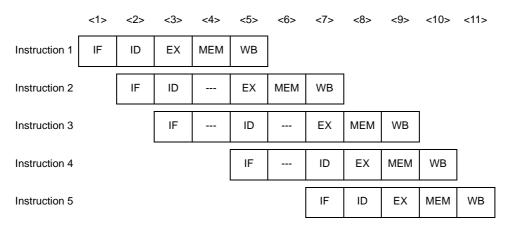

- 4-65 Alignment Hazard Example ... 566

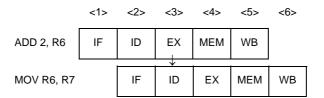

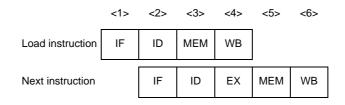

- 4-66 Example of Execution Result of Load Instruction ... 567

- 4-67 Example of Execution Result of Multiply Instruction ... 568

- 4-68 Example of Referencing Execution Result of LDSR Instruction for EIPC and FEPC ... 568

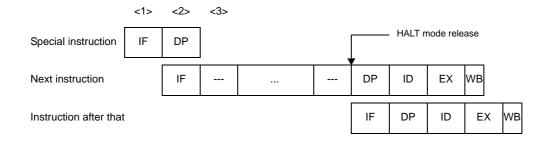

- 4-69 Example of Executing Nine Standard Instructions ... 589

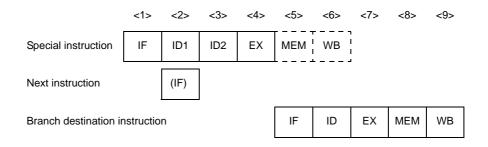

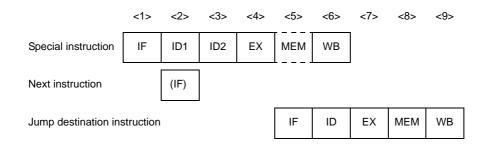

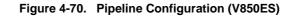

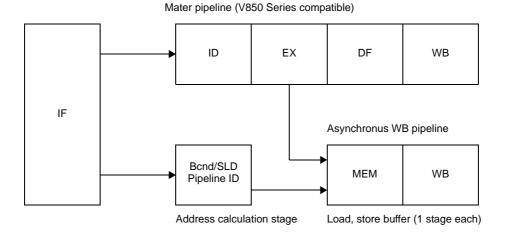

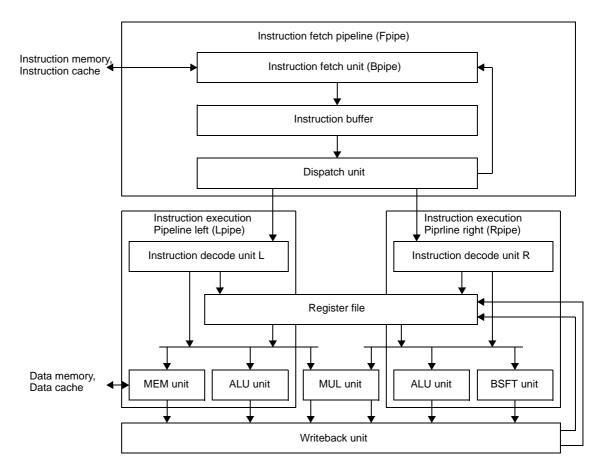

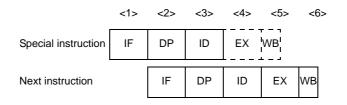

- 4-70 Pipeline Configuration (V850ES) ... 590

- 4-71 Alignment Hazard Example ... 594

- 4-72 Example of Execution Result of Load Instruction ... 595

- 4-73 Example of Execution Result of Multiply Instruction (Half Word Multiply Instruction) ... 595

- 4-74 Example of Execution Result of Multiply Instruction (Word Multiply Instruction) ... 596

- 4-75 Example of Referencing Execution Result of LDSR Instruction for EIPC and FEPC ... 596

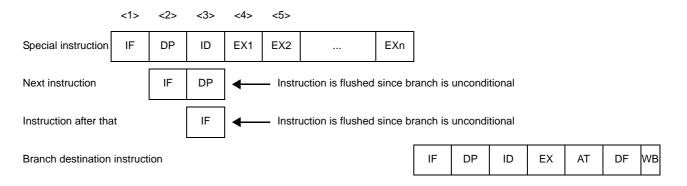

- 4-76 Example of Executing Nine Standard Instructions ... 629

- 4-77 Pipeline Configuration (V850E1) ... 630

- 4-78 Alignment Hazard Example ... 634

- 4-79 Example of Execution Result of Load Instruction ... 635

- 4-80 Example of Execution Result of Multiply Instruction ... 635

- 4-81 Example of Referencing Execution Result of LDSR Instruction for EIPC and FEPC ... 636

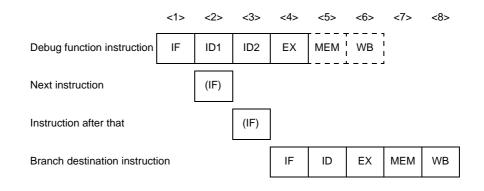

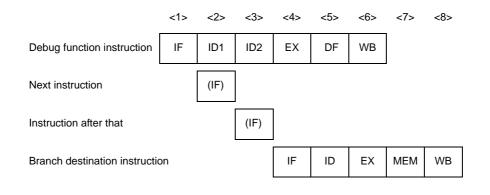

- 4-82 Example of Executing Twelve Standard Instructions ... 668

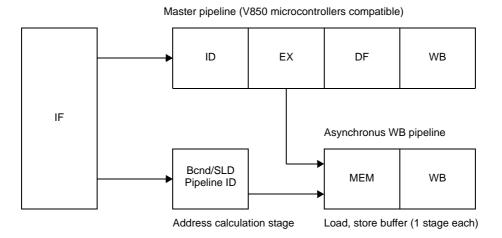

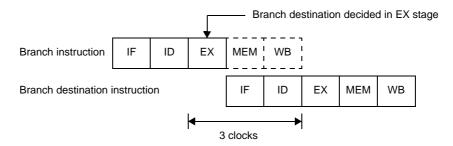

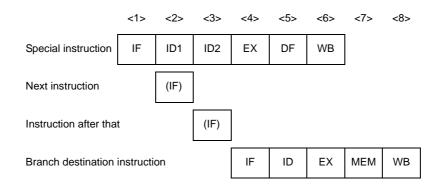

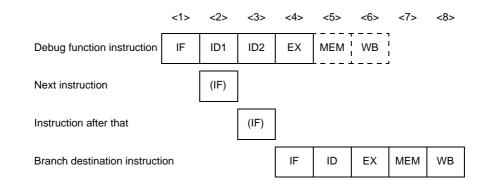

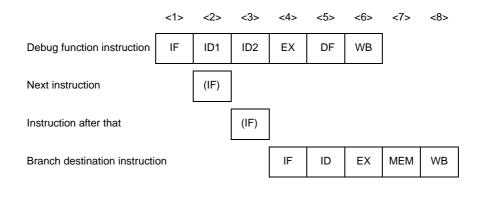

- 4-83 Pipeline Configuration (V850E2) ... 669

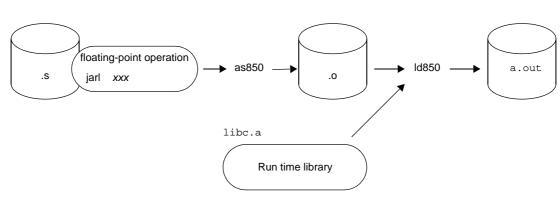

- 6-1 Image of Using Runtime Library ... 886

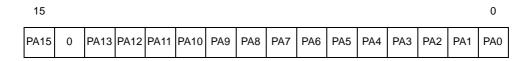

- 7-1 BPC Register ... 914

- 8-1 Creation of Object for ROMization ... 923

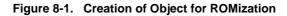

- 8-2 Image of Processing Before and After Copy Function Call ... 924

- 8-3 Link Directive Taking ROMization Processing into Consideration ... 926

- 8-4 Link Directive Taking ROMization Processing into Consideration (Size Considered) ... 927

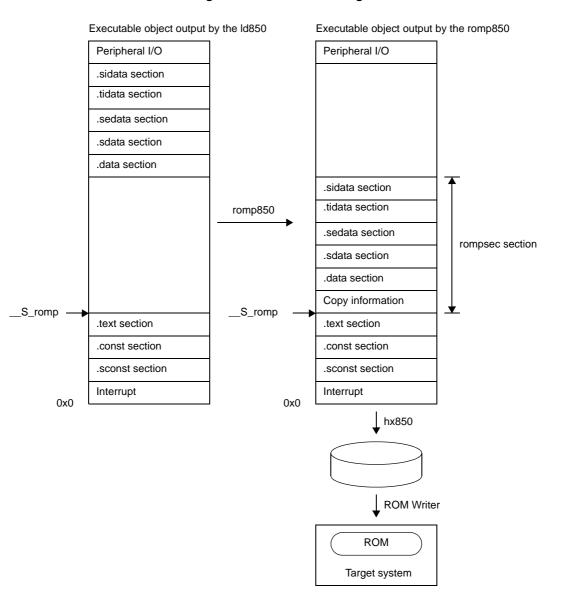

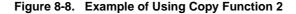

- 8-5 Example of Using Copy Function 1 ... 928

- 8-6 ROMization Image 1 ... 929

- 8-7 Example of rompack.s ... 930

- 8-8 Example of Using Copy Function 2 ... 930

- 8-9 Link Directive Specification Example ... 931

- 8-10 ROMization Image 2 ... 932

# LIST OF TABLES

| Table No.                    | Title, Page                                                             |

|------------------------------|-------------------------------------------------------------------------|

| 3-1 Data Types and Sizes     | 73                                                                      |

| 3-2 Expanded Notation an     | d Meaning 74                                                            |

| 3-3 Translation Limit Value  | es 75                                                                   |

| 3-4 Limit Values of Genera   | al Integer Type (limits.h File) 76                                      |

| 3-5 Definition of Limit Valu | es of Floating-point Type (float.h File) 77                             |

| 3-6 List of Supported Macr   | ros 84                                                                  |

| 3-7 Definition of NULL, siz  | e_t, ptrdiff_t (stddef.h File) 85                                       |

| 3-8 Processing When -ans     | i Option Strictly Conforming to Language Specifications is Specified 86 |

| 3-9 Value Area of Integer    | Гуре 87                                                                 |

| 3-10 Value Area of Floatin   | g-Point Type 88                                                         |

| 3-11 Alignment Condition f   | for Basic Type 93                                                       |

| 3-12 Alignment Condition f   | for Union Type 93                                                       |

| 3-13 Alignment Condition     | of Structure Type 94                                                    |

| 3-14 Using General-Purpo     | se Registers 95                                                         |

| 3-15 Referencing Data        | 96                                                                      |

| 3-16 Register Modes Supp     | blied by CA850 96                                                       |

| 3-17 List of Supported Mac   | cros 103                                                                |

| 3-18 Arithmetic Operation    | Instructions 113                                                        |

| 3-19 Arithmetic Operation    | Instructions 120                                                        |

| 3-20 Enabling or Disabling   | Maskable Interrupt 127                                                  |

| 3-21 Load/Store Instruction  | ns 129                                                                  |

| 3-22 Interrupt/Exception Ta  | able (V850ES/SG2) 131                                                   |

| 3-23 Registers for Registe   | r Variables 132                                                         |

| 3-24 Stack Frame for Inter   | rupt/Exception Handler 132                                              |

| 3-25 Stack Frame for Multi   | iple Interrupt/Exception Handler 133                                    |

| 3-26 Usage of Registers .    | 133                                                                     |

| 3-27 Processing for Saving   | g/Restoring Registers During Interrupt 134                              |

| 3-28 Trap Instructions and   | Software Exception Codes 137                                            |

| 3-29 Embedded Functions      | 5 145                                                                   |

| 3-30 Macros for Functions    | 165                                                                     |

| 3-31 Method of Accessing     | Stack Area 165                                                          |

| 3-32 Prologue/Epilogue Ru    | untime Functions 185                                                    |

| 3-33 Reserved Sections       | 191                                                                     |

| 4-1 Character Set and Usa    | age of Characters 193                                                   |

| 4-2 Value and Meaning of     | Escape Sequence 199                                                     |

| 4-3 Operators 205            |                                                                         |

| 4-4 Priority of Operators    | 205                                                                     |

| 4-5 peration Rules for Bina  | ary Operation 209                                                       |

| 4-6 Label Reference 2        | 14                                                                      |

| 47 Mamany Pataranaa Ing      | structions 016                                                          |

4-8 Operation Instructions ... 217 4-9 Branch Instructions ... 217 4-10 Area Allocation Quasi Directives ... 218 4-11 Area Allocation Quasi Directives ... 226 4-12 Section Definition Quasi Directives ... 228 4-13 Section Types ... 249 4-14 Section Types ... 250 4-15 Symbol Control Quasi Directives ... 252 4-16 Location Counter Control Quasi Directives ... 259 4-17 Area Allocation Quasi Directives ... 262 4-18 Program Linkage Quasi Directives ... 271 4-19 Assembler Control Quasi Directive ... 277 4-20 File Input Control Quasi Directives ... 282 4-21 Repetitive Assembly Quasi Directives ... 285 4-22 Conditional Assembly Quasi Directives ... 288 4-23 Skip Quasi Directives ... 301 4-24 Macro Quasi Directives ... 306 4-25 Program Registers ... 318 4-26 System Register No. ... 320 4-27 Exception Cause Register [V850, V850ES, V850E1, V850E2] ... 324 4-28 Program Status Word [V850, V850ES] ... 325 4-29 Program Status Word [V850E1] ... 327 4-30 Program Status Word [V850E2] ... 329 4-31 Contents to Be Saved to DBPC ... 333 4-32 Debug Interface Register [V850ES] ... 336 4-33 Debug Interface Register [V850E1] ... 337 4-34 Debug Interface Register [V850E2] ... 339 4-35 Breakpoint Control Registers [V850E1] ... 341 4-36 Breakpoint Control Register [V850E2] ... 343 4-37 Program ID Register [V850E1, V850E2] ... 345 4-38 Meaning of Symbols ... 361 4-39 Label Reference ... 364 4-40 Memory Reference Instruction ... 366 4-41 Operation Instructions ... 367 4-42 Branch Instructions ... 368 4-43 Area Allocation Pseudo-instruction ... 368 4-44 Area Allocation Pseudo-instruction ... 376 4-45 Load/Store Instructions ... 378 4-46 Arithmetic Operation Instructions ... 387 4-47 adfcond Instruction List ... 395 4-48 sbfcond Instruction List ... 403 4-49 cmovcnd Instruction List ... 442 4-50 setfcnd Instruction List ... 446

- 4-51 sasfcnd Instruction List ... 448

- 4-52 Saturated Operation Instructions ... 450

- 4-53 Logical Instructions ... 464

- 4-54 Branch Instructions ... 510

- 4-55 jcnd Instruction List ... 519

- 4-56 Bit Manipulation Instructions ... 527

- 4-57 Stack Manipulation Instructions ... 536

- 4-58 Special Instructions ... 541

- 4-59 System Register Numbers (ldsr) ... 542

- 4-60 System Register Numbers [V850E/MA1] (ldsr) ... 542

- 4-61 System Register Numbers [V850E/ME2] (ldsr) ... 543

- 4-62 System Register Numbers (stsr) ... 545

- 4-63 System Register Numbers [V850E/MA1] (stsr) ... 545

- 4-64 System Register Numbers [V850E/ME2] (stsr) ... 546

- 4-65 Access Time (number of clocks) ... 571

- 5-1 Item Specified in Segment Directive ... 701

- 5-2 Default Values for Omitted Segment Directive Specification Items ... 702

- 5-3 Reserved Section Names with Fixed Segment Names ... 702

- 5-4 Segment Attributes and their Meanings ... 703

- 5-5 Segment Example ... 705

- 5-6 Item Specified in Segment Directive ... 707

- 5-7 Default Values/Conventions for Values That Can Be Omitted in Mapping Directive Specification Items

- 5-8 Reserved Section Names with Fixed Segment Names ... 708

- 5-9 Section Types and Their Meanings ... 709

- 5-10 Section Attributes and Their Meanings ... 709

- 5-11 Section Types and Default Values for Alignment Condition ... 710

- 5-12 Output Based on Combination of Input Section and Object File Specifications ... 711

- 5-13 Specific Examples of Combined Input Section and Object File Specifications ... 711

- 5-14 Mapping Directive Specification Example ... 714

- 5-15 Specifiable Items When Creating tp Symbol ... 715

- 5-16 Default Values for tp Symbols ... 715

- 5-17 Specifiable Items When Creating gp Symbol ... 716

- 5-18 Default Values for gp Symbols ... 716

- 5-19 Specifiable Items When Creating ep Symbol ... 717

- 5-20 Default Values for ep Symbols ... 717

- 5-21 Address Specification for tp Symbol, gp Symboland and ep Symbol ... 718

- 5-22 Segment Names Targeted for Reference by tp Symbol and gp Symbol ... 719

- 5-23 Symbol Directive Specification Example ... 719

- 6-1 Supplied Libraries ... 721

- 6-2 Function with Variable Arguments ... 723

- 6-3 Character String Functions ... 723

- 6-4 Memory Management Functions ... 723

6-5 Character Conversion Functions ... 724 6-6 Character Classification Functions ... 724 6-7 Standard I/O Functions ... 724 6-8 Standard Utility Functions ... 725 6-9 Non-Local Jump Functions ... 726 6-10 Runtime Library ... 726 6-11 Prologue/Epilogue Runtime Library of Functions ... 727 6-12 Mathematical Functions ... 729 6-13 Copy Function ... 731 6-14 Header Files ... 732 6-15 Functions with Variable Arguments ... 733 6-16 Character String Functions ... 737 6-17 Memory Management Functions ... 755 6-18 Character Conversion Functions ... 763 6-19 Character Classification Functions ... 769 6-20 Standard I/O Functions ... 782 6-21 Standard Utility Functions ... 814 6-22 Non-Local Jump Functions ... 841 6-23 Mathematical Functions ... 844 6-24 Copy Function ... 885 6-25 Runtime Library ... 886 6-26 Functions with Variable Arguments ... 888 6-27 Character String Functions ... 888 6-28 Memory Management Functions ... 888 6-29 Character Conversion Functions ... 889 6-30 Character Classification Functions ... 889 6-31 Standard I/O Functions ... 890 6-32 Standard Utility Functions ... 891 6-33 Non-Local Jump Functions ... 891 6-34 Runtime Library ... 892 6-35 Prologue/Epilogue Runtime Library Functions ... 892 6-36 Mathematical Functions ... 898 6-37 Copy Function ... 899 7-1 Startup Routine Samples ... 900 7-2 Symbols of sbss Area ... 908 7-3 Symbols of bss Area ... 909 7-4 Symbols of sebss Area ... 910 7-5 Symbols of tibss.byte Area ... 911 7-6 Symbols of tibss.word Area ... 912 7-7 Symbols of sibss Area ... 913 7-8 BPC Register ... 914 7-9 Examples of Startup Routine ... 917 8-1 Copy Function ... 933

9-1 Identifier ... 939

- 9-2 Registers for Register Variables ... 939

- 9-3 Registers for Register Variables ... 940

- 9-4 Work Register ... 940

### CHAPTER 1 GENERAL

This chapter provides a general outline of the V850 microcontrollers C compiler package(CA850).

#### 1.1 Outline

The V850 microcontrollers C compiler package (CA850) is a program that converts programs described in C language or assembly language into machine language.

#### 1.2 Special Features

The V850 microcontrollers C compiler package is equipped with the following special features.

#### (1) Language specifications in accordance with ANSI standard

The C language specifications conform to the ANSI standard. Coexistence with prior C language specifications (K&R specifications) is also provided.

#### (2) Advanced optimization

Code size and speed priority optimization for the C compiler and assembler are offered.

#### (3) Built-in control functionality

Utilites to facilitate application system ROMization work are offered.

#### (4) Improvement to description ability

C language programming description ability has been improved due to enhanced language specifications. ASSEMBLY LANGUAGE SPECIFICATIONS This chapter explains the programming method and how to use the expansion functions for more efficient use of the CA850.

#### 2.1 Variables (C language)

This section explains variables (C language).

#### 2.1.1 Allocating to sections accessible with short instructions

The V850 contains 2-byte instruction length load/store instructions. By allocating variables to sections accessible with these instructions it is possible to reduce the code size.

When defining or referencing a variable use the #pragma section and specify "tidata" as the section type.

```

#pragma section section-type begin

variable-declaration/definition

#pragma section section-type end

```

#### Example

Remark See "#pragma section directive" .

#### 2.1.2 Changing allocated section

The default allocation sections are as follows:

- Variables with no initial value: .sbss section

- Variables with initial value: .sdata section

- const constants: .const section

To change the allocated section specify the section type using #pragma section.

#pragma section section-type begin

variable-declaration/definition

#pragma section section-type end

#### The relationship between section type and the section generated is as follows.

| Section Type | Initial Value | Default Section<br>Name | Section Name<br>Change | Base Register | Access Instruction    |

|--------------|---------------|-------------------------|------------------------|---------------|-----------------------|

| data         | Yes           | .data                   | Possible               | gp            | ld/st 2 instruction   |

|              | No            | .bss                    | Possible               | gp            | ld/st 2 instruction   |

| sdata        | Yes           | .sdata                  | Possible               | gp            | ld/st 1 instruction   |

|              | No            | .sbss                   | Possible               | gp            | ld/st 1 instruction   |

| sedata       | Yes           | .sedata                 | Not Possible           | ер            | Ild/st 1 instruction  |

|              | No            | .sebss                  | Not Possible           | ер            | ld/st 1 instruction   |

| sidata       | Yes           | .sidata                 | Not Possible           | ер            | ld/st 1 instruction   |

|              | No            | .sibss                  | Not Possible           | ер            | Id/st 1 instruction   |

| tidata.byte  | Yes           | .tidata.byte            | Not Possible           | ер            | sld/sst 1 instruction |

|              | No            | .tibss.byte             | Not Possible           | ер            | sld/sst 1 instruction |

| tidata.word  | Yes           | .tidata.word            | Not Possible           | ер            | sld/sst 1 instruction |

|              | No            | .tibss.word             | Not Possible           | ер            | sld/sst 1 instruction |

| sconst       | Yes           | .sconst                 | Possible               | rO            | ld/st 1 instruction   |

| const        | Yes           | .const                  | Possible               | rO            | ld/st 1 instruction   |

#### Example

| #pragma section sdata | "mysdata" begin                                  |

|-----------------------|--------------------------------------------------|

| int a = 1;            | /*allocated to mysdata.sdata attribute section*/ |

| int b;                | /*allocated to mysdata.sbss attribute section*/  |

| #pragma section sdata | "mysdata" end                                    |

When referencing a variable using the #pragma section instruction from a function in another file (i.e. reference file), it is necessary to also specify the #pragma section instruction in the reference file and to define the affected variable as extern format.

#### Example File that defines a table

```

#pragma section sconst begin

const unsigned char table_data[9] = {1, 2, 3, 4, 5, 6, 7, 8, 9};

#pragma section sconst end

```

#### **Example** File that references a table

```

#pragma section sconst begin

extern const unsigned char table_data[];

#pragma section sconst end

```

Remark See "#pragma section directive" .

#### 2.1.3 Defining variables for use during standard and interrupt processing

Specify as volatile variables that are to be used during both standard and interrupt processing.

When a variable is defined with the volatile qualifier, the variable is not optimized and optimization for assigning the variable to a register is no longer performed. When a variable specified as volatile is manipulated, a code that always reads the value of the variable from memory and writes the value to memory after the variable is manipulated is output. The access width of the variable with volatile specified is not changed. A variable for which volatile is not specified is assigned to a register as a result of optimization and the code that loads the variable from the memory may be deleted. When the same value is assigned to variables for which volatile is not specified, the instruction may be deleted as a result of optimization because it is interpreted as a redundant instruction.

[Example of source and output code when volatile has been specified]

If volatile is specified for "variable a", "variable b", and "variable c", a code that always reads the values of these variables from memory and writes them to memory after the variables are manipulated is output. Even if an interrupt occurs in the meantime and the values of the variables are changed by the interrupt, for example, the result in which the change is reflected can be obtained. (In this case, interrupts may have to be disabled while the variables are manipulated, depending on the timing of the interrupt.)

When volatile is specified, the code size increases compared with when volatile is not specified because the memory has to be read and written.

| volatile int a;              | _func:             |

|------------------------------|--------------------|

| volatile int b;              | .option volatile   |

| volatile int c;              | ld.w \$_a, r10     |

| <pre>void func(void) {</pre> | .option novolatile |

| if (a <= 0) {                | cmp r0, r10        |

| b++;                         | jgt .L2            |

| } else {                     | .option volatile   |

| C++;                         | ld.w \$_b, r11     |

| }                            | .option novolatile |

| b++;                         | add 1, rll         |

| C++;                         | .option volatile   |

| }                            | st.w rll, \$_b     |

|                              | .option novolatile |

|                              | jbr .L3            |

|                              | .L2:               |

|                              | .option volatile   |

|                              | ld.w \$_c, r12     |

|                              | .option novolatile |

|                              | add 1, r12         |

|                              | .option volatile   |

|                              | st.w r12, \$_c     |

|                              | .option novolatile |

|                              | .L3:               |

|                              | .option volatile   |

|                              | ld.w \$_b, r13     |

|                              | .option novolatile |

|                              | add 1, r13         |

|                              | .option volatile   |

|                              | st.w r13, \$_b     |

|                              | .option novolatile |

|                              |                    |

| .option volatile   |

|--------------------|

| ld.w \$_c, r14     |

| .option novolatile |

| add 1, r14         |

| .option volatile   |

| st.w r14, \$_c     |

| .option novolatile |

| jmp [lp]           |

### 2.1.4 Defining user port

With regards to the user port, specify volatile as in the following example to avoid optimization.

[Example of port description process]

```

/* 1.Port macro (format) definition*/

#define DEFPORTB(addr) (*((volatile unsigned char *)addr)) /* 8-bit port*/

#define DEFPORTH(addr) (*((volatile unsigned short *)addr)) /* 16-bit port*/

#define DEFPORTW(addr) (*((volatile unsigned int *)addr)) /* 32-bit port*/

/* 2.Port definition (Example: PORT1 0x00100000 8bit)*/

#define PORT1 DEFPORTB(0x00100000)

/* 0x00100000 8-bit port*/

/* 3. Port use*/

{

PORT1 = 0xFF; /* Write to PORT1*/

/* Read from PORT1*/

a = PORT1;

}

/* 4.C Compiler output code*/

:

mov

1048576, r10

#@BEGIN_VOLATILE

st.b

r20, [r10]

#@END_VOLATILE

1048576, r11

mov

#@BEGIN_VOLATILE

ld.b

[r11], r12

#@END_VOLATILE

:

```

- Remarks 1. By declaring a structure and assigning that structure variable to a specific section, and then assigning it to the corresponding port address in the link directive, bit access is possible in the same "X.X" format used in the CA850 internal region I/O register. However, in the case of 1-bit or 8-bit access both the bit field and byte union are required, so the format becomes "X.X.".

- 2. Assigning variables to sections should be performed using #pragma section or the section file.

#### 2.1.5 Defining const constant pointer

The pointer is interpreted differently depending on the "const" specified location. To assign the const section to the sconst section, specify #pragma section sconst.

```

- const char *p;

```

This indicates that the object (\*p) indicated by the pointer cannot be rewritten.

The pointer itself (p) can be rewritten.

Therefore the state becomes as follows and the pointer itself is allocated to RAM (.sdata/.data).

\*p = 0; /\*Error\*/

p = 0; /\*Correct\*/

#### - char \*const p;

This indicates that the pointer itself (p) cannot be rewritten.

The object (\*p) indicated by the pointer can be rewritten.

Therefore the state becomes as follows and the pointer itself is allocated to ROM (.sconst/.const).

```

*p = 0; /*Correct*/

p = 0; /*Error*/

```

#### - const char \*const p ;

This indicates that neither the pointer itself(p) nor the object (\*p) indicated by the pointer can be rewritten. Therefore the state becomes as follows and the pointer itself is allocated to ROM (.sconst/.const).

\*p = 0; /\*Error\*/

p = 0; /\*Error\*/

#### 2.2 Functions

This section explains functions.

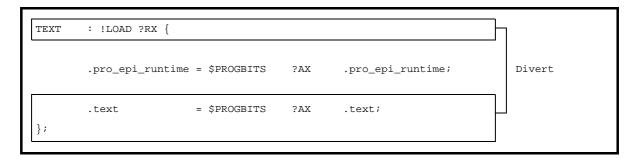

#### 2.2.1 Changing area to be allocated to

When changing a function's section name, specify the function using the #pragma text directive as shown below.

```

#pragma text ["section name"] function name

#pragma text ["section name"]

```

For a text attribute section that has had its section name changed, specify the initial section name from the time the input section was created in a link directive.

**Example** The link directive coding method for when [#pragma text "sec1" func1] has been coded in the C source, allocating function "func1" to the independently generated text-attribute section "sec1" (segment name: FUNC1):

```

FUNC1: !LOAD ?RX{

sec1.text = $PROGBITS ?AX sec1.text;

};

```

When allocating a specific function to an independently specified text-attribute section using the #pragma text directive, the section name actually generated will be "(specified character string)+.text", and the section name must be entered in the link directive.

In the above example it would be "sec1.text section".

Remark See "#pragma text directive" .

#### 2.2.2 Calling an away function

The C compiler uses the jarl instruction to call functions.

However, depending on the program allocation the address may not be able to be resolved, resulting in an error when linking because the jarl instruction is 22-bit displacement.

In such a case, it is possible to make the function call not depend on the displacement amount by using the C compiler's -Xfar\_jump option.

This is called the far jump function.

When calling a function set as far jump, the jmp instruction rather than the jarl/jal instruction is output.

One function is described per line in the file where the -Xfar\_jump option is specified. The names described should be C language function names prefixed with "\_" (an underscore).

#### Example

```

_func_led

_func_beep

_func_motor

:

:

_func_switch

```

If the following is described in place of "\_function-name", all functions will be called using far jump.

{all\_function}

Remark See "far jump function" .

#### 2.2.3 Embedding assembler instructions

With the CA850 assembler instructions can be described in the following formats within C language source programs.

- asm declaration

\_\_asm( character string constant); or \_\_asm( character string constant);

- #pragma directive

| #pragma asm           |

|-----------------------|

| Assembler instruction |

| #pragma endasm        |

To use registers with an inserted assembler, save or restore the contents of the registers in the program because they are not saved or restored by the CA850.

#### Example

```

__asm("nop ");

__asm(".str \"string\\0\"");;

#pragma asm

mov r0, r10

st.w r10, $_i

#pragma endasm

```

Assembler instructions written within asm declarations and between #pragma asm and #pragma endasm directives are never expanded even if the assembler source contains material defined by C language #define.

Furthermore assembler instructions written within asm declarations and between #pragma asm and #pragma endasm directives are not expanded even if the -P option is added in the C compiler because they are passed as is to the assembler.

Remark See "Describing assembler instruction" .

#### 2.2.4 Executing in RAM

A program allocated to external ROM can be copied to internal RAM and executed in internal RAM while linking and after copying if the relative value of each section and each symbol (TP, EP, GP) is not destroyed.

Use caution, as some programs can be copied while others cannot.

If a program is copied to internal RAM following reset and is not changed, this can be done more easily by using the ROMization function.

The text section can be packed with romp850.

#### 2.3 Using Microcomputer Functions

This section explains using microcomputer functions.

#### 2.3.1 Accessing peripheral I/O register with C language

When reading from and writing to the device's internal peripheral I/O register in C language, adding a pragma directive to the C source makes possible reading and writing using the peripheral I/O register name and bit names. The peripheral I/O register name can be treated as a standard unsigned external variable.

```

#pragma ioreg

register name = ...

register name.bit number = ...

bit name = ...

```

After describing the above pragma directive as above, the peripheral I/O register name becomes usable.

#### Example

```

#pragma ioreg

main() {

int i;

P0 = 1;

/* Writes 1 to PO*/

i = RXB0; /* Reads from RXB0*/

}

void func(void) {

P1 = 0;

/* Writes 0 to P1*/

}

void func2(void) {

P0.1 = 1; /* Sets bit 1 of PO to 1*/

P2.3 = 0; /* Sets bit 3 of P2 to 0*/

PS00 = 1; /* Sets the bit named PS00 to 1*/

1

```

For peripheral I/O register bit names, the relevant bit names are limited to ones defined by the CA850. An error will therefore occur if the bit name is undefined. To access an undefined bit, use "register name.bit number".

Remarks 1. To access the 4th bit of C port 3, use "P3.4".

2. See "Peripheral I/O register" .

#### 2.3.2 Describing interrupt processing with C language

With the CA850, the interrupt handler is specified using the "#pragma interrupt directive" and "\_\_\_interrupt qualifier" (for standard interrupt), or the "#pragma interrupt directive" and "\_\_\_multi\_interrupt qualifier" (for multiple interrupt). An example of the interrupt handler is shown below.

Example Non-maskable interrupt

```

#pragma interrupt NMI func1 /*non-maskable interrupt*/

__interrupt

void func1(void) {

:

}

```

Example Multiple interrupt specification

```

#pragma interrupt INTPO func2

__multi_interrupt /* multiple-interrupt function specified*/

void func2(void) {

:

}

```

Remark See "Interrupt/Exception processing handler" .

# 2.3.3 Using CPU instructions in C language

Some assembler instructions can be described in C language source as embedded functions. However, they are not described exactly as assembler instructions, but rather in the function format prepared by the CA850. Instructions that can be described as functions are shown below.

| Assembler   | Function                                                                                                                   | Embedded Function Description                              |

|-------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Instruction |                                                                                                                            |                                                            |

| di          | Interrupt control (ei)                                                                                                     | DI()                                                       |

| ei          | Interrupt control (di)                                                                                                     | EI()                                                       |

| nop         | nop                                                                                                                        | nop()                                                      |

| halt        | halt                                                                                                                       | halt()                                                     |

| satadd      | Saturated addition (satadd)                                                                                                | long a, b;<br>longsatadd(a, b);                            |

| satsub      | Saturated subtraction (satsub)                                                                                             | long a, b;<br>longsatsub(a, b);                            |

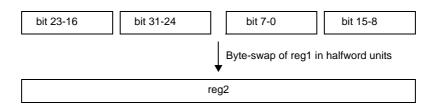

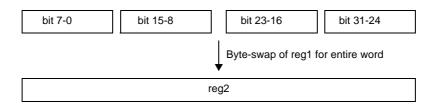

| bsh         | Halfword data byte swap (bsh) [V850E]                                                                                      | long a;<br>longbsh(a);                                     |

| bsw         | Word data byte swap (bsw) [V850E]                                                                                          | long a;<br>longbsw(a);                                     |

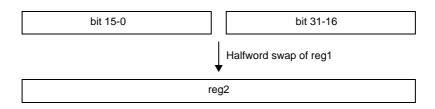

| hsw         | Word data halfword swap (hsw) [V850E]                                                                                      | long a;<br>longhsw(a);                                     |

| sxb         | Byte data sign extension (sxb) [V850E]                                                                                     | char a;<br>longsxb(a);                                     |

| sxh         | Halfword data sign extension (sxh) [V850E]                                                                                 | <pre>short a;<br/>longsxh(a);</pre>                        |

| mul         | Instruction that assigns higher 32 bits of multiplication result to variable using mul instruction [V850E]                 | long a; long b;<br>longmul32(a, b);                        |

| mulu        | Instruction that assigns higher 32 bits of unsigned<br>multiplication result to variable using mulu instruction<br>[V850E] | unsigned long a, b;<br>unsigned longmul32u(a, b);          |

| sasf        | Flag condition setting with logical left shift (sasf)<br>[V850E]                                                           | <pre>long a;<br/>unsigned int b;<br/>longsasf(a, b);</pre> |

#### Example

```

long a, b, c;

void func(void) {

:

c = __satsub(a, b); /* The result of the saturated operation of a and b is stored in c

(c = a - b) */

:

__nop();

:

}

```

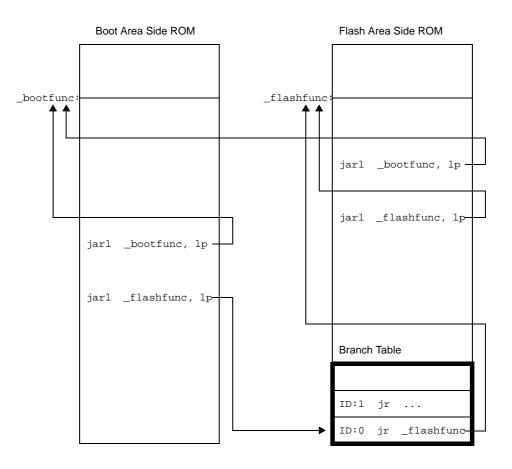

# 2.3.4 Creating a self-programming boot area

Variables and functions can be referenced between the flash area and boot area with the following operations.

- Boot area functions can be called directly from the flash area.

- Calling a function from the boot area to the flash area is performed via a branch table.

- External boot area variables can be referenced from the flash area.

- External flash area variables cannot be referenced from the boot area.

- Common external variables as well as global functions can be defined for use by both boot area programs and flash area programs. In this case the variable or function on the same area side is referenced.

Flash area functions called from the boot area are defined with the ext\_func directive.

..ext\_func function name, ID number

[Example (Within a C language program)]

```

#pragma asm

.ext_func _func_flash0, 0

.ext_func _func_flash1, 1

.ext_func _func_flash2, 2

#pragma endasm

```

Additional specifications such as options must be made. See "Flash relink function" in the "V850 Build" for details.

# 2.4 Variables (Assembler)

This section explains variables (Assembler).

## 2.4.1 Defining variables with no initial values

Use the .lcomm directive in a section with no initial value to allocate area for a variable with no initial value.

.lcomm label name, size, alignment condition

In order that it may be referenced from other files as well, it is necessary to define the label with the .globl directive.

.globl label name[, size]

#### [Example]

| .globl val0     | Sets val0 as able to be referenced from other files       |

|-----------------|-----------------------------------------------------------|

| .globl vall     | Sets vall as able to be referenced from other files       |

| .globl val2     | Sets val2 as able to be referenced from other files       |

| .sbss           |                                                           |

| .lcomm val0,4,4 | Allocates 4 bytes of area for val0 and sets its alignment |

|                 | condition to 4                                            |

| .lcomm val1,2,2 | Allocates 2 bytes of area for vall and sets its alignment |

|                 | condition to 2                                            |

| .lcomm val2,1,1 | Allocates 1 byte of area for val2 and sets its alignment  |

|                 | condition to 1                                            |

Remark See ".lcomm", ".globl" .

# 2.4.2 Defining const constants with initial values

To define a const with an initial value, use the following directives within the .const or .sconst section.

- 1-byte values

.byte value[, value, ...]

- 2-byte values

```

.hword value[, value, ...]

```

- 4-byte values

.word value[, value, ...]

Example Allocates 1 halfword and stores 100

```

.const

.align 4

.globl _p, 2

_p:

.hword 100

```

Remark See ".byte", ".hword", ".word" .

#### 2.4.3 Referencing section addresses

Symbols such as .data and .sdata (reserved symbols) which point to the beginnings and ends of sections are available. Therefore, utilize the appropriate symbol name when using the address value of a specified section from the assembler source.

| Start symbol: | s[section name] |

|---------------|-----------------|

| End symbol:   | e[section name] |

For example, the start symbol for the .sbss section is \_\_ssbss, and its end symbol is \_\_esbss.

These symbols can be used to retrieve the section start address and end address, but these symbol names cannot be used to make direct references with C language labels.

To retrieve these symbol values, create global variables to store these values then store the symbol values in the variables in assembler source such as that of the start up module.

By referencing these variables in the C source this can be realized.

The same applies to symbols such as \_\_gp\_DATA.

For example, the method for retrieving the start and end addresses of a .data section is as follows.

#### [In assembler source]

```

.comm _data_top, 4, 4

.comm _data_end, 4, 4

.extern __sdata, 4

.extern __edata, 4

mov #__sdata, r12

st.w r12, $_data_top

mov #__edata, r13

st.w r13, $_data_end

```

#### [In C source]

```

extern int data_top; /* extern defines data_top*/

extern int data_end; /* extern defines data_end*/

void funcl(void) {

int top, end;

top = data_top;

end = data_end;

:

}

```

Try using this method in cases where a C language label is used to initialize only a specified section.

## 2.5 Startup Routine

This section explains startup routine.

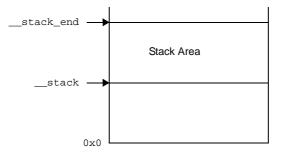

#### 2.5.1 Secure stack area

When setting a value to the stack pointer (sp), it is necessary to pay attention to the following points.

- The stack frame is generated downwards starting from the sp set value.

- Be sure to set the sp to point at the of 4-byte boundary position.

When the compiler references memory relative to a stack, it generates code based on the assumption the

stack pointer points at the 4-byte boundary position.

Allocate it to a data section (bss attribute section) as far as possible from gp.

If it is near the gp, there is a chance that the program data area will be destroyed.

[sp setting example]

.set STACKSIZE, 0x3f0

.bss

.lcomm \_\_stack, STACKSIZE, 4

mov #\_\_stack + STACKSIZE, sp

In the above example, the size of the stack frame used by the application is set to 0x3f0 bytes and area is secured. The label "\_\_\_stack" points to the lowest position (start) of the stack frame.