# **CPS-1848<sup>™</sup> User Manual**

**Central Packet Switch**

Formal Status June 2, 2014

#### GENERAL DISCLAIMER

Integrated Device Technology, Inc. ("IDT") reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance. IDT does not assume responsibility for use of any circuitry described herein other than the circuitry embodied in an IDT product. Disclosure of the information herein does not convey a license or any other right, by implication or otherwise, in any patent, trademark, or other intellectual property right of IDT. IDT products may contain errata which can affect product performance to a minor or immaterial degree. Current characterized errata will be made available upon request. Items identified herein as "reserved" or "undefined" are reserved for future definition. IDT does not assume responsibility for conflicts or incompatibilities arising from the future definition of such items. IDT products have not been designed, tested, or manufactured for use in, and thus are not warranted for, applications where the failure, malfunction, or any inaccuracy in the application carries a risk of death, serious bodily injury, or damage to tangible property. Code examples provided herein by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of such code examples shall be at the user's sole risk.

Copyright ©2014 Integrated Device Technology, Inc.

The IDT logo is registered to Integrated Device Technology, Inc.

|    | Abo  | out this Document                                                         |    |

|----|------|---------------------------------------------------------------------------|----|

|    |      | Content Summary                                                           |    |

|    |      | Additional Resources                                                      |    |

|    |      | Device Revision Information                                               |    |

|    |      | Revision History                                                          |    |

| 1. | Dev  | rice Overview                                                             |    |

|    | 1.1  | Device Description                                                        |    |

|    | 1.2  | Key Features                                                              |    |

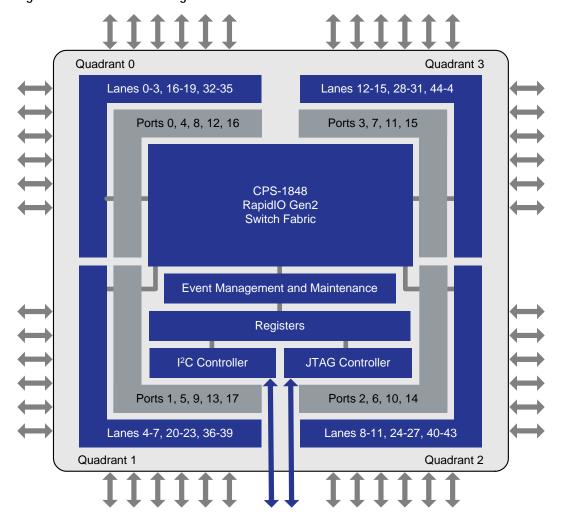

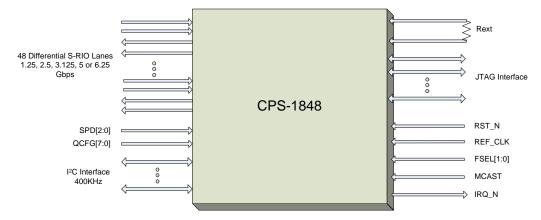

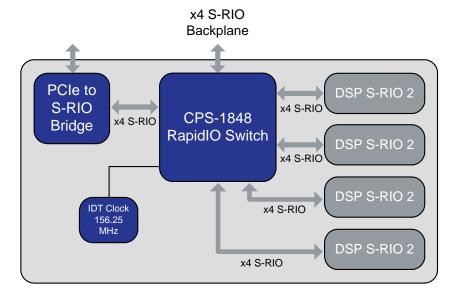

|    | 1.3  | Block Diagrams                                                            |    |

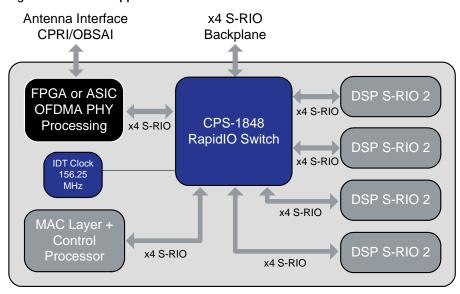

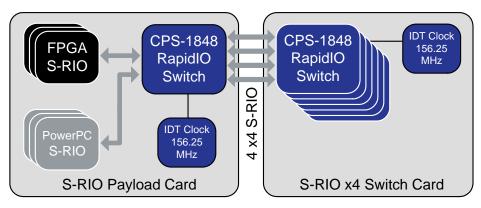

|    | 1.4  | Typical Applications                                                      |    |

|    | 1.4  | 1.4.1 Wireless Application Benefits                                       |    |

|    |      | 1.4.2 Defense and Aerospace Application Benefits                          |    |

|    |      | 1.4.3 Video and Imaging Application Benefits                              |    |

| 2. | Rap  | oidIO Ports                                                               |    |

|    | 2.1  | Overview                                                                  |    |

|    | 2.2  | Key Features                                                              |    |

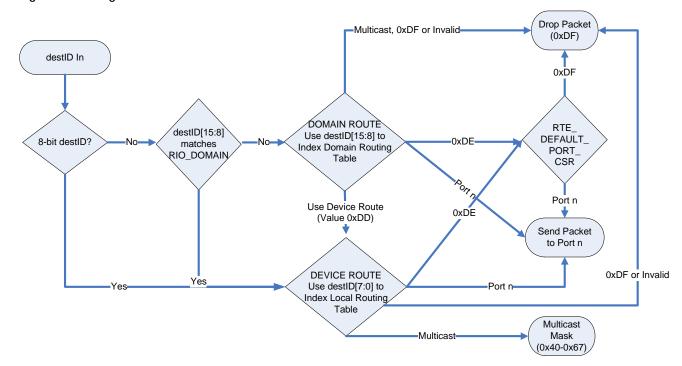

|    | 2.3  | Packet Routing                                                            |    |

|    |      | 2.3.1 Packet Routing Overview                                             |    |

|    |      | 2.3.2 Unicast Programming Model                                           |    |

|    |      | 2.3.3 Multicast Programming Model                                         |    |

|    |      | 2.3.4 Programming Examples                                                |    |

|    | 2.4  | Flow Control                                                              |    |

|    |      | 2.4.1 Transmitter- and Receiver-Controlled Flow Control Programming Model |    |

|    | 2.5  | Multicast Event Control Symbols                                           |    |

|    | 2.6  | Port Reconfiguration Operations                                           | 39 |

|    |      | 2.6.1 Disabling IDLE2 Operation                                           | 40 |

|    | 2.7  | Reset Control Symbol Processing                                           |    |

|    |      | 2.7.1 Per-Port Reset                                                      |    |

|    |      | 2.7.2 Port Disable/Enable                                                 | 42 |

|    |      | 2.7.3 Generating a Reset Request                                          | 42 |

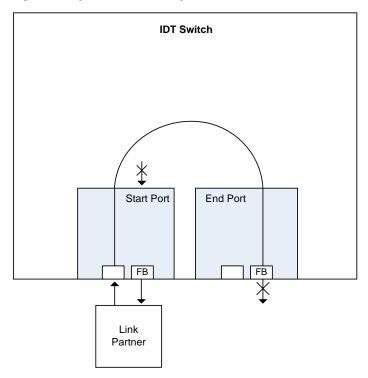

|    | 2.8  | Hot Extraction/Insertion                                                  | 42 |

|    |      | 2.8.1 Hot Extraction                                                      | 43 |

|    |      | 2.8.2 Controlled Removal/Reset                                            | 43 |

|    |      | 2.8.3 Link Partner Insertion                                              | 48 |

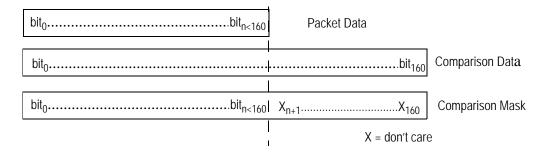

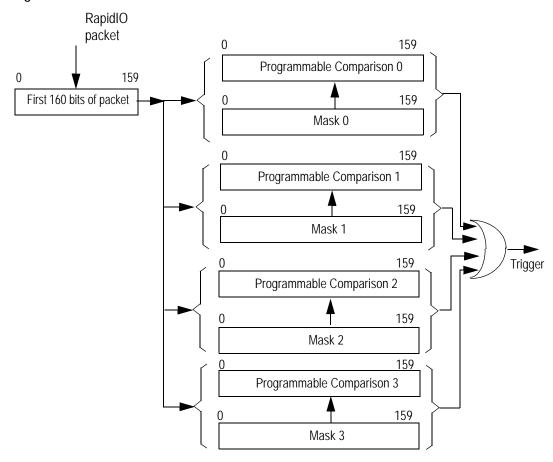

|    | 2.9  | Packet Trace and Filtering                                                | 53 |

|    |      | 2.9.1 Packet Trace                                                        | 53 |

|    |      | 2.9.2 Packet Filtering                                                    | 57 |

|    | 2.10 | Packet Generation and Capture                                             | 57 |

|    |      | 2.10.1 Packet Generation and Capture Mode Overview                        | 58 |

|    |      | 2.10.2 Packet Generation and Capture Mode Programming Model               | 59 |

|    | 2.11 | Packet Transfer Validation and Debug                                  |    |

|----|------|-----------------------------------------------------------------------|----|

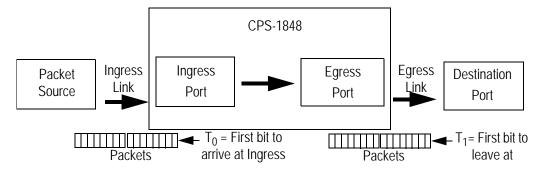

|    |      | 2.11.1 Overview                                                       |    |

|    |      | 2.11.2 Successful Packet Transfer                                     |    |

|    |      | 2.11.3 Switch Cannot Accept Packets                                   |    |

|    |      | 2.11.4 Switch Is Not Routing Packets Correctly                        |    |

|    |      | 2.11.5 Switch Cannot Transmit Packets                                 |    |

|    |      | 2.11.6 Requesting Debug Assistance                                    |    |

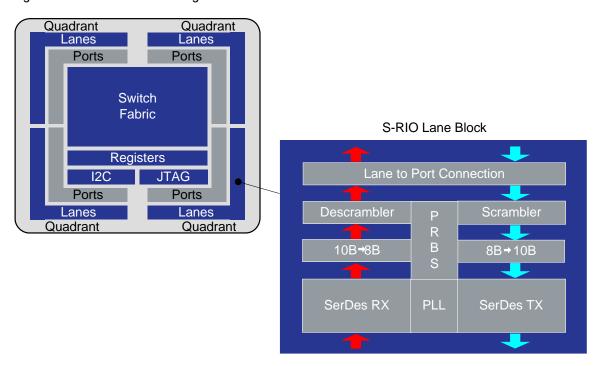

| 3. | Rap  | oidIO Lanes                                                           | 69 |

|    | 3.1  | Lane to Port Mapping                                                  | 70 |

|    | 3.2  | Lane and Port Speeds                                                  |    |

|    |      | 3.2.1 Lane Speed Change Examples                                      | 73 |

|    | 3.3  | Lane, PLL, and Port Power-Down                                        | 75 |

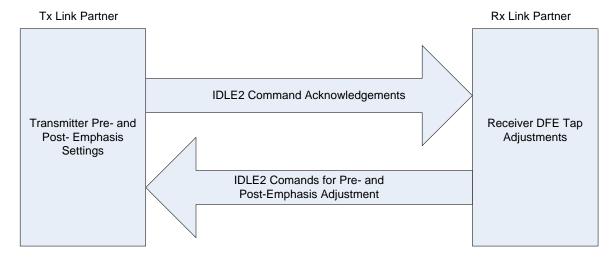

|    | 3.4  | Port and Lane Initialization Sequence                                 | 75 |

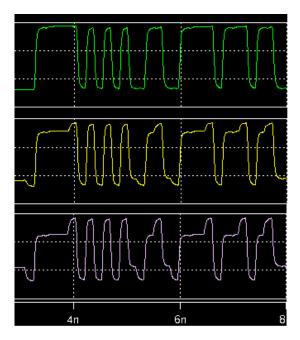

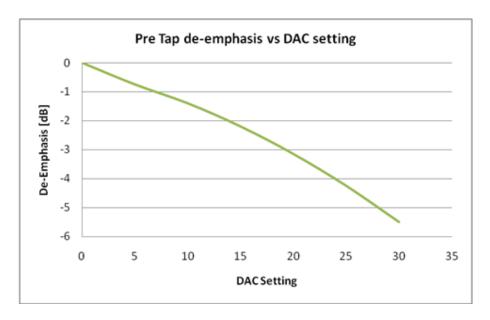

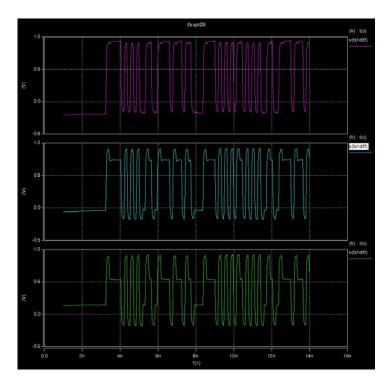

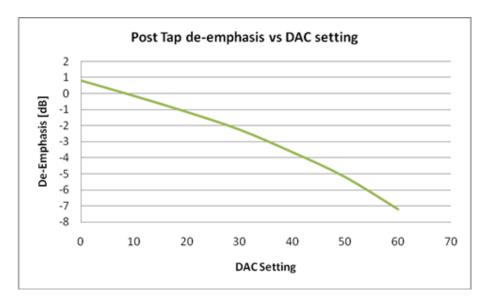

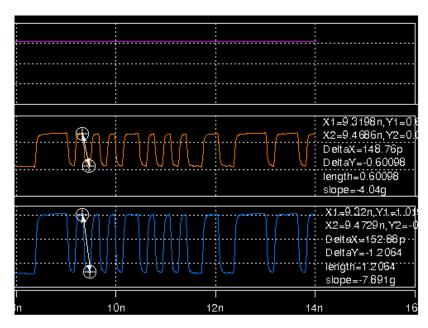

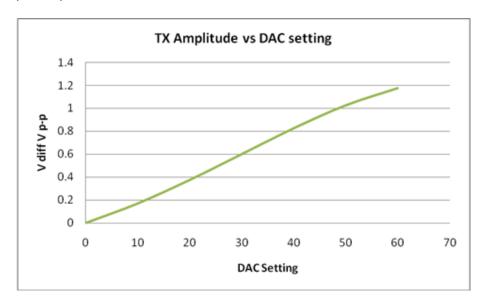

|    |      | 3.4.1 Signal Quality Optimization                                     | 76 |

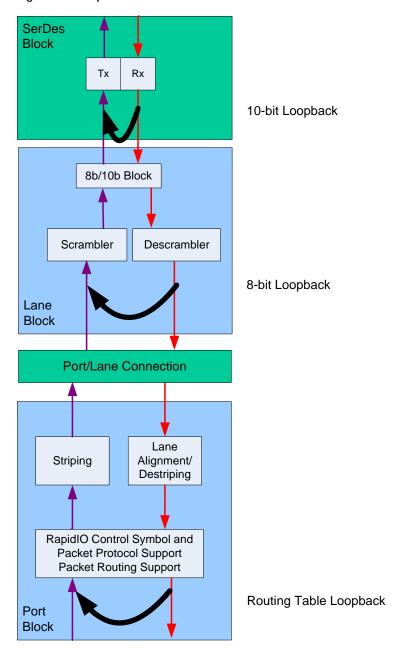

|    | 3.5  | Loopback Capabilities                                                 | 82 |

|    |      | 3.5.1 Lane Loopback Modes                                             | 83 |

|    |      | 3.5.2 Port Loopback Mode                                              | 83 |

|    | 3.6  | Bit Error Rate Testing                                                | 84 |

|    |      | 3.6.1 PRBS Polynomials                                                | 84 |

|    |      | 3.6.2 User-Defined Patterns                                           | 84 |

|    |      | 3.6.3 PRBS Pattern Generator                                          |    |

|    |      | 3.6.4 PRBS Pattern Checker and Log (Revision C)                       | 85 |

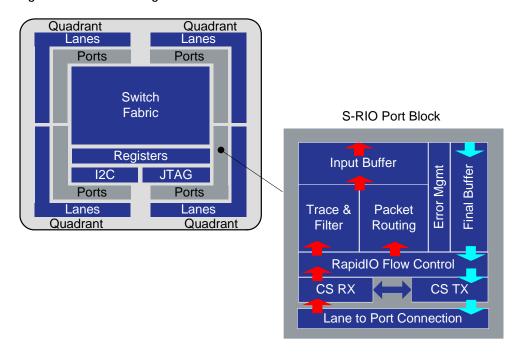

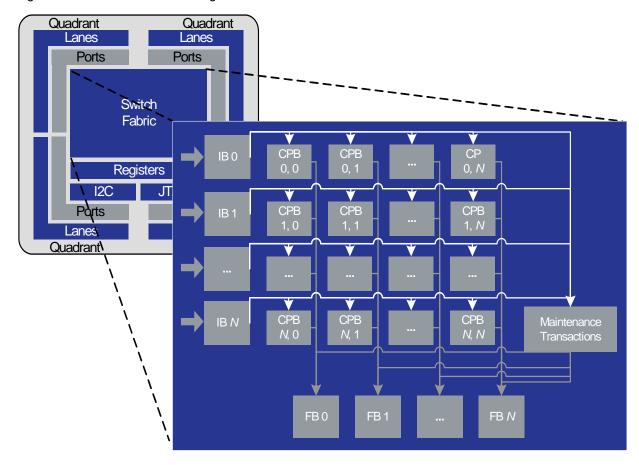

| 4. | Swi  | tch Fabric                                                            | 87 |

|    | 4.1  | Key Features                                                          | 87 |

|    | 4.2  | Switch Fabric Architecture                                            | 88 |

|    | 4.3  | Input Buffer                                                          | 89 |

|    | 4.4  | Input Buffer to Crosspoint Buffer Transfers                           | 89 |

|    |      | 4.4.1 VoQ Fairness/Starvation Avoidance                               | 90 |

|    |      | 4.4.2 Multicast Packets                                               | 90 |

|    | 4.5  | Crosspoint Buffers                                                    | 90 |

|    | 4.6  | Crosspoint Buffer to Final Buffer Transfers                           |    |

|    | 4.7  | Maintenance Transaction Support                                       | 91 |

|    | 4.8  | Final Buffer                                                          | 92 |

| 5. | Perf | formance                                                              | 93 |

|    | 5.1  | Overview                                                              |    |

|    | 0    | 5.1.1 Throughput                                                      |    |

|    |      | 5.1.2 Latency                                                         |    |

|    |      | 5.1.3 Latency Variation                                               |    |

|    | 5.2  | Performance Monitoring.                                               |    |

|    |      | 5.2.1 Traffic Efficiency                                              |    |

|    |      | 5.2.2 Congestion Detection                                            |    |

|    |      | 5.2.3 Resetting Performance Registers                                 |    |

|    | 5.3  | Performance Measurements                                              |    |

|    |      | 5.3.1 Buffer Management Settings                                      | 96 |

|    |      | 5.3.2 Store-and-Forward or Cut-Through Mode                           |    |

|    |      | 5.3.3 Transmitter-Controlled or Receiver-Controlled Flow Control Mode |    |

|    | 5.4  | Port-to-Port Performance Characteristics                              | 99 |

|    |      | 5.4.1 Packet Latency Performance                                      | 90 |

|    |     | 5.4.2    | Packet Throughput Performance                                                  | 100 |

|----|-----|----------|--------------------------------------------------------------------------------|-----|

|    |     | 5.4.3    | Multicast Latency Performance                                                  |     |

|    |     | 5.4.4    | Multicast Throughput Performance                                               | 102 |

|    |     | 5.4.5    | Multicast-Event Control Symbol (MECS) Latency                                  | 103 |

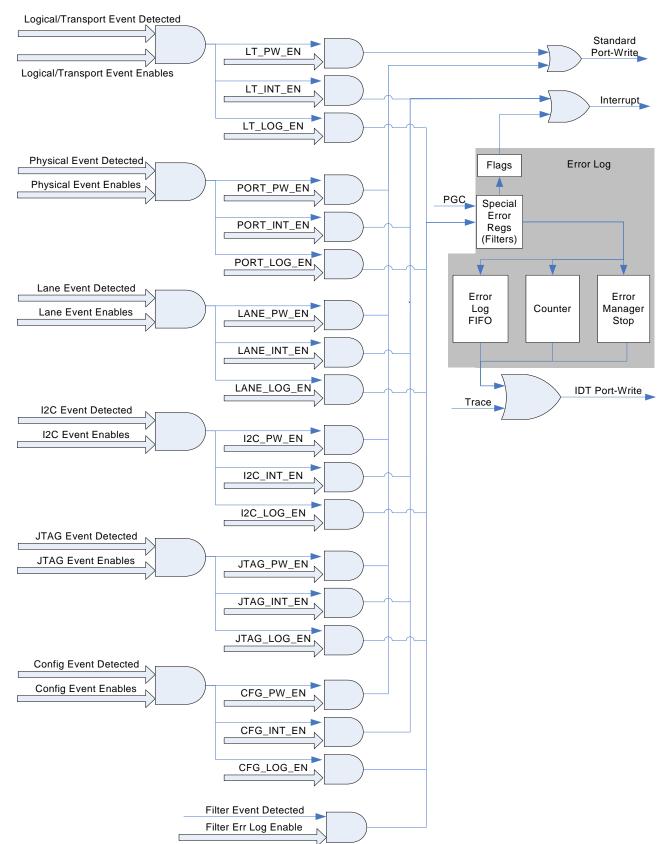

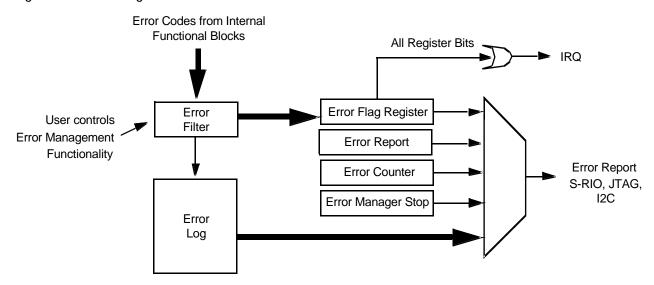

| 6. | Eve | nt Man   | nagement                                                                       | 104 |

|    | 6.1 | Event M  | Management Overview                                                            | 104 |

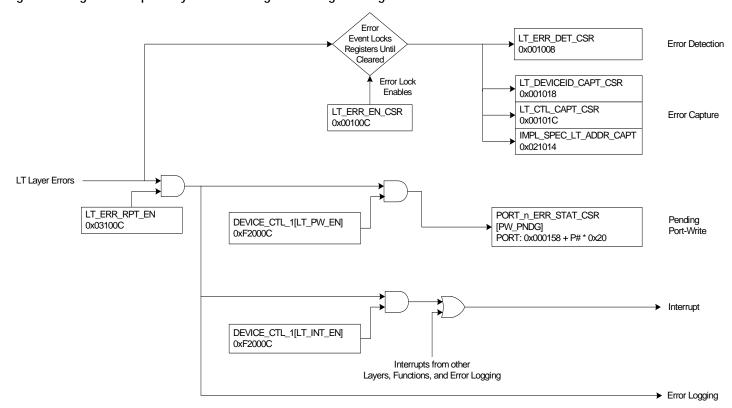

|    |     | 6.1.1    | Logical/Transport Layer Events Overview                                        | 108 |

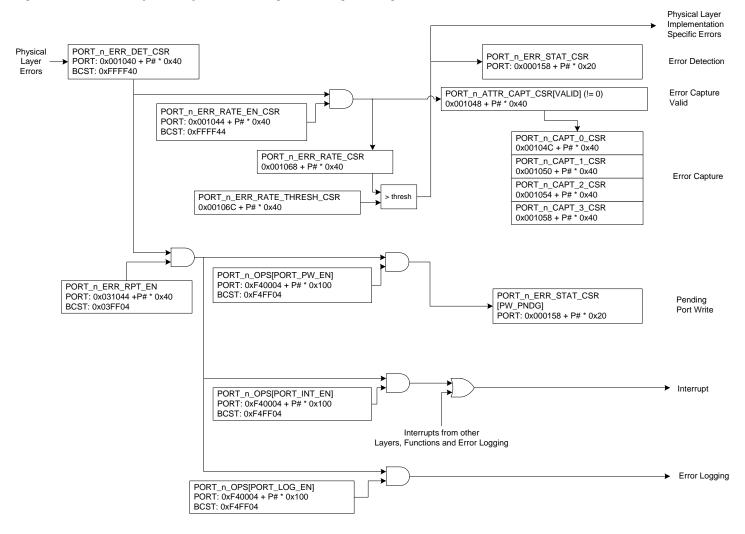

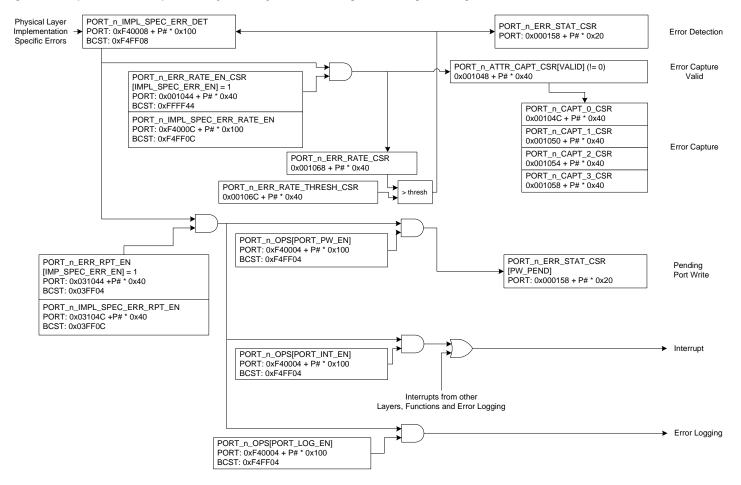

|    |     | 6.1.2    | Physical Layer Error Management Overview                                       | 109 |

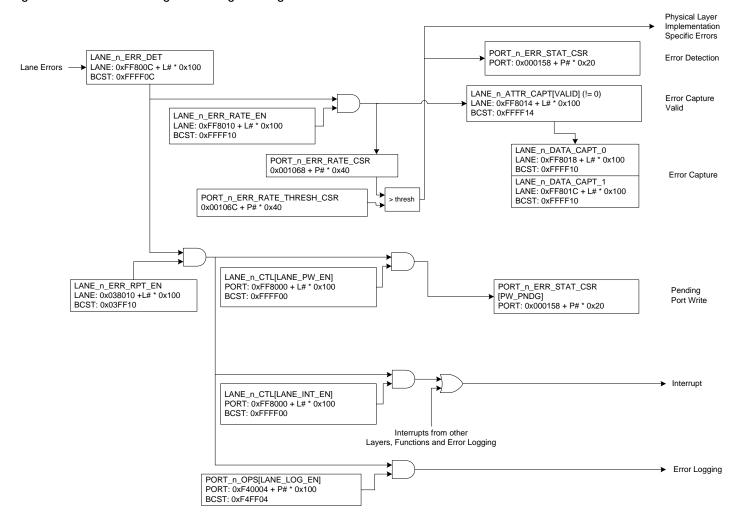

|    |     | 6.1.3    | Lane Error Management Overview                                                 | 111 |

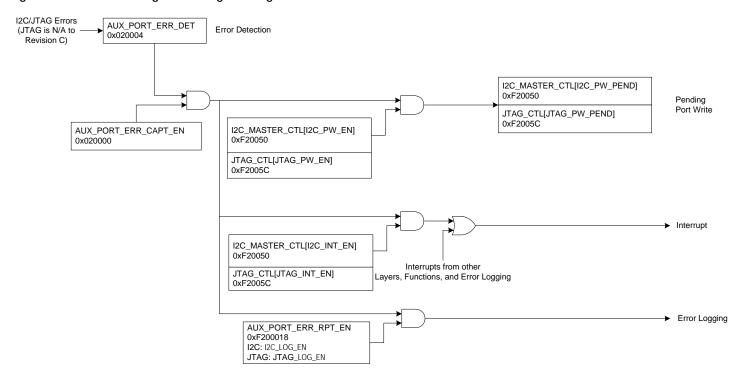

|    |     | 6.1.4    | I2C Error Management Overview                                                  | 112 |

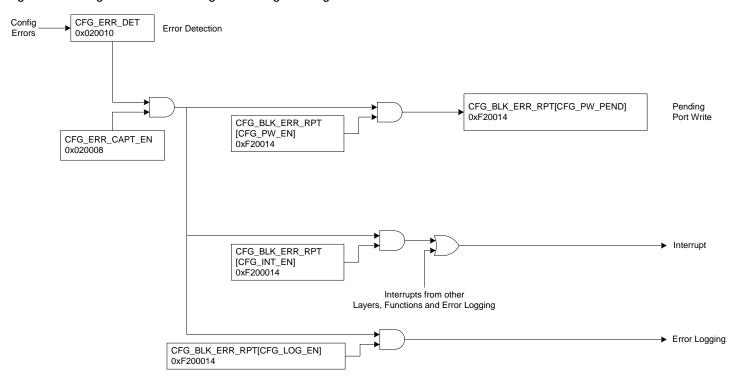

|    |     | 6.1.5    | Configuration Error Management Overview                                        | 113 |

|    | 6.2 | Event D  | Detection                                                                      | 113 |

|    |     | 6.2.1    | Logical and Transport Layer Events                                             | 113 |

|    |     | 6.2.2    | Physical Layer Events                                                          | 115 |

|    |     | 6.2.3    | Lane Events                                                                    | 124 |

|    |     | 6.2.4    | I2C Events                                                                     | 126 |

|    |     | 6.2.5    | JTAG Events (Revision A/B Only)                                                | 126 |

|    |     | 6.2.6    | Configuration Block Events                                                     |     |

|    |     | 6.2.7    | Trace and Filter Events                                                        | 127 |

|    |     | 6.2.8    | Packet Generation and Capture Mode Events                                      | 127 |

|    |     | 6.2.9    | Error Log Events                                                               | 127 |

|    | 6.3 | Event N  | lotification                                                                   | 137 |

|    |     | 6.3.1    | Logical Layer Events Notification                                              | 137 |

|    |     | 6.3.2    | Physical Layer Events Notification                                             | 139 |

|    |     | 6.3.3    | Lane Event Notification                                                        | 146 |

|    |     | 6.3.4    | I2C Event Notification                                                         | 146 |

|    |     | 6.3.5    | JTAG 1149.1 Event Notification (Revision A/B Only)                             | 147 |

|    |     | 6.3.6    | Configuration Block Event Notification                                         | 147 |

|    |     | 6.3.7    | Trace and Filter Event Notification                                            | 147 |

|    |     | 6.3.8    | Packet Generation and Capture Mode Event Notification                          | 147 |

|    |     | 6.3.9    | Port-Write Formats, Programming Model, and Generation                          | 148 |

|    |     | 6.3.10   | Interrupt Notification                                                         |     |

|    |     | 6.3.11   | Error Log Event Notification Programming Model                                 |     |

|    | 6.4 | Event Is | solation                                                                       | 154 |

|    |     | 6.4.1    | Fatal Link Response Timeout Isolation                                          |     |

|    |     | 6.4.2    | Received Retry Count Trigger Congestion Isolation                              |     |

|    |     | 6.4.3    | TTL Event Isolation                                                            |     |

|    |     | 6.4.4    | Transmit Packet Dropped via CRC Retransmit Limit Isolation                     |     |

|    |     | 6.4.5    | Packet Received With a CRC Error While CRC Error Suppression Enabled Isolation |     |

|    |     | 6.4.6    | Software Controlled Isolation Functions                                        | 158 |

|    | 6.5 | Event C  | Clearing and Recovery                                                          |     |

|    |     | 6.5.1    | Logical Layer Event Clearing and Handling                                      |     |

|    |     | 6.5.2    | Physical Layer Events Clearing and Handling                                    |     |

|    |     | 6.5.3    | Lane Event Clearing and Handling                                               |     |

|    |     | 6.5.4    | I2C Event Clearing and Handling                                                |     |

|    |     | 6.5.5    | JTAG 1149.1 Events (Revision A/B Only)                                         |     |

|    |     | 6.5.6    | Configuration Block Events                                                     |     |

|    |     | 6.5.7    | Trace, Filter, and PGC Events                                                  | 169 |

| <b>7</b> . | I2C                      | Interfa    | ace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 170 |  |  |

|------------|--------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

|            | 7.1                      | Overvie    | ew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 170 |  |  |

|            | 7.2                      | Master     | /Slave Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 170 |  |  |

|            | 7.3                      |            | rary Master Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |  |  |

|            | ,,,                      | 7.3.1      | Obtaining Configuration in Master Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |  |  |

|            |                          | 7.3.2      | Commanded Master Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |  |  |

|            |                          | 7.3.3      | Master Clock Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |  |  |

|            |                          | 7.3.4      | EEPROM Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |  |  |

|            |                          | 7.3.5      | CRC Calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |

|            |                          | 7.3.6      | Register Map Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |

|            |                          | 7.3.7      | EEPROM Format Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |  |  |

|            |                          | 7.3.8      | I2C Master Mode Validation Debug                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |  |  |

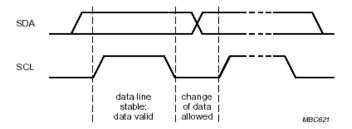

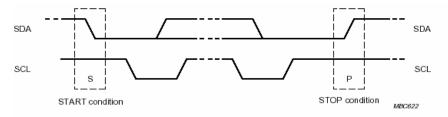

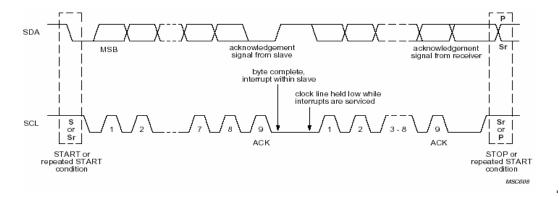

|            | 7.4                      |            | Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |

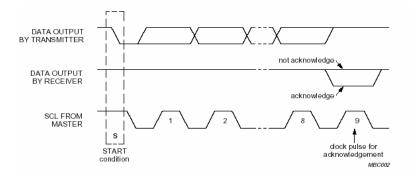

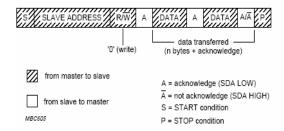

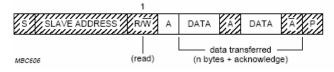

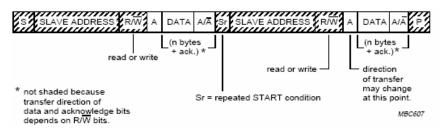

|            | 7.4                      | 7.4.1      | Signaling in Slave Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |  |  |

|            |                          | 7.4.1      | Connecting to Standard-, Fast-, and Hs-Mode Devices as a Slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |  |  |

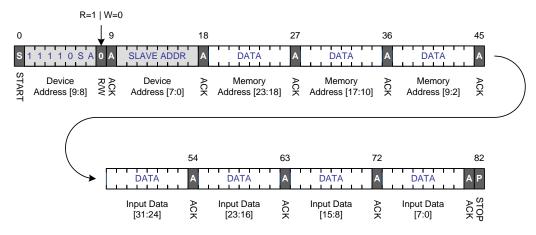

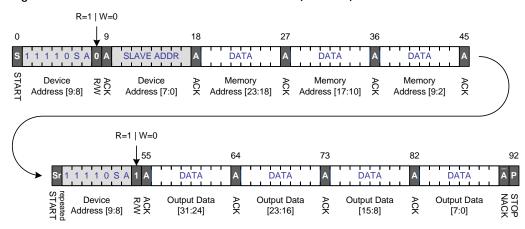

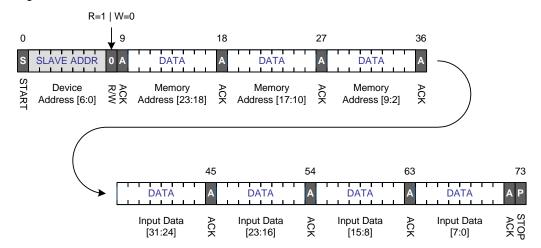

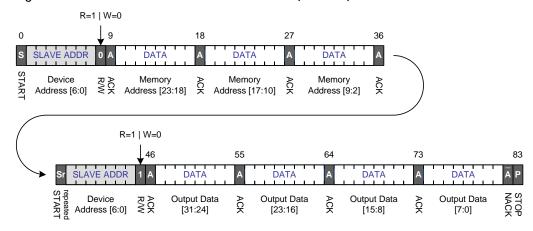

|            |                          | 7.4.2      | CPS-1848 Memory Access through I2C as a Slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |  |  |

| _          |                          |            | , and the second |     |  |  |

| 8.         |                          |            | Boundary Scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |  |  |

|            | 8.1                      |            | ew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |

|            | 8.2                      |            | and AC Extest Compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |  |  |

|            | 8.3                      |            | structions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |  |  |

|            | 8.4                      | Device     | ID Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 184 |  |  |

|            | 8.5                      | Initializa | ation and Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 185 |  |  |

|            | 8.6                      | Configu    | uration Register Access (Revision A/B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 185 |  |  |

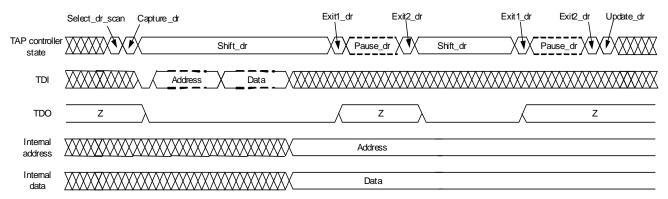

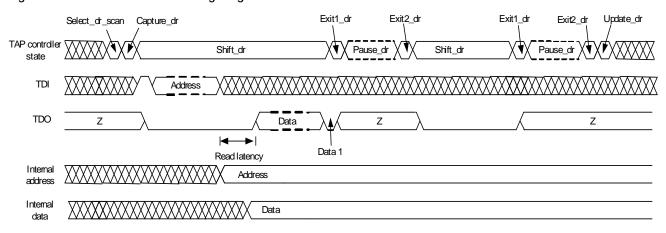

|            |                          | 8.6.1      | Configuration Register Access – Writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |  |  |

|            |                          | 8.6.2      | Configuration Register Access – Reads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |  |  |

|            | 8.7                      | Configu    | uration Register Access (Revision C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 187 |  |  |

|            |                          | 8.7.1      | Inter-Command Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 188 |  |  |

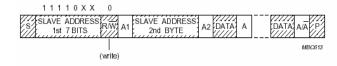

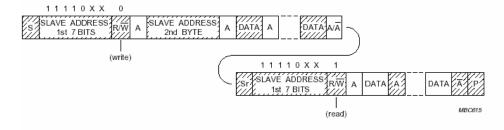

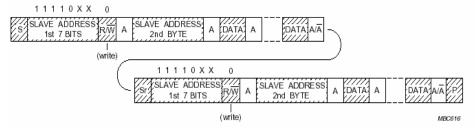

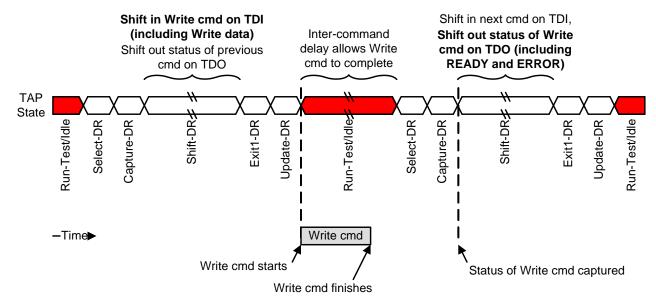

|            |                          | 8.7.2      | Configuration Register Access – Writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 190 |  |  |

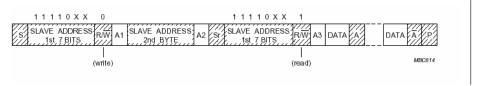

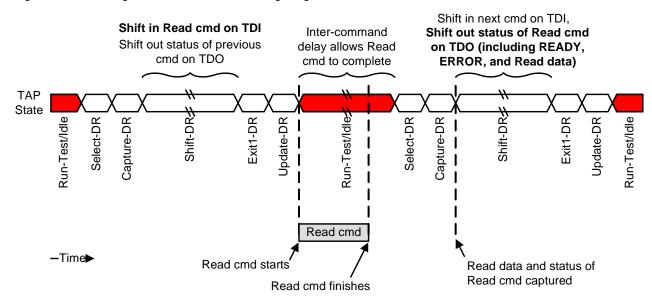

|            |                          | 8.7.3      | Configuration Register Access – Reads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 190 |  |  |