# **ZSSC3154 Functional Description**

## Contents

| 1. | Cont                      | rol Logic                       |                                      | 4  |  |  |  |  |

|----|---------------------------|---------------------------------|--------------------------------------|----|--|--|--|--|

|    | 1.1                       | Genera                          | al Description                       | 4  |  |  |  |  |

|    | 1.2                       | CMC D                           | Description                          | 4  |  |  |  |  |

|    | 1.3                       | Genera                          | al Working Modes                     | 4  |  |  |  |  |

|    |                           | 1.3.1                           | Normal Operation Mode (NOM)          | 4  |  |  |  |  |

|    |                           | 1.3.2                           | Command Mode (CM)                    | 5  |  |  |  |  |

|    |                           | 1.3.3                           | Diagnostic Mode (DM)                 | 7  |  |  |  |  |

|    |                           | 1.3.4                           | Failsafe Tasks and Error Codes       | 7  |  |  |  |  |

| 2. | Signa                     | al Conditi                      | ioning                               | 10 |  |  |  |  |

|    | 2.1                       | 1 A/D Conversion                |                                      |    |  |  |  |  |

|    | 2.2                       | Bridge                          | Sensor Signal Conditioning Formula   | 11 |  |  |  |  |

|    | 2.3                       | Temper                          | rature Signal Conditioning Formula   |    |  |  |  |  |

|    | 2.4                       | Half-Bri                        | idge Signal Conditioning Formula     | 12 |  |  |  |  |

|    | 2.5                       | Fitting (                       | Conditioning Result to Analog Output |    |  |  |  |  |

|    | 2.6                       | Digital I                       | Filter Function for Analog Output    | 14 |  |  |  |  |

|    | 2.7                       | Analog                          | Output Signal Range and Limitation   |    |  |  |  |  |

| 3. | Analog Output             |                                 |                                      |    |  |  |  |  |

|    | 3.1                       | 1 Analog Output Modes           |                                      |    |  |  |  |  |

|    | 3.2                       | .2 Power-On Diagnostic Output   |                                      |    |  |  |  |  |

|    | 3.3                       | 3 Sequential Analog Output Mode |                                      |    |  |  |  |  |

| 4. | Serial Digital Interfaces |                                 |                                      |    |  |  |  |  |

|    | 4.1                       | 4.1 General Description         |                                      |    |  |  |  |  |

|    |                           | 4.1.1                           | Command Structure                    |    |  |  |  |  |

|    |                           | 4.1.2                           | Addressing                           |    |  |  |  |  |

|    |                           | 4.1.3                           | Read-Request                         |    |  |  |  |  |

|    |                           | 4.1.4                           | Communication Verification           |    |  |  |  |  |

|    |                           | 4.1.5                           | Communication Protocol Selection     |    |  |  |  |  |

|    | 4.2                       | Digital (                       | Output                               |    |  |  |  |  |

|    | 4.3                       | 3 I2C Protocol                  |                                      |    |  |  |  |  |

|    | 4.4                       | One-W                           | /ire Communication (OWI)             |    |  |  |  |  |

|    |                           | 4.4.1                           | Properties and Parameters            |    |  |  |  |  |

|    |                           | 4.4.2                           | OWI Startup Window                   |    |  |  |  |  |

|    |                           | 4.4.3                           | OWI Protocol                         |    |  |  |  |  |

| 5. | Interface Commands        |                                 |                                      |    |  |  |  |  |

|    | 5.1                       | Command Set                     |                                      |    |  |  |  |  |

|    | 5.2                       | Command Processing              |                                      |    |  |  |  |  |

|    | 5.3                       | Digital (                       | Output Data in Command Mode          |    |  |  |  |  |

|    |                           |                                 |                                      |    |  |  |  |  |

|    | 5.4            | Detailed Description for Particular Commands |                                                                                                               |    |  |  |  |  |

|----|----------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|    |                | 5.4.1                                        | Acquisition of Raw Measurement Data with START_AD_CNT [62] <sub>HEX</sub>                                     | 36 |  |  |  |  |

|    |                | 5.4.2                                        | Oscillator Frequency Adjustment with ADJ_OSC_ACQ [50] <sub>HEX</sub> and ADJ_OSC_WRI [65 data] <sub>HEX</sub> | 37 |  |  |  |  |

| 6. | EEPROM and RAM |                                              |                                                                                                               |    |  |  |  |  |

|    | 6.1            | 6.1 Programming the EEPROM                   |                                                                                                               |    |  |  |  |  |

|    | 6.2            | .2 EEPROM and RAM Contents                   |                                                                                                               |    |  |  |  |  |

|    | 6.3            | .3 Traceability Information                  |                                                                                                               |    |  |  |  |  |

|    | 6.4            | Configura                                    | ation Words                                                                                                   | 42 |  |  |  |  |

|    |                |                                              | / Signature                                                                                                   |    |  |  |  |  |

|    | 6.6            | EEPRON                                       | / Write Locking                                                                                               | 47 |  |  |  |  |

| 7. | Gloss          | ary                                          |                                                                                                               | 48 |  |  |  |  |

| 8. | у              | 49                                           |                                                                                                               |    |  |  |  |  |

# **List of Figures**

| Figure 1.1  | Measurement Cycle                                                              | 6  |

|-------------|--------------------------------------------------------------------------------|----|

| Figure 1.2  | Measurement Cycle<br>Modes of Digital Serial Communication                     | 7  |

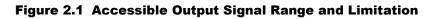

| Figure 2.1  | Accessible Output Signal Range and Limitation                                  | 15 |

| Figure 3.1  | Power-On Diagnostic Output Wave with the DFBH Pin Open                         |    |

| Figure 3.2  | Power-On Diagnostic Output Wave with Pin DFBH Connected to VSSA                |    |

| Figure 3.3  | Sequential Analog Output with the DFBH Pin Open                                | 19 |

| Figure 3.4  | Sequential Analog Output with the DFBH Pin Connected to VSSA                   | 19 |

| Figure 4.1  | I2C Read Request during NOM                                                    |    |

| Figure 4.2  | I2C or OWI Read Request in Temporary DM                                        |    |

| Figure 4.3  | I2C or OWI Read Request after Detecting an Error (Steady DM)                   |    |

| Figure 4.4  | I2C or OWI Read Request Answering a Command (CM)                               |    |

| Figure 4.5  | Principles of I2C Protocol<br>Write Operation I2C                              |    |

| Figure 4.6  | Write Operation I2C                                                            |    |

| Figure 4.7  | Read Operation I2C - (Data Request)                                            |    |

| Figure 4.8  | Timing I2C Protocol                                                            |    |

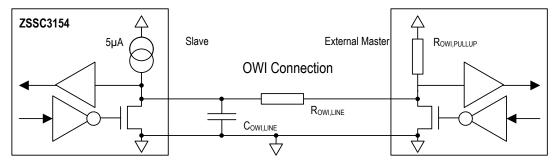

| Figure 4.9  | Block Schematic of an OWI Connection                                           |    |

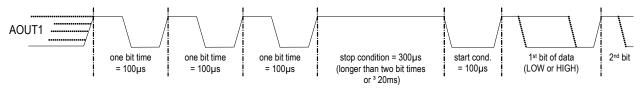

| Figure 4.10 | OWI and Actively Driven AOUT1-Starting OWI Communication with a Stop Condition |    |

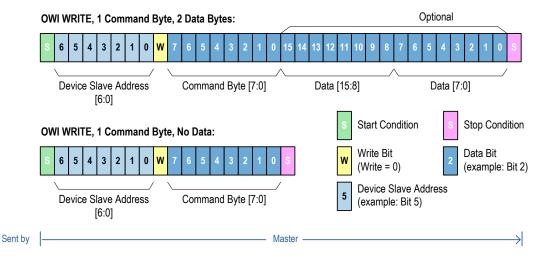

| Figure 4.11 | OWI Write Operation                                                            |    |

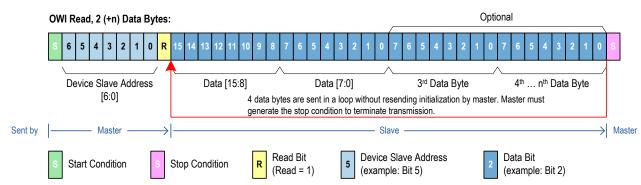

| Figure 4.12 | OWI Read Operation                                                             |    |

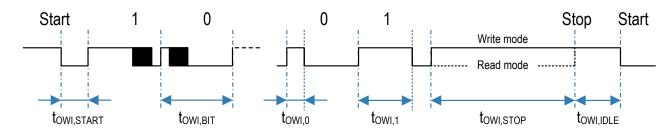

| Figure 4.13 | OWI Protocol Timing                                                            |    |

## **List of Tables**

| Error Detection Functionality and Error Codes               | 7                   |

|-------------------------------------------------------------|---------------------|

| Timing I2C Protocol                                         | 24                  |

| OWI Interface Basic Parameters                              | 25                  |

| OWI Interface Signal Parameters                             | 29                  |

| Command Set                                                 | 30                  |

| Digital Output Data Resulting from Processed Commands       | 36                  |

| A/D Conversion Response Resulting from START_AD_CNT Command |                     |

| EEPROM and RAM Contents                                     |                     |

|                                                             |                     |

| Configuration Word CFGAFE2                                  | 43                  |

| •                                                           |                     |

| Configuration Word CFGAPP2                                  | 44                  |

| Configuration Word CFGSF                                    | 45                  |

| C Source Code Signature Generation                          | 46                  |

|                                                             | Timing I2C Protocol |

## 1. Control Logic

## **1.1 General Description**

The control logic of the ZSSC3154 consists of the calibration microcontroller (CMC), the module control logic of the analog-to-digital converter (ADC) and the serial digital interface. The configuration of the various modes of the device is done by programming settings in EEPROM.

The CMC controls the measurement cycle and performs the calculations for sensor signal conditioning. This eliminates the gain deviation, the offset, the temperature deviation, and the non-linearity of the pre-amplified and A/D converted sensor signal. The A/D conversion is executed as a continuous measurement cycle. The conditioning calculation by the CMC is performed in parallel with the A/D conversion.

The ZSSC3154 communicates with an external microcontroller, especially for calibration purposes, via a serial digital interface. A communication protocol according to the I2C standard is supported. Additionally IDT's ZACwire<sup>™</sup> interface is implemented for one-wire communication (OWI). These serial interfaces are used for the calibration of the sensor system consisting of a transducer and the ZSSC3154. The serial interface provides the read out of the results of sensor signal conditioning as digital values during the calibration. The internal processing of received interface commands is done by the CMC. As a consequence, the measurement cycle is interrupted if a command is received. Only the read out of data is controlled by the serial interface itself, and this does not interrupt the CMC.

## 1.2 CMC Description

The calibration microcontroller (CMC) is especially adapted to the tasks connected with the signal conditioning.

These are the main features:

- The microcontroller uses 16-bit processing width and is programmed via ROM.

- A watchdog timer controls the proper operation of the microcontroller.

- Constants/coefficients for the conditioning calculation are stored in the EEPROM. The EEPROM is mirrored to the RAM after power-on or after re-initialization from EEPROM by sending a specific command to the serial interface.

- Parity is checked continuously during every read from RAM. If incorrect data is detected, the Diagnostic Mode is activated (an error code is written to the serial digital output, and the analog output is set to the diagnostic level).

## 1.3 General Working Modes

ZSSC3154 supports three different working modes:

- Normal Operation Mode (NOM)

- Command Mode (CM)

- Diagnostic Mode (DM)

## **1.3.1 Normal Operation Mode (NOM)**

The Normal Operation Mode (NOM) is the recommended working mode for applications. After power-on, the ZSSC3154 completes an initialization routine during which the EEPROM is mirrored to RAM and the contents are checked against a stored signature. If enabled, a ROM signature check is processed (see Table 6.6). If any error is detected, the Diagnostic Mode is activated. Otherwise the configuration of the ZSSC3154 is set, the serial digital interfaces are enabled, and NOM is started.

In NOM, the continuous measurement cycle and conditioning calculations are processed. The signal conditioning results generate the analog output at pins AOUT1 and AOUT2. The measurement cycle covers one or two main signals. The differential bridge sensor signal is always available. In addition, a temperature sensor signal or the half-bridge signal can be measured. Various analog output modes are available (refer to section 3.1).

Provided that the EEPROM is programmed correctly, NOM runs without sending any command to the digital serial interface. Readout of the conditioning results via the digital serial interface (I2C) is possible. This does not interrupt the continuous processing of the signal conditioning routine.

After power-on, a startup window is opened for one-wire communication (OWI) via the AOUT1 pin. During the startup window, the output levels at the AOUT1 pin depend on the selected OWI mode and the configured analog output mode (see section 4.4). To activate the Command Mode (CM) for end-of-line configuration and calibration, send the START\_CM command via OWI communication during the startup window (refer to the data sheet for timing specifications for the startup window). In CM, NOM is stopped and the ZSSC3154 waits for further commands.

The ZSSC3154 provides two analog voltage outputs at the AOUT1 and AOUT2 pins. The bridge sensor signal is always output at the AOUT1 pin. For the compensation of temperature dependent deviations via conditioning calculations, a calibration temperature is measured.

At the AOUT2 pin, there are several options for the output mode (see section 3), which can be configured in EEPROM. A separate temperature measurement is available for the output of a conditioned temperature signal. A half-bridge measurement is available for validating the main bridge sensor signal.

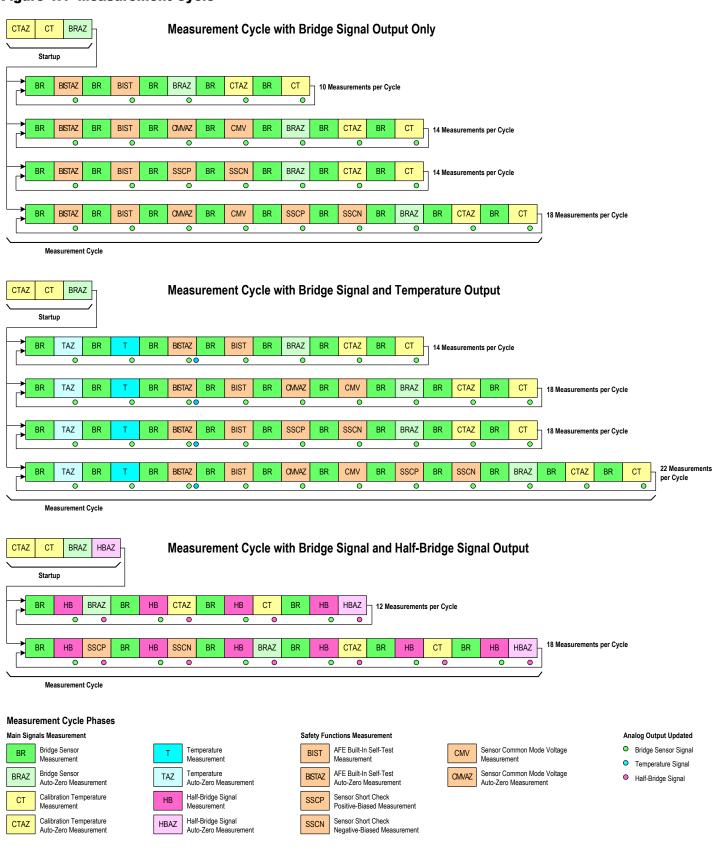

The measurement cycle is adapted to the selected measurement and safety tasks configured in EEPROM CFGAPP2:AOUT2MD and CFGSF, respectively. The measurement cycle is reduced to the minimum necessary measurement phases (see Figure 1.1). All measured signals are auto-zero compensated to eliminate offsets resulting from the selected measurement channel.

## 1.3.2 Command Mode (CM)

The Command Mode (CM) is the working mode that is used for calibration data acquisition and access to the internal RAM and EEPROM of the ZSSC3154. The CM start command START\_CM aborts the running NOM, so the measurement cycle stops. The ZSSC3154 changes to CM only after receiving the START\_CM command by digital serial communication (I2C or OWI). This protects the ZSSC3154 against interruption of processing the NOM (continuous signal conditioning mode) and/or unintentional changes of configuration. In CM, the full set of commands is supported (see section 5.1).

Starting CM via I2C communication (SCL and SDA pins) is possible at any time. If starting CM via one-wire communication (AOUT1 pin), the START\_CM command must be transmitted during the startup window.

If the ZSSC3154 receives a command other than START\_CM in NOM, it is not valid. It is ignored, and no interrupt to the continuous measurement cycle is generated.

In CM, the full command set is enabled for processing. During processing of a received command, the digital serial interfaces are disabled; no further commands are recognized. After finishing the processing, the CMC waits for further commands or processes requested measurement loops continuously. EEPROM programming is only enabled after receiving the EEP\_WRITE\_EN command.

#### Figure 1.1 Measurement Cycle

### Figure 1.2 Modes of Digital Serial Communication

## **1.3.3 Diagnostic Mode (DM)**

The ZSSC3154 detects various failures. When a failure is detected, Diagnostic Mode (DM) is activated. DM is indicated by setting both output pins AOUT1 and AOUT2 to the diagnostic fault band. The level of diagnostic output is configured by the DFBH pin. If the DFBH pin is open, the output is set to Diagnostic Fault Band Low (DFBL). If pin DFBH is connected to VSSA, output is set to Diagnostic Fault Band High (DFBH).

When using digital serial communication protocols (I2C or OWI) to read out conditioning results data, the error status is indicated by two bits in every data word.

DM generates a significant error code that can be read using the command GET\_ERR\_STATUS.

OWI communication is enabled during DM. Because the analog output pin AOUT1 is driven to the diagnostic range, the AOUT1 pin must be overwritten when starting OWI communication. The communication master must provide driving capability (AOUT1 current limitation: < 20mA).

Note that many of the error detection features can be enabled/disabled by configuration word CFGSF (refer to section 6.4).

There are three options for Diagnostic Mode:

- Steady Diagnostic Mode. In steady DM, the measurement cycle is stopped and failure notification is activated.

If enabled by the configuration bit CFGSF:DMRES, a reset after the timeout of a watchdog is executed.

- Temporary Diagnostic Mode. There is a failure counting sequence that can result in a temporary DM. DM is activated after two

consecutively detected failure events and is deactivated after a failure counter counts down if the failure condition is no longer detected.

The measurement cycle is continuously processed during temporary DM.

- Power and Ground Loss. Power and ground loss cases are signaled by setting the analog output pins to high-impedance states. The

output levels are determined by the external loads.

### 1.3.4 Failsafe Tasks and Error Codes

#### Table 1.1 Error Detection Functionality and Error Codes

| Failsafe Task                | Description                                                                                      | Error<br>Code       | Activation       | Messaging Time | Action          |

|------------------------------|--------------------------------------------------------------------------------------------------|---------------------|------------------|----------------|-----------------|

| Oscillator Fail Detection    | Oscillator is observed generating clock pulses by an asynchronous timing logic.                  | -                   | -                | < 200µs        | Temporary<br>DM |

| EEPROM<br>Signature          | Checks signature of RAM mirror against signature stored in EEPROM.                               | 6600 <sub>HEX</sub> | -                | Startup        |                 |

| ROM Signature                | Checks CMC ROM signature.<br>Note that this check potentially increases<br>startup time by 10ms. | 6500 <sub>HEX</sub> | CFGSF:<br>CHKROM | Startup        | Steady DM       |

| EEPROM<br>Multiple-Bit Error | Detection of non-correctable multiple-bit error per 16-bit word.                                 | 6440 <sub>HEX</sub> | -                | Startup        |                 |

| Failsafe Task        | Description                                                                                                                                                                                    | Error<br>Code       | Activation                 | Messaging Time                          | Action                          |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------|-----------------------------------------|---------------------------------|--|--|--|

| Arithmetic Check     | Functional check of arithmetic unit.                                                                                                                                                           | 6480 <sub>HEX</sub> | -                          | One measurement cycle                   | Stoody DM                       |  |  |  |

| Register Parity      | Permanent parity check of configuration registers.                                                                                                                                             | 6410 <sub>HEX</sub> | -                          | Immediate                               | Steady DM<br>or<br>Reset after  |  |  |  |

| RAM Parity           | Parity check at every RAM access.                                                                                                                                                              | 6404 <sub>HEX</sub> | -                          | Immediate                               | Watchdog<br>Timeout             |  |  |  |

| Watchdog             | Watchdog timeout during start routine<br>(65536 clocks if CFGAFE:ADCSLOW=0;<br>131072 clocks if ADCSLOW=1; refer to<br>Table 6.2) or measurement cycle<br>( $2 \times$ conversion cycle time). | 6402 <sub>HEX</sub> | _                          | Startup, 2 or 3<br>measurement<br>times | (enabled by<br>CFGSF:<br>DMRES) |  |  |  |

| BCC                  | Broken chip check.                                                                                                                                                                             | AA00 <sub>HEX</sub> | CFGSF:<br>CHKBCC           |                                         |                                 |  |  |  |

| TSC                  | Temperature sensor check: Detection of<br>overdriving the analog front-end during<br>temperature measurement.                                                                                  | C900 <sub>HEX</sub> | CFGSF:<br>CHKTSC           |                                         |                                 |  |  |  |

| SAC                  | Sensor aging check.                                                                                                                                                                            | A880 <sub>HEX</sub> | CFGSF:<br>CHKSAC           |                                         | Temporary<br>DM                 |  |  |  |

| SCC                  | Sensor connection check.                                                                                                                                                                       | A840 <sub>HEX</sub> | CFGSF:<br>CHKSCC           |                                         |                                 |  |  |  |

| SSC                  | Sensor short check.                                                                                                                                                                            | A820 <sub>HEX</sub> | CFGSF:<br>CHKSSC           | Two measurement cycles                  |                                 |  |  |  |

| AFEBIST              | Analog front-end (AFE) built-in self-test;<br>not executed if half-bridge signal<br>measurement is configured.                                                                                 | A810 <sub>HEX</sub> | AFEBISTMIN /<br>AFEBISTMAX |                                         |                                 |  |  |  |

| МССН                 | Main channel check – high: Detection of positive overdriving of the analog front-end during bridge measurement.                                                                                | A808 <sub>HEX</sub> | CFGSF:<br>CHKMCCH          |                                         |                                 |  |  |  |

| MCCL                 | Main channel check – low: Detection of negative overdriving of the analog front-end during bridge measurement.                                                                                 | A804 <sub>HEX</sub> | CFGSF:<br>CHKMCCL          |                                         |                                 |  |  |  |

| Power or Ground Loss | Power or ground loss detection.                                                                                                                                                                | _                   | _                          | < 5ms                                   | Reset                           |  |  |  |

Note: Error codes can be bit-wise masked. Bit [15] (MSB) is even parity. Bits [14:13] are error status flags. Error status is 1 (Temporary DM), 2 (Temporary DM, Temperature Fail), or 3 (Steady DM).

If the error status is 0 but the error code at bits [12:0] is set, this means that the indicated error was temporarily detected during normal operation but is currently not active anymore.

Note that the reset after the watchdog timeout clears any error codes that were previously generated.

## 1.3.4.1 Broken Chip Check (BCC)

The BCC detects damage and fractions of the silicon chip and its passivation caused by the production and assembly process. The check can be applied by the GET\_BCC\_STATUS command during the calibration process or cyclically in the measurement cycle during NOM.

## **1.3.4.2 Temperature Sensor Check (TSC)**

The temperature sensor check detects whether the ADC dynamic range has been exceeded during the temperature measurement. The temperature signal raw value is checked to determine if it is less than 128 or greater than  $(2^{14} - 128)$ .

This can result from various causes: the external temperature sensor is disconnected; the analog temperature input channel is not sufficiently calibrated or defective; or the temperature signal is out of targeted range.

## 1.3.4.3 Bridge Sensor Aging Check (SAC)

The sensor aging check detects long-term altering of the bridge sensor resistors that would result in a shift of the calibrated output characteristics. The SAC evaluates the common mode voltage of the sensor bridge once per measurement cycle if enabled. The measurement result is checked for compliance with programmed limits (CMVMIN / CMVMAX).

### **1.3.4.4 Bridge Sensor Connection Check (SCC)**

The sensor connection check monitors the connection of the bridge sensor at the VBP and VBN pins. An internally determined current is applied to the sensor, and the resulting differential input signal is evaluated once per measurement cycle if enabled.

The following failures are detected by SCC:

- High-resistive sensor bridge elements (e.g., a diaphragm rapture)

- Connection loss at the pins VBP, VBN, VBR\_T or VBR\_B

- Short between pins VBP or VBN and pins VBR\_T or VBR\_B

- Enabling the SCC High Capacitor Mode (CFGSF:CHKSCCHIC; see Table 6.6) is recommended in applications with a high capacitive load greater than 1nF up to 10nF at the input pins VBP and VBN.

### **1.3.4.5 Bridge Sensor Short Check (SSC)**

The sensor short check detects a short between the bridge sensor input pins VBP and VBN (connections less than  $50\Omega$  nominal). An internally determined current is applied to the sensor in both directions, resulting in differential input signals, which are evaluated once per measurement cycle if enabled. If a short occurs, the input signal difference of both is less than an internally determined limit.

### 1.3.4.6 Analog Front-End Built-In Self-Test (AFEBIST)

The analog front-end (AFE) built-in self-test detects whether the AFE (the programmable amplifier and the A/D converter) is functioning correctly. Adjusted to the configured analog gain, an internally generated analog input signal is measured via the main channel. The measurement result is checked against programmed limits (AFEBISTMIN / AFEBISTMAX; see Table 6.1).

Note that limits must be calibrated if AFEBIST is used. AFEBIST adds two further measurement phases to the measurement cycle. AFEBIST and the half-bridge measurement validate the same measurement channel. Hence AFEBIST is measured if and only if the half-bridge measurement is not enabled. AFEBIST validation can be disabled by setting the limits AFEBISTMIN / AFEBISTMAX to 0<sub>HEX</sub> and 3FFF<sub>HEX</sub>, respectively.

#### 1.3.4.7 Main Channel Check (MCCH/MCCL)

The main channel check detects whether the ADC dynamic range has been exceeded during the bridge measurement. The bridge signal raw value is checked to determine if the value is less than 128 or greater than  $(2^{14} - 128)$ . This can result from various causes: the bridge sensor is disconnected; the main input channel is defective or not sufficiently calibrated; or the bridge signal is out of targeted range.

The main channel check distinguishes between positive (MCCH) and negative (MCCL) overdrive to allow tailored overdrive handling at the bridge channel.

#### **1.3.4.8 Power and Ground Loss**

The detection of a power or ground loss is indicated by pulling the analog outputs AOUT1 and AOUT2 to the Diagnostic Fault Band. The level of the diagnostic output depends on the lost node and load connection to ground or supply. In such cases, the ZSSC3154 is inactive and the specified leakage current in combination with the load resistor guarantees reaching DFBH or DFBL.

## 2. Signal Conditioning

## 2.1 A/D Conversion

During NOM, the analog preconditioned sensor signal is continuously converted from analog to digital. The A/D conversion is performed with a 14-bit resolution  $r_{ADC}$  for all measurements in the measurement cycle (e.g., bridge sensor signal, temperature, half-bridge, auto-zero, etc.). The A/D conversion is configurable regarding the inherent range shift  $r_{ADC}$  for the bridge sensor signal and half-bridge signal measurement. All resulting digital raw values are determined by the following equations:

### Analog differential input voltage to A/D conversion (V<sub>ADC\_DIFF</sub>)

$$V_{ADC}_{DIFF} = a_{IN} * V_{IN}_{DIFF} + a_{XZC} * V_{XZC}$$

Where

| $V_{\text{IN}\_\text{DIFF}}$ | Differential input voltage to analog front-end                                                        |

|------------------------------|-------------------------------------------------------------------------------------------------------|

| V <sub>XZC</sub>             | Extended zero compensation voltage (programmable via CFGAFE:BRXZC and CFGAFE2:HBXZC; see section 6.4) |

| a <sub>IN</sub>              | Gain of analog front-end                                                                              |

| a <sub>XZC</sub>             | Gain for extended zero compensation voltage                                                           |

| V <sub>ADC_DIFF</sub>        | Differential input voltage to ADC                                                                     |

## Digital raw A/D conversion result (ZADC)

$$Z_{ADC} = 2^{r_{ADC}} * \left( \frac{V_{ADC\_DIFF} + V_{OFF}}{V_{ADC\_REF}} + r_{S_{ADC}} \right)$$

(2)

Where

| Voff                         | Residual offset voltage of analog front-end (which is eliminated by auto-zero compensation)  |

|------------------------------|----------------------------------------------------------------------------------------------|

| $V_{\text{ADC}\_\text{REF}}$ | ADC reference voltage (ratiometric reference for measurement)                                |

| r <sub>ADC</sub>             | Resolution of A/D conversion (14-bit)                                                        |

| rs <sub>ADC</sub>            | Range shift of A/D conversion (bridge or half-bridge: 1/2, 1/4, 1/8, 1/16; temperature: 1/2) |

### Auto-zero value (Z<sub>AZ</sub>)

$$Z_{AZ} = 2^{r_{ADC}} * \left( \frac{V_{OFF}}{V_{ADC} \_ REF} + r_{S_{ADC}} \right)$$

(3)

## Auto-zero corrected raw A/D conversion result (Z<sub>CORR</sub>)

$$Z_{CORR} = Z_{ADC} - Z_{AZ} = 2^{r_{ADC}} * \frac{V_{ADC} \_ DIFF}{V_{ADC} \_ REF}$$

(4)

(1)

## 2.2 Bridge Sensor Signal Conditioning Formula

The digital raw value Z<sub>BR,CORR</sub> for the measured bridge sensor signal is processed with a conditioning formula to remove offset and temperature dependency and to compensate nonlinearity up to 3<sup>rd</sup> order. The signal conditioning equation is processed by the CMC and is defined as follows:

Range definition of inputs (ZBR,CORR and ZCT,CORR)

$$Z_{\text{BR,CORR}} \in \left[ -2^{r_{\text{ADC}}}; 2^{r_{\text{ADC}}} \right)$$

$$Z_{\text{CT,CORR}} \in \left[ -2^{r_{\text{ADC}}-1}; 2^{r_{\text{ADC}}-1} \right)$$

(5)

(6)

Where

| r <sub>ADC</sub>     | Resolution of A/D conversion(14-bit)                                          |

|----------------------|-------------------------------------------------------------------------------|

| Z <sub>BR,CORR</sub> | Raw A/D conversion result for bridge sensor signal (auto-zero compensated)    |

| Z <sub>CT CORR</sub> | Raw A/D conversion result for calibration temperature (auto-zero compensated) |

In the following conditioning formulas, equation (7) compensates the offset and fits the gain including its temperature dependence. The nonlinearity for the intermediate result Y is then corrected in equation (8). The result of these equations is a non-negative value BR for measured bridge sensor signal in the range [0; 1).

Note that the conditioning coefficients c<sub>i</sub> are positive or negative values in two's complement.

#### Bridge signal conditioning equations

$$Y = \frac{Z_{BR,CORR} + c_0 + 2^{-(r_{ADC}-1)} * c_4 * Z_{CT,CORR} + 2^{-2(r_{ADC}-1)} * c_5 * Z_{CT,CORR}^2}{c_1 + 2^{-(r_{ADC}-1)} * c_6 * Z_{CT,CORR} + 2^{-2(r_{ADC}-1)} * c_7 * Z_{CT,CORR}^2} \qquad Y \in [0;1)$$

(7)

$$BR = Y * \left(1 - 2^{-15} * c_2 - 2^{-15} * c_3\right) + 2^{-15} * c_2 * Y^2 + 2^{-15} * c_3 * Y^3 \qquad BR \in [0;1)$$

(8)

Where

Conditioning coefficients stored in EEPROM registers  $00_{HEX}$  to  $07_{HEX}$ :

$c_i \in$  [-2^{15}; 2^{15}), two's complement.

- c<sub>0</sub> Bridge offset

- c1 Bridge gain

- c<sub>2</sub> Non-linearity correction 2<sup>nd</sup> order

- c<sub>3</sub> Non-linearity correction 3<sup>rd</sup> order

- c4 Temperature coefficient bridge offset 1st order

- c5 Temperature coefficient bridge offset 2<sup>nd</sup> order

- c<sub>6</sub> Temperature coefficient gain 1<sup>st</sup> order

- c7 Temperature coefficient gain 2<sup>nd</sup> order

## 2.3 Temperature Signal Conditioning Formula

The temperature measurement is enabled by selecting the appropriate analog output mode for the AOUT2 pin (CFGAPP2:AOUT2MD; see Table 6.5). The digital raw value  $Z_{T,CORR}$  for the measured temperature is processed with a conditioning formula to remove offset and to compensate nonlinearity up to 2<sup>nd</sup> order. The signal conditioning equation is processed by the CMC and is defined as follows:

#### Range definition of input (Z<sub>T,CORR</sub>):

$$Z_{T,CORR} \in \left[-2^{r_{ADC}-1}; 2^{r_{ADC}-1}\right]$$

Where

r<sub>ADC</sub> Resolution of A/D conversion (14-bit)

Z<sub>T,CORR</sub> Raw A/D conversion result for temperature (auto-zero compensated)

In the following temperature conditioning formulas, equation (10) compensates the offset and fits the gain. The nonlinearity for the intermediate result  $Y_T$  is then corrected in equation (11). The result of these equations is a non-negative value T for measured temperature in the range [0; 1).

Note that the conditioning coefficients t<sub>i</sub> are positive or negative values in two's complement format.

## Temperature signal conditioning equations

$$Y_{T} = \frac{Z_{T,CORR} + t_{0}}{t_{1}} \qquad Y_{T} \in [0;1)$$

(10)

$$T = Y_T * (1 - 2^{-15} * t_2) + 2^{-15} * t_2 * Y_T^2 \qquad T \in [0;1)$$

(11)

Where

Conditioning coefficients stored in EEPROM registers 08<sub>HEX</sub> to 0A<sub>HEX</sub> when temperature measurement is selected:

$t_i \in$  [-2<sup>15</sup>; 2<sup>15</sup>), two's complement.

- to Temperature offset

- t<sub>1</sub> Temperature gain

- t<sub>2</sub> Temperature non-linearity correction 2<sup>nd</sup> order

## 2.4 Half-Bridge Signal Conditioning Formula

The half-bridge signal measurement is enabled by selecting the appropriate analog output mode for the AOUT2 pin (CFGAPP2:AOUT2MD; see Table 6.5). The digital raw value  $Z_{HB,CORR}$  for the measured half-bridge signal is processed with a conditioning formula to remove offset and temperature dependency and to compensate nonlinearity up to  $2^{nd}$  order. The signal conditioning equation is processed by the CMC and is defined as follows:

(9)

Range definition of input (ZHB,CORR and ZCT,CORR):

$$Z_{HB,CORR} \in \left[-2^{r_{ADC}}; 2^{r_{ADC}}\right)$$

(12)

$$Z_{CT,CORR} \in \left[-2^{r_{ADC}-1}; 2^{r_{ADC}-1}\right)$$

Where

r<sub>ADC</sub>

Resolution of A/D conversion (14-bit)

Z<sub>HB,CORR</sub>

Raw A/D conversion result for half-bridge sensor signal (auto-zero compensated)

Z<sub>CT.CORR</sub>

Raw A/D conversion result for calibration temperature (auto-zero compensated)

In the following conditioning formulas, equation (14) compensates the offset and fits the gain including its temperature dependence. The nonlinearity for the intermediate result  $Y_{HB}$  is then corrected in equation (15). The result of these equations is a non-negative value HB for the measured half-bridge signal in the range [0; 1).

Note that the conditioning coefficients h<sub>i</sub> are positive or negative values in two's complement format.

### Half-bridge signal conditioning equations:

$$Y_{HB} = \frac{Z_{HB,CORR} + h_0 + 2^{-(r_{ADC}-1)} * h_4 * Z_{CT,CORR} + 2^{-2(r_{ADC}-1)} * h_5 * Z_{CT,CORR}^2}{h_1 + 2^{-(r_{ADC}-1)} * h_6 * Z_{CT,CORR} + 2^{-2(r_{ADC}-1)} * h_7 * Z_{CT,CORR}^2}$$

$$Y_{HB} \in [0;1)$$

(14)

$$HB = Y_{HB} * \left(1 - 2^{-15} * h_2\right) + 2^{-15} * h_2 * Y_{HB}^2 \qquad HB \in [0;1)$$

(15)

### Where

Conditioning coefficients stored in EEPROM registers 08<sub>HEX</sub> to 0E<sub>HEX</sub> when half-bridge measurement is selected:

- $h_i \in$  [-2<sup>15</sup>; 2<sup>15</sup>), two's complement.

- h<sub>0</sub> Half-bridge offset

- h1 Half-bridge gain

- h<sub>2</sub> Half-bridge non-linearity correction 2<sup>nd</sup> order

- h<sub>4</sub> Temperature coefficient half-bridge offset 1<sup>st</sup> order

- h<sub>5</sub> Temperature coefficient half-bridge offset 2<sup>nd</sup> order

- h<sub>6</sub> Temperature coefficient half-bridge gain 1<sup>st</sup> order

- h7 Temperature coefficient half-bridge gain 2<sup>nd</sup> order

## 2.5 Fitting Conditioning Result to Analog Output

The analog output is generated by a 5632-step D/A converter. This guarantees 12-bit analog output resolution for a typical output range of 10-to-90% VDDA or larger. For the calibration of the conditioning coefficients, the target output values must be fitted to that DAC resolution.

The fitting factor is 0.6875 =  $\begin{pmatrix} 5632\\ 2^{13} \end{pmatrix}$  and is applied to the normalized target values BR, T, HB  $\in$  [0; 1).

Note that this fitting is supported by the ZSSC3154 Evaluation Kit Software, which can be freely downloaded from IDT's web site (<u>www.IDT.com/ZSSC3154KIT</u>), but fitting is not part of the *RBIC1.DLL*, which is available on request for use with customer proprietary software.

(13)

## 2.6 Digital Filter Function for Analog Output

The ZSSC3154 offers digital (averaging) low-pass filters for the two analog output signals at pins AOUT1 and AOUT2. The output signal and mode at the AOUT2 pin are configured by EEPROM CFGAPP2:AOUT2MD (see section 6.4 and Table 6.5).

In NOM, the conditioned bridge sensor signal is always continually output at the AOUT1 pin. The AOUT1 output value is filtered with the integrating coefficient LPFAVRGBR and the differential coefficient LPFDIFFBR (see Table 6.1)

If the AOUT2 pin is configured to output a function of the bridge sensor signal, the AOUT2 output value is calculated with the conditioned and filtered bridge sensor value that is output at the AOUT1 pin.

If the AOUT2 pin is configured to output the temperature signal, the AOUT2 output value is filtered with the integrating coefficient LPFAVRGT and the differential coefficient LPFDIFFT.

If the AOUT2 pin is configured to output the half-bridge signal or a function of this signal, the AOUT2 output value is filtered with the integrating coefficient LPFAVRGHB and the differential coefficient LPFDIFFHB.

If the half-bridge sensor signal is output at the AOUT2 pin for validating the analog output of the bridge sensor signal at the AOUT1 pin, using equal filter coefficients is recommended.

The filter function is implemented as follows:

### Digital Filter Function (SOUT,0 and SOUT,i)

$$S_{OUT,0} = S_0 \tag{16}$$

$$S_{OUT,i} = S_{OUT,i-1} + (S_i - S_{OUT,i-1}) * \frac{LPFDIFF + 1}{2^{LPFAVRG}} \qquad i > 0$$

(17)

with LPFAVRG, LPFDIFF

$$\in$$

[0;7] and S<sub>OUT,i</sub>  $\in$  [0;1)

Where

| Si                 | Conditioned signal output result (refer to sections 2.2 through 2.4) |

|--------------------|----------------------------------------------------------------------|

| S <sub>OUT,i</sub> | Filtered signal output result                                        |

| LPFAVRG            | Averaging filter coefficient                                         |

| LPFDIFF            | Differential filter coefficient                                      |

The result of the filter function is a non-negative value  $S_{OUT}$  in the range [0; 1) which is used for continuously updating the analog output value during the measurement cycle.

Note that filtering is not applicable if CFGAPP:ADCMD is set to 11<sub>BIN</sub> (7-bit) (see Table 6.2).

Note that setting the coefficients LPFAVRG and LPFDIFF to 0 disables the filter function.

**Important:** For proper function, ensure that the factor  $\frac{LPFDIFF+1}{2^{LPFAVRG}}$  never becomes larger than 2!

Note that the readout of measurement values in NOM via I2C delivers conditioned but unfiltered result values S<sub>i</sub>.

## 2.7 Analog Output Signal Range and Limitation

The filtered conditioning results  $S_{OUT}$  for the measured bridge signal, the temperature signal, or the half-bridge signal are output at the analog output pins AOUT1 and AOUT2 with a resolution greater than 12 bits. The analog output voltage is generated using a resistor-string DAC with 5632 steps, of which 5120 steps (256 to 5375) can be addressed. As a result, an adjustable range from 5% to 95% of the supply voltage is guaranteed, including all possible tolerances.

Setting the analog output outside the allowed range (for example via the SET\_AOUTx command) will result in entering the diagnostic mode (DM) and setting the output to the DFB (Diagnostic Fault Band) level.

The ZSSC3154 offers an output limitation function for the analog output  $S_{OUT}$  that clips the output signal with the configurable limits AOUTMINx and AOUTMAXx as illustrated in Figure 2.1. These output minimum and maximum limits (13-bit accuracy) are defined in EEPROM with separate settings for the bridge, temperature, and half-bridge signal limits (see Table 6.1).

Note that these limit-setting registers (0F<sub>HEX</sub> through 12<sub>HEX</sub>) are shared with the digital filter configuration (the 3 LSBs).

## Analog Output Limitation (SAOUT)

$S_{AOUT} (S_{OUT} > AOUTMAX) = AOUTMAX$ (18)

$S_{AOUT} \left( S_{OUT} \in \left[ AOUTMAX; AOUTMIN \right] \right) = S_{OUT}$ (19)

$S_{AOUT} (S_{OUT} < AOUTMIN) = AOUTMIN$ (20)

with AOUTMIN, AOUTMAX

$$\in$$

[256;5375]

=  $[100_{HEX}; 14FF_{HEX}]$  (21)

### Where

| Sout    | Conditioned and filtered signal output result (refer to section 2.6) |

|---------|----------------------------------------------------------------------|

| SAOUT   | Clipped analog output result                                         |

| AOUTMIN | Lower analog output limit                                            |

| AOUTMAX | Upper analog output limit                                            |

The analog output voltage V<sub>AOUT</sub> is ratiometric to the power supply (V<sub>VDDE</sub> - V<sub>VSSE</sub>) and can be calculated using the following formula.

Analog Output Voltage (VAOUT)

$$V_{AOUT} = (V_{VDDE} - V_{VSSE}) * \frac{S_{AOUT}}{5632}$$

(22)

Where

S<sub>AOUT</sub> Conditioned, filtered and clipped signal output result

V<sub>AOUT</sub> Analog output voltage

V<sub>VDDE</sub>, V<sub>VSSE</sub> Voltages at VDDE and VSSE pins

Note that the readout of measured values in NOM via I2C delivers conditioned but unfiltered and unclipped values for S.

Note that if the output is a function *f* of the bridge sensor signal via AOUT2  $(1 - BR, \frac{1}{2} * BR, \text{ or } \frac{1}{2} * (1 - BR))$ , which can be configured by CFGAPP2:AOUT2MD, the function is applied to the conditioned, filtered, and clipped bridge signal BR<sub>AOUT</sub>. The resulting clipping limits for *f*(BR) at AOUT2 are consequently *f*(AOUTMINBR) and *f*(AOUTMAXBR).

## 3. Analog Output

## 3.1 Analog Output Modes

The ZSSC3154 provides two analog voltage outputs at the pins AOUT1 and AOUT2.

In NOM, the conditioned bridge sensor signal is continually output at the AOUT1 pin.

At the AOUT2 pin, several output modes are supported that are configured by EEPROM CFGAPP2:AOUT2MD:

- Continual output of the conditioned temperature signal

The selected temperature sensor is configured with CFGAPP:TS. It is possible to select the same sensor as is used for calibration temperature or to select a different temperature sensor (see Table 6.4).

- Continual output of the conditioned half-bridge signal

The half-bridge sensor signal can be used to validate the bridge sensor signal output at the AOUT1 pin (see Table 6.5). If the filter function is used for the bridge sensor signal, setting the coefficients for filtering the half-bridge signal to the same value is recommended. Note, that validating the main signal channel by the half-bridge sensor signal disables the analog front-end BIST functionality (AFEBIST, see Table 1.1 and Figure 1.1).

• Continual output of a function of bridge sensor signal

Output of a function of the bridge sensor signal can be used to validate the bridge sensor signal output at the AOUT1 pin. Several functions are available and are calculated from the conditioned and filtered bridge sensor output value (see Table 6.5).

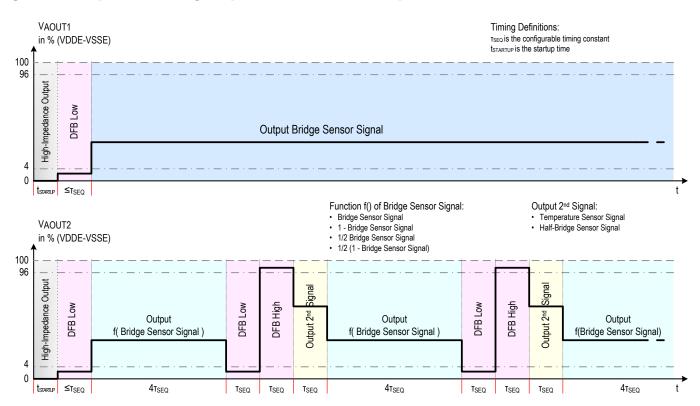

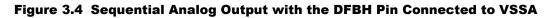

### - Sequential Analog Output Mode (SEQAOUT)

If the Sequential Analog Output Mode (SEQAOUT) is enabled, a configurable, continuous sequence is output on the AOUT2 pin (see Table 6.5 for the settings and section 3.3 for the order). The running sequence begins with the bridge signal or a function of the bridge signal; the Diagnostic Fault Band level driven by the DFBH pin; the inverted DFB level; and then the temperature or the half-bridge sensor. This allows validating the bridge sensor signal output at the AOUT1 pin. The Diagnostic Fault Band levels can be checked to ensure proper failure messaging.

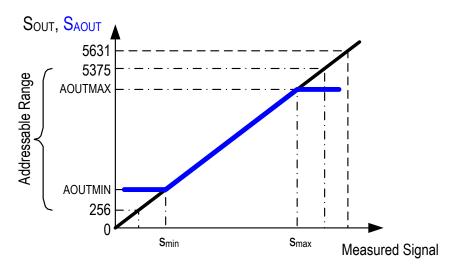

## 3.2 Power-On Diagnostic Output

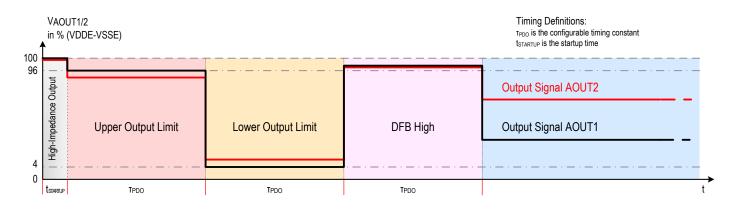

The ZSSC3154 provides a Power-On Diagnostic Output (PDO) wave. If enabled by EEPROM CFGSF:PDOENA, after power-on, the analog outputs at AOUT1 and AOUT2 run a one-time sequence of the upper and lower output limits followed by the diagnostic fault band output level (see Figure 3.1 and Figure 3.2). This can be used to check the operability of the chip and its output levels.

The upper and lower output limits are programmed in EEPROM independently for both output pins.

The diagnostic fault band output level depends on the DFBH pin. If the DFBH pin is open, both output pins AOUT1 and AOUT2 switch to the lower diagnostic fault band. If the DFBH pin is connected to VSSA, both output pins switch to the higher diagnostic fault band. Use the appropriate configuration for the user's application according to output pin loads.

Enabling the sequential analog output (SEQAOUT) for the AOUT2 pin with CFGAPP2:AOUT2MD disables PDO independently of control bit CFGSF:PDOENA.

If PDO is enabled, the startup window for one-wire communication via the AOUT1 pin is open during the two phases for the upper and lower output limits.

The duration  $\tau_{PDO}$  of each phase in the PDO sequence is 160ms (nominal) at  $f_{OSC}$  = 2.6MHz. This timing can be shortened by setting the divider CFGAPP:TIMEDIV.

#### Figure 3.1 Power-On Diagnostic Output Wave with the DFBH Pin Open

## 3.3 Sequential Analog Output Mode

The ZSSC3154 can provide the Sequential Analog Output Mode (SEQAOUT) at the AOUT2 pin if enabled by EEPROM CFAPP2:AOUT2MD. In this mode, the analog output at AOUT2 continuously runs a sequence of the bridge sensor signal followed by both diagnostic fault band output levels and by a 2<sup>nd</sup> configurable output signal (see Figure 3.3 and Figure 3.4). At the AOUT1 pin, the bridge sensor signal is continuously output.

The output of the diagnostic fault band levels can be used to check operability and proper failure messaging of the chip and to synchronize for evaluating both output signals. The actively driven diagnostic fault band level must be configured by connecting the DFBH pin to VSSA or by leaving it open. This actively driven diagnostic fault band level is output first in the SEQAOUT sequence; the reverse level follows.

The bridge sensor signal output in the SEQAOUT sequence can be manipulated by several functions selectable by CFGAPP2:AOUT2MD. This supports validating the bridge sensor signal output at pin AOUT1.

A half-bridge signal is selectable as the second signal output in the SEQAOUT sequence, which can also be used to validate bridge sensor signal.

Alternately the temperature signal can be selected as the second signal output. Depending on the selected temperature sensor (see Table 6.4, bits 5:3), this can be the sensor output used for calibration, which provides temperature compensation of the bridge sensor signal, or another temperature sensor.

The timing constant  $\tau_{SEQ}$ , which determines duration of the individual phases in the SEQAOUT sequence, is 37ms (nominal) at f<sub>OSC</sub>=2.6MHz. This timing can be shortened by setting the divider CFGAPP:TIMEDIV.

#### Figure 3.3 Sequential Analog Output with the DFBH Pin Open

## 4. Serial Digital Interfaces

## 4.1 General Description

The ZSSC3154 includes a serial digital I2C interface and a ZACwire<sup>™</sup> interface for one-wire communication (OWI). The digital interfaces allow programming the EEPROM to configure the application mode for the ZSSC3154 and to calibrate the conditioning equations. It also provides the readout of the conditioning results as a digital value. The ZSSC3154 always functions as a slave.

I2C access to the ZSSC3154 is available in all operation modes independent of the programmed configuration. The I2C interface is enabled after power-on and a short initialization phase. In Normal Operation Mode (NOM), the result values for the bridge sensor signal and for the temperature or the half-bridge signal can be read out.

To access the ZSSC3154 by using OWI communication, the START\_CM command must be transmitted in the startup window after power-on. For OWI communication, there are two possible startup window modes selectable by the CFGAPP2:OWIMD bit: with simultaneous analog output or without analog output during the startup window. The duration of the startup window depends on the selected analog output mode (refer to section 4.4.2). In NOM after the startup window, OWI communication is not applicable.

Transmitting the command START\_CM enables the Command Mode (CM). In CM, either communication protocol can be used; all commands are available to process calibration. EEPROM write access via I2C is always available in CM. The EEPROM lock bit only affects EEPROM write access via OWI communication (refer to section 6.6).

In Diagnostic Mode (DM), both communication protocols can be used to read an error code to identify the error source. A non-configured device, identified by a non-consistent EEPROM signature, starts up in DM. Because the analog output pin AOUT1 is driven to the diagnostic range in DM, the analog output must be overwritten when starting communication using OWI communication. Starting CM from DM by transmitting the START\_CM command is possible by using I2C or OWI communication.

In CM and DM, an alternating use of communication protocols is permitted.

## 4.1.1 Command Structure

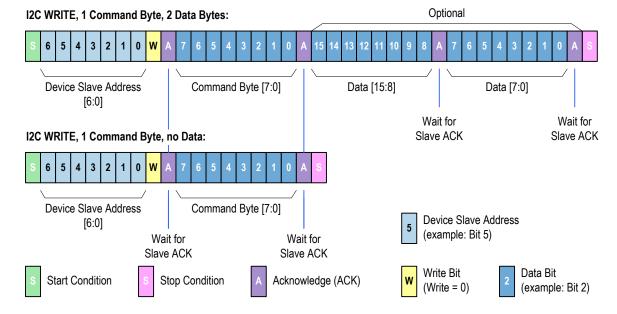

A command consists of a device address byte and a command byte. Some commands (e.g. writing data into EEPROM) also include two data bytes. The command structure is independent from the communication protocol used. Refer to section 1.3 for details of working modes and section 5 for command descriptions.

## 4.1.2 Addressing

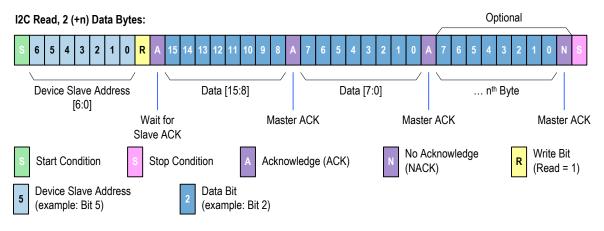

Addressing is supported by I2C and OWI communication protocol. Every slave connected to the master responds to a defined address. After generating the start condition, the master sends the address byte containing a 7-bit address followed by a data direction bit (R/W). A '0' indicates a transmission from master to slave (WRITE); a '1' indicates a data request (READ). The addressed slave answers with an acknowledge bit (I2C only). All other slaves connected to the master ignore this communication.

The ZSSC3154 always responds to its general ZSSC3154 slave address, which is  $28_{HEX}$  (7-bit). Via EEPROM programming, it is possible to allocate and activate an additional unique slave address within the range  $20_{HEX}$  to  $2F_{HEX}$  to the ZSSC3154. In this case, the device recognizes communication on both addresses, on the general one and on the additional one.

## 4.1.3 Read-Request

There are two general types of requests for reading data from the ZSSC3154:

Digital read out: Continuously reading the conditioned result in NOM via I2C communication only

During the measurement cycle, the ZSSC3154 transfers the conditioned results for the bridge sensor signal and for the temperature or halfbridge signal (as configured by CFGAPP2:AOUT2MD[bit 13] in register  $16_{HEX}$ ; see Table 6.5) into the output registers of the I2C interface. These data will be sent if the master generates a read-request via I2C. The active measurement cycle is not interrupted by this.

Calibration and/or configuration tasks via I2C or via OWI communication: Reading internal data (e.g., EEPROM content) or acquired measurement data in CM

To read internal and/or measurement data from the ZSSC3154 in CM, usually a specific command must be sent to transfer this data into the output registers of the digital interfaces. Thereafter the data will be sent if the master generates a read-request.

## 4.1.4 Communication Verification

In Normal Operation Mode (NOM) 16-bit data words are protected by even parity on the MSB (see section 4.2).

In Command Mode (CM) a read request is answered by the return of the data present in the digital interface output registers (2 bytes). Next a check sum is sent (1 byte) followed by the command which is answered (refer to section 4.2). The check sum and the returned command allow the verification of received data by the master. For details and exceptions, also see Table 5.2.

#### 4.1.5 Communication Protocol Selection

Both available protocols, I2C and OWI, can be active simultaneously, but only one interface can be used at a time.

An OWI communication access is also possible if OWI communication is enabled and analog output is active at the same time (i.e. during the startup window, in Diagnostic Mode, or in Command Mode after START\_CYCL commands). For this, the active output AOUT1 must be overwritten by the communication master, so generating a stop condition before starting the communication is recommended to guarantee a defined start of communication (refer to Figure 4.10).

## 4.2 Digital Output

A read request is answered by transmitting data from the digital interface output registers.

During the continuous measurement cycle (NOM, Temporary DM), the digital output via the I2C interface sends the 13-bit bridge sensor value and 13-bit temperature or half-bridge value (configured by the 16<sub>HEX</sub> register CFGAPP2:AOUT2MD[bit 13], see Table 6.5), depending on the configured analog output mode. The diagnostic status (ERR) is included with 2 bits per 16-bit word. The MSB carries an even-parity (PAR). The data is updated continuously when a new conditioned value is calculated.

Figure 4.1 I2C Read Request during NOM

|       |                   |           |     |                   | Bridge Sen                                  | isor Signal | Temperature or Half-Bridge Signal |                   |          |                                                    |     |

|-------|-------------------|-----------|-----|-------------------|---------------------------------------------|-------------|-----------------------------------|-------------------|----------|----------------------------------------------------|-----|

| Byte  | Device Address    | High Byte |     | gh Byte           | Low Byte                                    | Hi          |                                   | gh Byte           | Low Byte |                                                    |     |

|       | Address           | R/W       | PAR | ERR               | Bridge signal<br>(conditioned 13-bit value) |             |                                   | ERR               | Half-    | nperature or<br>Bridge signal<br>ned 13-bit value) |     |

| Value | 28 <sub>HEX</sub> | 1         | Ρ   | 00 <sub>bin</sub> | MSB                                         | LSB         | Ρ                                 | 00 <sub>bin</sub> | MSB      |                                                    | LSB |

During Temporary Diagnostic Mode (refer to section 1.3.3), the 2-bit diagnostic status ERR is set to 01<sub>BIN</sub> for bridge sensor and main channel related failures and set to 10<sub>BIN</sub> for temperature sensor related failures.

Figure 4.2 I2C or OWI Read Request in Temporary DM

|       |                   |     |     |                                          | Bridge Ser                                                      | nsor Signal |     | Temperature or Half-Bridge Signal        |                                                                                      |          |     |

|-------|-------------------|-----|-----|------------------------------------------|-----------------------------------------------------------------|-------------|-----|------------------------------------------|--------------------------------------------------------------------------------------|----------|-----|

| Byte  | Device Address    |     |     | Hig                                      | jh Byte                                                         | Low Byte    |     | Hig                                      | ıh Byte                                                                              | Low Byte |     |

|       | Address           | R/W | PAR | ERR                                      | Possibly invalid<br>Bridge signal<br>(conditioned 13-bit value) |             | PAR | ERR                                      | Possibly invalid<br>Temperature or<br>Half-Bridge signal<br>(conditioned 13-bit valu |          |     |

| Value | 28 <sub>HEX</sub> | 1   | Ρ   | 01 <sub>віл</sub> /<br>10 <sub>віл</sub> | MSB                                                             | LSB         | Ρ   | 01 <sub>віN</sub> /<br>10 <sub>віN</sub> |                                                                                      |          | LSB |

During Steady Diagnostic Mode (DM), i.e., when a permanent failure has been detected, the diagnostic status ERR is set to 11<sub>BIN</sub>. An error code is also transmitted to identify the failure source.

|       |                   |     |           | Error Code        |     |            |     |                   | Error Code |            |     |  |

|-------|-------------------|-----|-----------|-------------------|-----|------------|-----|-------------------|------------|------------|-----|--|

| Byte  | Device Address    |     | High Byte |                   |     | Low Byte   |     | High Byte Low By  |            |            |     |  |

|       | Address           | R/W | PAR       | ERR               |     | Error code | PAR | ERR               | E          | Error Code |     |  |

| Value | 28 <sub>HEX</sub> | 1   | Ρ         | 11 <sub>BIN</sub> | MSB | LSB        | Ρ   | 11 <sub>BIN</sub> | MSB        |            | LSB |  |

Figure 4.3 I2C or OWI Read Request after Detecting an Error (Steady DM)

In Command Mode (CM) a 2-byte answer is generated for every received command. A 1-byte check sum is added followed by the command that is being answered. The check sum and the command echo allow verification of received data by the master. For details and exceptions, refer to section 5.3.

Figure 4.4 I2C or OWI Read Request Answering a Command (CM)

|       |                   |     | Ans       | wer      | Verification |         |           |         |  |

|-------|-------------------|-----|-----------|----------|--------------|---------|-----------|---------|--|

| Byte  | Device Address    |     | High Byte | Low Byte | Hi           | gh Byte | Lo        | ow Byte |  |

|       | Address           | R/W | Response  | Ch       | eck Sum      | Com     | mand Echo |         |  |

| Value | 28 <sub>HEX</sub> | 1   | MSB       | LSB      | MSB          | LSB     | MSB       | LSB     |  |

## 4.3 I2C Protocol

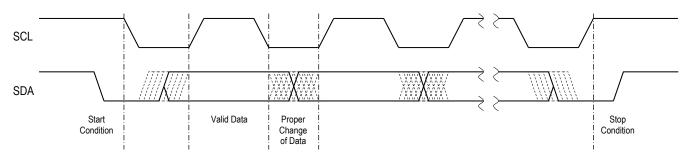

For I2C communication, a data line (SDA) and a clock line (SCL) are required as illustrated in Figure 4.5.

## Figure 4.5 Principles of I2C Protocol

The I2C communication and protocol used are defined as follows:

- Idle period: When the bus is inactive, SDA and SCL are pulled-up to supply voltage VDDA.

- Start condition: A high-to-low transition on SDA while SCL is at the high level indicates a start condition. Every command must be initiated by a start condition sent by a master. A master can always generate a start condition.

- Stop condition: A low-to-high transition on SDA while SCL is at the high level indicates a stop condition. A command must be closed by

a stop condition for the ZSSC3154 to start processing the command routine. The ZSSC3154 changes to inactive interface mode during

processing of internal command routines started by a previously sent command.

- Valid data: Data is transmitted in bytes starting with the most significant bit (MSB). Each byte transmitted is followed by an acknowledge bit. Transmitted bits are valid if after a start condition, SDA maintains a constant level during a high period of SCL. The SDA level must change only when the clock signal at SCL is low.

Acknowledge: An acknowledge after a transmitted byte is required. The master must generate an acknowledge-related clock pulse. The

receiver (slave or master) pulls-down the SDA line during the acknowledge clock pulse. If no acknowledge is generated by the receiver, a

transmitting slave will remain inactive. A transmitting master can abort the transmission by generating a stop condition and can then

repeat the command.

A receiving master must signal the end of transfer to the transmitting slave by not generating an acknowledge bit and by transmitting a subsequent stop condition.

- Write operation: During transmission from master to slave (WRITE), the device address byte is followed by a command byte and depending on the transmitted command, up to 2 optional data bytes. The internal microcontroller evaluates the received command and processes the related routine. See Figure 4.6.

- Read operation: After a data request from master to slave by sending a device address byte including a set-data-direction bit of 1, the slave answers by sending data from the interface output registers. The master must generate the transmission clock on SCL, acknowledges after each data byte (except after the last one), and then the stop condition. See Figure 4.7.

A data request is answered by the interface module itself and consequently does not interrupt the current process of the internal microcontroller.

The data in the output registers is sent continuously until a missed acknowledge occurs or a stop condition is detected. After transmitting all available data, the slave starts repeating the data.

During operation, measurement cycle data is continuously updated with conditioning results. To get other data from the slave (e.g., EEPROM content) a specific command must be sent before the data request to initiate the transfer of this data to the interface output registers. This command does interrupt the current process of the internal microcontroller, e.g. the active measurement cycle.

### Figure 4.6 Write Operation I2C

## Figure 4.7 Read Operation I2C – (Data Request)

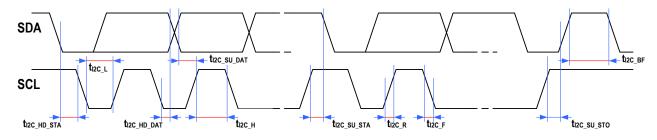

Figure 4.8 Timing I2C Protocol

| Table 4.1 | Fiming I2C | Protocol |

|-----------|------------|----------|

|-----------|------------|----------|

| No. | Parameter                                      | Symbol                  | Min | Typical | Max | Unit | Conditions              |

|-----|------------------------------------------------|-------------------------|-----|---------|-----|------|-------------------------|

| 1   | SCL clock frequency                            | f <sub>SCL</sub>        |     |         | 400 | kHz  | f <sub>OSC</sub> ≥ 2MHz |

| 2   | Bus free time between start and stop condition | t <sub>I2C_BF</sub>     | 1.3 |         |     | μs   |                         |

| 3   | Hold time start condition                      | t <sub>I2C_HD_STA</sub> | 0.6 |         |     | μs   |                         |

| 4   | Setup time repeated start condition            | t <sub>I2C_SU_STA</sub> | 0.6 |         |     | μs   |                         |

| 5   | Low period SCL/SDA                             | t <sub>I2C_L</sub>      | 1.3 |         |     | μs   |                         |

| 6   | High period SCL/SDA                            | t <sub>I2C_H</sub>      | 0.6 |         |     | μs   |                         |

| 7   | Data hold time                                 | t <sub>I2C_HD_DAT</sub> | 0   |         |     | μs   |                         |

| 8   | Data setup time                                | t <sub>I2C_SU_DAT</sub> | 0.1 |         |     | μs   |                         |

| 9   | Rise time SCL/SDA                              | t <sub>I2C_R</sub>      |     |         | 0.3 | μs   |                         |

| 10  | Fall time SCL/SDA                              | t <sub>I2C_F</sub>      |     |         | 0.3 | μs   |                         |

| 11  | Setup time stop condition                      | t <sub>I2C_SU_STO</sub> | 0.6 |         |     | μs   |                         |

| 12  | Noise interception SDA/SCL                     | t <sub>I2C_NI</sub>     |     |         | 50  | ns   | Spike suppression       |

## 4.4 One-Wire Communication (OWI)

The ZSSC3154 utilizes a ZACwire<sup>™</sup> interface, a digital interface concept for one-wire communication (OWI). It combines a simple and easy protocol adaptation with cost-saving pin sharing. The OWI communication principle is derived from the I2C protocol, so becoming familiar with the I2C protocol is recommended for an understanding of OWI communication.

Both the analog voltage output for normal operation and the one-wire digital interface for calibration use the same pin AOUT1. This enables "end of line" calibration; no additional pins are required to digitally calibrate a finished assembly.

## 4.4.1 Properties and Parameters

The ZSSC3154 functions as an OWI slave. An external master must control the communication by transmitting commands or data requests. Figure 4.9 explains the physical OWI connection in principle. Note that pulling up the OWI connection line must be done externally. There is no guarantee for using the ZSSC3154 internal pull-up. In addition, it might be necessary to implement a master push-pull driver to overwrite an analog output voltage at pin AOUT1 (I<sub>OUT,max</sub> = 20mA).

OWI communication is self-locking (synchronizing) on the master's communication speed in the range of the defined OWI bit time, which is guaranteed for the ZSSC3154's clock frequency in the range of 2 to 3MHz.

Figure 4.9 Block Schematic of an OWI Connection

### Table 4.2 OWI Interface Basic Parameters

Note: Also see Table 4.3 for additional specifications related to signal conditions and bit definitions.

| No. | Parameter                 | Symbol                  |               | Unit         | Conditions                                                                                   |

|-----|---------------------------|-------------------------|---------------|--------------|----------------------------------------------------------------------------------------------|

| 1   | OWI bit time              | t <sub>owi,BIT</sub>    | 0.04 to 4     | ms           | $t_{OWI,BIT} = 10 * R_{OWI,PULLUP} * C_{OWI,LINE}$<br>Guaranteed for $f_{OSC} = 2$ to 3 MHz. |

| 2   | Pull-up resistance master | R <sub>OWI,PULLUP</sub> | 3.3 (typical) | kΩ           |                                                                                              |

| 3   | OWI line resistance       | <b>R</b> owi,Line       | < 0.01        | Rowi, pullup |                                                                                              |

| 4   | OWI load capacitance      | $C_{\text{OWI,LOAD}}$   | 50 (typical)  | nF           | Total OWI line load.                                                                         |

| 5   | Voltage level LOW         | V <sub>OWI,L</sub>      | 0.2           | VDDA         | Min VDDA is 4.2V @ 4.5V VDDE                                                                 |

| 6   | Voltage level HIGH        | V <sub>OWI,H</sub>      | 0.75          | VDDA         | Max VDDA is 5.5V @ 5.5V VDDE                                                                 |

## 4.4.2 OWI Startup Window

OWI communication must be started via the start command START\_CM [72 74]<sub>HEX</sub> sent to the AOUT1 pin within a time window (nominal 200ms) after power-on. If this OWI startup window expires without the ZSSC3154 receiving a valid start command, OWI access is disabled.

The OWI startup window is activated immediately after initialization (nominal 5ms).

OWI startup window is affected by several EEPROM configuration bits:

#### CFGAPP2:OWIMD → OWI startup window mode

Analog voltage output starts after expiration of the OWI startup window (nominal 200ms). If CFGAPP2:OWIMD is set to 1, analog voltage output starts immediately after power-on, simultaneously with the OWI startup window. If CFGAPP2:OWIMD is set to 1, the OWI window is shortened to 50ms (nominal) and the OWI master must overwrite the active analog voltage output on the AOUT1 pin to send the start command START\_CM if OWI communication is needed.

#### CFGSF:PDOENA → Power-on Diagnostic Output

If the Power-on Diagnostic Output (PDO) is activated, a diagnostic sequence of the output limits and the diagnostic fault band (DFB) level is sent after power-on. The OWI startup window occurs simultaneously during the two PDO phases for the upper and lower analog output limits, so the startup window is 320ms (nominal) at  $f_{OSC} = 2.6$ MHz. (Refer to section 3.2 for further details on the timing).

#### CFGAPP2:AOUT2MD → Sequential Analog Output Mode (SEQAOUT) at AOUT2

When Sequential Analog Output Mode (SEQAOUT; see AOUT2MD in Table 6.5) is enabled, the OWI startup window is activated immediately after initialization and remains open until the beginning of the first occurrence of the Second Analog Signal on the AOUT2 pin (refer to section 3.3).

Note: Enabling SEQAOUT disables the Power-On Diagnostic Output (PDO) regardless of the setting for the control bit CFGSF:PDOENA.

In Command Mode (CM), OWI communication is always possible. After commands requesting an analog output at pin AOUT1, the OWI master must overwrite the analog voltage output for further communication.

In Diagnostic Mode (DM), OWI communication is also possible. If the pin AOUT1 is driven to Diagnostic Fault Band Low (DFBL), again the OWI master must overwrite this voltage level for communication. Note that an unconfigured ZSSC3154 with an invalid EEPROM signature always starts in DM.

### 4.4.3 OWI Protocol

OWI communication is always initiated by a master. Transmission starts with an address byte including a read/write bit to define the direction of the following byte transfer.

The OWI protocol is defined as follows:

Idle Period

During inactivity of the bus, the OWI communication line is pulled-up to supply voltage V<sub>VDDE</sub> by an external resistor.

Start Condition

When the OWI communication line is in idle mode, a low pulse with a minimum width of  $10\mu s^{1}$  and then a return to high indicates a start condition. Every command must be initiated by a start condition sent by a master. A master can generate a start condition only when the OWI line is in idle mode.

Stop Condition

A constant level at the OWI line (no transition from low to high or from high to low) for at least twice the period of the last transmitted valid bit indicates a stop condition. Without considering the last bit-time (secure stop condition), a stop condition is generated with a constant level at the OWI line for at least 20ms.

<sup>&</sup>lt;sup>1</sup> 10 $\mu$ s is the minimum t<sub>OWL\_START</sub> that guarantees the OWI start condition in the range of f<sub>OSC</sub> = 2 to 3 MHz.

The master finishes a transmission by changing back to the high level (idle mode). Every command (refer to the subsequent "Write Operation" section) must be closed by a stop condition to start the processing of the command. The master must interrupt a sending slave after it has completed a data request (refer to the subsequent "Read Operation" section) by clamping the OWI line to the low level for generating a stop condition.

In the case of an active analog voltage output at pin AOUT1, the output level must be overwritten by the OWI master. For example, this can occur if the OWI communication is started in the OWI startup window with a simultaneous analog voltage output. To ensure correct communication, first generate a stop condition (see Figure 4.10) before sending the first command (e.g., START\_CM). After the ZSSC3154 receives this first command, the analog output is disabled and OWI communication functions without sending additional sequences for this purpose.

#### Figure 4.10 OWI and Actively Driven AOUT1—Starting OWI Communication with a Stop Condition

Note: Bit times shown here are examples based on a given force.

#### Valid Data

Data is transmitted in bytes (8 bits) starting with the most significant bit (MSB). Transmitted bits are recognized after a start condition at every transition from low to high at the OWI line. The value of the transmitted bit depends on the duty ratio between the high phase and high/low period (bit period, t<sub>OWI,BIT</sub> in Figure 4.13). A duty ratio greater than 1/8 and less than 3/8 is detected as '0', a duty ratio greater than 5/8 and less than 7/8 is detected as '1'. The bit period of consecutive bits must not change by more than a factor of 2 because the stop condition is detected in this case.

#### Write Operation