32

# SH7734

Additional Document for User's Manual: Hardware

Renesas 32-Bit RISC Microcomputer SuperH<sup>TM</sup> RISC engine Family / SH-4A Series

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

All trademarks and registered trademarks are the property of their respective owners.

## Contents

| Sect | tion 1 S                                   | tream Interface (STIF)                                             | 1       |  |  |  |  |  |  |

|------|--------------------------------------------|--------------------------------------------------------------------|---------|--|--|--|--|--|--|

| 1.1  | Feature                                    | s                                                                  | 1       |  |  |  |  |  |  |

| 1.2  | Input/Output Pins                          |                                                                    |         |  |  |  |  |  |  |

| 1.3  | Registe                                    | Register Descriptions                                              |         |  |  |  |  |  |  |

|      | 1.3.1                                      | 1.3.1 STIF Mode Select Register (STMDR)                            |         |  |  |  |  |  |  |

|      | 1.3.2                                      | STIF Control Register (STCTLR)                                     | 8       |  |  |  |  |  |  |

|      | 1.3.3                                      | STIF Internal Counter Control Register (STCNTCR)                   | 10      |  |  |  |  |  |  |

|      | 1.3.4                                      | STIF Internal Counter Set Register (STCNTVR)                       | 11      |  |  |  |  |  |  |

|      | 1.3.5                                      | STIF Status Register (STSTR)                                       | 11      |  |  |  |  |  |  |

|      | 1.3.6                                      | STIF Interrupt Enable Register (STIER)                             | 14      |  |  |  |  |  |  |

|      | 1.3.7                                      | STIF Transfer Size Register (STSIZER) (n = 0,1)                    | 15      |  |  |  |  |  |  |

|      | 1.3.8                                      | STIFPWM Mode Register (STPWMMR)                                    | 16      |  |  |  |  |  |  |

|      | 1.3.9                                      | STIFPWM Control Register (STPWMCR)                                 | 20      |  |  |  |  |  |  |

|      | 1.3.10                                     | STIFPWM Register (STPWMR)                                          | 22      |  |  |  |  |  |  |

|      | 1.3.11                                     | STIFPCR0, STIFPCR1 Registers (STPCR0R, STPCR1R)                    | 23      |  |  |  |  |  |  |

|      | 1.3.12                                     | STIFSTC0, STIFSTC1 Registers (STSTC0R, STSTC1R)                    | 24      |  |  |  |  |  |  |

|      | 1.3.13 STIF Lock Control Register (STLKCR) |                                                                    |         |  |  |  |  |  |  |

|      | 1.3.14                                     | STIF Debugging Status Register (STDBGR)                            | 28      |  |  |  |  |  |  |

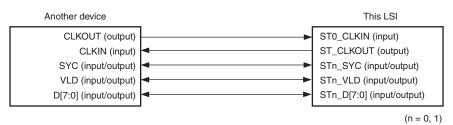

| 1.4  | Exampl                                     | les of Clock Connection to Another Device                          |         |  |  |  |  |  |  |

|      | 1.4.1                                      | A Basic Example                                                    | 28      |  |  |  |  |  |  |

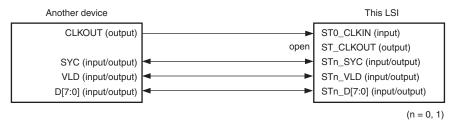

|      | 1.4.2                                      | An Example of Clock Connection                                     |         |  |  |  |  |  |  |

|      |                                            | when Another Device Has No Clock Input                             | 29      |  |  |  |  |  |  |

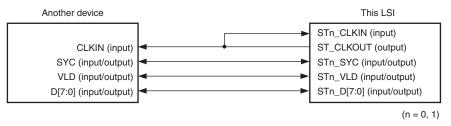

|      | 1.4.3                                      | An Example of Clock Connection                                     |         |  |  |  |  |  |  |

|      |                                            | when Another Device Has No Clock Output                            | 29      |  |  |  |  |  |  |

| 1.5  | Input/C                                    | Output Timing                                                      | 29      |  |  |  |  |  |  |

| 1.6  | PCR Cl                                     | lock Recovery Module (PCRRCV)                                      | 36      |  |  |  |  |  |  |

|      | 1.6.1                                      | Operation of PCR Clock Recovery                                    | 37      |  |  |  |  |  |  |

|      | 1.6.2                                      | PCR Clock Recovery Operation                                       | 39      |  |  |  |  |  |  |

| 1.7  | Usage I                                    | Notes                                                              | 43      |  |  |  |  |  |  |

| Sect | tion 2 S                                   | Stream Interface (STIF) Electrical Characteristics                 | 15      |  |  |  |  |  |  |

| 2.1  |                                            | Module Signal Timing (1)                                           |         |  |  |  |  |  |  |

| ۷,1  | 2.1.1                                      | STIF Module Signal Timing (2)                                      |         |  |  |  |  |  |  |

|      | 2.1.1                                      | STIF Module Signal Timing (2)                                      |         |  |  |  |  |  |  |

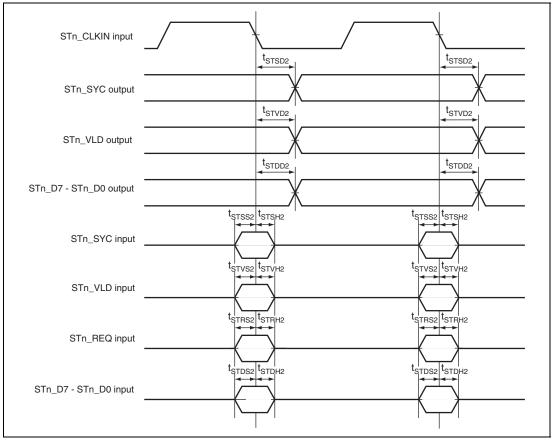

|      | 2.1.2                                      | (With Stream Input/Output Set Synchronized with STn_CLKIN Rise Ti  | ime) 47 |  |  |  |  |  |  |

|      |                                            | ( ,, in stream input output out syncinomized with stri_CERM Rise I | c, + /  |  |  |  |  |  |  |

|       | 2.1.3  | STIF Module Signal Timing (4)                                                |    |

|-------|--------|------------------------------------------------------------------------------|----|

|       |        | (With Stream Input/Output Set Synchronized with STn_CLKIN Fall Time)         | 49 |

|       | 2.1.4  | STIF Module Signal Timing (5)                                                |    |

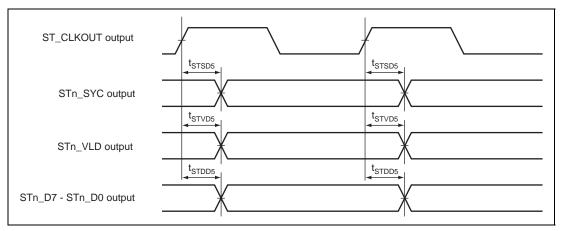

|       |        | (With Stream Input/Output Set Synchronized with ST_CLKOUT Rise               |    |

|       |        | Time)                                                                        | 51 |

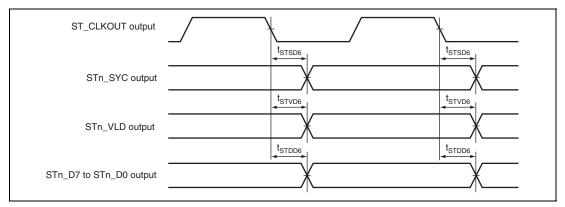

|       | 2.1.5  | STIF Module Signal Timing (6)                                                |    |

|       |        | (With Stream Input/Output Set Synchronized with ST_CLKOUT Fall               |    |

|       |        | Time)                                                                        | 52 |

|       |        |                                                                              |    |

| Secti |        | MAC That Works with Forward Error Correction Core                            |    |

|       | `      | ı-DMAC)                                                                      |    |

| 3.1   |        | N                                                                            |    |

|       | 3.1.1  | Features                                                                     |    |

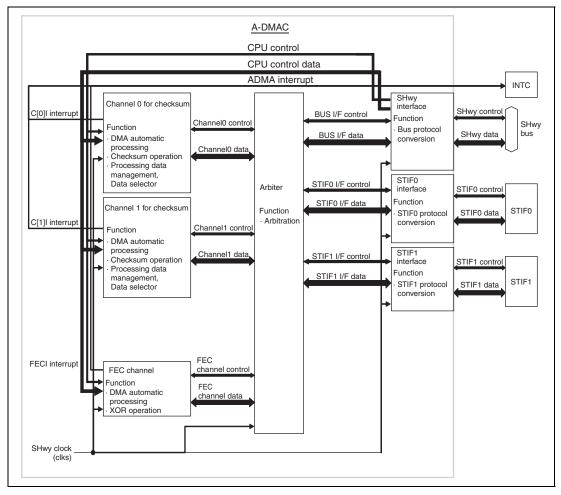

|       | 3.1.2  | Overall Configuration of the A-DMAC                                          |    |

|       | 3.1.3  | Restrictions on the A-DMAC                                                   |    |

| 3.2   | _      | Descriptions                                                                 |    |

|       | 3.2.1  | Channel [i] Processing Control Register ( $C[i]C$ ) ( $i = 0, 1$ )           |    |

|       | 3.2.2  | Channel [i] Processing Mode Register ( $C[i]M$ ) ( $i = 0, 1$ )              |    |

|       | 3.2.3  | Channel [i] Processing Interrupt Request Register ( $C[i]I$ ) ( $i = 0, 1$ ) | 65 |

|       | 3.2.4  | Channel [i] Processing Descriptor Start Address Register (C[i]DSA)           |    |

|       |        | (i = 0, 1)                                                                   | 67 |

|       | 3.2.5  | Channel [i] Processing Descriptor Current Address Register (C[i]DCA)         |    |

|       |        | (i = 0, 1)                                                                   |    |

|       | 3.2.6  | Channel [i] Processing Descriptor 0 Register (C[i]D0) [Control] (i = 0, 1)   | 69 |

|       | 3.2.7  | Channel [i] Processing Descriptor 1 Register (C[i]D1) [Source Address]       |    |

|       |        | (i = 0, 1)                                                                   | 75 |

|       | 3.2.8  | Channel [i] Processing Descriptor 2 Register (C[i]D2) [Destination Address]  |    |

|       |        | (i = 0, 1)                                                                   | 76 |

|       | 3.2.9  | Channel [i] Processing Descriptor 3 Register (C[i]D3) [Data Length]          |    |

|       |        | (i = 0, 1)                                                                   | 76 |

|       | 3.2.10 | Channel [i] Processing Descriptor 4 Register (C[i]D4)                        |    |

|       |        | [Checksum Value Write Address] (i = 0, 1)                                    |    |

|       | 3.2.11 | FEC DMAC Processing Control Register (FECC)                                  | 79 |

|       | 3.2.12 | FEC DMAC Processing Interrupt Request Register (FECI)                        | 82 |

|       | 3.2.13 | FEC DMAC Processing Descriptor Start Address Register (FECDSA)               | 85 |

|       | 3.2.14 | FEC DMAC Processing Descriptor Current Address Register (FECDCA)             | 86 |

|       | 3.2.15 | FEC DMAC Processing Descriptor 0 Register (FECD00) [Control]                 | 87 |

|       | 3.2.16 | FEC DMAC Processing Descriptor 1 Register (FECD01D0A)                        |    |

|       |        | [Destination Address]                                                        | 91 |

|      | 3.2.17    | FEC DMAC Processing Descriptor 2 Register (FECD02S0A)             |     |

|------|-----------|-------------------------------------------------------------------|-----|

|      |           | [Source 0 Address]                                                | 91  |

|      | 3.2.18    | FEC DMAC Processing Descriptor 3 Register (FECD03S1A)             |     |

|      |           | [Source 1 Address]                                                |     |

| 3.3  | Function  | ns                                                                |     |

|      | 3.3.1     | DMAC Channel Function                                             |     |

|      | 3.3.2     | Checksum                                                          |     |

|      | 3.3.3     | FEC Channel                                                       |     |

|      | 3.3.4     | FEC Operation                                                     | 95  |

| 3.4  | Channel   | Operation                                                         | 96  |

|      | 3.4.1     | Descriptor Format                                                 | 96  |

|      | 3.4.2     | Basic Channel Operation                                           | 97  |

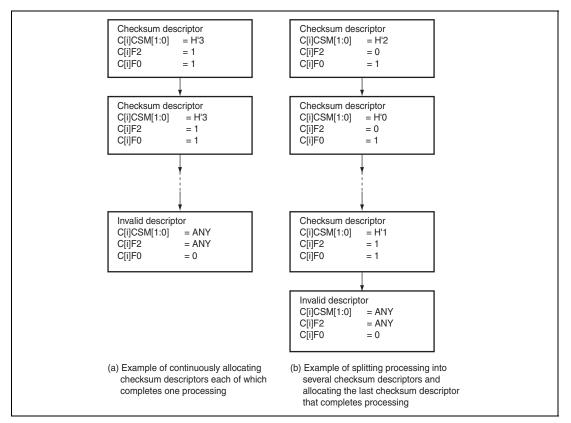

|      | 3.4.3     | Checksum                                                          | 98  |

| 3.5  | FEC Ch    | annel Operation                                                   | 99  |

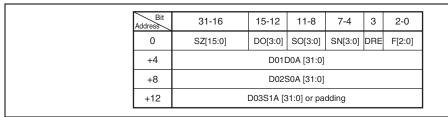

|      | 3.5.1     | Descriptor Format for FEC Channel                                 | 99  |

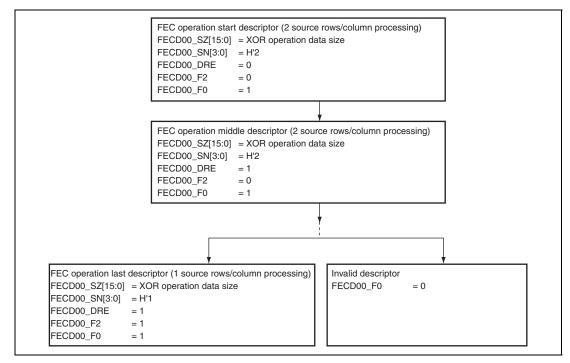

|      | 3.5.2     | Basic FEC Channel Operation                                       | 100 |

| 3.6  | Usage N   | Notes                                                             | 102 |

|      | 3.6.1     | Data Transfer Size Set in Descriptor for A-DMAC Channel Operation | 102 |

| Sect | tion 4 II | EBus <sup>™</sup> Controller                                      | 103 |

| 4.1  | Overvie   | W                                                                 | 103 |

|      | 4.1.1     | Features                                                          |     |

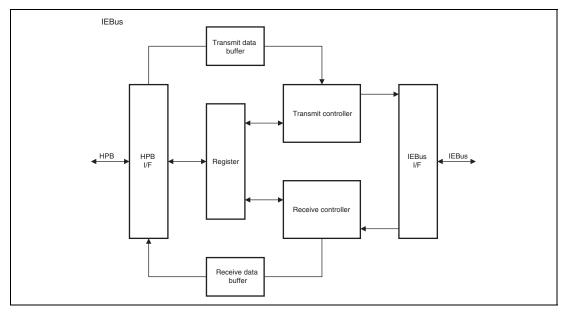

|      | 4.1.2     | Block Diagram                                                     |     |

|      | 4.1.3     | Input/Output Pins                                                 |     |

|      | 4.1.4     | Register Configuration                                            |     |

| 4.2  |           | Descriptions                                                      |     |

|      | 4.2.1     | IEBus Control Register (IECTR)                                    |     |

|      | 4.2.2     | IEBus Command Register (IECMR)                                    |     |

|      | 4.2.3     | IEBus Master Control Register (IEMCR)                             |     |

|      | 4.2.4     | IEBus Local Address Register 1 (IEAR1)                            |     |

|      | 4.2.5     | IEBus Local Address Register 2 (IEAR2)                            |     |

|      | 4.2.6     | IEBus Slave Address Setting Register 1 (IESA1)                    |     |

|      | 4.2.7     | IEBus Slave Address Setting Register 2 (IESA2)                    |     |

|      | 4.2.8     | IEBus Transmit Telegram Length Register (IETBFL)                  |     |

|      | 4.2.9     | IETBR                                                             |     |

|      | 4.2.10    | IEBus Receive Master Address Register 1 (IEMA1)                   |     |

|      | 4.2.11    | IEBus Receive Master Address Register 2 (IEMA2)                   |     |

|      | 4.2.12    | IEBus Receive Control Field Register (IERCTL)                     |     |

|      | 4.2.13    | IEBus Receive Telegram Length Register (IERBFL)                   |     |

|      | 4.2.14    | IERBR                                                             |     |

|      | 7.4.17    | 1L/1XL/1X                                                         | 144 |

|      | 4.2.15    | IELA1                                            | 122 |

|------|-----------|--------------------------------------------------|-----|

|      | 4.2.16    | IELA2                                            | 123 |

|      | 4.2.17    | IEBus General Flag Register (IEFLG)              | 124 |

|      | 4.2.18    | IEBus Transmit Status Register (IETSR)           | 126 |

|      | 4.2.19    | IEBus Transmit Interrupt Enable Register (IEIET) | 129 |

|      | 4.2.20    | IETEF                                            |     |

|      | 4.2.21    | IEBus Receive Status Register (IERSR)            | 131 |

|      | 4.2.22    | IEBus Receive Interrupt Enable Register (IEIER)  | 136 |

|      | 4.2.23    | IEREF                                            | 138 |

|      | 4.2.24    | IEBus Transmit Data Buffer (IETB01 to IETB32)    | 138 |

|      | 4.2.25    | IEBus Receive Data Buffer (IERB01 to IERB32)     | 139 |

| 4.3  | Operation | on                                               | 140 |

|      | 4.3.1     | Interface                                        | 140 |

|      | 4.3.2     | Data Format                                      | 141 |

|      | 4.3.3     | Software Control Flow                            | 142 |

|      | 4.3.4     | Operational Timing                               | 145 |

| Sect | ion 5 E   | nabling the IEBus <sup>TM</sup> Controller       | 147 |

| Maiı | n Revisio | ons and Additions in this Edition                | 149 |

## Section 1 Stream Interface (STIF)

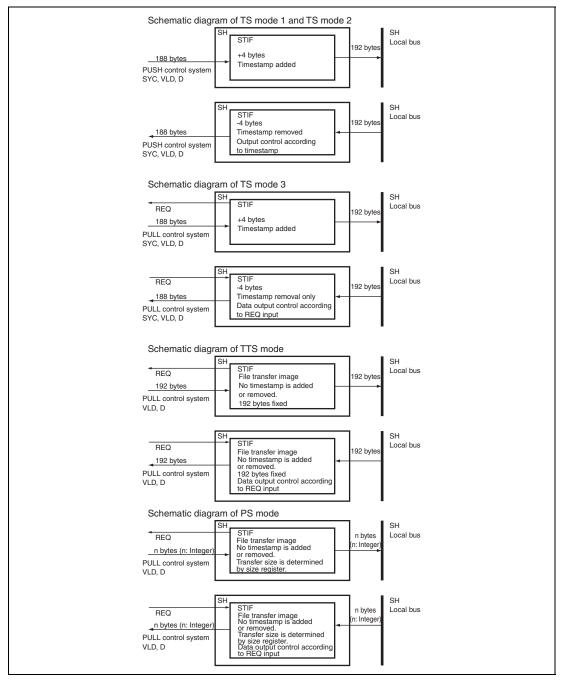

This LSI has a 2-channel stream interface (STIF).

#### 1.1 **Features**

- Two-channel bidirectional interface

- Supports TS packets (packet size: 188 bytes).

- Supports TTS packets (packet size: 192 bytes).

- Supports PS packets (packet size: specified by the size register).

- 8-bit parallel transfer or 1-bit serial transfer is selectable.

- Transfer direction is settable for each channel.

- Polarity of each clock signal, request signal, synchronizing signal, and data enable signal is selectable.

- A PCR clock recovery module (PCRRCV) incorporated

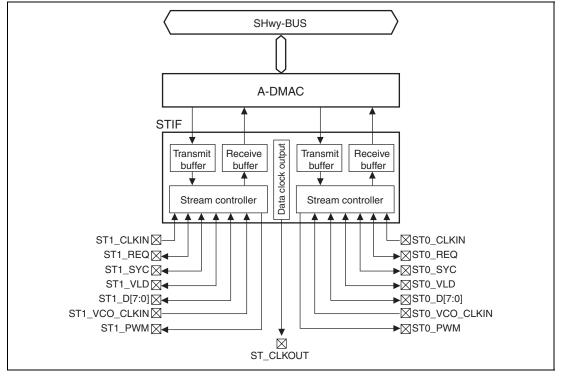

Figure 1.1 shows a block diagram of the STIF.

Figure 1.1 Block Diagram of STIF

## 1.2 Input/Output Pins

Table 1.1 shows the pin configuration of the STIF.

**Table 1.1** Pin Configuration

| Name          | I/O    | Function                                                                                   |

|---------------|--------|--------------------------------------------------------------------------------------------|

| ST_CLKOUT     | Output | Data clock output (common to channels)                                                     |

|               |        | This is defined by bits [15:12] in FRQCR2 of the CPG.                                      |

| ST0_CLKIN     | Input  | Data clock input                                                                           |

| ST0_REQ       | I/O    | Request signal                                                                             |

| ST0_SYC       | I/O    | Synchronizing signal                                                                       |

| ST0_VLD       | I/O    | Data enable                                                                                |

| ST0_D[7:0]    | I/O    | Data (ST0_D[0] is used in serial mode)                                                     |

| ST0_VCO_CLKIN | Input  | The MPEG base clock is input from the external 27-MHz voltage controlled oscillator (VCO). |

| ST0_PWM       | Output | The 27-MHz VCO is controlled through the low-pass filter (LPF).                            |

| ST1_CLKIN     | Input  | Data clock input                                                                           |

| ST1_REQ       | I/O    | Request signal                                                                             |

| ST1_SYC       | I/O    | Synchronizing signal                                                                       |

| ST1_VLD       | I/O    | Data enable                                                                                |

| ST1_D[7:0]    | I/O    | Data (ST1_D[0] is used in serial mode)                                                     |

| ST1_VCO_CLKIN | Input  | The MPEG base clock is input from the external 27-MHz VCO.                                 |

| ST1_PWM       | Output | The 27-MHz VCO is controlled through the LPF.                                              |

## 1.3 Register Descriptions

Table 1.2 (1) shows the register configurations. Table 1.2 (2) shows the register states in each processing mode.

**Table 1.2 (1) Register Configuration**

| Channel | Register Name                          | Abbreviation | Address     | Access<br>Size |

|---------|----------------------------------------|--------------|-------------|----------------|

| 0       | STIF mode select register              | STMDR_0      | H'FFEE 0000 | 32             |

|         | STIF control register                  | STCTLR_0     | H'FFEE 0004 | 32             |

|         | STIF internal counter control register | STCNTCR_0    | H'FFEE 0008 | 32             |

|         | STIF internal counter set register     | STCNTVR_0    | H'FFEE 000C | 32             |

|         | STIF status register                   | STSTR_0      | H'FFEE 0010 | 32             |

|         | STIF interrupt enable register         | STIER_0      | H'FFEE 0014 | 32             |

|         | STIF transfer size register            | STSIZER_0    | H'FFEE 0018 | 32             |

|         | STIFPWM mode register                  | STPWMMR_0    | H'FFEE 0020 | 32             |

|         | STIFPWM control register               | STPWMCR_0    | H'FFEE 0024 | 32             |

|         | STIFPWM register                       | STPWMR_0     | H'FFEE 0028 | 32             |

|         | STIFPCR0 register                      | STPCR0R_0    | H'FFEE 002C | 32             |

|         | STIFPCR1 register                      | STPCR1R_0    | H'FFEE 0030 | 32             |

|         | STIFSTC0 register                      | STSTC0R_0    | H'FFEE 0034 | 32             |

|         | STIFSTC1 register                      | STSTC1R_0    | H'FFEE 0038 | 32             |

|         | STIF lock control register             | STLKCR_0     | H'FFEE 003C | 32             |

|         | STIF debugging status register         | STDBGR_0     | H'FFEE 0060 | 32             |

| 1       | STIF mode select register              | STMDR_1      | H'FFEE8000  | 32             |

|         | STIF control register                  | STCTLR_1     | H'FFEE 8004 | 32             |

|         | STIF internal counter control register | STCNTCR_1    | H'FFEE 8008 | 32             |

|         | STIF internal counter set register     | STCNTVR_1    | H'FFEE 800C | 32             |

|         | STIF status register                   | STSTR_1      | H'FFEE 8010 | 32             |

|         | STIF interrupt enable register         | STIER_1      | H'FFEE 8014 | 32             |

|         | STIF transfer size register            | STSIZER_1    | H'FFEE 8018 | 32             |

|         | STIFPWM mode register                  | STPWMMR_1    | H'FFEE 8020 | 32             |

|         | STIFPWM control register               | STPWMCR_1    | H'FFEE 8024 | 32             |

|         | STIFPWM register                       | STPWMR_1     | H'FFEE 8028 | 32             |

|         | STIFPCR0 register                      | STPCR0R_1    | H'FFEE 802C | 32             |

| Channe | el Register Name               | Abbreviation | Address     | Access<br>Size |

|--------|--------------------------------|--------------|-------------|----------------|

| 1      | STIFPCR1 register              | STPCR1R_1    | H'FFEE 8030 | 32             |

|        | STIFSTC0 register              | STSTC0R_1    | H'FFEE 8034 | 32             |

|        | STIFSTC1 register              | STSTC1R_1    | H'FFEE 8038 | 32             |

|        | STIF lock control register     | STLKCR_1     | H'FFEE 803C | 32             |

|        | STIF debugging status register | STDBGR_1     | H'FFEE 8060 | 32             |

**Table 1.2 (2)** State of Registers in Each Operating Mode (Common to Each Channel)

| Abbr.   | Power-on<br>Reset | Manual<br>Reset | Sleep    | Software<br>Standby | Module<br>Standby | Deep<br>Standby |

|---------|-------------------|-----------------|----------|---------------------|-------------------|-----------------|

| STMDR   | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STCTLR  | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STCNTCR | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STCNTVR | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STSTR   | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STIER   | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STSIZER | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STPWMMR | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STPWMCR | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STPWMR  | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STPCR0R | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STPCR1R | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STSTC0R | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STSTC1R | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STLKCR  | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

| STDBGR  | Initialized       | Initialized     | Retained | Retained            | Retained          | Initialized     |

### 1.3.1 STIF Mode Select Register (STMDR)

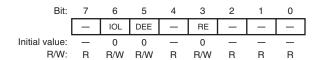

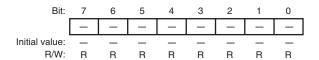

STMDR is a 32-bit register that selects operating mode, etc. of the on-chip STIF module. STMDR is initialized to H'00000000 by a power-on reset.

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                                                                  |

|----------|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------|

| 31 to 15 | _        | All 0            | R   | Reserved                                                                                                     |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                         |

| 14       | LSBSEL   | 0                | R/W | Selects MSB first or LSB first in serial mode.                                                               |

|          |          |                  |     | 0: MSB-first data input/output                                                                               |

|          |          |                  |     | 1: LSB-first data input/output                                                                               |

| 13       | EDGSEL   | 0                | R/W | Selects input/output timing of STn_REQ, STn_SYC, STn_VLD, and STn_D[7:0].                                    |

|          |          |                  |     | Output and sampled at the rising edge of the<br>synchronizing clock                                          |

|          |          |                  |     | Output and sampled at the falling edge of the<br>synchronizing clock                                         |

|          |          |                  |     | The synchronizing clock is defined by the CLKSEL bit in this register and bits [15:12] in FRQCR2 of the CPG. |

| 12       | CLKSEL   | 0                | R/W | Selects synchronizing clock for stream transmit mode                                                         |

|          |          |                  |     | 0: STn_SYC, STn_VLD, and STn_D[7:0] are output in synchronization with ST_CLKOUT.                            |

|          |          |                  |     | STn_REQ is sampled in synchronization with ST_CLKOUT                                                         |

|          |          |                  |     | 1: STn_SYC, STn_VLD, and STn_D[7:0] are output in synchronization with STn_CLKIN.                            |

|          |          |                  |     | STn_REQ is sampled in synchronization with STn_CLKIN.                                                        |

| 11 to 8  | _        | All 0            | R   | Reserved                                                                                                     |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                         |

| Bit | Bit Name  | Initial<br>Value | R/W | Description                                     |

|-----|-----------|------------------|-----|-------------------------------------------------|

| 7   | REQACTSEL | 0                | R/W | Selects the active polarity of STn_REQ.         |

|     |           |                  |     | 0: Active-high                                  |

|     |           |                  |     | 1: Active-low                                   |

| 6   | VLDACTSEL | 0                | R/W | Selects the active polarity of STn_VLD.         |

|     |           |                  |     | 0: Active-high                                  |

|     |           |                  |     | 1: Active-low                                   |

| 5   | SYCACTSEL | 0                | R/W | Selects the active polarity of STn_SYC.         |

|     |           |                  |     | 0: Active-high                                  |

|     |           |                  |     | 1: Active-low                                   |

| 4   | IOSEL     | 0                | R/W | Selects stream input or output direction.       |

|     |           |                  |     | 0: Input (from an external device to this LSI)  |

|     |           |                  |     | 1: Output (from this LSI to an external device) |

| 3   | IFMDSEL3  | 0                | R/W | These bits select operating mode.               |

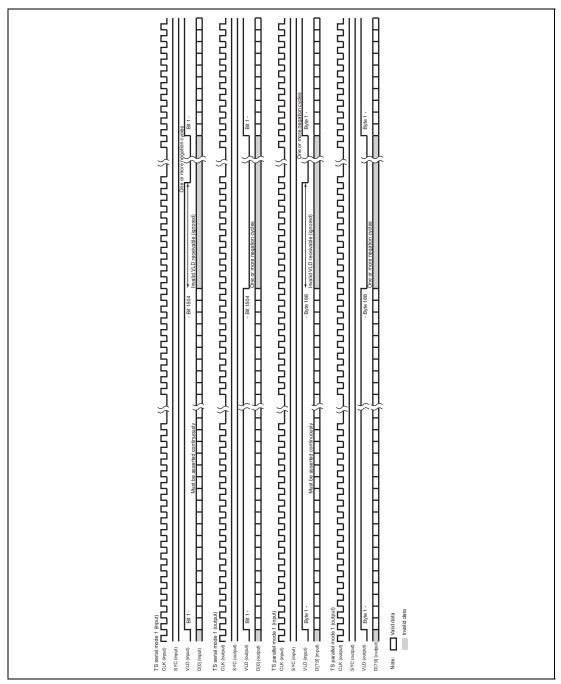

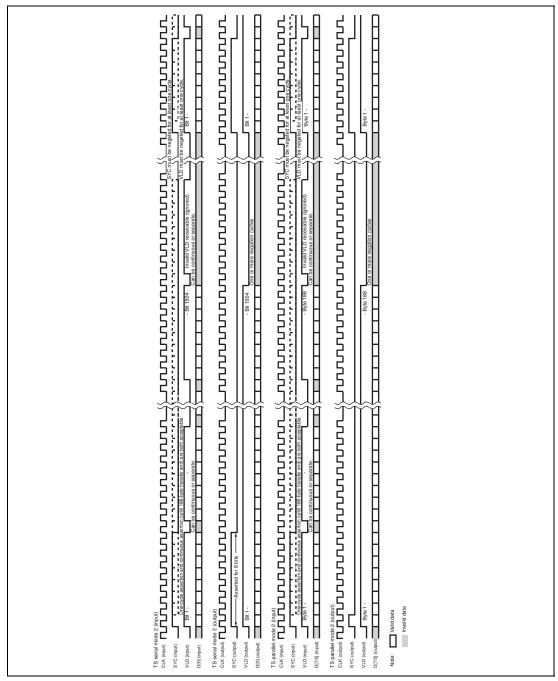

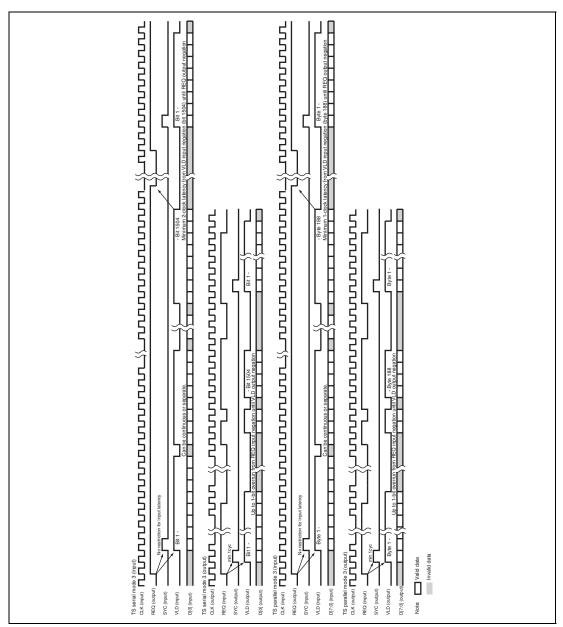

| 2   | IFMDSEL2  | 0                | R/W | 0000: TS serial mode 1                          |

| 1   | IFMDSEL1  | 0                | R/W | 0001: TS parallel mode 1                        |

| 0   | IFMDSEL0  | 0                | R/W | 0010: TS serial mode 2                          |

|     |           |                  |     | 0011: TS parallel mode 2                        |

|     |           |                  |     | 0100: TS serial mode 3                          |

|     |           |                  |     | 0101: TS parallel mode 3                        |

|     |           |                  |     | 0110: Reserved (setting prohibited)             |

|     |           |                  |     | 0111: Reserved (setting prohibited)             |

|     |           |                  |     | 1000: TTS serial mode                           |

|     |           |                  |     | 1001: TTS parallel mode                         |

|     |           |                  |     | 1010: Reserved (setting prohibited)             |

|     |           |                  |     | 1011: Reserved (setting prohibited)             |

|     |           |                  |     | 1100: PS serial mode                            |

|     |           |                  |     | 1101: PS parallel mode                          |

|     |           |                  |     | 1110: Reserved (setting prohibited)             |

|     |           |                  |     | 1111: Reserved (setting prohibited)             |

[Legend] n = 0, 1

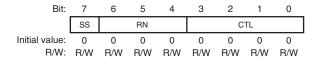

### 1.3.2 STIF Control Register (STCTLR)

STCTLR is a 32-bit register that sets the recovery processing switching threshold value and enables/disables DMA transfer requests. STCTLR is initialized to H'00000000 by a power-on reset.

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                        |

|----------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 12 | _        | All 0            | R   | Reserved                                                                                                                                                                                                                                                                                                                                           |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                               |

| 11       | RCVTM2   | 0                | R/W | These bits set the recovery processing switching threshold                                                                                                                                                                                                                                                                                         |

| 10       | RCVTM1   | 0                | R/W | value for packet output in TS mode 1 or TS mode 2. These bits are valid when RCV = 1.                                                                                                                                                                                                                                                              |

| 9        | RCVTM0   | 0                | R/W | 000: Approximately 0.625 seconds                                                                                                                                                                                                                                                                                                                   |

|          |          |                  |     | 001: Approximately 1.25 seconds                                                                                                                                                                                                                                                                                                                    |

|          |          |                  |     | 010: Approximately 2.5 seconds                                                                                                                                                                                                                                                                                                                     |

|          |          |                  |     | 011: Approximately 5 seconds                                                                                                                                                                                                                                                                                                                       |

|          |          |                  |     | 100: Approximately 10 seconds                                                                                                                                                                                                                                                                                                                      |

|          |          |                  |     | 101: Approximately 20 seconds                                                                                                                                                                                                                                                                                                                      |

|          |          |                  |     | 110: Approximately 40 seconds                                                                                                                                                                                                                                                                                                                      |

|          |          |                  |     | 111: Approximately 80 seconds                                                                                                                                                                                                                                                                                                                      |

|          |          |                  |     | The recovery functions are processed as follows:                                                                                                                                                                                                                                                                                                   |

|          |          |                  |     | Recovery function (1)                                                                                                                                                                                                                                                                                                                              |

|          |          |                  |     | When the internal counter value exceeds the timestamp value and the difference is smaller than the set threshold value, the packet is output immediately.                                                                                                                                                                                          |

|          |          |                  |     | Recovery function (2)                                                                                                                                                                                                                                                                                                                              |

|          |          |                  |     | When the internal counter value exceeds the timestamp value and the difference is larger than the set threshold value, the packet is discarded and the recovery processing restarts with the next packet. (The next packet is output immediately, and the packet's timestamp is reloaded to the internal counter for timestamp at the same time.)  |

|          |          |                  |     | Recovery function (3)                                                                                                                                                                                                                                                                                                                              |

|          |          |                  |     | When the internal counter value is under the timestamp value but the difference is larger than the set threshold value, the packet is discarded and the recovery processing restarts with the next packet. (The next packet is output immediately, and the packet's timestamp is reloaded to the internal counter for timestamp at the same time.) |

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                       |  |

|--------|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8      | RCV      | 0                | R/W | Enables the recovery functions when outputting packets in TS mode 1 or TS mode 2.                                                                                 |  |

|        |          |                  |     | 0: Recovery functions disabled                                                                                                                                    |  |

|        |          |                  |     | 1: Recovery functions enabled                                                                                                                                     |  |

| 7      | TRICK    | 0                | R/W | Enables the function that transfers stream independently of timestamp when outputting packets in TS mode 1 or TS mode 2.                                          |  |

|        |          |                  |     | 0: Transfer function disabled                                                                                                                                     |  |

|        |          |                  |     | 1: Transfer function enabled                                                                                                                                      |  |

| 6 to 3 | _        | All 0            | R   | Reserved                                                                                                                                                          |  |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                              |  |

| 2      | REQEN    | 0                | R/W | Enables or disables DMA transfer requests to the A-DMAC.                                                                                                          |  |

|        |          |                  |     | 0: Disabled                                                                                                                                                       |  |

|        |          |                  |     | 1: Enabled                                                                                                                                                        |  |

| 1      | EN       | 0                | R/W | Enables or disables stream input/output.                                                                                                                          |  |

|        |          |                  |     | 0: Disabled                                                                                                                                                       |  |

|        |          |                  |     | 1: Enabled                                                                                                                                                        |  |

| 0      | SRST     | 0                | R/W | Setting this bit to 1 causes the internal state of this module to be initialized with register settings retained.                                                 |  |

|        |          |                  |     | When a TS packet is received for the first time after the initialization, the timestamp value of the TS packet is reloaded to the internal counter for timestamp. |  |

|        |          |                  |     | While 1 is read from this bit, the initialization is in progress.                                                                                                 |  |

|        |          |                  |     | This bit is automatically cleared to 0.                                                                                                                           |  |

|        |          |                  |     | Whenever the STMDR setting is modified, be sure to set SRST to 1 to initialize this module and then set EN and REQEN to 1 to enable stream transfer.              |  |

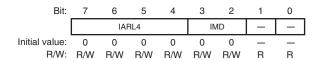

## 1.3.3 STIF Internal Counter Control Register (STCNTCR)

STCNTCR is a 32-bit register to control the internal counter for timestamp. STCNTCR is initialized to H'00000000 by a power-on reset.

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                                                          |  |

|---------|----------|------------------|-----|------------------------------------------------------------------------------------------------------|--|

| 31 to 4 | _        | All 0            | R   | Reserved                                                                                             |  |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0.                                 |  |

| 3       | CRD      | 0                | R/W | Setting this bit to 1 causes the internal counter value for timestamp to be read to STCNTVR.         |  |

|         |          |                  |     | This bit is automatically cleared to 0.                                                              |  |

| 2       | CSTP     | 0                | R/W | Stops the internal counter for timestamp.                                                            |  |

|         |          |                  |     | 0: Count operation is continued.                                                                     |  |

|         |          |                  |     | 1: Counter is stopped with its value retained.                                                       |  |

| 1       | CSET     | 0                | R/W | Setting this bit to 1 causes the STCNTVR value to be reloaded to the internal counter for timestamp. |  |

|         |          |                  |     | This bit is automatically cleared to 0.                                                              |  |

| 0       | CRST     | 0                | R/W | Setting this bit to 1 causes the internal counter for timestamp to be initialized to H'00000000.     |  |

|         |          |                  |     | This bit is automatically cleared to 0.                                                              |  |

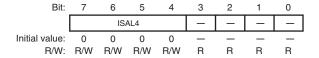

#### 1.3.4 STIF Internal Counter Set Register (STCNTVR)

STCNTVR is a 32-bit register that reads or reloads the value of the internal counter for timestamp in combination with the settings of the CRD and CSET bits in STCNTCR. STCNTVR is initialized to H'000000000 by a power-on reset.

| Bit     | Bit Name         | Initial<br>Value | R/W | Description                          |

|---------|------------------|------------------|-----|--------------------------------------|

| 31 to 0 | VLU31 to<br>VLU0 | All 0            | R/W | Internal counter value for timestamp |

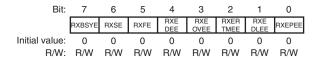

#### 1.3.5 STIF Status Register (STSTR)

STSTR is a 32-bit register that indicates the status of the recovery functions, packet transmission/reception, and PCR clock recovery. STSTR is initialized to H'00000000 by a power-on reset.

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                  |

|----------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 13 | _        | All 0            | R   | Reserved                                                                                                                                     |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                         |

| 12       | LKZF     | 0                | R/W | Indicates whether the PLL error amount (internal STC - internal PCR) falls within threshold value range LKCYC when a PCR packet is received. |

|          |          |                  |     | 0: Within threshold value range (PLL error amount (internal STC - internal PCR) =< LKCYC)                                                    |

|          |          |                  |     | 1: Outside threshold value range (PLL error amount (internal STC - internal PCR) > LKCYC)                                                    |

|          |          |                  |     | This bit is cleared to 0 by writing 1.                                                                                                       |

| Bit | Bit Name                                       | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                            |  |

|-----|------------------------------------------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 11  | LKF                                            | 0                | R/W | Indicates PLL lock status.                                                                                                                                                                                                                                                                                                                             |  |

|     |                                                |                  |     | 0: PLL unlocked                                                                                                                                                                                                                                                                                                                                        |  |

|     |                                                |                  |     | In the case of ULCNT >= ULREF due to continued LKZI<br>= 1 state (outside threshold value range) when a PCR<br>packet is received with PLL locked (LKF = 1)                                                                                                                                                                                            |  |

|     |                                                |                  |     | 1: PLL locked                                                                                                                                                                                                                                                                                                                                          |  |

|     |                                                |                  |     | In the case of LKCNT >= LKREF due to continued LKZF = 0 state (within threshold value range) when a PCR packet is received with PLL unlocked (LKF = 0)                                                                                                                                                                                                 |  |

|     |                                                |                  |     | This bit is cleared to 0 by writing 1.                                                                                                                                                                                                                                                                                                                 |  |

| 10  | DISF                                           | 0                | R/W | Status flag bit that indicates the discontinuity_indicator (table 1.6) of received PCR_PID. This bit is set to 1 upon completion of transfer (internal PCR $\rightarrow$ STC $\rightarrow$ internal STC).                                                                                                                                              |  |

|     |                                                |                  |     | This bit is cleared to 0 by writing 1.                                                                                                                                                                                                                                                                                                                 |  |

| 9   | regist<br>to inte<br>of the<br>(interr<br>comp |                  | R/W | This bit is set to 1 when data transfer from internal PCR register to STC counter and data transfer from STC counter to internal STC register are completed and the comparison of the upper data of received PCR_PID does not match (internal STC - internal PCR exceeded the acceptable comparison result range specified by PWMCYC; see figure 1.9). |  |

|     |                                                |                  |     | This bit is also set to 1 when PCR_PID (table 1.6) is received after "discont."                                                                                                                                                                                                                                                                        |  |

|     |                                                |                  |     | Furthermore, if the PWM control variable with a bit width of the effective comparison bit count "n" specified by PWMCYC is -(2^n), this bit is set to 1 as invalid PWM control variable (ILGL = 1 hereinafter) in the same manner as above.                                                                                                            |  |

|     |                                                |                  |     | This bit is cleared to 0 by writing 1.                                                                                                                                                                                                                                                                                                                 |  |

| 8   | PCRF                                           | 0                | R/W | This bit is set to 1 when data transfer from internal PCR register to STC counter and data transfer from STC counter to internal STC register are completed.                                                                                                                                                                                           |  |

|     |                                                |                  |     | These transfers take place when a packet whose PCR_PID was detected satisfies the conditions in table 1.5.                                                                                                                                                                                                                                             |  |

|     |                                                |                  |     | This bit is cleared to 0 by writing 1.                                                                                                                                                                                                                                                                                                                 |  |

|     |          | Initial |     |                                                                                                                                                      |  |

|-----|----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit | Bit Name | Value   | R/W | Description                                                                                                                                          |  |

| 7   | TENDF    | 0       | R/W | Indicates completion of output packet transfer for the transfer data size specified by STSIZER in PS mode.                                           |  |

|     |          |         |     | This bit is cleared to 0 by writing 1.                                                                                                               |  |

| 6   | RENDF    | 0       | R/W | Indicates completion of input packet transfer for the transfer data size specified by STSIZER in PS mode.                                            |  |

|     |          |         |     | This bit is cleared to 0 by writing 1.                                                                                                               |  |

| 5   | RCVF3    | 0       | R/W | This bit is set to 1 when recovery function (3) is activated when outputting a packet in TS mode 1 or TS mode 2.                                     |  |

|     |          |         |     | This bit is cleared to 0 by writing 1.                                                                                                               |  |

| 4   | RCVF2    | 0       | R/W | This bit is set to 1 when recovery function (2) is activated when outputting a packet in TS mode 1 or TS mode 2.                                     |  |

|     |          |         |     | This bit is cleared to 0 by writing 1.                                                                                                               |  |

| 3   | RCVF1    | 0       | R/W | This bit is set to 1 when recovery function (1) is activated when outputting a packet in TS mode 1 or TS mode 2.                                     |  |

|     |          |         |     | This bit is cleared to 0 by writing 1.                                                                                                               |  |

| 2   | UPF      | 0       | R/W | This bit is set to 1 when a packet shorter than 188 bytes is received in TS mode 1 or TS mode 2. Such packets are discarded.                         |  |

|     |          |         |     | This bit is cleared to 0 by writing 1.                                                                                                               |  |

| 1   | OPF      | 0       | R/W |                                                                                                                                                      |  |

|     |          |         |     | This bit is cleared to 0 by writing 1.                                                                                                               |  |

| 0   | ŌVF      | 0       | R/W | This bit is set to 1 when data read by the A-DMAC is delayed and therefore the receive data which came later is discarded in TS mode 1 or TS mode 2. |  |

|     |          |         |     | This bit is cleared to 0 by writing 1.                                                                                                               |  |

|     |          |         |     |                                                                                                                                                      |  |

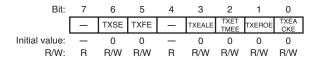

## 1.3.6 STIF Interrupt Enable Register (STIER)

STIER is a 32-bit register to control various interrupt requests. STIER is initialized to H'00000000 by a power-on reset.

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                          |  |

|----------|----------|------------------|-----|----------------------------------------------------------------------|--|

| 31 to 13 | _        | All 0            | R   | Reserved                                                             |  |

| 011010   |          | 7111 0           |     | These bits are always read as 0. The write value should always be 0. |  |

| 12       | LKZE     | 0                | R/W | Enables or disables LKZF interrupt requests.                         |  |

|          |          |                  |     | 0: LKZF interrupt requests are disabled.                             |  |

|          |          |                  |     | 1: LKZF interrupt requests are enabled.                              |  |

| 11       | LKE      | 0                | R/W | Enables or disables LKF interrupt requests.                          |  |

|          |          |                  |     | 0: LKF interrupt requests are disabled.                              |  |

|          |          |                  |     | 1: LKF interrupt requests are enabled.                               |  |

| 10       | DISE     | 0                | R/W | Enables or disables DISF interrupt requests.                         |  |

|          |          |                  |     | 0: DISF interrupt requests are disabled.                             |  |

|          |          |                  |     | 1: DISF interrupt requests are enabled.                              |  |

| 9        | UNZE     | 0                | R/W | Enables or disables UNZF interrupt requests.                         |  |

|          |          |                  |     | 0: UNZF interrupt requests are disabled.                             |  |

|          |          |                  |     | 1: UNZF interrupt requests are enabled.                              |  |

| 8        | PCRE     | 0                | R/W | Enables or disables PCRF interrupt requests.                         |  |

|          |          |                  |     | 0: PCRF interrupt requests are disabled.                             |  |

|          |          |                  |     | 1: PCRF interrupt requests are enabled.                              |  |

| 7        | TENDE    | 0                | R/W | Enables or disables TENDF interrupt requests.                        |  |

|          |          |                  |     | 0: TENDF interrupt requests are disabled.                            |  |

|          |          |                  |     | 1: TENDF interrupt requests are enabled.                             |  |

| 6        | RENDE    | 0                | R/W | Enables or disables RENDF interrupt requests.                        |  |

|          |          |                  |     | 0: RENDF interrupt requests are disabled.                            |  |

|          |          |                  |     | 1: RENDF interrupt requests are enabled.                             |  |

| 5        | RCVE3    | 0                | R/W | Enables or disables RCVF3 interrupt requests.                        |  |

|          |          |                  |     | 0: RCVF3 interrupt requests are disabled.                            |  |

|          |          |                  |     | 1: RCVF3 interrupt requests are enabled.                             |  |

| D:4 | Dit Name | Initial | DAM                                             | Description                                   |

|-----|----------|---------|-------------------------------------------------|-----------------------------------------------|

| Bit | Bit Name | Value   | R/W                                             | Description                                   |

| 4   | RCVE2    | 0       | R/W                                             | Enables or disables RCVF2 interrupt requests. |

|     |          |         |                                                 | 0: RCVF2 interrupt requests are disabled.     |

|     |          |         |                                                 | 1: RCVF2 interrupt requests are enabled.      |

| 3   | RCVE1    | 0       | R/W                                             | Enables or disables RCVF1 interrupt requests. |

|     |          |         |                                                 | 0: RCVF1 interrupt requests are disabled.     |

|     |          |         |                                                 | 1: RCVF1 interrupt requests are enabled.      |

| 2   | UPE      | 0       | R/W Enables or disables UPF interrupt requests. |                                               |

|     |          |         |                                                 | 0: UPF interrupt requests are disabled.       |

|     |          |         |                                                 | 1: UPF interrupt requests are enabled.        |

| 1   | OPE      | 0       | R/W Enables or disables OPF interrupt requests. |                                               |

|     |          |         |                                                 | 0: OPF interrupt requests are disabled.       |

|     |          |         |                                                 | 1: OPF interrupt requests are enabled.        |

| 0   | OVE      | 0       | R/W                                             | Enables or disables OVF interrupt requests.   |

|     |          |         |                                                 | 0: OVF interrupt requests are disabled.       |

|     |          |         |                                                 | 1: OVF interrupt requests are enabled.        |

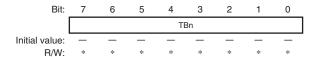

## 1.3.7 STIF Transfer Size Register (STSIZER) (n = 0,1)

STSIZER is a 32-bit register that specifies a transfer byte count for PS mode. STSIZER is initialized to H'FFFFFFF by a power-on reset.

| Bit     | Bit Name           | Initial<br>Value | R/W | Description                     |

|---------|--------------------|------------------|-----|---------------------------------|

| 31 to 0 | SIZE31 to<br>SIZE0 | All 1            | R/W | Transfer byte count for PS mode |

### 1.3.8 STIFPWM Mode Register (STPWMMR)

STPWMMR is a 32-bit register that selects PWM mode, sets PWM control cycle, reference bit shift amount, and reference clock, enables/disables PID filtering, and sets the PID of a PCR packet to be filtered. STPWMMR is initialized to H'000000000 by a power-on reset.

|          |                  | Initial |     |                                                                                                                                                                                                                                                                                                                                                        |  |

|----------|------------------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit      | Bit Name         | Value   | R/W | Description                                                                                                                                                                                                                                                                                                                                            |  |

| 31 to 29 | _                | All 0   | R   | Reserved                                                                                                                                                                                                                                                                                                                                               |  |

|          |                  |         |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                                   |  |

| 28 to 16 | PID12 to<br>PID0 | All 0   | R/W | These bits set the PID (PCR_PID) of filtering target PCR packet.                                                                                                                                                                                                                                                                                       |  |

| 15       | PIDEN            | 0       | R/W | Enables or disables PCR packet filtering.                                                                                                                                                                                                                                                                                                              |  |

|          |                  |         |     | 0: Filtering is disabled.                                                                                                                                                                                                                                                                                                                              |  |

|          |                  |         |     | 1: Filtering is enabled.                                                                                                                                                                                                                                                                                                                               |  |

| 14       | PWMUEN           | 0       | R/W | Selects whether to reflect the PWM control difference (internal STC register - internal PCR register) in the PWM control output according to the comparison of the residual upper bits (comparison target bits) in the comparison of bits 0 to 11. The comparison result of target bits is reflected in UNZF. This bit is valid only when PWMSEL is 0. |  |

|          |                  |         |     | 0: When the comparison results in a mismatch, PWM control variable is reflected in PWM control.                                                                                                                                                                                                                                                        |  |

|          |                  |         |     | [Match: UNZF = 0] PWM control variable is reflected in PWM output control.                                                                                                                                                                                                                                                                             |  |

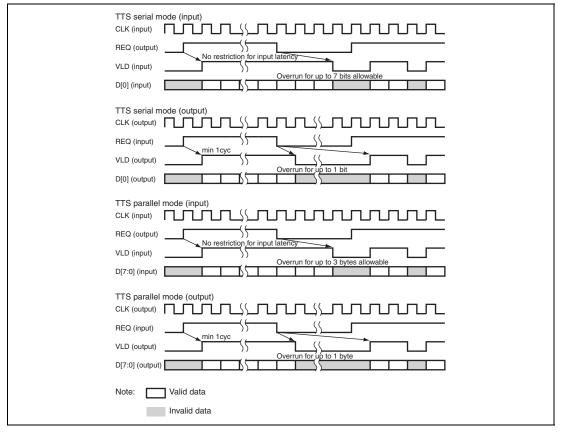

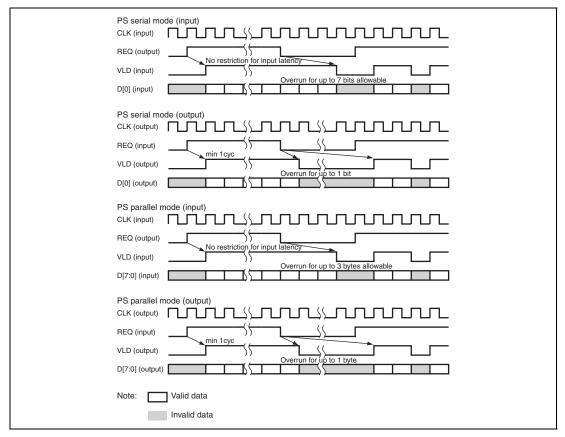

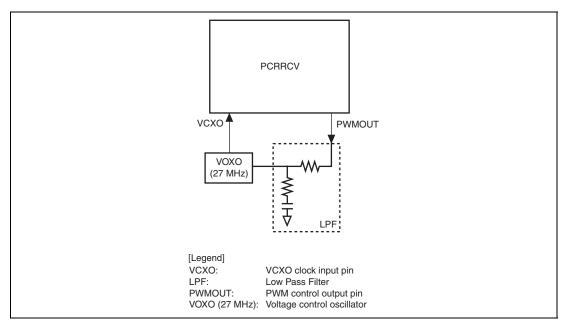

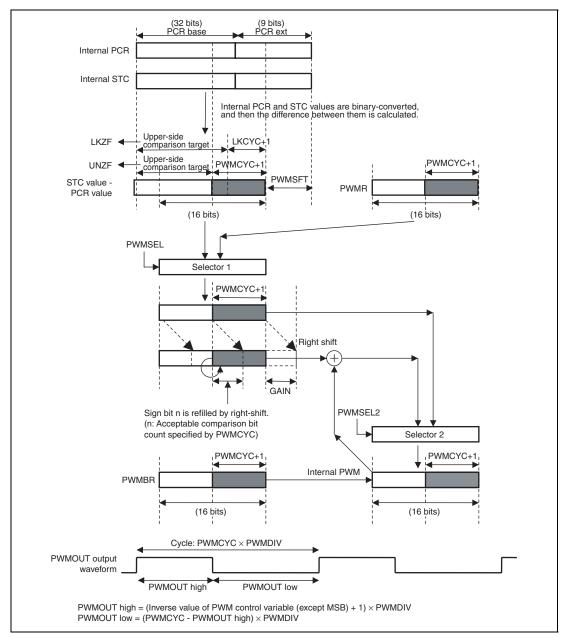

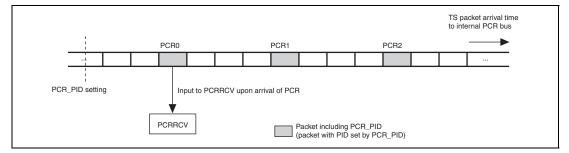

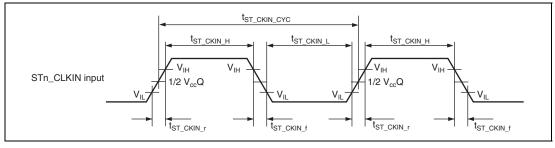

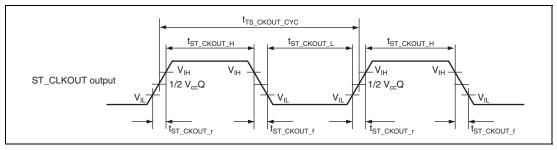

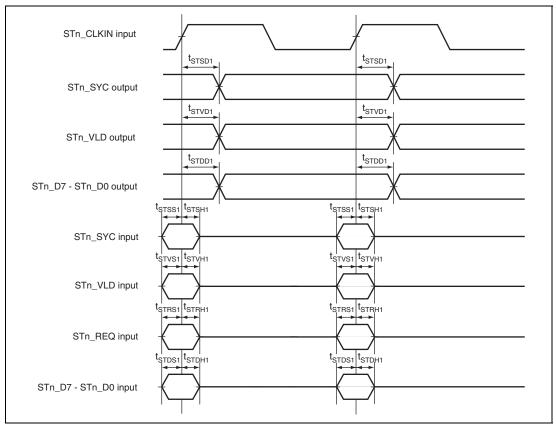

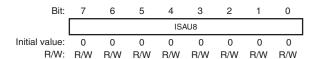

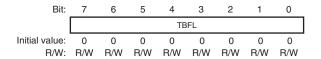

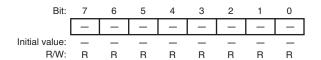

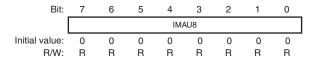

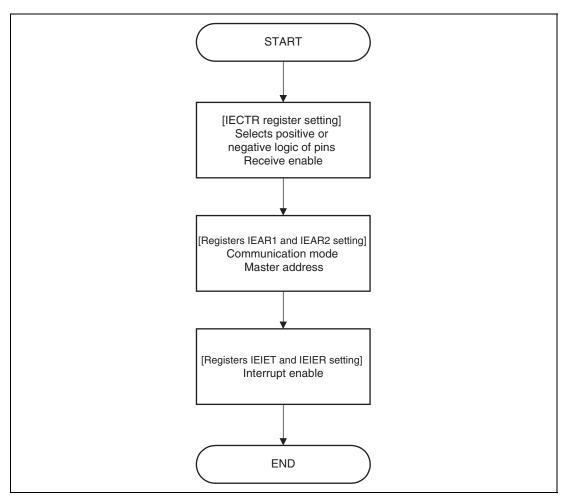

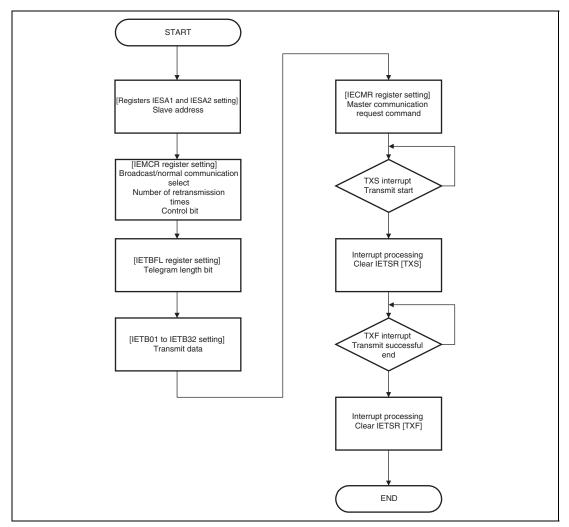

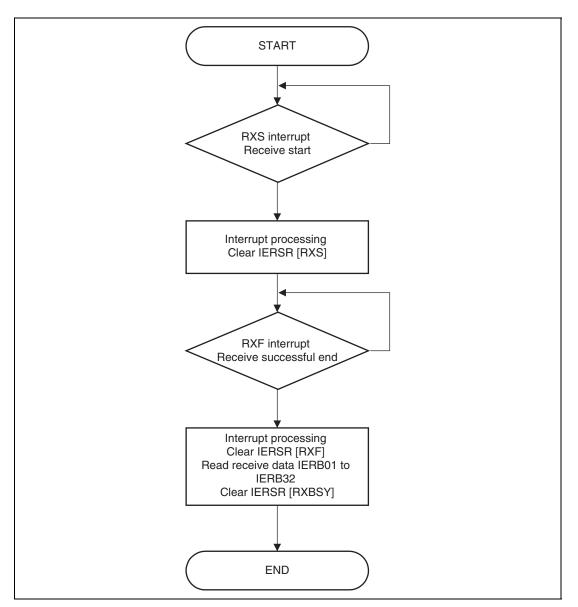

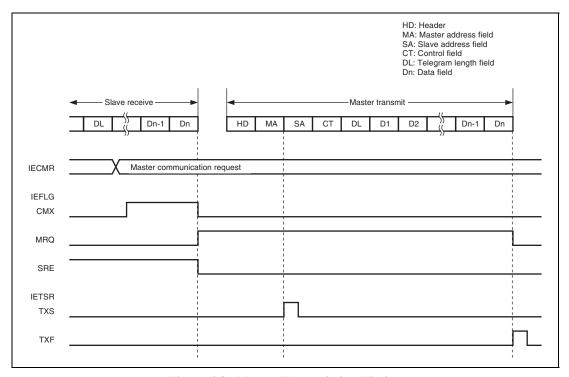

|          |                  |         |     | [Mismatch: UNZF = 1] PWM control variable is reflected in PWM output control.                                                                                                                                                                                                                                                                          |  |