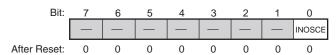

# SH7455 Group, SH7456 Group

User's Manual: Hardware

Renesas 32-Bit RISC Microcomputer SuperH<sup>TM</sup> RISC engine Family

SH74552 R5F74552KBG SH74562 R5F74562KBG

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

# 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

— The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions may occur due to the false recognition of the pin state as an input signal. Unused pins should be handled as described under Handling of Unused Pins in the manual.

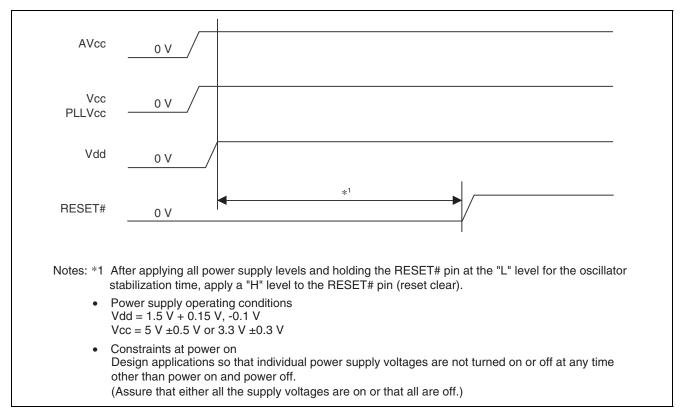

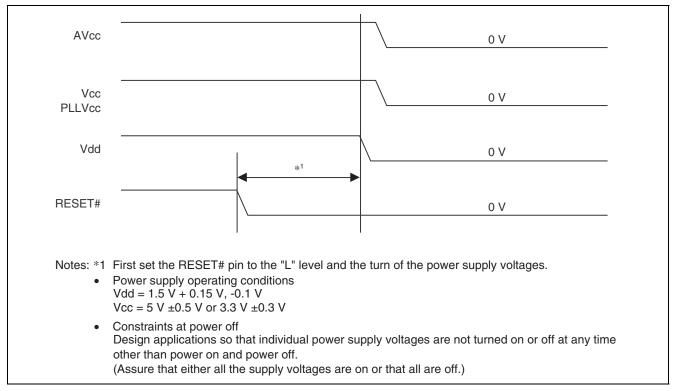

## 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

- In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

- In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

- 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

## 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to one with a different type number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different type numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different type numbers, implement a system-evaluation test for each of the products.

This page is blank for reasons of layout.

|          | Revision History |                                | SH7455 Group, SH7456 Group User's Manual: Hardware |

|----------|------------------|--------------------------------|----------------------------------------------------|

| Rev.     | Date             | Page of<br>Previous<br>Edition | Description                                        |

| Rev.1.10 | Sep. 22, 2011    | _                              | First edition issued.                              |

This page is blank for reasons of layout.

# How to Use This Manual

# 1. Purpose and Target Readers

This manual is designed to provide the user with an understanding of the hardware functions and electrical characteristics of the MCU. It is intended for users designing application systems incorporating the MCU. A basic understanding of electrical circuits, logic circuits, and microcontrollers is required to use this manual.

This manual includes an overview of the product; descriptions of the CPU, system control functions, peripheral functions, and the electrical characteristics; and usage notes.

Particular attention must be paid to the precautionary notes included in this manual. These notes appear in the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the main places that have been revised and added since the first edition. It does not list all revisions. Refer to the text of the manual for details.

Renesas provides the following documents for the SH7455 Group and SH7456 Group. Be sure to refer to the latest versions of these documents. The most recent versions of these documents can be obtained from the Renesas Electronics web site.

| Document Type              | Description                                                                                                                                                          | Document Title                                           | Document No.       |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------|

| Datasheet                  | Hardware overview and electrical characteristics                                                                                                                     | _                                                        | _                  |

| User's manual for hardware | Hardware specifications (pin assignments, memory maps, peripheral function specifications, electrical characteristics, and timing charts) and operation descriptions | SH7455 Group,<br>SH7456 Group<br>User's Manual: Hardware | This user's manual |

| User's manual for software | Descriptions of the CPU and instruction set                                                                                                                          | SH-4A Extended Function<br>Software Manual               | REJ09B0224         |

| Application note           | Sample application programs and other materials                                                                                                                      | _                                                        |                    |

| Renesas technical update   | Product specifications, the latest updates on documents, and other information                                                                                       | -                                                        |                    |

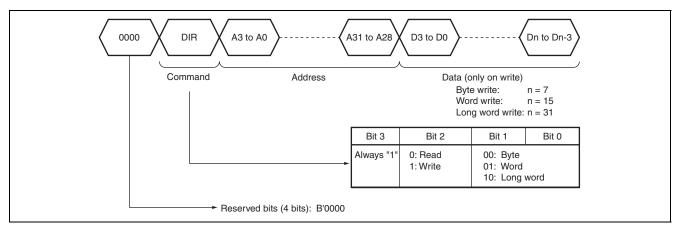

# 2. Notation of Numbers and Symbols

The notational conventions for register names, bit names, numbers, and symbols used in this manual are described below.

# (1) Register Names, Bit Names, and Pin Names

Registers, bits, and pins are referred to in the text by symbols. These symbols are followed by the word "register", "bit", or "pin" to distinguish the three categories.

Examples: the CS# pin, the Vcc pin,

the ICR0 register

# (2) Notation of Numbers

Binary numbers are notated as B'nnnn (However, the "B" may be omitted when it is clear that the number is binary), hexadecimal numbers are notated as H'nnnn, and decimal numbers are notated as nnnn.

Examples - Binary: B'11 or 11

Hexadecimal: H'EFA0

Decimal: 1234

# (3) Notation for "L" Active (Active-Low) Signals

A sharp sign (#) is appended to the names of signals and pins which are "L" active.

Example: the CS0# pin

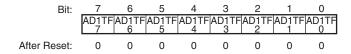

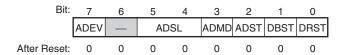

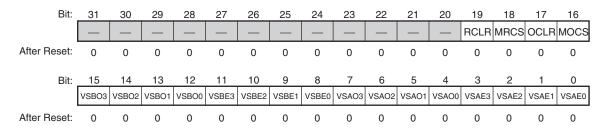

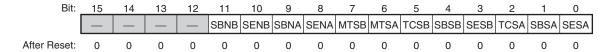

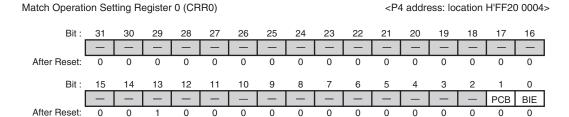

# 3. Register Configuration

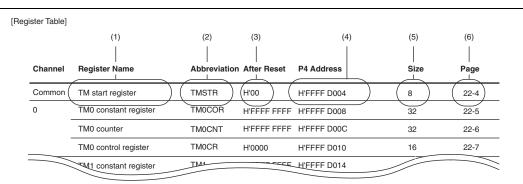

Each section in this manual provides a table listing all the registers used by the corresponding module before the register descriptions in the section. The symbols and terms used in these tables are described below.

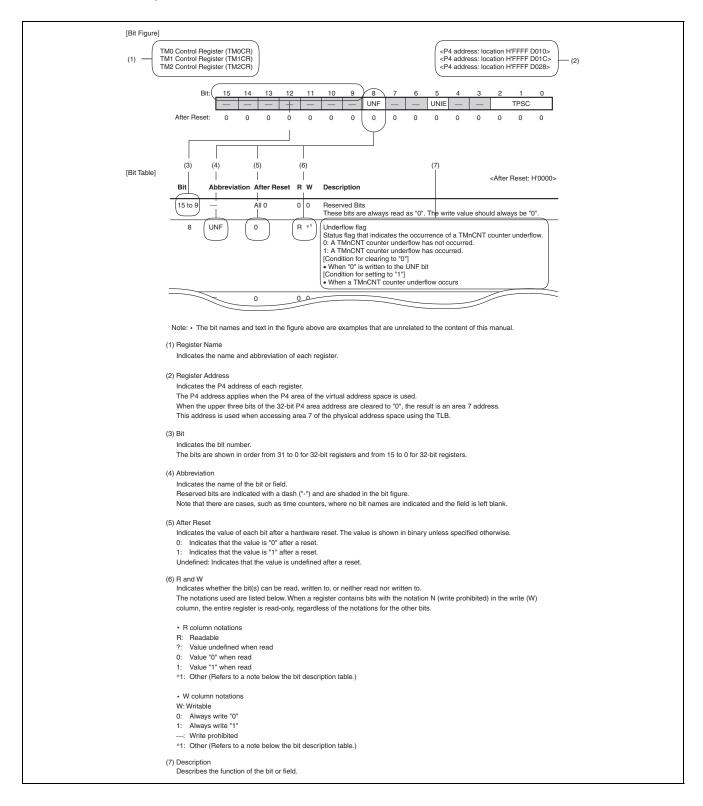

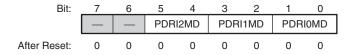

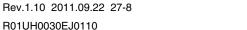

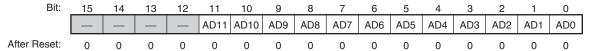

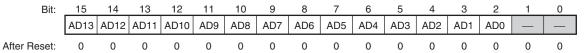

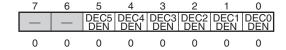

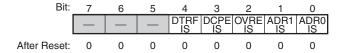

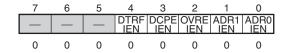

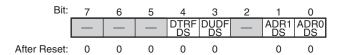

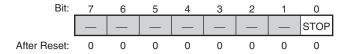

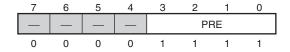

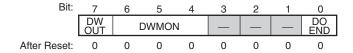

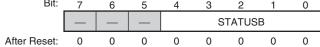

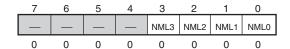

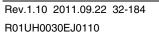

Note: • The bit names and text in the figure above are examples that are unrelated to the content of this manual.

#### (1) Register Name

The register name are shown for each register.

#### (2) Abbreviation

Gives the name of the register.

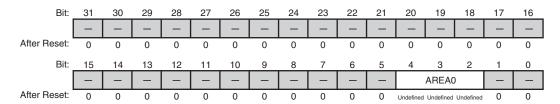

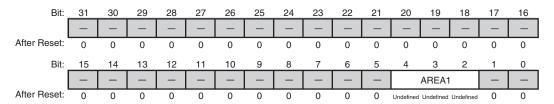

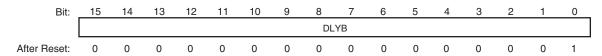

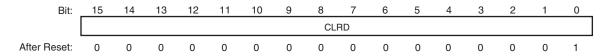

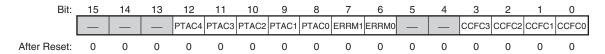

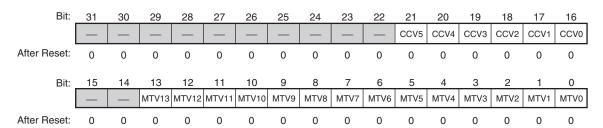

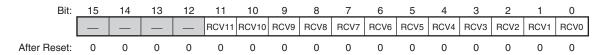

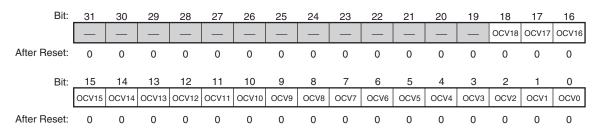

#### (3) After Reset

Indicates the values of each bit after a hardware reset in hexadecimal.

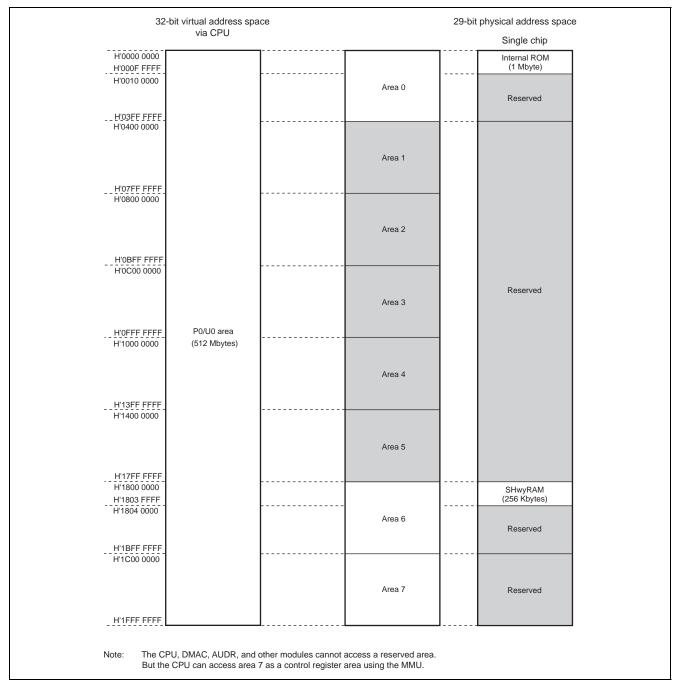

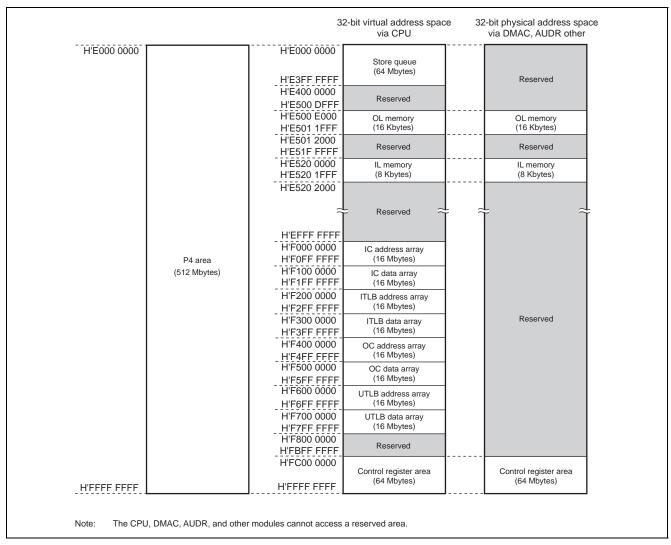

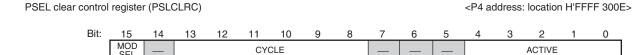

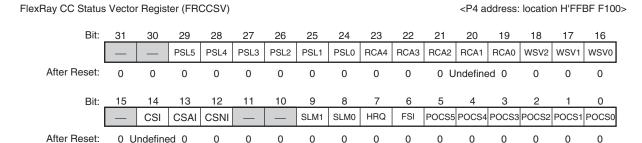

## (4) P4 Address

Indicates the P4 address of each register.

The P4 address applies when the P4 area of the virtual address space is used. When the upper three bits of the 32-bit P4 area address are cleared to "0", the result is an area 7 address. This address is used when accessing area 7 of the physical address space using the TLB.

# (5) Access Size

8-bit access is indicated as "8", 16-bit access as "16", and 32-bit access as "32", respectively.

For registers that allow multiple accesses, each access size is indicated with a slash (/).

If an access size is indicated without a slash (/), only the indicated size is allowed.

- For 32-bit registers that can be accessed using 32-bit and 16-bit accesses The access size is indicated as "16/32".

- For 8-bit registers that can be accessed using 8-bit access, and also using 16-bit access at the same time with the next aligned 8-bit register

The access size is indicated as "8/16".

# (6) Page

Indicates the page on which the functions and bit settings of the register are described. If the description runs to multiple pages, only the first page is indicated. For example, if the description starts on page 12-9 and continues to page 12-10, page 12-9 is indicated.

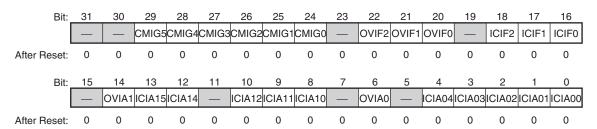

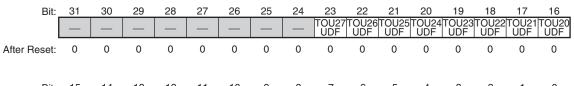

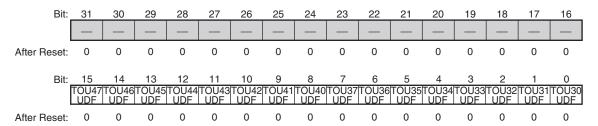

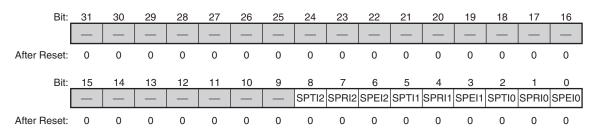

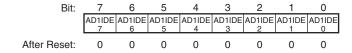

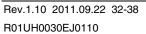

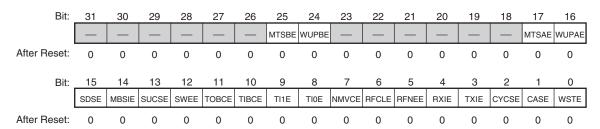

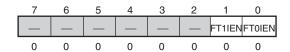

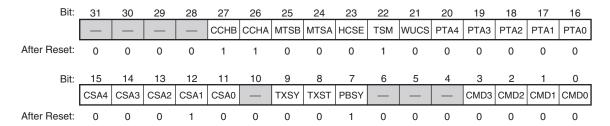

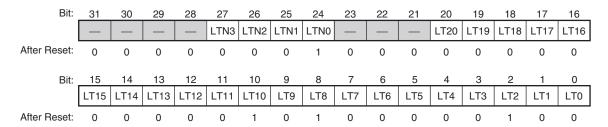

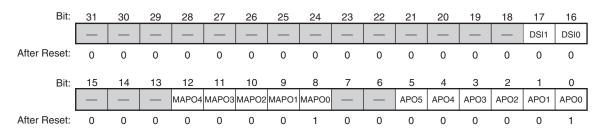

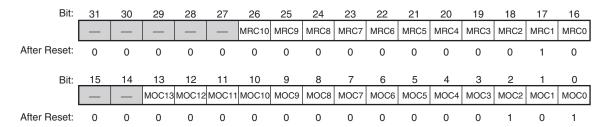

# 4. Register Notation

Each register description includes both a bit figure that shows the bit sequence and a bit table that describes the content set with each bit. The symbols and terms used are described below.

# 5. Abbreviations and Symbols

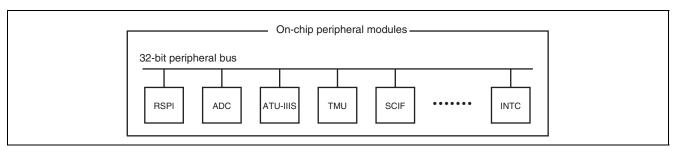

The table below describes the abbreviations and symbols used in this document.

| Abbreviation | Full Name                           |

|--------------|-------------------------------------|

| FPU          | Floating-Point Unit                 |

| MMU          | Memory Management Unit              |

| SHwyRAM      | Super Hyway RAM                     |

| CPG          | Clock Pulse Generator               |

| INTC         | Interrupt Controller                |

| WDT          | Watchdog Timer                      |

| BSC          | Bus State Controller                |

| DMAC         | Direct Memory Access Controller     |

| ATU-IIIS     | Advanced Timer Unit IIIS            |

| TMU          | Timer Unit                          |

| SCIF         | Serial Communication Interface      |

| RSPI         | Renesas Serial Peripheral Interface |

| IIC3         | I2C Bus Interface 3                 |

| CAN          | Controller Area Network             |

| ADC          | A/D Converter                       |

| DRI          | Direct RAM Input Interface          |

| DRO          | Direct RAM Output Interface         |

| PDAC         | Parallel DAC Controller             |

| PSEL         | Parallel Selector                   |

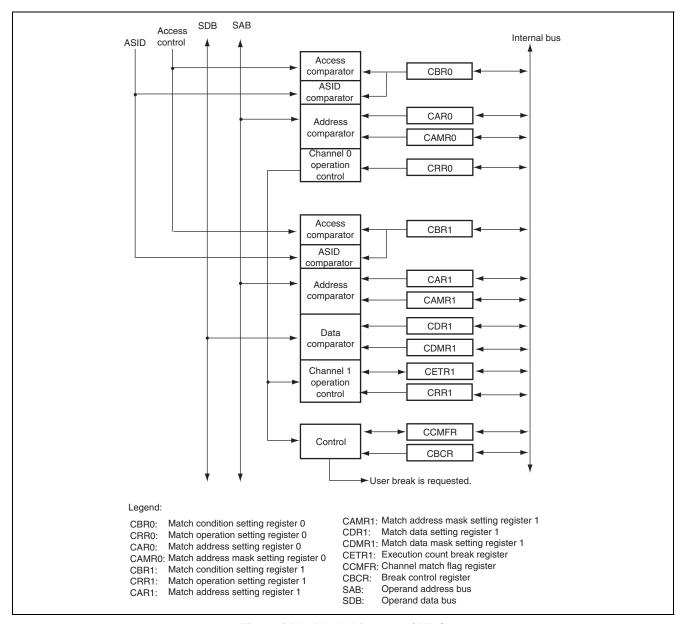

| UBC          | User Break Controller               |

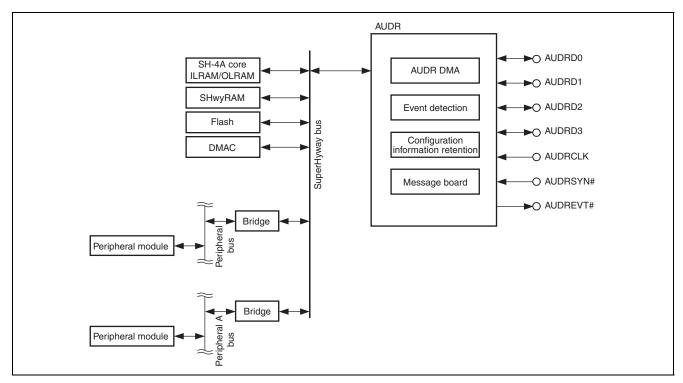

| AUDR         | AUD RAM Monitor                     |

| H-UDI        | User Debugging Interface            |

# **6.** Trademarks and Registered Trademarks

All trademarks and registered trademarks are the property of their respective owners.

# Contents

| Sect | tion 1 Overview                                                   | 1-1             |

|------|-------------------------------------------------------------------|-----------------|

| 1.1  | Features                                                          | 1-1             |

|      | 1.1.1 Applications                                                | 1-1             |

|      | 1.1.2 Specifications Overview                                     | 1-2             |

| 1.2  | Product Line Overview                                             | 1-7             |

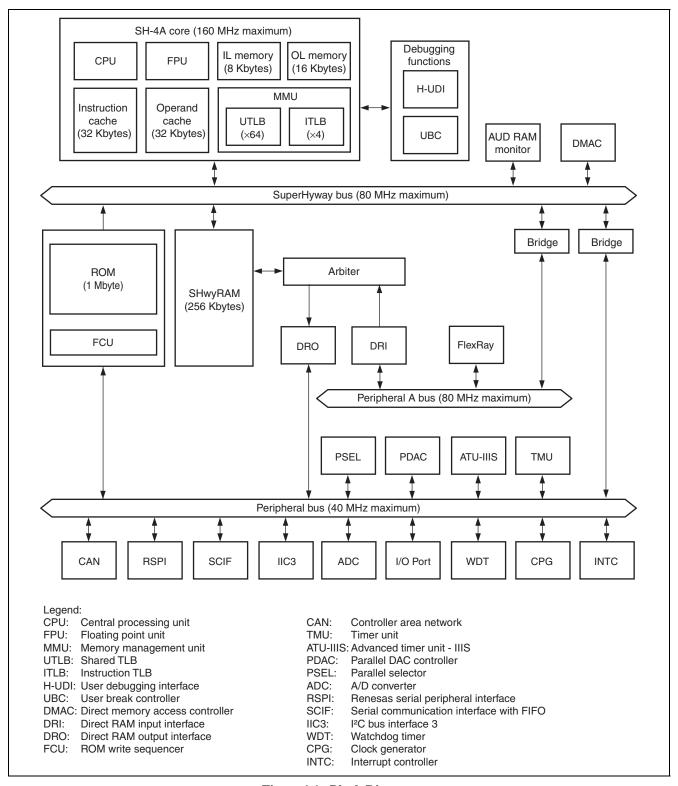

| 1.3  | Block Diagram                                                     |                 |

| 1.4  | Pin Arrangement                                                   | 1-9             |

| 1.5  | Pin Functions                                                     | 1-10            |

| 1.6  | Descriptions of Pin Functions                                     | 1-17            |

| Sect | tion 2 Programming Model                                          | 2-1             |

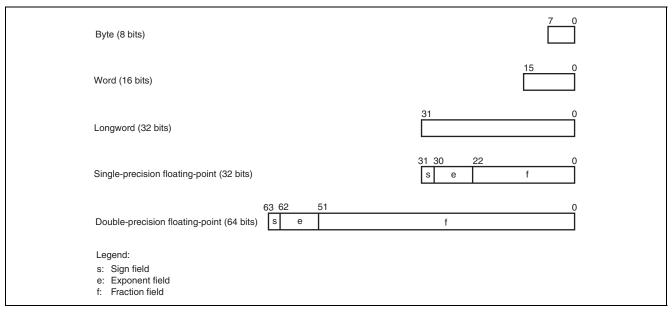

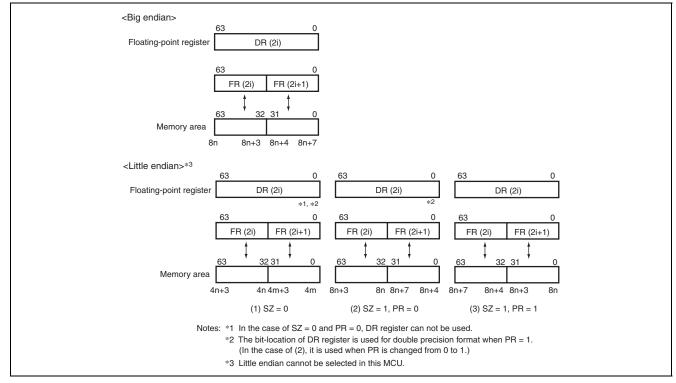

| 2.1  | Data Formats                                                      | 2-1             |

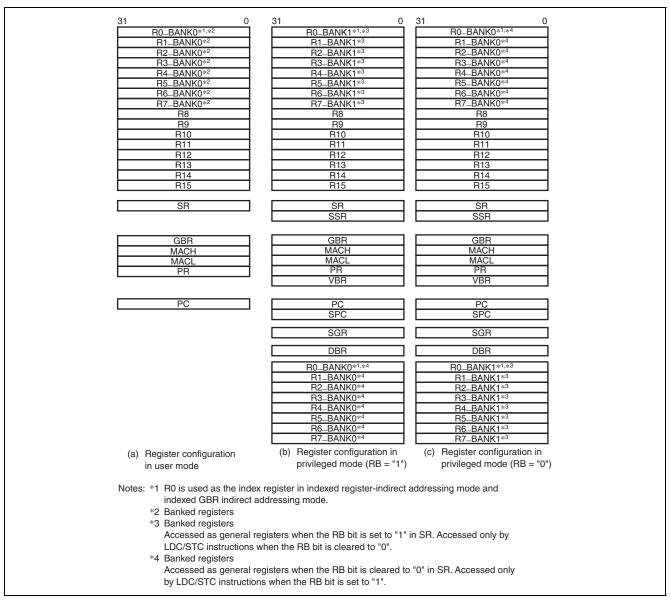

| 2.2  | Register Descriptions                                             | 2-2             |

|      | 2.2.1 Privileged Mode and Banks                                   | 2-2             |

|      | 2.2.2 General Registers                                           | 2-5             |

|      | 2.2.3 Floating-Point Registers                                    | 2- <del>6</del> |

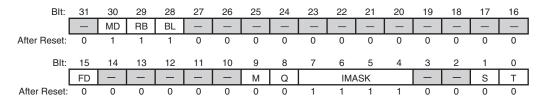

|      | 2.2.4 Control Registers                                           | 2-8             |

|      | 2.2.5 System Registers                                            | 2-10            |

| 2.3  | Memory-Mapped Registers                                           |                 |

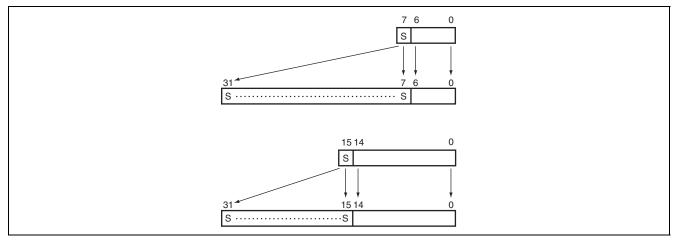

| 2.4  | Data Formats in Registers                                         |                 |

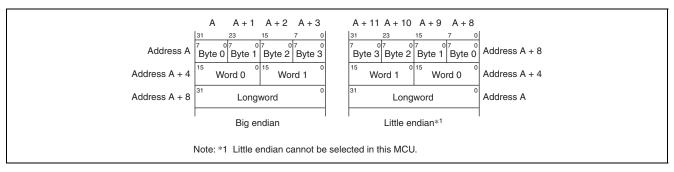

| 2.5  | Data Formats in Memory                                            | 2-13            |

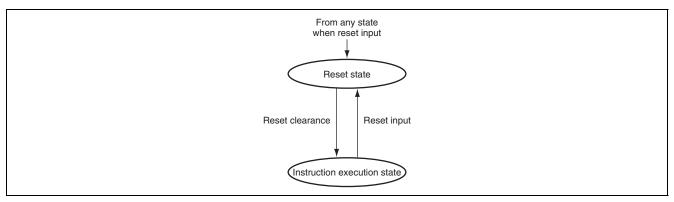

| 2.6  | Processing States                                                 |                 |

| 2.7  | Usage Notes                                                       | 2-15            |

|      | 2.7.1 Notes on Self-Modifying Code                                | 2-15            |

| Sect | tion 3 Instruction Set                                            | 3-1             |

| 3.1  | Execution Environment                                             | 3-1             |

| 3.2  | Addressing Modes                                                  | 3-3             |

| 3.3  | Instruction Set                                                   | 3-6             |

| 3.4  | Usage Notes                                                       | 3-17            |

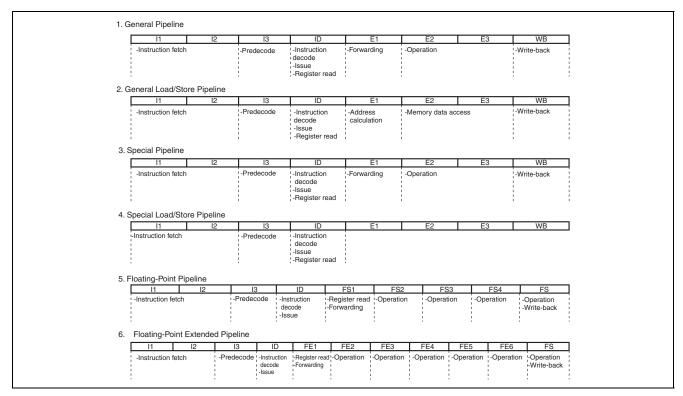

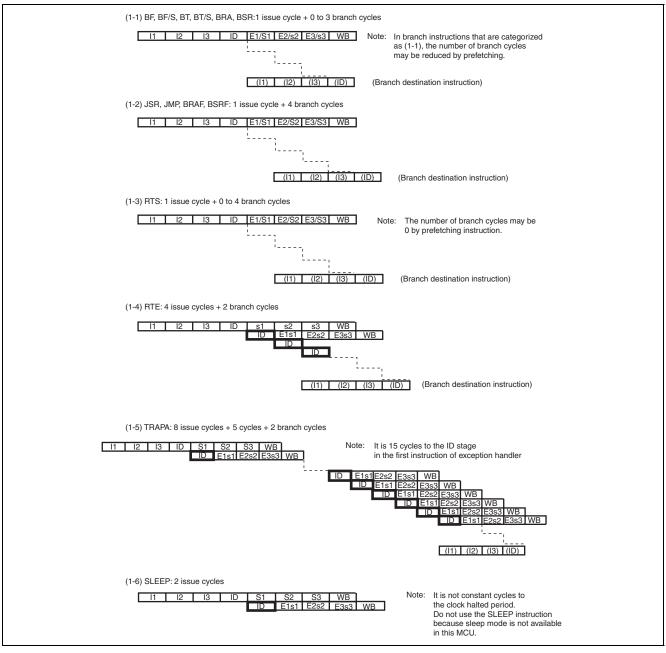

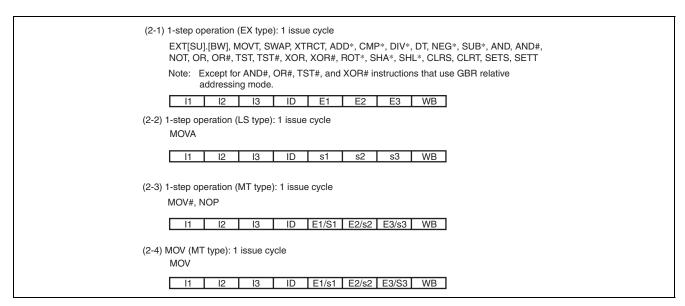

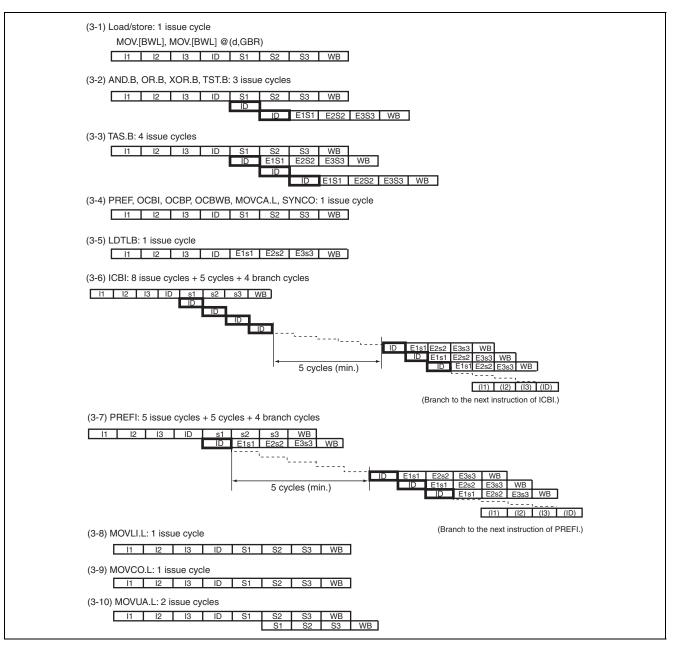

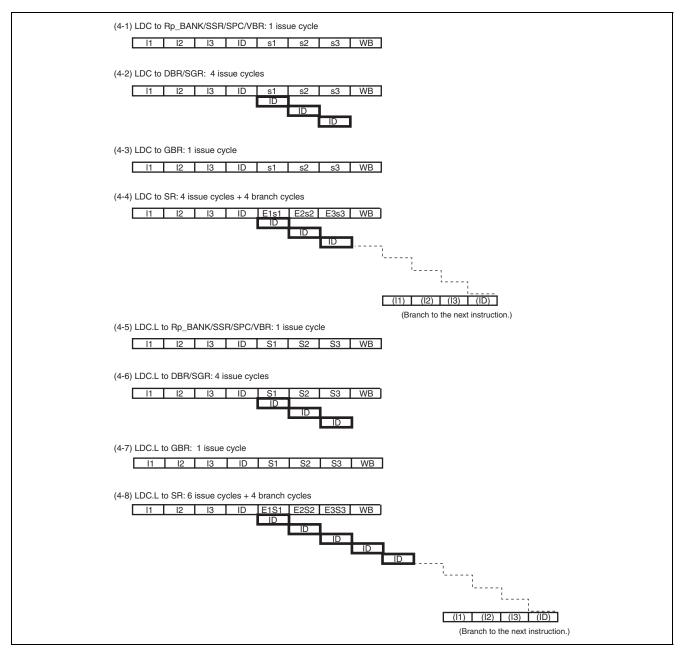

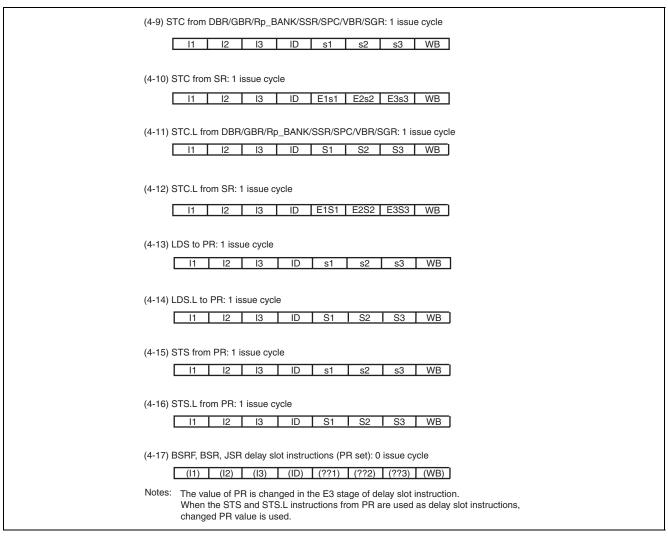

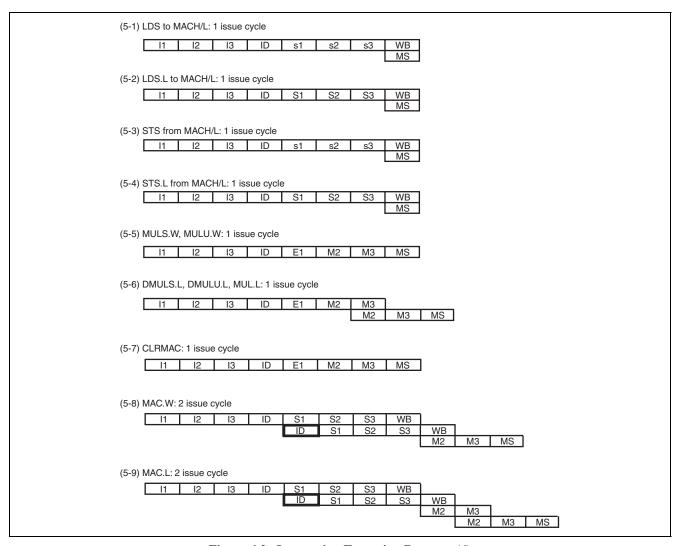

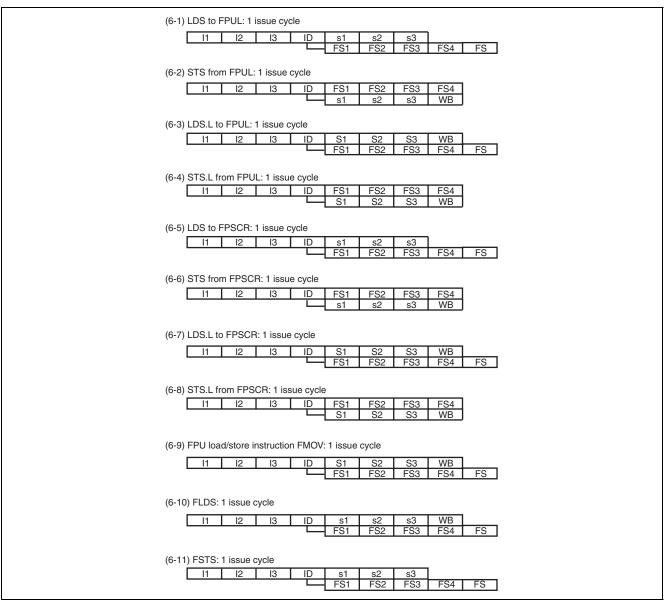

| Sect | tion 4 Pipelining                                                 | 4-1             |

| 4.1  | Pipelines                                                         | 4-1             |

| 4.2  | Parallel-Executability                                            | 4-11            |

| 4.3  | Issue Rates and Execution Cycles                                  |                 |

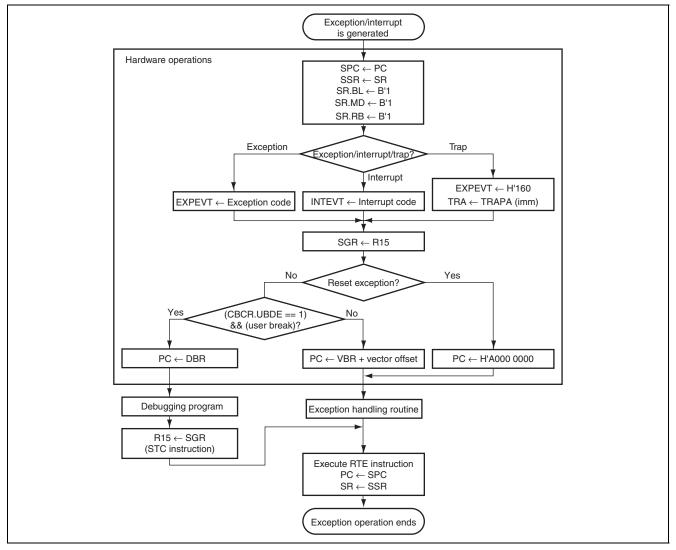

| Sect | tion 5 Exception Handling                                         | 5-1             |

| 5.1  | Overview                                                          |                 |

| 5.2  | Register Descriptions                                             | 5-1             |

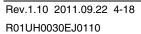

|      | 5.2.1 TRAPA Exception Register (TRA)                              |                 |

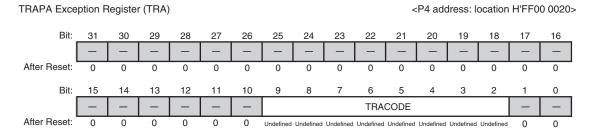

|      | 5.2.2 Exception Event Register (EXPEVT)                           |                 |

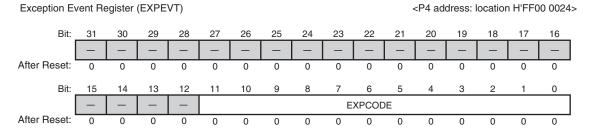

|      | 5.2.3 Interrupt Event Register (INTEVT)                           |                 |

|      | 5.2.4 Unsupported Function Detection Exception Register (EXPMASK) |                 |

| 5.3  | Exception Handling Functions                                      |                 |

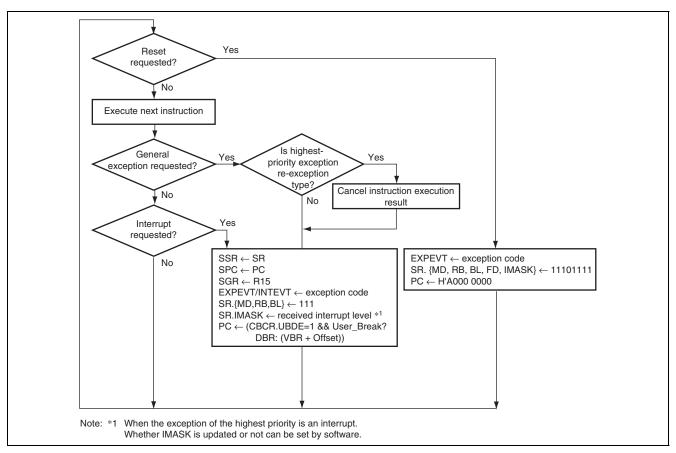

|      | 5.3.1 Exception Handling Flow                                     |                 |

|      | 5.3.2 Exception Handling Vector Addresses                         |                 |

| 5.4  | Exception Types and Priorities                                    |                 |

| 5.5  | Exception Flow                                                    |                 |

|      |                                                                   |                 |

|      | 5.5.1   | Exception Flow                                        | 5-7  |

|------|---------|-------------------------------------------------------|------|

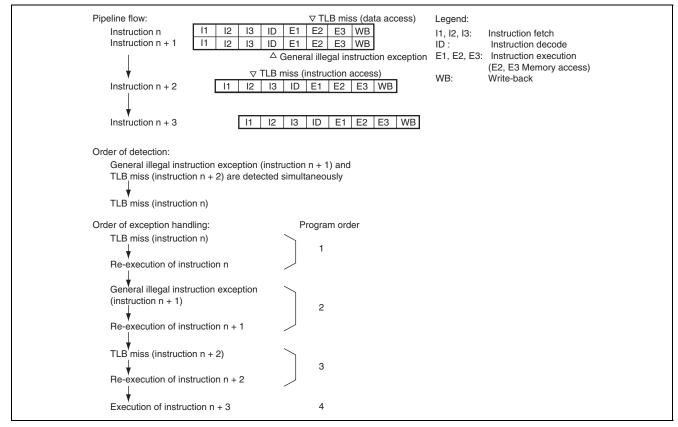

|      | 5.5.2   | Exception Source Acceptance                           | 5-8  |

|      | 5.5.3   | Exception Requests and BL Bit                         | 5-9  |

|      | 5.5.4   | Return from Exception Handling                        | 5-9  |

| 5.6  | Descri  | ption of Exceptions                                   | 5-10 |

|      | 5.6.1   | Resets                                                | 5-10 |

|      | 5.6.2   | General Exceptions                                    | 5-11 |

|      | 5.6.3   | Interrupts                                            | 5-23 |

|      | 5.6.4   | Priority Order with Multiple Exceptions               |      |

| 5.7  | Usage   | Notes                                                 |      |

| Sect | ion 6 I | Floating-Point Unit (FPU)                             | 6-1  |

| 6.1  | Overvi  | iew                                                   | 6-1  |

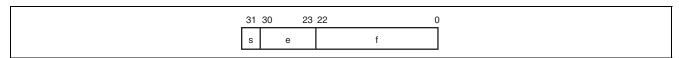

| 6.2  | Data F  | formats                                               | 6-2  |

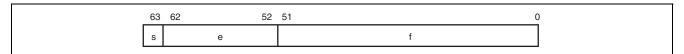

|      | 6.2.1   | Floating-Point Format                                 | 6-2  |

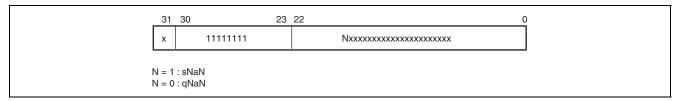

|      | 6.2.2   | Non-Numbers (NaN)                                     | 6-3  |

|      | 6.2.3   | Denormalized Numbers                                  | 6-4  |

| 6.3  | Registe | er Descriptions                                       | 6-5  |

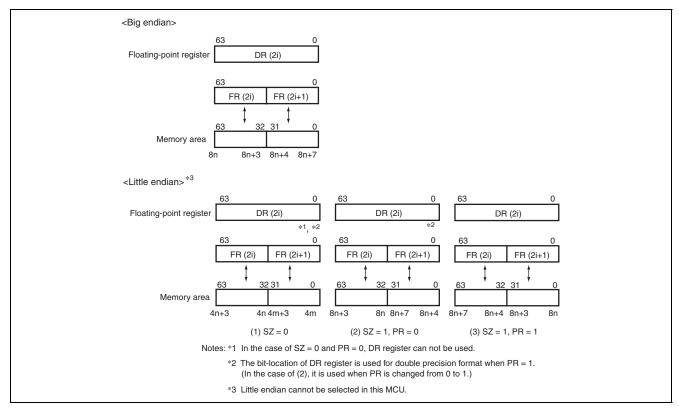

|      | 6.3.1   | Floating-Point Registers                              |      |

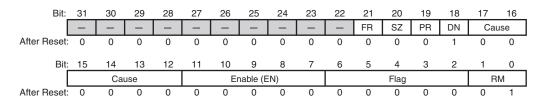

|      | 6.3.2   | Floating-Point Status/Control Register (FPSCR)        |      |

|      | 6.3.3   | Floating-Point Communication Register (FPUL)          |      |

| 6.4  | Round   | ing                                                   |      |

| 6.5  |         | ng-Point Exceptions                                   |      |

| 6.6  |         | ics Support Functions                                 |      |

|      | 6.6.1   | Geometric Operation Instructions                      |      |

|      | 6.6.2   | Pair Single-Precision Data Transfer                   |      |

|      | 0.0.2   | 1 W.1 0.11.8.4 1 1 4 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1  |      |

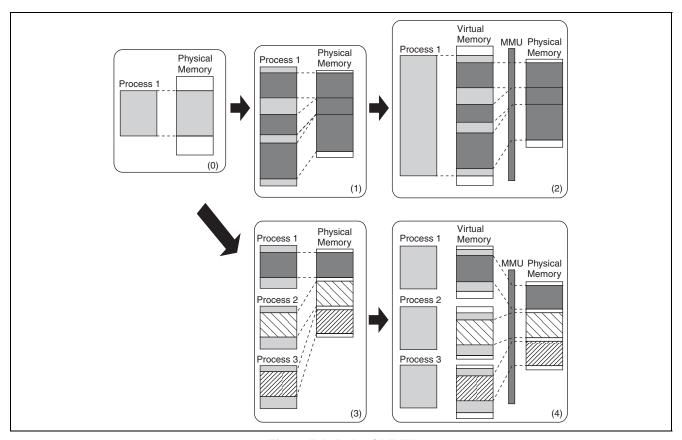

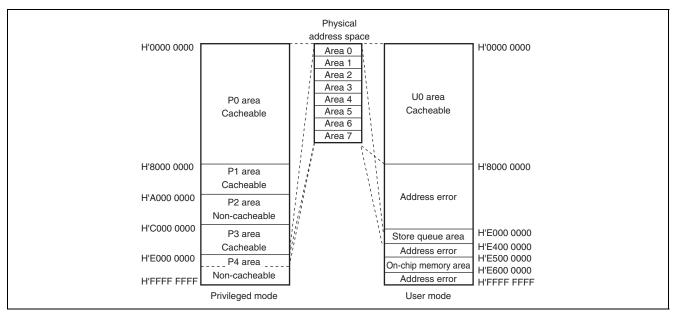

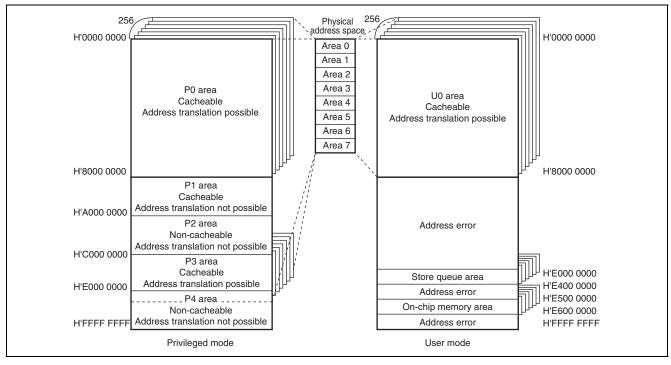

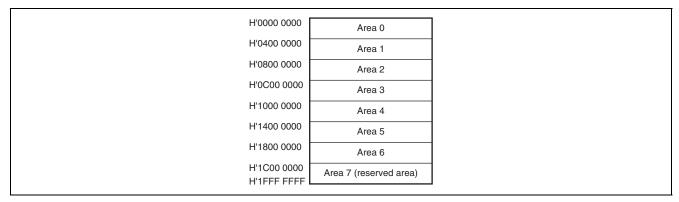

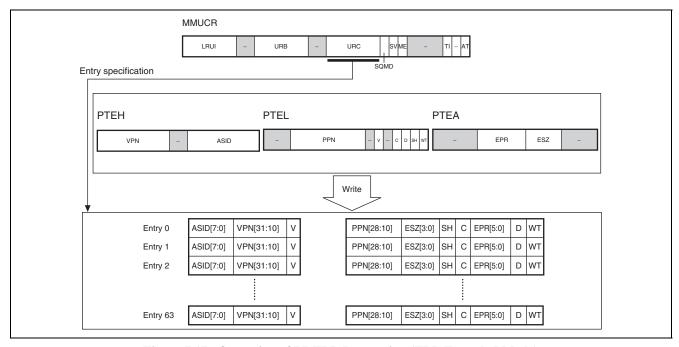

| Sect | ion 7 1 | Memory Management Unit (MMU)                          | 7-1  |

| 7.1  |         | iew                                                   |      |

|      | 7.1.1   | Address Spaces                                        |      |

| 7.2  |         | er Descriptions                                       |      |

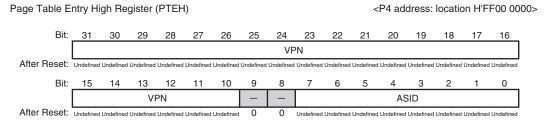

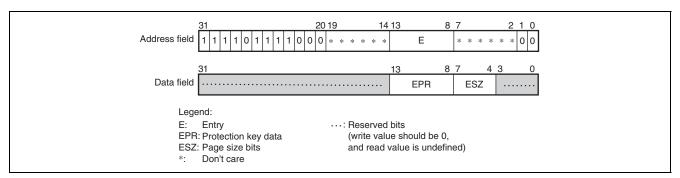

|      | 7.2.1   | Page Table Entry High Register (PTEH)                 |      |

|      | 7.2.2   | Page Table Entry Low Register (PTEL)                  |      |

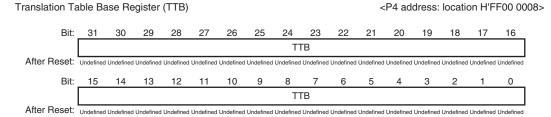

|      | 7.2.3   | Translation Table Base Register (TTB)                 |      |

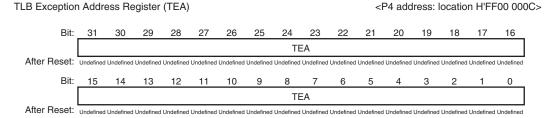

|      | 7.2.4   | TLB Exception Address Register (TEA)                  |      |

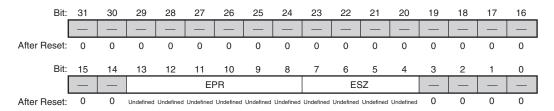

|      | 7.2.4   | MMU Control Register (MMUCR)                          |      |

|      | 7.2.5   | Page Table Entry Assistance Register (PTEA)           |      |

|      |         |                                                       |      |

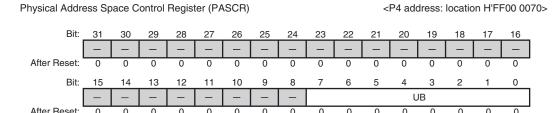

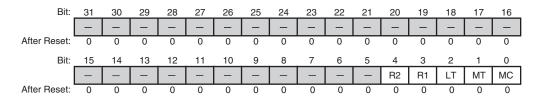

|      | 7.2.7   | Physical Address Space Control Register (PASCR)       |      |

| 7.2  | 7.2.8   | Instruction Re-Fetch Inhibit Control Register (IRMCR) |      |

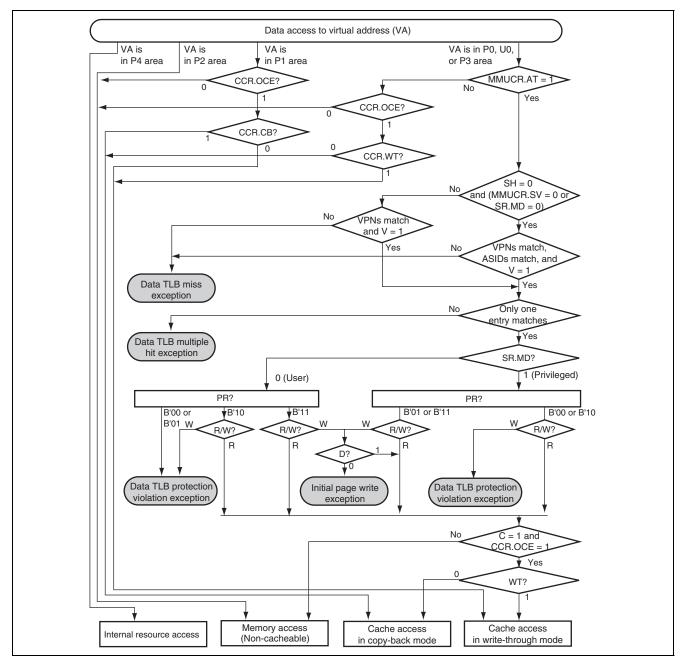

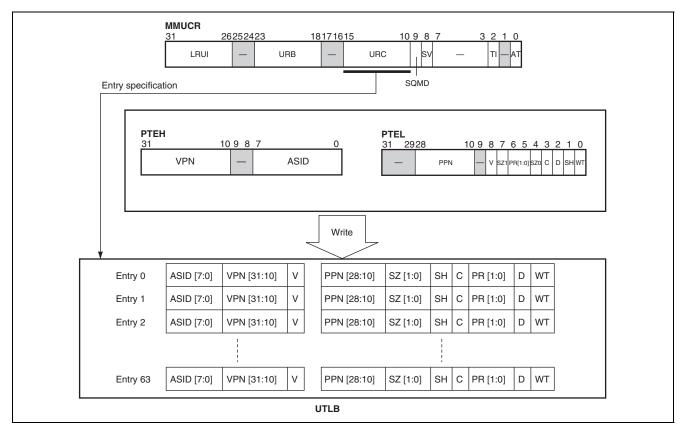

| 7.3  |         | Functions (TLB Compatible Mode)                       |      |

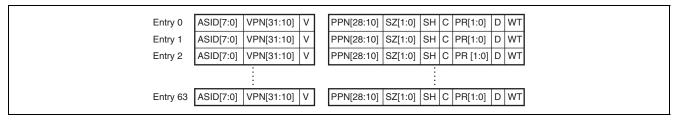

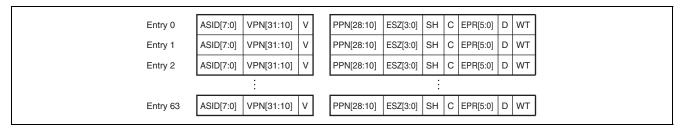

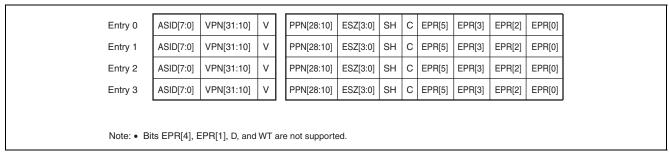

|      | 7.3.1   | Unified TLB (UTLB) Configuration                      |      |

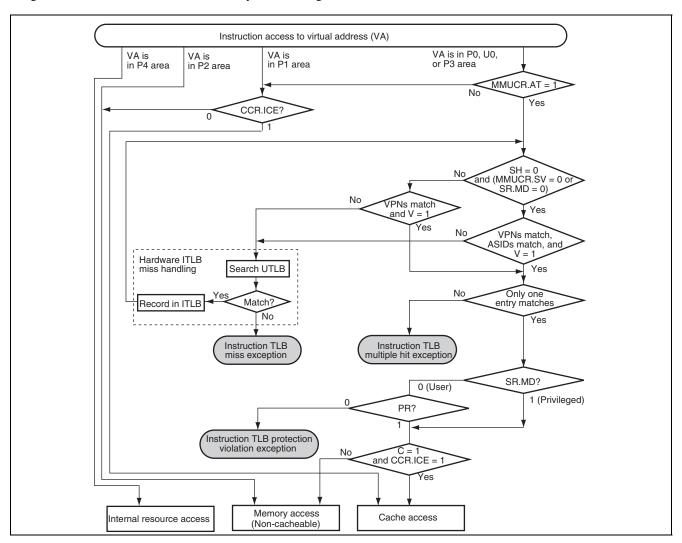

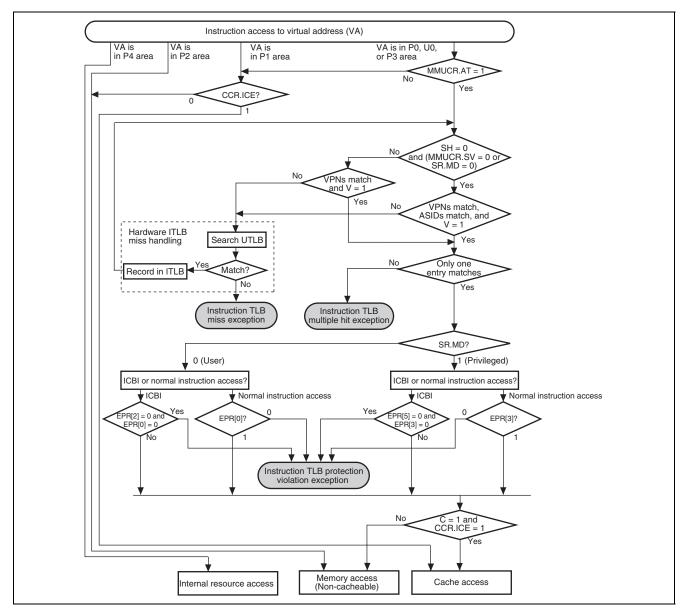

|      | 7.3.2   | Instruction TLB (ITLB) Configuration                  |      |

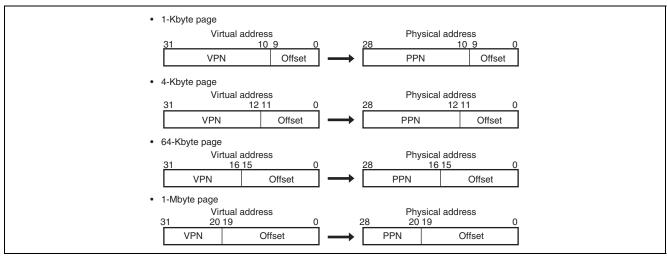

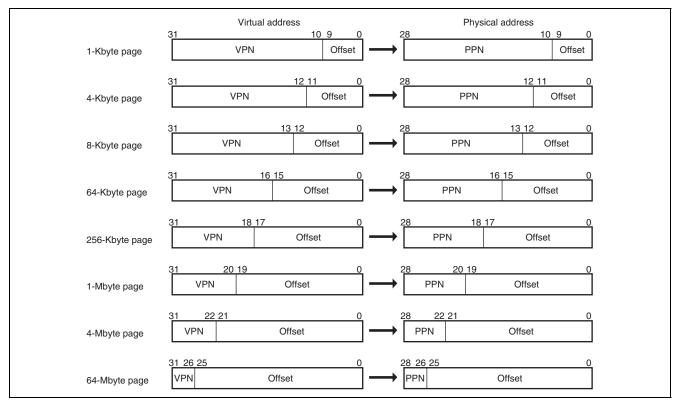

|      | 7.3.3   | Address Translation Method                            |      |

| 7.4  |         | functions (TLB Extended Mode)                         |      |

|      | 7.4.1   | Unified TLB (UTLB) Configuration                      |      |

|      | 7.4.2   | Instruction TLB (ITLB) Configuration                  |      |

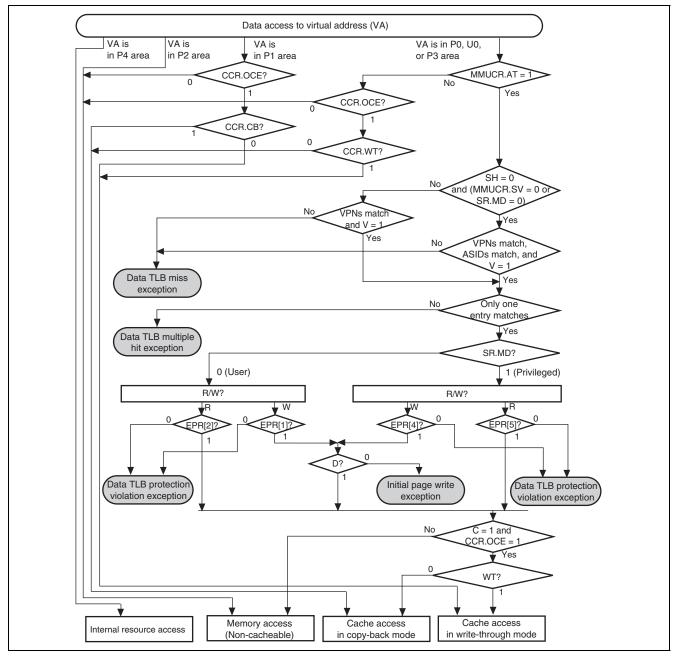

|      | 7.4.3   | Address Translation Method                            |      |

| 7.5  | MMU     | Functions                                             | 7-27 |

|      | 7.5.1   | MMU Hardware Management                               | 7-27 |

|      | 7.5.2   | MMU Software Management                               | 7-27 |

|      | 7.5.3   | MMU Instruction (LDTLB)                               | 7-27 |

|      | 7.5.4   | Hardware ITLB Miss Handling                    | 7-29        |

|------|---------|------------------------------------------------|-------------|

|      | 7.5.5   | Avoiding Synonym Problems                      | 7-29        |

| 7.6  | MMU I   | Exceptions                                     | 7-30        |

|      | 7.6.1   | Instruction TLB Multiple Hit Exception         | 7-30        |

|      | 7.6.2   | Instruction TLB Miss Exception                 | 7-30        |

|      | 7.6.3   | Instruction TLB Protection Violation Exception | 7-31        |

|      | 7.6.4   | Data TLB Multiple Hit Exception                | 7-32        |

|      | 7.6.5   | Data TLB Miss Exception                        | 7-32        |

|      | 7.6.6   | Data TLB Protection Violation Exception        | 7-33        |

|      | 7.6.7   | Initial Page Write Exception                   | 7-34        |

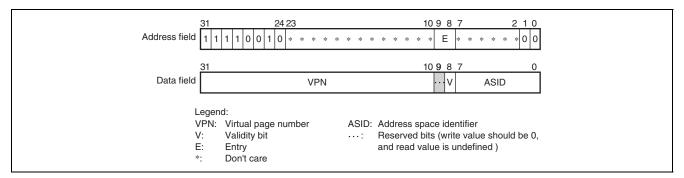

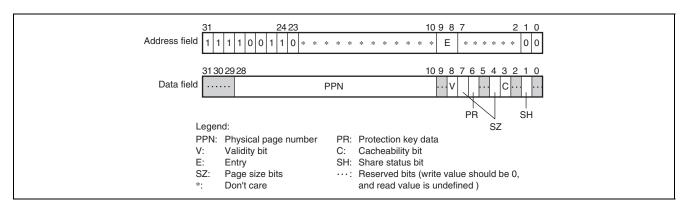

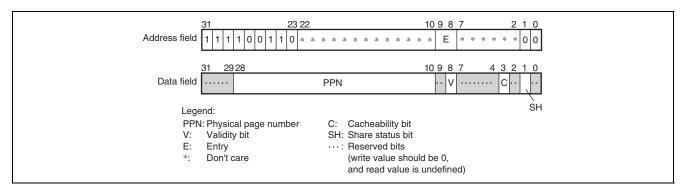

| 7.7  | Memor   | ry-Mapped TLB Configuration                    | 7-35        |

|      | 7.7.1   | ITLB Address Array                             | 7-35        |

|      | 7.7.2   | ITLB Data Array (TLB Compatible Mode)          | 7-36        |

|      | 7.7.3   | ITLB Data Array (TLB Extended Mode)            | 7-37        |

|      | 7.7.4   | UTLB Address Array                             | 7-38        |

|      | 7.7.5   | UTLB Data Array (TLB Compatible Mode)          | 7-39        |

|      | 7.7.6   | UTLB Data Array (TLB Extended Mode)            | 7-40        |

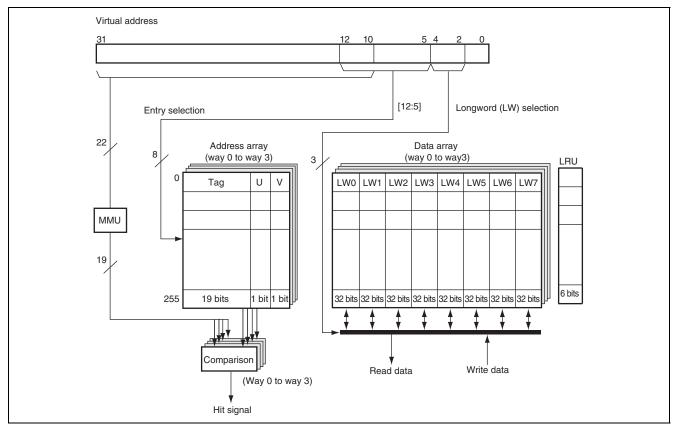

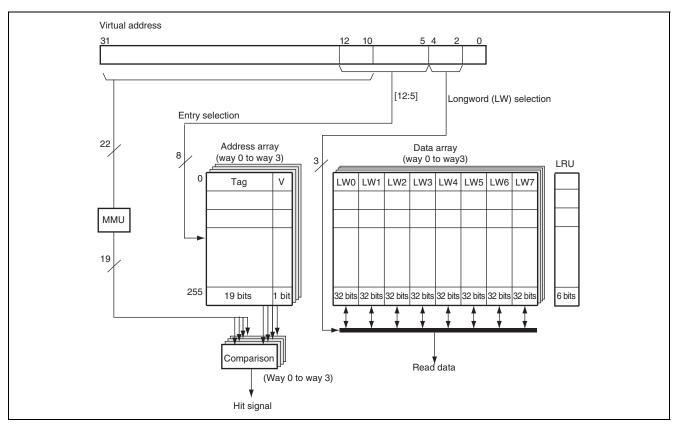

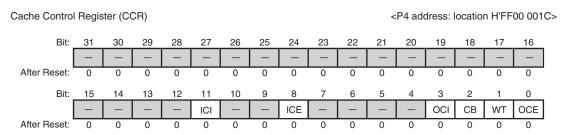

| Sect | ion 8 ( | Caches                                         | <b>8</b> _1 |

| 8.1  |         | ew                                             |             |

| 8.2  |         | er Descriptions                                |             |

| 0.2  | 8.2.1   | Cache Control Register (CCR)                   |             |

|      | 8.2.2   | Queue Address Control Register (QACR0)         |             |

|      | 8.2.3   | Queue Address Control Register 1 (QACR1)       |             |

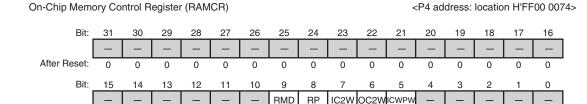

|      | 8.2.4   | On-Chip Memory Control Register (RAMCR)        |             |

| 8.3  |         | nd Cache Operation                             |             |

| 0.0  | 8.3.1   | Read Operation                                 |             |

|      | 8.3.2   | Prefetch Operation                             |             |

|      | 8.3.3   | Write Operation                                |             |

|      | 8.3.4   | Write-Back Buffer                              |             |

|      | 8.3.5   | Write-Through Buffer                           |             |

|      | 8.3.6   | OC Two-Way Mode                                |             |

| 8.4  |         | tion Cache Operation                           |             |

| 0    | 8.4.1   | Read Operation                                 |             |

|      | 8.4.2   | Prefetch Operation                             | 8-11        |

|      | 8.4.3   | IC Two-Way Mode                                |             |

|      | 8.4.4   | Instruction Cache Way Prediction Operation     |             |

| 8.5  |         | Operation Instruction                          |             |

|      | 8.5.1   | Coherency between Cache and External Memory    |             |

|      | 8.5.2   | Prefetch Operation                             |             |

| 8.6  |         | ry-Mapped Cache Configuration                  |             |

|      | 8.6.1   | IC Address Array                               |             |

|      | 8.6.2   | IC Data Array                                  |             |

|      | 8.6.3   | OC Address Array                               |             |

|      | 8.6.4   | OC Data Array                                  |             |

|      | 8.6.5   | Memory Allocation Associative Write Operation  |             |

| 8.7  |         | Queues                                         |             |

|      | 8.7.1   | SQ Configuration                               |             |

|      | 8.7.2   | Writing to SQ                                  |             |

|      | 8.7.3   | Transfer to External Memory                    |             |

|      | 8.7.4   | Determination of SQ Access Exception           |             |

|      |         | · 1 · · · · · · · · · · · · · · · · · ·        |             |

|       | 8.7.5    | Reading from SQ                                          | 8-21                 |

|-------|----------|----------------------------------------------------------|----------------------|

| Secti | ion 9 II | L Memory/OL Memory                                       | 9-1                  |

| 9.1   |          | ew                                                       |                      |

| 9.2   |          | er Descriptions                                          |                      |

|       | 9.2.1    | On-Chip Memory Control Register (RAMCR)                  |                      |

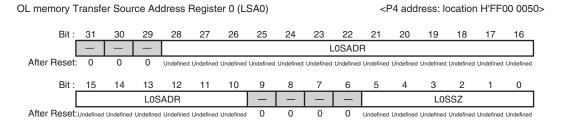

|       | 9.2.2    | OL memory Transfer Source Address Register 0 (LSA0)      |                      |

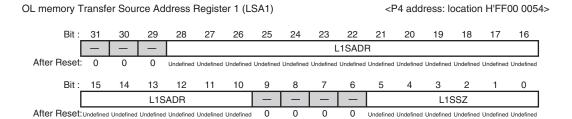

|       | 9.2.3    | OL memory Transfer Source Address Register 1 (LSA1)      |                      |

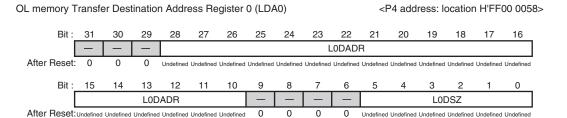

|       | 9.2.4    | OL memory Transfer Destination Address Register 0 (LDA0) |                      |

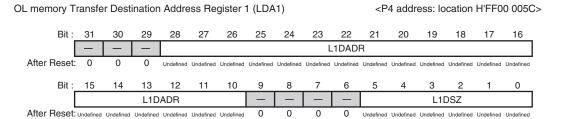

|       | 9.2.5    | OL memory Transfer Destination Address Register 1 (LDA1) |                      |

| 9.3   | Operati  | on                                                       |                      |

|       | 9.3.1    | Instruction Fetch Access from the CPU                    | 9-9                  |

|       | 9.3.2    | Operand Access from the CPU and Access from the FPU      | 9-9                  |

|       | 9.3.3    | Access from the SuperHyway Bus Master Module             | 9-9                  |

|       | 9.3.4    | OL Memory Block Transfer                                 | 9-9                  |

|       | 9.3.5    | On-Chip Memory Protection Functions                      | 9-11                 |

| 9.4   | Usage 1  | Notes                                                    | 9-12                 |

|       | 9.4.1    | Page Conflict                                            | 9-12                 |

|       | 9.4.2    | Access Across Different Pages                            | 9-12                 |

|       | 9.4.3    | IL Memory Coherency                                      |                      |

| Secti | on 10    | Operating Modes                                          | 10-1                 |

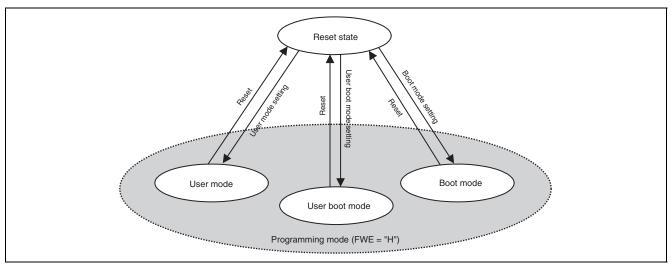

| 10.1  |          | ng Modes                                                 |                      |

| 10.1  | 10.1.1   | MCU Operating Modes                                      |                      |

|       | 10.1.2   | On-Board Programming Modes                               |                      |

| 10.2  |          | r Descriptions                                           |                      |

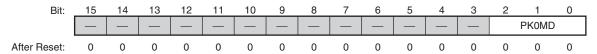

| 10.2  | 10.2.1   | Mode Control Register (MDCR)                             |                      |

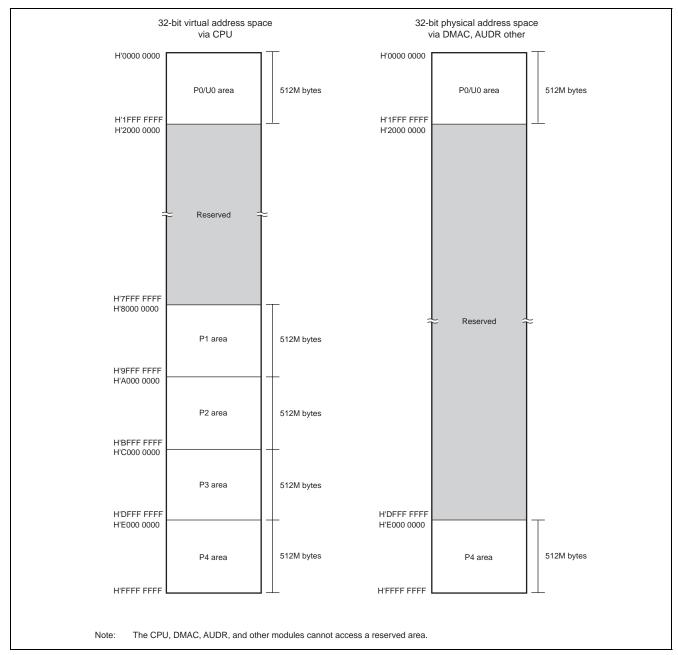

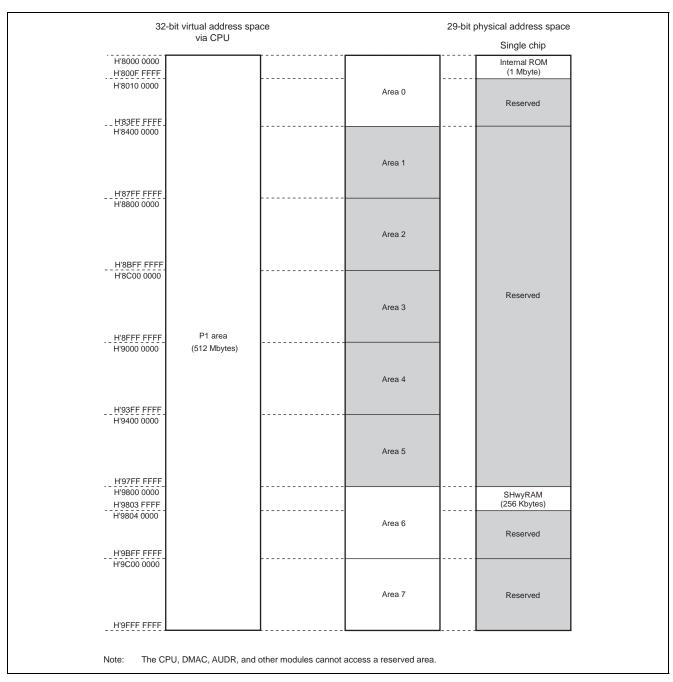

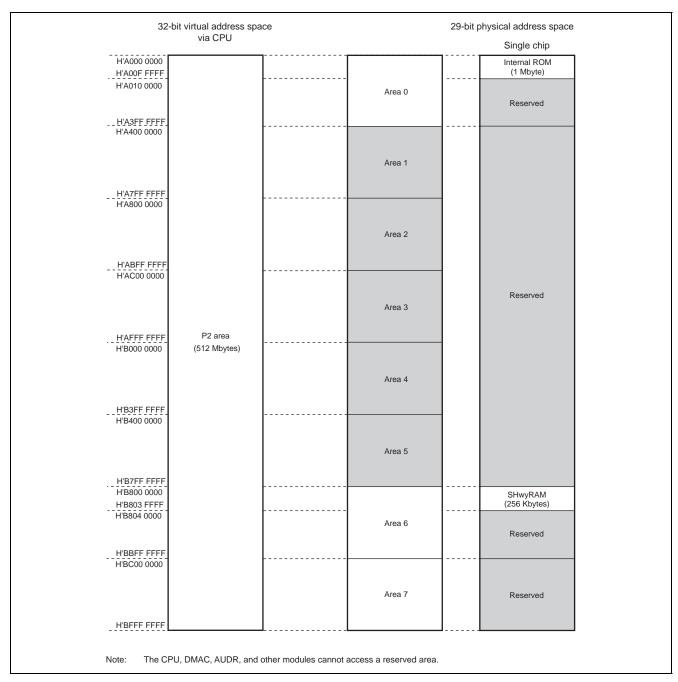

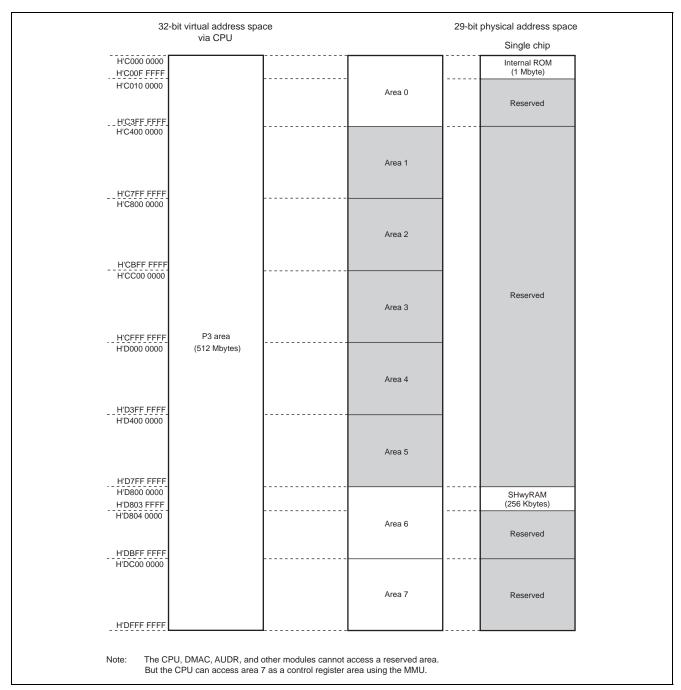

| Secti | ion 11   | Address Space                                            | 11-1                 |

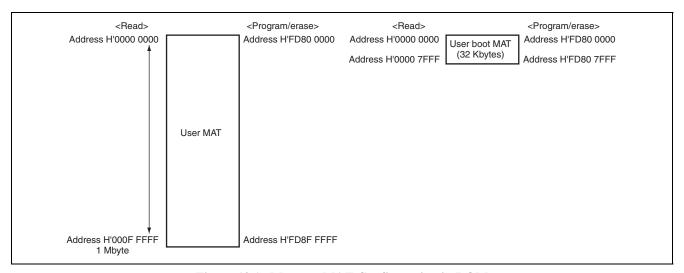

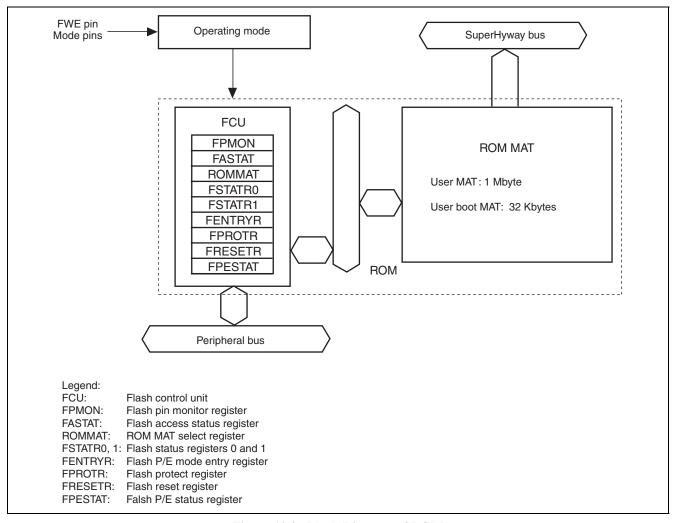

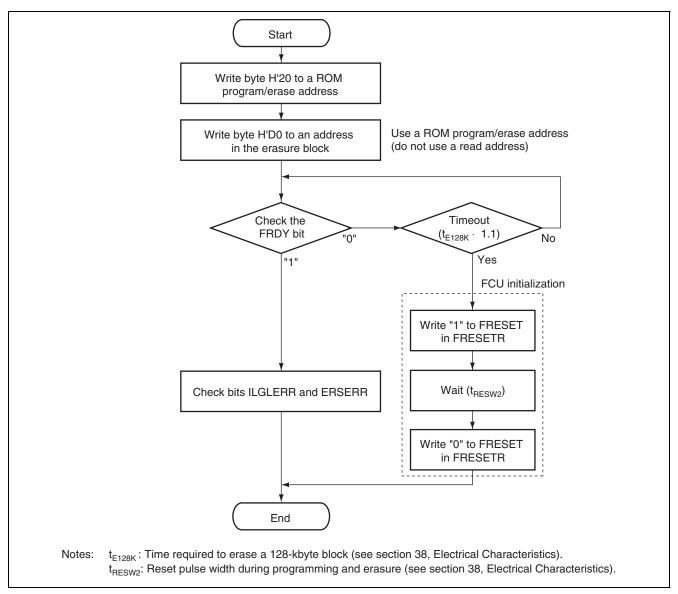

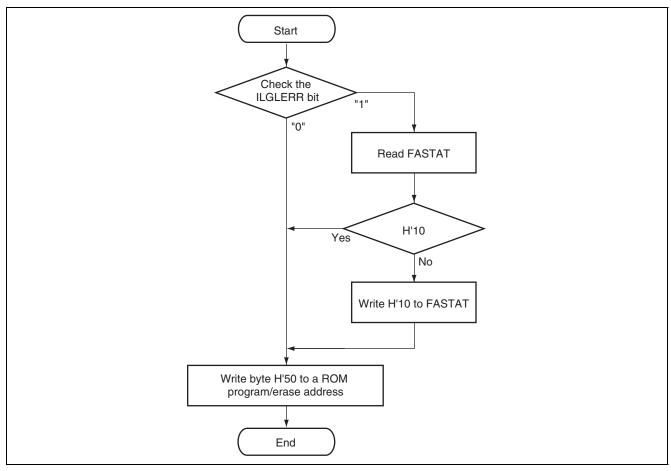

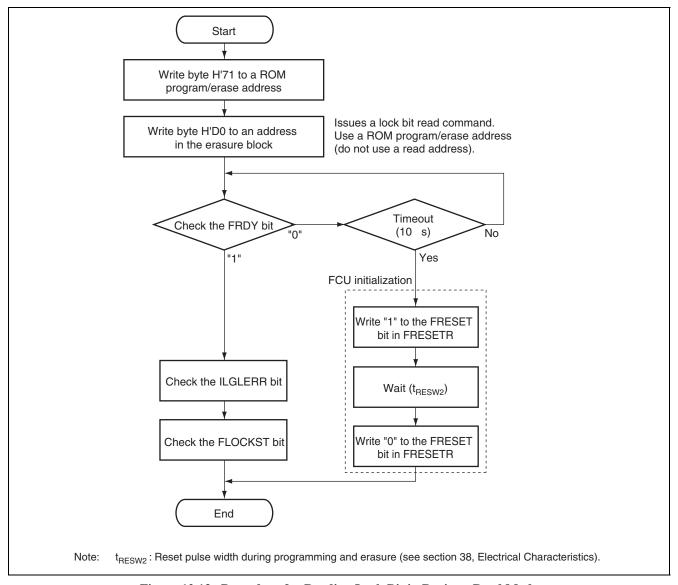

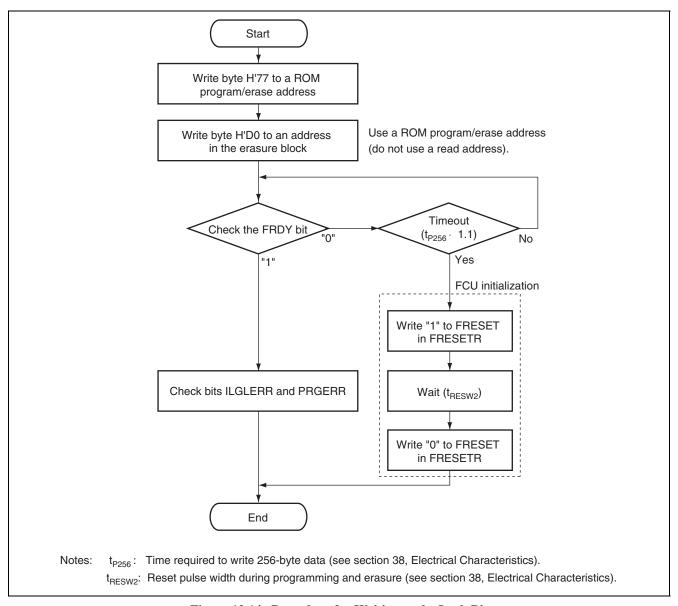

| Secti | ion 12   | ROM                                                      | 12-1                 |

| 12.1  |          | EW                                                       |                      |

| 12.2  |          | Output Pins                                              |                      |

| 12.3  | -        | or Descriptions                                          |                      |

| 12.3  | _        | Flash Pin Monitor Register (FPMON)                       |                      |

|       | 12.3.1   | Flash Access Status Register (FASTAT)                    |                      |

|       | 12.3.3   | ROM MAT Select Register (ROMMAT)                         |                      |

|       | 12.3.4   | Flash Status Register 0 (FSTATR0)                        |                      |

|       | 12.3.5   | Flash Status Register 1 (FSTATR1)                        |                      |

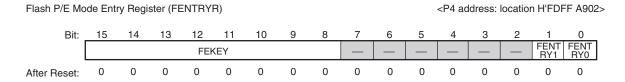

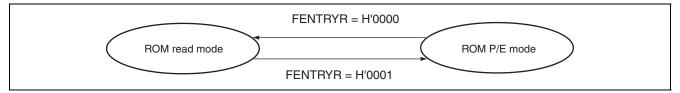

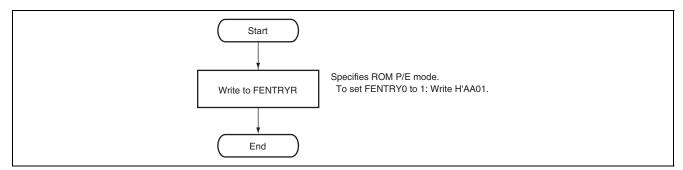

|       | 12.3.6   | Flash P/E Mode Entry Register (FENTRYR)                  |                      |

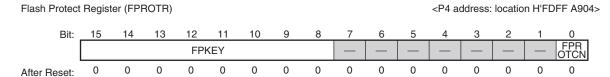

|       | 12.3.7   | Flash Protect Register (FPROTR)                          |                      |

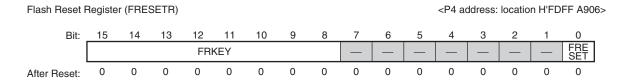

|       | 12.3.8   | Flash Reset Register (FRESETR)                           |                      |

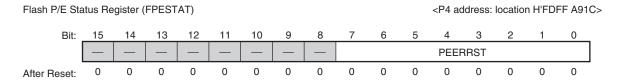

|       | 12.3.9   | Flash P/E Status Register (FPESTAT)                      |                      |

| 12.4  |          | ew of ROM-Related Modes                                  |                      |

| 12.5  |          | lode                                                     |                      |

| 12.5  | 12.5.1   | System Configuration                                     |                      |

| 12.6  |          | lode and User Boot Mode                                  |                      |

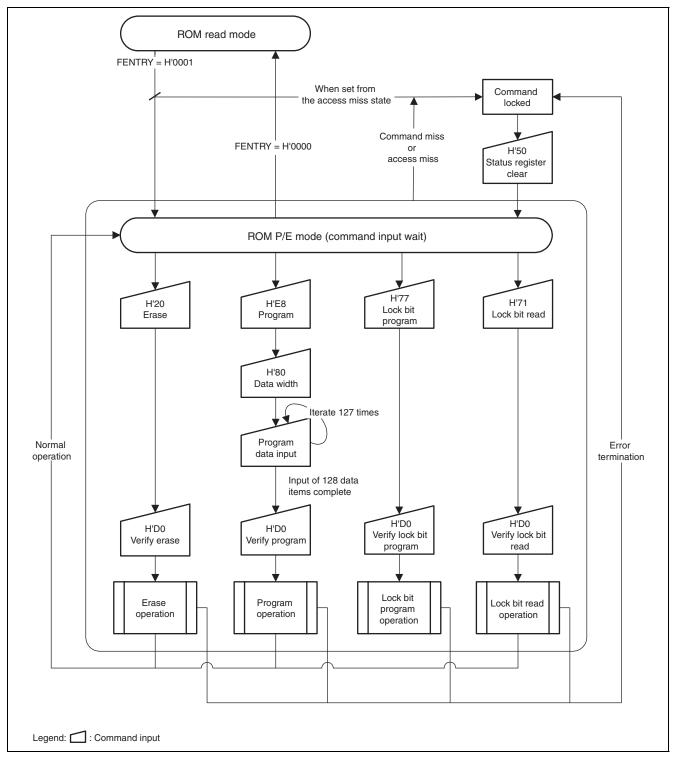

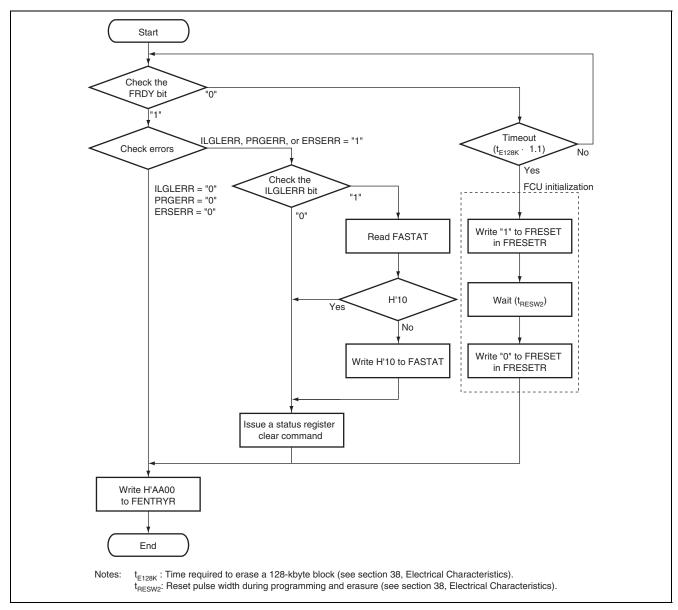

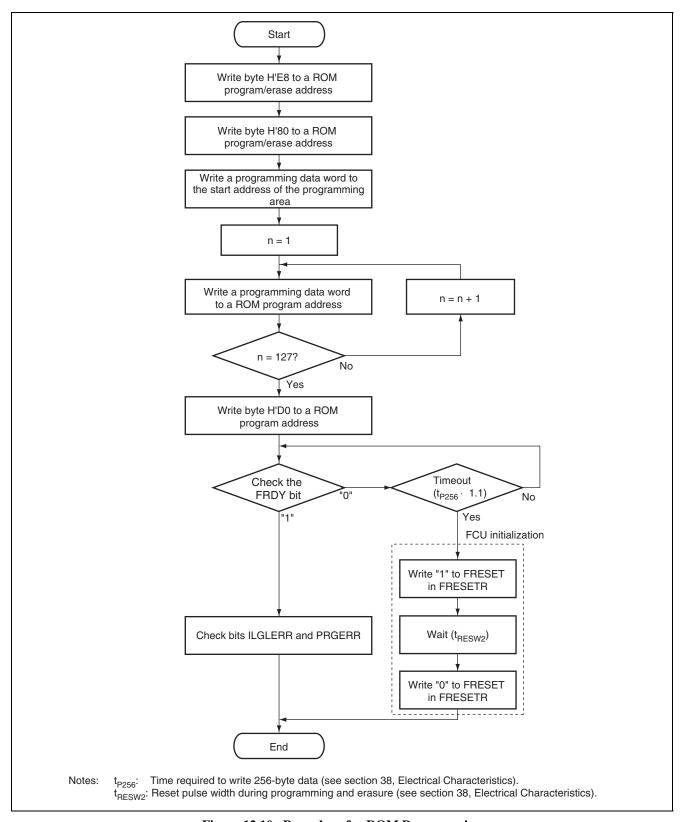

| 12.0  | 12.6.1   | FCU Command List                                         |                      |

|       | 12.6.1   | Conditions for FCU Command Acceptance                    |                      |

|       | 12.6.3   | FCU Command Usage                                        |                      |

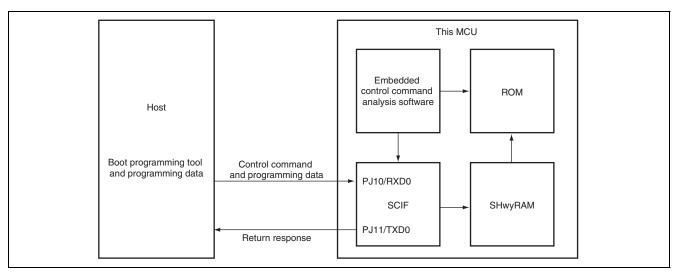

| 12.7  |          | oot Mode                                                 |                      |

| /     |          | OOL 1710 <b>00</b>                                       | 1 4 <sup>-</sup> J 1 |

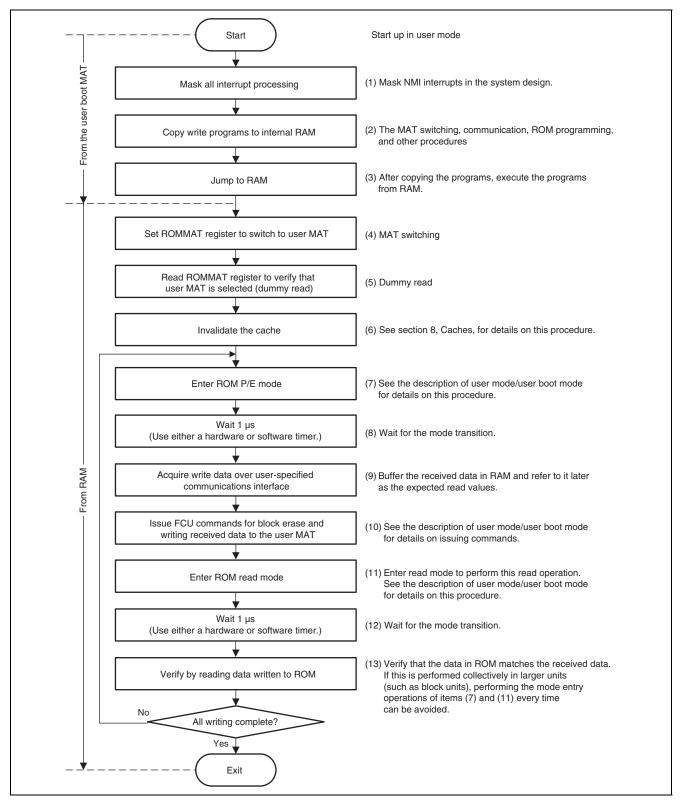

|       | 12.7.1          | Switching between User MAT and User Boot MAT                         | 12-31 |

|-------|-----------------|----------------------------------------------------------------------|-------|

|       | 12.7.2          | Programming the User MAT                                             | 12-32 |

| 12.8  | Protection      | n                                                                    | 12-33 |

|       | 12.8.1          | Hardware Protection                                                  | 12-33 |

|       | 12.8.2          | Software Protection                                                  | 12-33 |

|       | 12.8.3          | Error Protection                                                     | 12-33 |

| 12.9  | Usage N         | otes                                                                 | 12-35 |

|       | 12.9.1          | Key Code Stored Area                                                 | 12-35 |

|       | 12.9.2          | Compatibility with Programming/Erasing Program                       |       |

|       |                 | of Conventional F-ZTAT SH Microcomputers (MCUs)                      | 12-35 |

|       | 12.9.3          | FWE Pin State                                                        | 12-35 |

|       | 12.9.4          | Reset during Programming or Erasure                                  | 12-35 |

|       | 12.9.5          | Prohibition of Additional Programming                                | 12-35 |

|       | 12.9.6          | Power Supply Control during Reprogramming                            |       |

|       | 12.9.7          | Accessing ROM-Related Registers                                      |       |

|       |                 |                                                                      |       |

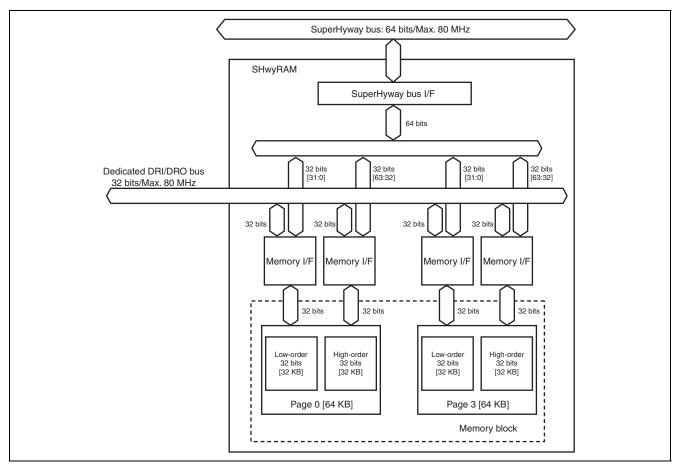

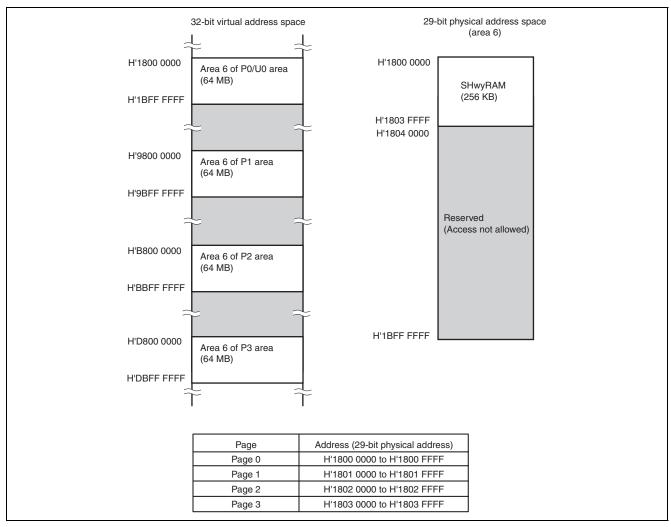

| Secti | ion 13 S        | SuperHyway RAM (SHwyRAM)                                             | 13-1  |

| 13.1  |                 | W                                                                    |       |

|       |                 |                                                                      |       |

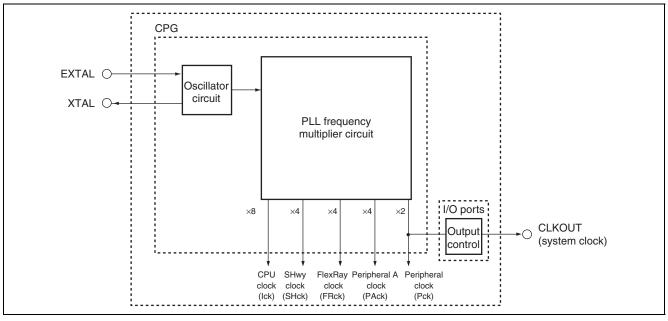

| Secti | ion 14 <b>(</b> | Clock Generator (CPG)                                                | 14-1  |

| 14.1  |                 | W                                                                    |       |

| 14.2  |                 | ıtput Pins                                                           |       |

| 14.3  |                 | Descriptions                                                         |       |

|       | 14.3.1          | Oscillator Status Register (OSCSR)                                   |       |

|       | 14.3.2          | Oscillator Control Register (OSCCR)                                  |       |

| 14.4  |                 | ources                                                               |       |

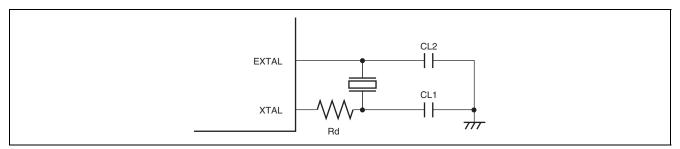

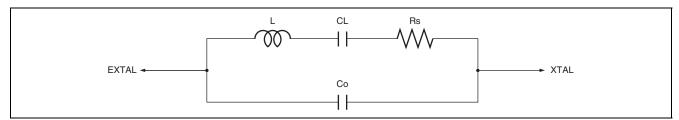

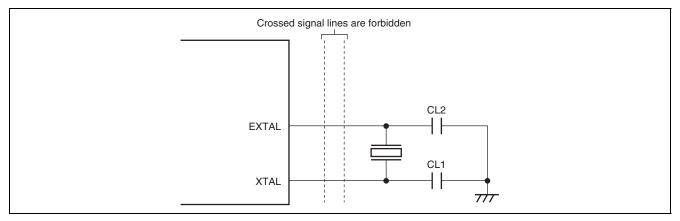

| 1     | 14.4.1          | Crystal Resonator Connection                                         |       |

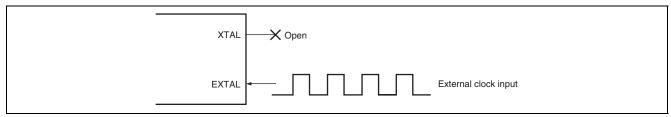

|       | 14.4.2          | External Clock Input                                                 |       |

| 14.5  |                 | Totes                                                                |       |

| 17.5  | 14.5.1          | Board Design Notes                                                   |       |

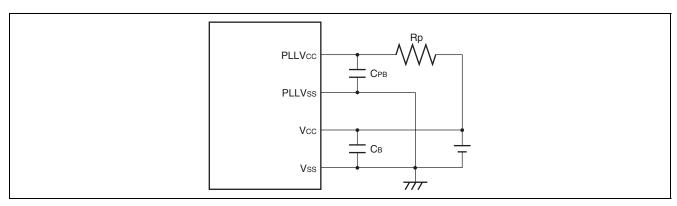

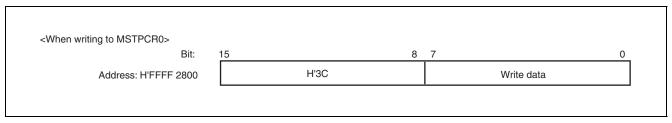

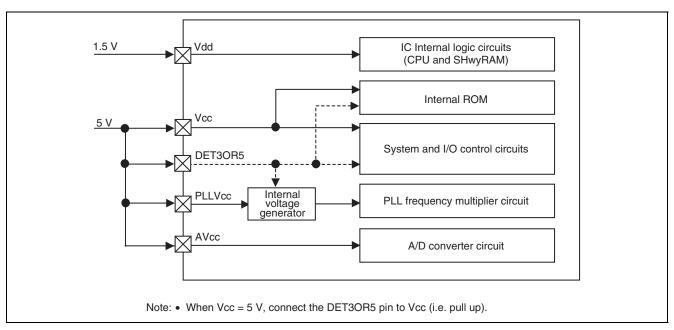

|       | 14.5.2          | PLL Frequency Multiplier Circuit Power Supply Connection Notes       |       |

|       | 17.5.2          | 1 LL I requeries munipher chedit I ower suppry connection rotes      | 14-3  |

| Secti | on 15 I         | nterrupt Controller (INTC)                                           | 15_1  |

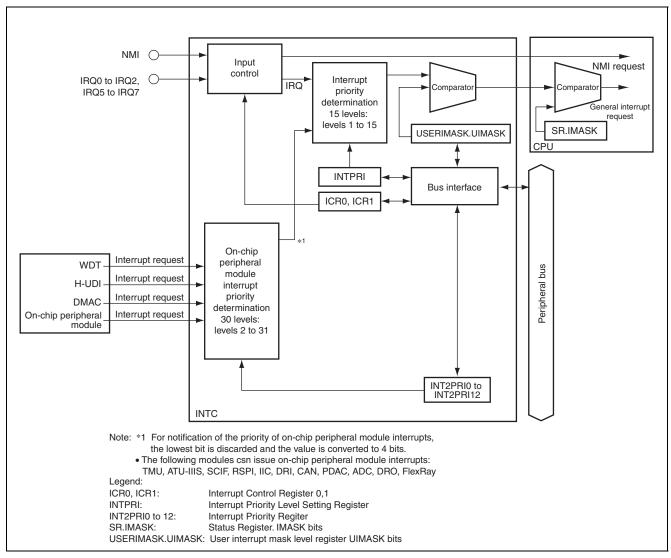

| 15.1  |                 | w                                                                    |       |

| 13.1  |                 | Interrupt Request Sources in INTC                                    |       |

| 15.2  |                 | itput Pins                                                           |       |

| 15.2  |                 | Descriptions                                                         |       |

| 13.3  | 15.3.1          | Interrupt Control Register 0 (ICR0)                                  |       |

|       |                 |                                                                      |       |

|       | 15.3.2          | Interrupt Control Register 1 (ICR1)                                  |       |

|       | 15.3.3          | Interrupt Priority Register (INTPRI)                                 |       |

|       | 15.3.4          | Interrupt Source Register (INTREQ)                                   |       |

|       | 15.3.5          | Interrupt Mask Register (INTMSK)                                     |       |

|       | 15.3.6          | Interrupt Mask Clear Register (INTMSKCLR)                            |       |

|       | 15.3.7          | NMI Flag Control Register (NMIFCR)                                   |       |

|       | 15.3.8          | User Interrupt Mask Level Register (USERIMASK)                       |       |

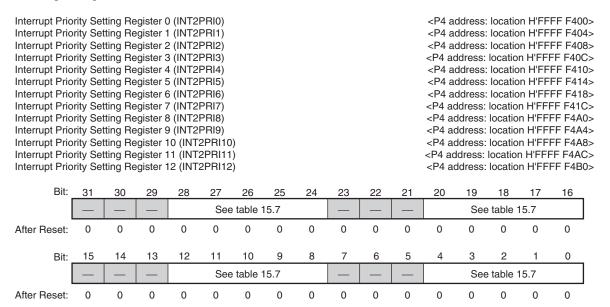

|       | 15.3.9          | Interrupt Priority Setting Registers 0 to 12 (INT2PRI0 to INT2PRI12) |       |

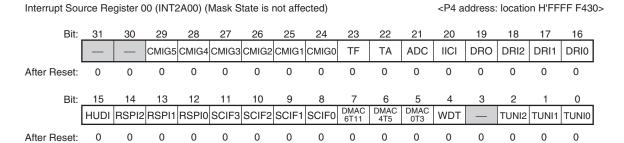

|       | 15.3.10         | Interrupt Source Register 00 (INT2A00) (Mask State is not affected)  |       |

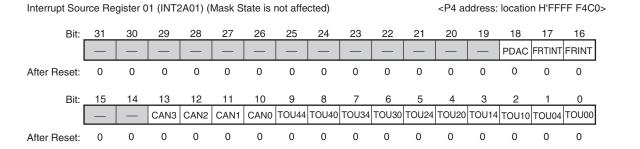

|       | 15.3.11         | Interrupt Source Register 01 (INT2A01) (Mask State is not affected)  |       |

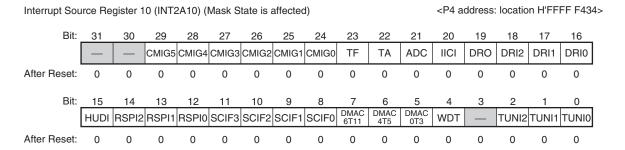

|       | 15.3.12         | Interrupt Source Register 10 (INT2A10) (Mask State is affected)      |       |

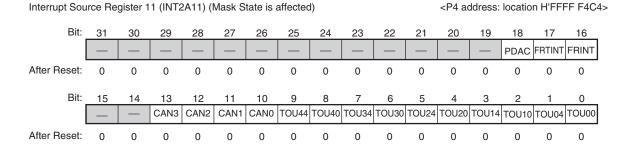

|       | 15.3.13         | Interrupt Source Register 11 (INT2A11) (Mask State is affected)      |       |

|       | 15.3.14         | Interrupt Mask Register 0 (INT2MSKR)                                 | 15-30 |

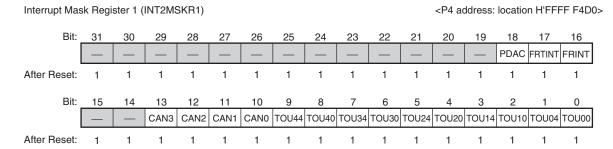

|       | 15.3.15   | Interrupt Mask Register 1 (INT2MSKR1)                                 |        |

|-------|-----------|-----------------------------------------------------------------------|--------|

|       | 15.3.16   | Interrupt Mask Clear Register 0 (INT2MSKCR)                           | 15-33  |

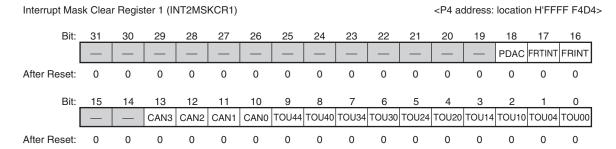

|       | 15.3.17   | Interrupt Mask Clear Register 1 (INT2MSKCR1)                          | 15-35  |

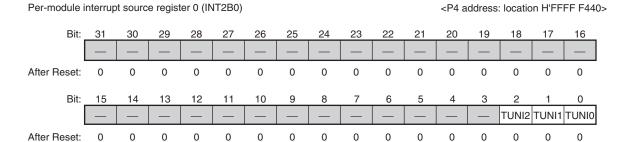

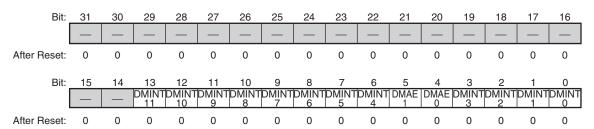

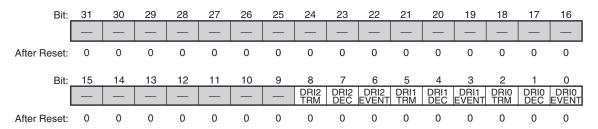

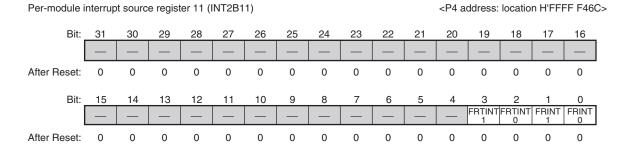

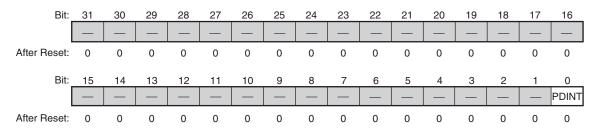

|       | 15.3.18   | Per-Module Interrupt Source Registers 0 to 12 (INT2B0 to INT2B12)     | 15-36  |

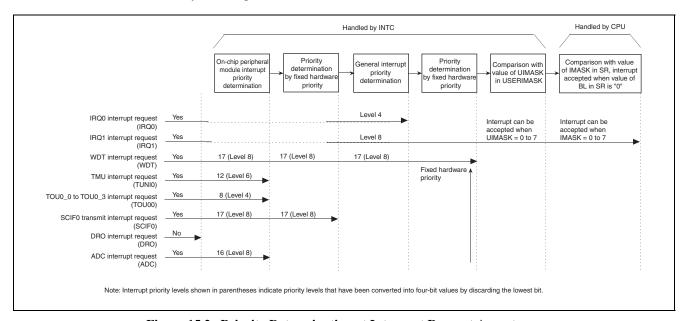

| 15.4  | Operation | on                                                                    | 15-51  |

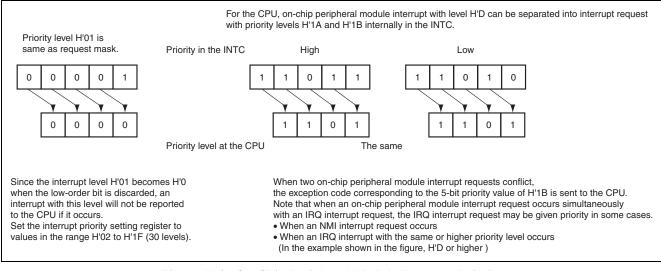

|       | 15.4.1    | Interrupt Sources and Priorities                                      | 15-51  |

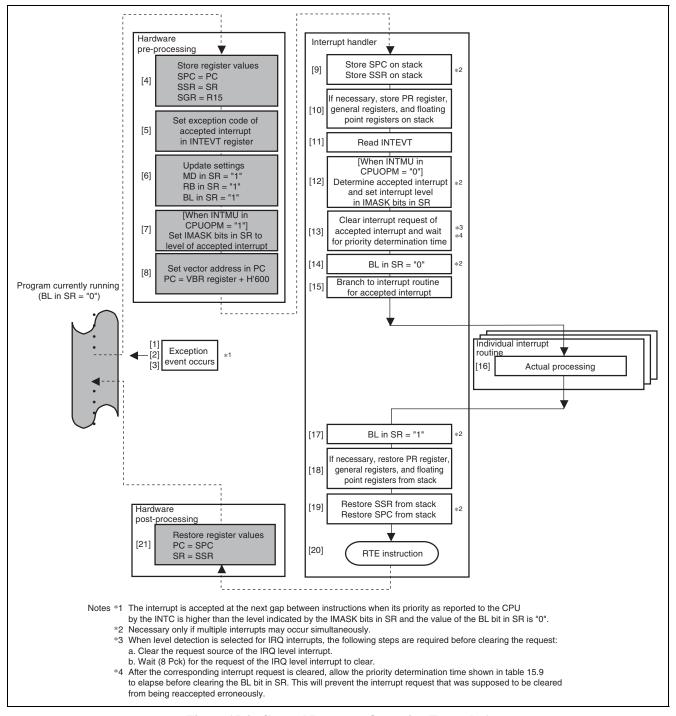

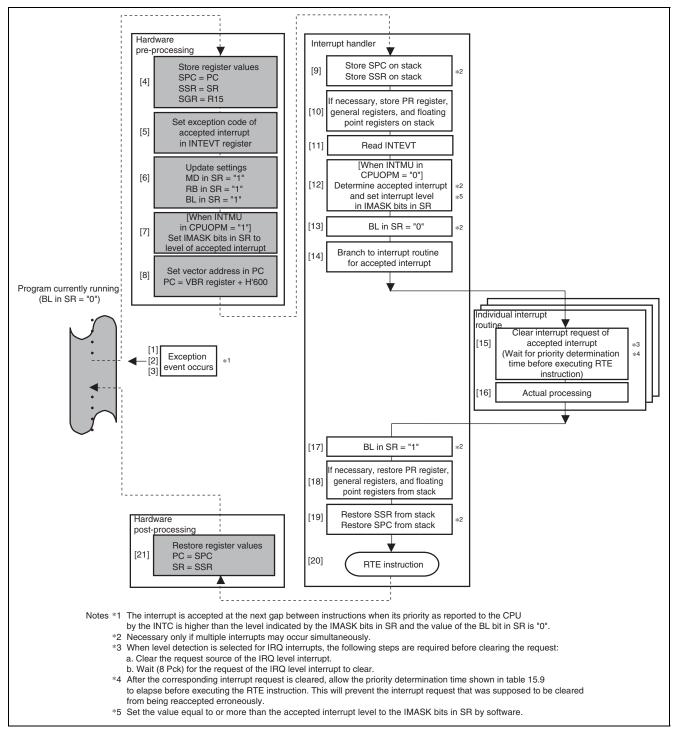

|       | 15.4.2    | General Interrupt Sequence                                            | 15-54  |

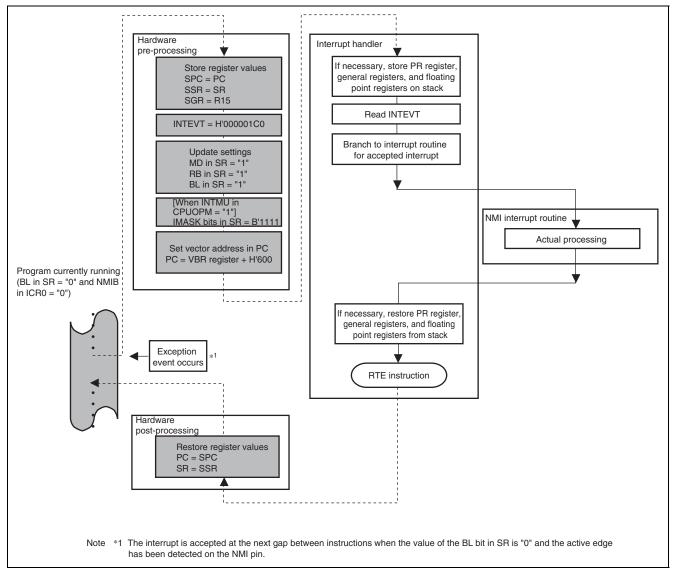

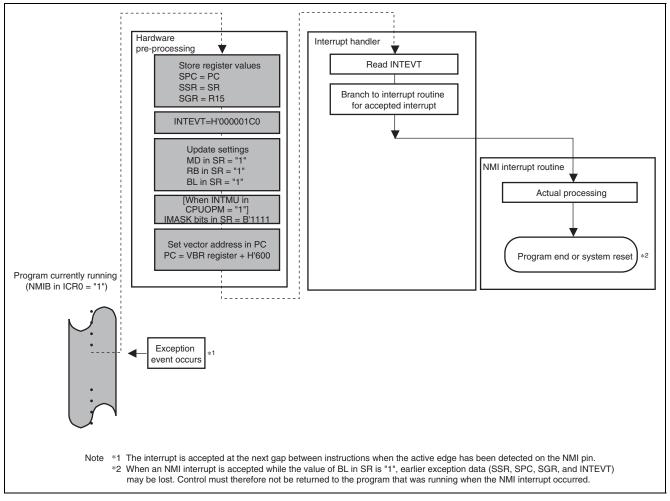

|       | 15.4.3    | NMI Interrupt Operation Sequence                                      | 15-58  |

| 15.5  | Interrup  | t Response Time                                                       |        |

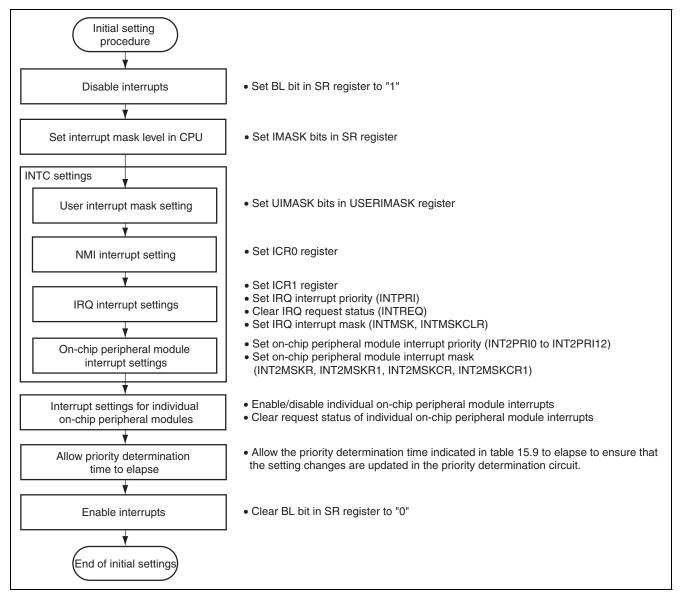

| 15.6  | -         | etting Procedure Example                                              |        |

| 15.7  |           | Notes                                                                 |        |

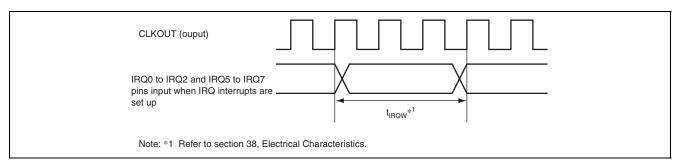

|       | 15.7.1    | Notes on Setting IRQ Pin Function                                     |        |

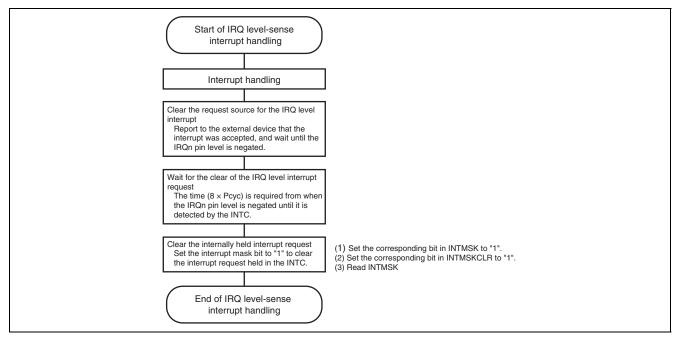

|       | 15.7.2    | To Clear IRQ Interrupt Requests When Level Detection is Selected      |        |

|       | 15.7.3    | To Clear IRQ Interrupt Requests When Edge Detection is Selected       |        |

| Secti | on 16     | Reset                                                                 | 16-1   |

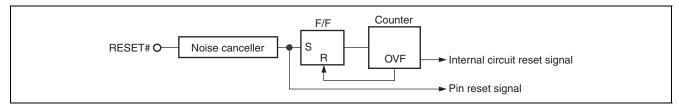

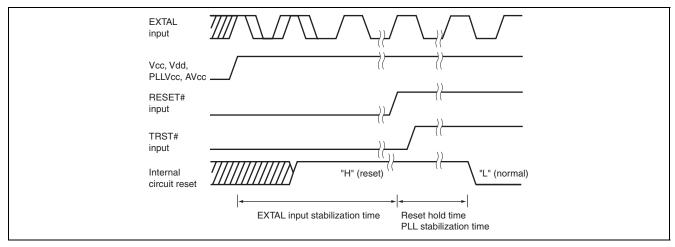

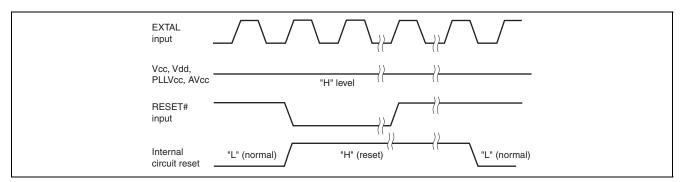

| 16.1  |           | peration                                                              |        |

| 16.2  |           | utput Pins                                                            |        |

| 16.3  | -         | On                                                                    |        |

|       | 16.3.1    | Reset Request                                                         |        |

|       | 16.3.2    | Reset with the RESET# Pin                                             |        |

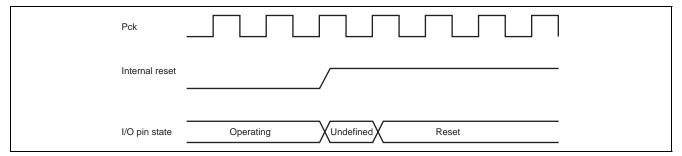

| 16.4  |           | Notes                                                                 |        |

|       | 16.4.1    | Usage Notes Regarding Internal Reset                                  |        |

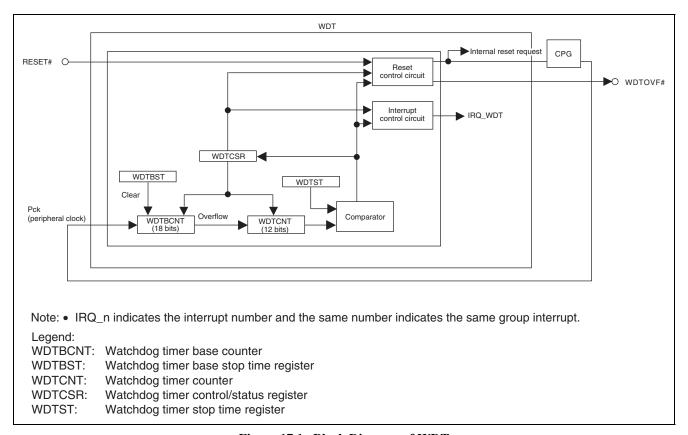

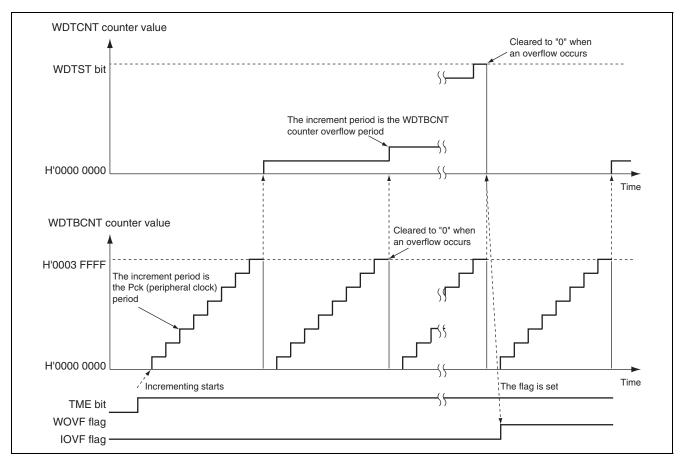

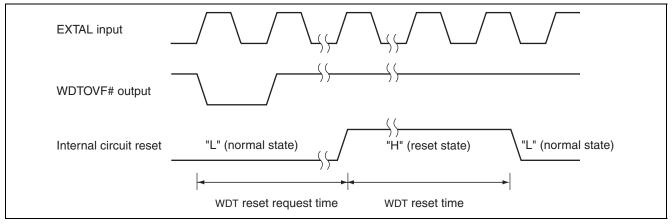

| Secti | ion 17    | Watchdog Timer (WDT)                                                  | 17-1   |

| 17.1  |           | w                                                                     |        |

| 17.2  |           | utput Pins                                                            |        |

| 17.3  | -         | Descriptions                                                          |        |

|       | 17.3.1    | Watchdog Timer Stop Time Register (WDTST)                             |        |

|       | 17.3.2    | Watchdog Timer Control/Status Register (WDTCSR)                       |        |

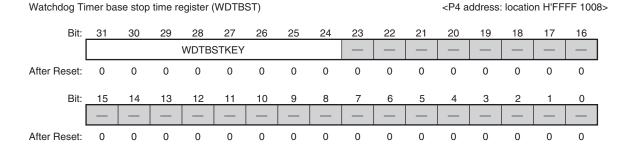

|       | 17.3.3    | Watchdog Timer Base Stop Time Register (WDTBST)                       |        |

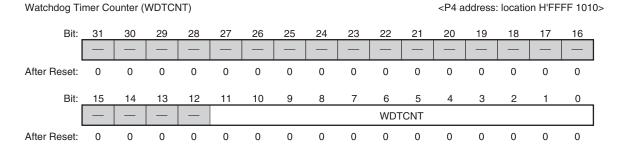

|       | 17.3.4    | Watchdog Timer Counter (WDTCNT)                                       |        |

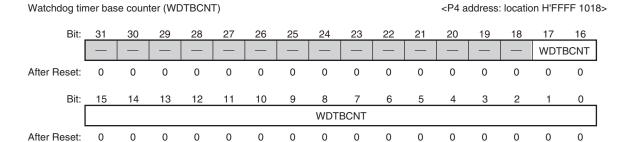

|       | 17.3.5    | Watchdog Timer Base Counter (WDTBCNT)                                 |        |

| 17.4  |           | On                                                                    |        |

| . /   | 17.4.1    | Using Watchdog Timer Mode                                             |        |

|       | 17.4.1    | Using Interval Timer Mode                                             |        |

|       | 17.4.3    | Time Until a WDT Overflow Occurs                                      |        |

|       | 17.4.4    | Clearing the WDT Counter                                              |        |

|       | 17.4.5    | Hardware Reset due to WDT Overflow                                    |        |

| Secti | on 18     | I/O Ports and Pin Function Unit                                       | 18_1   |

| 18.1  |           | W                                                                     |        |

| 18.2  |           | ex Pin Functions                                                      |        |

| 18.3  | -         | Descriptions                                                          |        |

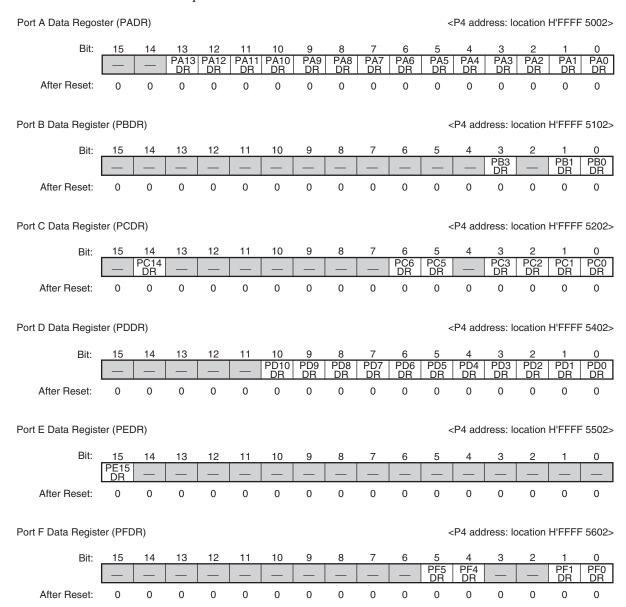

| 10.5  | 18.3.1    | Port A to H and J to L Data Registers (PADR to PHDR and PJDR to PLDR) |        |

|       | 18.3.2    | Port A to H and J to N Port Registers (PAPR to PHPR and PJPR to PNPR) |        |

|       | 18.3.3    | Port A to H and J to L Driving Ability Setting Registers              | 10-13  |

|       | 10.3.3    | (PADSR to PHDSR and PJDSR to PLDSR)                                   | 10 10  |

|       | 18.3.4    | Port ABC Input Threshold Value Switching Register (PALVR)             |        |

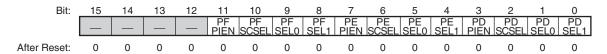

|       | 18.3.5    | Port DEF Input Threshold Value Switching Register (PDLVR)             |        |

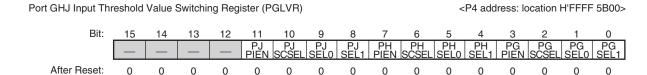

|       | 18.3.6    | Port GHJ Input Threshold Value Switching Register (PGLVR)             |        |

|       | 10.5.0    | TOTA OTTS HIDRET HICSHOID VALUE SWILCHIER NERRIGIE (FULVA)            | 10-4.) |

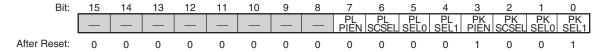

|      | 18.3.7           | Port KL Input Threshold Value Switching Register (PKLVR)                   | 18-26 |

|------|------------------|----------------------------------------------------------------------------|-------|

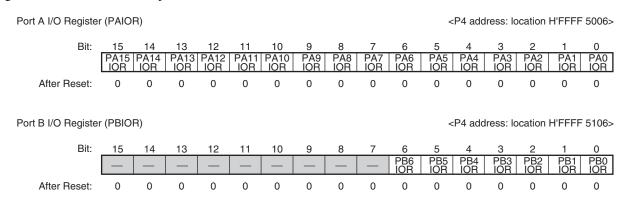

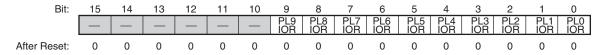

|      | 18.3.8           | Port A to H and J to L I/O Registers (PAIOR to PHIOR and PJIOR to PLIOR)   | 18-27 |

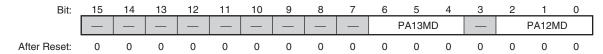

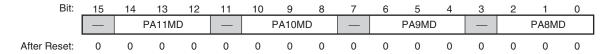

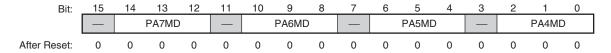

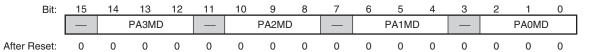

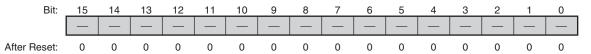

|      | 18.3.9           | Port A Control Registers 1 to 4 (PACR1 to PACR4)                           | 18-30 |

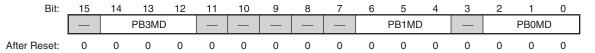

|      | 18.3.10          | Port B Control Registers 1 and 2 (PBCR1 and PBCR2)                         | 18-34 |

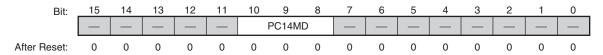

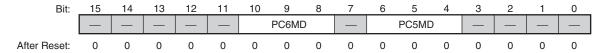

|      | 18.3.11          | Port C Control Registers 1 to 4 (PCCR1 to PCCR4)                           | 18-36 |

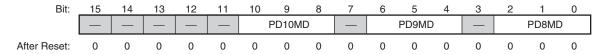

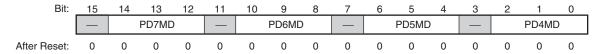

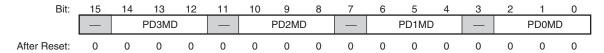

|      | 18.3.12          | Port D Control Registers 1 to 4 (PDCR1 to PDCR4)                           | 18-39 |

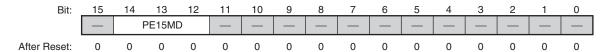

|      | 18.3.13          | Port E Control Registers 3 and 4 (PECR3 and PECR4)                         | 18-43 |

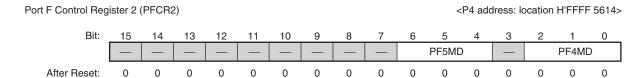

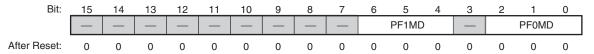

|      | 18.3.14          | Port F Control Registers 1 and 2 (PFCR1 and PFCR2)                         |       |

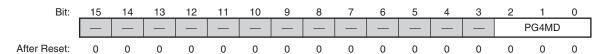

|      | 18.3.15          | Port G Control Registers 1 and 2 (PGCR1 and PGCR2)                         |       |

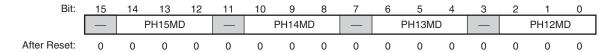

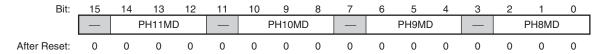

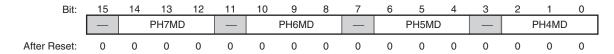

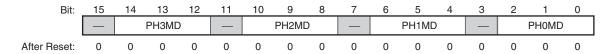

|      | 18.3.16          | Port H Control Registers 1 to 4 (PHCR1 to PHCR4)                           | 18-48 |

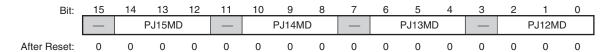

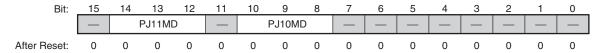

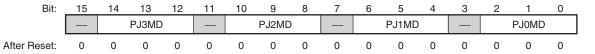

|      | 18.3.17          | Port J Control Registers 1 to 4 (PJCR1 to PJCR4)                           |       |

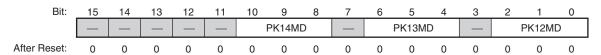

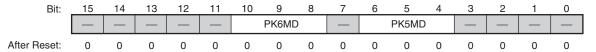

|      | 18.3.18          | Port K Control Registers 1 to 4 (PKCR1 to PKCR4)                           | 18-57 |

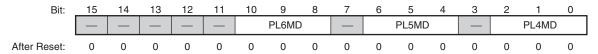

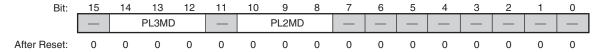

|      | 18.3.19          | Port L Control Registers 1 to 3 (PLCR1 to PLCR3)                           | 18-61 |

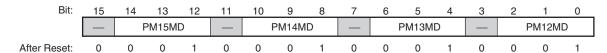

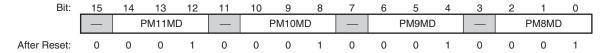

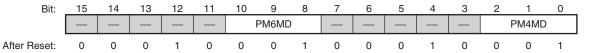

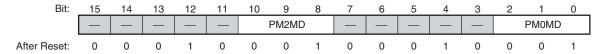

|      | 18.3.20          | Port M Control Registers 1 to 4 (PMCR1 to PMCR4)                           |       |

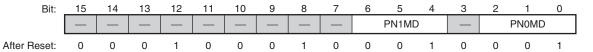

|      | 18.3.21          | Port N Control Registers 1 and 2 (PNCR1 and PNCR2)                         |       |

|      | 18.3.22          | Port DRI Input Channel Switching Register (PDRIR)                          | 18-70 |

| 18.4 | I/O Port         | Initial Setting Procedure Examples                                         | 18-71 |

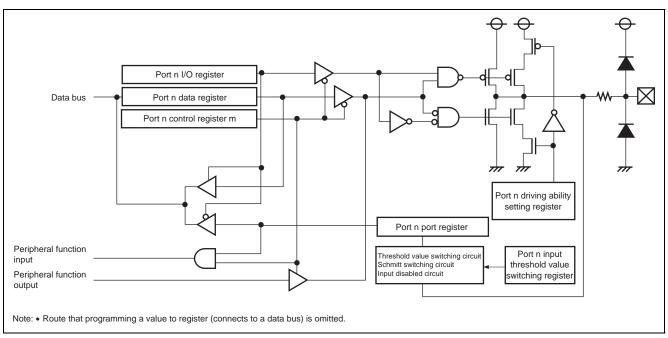

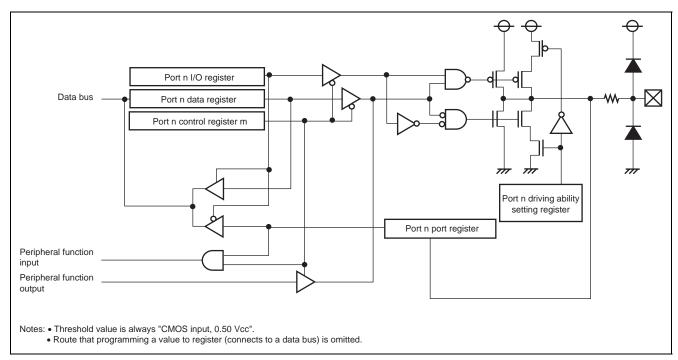

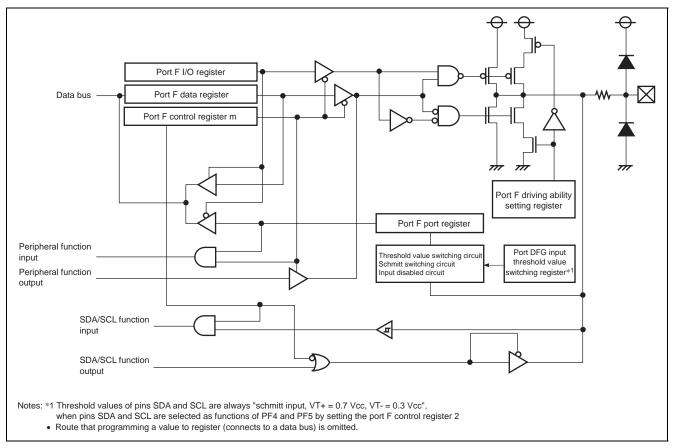

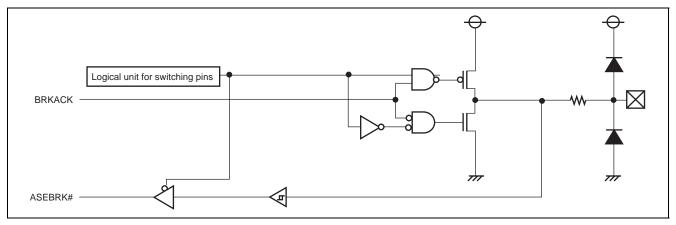

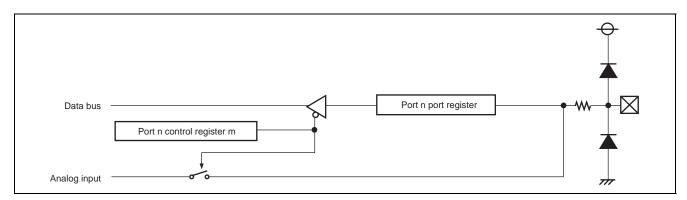

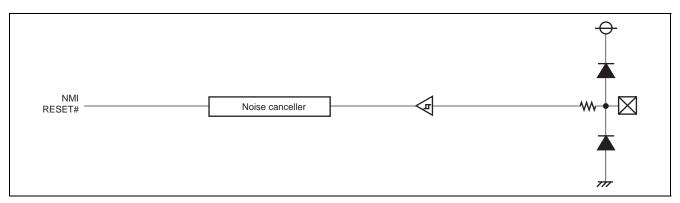

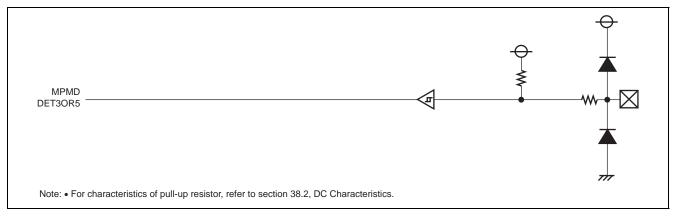

| 18.5 | Port Peri        | pheral Circuits                                                            | 18-73 |

| 18.6 | Usage N          | otes                                                                       | 18-79 |

|      | 18.6.1           | Port Input Disable Function                                                | 18-79 |

|      | 18.6.2           | Peripheral Function Input When Pins are Set as General Port Pins           | 18-79 |

|      | 18.6.3           | I/O Port Initial Setting                                                   | 18-79 |

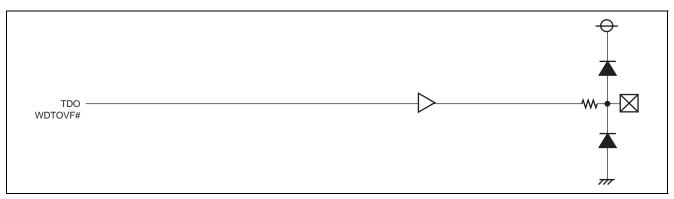

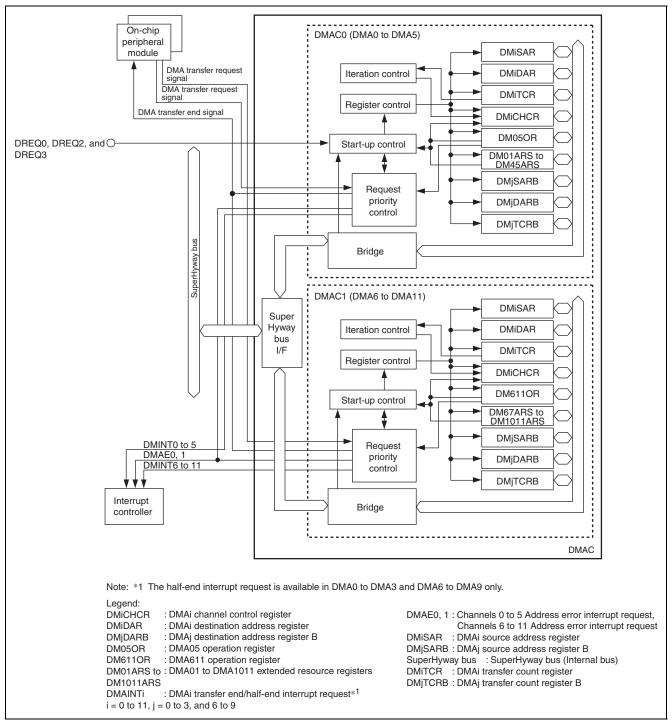

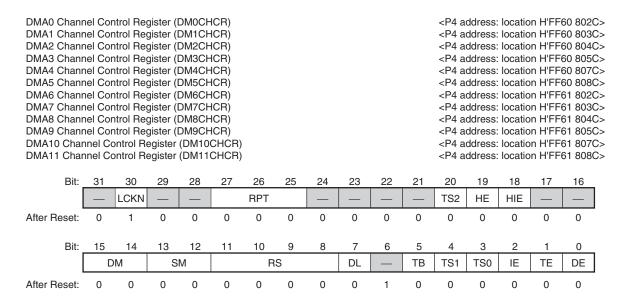

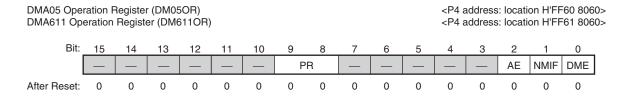

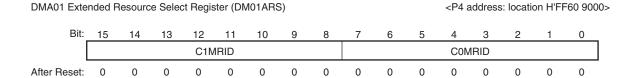

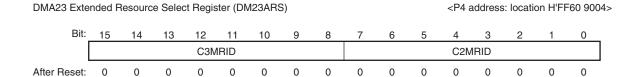

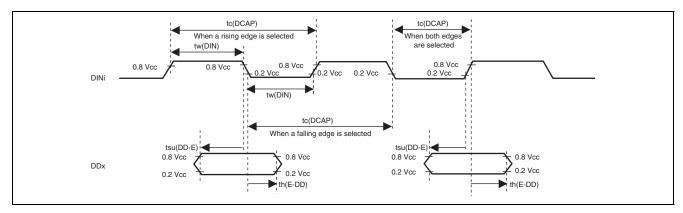

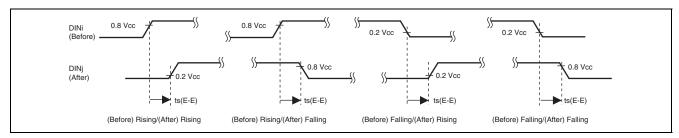

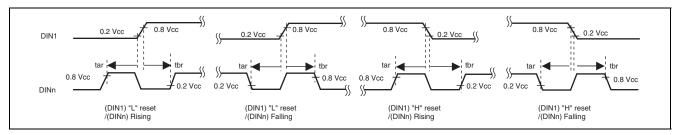

| 20.1 | Overview         | Direct Memory Access Controller (DMAC)                                     | 20-1  |

| 20.2 | -                | ntput Pins                                                                 |       |

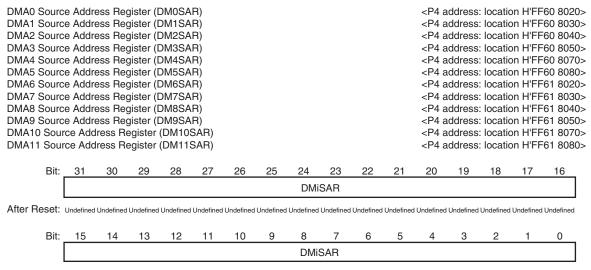

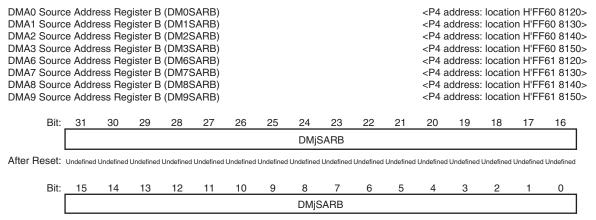

| 20.3 | _                | Descriptions (DMSAP)                                                       |       |

|      | 20.3.1           | DMAi Source Address Register (DMiSAR)                                      |       |

|      | 20.3.2           | DMAj Source Address Register B (DMjSARB)                                   |       |

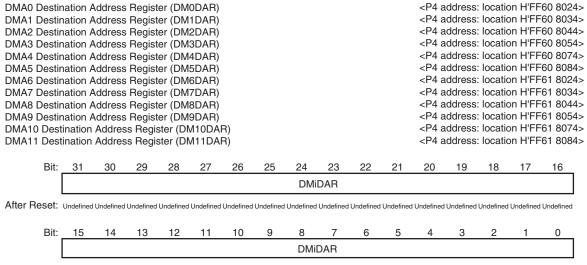

|      | 20.3.3           | DMAi Destination Address Register (DMiDAR)                                 |       |

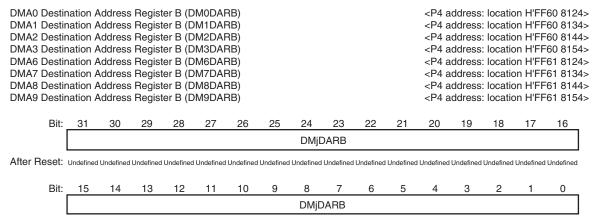

|      | 20.3.4           | DMAj Destination Address Register B (DMjDARB)                              |       |

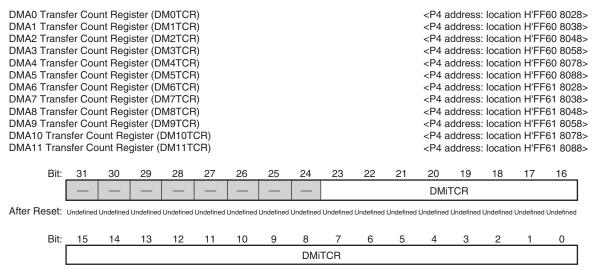

|      | 20.3.5           | DMAi Transfer Count Register (DMiTCR)                                      |       |

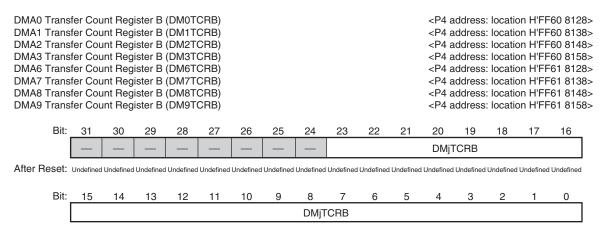

|      | 20.3.6           | DMAj Transfer Count Register B (DMjTCRB)                                   | 20-13 |

|      | 20.3.7           | DMAi Channel Control Register (DMiCHCR)                                    |       |

|      | 20.3.8           | DMA05 and DMA611 Operation Registers (DM05OR and DM611OR)                  |       |

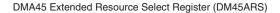

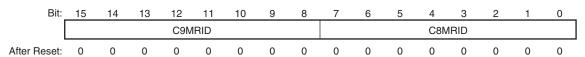

| 20.4 | 20.3.9           | DMA01 to DMA1011 Extended Resource Select Registers (DM01ARS to DM1011ARS) |       |

| 20.4 | -                | DMA Transfer Dequest Sources                                               |       |

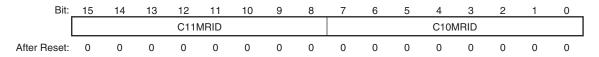

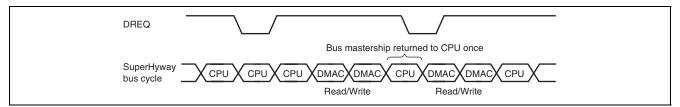

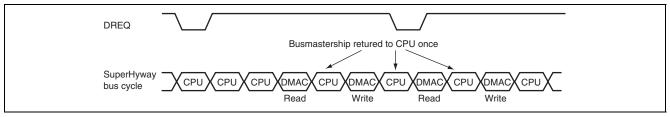

|      | 20.4.1<br>20.4.2 | DMA Transfer Request Sources  DMA Transfer Modes                           |       |

|      | 20.4.2           | DMA Transfer Modes                                                         |       |

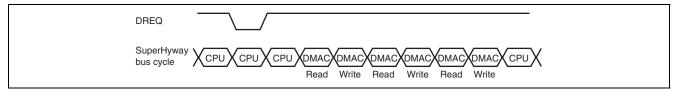

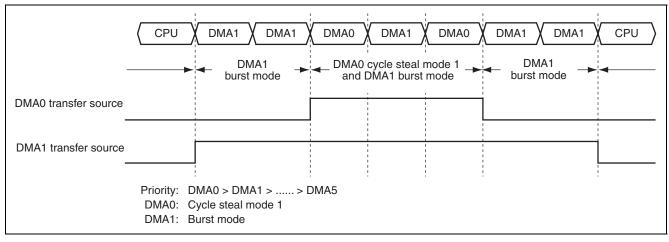

|      | 20.4.3           | Channel Priority in Modules                                                |       |

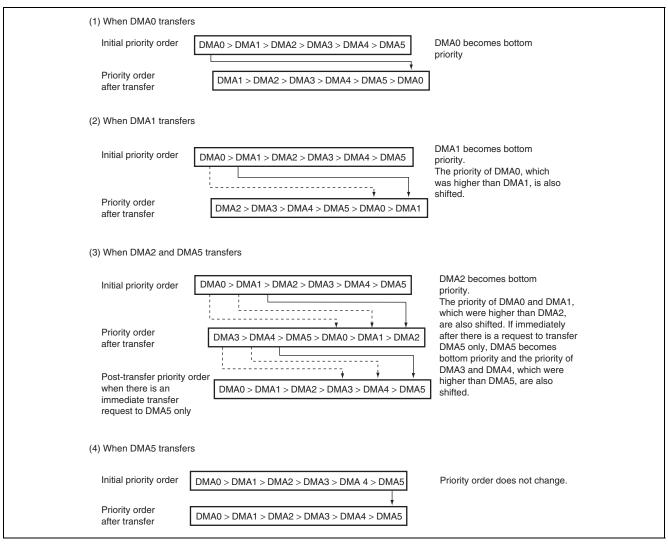

|      | 20.4.4           | Operation Example of Multiple Channels in the Same DMAC Module             |       |

|      |                  |                                                                            |       |

|      | 20.4.6           | Priority between DMAC Modules                                              |       |

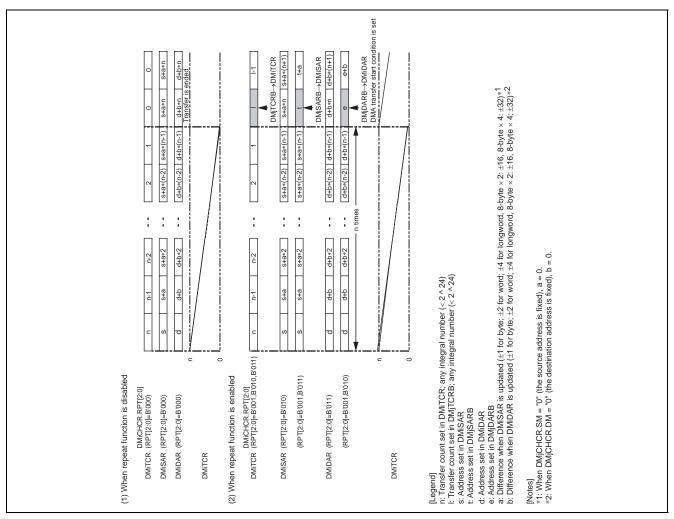

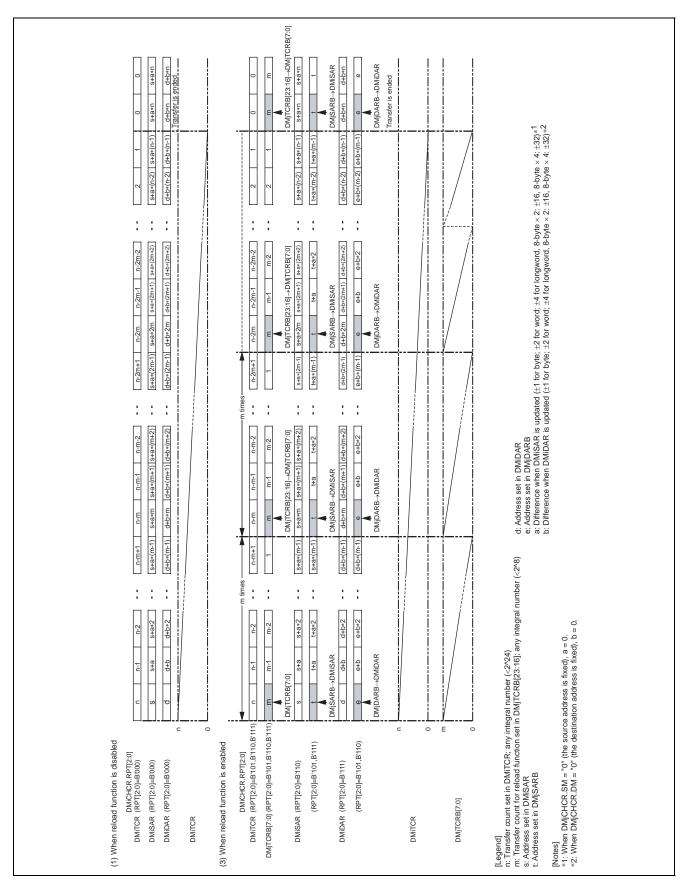

|      | 20.4.7<br>20.4.8 | Reload Function                                                            |       |

| 20.5 |                  | otes                                                                       |       |

| 20.3 | 20.5.1           | Address Error                                                              |       |

|      | 20.5.1           | DMA Transfer to DMAC Prohibited                                            |       |

|      | 20.5.3           | NMI Interrupt                                                              |       |

|      | -3.5.5           |                                                                            |       |

|         | 20.5.4   | Accessing Registers during DMA Operation                              | 20-41 |

|---------|----------|-----------------------------------------------------------------------|-------|

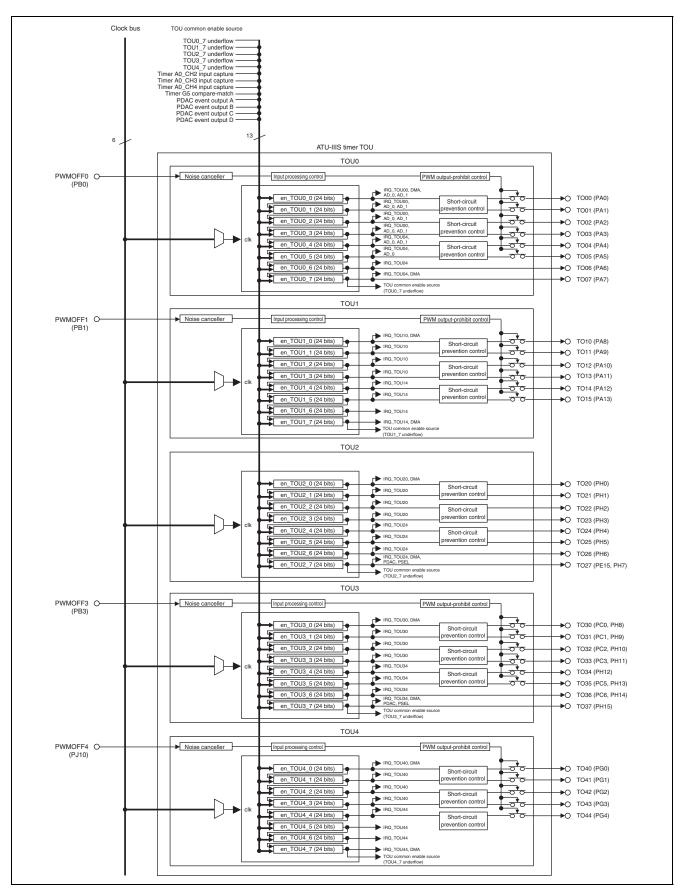

| Section | on 21 A  | Advanced Timer Unit IIIS (ATU-IIIS)                                   | 21-1  |

| 21.1    |          | W                                                                     |       |

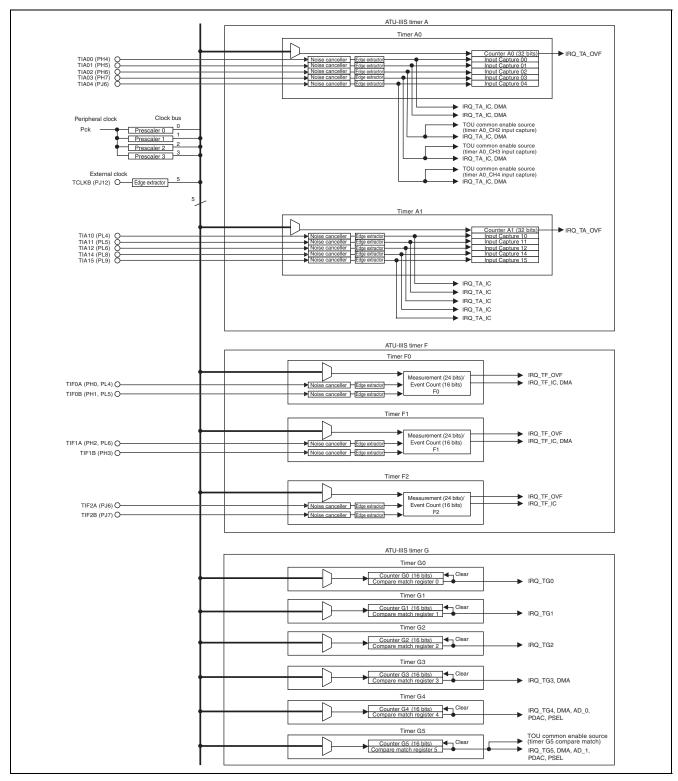

| 21.2    |          | iagram                                                                |       |

| 21.3    |          | utput Pins                                                            |       |

| 21.4    | -        | Descriptions                                                          |       |

| 21.5    | _        | w of Common Controller                                                |       |

|         | 21.5.1   | Clock Bus.                                                            |       |

| 21.6    |          | Description of Common Controller                                      |       |

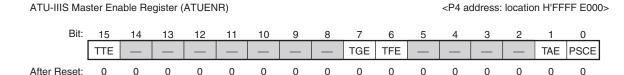

|         | 21.6.1   | ATU-IIIS Master Enable Register (ATUENR)                              |       |

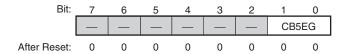

|         | 21.6.2   | ATU-IIIS Clock Bus Control Register (ATCBCNT)                         |       |

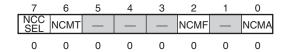

|         | 21.6.3   | ATU-IIIS Noise Cancellation Mode Register (ATNCMR)                    |       |

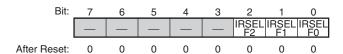

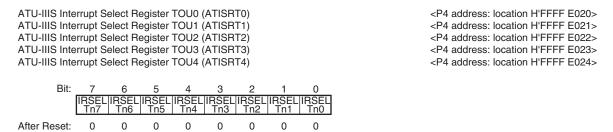

|         | 21.6.4   | ATU-IIIS Interrupt Select Register Ai (ATISRAi)                       |       |

|         | 21.6.5   | ATU-IIIS Interrupt Select Register F (ATISRF)                         |       |

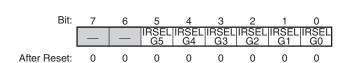

|         | 21.6.6   | ATU-IIIS Interrupt Select Register G (ATISRG)                         |       |

|         | 21.6.7   | ATU-IIIS Interrupt Select Registers TOU0 to TOU4 (ATISRT0 to ATISRT4) |       |

| 21.7    |          | w of Prescalers                                                       |       |

| 21.7    |          | Description of Prescalers                                             |       |

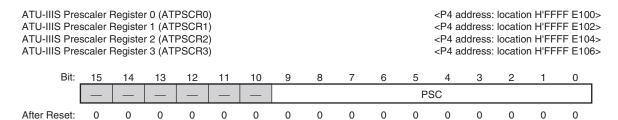

| 21.0    | 21.8.1   | ATU-IIIS Prescaler Registers 0 to 3 (ATPSCR0 to ATPSCR3)              |       |

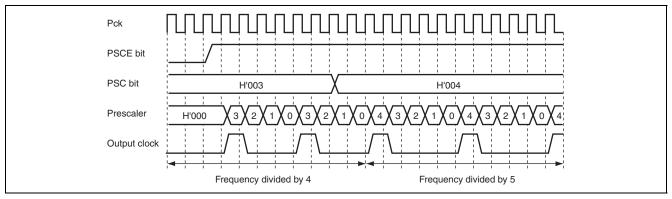

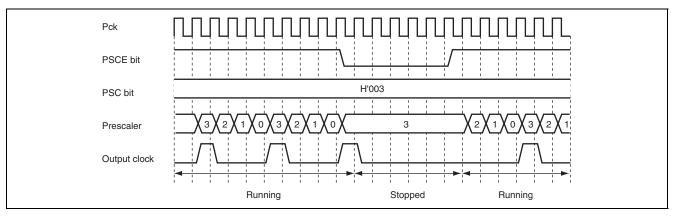

| 21.9    |          | on of Prescalers                                                      |       |

| 21.9    | 21.9.1   | Starting Prescalers                                                   |       |

|         | 21.9.1   | Stopping and Restarting Operation                                     |       |

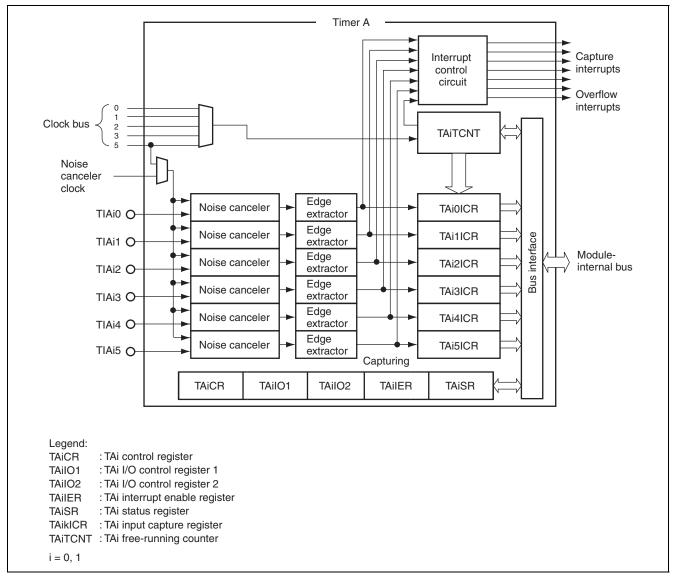

| 21.10   |          | w of Timer A                                                          |       |

| 21.10   |          |                                                                       |       |

| 01 11   |          | Block Diagram                                                         |       |

| 21.11   | •        | ion of Timer A Registers                                              |       |

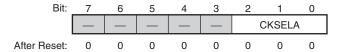

|         | 21.11.1  | TAI Control Register (TAiCR)                                          |       |

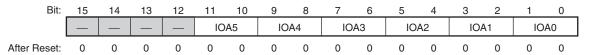

|         | 21.11.2  | TAil/O Control Register 1 (TAiIO1)                                    |       |

|         | 21.11.3  | TAil/O Control Register 2 (TAiIO2)                                    |       |

|         | 21.11.4  | TAi Status Register (TAiSR)                                           |       |

|         | 21.11.5  | TAi Interrupt Enable Register (TAiIER)                                |       |

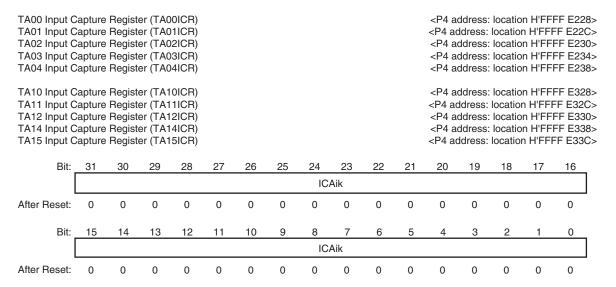

|         | 21.11.6  | TAik Input Capture Register (TAikICR)                                 |       |

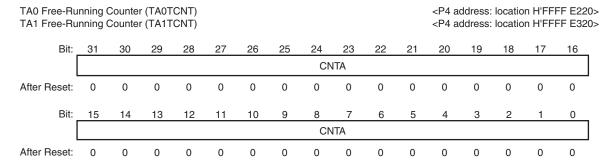

|         | 21.11.7  | TAi Free-Running Counter (TAiTCNT)                                    |       |

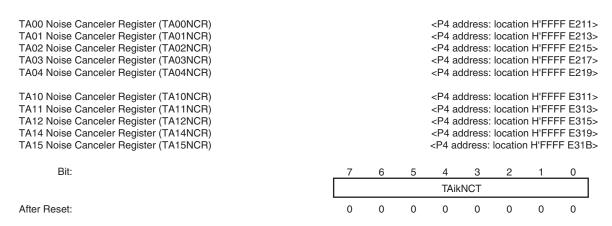

|         | 21.11.8  | TAik Noise Canceler Counter (TAikNCNT)                                |       |

|         | 21.11.9  | TAik Noise Canceler Register (TAikNCR)                                | 21-44 |

| 21.12   | -        | ons of Timer A                                                        |       |

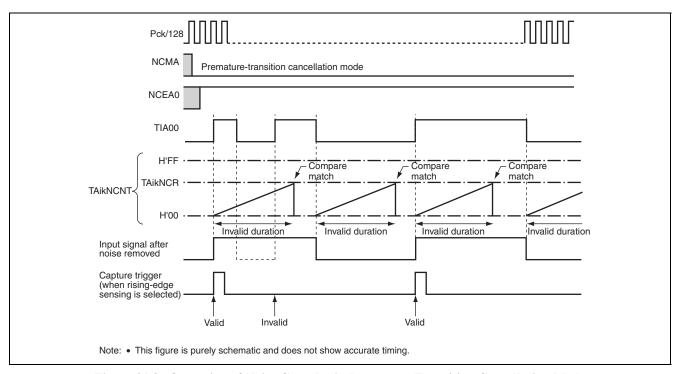

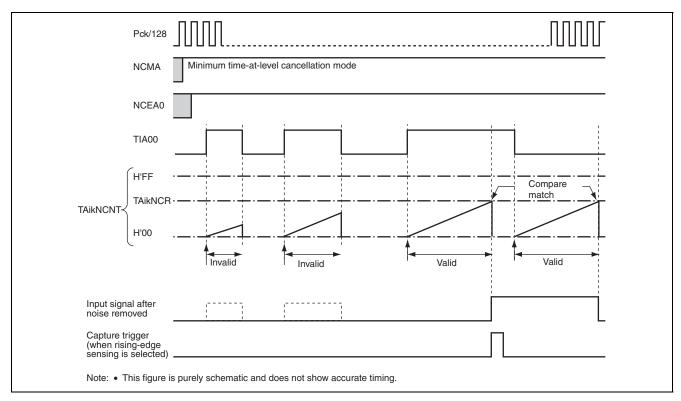

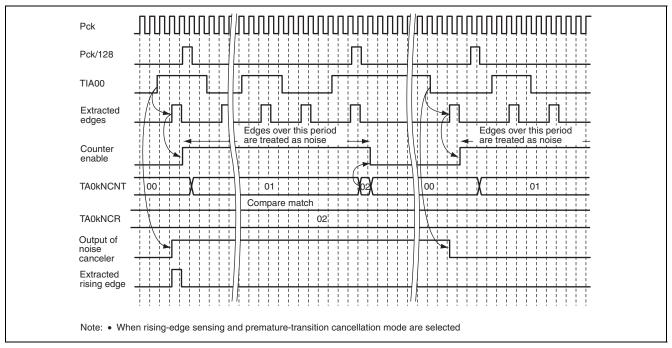

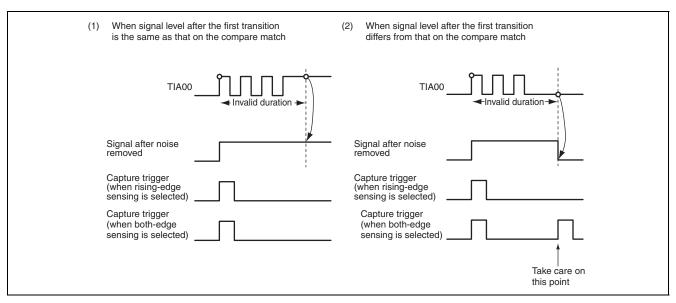

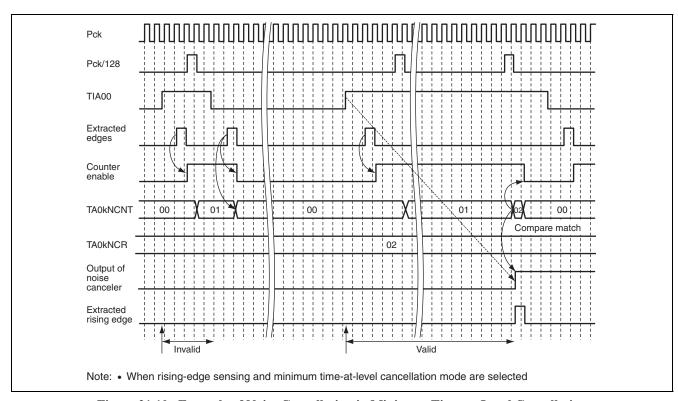

|         |          | Operation of Noise Canceler                                           |       |

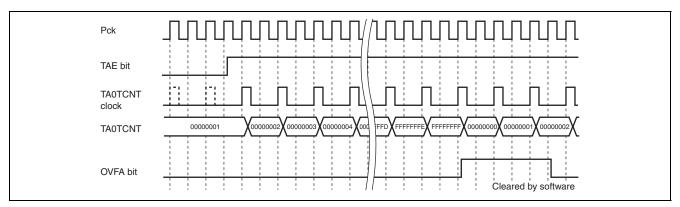

|         | 21.12.2  | Operation of Free-Running Counter                                     |       |

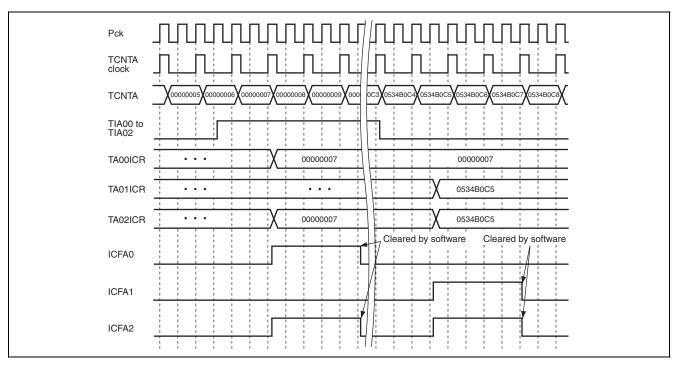

|         | 21.12.3  | Input Capture                                                         |       |

|         | 21.12.4  | DMA Transfer                                                          |       |

| 21.13   | Overvie  | w of Timer F                                                          |       |

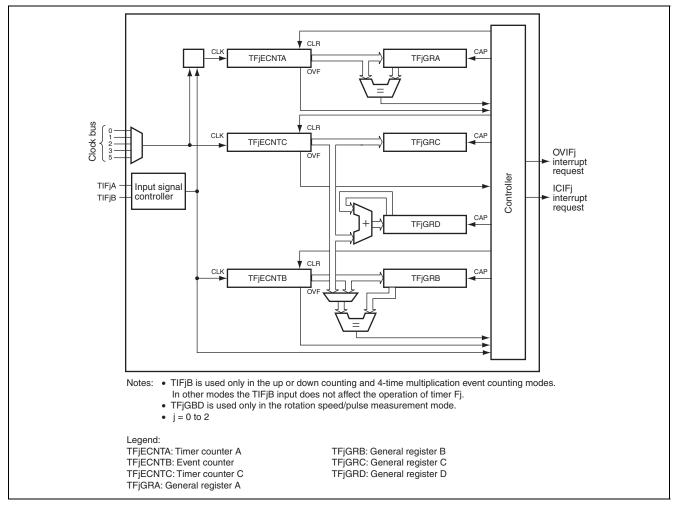

|         | 21.13.1  | Block Diagram                                                         | 21-50 |

|         | 21.13.2  | Interrupts                                                            |       |

| 21.14   | Descript | ion of Timer F Registers                                              |       |

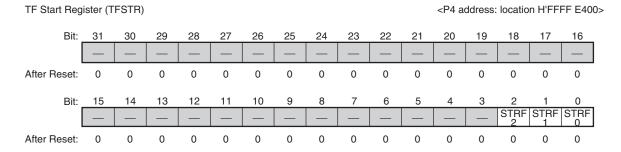

|         | 21.14.1  | TF Start Register (TFSTR)                                             | 21-52 |

|         | 21.14.2  | TF Noise Canceller Control Register (TFNCCR)                          | 21-53 |

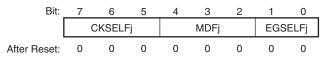

|         | 21.14.3  | TFj Control Register (TFjCR)                                          |       |

|         | 21.14.4  | TFj Interrupt Enable Register (TFjIER)                                | 21-57 |

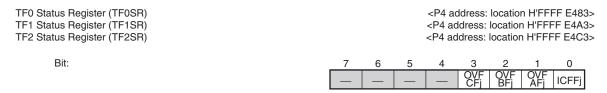

|         | 21.14.5  | TFj Status Register (TFjSR)                                           | 21-58 |

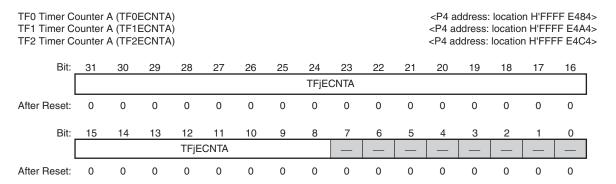

|         | 21.14.6  | TFj Timer Counter A (TFjECNTA)                                        | 21-60 |

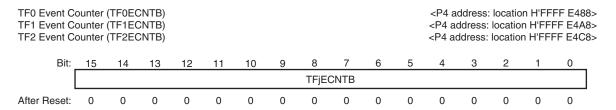

|         | 21.14.7  | TFj Event Counter (TFjECNTB)                                          | 21-61 |

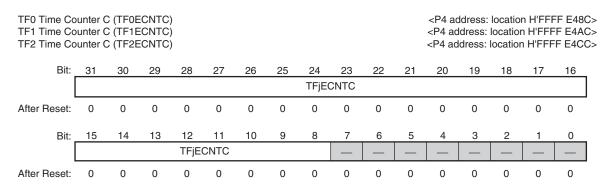

|       | 21.14.8   | TFj Timer Counter C (TFjECNTC)                                                           | 21-62  |

|-------|-----------|------------------------------------------------------------------------------------------|--------|

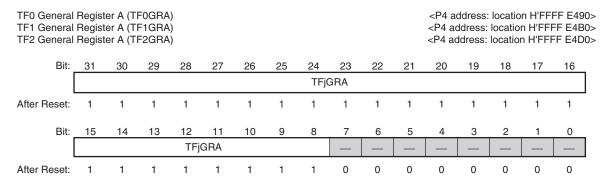

|       | 21.14.9   | TFj General Register A (TFjGRA)                                                          | 21-63  |

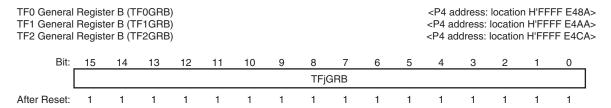

|       | 21.14.10  | TFj General Register B (TFjGRB)                                                          | 21-64  |

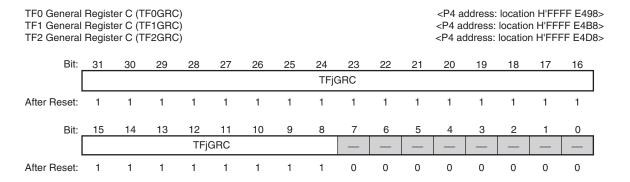

|       | 21.14.11  | TFj General Register C (TFjGRC)                                                          | 21-65  |

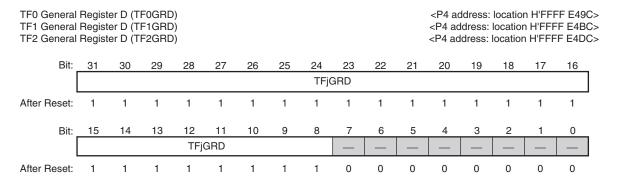

|       |           | TFj General Register D (TFjGRD)                                                          |        |

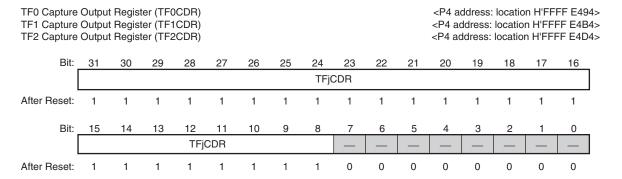

|       | 21.14.13  | TFj Capture Output Register (TFjCDR)                                                     | 21-67  |

|       | 21.14.14  | TFj Noise Canceler Counter A (TFjNCNTA)                                                  | 21-68  |

|       | 21.14.15  | TFj Noise Canceler Counter B (TFjNCNTB)                                                  | 21-69  |

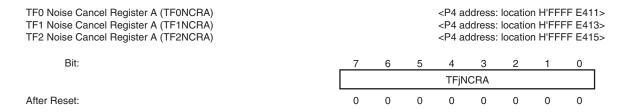

|       | 21.14.16  | TFj Noise Cancel Register A (TFjNCRA)                                                    | 21-71  |

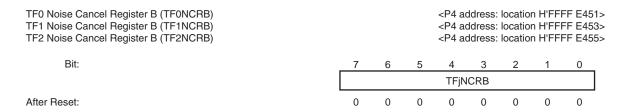

|       | 21.14.17  | TFj Noise Cancel Register B (TFjNCRB)                                                    | 21-72  |

| 21.15 | Operation | ns of Timer F                                                                            | 21-73  |

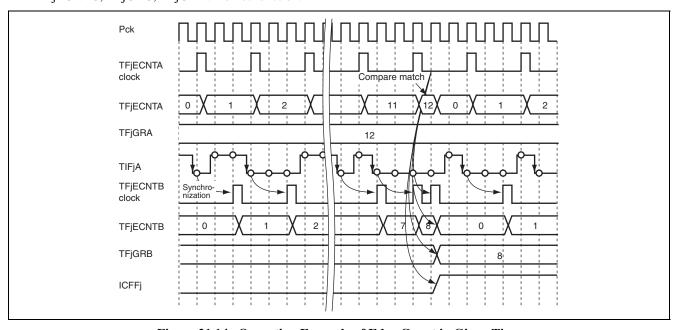

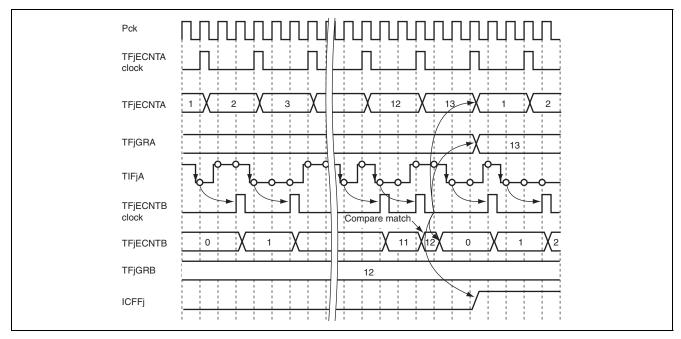

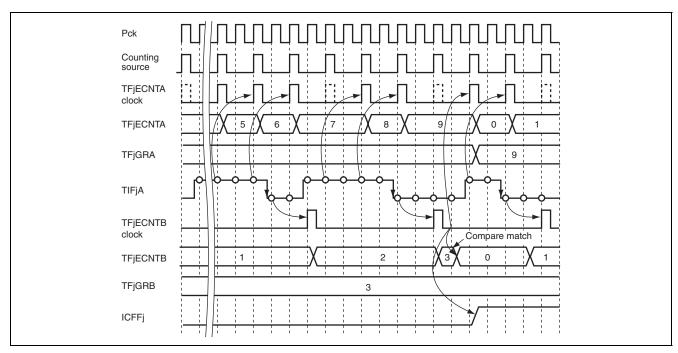

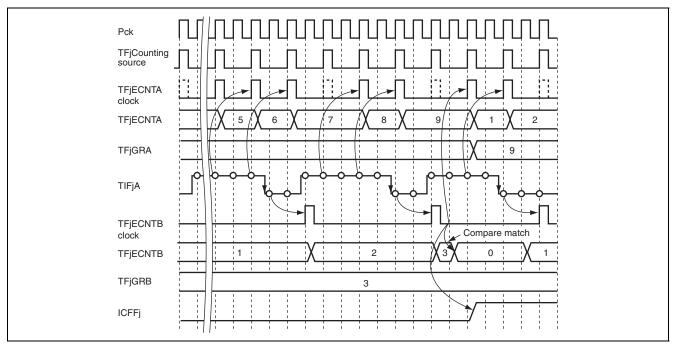

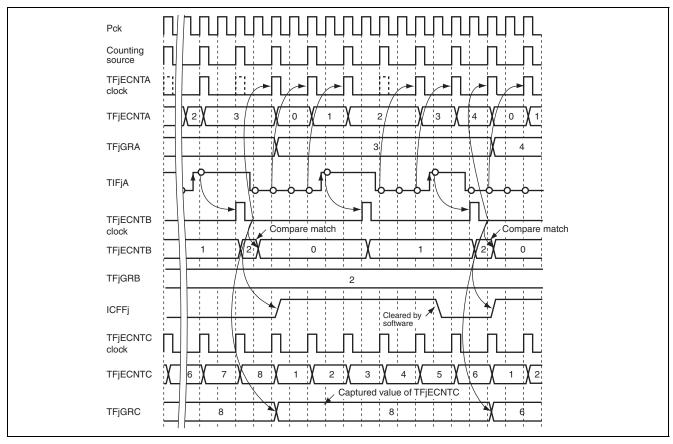

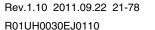

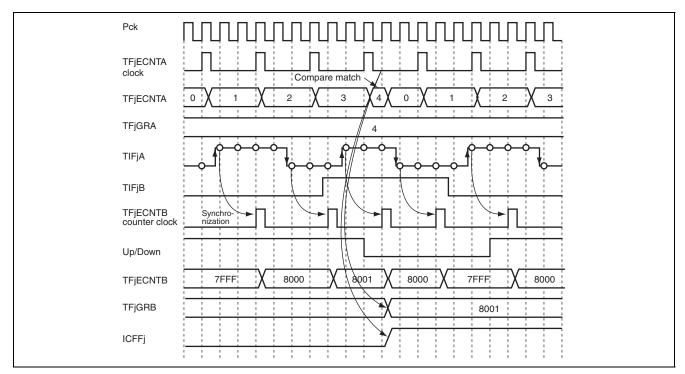

|       | 21.15.1   | Fixed-Period Edge Counting                                                               | 21-73  |

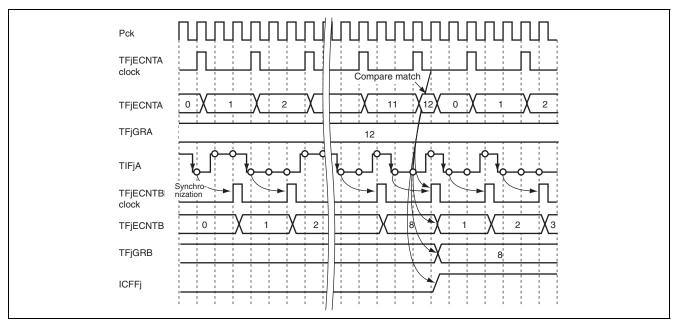

|       | 21.15.2   | Valid Edge Interval Counting                                                             | 21-74  |

|       | 21.15.3   | Measurement of Time during "H"/"L" Input Levels                                          | 21-75  |

|       | 21.15.4   | Measurement of PWM Input Waveform Timing                                                 |        |

|       | 21.15.5   | Rotation Speed/Pulse Measurement                                                         |        |

|       | 21.15.6   | Up/Down Event Count                                                                      |        |

|       |           | Four-time Multiplication Event Count                                                     |        |

|       | 21.15.8   | Overflow and Underflow                                                                   |        |

| 21 16 |           | of Timer G                                                                               |        |

| 21.10 | 21.16.1   | Block Diagram of Robots                                                                  |        |

|       | 21.16.2   | Interrupt Requests                                                                       |        |

| 21 17 |           | on of Timer G Registers                                                                  |        |

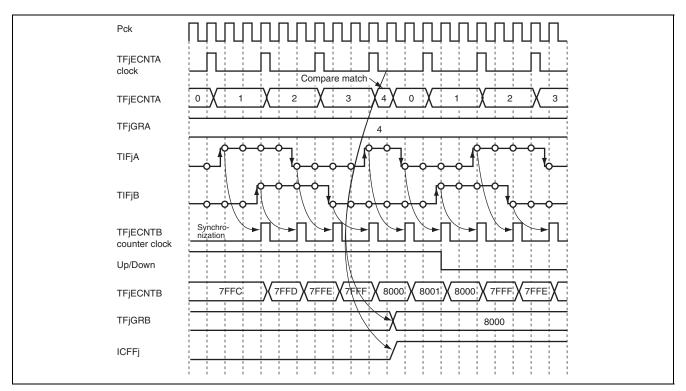

| 21.17 | -         | TG Start Register (TGSTR)                                                                |        |

|       |           | TGk Control Register (TGkCR)                                                             |        |

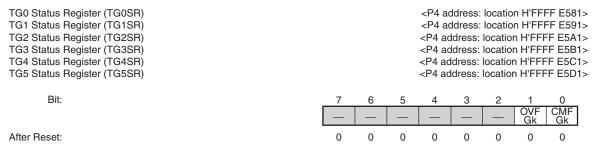

|       | 21.17.2   | TGk Status Register (TGkSR)                                                              |        |

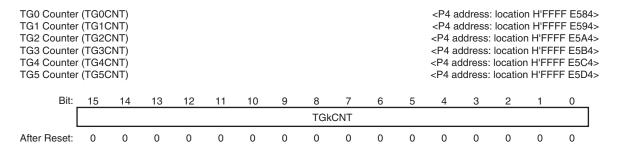

|       | 21.17.3   | TGk Counter (TGkCNT)                                                                     |        |

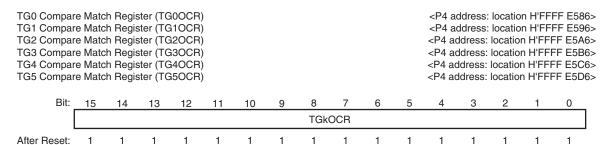

|       |           | TGk Compare Match Register (TGkOCR)                                                      |        |

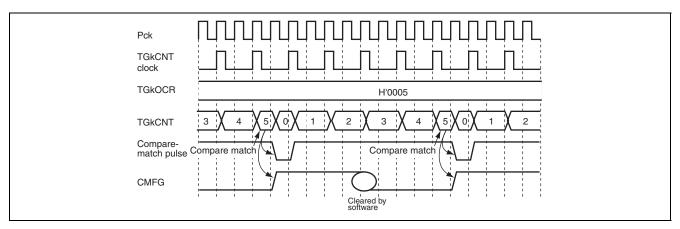

| 21 10 | 21.17.5   | ns of Timer G                                                                            |        |

|       | -         |                                                                                          |        |

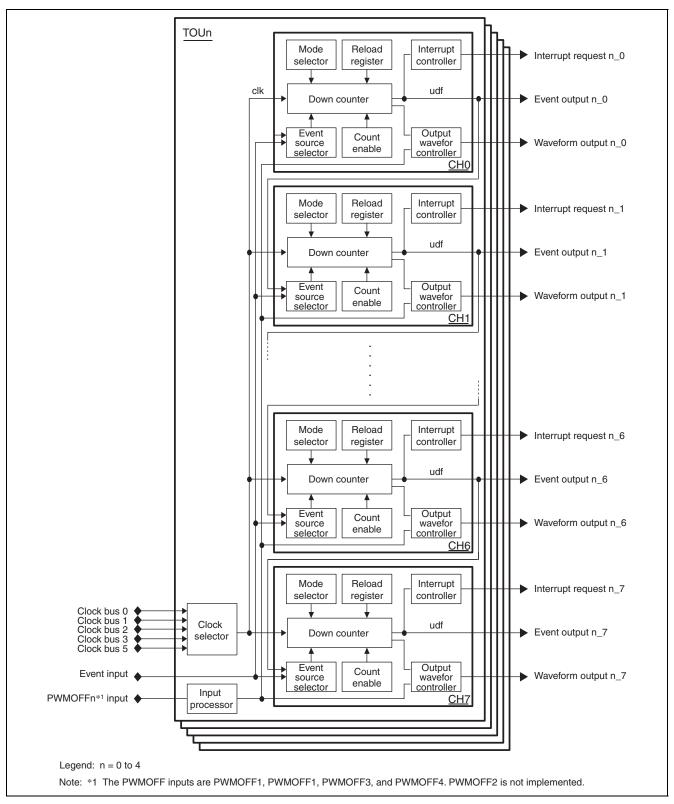

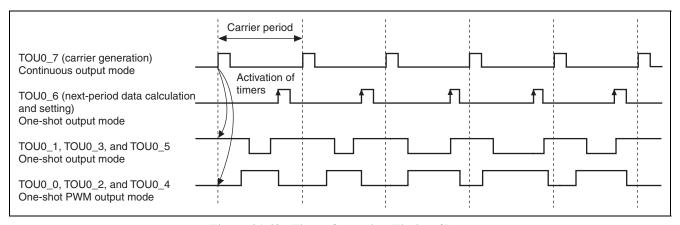

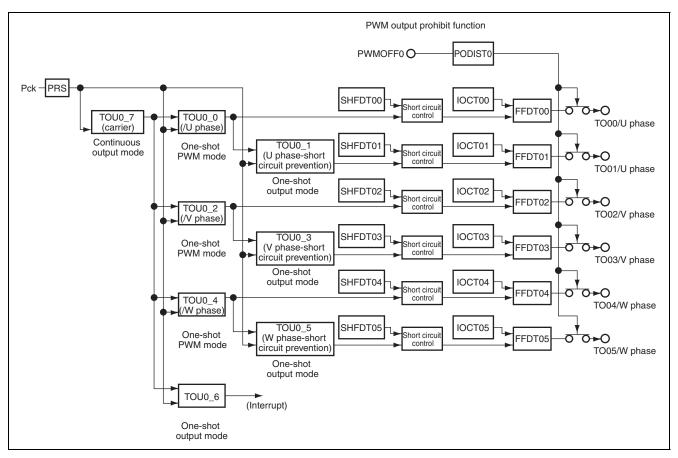

| 21.19 |           | of Timer TOU                                                                             |        |

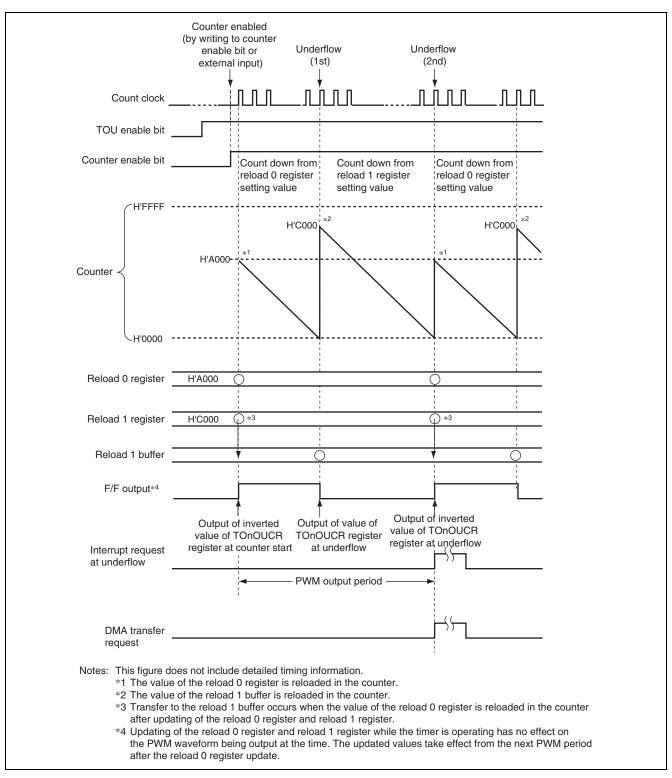

|       |           | Block Diagram                                                                            |        |

| 21.20 |           | Overview of Timer TOU Operating Modes                                                    |        |

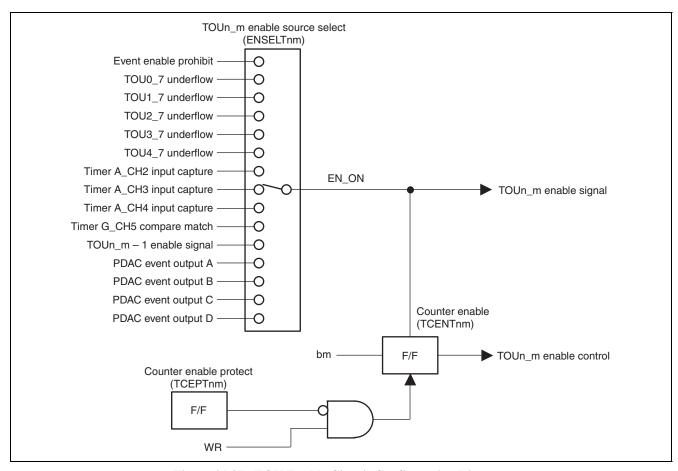

| 21.20 | -         | ons of Timer TOU Registers                                                               |        |

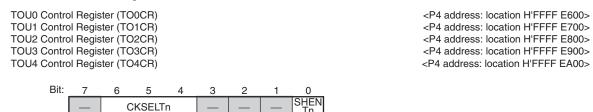

|       | 21.20.1   | TOUn Control Register (TOnCR)                                                            |        |

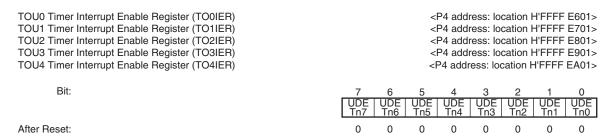

|       |           | TOUn Timer Interrupt Enable Register (TOnIER)                                            | 21-96  |

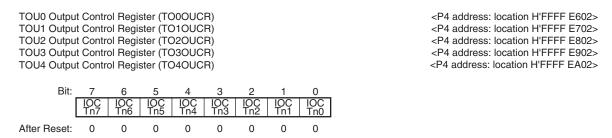

|       |           | TOUn Output Control Register (TOnOUCR)                                                   |        |

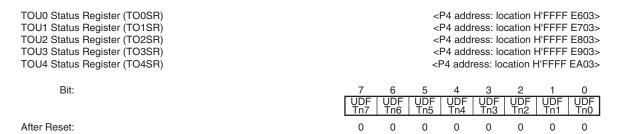

|       | 21.20.4   | TOUn Status Register (TOnSR)                                                             |        |

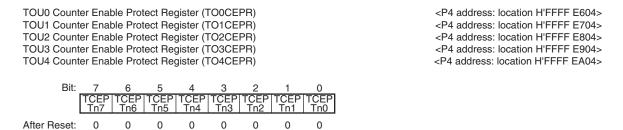

|       |           | TOUn Counter Enable Protect Register (TOnCEPR)                                           |        |

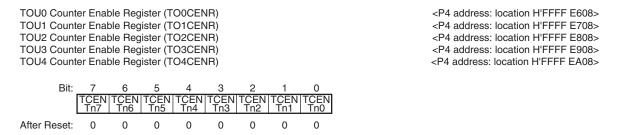

|       | 21.20.6   | TOUn Counter Enable Register (TOnCENR)                                                   | 21-100 |

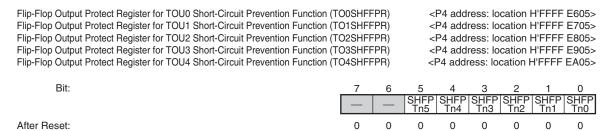

|       | 21.20.7   | Flip-Flop Output Protect Register for TOUn Short-Circuit Prevention Function (TOnSHFFPR) | 21-102 |

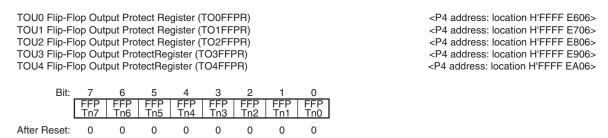

|       | 21.20.8   | Flip-Flop Output Data Register for TOUn Short-Circuit Prevention Function (TOnSHFFDR)    | 21-103 |

|       | 21.20.9   | TOUn Flip-Flop Output Protect Register (TOnFFPR)                                         |        |

|       |           | TOUn Flip-Flop Output Data Register (TOnFFDR)                                            |        |

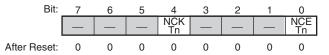

|       |           | TOUn Noise Canceler Control Register (TOnNCCR)                                           |        |

|       |           | TOUn Noise Canceler Counter (TOnNCNT)                                                    |        |

|       |           | TOUn Noise Canceler Register (TOnNCR)                                                    |        |

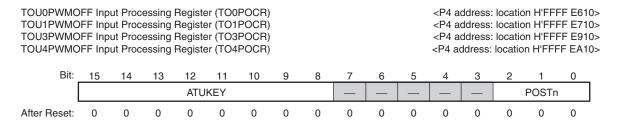

|       |           | TOUnPWMOFF Input Processing Register (TOnPOCR)                                           |        |

|       |           | TOUnPWMOFF Function Enable Register (TOnPOER)                                            |        |

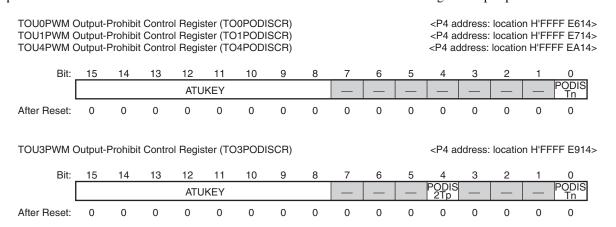

|       |           | TOUnPWM Output-Prohibit Control Register (TOnPODISCR)                                    |        |

|       | 21.20.10  | 100m 1111 Output-110mon Comon Register (10m ODISCR)                                      |        |

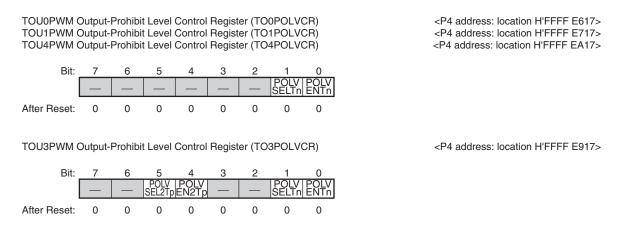

|       | 21.20.17    | TOUnPWM Output-Prohibit Level Control Register (TOnPOLVCR)   | 21-113 |

|-------|-------------|--------------------------------------------------------------|--------|

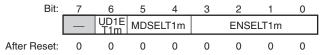

|       | 21.20.18    | TOUnm Mode Control Register (TOnmMCR)                        | 21-115 |

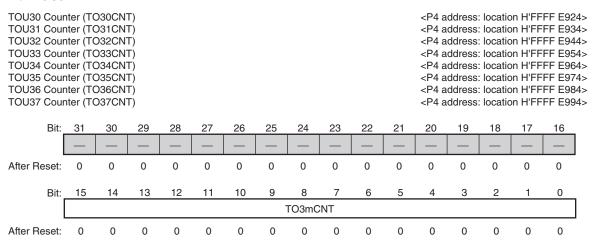

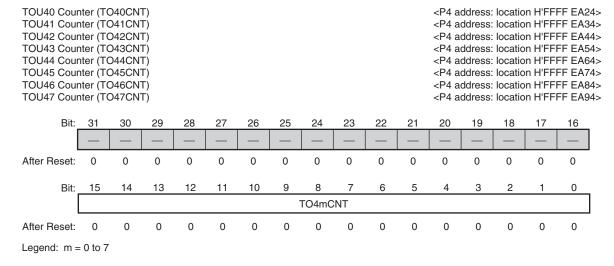

|       | 21.20.19    | TOUnm Counter (TOnmCNT)                                      | 21-117 |

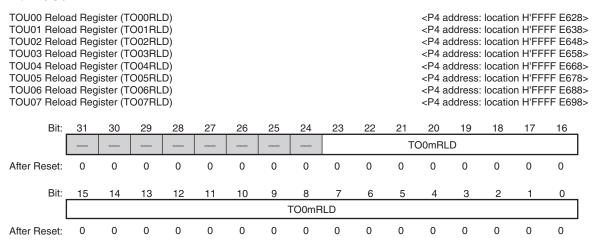

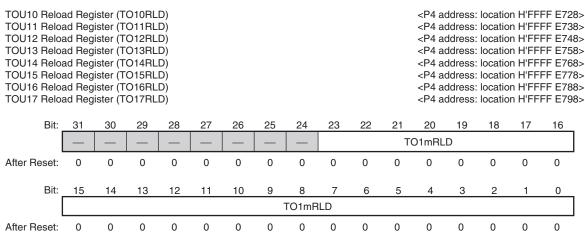

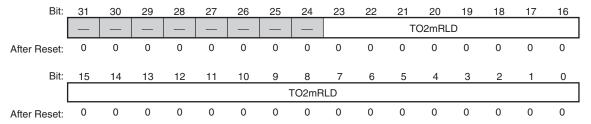

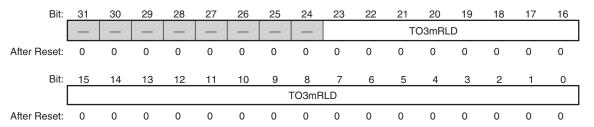

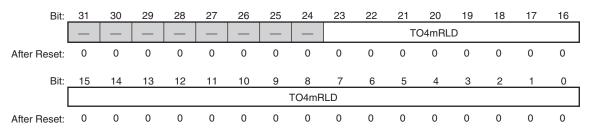

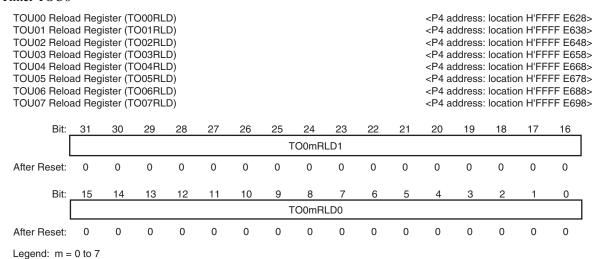

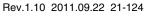

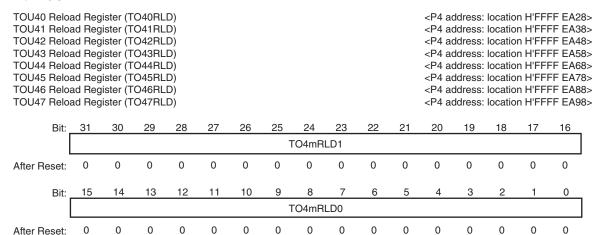

|       | 21.20.20    | TOUnm Reload Register (TOnmRLD)                              | 21-121 |

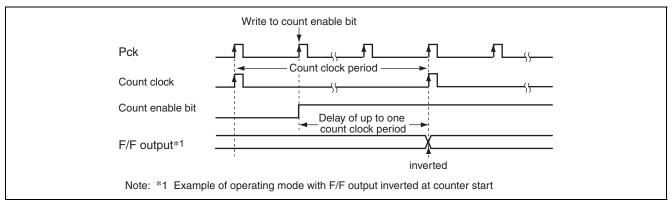

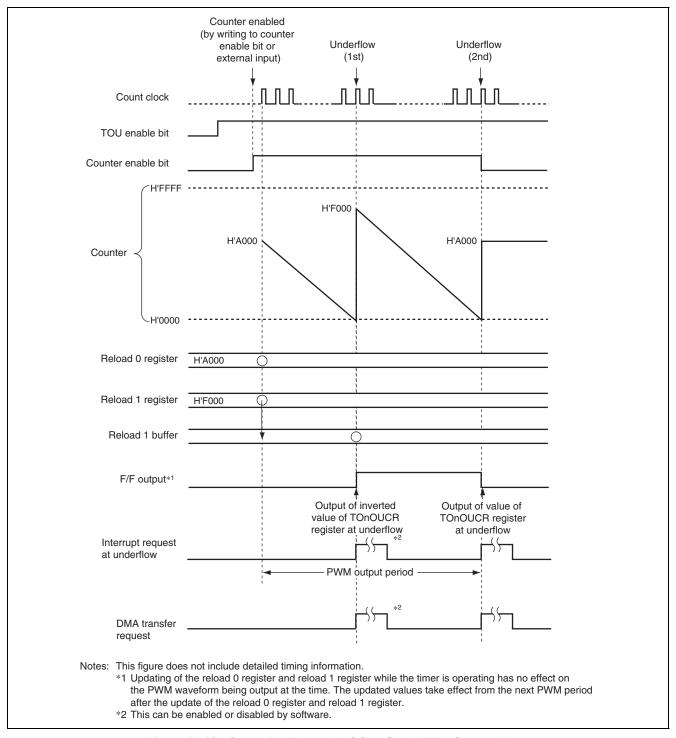

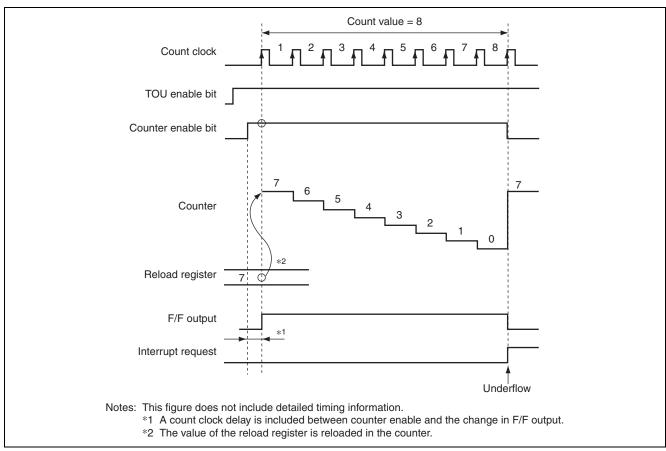

| 21.21 | Operatio    | n of Timer TOU                                               | 21-127 |

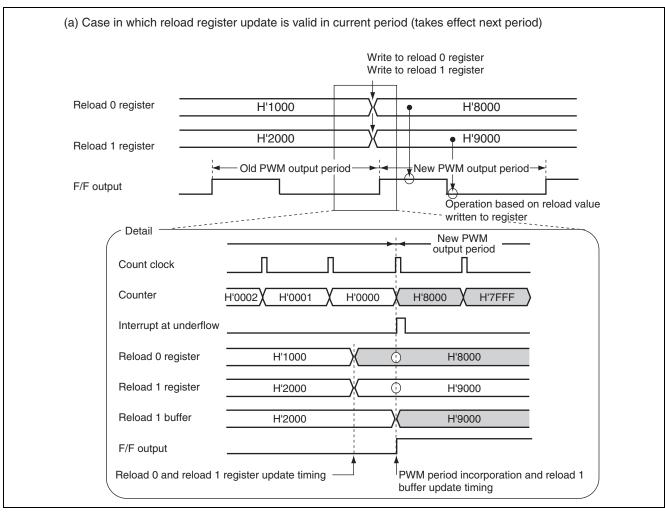

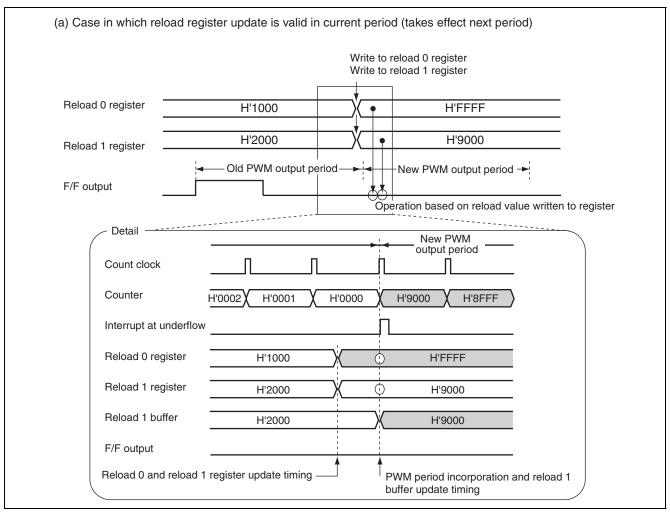

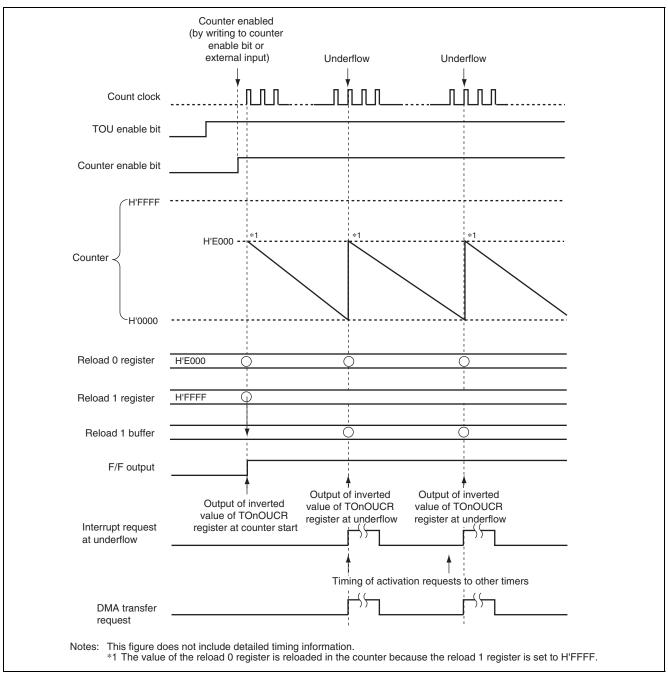

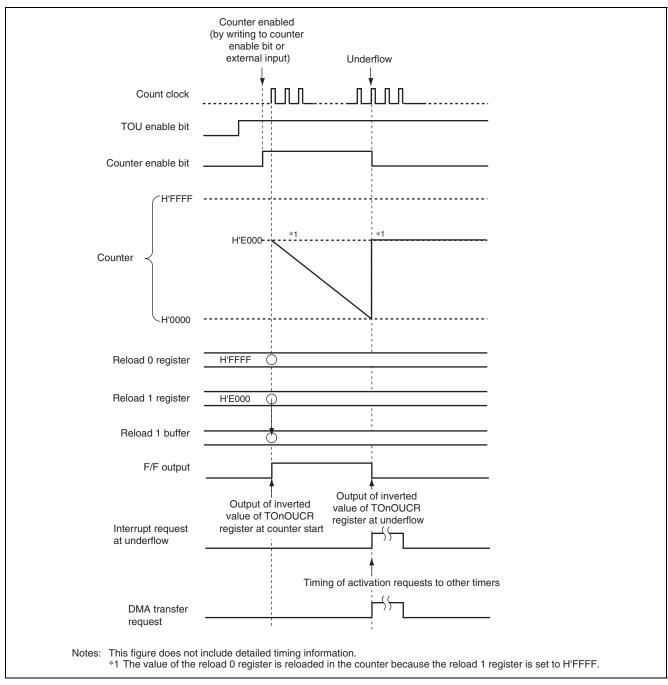

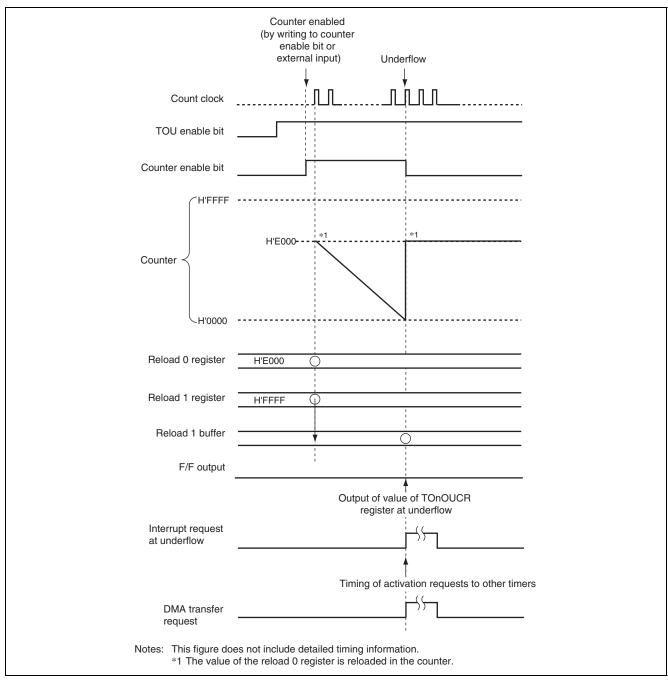

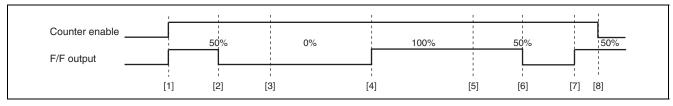

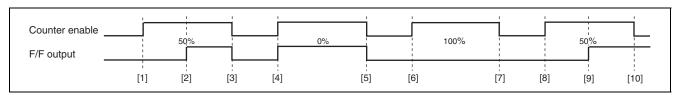

|       | 21.21.1     | Operation in PWM Output Mode                                 | 21-127 |

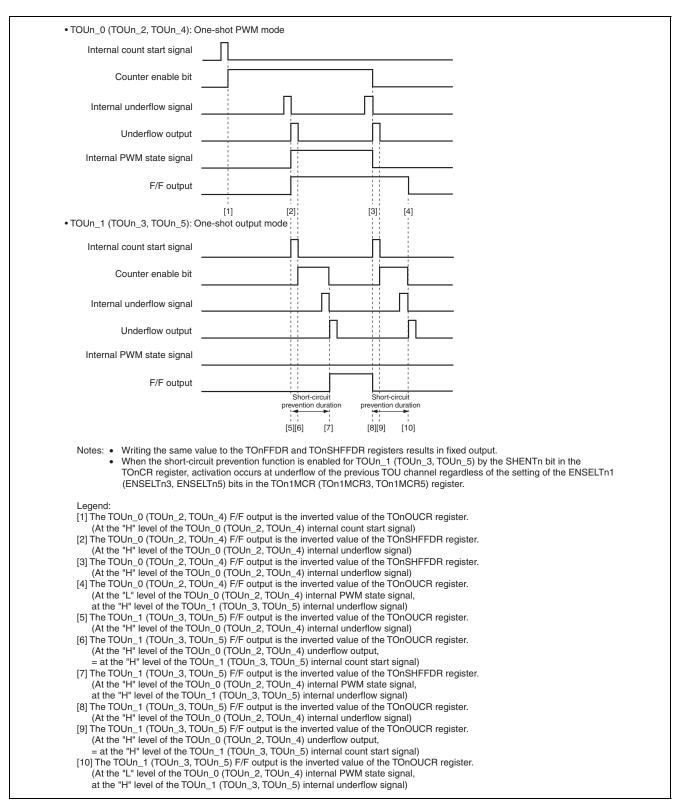

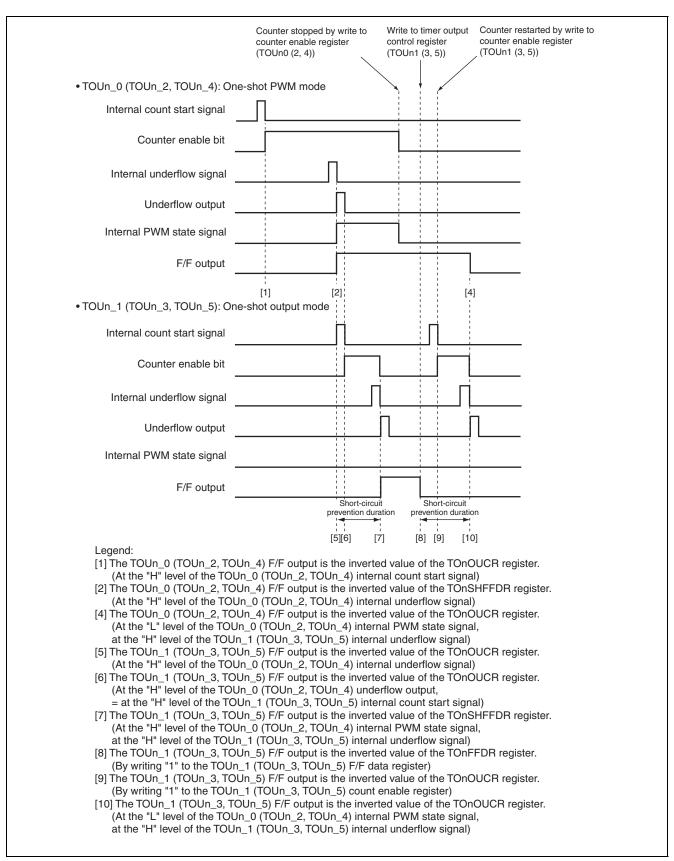

|       | 21.21.2     | Operation in One-Shot PWM Output Mode                        | 21-132 |

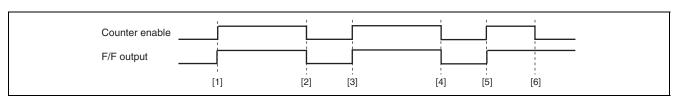

|       | 21.21.3     | Operation in One-Shot Output Mode                            | 21-135 |

|       | 21.21.4     | Operation in Continuous Output Mode                          | 21-137 |

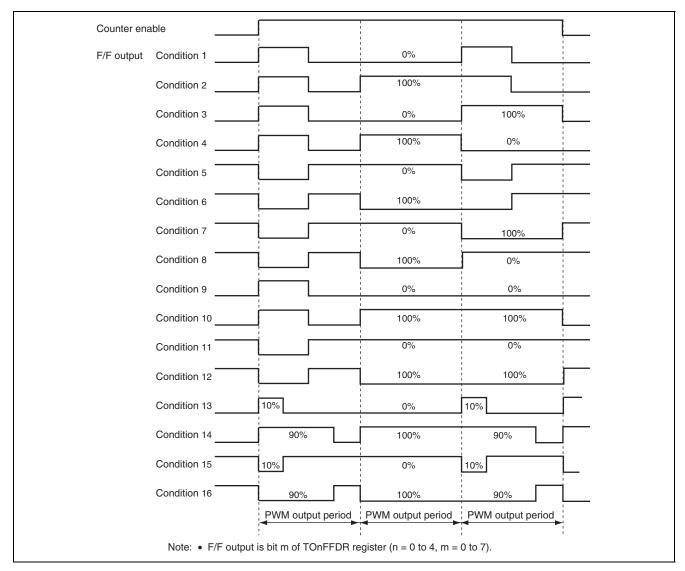

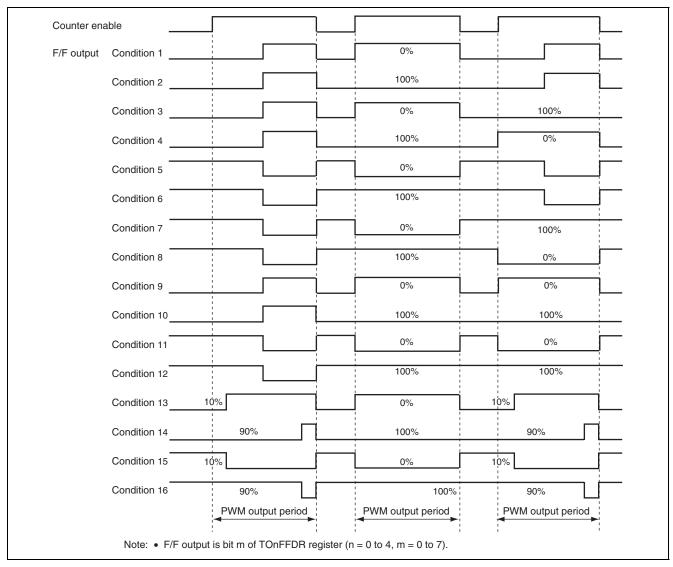

|       | 21.21.5     | 0% or 100% Duty Cycle in PWM Output/One-Shot PWM Output Mode | 21-139 |

|       | 21.21.6     | F/F Output in Each Operating Mode                            | 21-146 |

|       | 21.21.7     | PWM Output-Prohibit Function.                                | 21-149 |

|       | 21.21.8     | Short-Circuit Prevention Function                            | 21-152 |

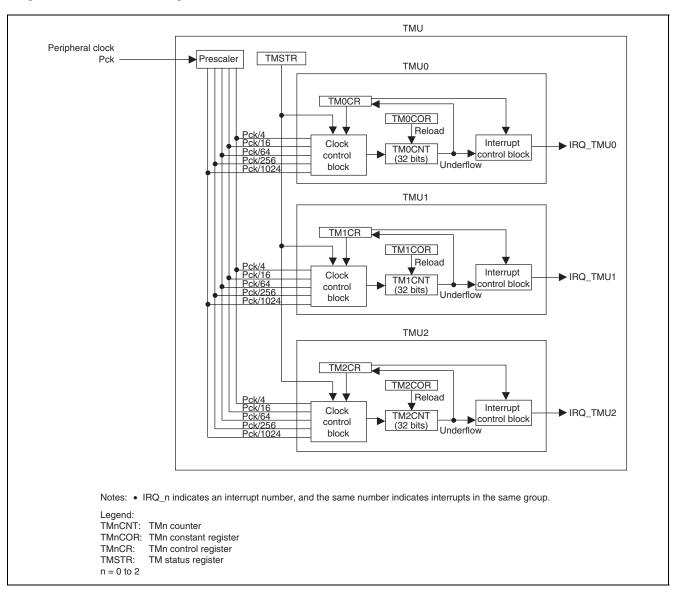

| Secti | ion 22 T    | Fimer Unit (TMU)                                             | 22-1   |

| 22.1  | Overviev    | W                                                            | 22-1   |

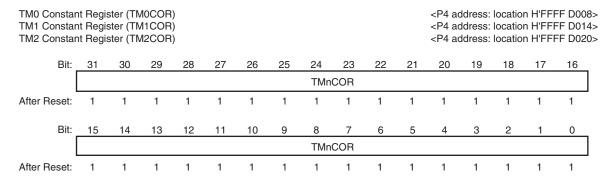

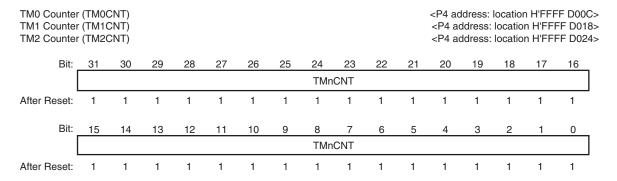

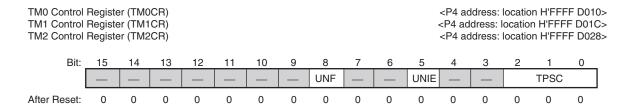

| 22.2  | Register    | Descriptions                                                 | 22-2   |

|       | 22.2.1      | TM Start Register (TMSTR)                                    | 22-2   |

|       | 22.2.2      | TMn Constant Register (TMnCOR)                               | 22-3   |

|       | 22.2.3      | TMn Counter (TMnCNT)                                         | 22-3   |

|       | 22.2.4      | TMn Control Register (TMnCR)                                 | 22-4   |

| 22.3  | Operatio    | n                                                            | 22-6   |

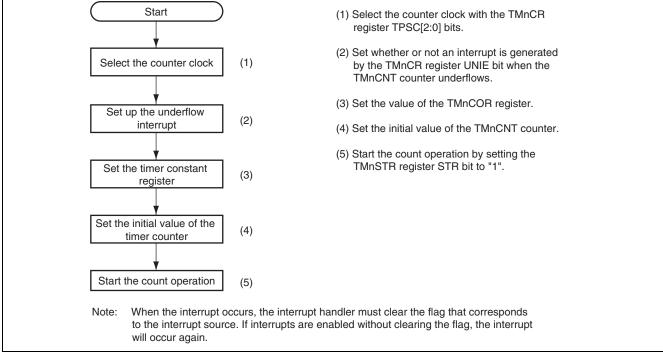

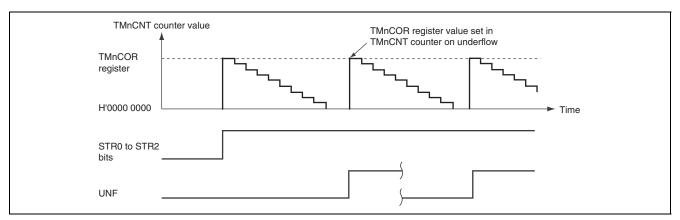

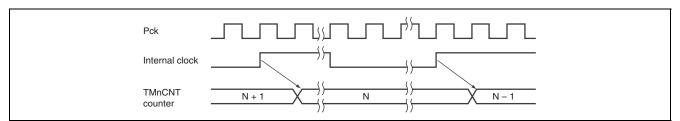

|       | 22.3.1      | Counter Operation                                            | 22-6   |

| 22.4  | Interrupt   | S                                                            | 22-8   |

| 22.5  | Usage Notes |                                                              | 22-8   |

|       | 22.5.1      | Register Writes                                              | 22-8   |

|       | 22.5.2      | Reading from TMnCNT Counter                                  |        |

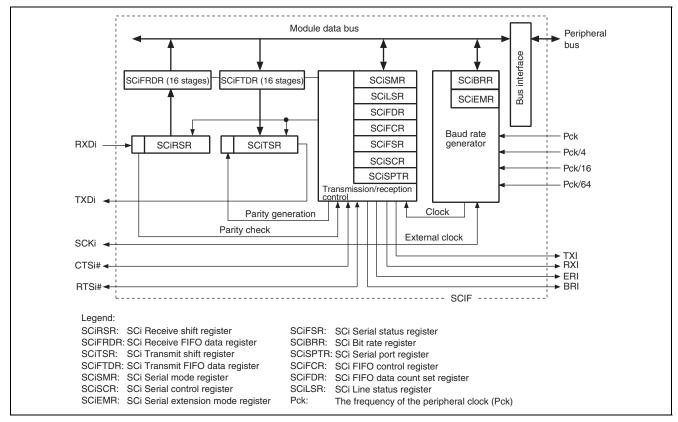

| Secti | ion 23 S    | Serial Communication Interface with FIFO (SCIF)              | 23-1   |

| 23.1  | Overviev    | W                                                            | 23-1   |

| 23.2  | Input/Ou    | ıtput Pins                                                   | 23-3   |

| 23.3  | Register    | Descriptions                                                 | 23-4   |

|       | 23.3.1      | SCi Receive Shift Register (SCiRSR)                          |        |

|       | 23.3.2      | SCi Receive FIFO Data Register (SCiFRDR)                     | 23-6   |

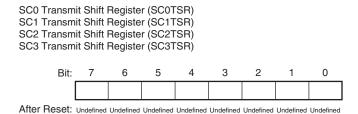

|       | 23.3.3      | SCi Transmit Shift Register (SCiTSR)                         | 23-7   |

|       | 23.3.4      | SCi Transmit FIFO Data Register (SCiFTDR)                    | 23-7   |

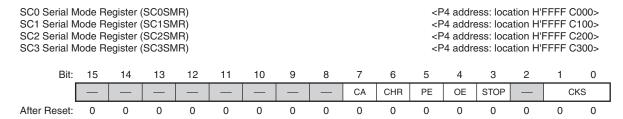

|       | 23.3.5      | SCi Serial Mode Register (SCiSMR)                            | 23-8   |

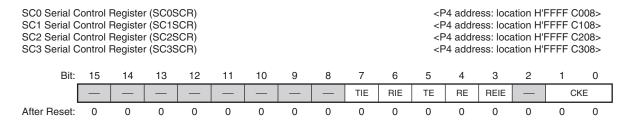

|       | 23.3.6      | SCi Serial Control Register (SCiSCR)                         | 23-10  |

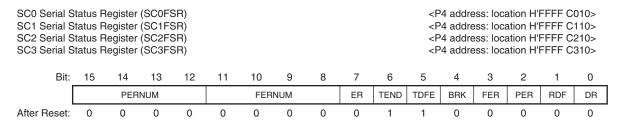

|       | 23.3.7      | SCi Serial Status Register (SCiFSR)                          | 23-13  |

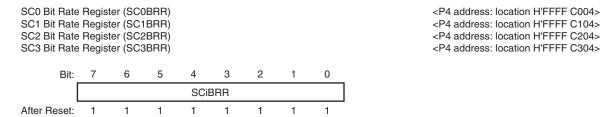

|       | 23.3.8      | SCi Bit Rate Register (SCiBRR)                               | 23-19  |

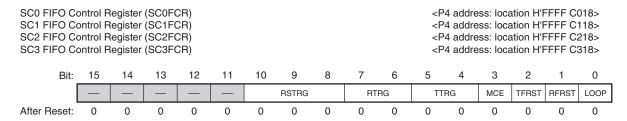

|       | 23.3.9      | SCi FIFO Control Register (SCiFCR)                           | 23-23  |

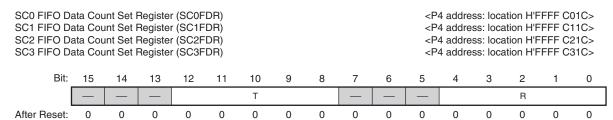

|       | 23.3.10     | SCi FIFO Data Count Set Register (SCiFDR)                    | 23-25  |

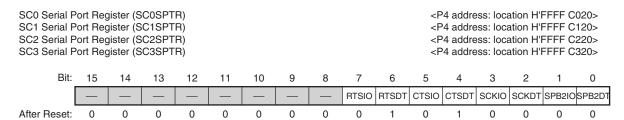

|       | 23.3.11     | SCi Serial Port Register (SCiSPTR)                           | 23-26  |

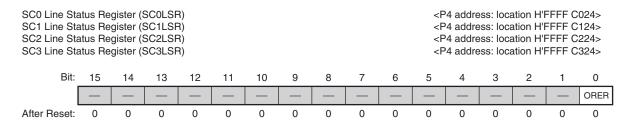

|       | 23.3.12     | SCi Line Status Register (SCiLSR)                            | 23-28  |

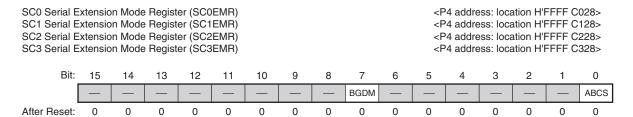

|       | 23.3.13     | SCi Serial Extension Mode Register (SCiEMR)                  |        |

| 23.4  |             | n                                                            |        |

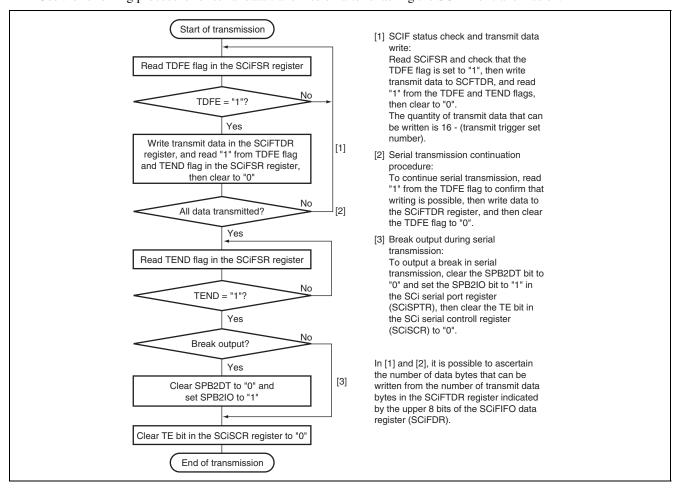

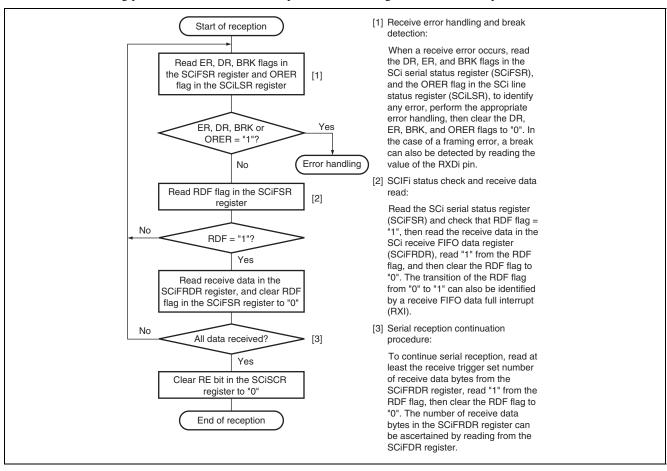

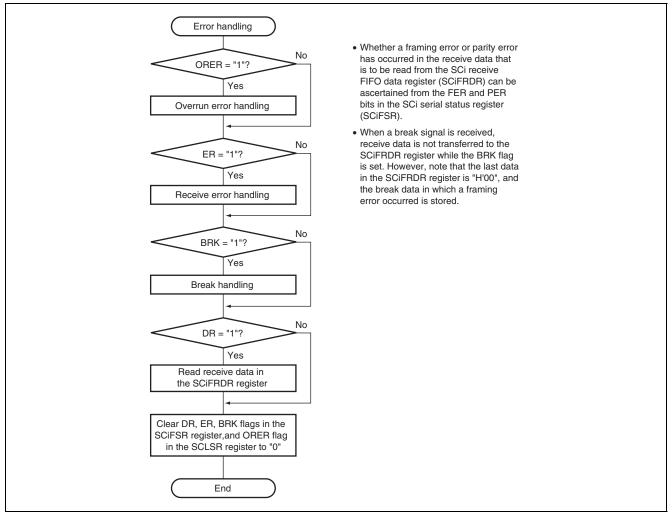

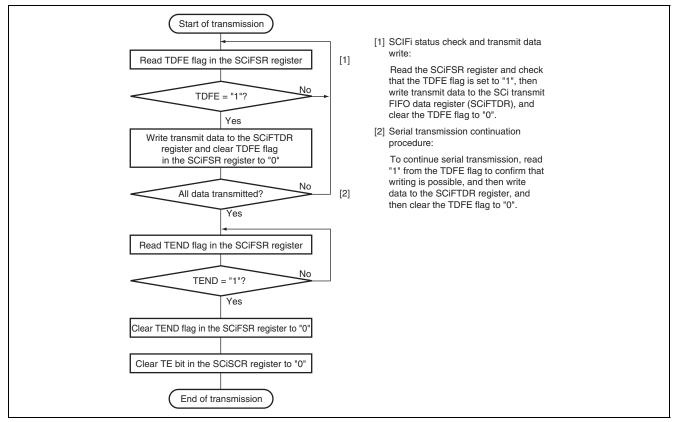

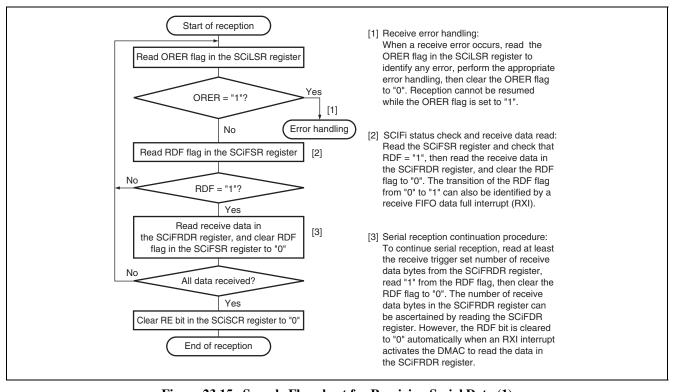

|       | 23.4.1      | Overview                                                     |        |

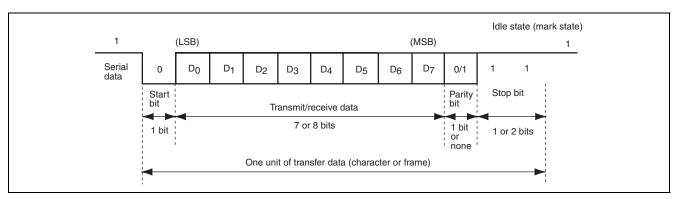

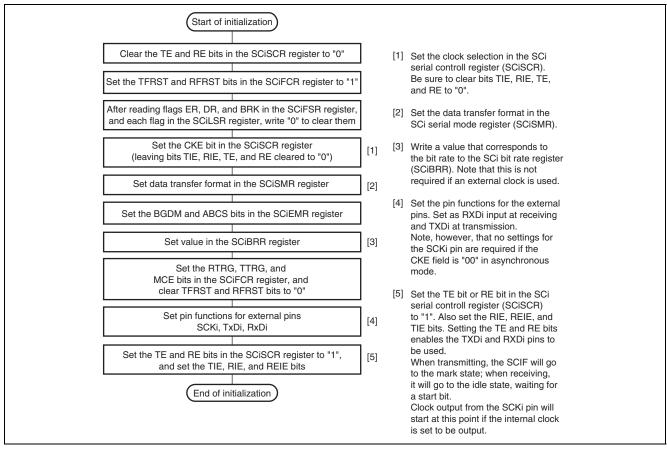

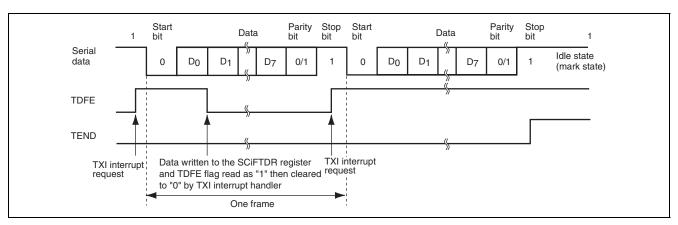

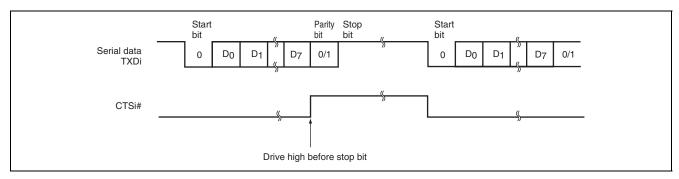

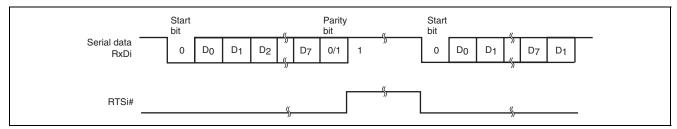

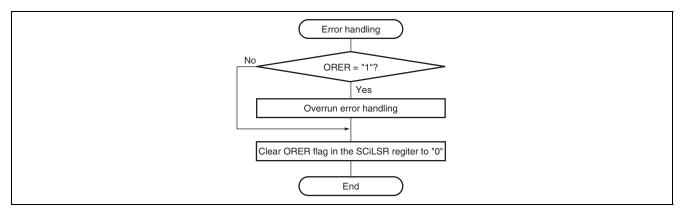

|       | 23.4.2      | Operation in Asynchronous Mode                               |        |

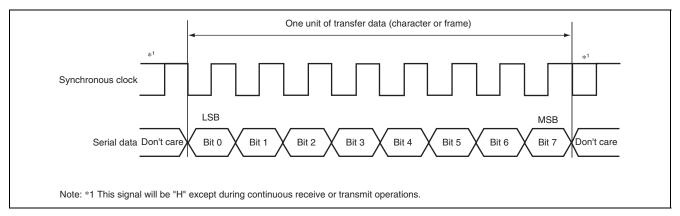

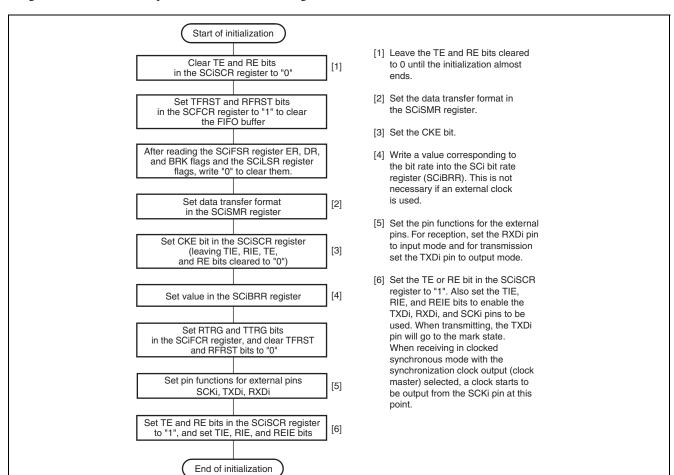

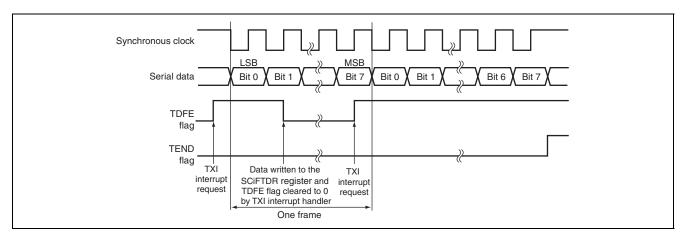

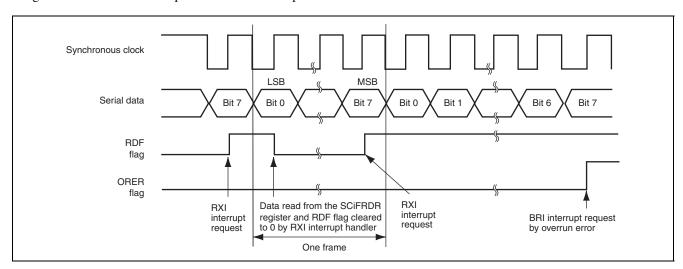

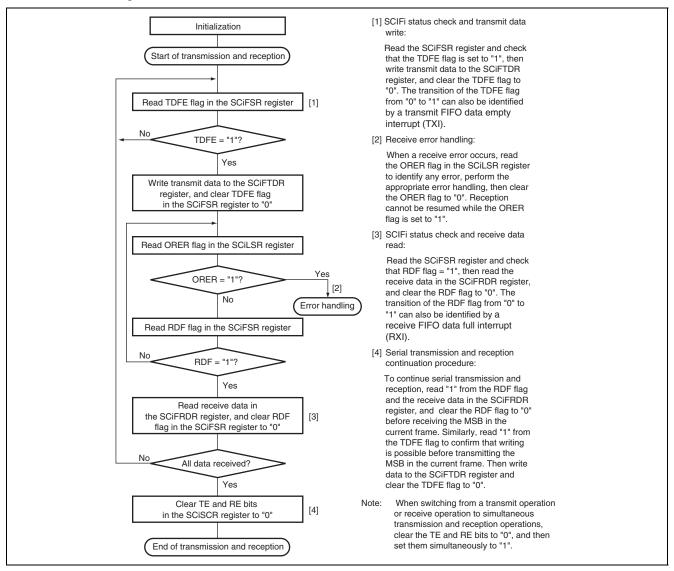

|       | 23.4.3      | Operation in Clock Synchronous Mode                          |        |

| 23.5  |             | terrupt Sources and DMAC                                     |        |

| 23.6  |             | otes                                                         |        |

|       |             |                                                              |        |

|       | 23.6.1   | SCiFTDR Register Writing and TDFE Flag                 | 23-47 |

|-------|----------|--------------------------------------------------------|-------|

|       | 23.6.2   | SCiFRDR Reading and RDF Flag                           | 23-47 |

|       | 23.6.3   | Break Detection and Processing                         | 23-47 |

|       | 23.6.4   | Sending a Break Signal                                 | 23-47 |

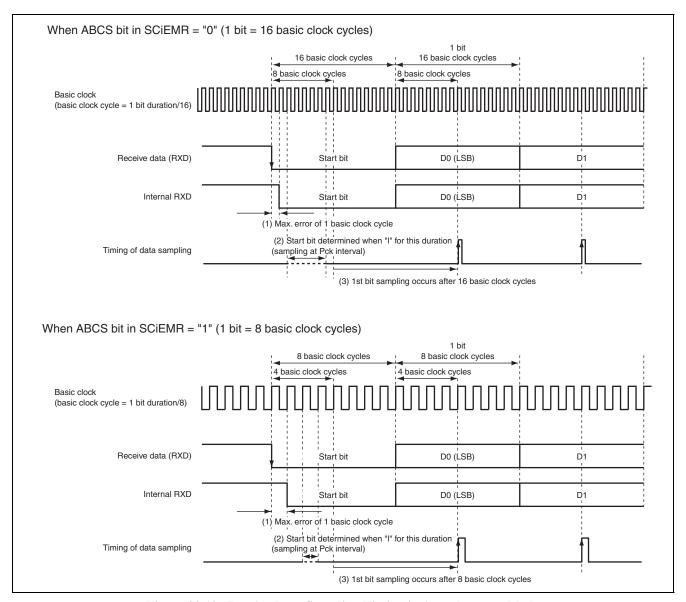

|       | 23.6.5   | Receive Data Sampling Timing in Asynchronous Mode      | 23-48 |

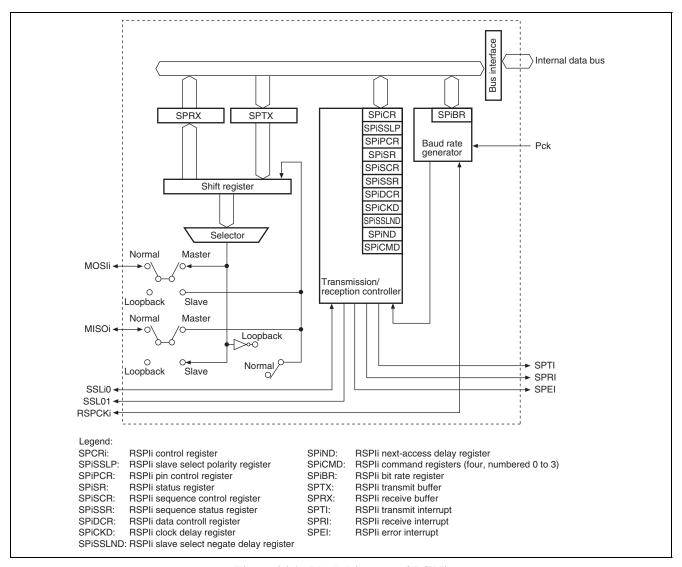

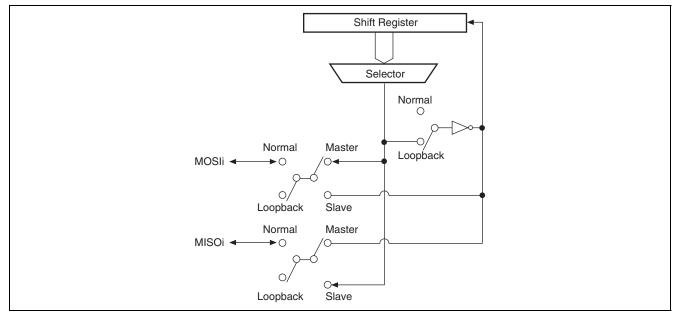

| Secti | on 24 I  | Renesas Serial Peripheral Interface (RSPI)             | 24-1  |

| 24.1  |          | W                                                      |       |

| 24.2  |          | utput Pins                                             |       |

| 24.3  | Register | Descriptions                                           | 24-5  |

|       | 24.3.1   | RSPIi Control Register (SPiCR)                         | 24-7  |

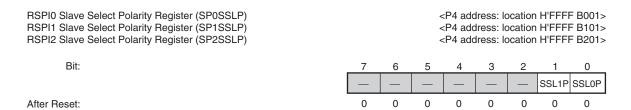

|       | 24.3.2   | RSPIi Slave Select Polarity Register (SPiSSLP)         |       |

|       | 24.3.3   | RSPIi Pin Control Register (SPiPCR)                    |       |

|       | 24.3.4   | RSPIi Status Register (SPiSR)                          |       |

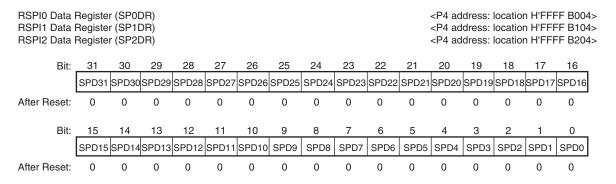

|       | 24.3.5   | RSPIi Data Register (SPiDR)                            |       |

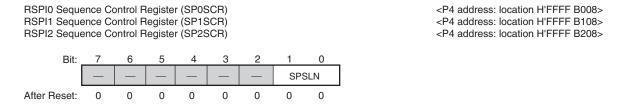

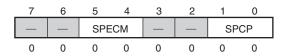

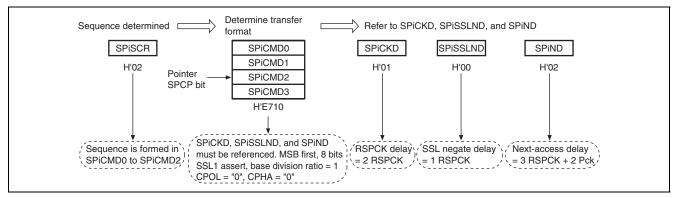

|       | 24.3.6   | RSPIi Sequence Control Register (SPiSCR)               |       |

|       | 24.3.7   | RSPIi Sequence Status Register (SPiSSR)                |       |

|       | 24.3.8   | RSPIi Bit Rate Register (SPiBR)                        |       |

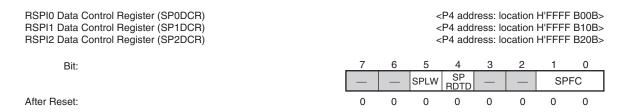

|       | 24.3.9   | RSPIi Data Control Register (SPiDCR)                   |       |

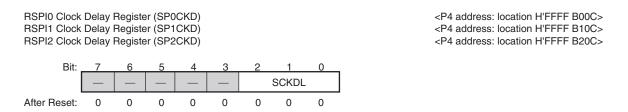

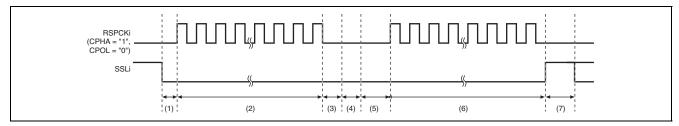

|       | 24.3.10  | RSPIi Clock Delay Register (SPiCKD)                    |       |

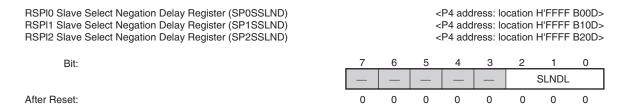

|       | 24.3.11  | RSPIi Slave Select Negation Delay Register (SPiSSLND)  |       |

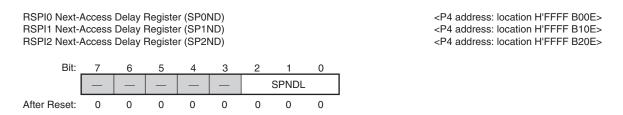

|       | 24.3.12  | RSPIi Next-Access Delay Register (SPiND)               |       |

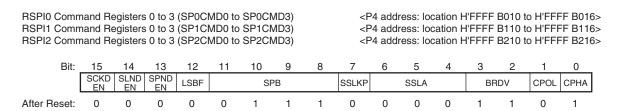

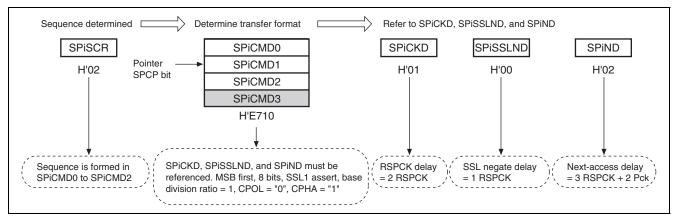

|       | 24.3.13  | RSPIi Command Registers 0 to 3 (SPiCMD0 to SPiCMD3)    |       |

| 24.4  |          | on                                                     |       |

|       | 24.4.1   | Overview of RSPIi Operations                           |       |

|       | 24.4.2   | Controlling RSPIi Pins                                 |       |

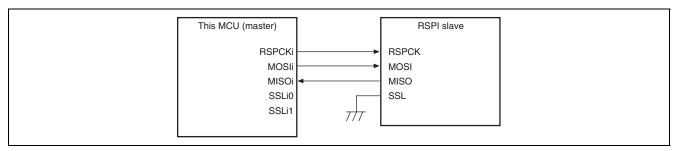

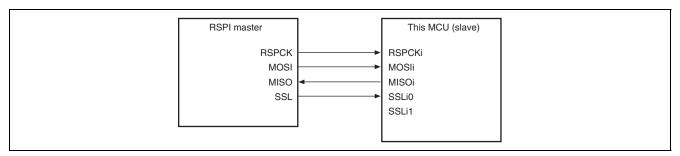

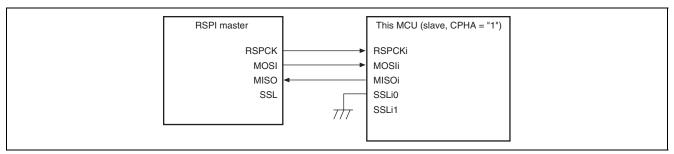

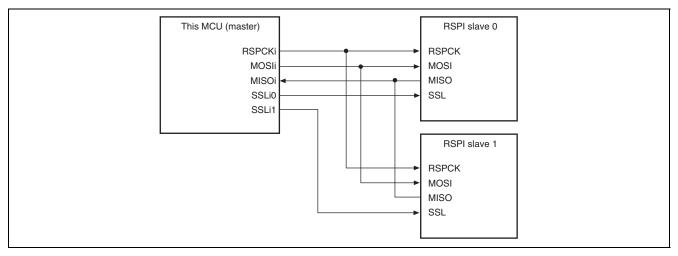

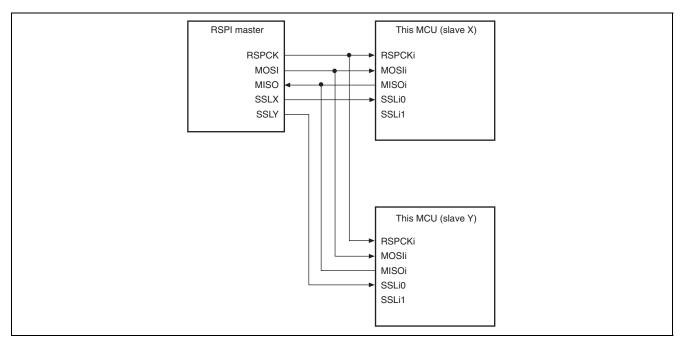

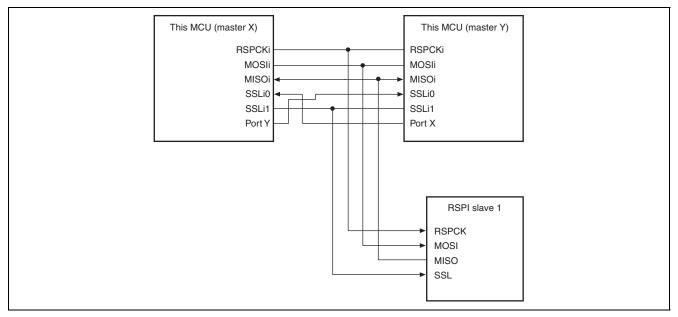

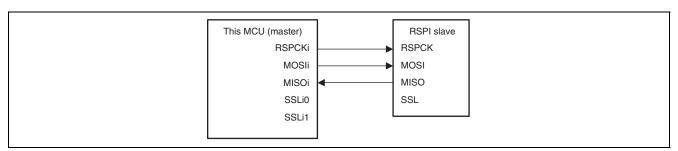

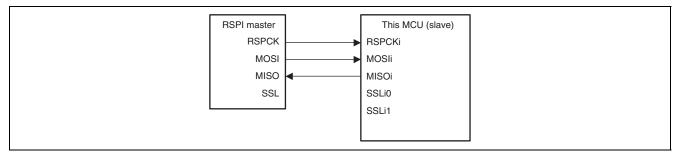

|       | 24.4.3   | RSPI System Configuration Example                      |       |

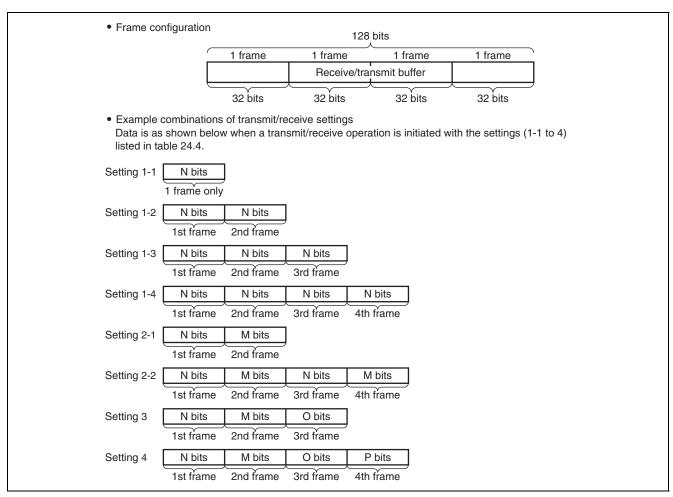

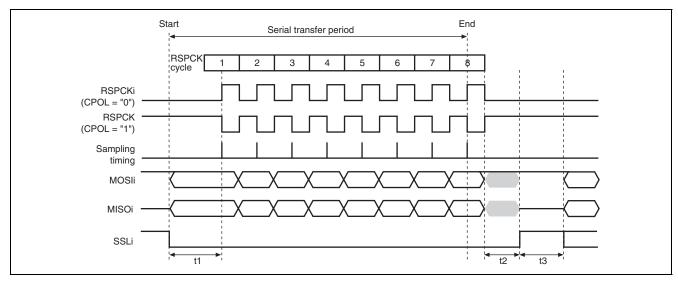

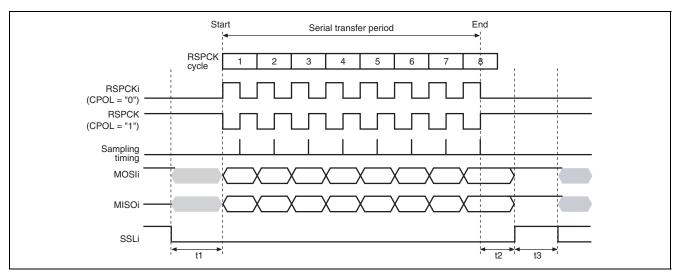

|       | 24.4.4   | Transfer Format                                        |       |

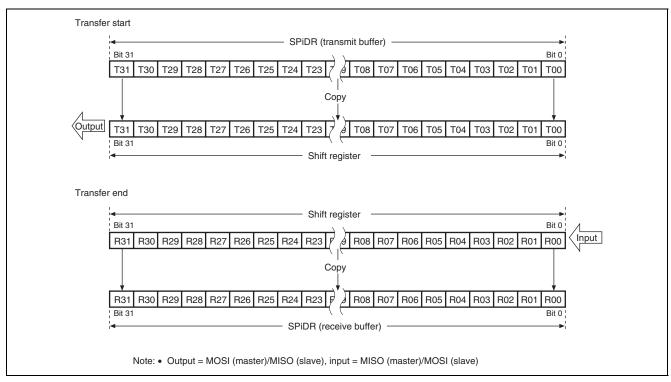

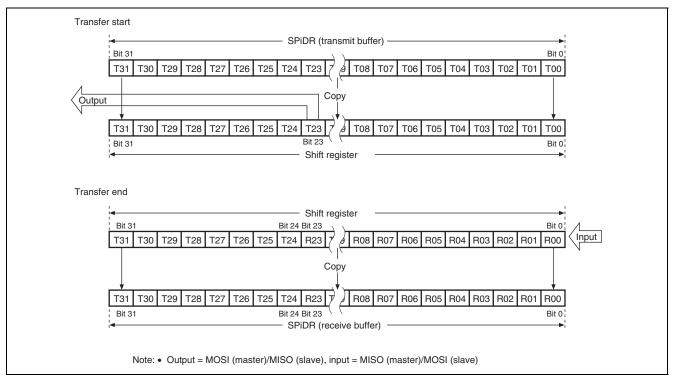

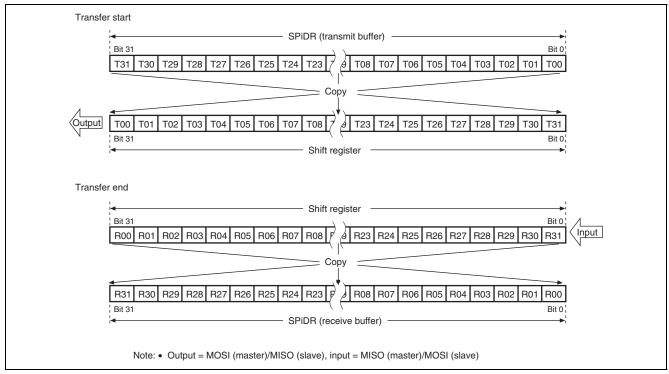

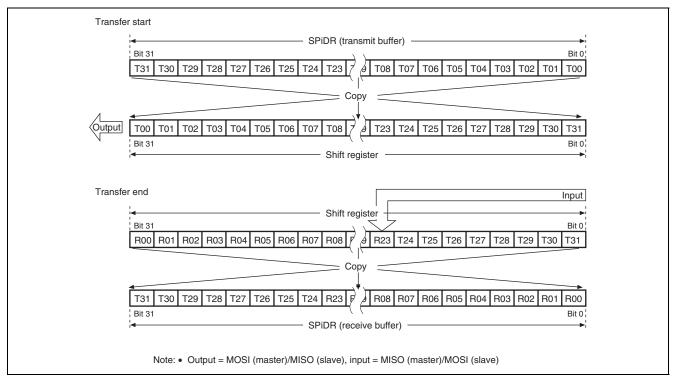

|       | 24.4.5   | Data Format                                            |       |

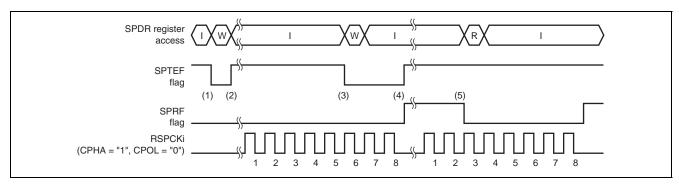

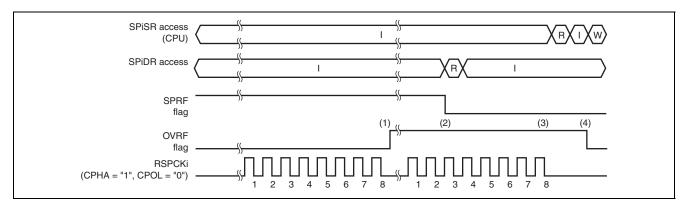

|       | 24.4.6   | Transmission Buffer Empty/Receive Buffer Full Flags    |       |

|       | 24.4.7   | Error Detection                                        |       |

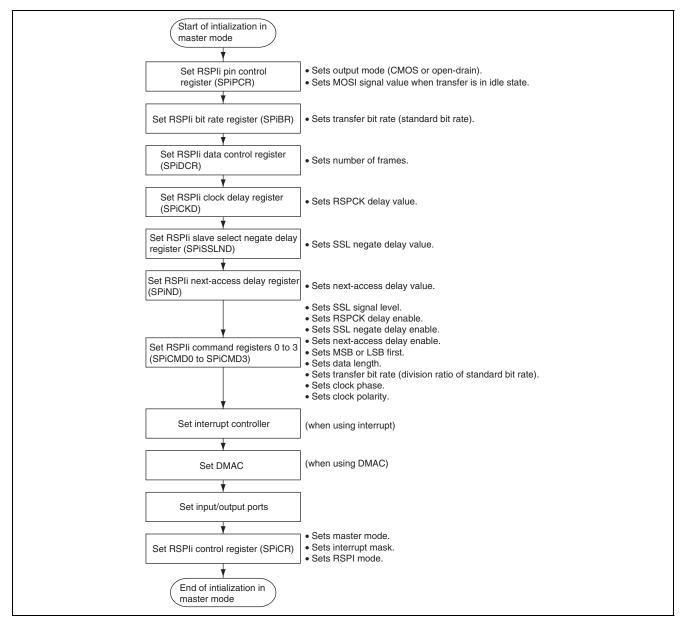

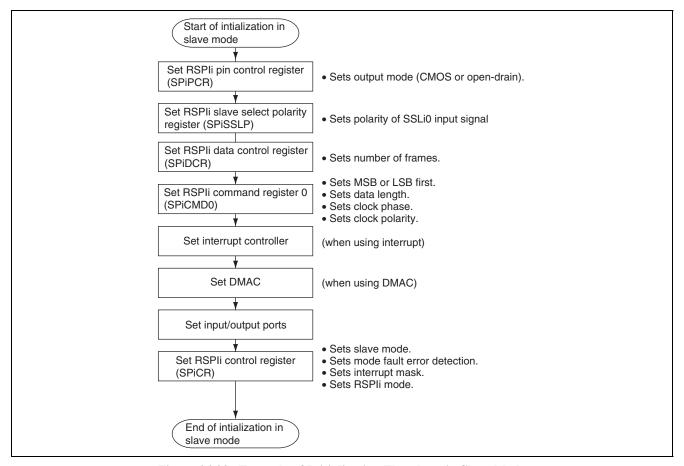

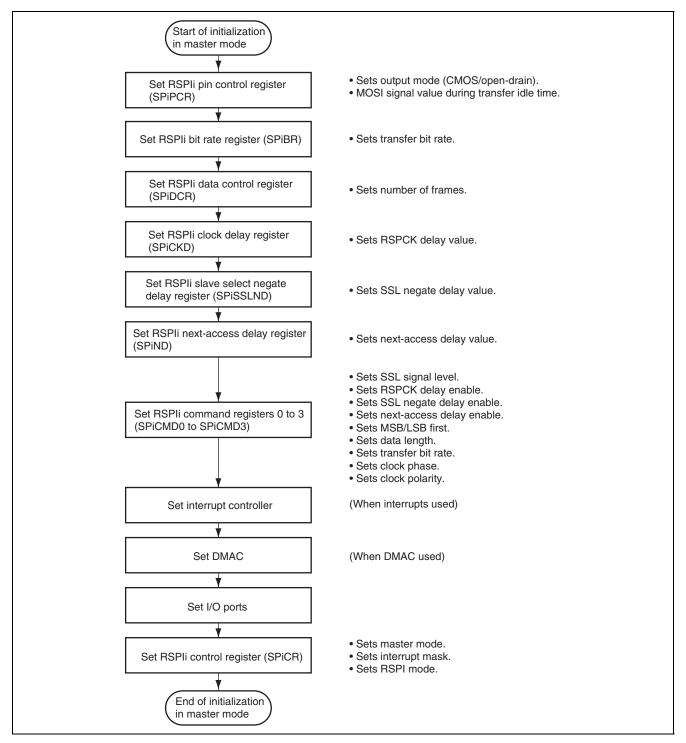

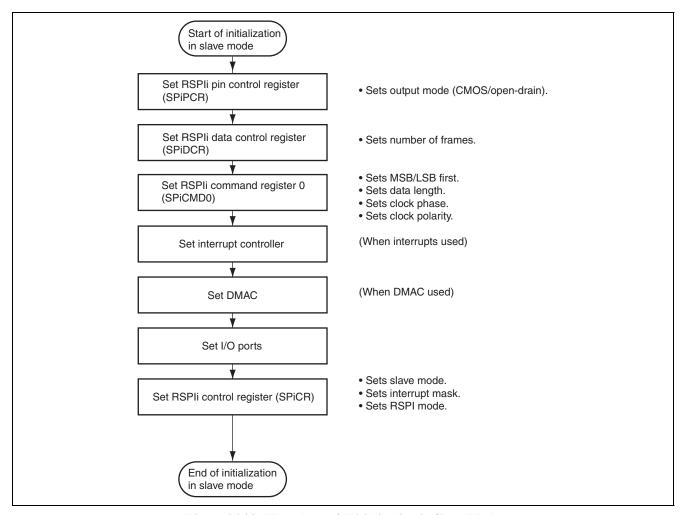

|       | 24.4.8   | Initializing RSPI                                      |       |

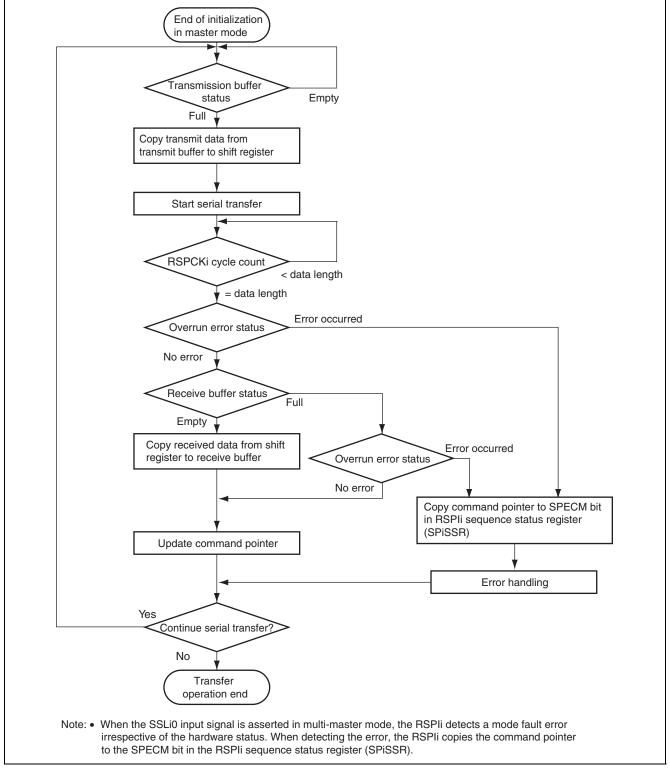

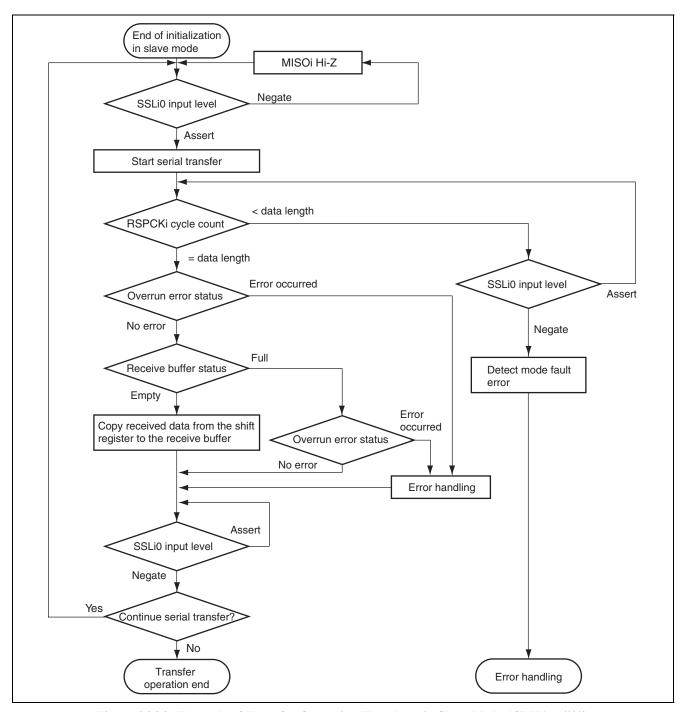

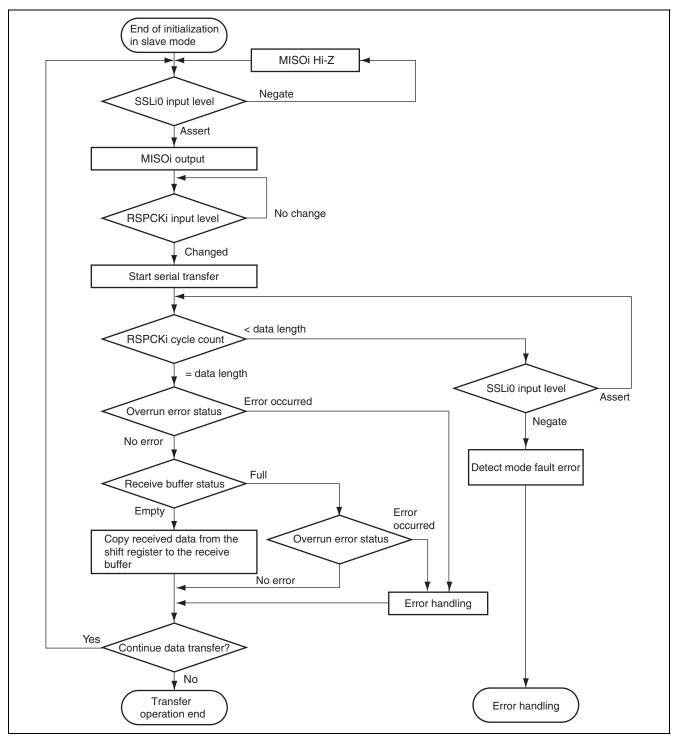

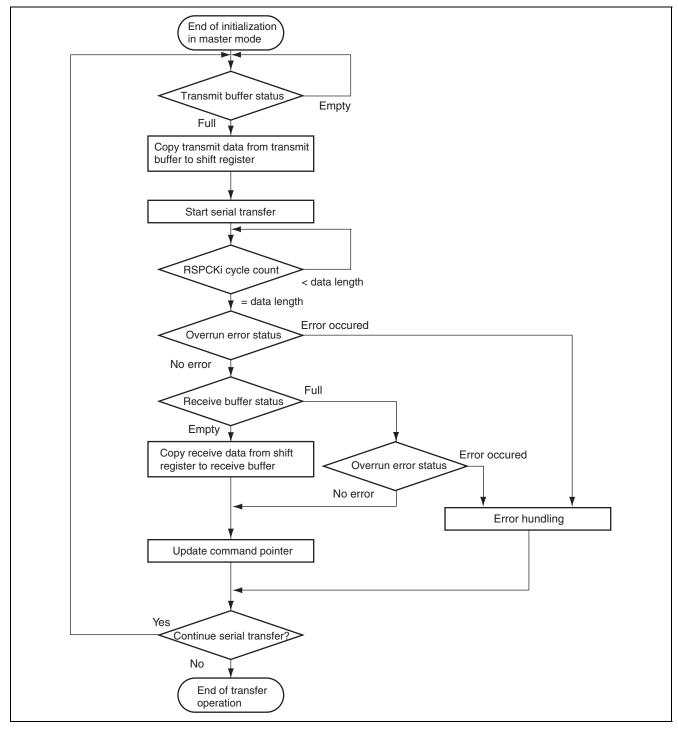

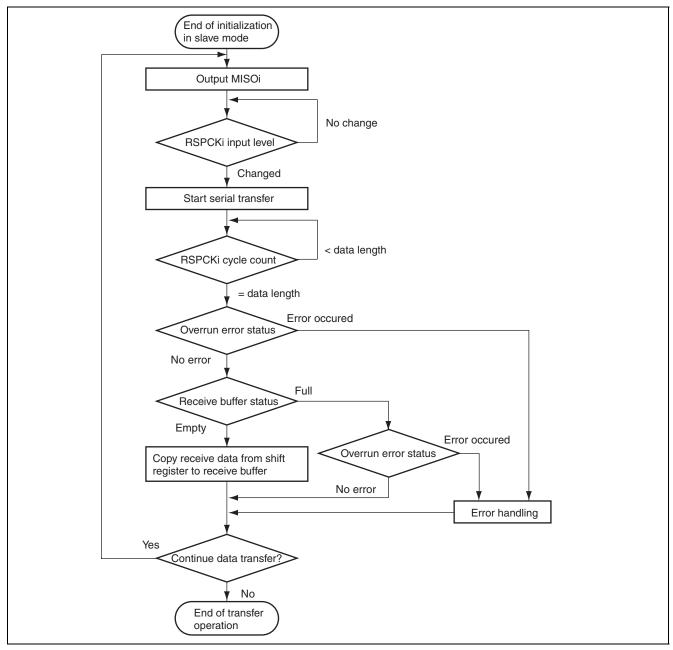

|       | 24.4.9   | SPI Operation.                                         |       |

|       | 24.4.10  | Clock Synchronous Operation                            |       |

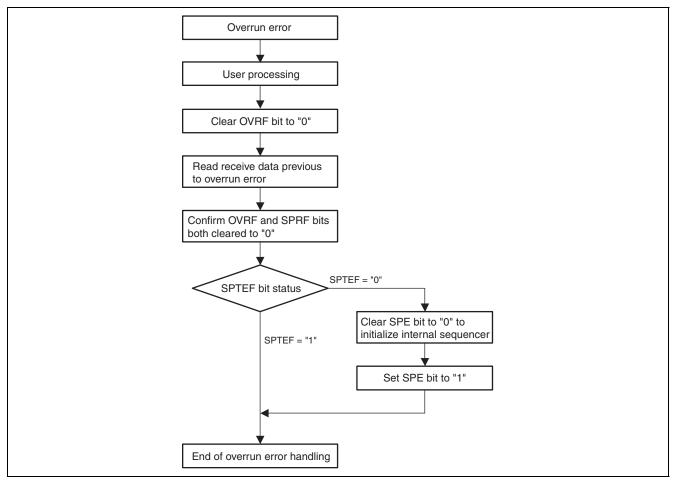

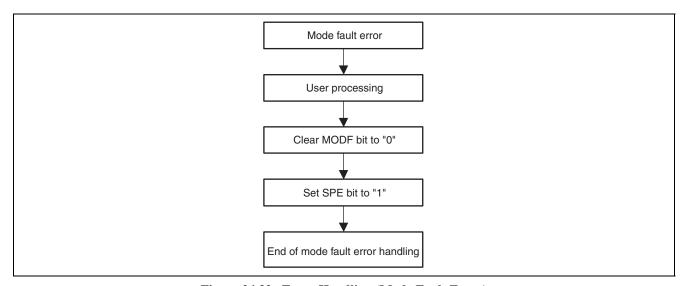

|       | 24.4.11  | Error Handling                                         | 24-62 |

|       | 24.4.12  | Loopback Mode                                          |       |

|       | 24.4.13  | Interrupt Sources                                      |       |

|       | 24.4.14  | DMA Transfer Sources                                   |       |

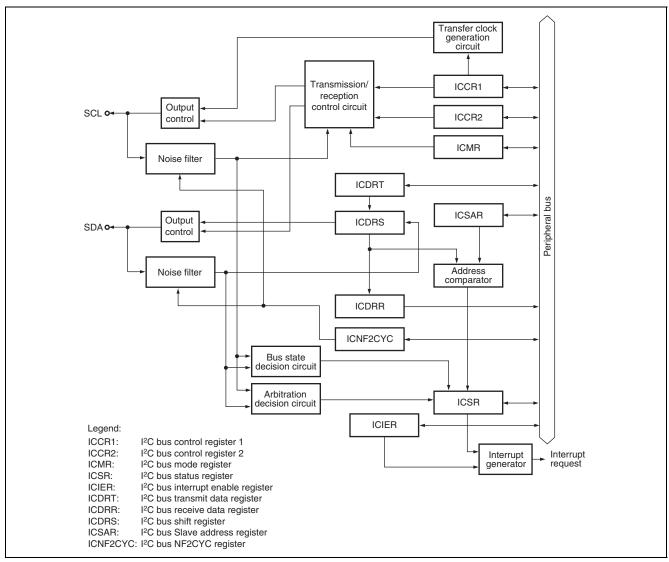

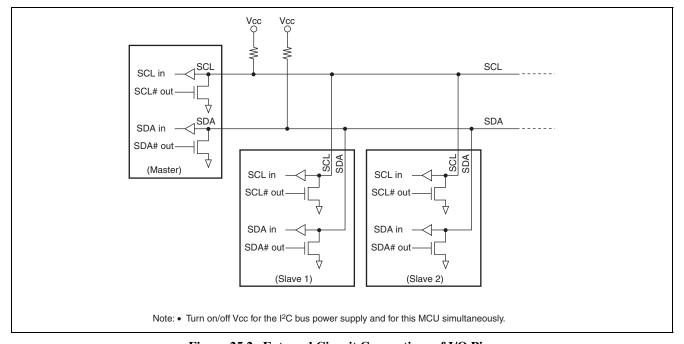

| Secti | on 25 I  | <sup>2</sup> C Bus Interface 3 (IIC3)                  | 25-1  |

| 25.1  |          | w                                                      |       |

| 25.2  |          | utput Pins                                             |       |

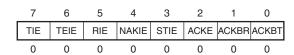

| 25.3  | -        | Descriptions                                           |       |

| 23.3  | 25.3.1   | I <sup>2</sup> C Bus Control Register 1 (ICCR1)        |       |

|       | 25.3.2   | I <sup>2</sup> C Bus Control Register 2 (ICCR2)        |       |

|       | 25.3.3   | I <sup>2</sup> C Bus Mode Register (ICMR)              |       |

|       | 25.3.4   | I <sup>2</sup> C Bus Interrupt Enable Register (ICIER) |       |

|       | 25.3.5   | I <sup>2</sup> C Bus Status Register (ICSR)            |       |

|       | 25.3.6   | I <sup>2</sup> C Bus Slave Address Register (ICSAR)    |       |

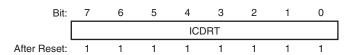

|       | 25.3.7   | I <sup>2</sup> C Bus Transmit Data Register (ICDRT)    |       |

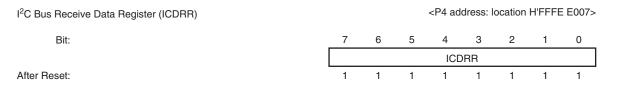

|       | 25.3.8   | I <sup>2</sup> C Bus Receive Data Register (ICDRR)     |       |

|       | ں.ں.ں    | I C Duo ROCCITO Data Regiotal (ICDRR)                  |       |

|       | 25.3.9    | I <sup>2</sup> C Bus Shift Register (ICDRS)                                  | 25-13 |

|-------|-----------|------------------------------------------------------------------------------|-------|

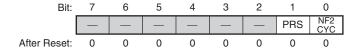

|       | 25.3.10   | I <sup>2</sup> C Bus NF2CYC Register (ICNF2CYC)                              | 25-14 |

| 25.4  | Operation | n                                                                            | 25-15 |

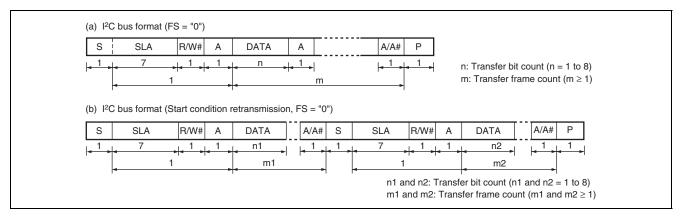

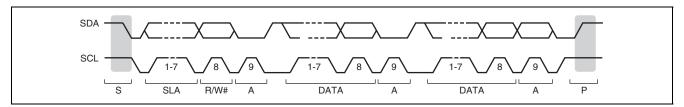

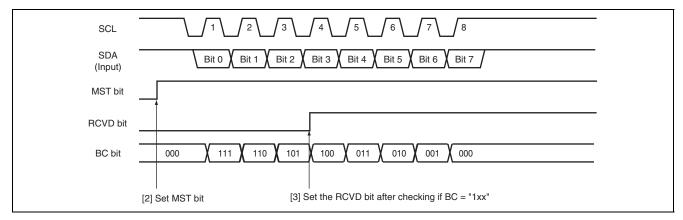

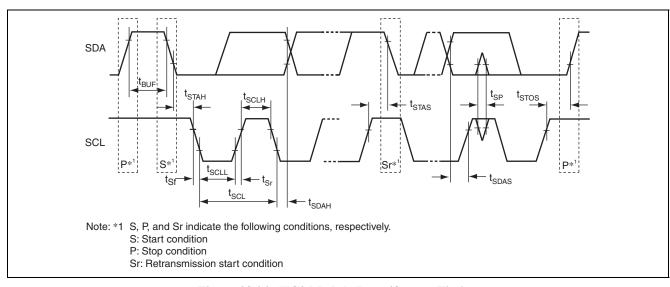

|       | 25.4.1    | I <sup>2</sup> C Bus Format                                                  | 25-15 |

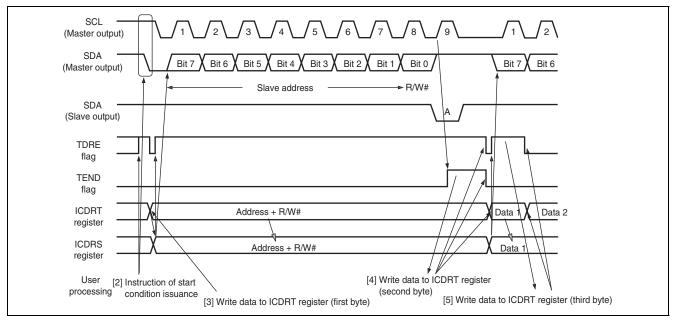

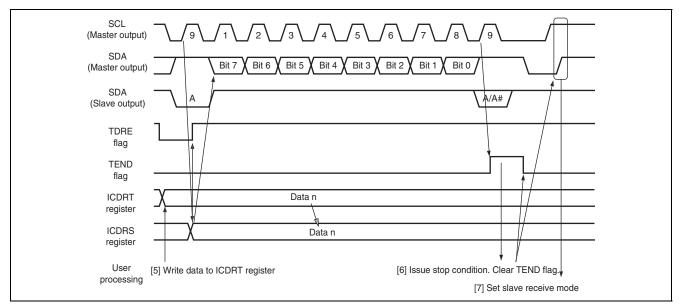

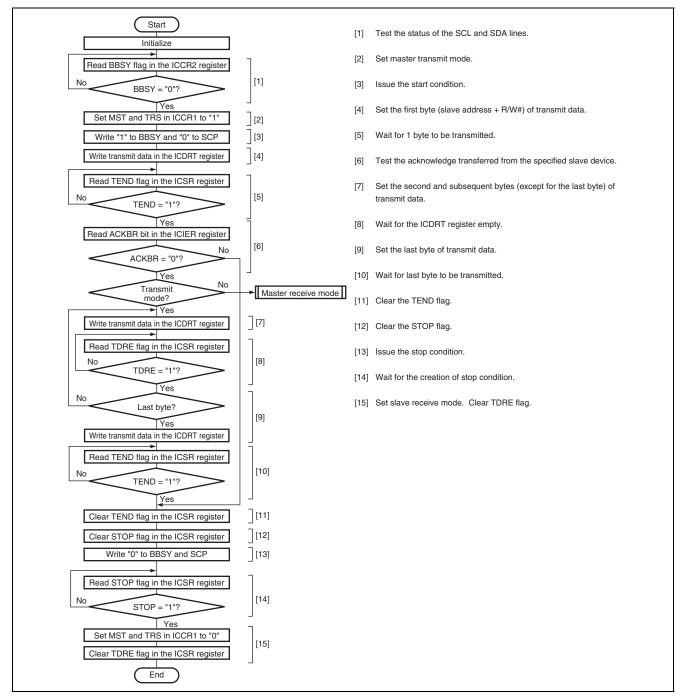

|       | 25.4.2    | Master Transmit Operation                                                    | 25-16 |

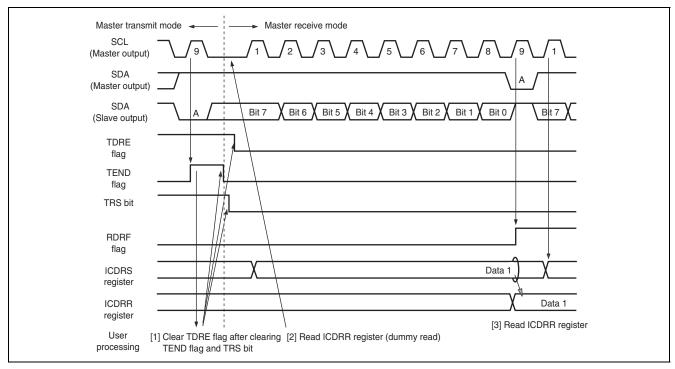

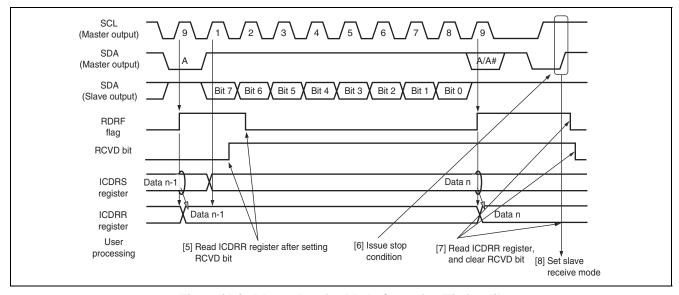

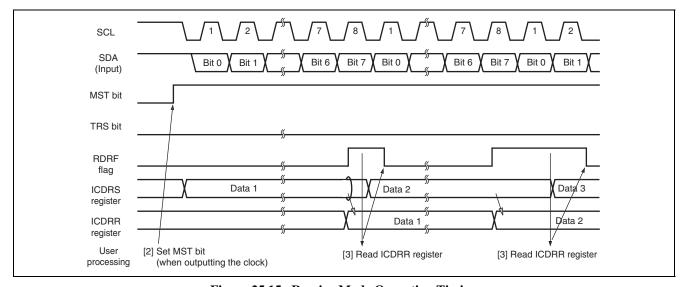

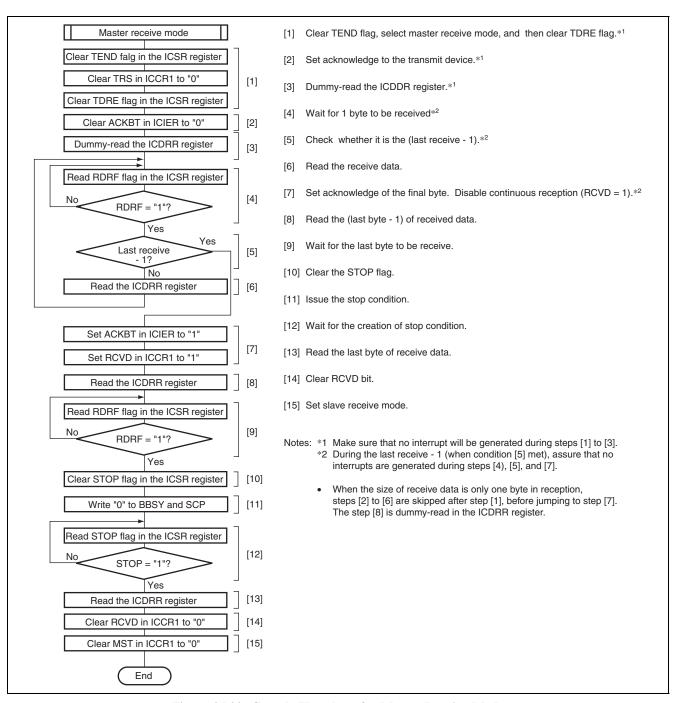

|       | 25.4.3    | Master Receive Operation                                                     | 25-17 |

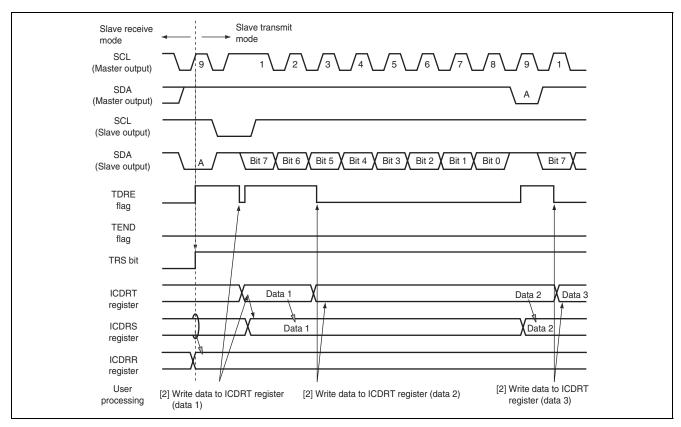

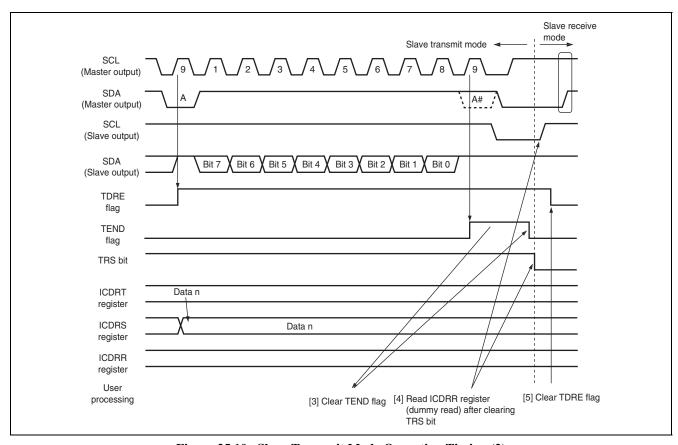

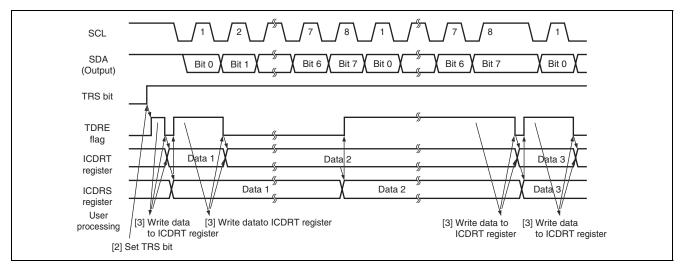

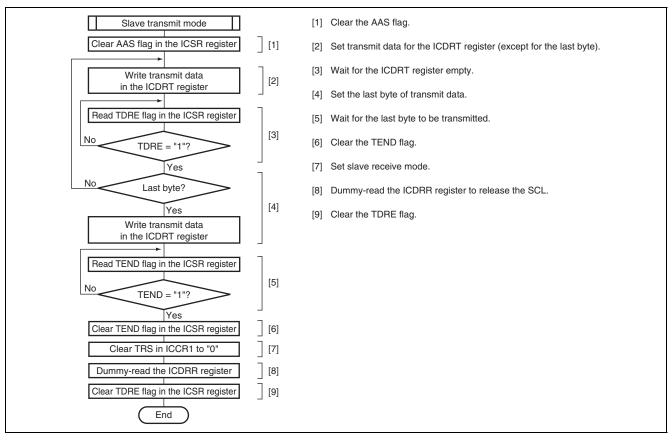

|       | 25.4.4    | Slave Transmit Operation                                                     | 25-19 |

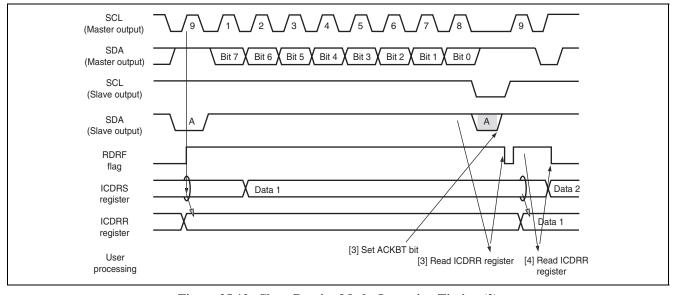

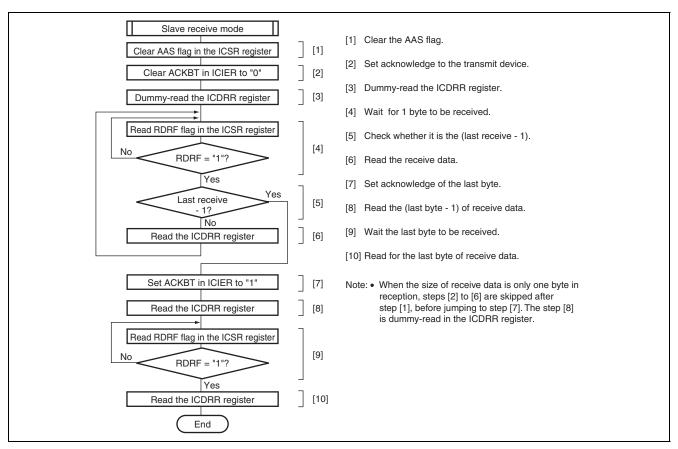

|       | 25.4.5    | Slave Receive Operation                                                      | 25-20 |

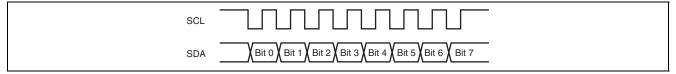

|       | 25.4.6    | Clocked Synchronous Serial Format                                            | 25-22 |

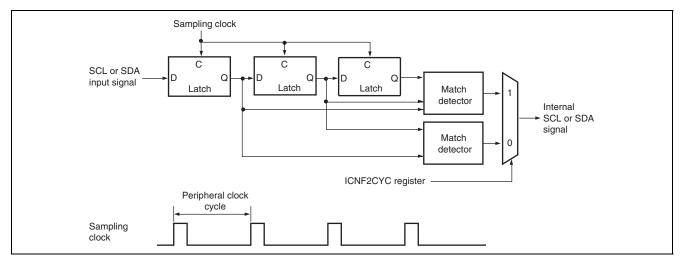

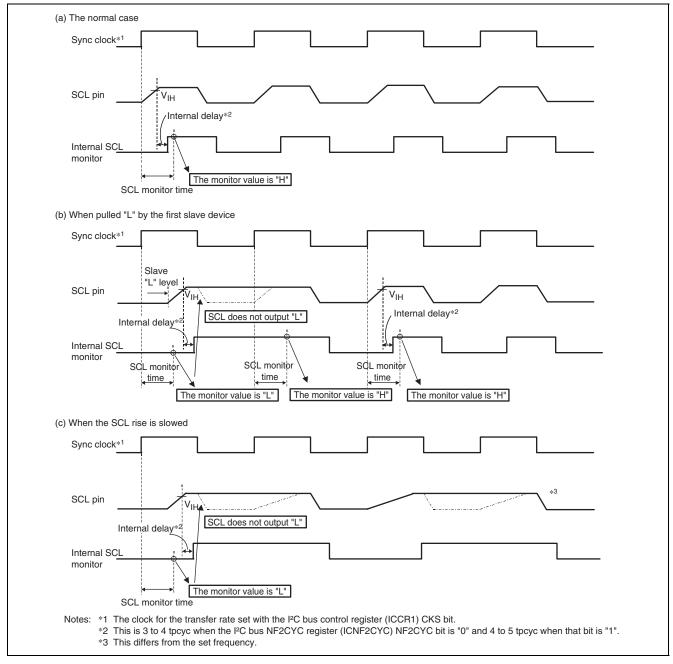

|       | 25.4.7    | Noise Filter                                                                 | 25-24 |

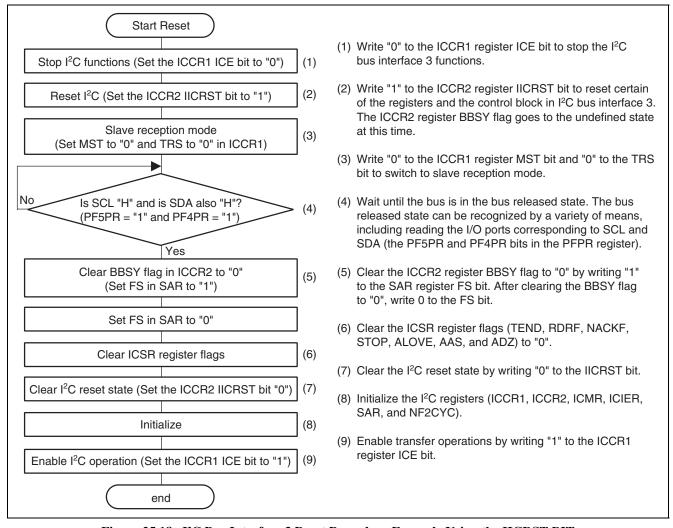

|       | 25.4.8    | I <sup>2</sup> C Bus Interface 3 Reset by the IICRST Bit                     | 25-25 |

|       | 25.4.9    | Example of Use                                                               | 25-26 |

| 25.5  | Interrupt | Requests                                                                     | 25-30 |

| 25.6  | DMA Tı    | ransfer Requests                                                             | 25-30 |

| 25.7  | Bit Sync  | hronous Circuit                                                              | 25-31 |

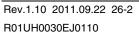

| 25.8  | Usage N   | otes                                                                         | 25-32 |