#### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics atta abooks, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU ROHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# SH-2E

# Software Manual Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC engine Family/ SH7000 Series

Renesas Electronics

Rev.2.00 2006.05

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport control to the export control laws and regulations of Japan and/or the

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

# Introduction

The SH-2E is a new generation of RISC microcomputers that integrate a RISC-type CPU and the peripheral functions required for system configuration onto a single chip to achieve high-performance operation. It can operate in a power-down state, which is an essential feature for portable equipment.

This CPU has a RISC-type instruction set. Basic instructions can be executed in one clock cycle, improving instruction execution speed. In addition, the CPU has a 32-bit internal architecture for enhanced data-processing ability.

In addition, the SH-2E supports single-precision floating point calculations as well as entirely PCAPI compatible emulation of double-precision floating point calculations. The SH-2E instructions are a subset of the floating point calculations conforming to the IEEE754 standard.

This programming manual describes in detail the instructions for the SH-2E Series and is intended as a reference on instruction operation and architecture. It also covers the pipeline operation, which is a feature of the SH-2E Series.

For information on the hardware, please refer to the hardware manual for the product in question.

Rev. 2.00 May 31, 2006 page iii of xii

# Main Revisions for This Edition

| Item | Page | Revision (See Manual for Details)                                     |

|------|------|-----------------------------------------------------------------------|

| All  | _    | <ul> <li>Notification of change in company name amended</li> </ul>    |

|      |      | (Before) Hitachi, Ltd. $\rightarrow$ (After) Renesas Technology Corp. |

Rev. 2.00 May 31, 2006 page v of xii

# Contents

| Secti | on 1 Features                      | 1   |

|-------|------------------------------------|-----|

| 1.1   | SH-2E Features                     | 1   |

|       |                                    |     |

| Secti | on 2 Register Configuration        | 3   |

| 2.1   | General Registers                  | 3   |

| 2.2   | Control Registers                  | 4   |

| 2.3   | System Registers                   | 5   |

| 2.4   | Floating-Point Registers           | 6   |

| 2.5   | Floating-Point System Registers    | 7   |

| 2.6   | Initial Values of Registers        | 8   |

| Secti | on 3 Data Formats                  | 9   |

| 3.1   | Data Format in Registers           | 9   |

| 3.2   | Data Format in Memory              | 9   |

| 3.3   | -                                  | 10  |

|       |                                    |     |

| Secti | on 4 Floating-Point Unit (FPU)     | 11  |

| 4.1   | -                                  | 11  |

| 4.2   |                                    | 12  |

|       |                                    | 12  |

|       |                                    | 12  |

|       |                                    | 12  |

| 4.3   |                                    | 15  |

|       | -                                  | 15  |

|       | e                                  | 16  |

|       |                                    | 16  |

|       |                                    | 17  |

| 4.4   |                                    | 17  |

|       |                                    | 17  |

|       | 1                                  | 17  |

|       | -                                  | 18  |

|       |                                    | 18  |

|       |                                    | 18  |

| 4.5   |                                    | 18  |

|       |                                    |     |

| Secti | on 5 Instruction Features          | 19  |

| 5.1   |                                    | 19  |

| 5.2   |                                    | 22  |

|       | Rev. 2.00 May 31, 2006 page vii of | xii |

| 5.3  | Instruc | tion Format                                                          | 25   |

|------|---------|----------------------------------------------------------------------|------|

| Sect | tion 6  | Instruction Set                                                      | 29   |

| 6.1  | Instruc | tion Set by Classification                                           | 29   |

| 6.2  |         | tion Set in Alphabetical Order                                       |      |

| Sect | tion 7  | Instruction Descriptions                                             | 53   |

| 7.1  | Sample  | e Description (Name): Classification                                 | 53   |

| 7.2  | CPU II  | nstruction                                                           |      |

|      | 7.2.1   | ADD (ADD Binary): Arithmetic Instruction                             |      |

|      | 7.2.2   | ADDC (ADD with Carry): Arithmetic Instruction                        |      |

|      | 7.2.3   | ADDV (ADD with V Flag Overflow Check): Arithmetic Instruction        |      |

|      | 7.2.4   | AND (AND Logical): Logic Operation Instruction                       | 60   |

|      | 7.2.5   | BF (Branch if False): Branch Instruction                             | 62   |

|      | 7.2.6   | BF/S (Branch if False with Delay Slot): Branch Instruction           |      |

|      | 7.2.7   | BRA (Branch): Branch Instruction                                     | 65   |

|      | 7.2.8   | BRAF (Branch Far): Branch Instruction                                | 67   |

|      | 7.2.9   | BSR (Branch to Subroutine): Branch Instruction                       | 69   |

|      | 7.2.10  | BSRF (Branch to Subroutine Far): Branch Instruction                  | 71   |

|      | 7.2.11  | BT (Branch if True): Branch Instruction                              | 73   |

|      | 7.2.12  | BT/S (Branch if True with Delay Slot): Branch Instruction            | 74   |

|      | 7.2.13  |                                                                      |      |

|      | 7.2.14  | CLRT (Clear T Bit): System Control Instruction                       | 77   |

|      | 7.2.15  | CMP/cond (Compare Conditionally): Arithmetic Instruction             |      |

|      | 7.2.16  | DIV0S (Divide Step 0 as Signed): Arithmetic Instruction              | 82   |

|      | 7.2.17  | DIV0U (Divide Step 0 as Unsigned): Arithmetic Instruction            | 83   |

|      | 7.2.18  | DIV1 (Divide 1 Step): Arithmetic Instruction                         | . 84 |

|      | 7.2.19  | DMULS.L (Double-Length Multiply as Signed): Arithmetic Instruction   | . 89 |

|      | 7.2.20  | DMULU.L (Double-Length Multiply as Unsigned): Arithmetic Instruction | 91   |

|      | 7.2.21  | DT (Decrement and Test): Arithmetic Instruction                      | 93   |

|      | 7.2.22  | EXTS (Extend as Signed): Arithmetic Instruction                      | 94   |

|      | 7.2.23  | EXTU (Extend as Unsigned): Arithmetic Instruction                    | 95   |

|      | 7.2.24  | JMP (Jump): Branch Instruction                                       | 96   |

|      | 7.2.25  | JSR (Jump to Subroutine): Branch Instruction                         |      |

|      |         | (Class: Delayed Branch Instruction)                                  | 98   |

|      | 7.2.26  | LDC (Load to Control Register): System Control Instruction           |      |

|      |         | (Class: Interrupt Disabled Instruction)                              | 100  |

|      | 7.2.27  | LDS (Load to System Register): System Control Instruction            | 102  |

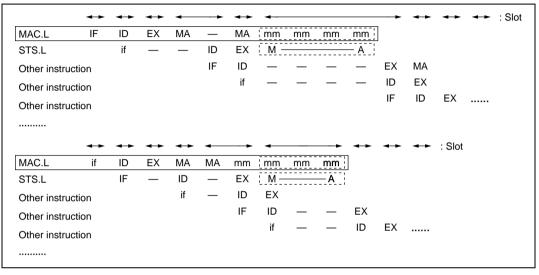

|      | 7.2.28  | MAC.L (Multiply and Accumulate Calculation Long):                    |      |

|      |         | Arithmetic Instruction                                               | 104  |

| 7.2.29 | MAC.W (Multiply and Accumulate Calculation Word):                   |     |

|--------|---------------------------------------------------------------------|-----|

|        | Arithmetic Instruction                                              | 107 |

| 7.2.30 | MOV (Move Data): Data Transfer Instruction                          | 110 |

| 7.2.31 | MOV (Move Immediate Data): Data Transfer Instruction                | 115 |

| 7.2.32 | MOV (Move Peripheral Data): Data Transfer Instruction               | 117 |

| 7.2.33 | MOV (Move Structure Data): Data Transfer Instruction                | 120 |

| 7.2.34 | MOVA (Move Effective Address): Data Transfer Instruction            | 123 |

| 7.2.35 | MOVT (Move T Bit): Data Transfer Instruction                        | 124 |

| 7.2.36 | MUL.L (Multiply Long): Arithmetic Instruction                       | 125 |

| 7.2.37 | MULS.W (Multiply as Signed Word): Arithmetic Instruction            | 126 |

| 7.2.38 | MULU.W (Multiply as Unsigned Word): Arithmetic Instruction          | 127 |

| 7.2.39 | NEG (Negate): Arithmetic Instruction                                | 128 |

| 7.2.40 | NEGC (Negate with Carry): Arithmetic Instruction                    | 129 |

| 7.2.41 | NOP (No Operation): System Control Instruction                      | 130 |

| 7.2.42 | NOT (NOT-Logical Complement): Logic Operation Instruction           | 131 |

| 7.2.43 | OR (OR Logical) Logic Operation Instruction                         | 132 |

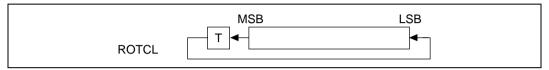

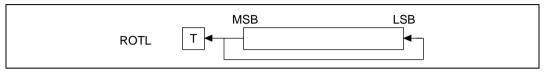

| 7.2.44 | ROTCL (Rotate with Carry Left): Shift Instruction                   | 134 |

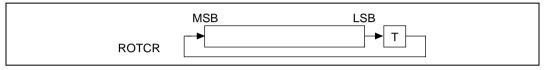

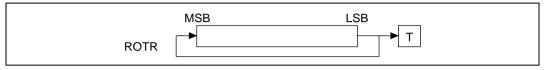

| 7.2.45 | ROTCR (Rotate with Carry Right): Shift Instruction                  | 135 |

| 7.2.46 | ROTL (Rotate Left): Shift Instruction                               | 136 |

| 7.2.47 | ROTR (Rotate Right): Shift Instruction                              | 137 |

| 7.2.48 | RTE (Return from Exception): System Control Instruction             | 138 |

| 7.2.49 | RTS (Return from Subroutine): Branch Instruction                    |     |

|        | (Class: Delayed Branch Instruction)                                 | 140 |

| 7.2.50 | SETT (Set T Bit): System Control Instruction                        | 142 |

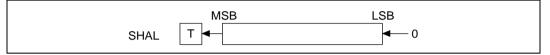

| 7.2.51 | SHAL (Shift Arithmetic Left): Shift Instruction                     | 143 |

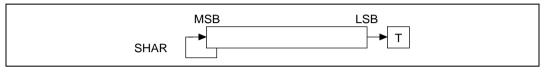

| 7.2.52 | SHAR (Shift Arithmetic Right): Shift Instruction                    | 144 |

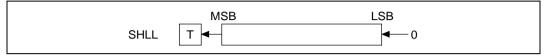

| 7.2.53 | SHLL (Shift Logical Left): Shift Instruction                        | 145 |

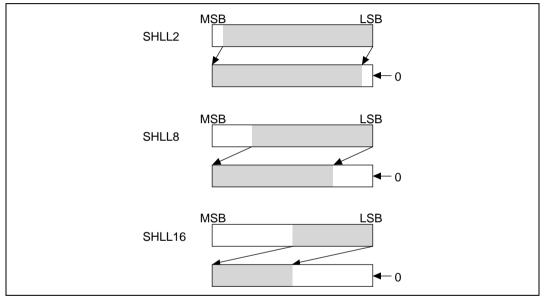

| 7.2.54 | SHLLn (Shift Logical Left n Bits): Shift Instruction                | 146 |

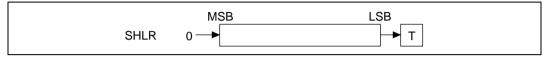

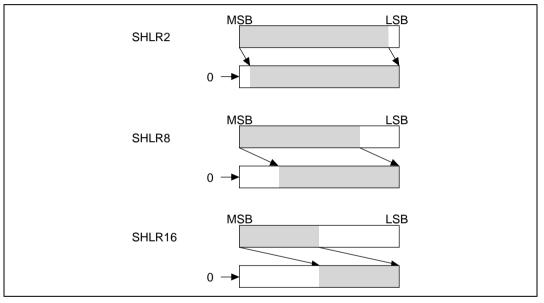

| 7.2.55 | SHLR (Shift Logical Right): Shift Instruction                       | 148 |

| 7.2.56 | SHLRn (Shift Logical Right n Bits): Shift Instruction               |     |

| 7.2.57 | SLEEP (Sleep): System Control Instruction                           | 151 |

| 7.2.58 | STC (Store Control Register): System Control Instruction            |     |

|        | (Interrupt Disabled Instruction)                                    | 152 |

| 7.2.59 | STS (Store System Register): System Control Instruction             |     |

|        | (Interrupt Disabled Instruction)                                    | 154 |

| 7.2.60 | SUB (Subtract Binary): Arithmetic Instruction                       | 156 |

| 7.2.61 | SUBC (Subtract with Carry): Arithmetic Instruction                  |     |

| 7.2.62 | SUBV (Subtract with V Flag Underflow Check): Arithmetic Instruction |     |

| 7.2.63 | SWAP (Swap Register Halves): Data Transfer Instruction              |     |

| 7.2.64 | TAS (Test and Set): Logic Operation Instruction                     |     |

| 7.2.65 | TRAPA (Trap Always): System Control Instruction                     | 162 |

Rev. 2.00 May 31, 2006 page ix of xii

| 7.2.66   | TST (Test Logical): Logic Operation Instruction                                                                                                                                                                                                                                                                                                                                | 163                                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| 7.2.67   | XOR (Exclusive OR Logical): Logic Operation Instruction                                                                                                                                                                                                                                                                                                                        | 165                                                                            |

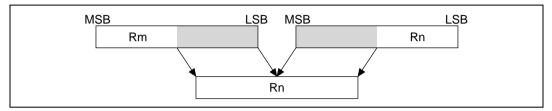

| 7.2.68   | XTRCT (Extract): Data Transfer Instruction                                                                                                                                                                                                                                                                                                                                     | 167                                                                            |

| Floating | g Point Instructions and FPU Related CPU Instructions                                                                                                                                                                                                                                                                                                                          | 168                                                                            |

| 7.3.1    | FABS (Floating Point Absolute Value): Floating Point Instruction                                                                                                                                                                                                                                                                                                               | 170                                                                            |

| 7.3.2    | FADD (Floating Point Add): Floating Point Instruction                                                                                                                                                                                                                                                                                                                          | 172                                                                            |

| 7.3.3    | FCMP (Floating Point Compare): Floating Point Instruction                                                                                                                                                                                                                                                                                                                      | 175                                                                            |

| 7.3.4    | FDIV (Floating Point Divide): Floating Point Instruction                                                                                                                                                                                                                                                                                                                       | 179                                                                            |

| 7.3.5    | FLDI0 (Floating Point Load Immediate 0): Floating Point Instruction                                                                                                                                                                                                                                                                                                            | 181                                                                            |

| 7.3.6    | FLDI1 (Floating Point Load Immediate 1): Floating Point Instruction                                                                                                                                                                                                                                                                                                            | 182                                                                            |

| 7.3.7    | FLDS (Floating Point Load to System Register): Floating Point Instruction                                                                                                                                                                                                                                                                                                      | 183                                                                            |

| 7.3.8    | FLOAT (Floating Point Convert from Integer): Floating Point Instruction                                                                                                                                                                                                                                                                                                        | 184                                                                            |

| 7.3.9    | FMAC (Floating Point Multiply Accumulate): Floating Point Instruction                                                                                                                                                                                                                                                                                                          | 185                                                                            |

| 7.3.10   | FMOV (Floating Point Move): Floating Point Instruction                                                                                                                                                                                                                                                                                                                         | 188                                                                            |

| 7.3.11   | FMUL (Floating Point Multiply): Floating Point Instruction                                                                                                                                                                                                                                                                                                                     | 192                                                                            |

| 7.3.12   | FNEG (Floating Point Negate): Floating Point Instruction                                                                                                                                                                                                                                                                                                                       | 194                                                                            |

| 7.3.13   | FSTS (Floating Point Store From System Register): Floating Point                                                                                                                                                                                                                                                                                                               |                                                                                |

|          | Instruction                                                                                                                                                                                                                                                                                                                                                                    | 195                                                                            |

| 7.3.14   | FSUB (Floating Point Subtract): Floating Point Instruction                                                                                                                                                                                                                                                                                                                     | 196                                                                            |

| 7.3.15   | FTRC (Floating Point Truncate And Convert To Integer): Floating Point                                                                                                                                                                                                                                                                                                          |                                                                                |

|          | Instruction                                                                                                                                                                                                                                                                                                                                                                    | 199                                                                            |

| 7.3.16   | LDS (Load to System Register): FPU Related CPU Instruction                                                                                                                                                                                                                                                                                                                     | 201                                                                            |

| 7.3.17   | STS (Store from FPU System Register): FPU Related CPU Instruction                                                                                                                                                                                                                                                                                                              | 204                                                                            |

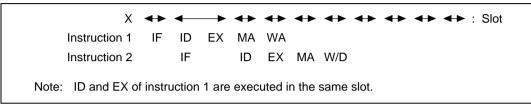

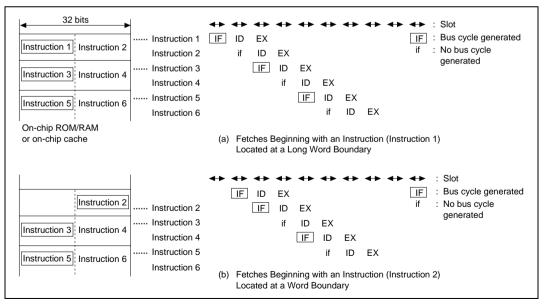

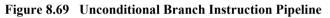

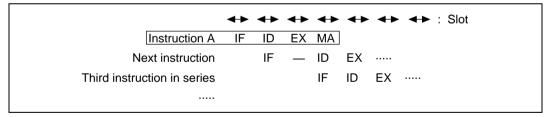

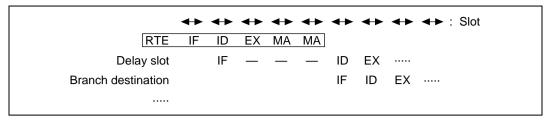

| on 8 1   | Pipeline Operation                                                                                                                                                                                                                                                                                                                                                             | 207                                                                            |

|          | · ·                                                                                                                                                                                                                                                                                                                                                                            |                                                                                |

| Slot and | d Pipeline Flow                                                                                                                                                                                                                                                                                                                                                                | 209                                                                            |

|          | *                                                                                                                                                                                                                                                                                                                                                                              |                                                                                |

|          | •                                                                                                                                                                                                                                                                                                                                                                              |                                                                                |

| Effects  | of Memory Load Instructions on the Pipeline.                                                                                                                                                                                                                                                                                                                                   | 215                                                                            |

|          |                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

| Program  | nming Guide                                                                                                                                                                                                                                                                                                                                                                    | 217                                                                            |

| Operati  | on of Instruction Pipelines                                                                                                                                                                                                                                                                                                                                                    | 218                                                                            |

| 8.8.1    | Data Transfer Instructions                                                                                                                                                                                                                                                                                                                                                     | 228                                                                            |

| 8.8.2    | Arithmetic Instructions                                                                                                                                                                                                                                                                                                                                                        | 231                                                                            |

| 8.8.3    | Logic Operation Instructions                                                                                                                                                                                                                                                                                                                                                   | 265                                                                            |

| 8.8.4    | Shift Instructions                                                                                                                                                                                                                                                                                                                                                             | 267                                                                            |

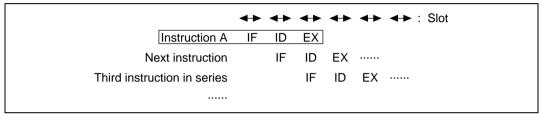

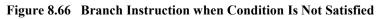

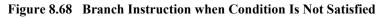

| 8.8.5    | Branch Instructions                                                                                                                                                                                                                                                                                                                                                            | 268                                                                            |

| 8.8.6    | System Control Instructions                                                                                                                                                                                                                                                                                                                                                    | 271                                                                            |

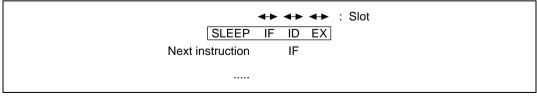

| 8.8.7    | Exception Processing                                                                                                                                                                                                                                                                                                                                                           | 277                                                                            |

|          | 7.2.67<br>7.2.68<br>Floating<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6<br>7.3.7<br>7.3.8<br>7.3.7<br>7.3.8<br>7.3.9<br>7.3.10<br>7.3.11<br>7.3.12<br>7.3.13<br>7.3.14<br>7.3.13<br>7.3.14<br>7.3.15<br>7.3.16<br>7.3.17<br>0n 8 I<br>Basic C<br>Slot and<br>Numbe<br>Conten<br>Effects<br>FPU Co<br>Prograti<br>8.8.1<br>8.8.2<br>8.8.3<br>8.8.4<br>8.8.5<br>8.8.6 | <ul> <li>7.3.2 FADD (Floating Point Add): Floating Point Instruction</li></ul> |

|      | 8.8.8    | Relationship between Floating-point Instructions and FPU-related CPU |     |

|------|----------|----------------------------------------------------------------------|-----|

|      |          | Instructions                                                         | 279 |

|      |          |                                                                      |     |

| Appe | endix A  | Instruction Code                                                     | 293 |

| A.1  | Instruct | ion Set by Addressing Mode                                           | 293 |

|      | A.1.1    | No Operand                                                           |     |

|      | A.1.2    | Direct Register Addressing                                           | 295 |

|      | A.1.3    | Indirect Register Addressing                                         | 299 |

|      | A.1.4    | Post-Increment Indirect Register Addressing                          |     |

|      | A.1.5    | Pre-Decrement Indirect Register Addressing                           | 301 |

|      | A.1.6    | Indirect Register Addressing with Displacement                       | 301 |

|      | A.1.7    | Indirect Indexed Register Addressing                                 | 302 |

|      | A.1.8    | Indirect GBR Addressing with Displacement                            |     |

|      | A.1.9    | Indirect Indexed GBR Addressing                                      | 303 |

|      | A.1.10   | PC Relative Addressing with Displacement                             | 303 |

|      | A.1.11   | PC Relative Addressing                                               | 304 |

|      | A.1.12   | Immediate                                                            | 305 |

| A.2  | Instruct | ion Sets by Instruction Format                                       | 306 |

|      | A.2.1    | 0 Format                                                             | 307 |

|      | A.2.2    | n Format                                                             | 308 |

|      | A.2.3    | m Format                                                             | 310 |

|      | A.2.4    | nm Format                                                            | 312 |

|      | A.2.5    | md Format                                                            | 316 |

|      | A.2.6    | nd4 Format                                                           | 316 |

|      | A.2.7    | nmd Format                                                           | 316 |

|      | A.2.8    | d Format                                                             | 317 |

|      | A.2.9    | d12 Format                                                           | 318 |

|      | A.2.10   | nd8 Format                                                           | 318 |

|      | A.2.11   | i Format                                                             | 318 |

|      | A.2.12   | ni Format                                                            | 319 |

| A.3  | Instruct | ion Set by Instruction Code                                          | 320 |

| A.4  | Operati  | on Code Map                                                          | 329 |

|      | –        |                                                                      |     |

| Appe | endix B  | B Pipeline Operation and Contention                                  | 332 |

Rev. 2.00 May 31, 2006 page xii of xii

# Section 1 Features

#### 1.1 SH-2E Features

The SH-2E CPU has RISC-type instruction sets. Basic instructions are executed in one clock cycle, which dramatically improves instruction execution speed. The CPU also has an internal 32-bit architecture for enhanced data processing ability. Table 1.1 lists the SH-2E CPU features.

| Item                       | Feature                                                                                                                                                                                                                                                                                                                          |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Architecture               | Original Renesas Technology architecture                                                                                                                                                                                                                                                                                         |  |

|                            | 32-bit internal data bus                                                                                                                                                                                                                                                                                                         |  |

| General-register machine   | Sixteen 32-bit general registers                                                                                                                                                                                                                                                                                                 |  |

|                            | Three 32-bit control registers                                                                                                                                                                                                                                                                                                   |  |

|                            | Four 32-bit system registers                                                                                                                                                                                                                                                                                                     |  |

|                            | Sixteen 32-bit froating-point registers                                                                                                                                                                                                                                                                                          |  |

|                            | Two 32-bit froating point system registers                                                                                                                                                                                                                                                                                       |  |

| Instruction set            | Instruction length: 16-bit fixed length for improved code efficiency                                                                                                                                                                                                                                                             |  |

|                            | Load-store architecture (basic arithmetic and logic operations are                                                                                                                                                                                                                                                               |  |

|                            | executed between registers)                                                                                                                                                                                                                                                                                                      |  |

|                            | Delayed branch system used for reduced pipeline disruption                                                                                                                                                                                                                                                                       |  |

|                            | Instruction set optimized for C language                                                                                                                                                                                                                                                                                         |  |

| Instruction execution time | One instruction/cycle for basic instructions                                                                                                                                                                                                                                                                                     |  |

| Address space              | Architecture makes 4 Gbytes available                                                                                                                                                                                                                                                                                            |  |

| On-chip multiplier         | <ul> <li>Multiplication operations executed in 1 to 2 cycles (16 bits × 16 bits → 32 bits) or 2 to 4 cycles (32 bits × 32 bits → 64 bits), and multiplication/accumulation operations executed in 3/(2)* cycles (16 bits × 16 bits + 64 bits → 64 bits) or 3/(2 to 4)* cycles (32 bits × 32 bits + 64 bits → 64 bits)</li> </ul> |  |

| Pipeline                   | Five-stage pipeline                                                                                                                                                                                                                                                                                                              |  |

| Processing states          | Reset state                                                                                                                                                                                                                                                                                                                      |  |

|                            | Exception processing state                                                                                                                                                                                                                                                                                                       |  |

|                            | Program execution state                                                                                                                                                                                                                                                                                                          |  |

|                            | Power-down state                                                                                                                                                                                                                                                                                                                 |  |

|                            | Bus release state                                                                                                                                                                                                                                                                                                                |  |

| Table 1.1 | SH-2E C | <b>CPU Features</b> |

|-----------|---------|---------------------|

|-----------|---------|---------------------|

| Item              | Feature                                                                                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------|

| Power-down states | Sleep mode                                                                                                           |

|                   | Standby mode                                                                                                         |

| FPU               | Single-precision floating point format                                                                               |

|                   | Subset of IEEE754 standard data types                                                                                |

|                   | <ul> <li>Invalid calculation exception and divide-by-zero exception (in compliance with IEEE754 standard)</li> </ul> |

|                   | Rounding to zero (in compliance with IEEE754 standard)                                                               |

|                   | General purpose register file, 16 32-bit floating point registers                                                    |

|                   | <ul> <li>Execution pitch for basic instructions: 1 cycle/latency or 2 cycles<br/>(FADD, FSUB, FMUL)</li> </ul>       |

|                   | FMAC (floating point multiply accumulate)                                                                            |

|                   | Execution pitch: 1 cycle/latency or 2 cycles                                                                         |

|                   | Support for FDIV                                                                                                     |

|                   | <ul> <li>Support for FLDI0 and FLDI1 (load constant 0/1)</li> </ul>                                                  |

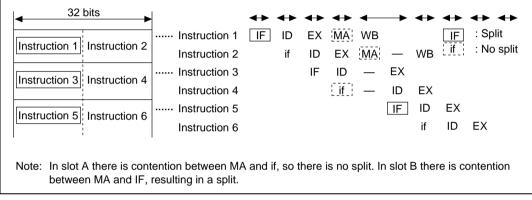

number in contention with preceding/following instructions.

# Section 2 Register Configuration

The register set consists of sixteen 32-bit general registers, three 32-bit control registers and four 32-bit system registers.

# 2.1 General Registers

There are 16 general registers (Rn) numbered R0–R15, which are 32 bits in length. General registers are used for data processing and address calculation. R0 is also used as an index register. Several instructions use R0 as a fixed source or destination register. R15 is used as the hardware stack pointer (SP). Saving and recovering the status register (SR) and program counter (PC) in exception processing is accomplished by referencing the stack using R15.

| 21                                                                                                                                                                                                                                                                                                             |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 31 0<br>R0 <sup>*1</sup>                                                                                                                                                                                                                                                                                       |  |  |

| R1                                                                                                                                                                                                                                                                                                             |  |  |

| R2                                                                                                                                                                                                                                                                                                             |  |  |

| R3                                                                                                                                                                                                                                                                                                             |  |  |

| R4                                                                                                                                                                                                                                                                                                             |  |  |

| R5                                                                                                                                                                                                                                                                                                             |  |  |

| R6                                                                                                                                                                                                                                                                                                             |  |  |

| R7                                                                                                                                                                                                                                                                                                             |  |  |

| R8                                                                                                                                                                                                                                                                                                             |  |  |

| R9                                                                                                                                                                                                                                                                                                             |  |  |

| R10                                                                                                                                                                                                                                                                                                            |  |  |

| R11                                                                                                                                                                                                                                                                                                            |  |  |

| R12                                                                                                                                                                                                                                                                                                            |  |  |

| R13                                                                                                                                                                                                                                                                                                            |  |  |

| R14                                                                                                                                                                                                                                                                                                            |  |  |

| R15, SP (hardware stack pointer) <sup>*2</sup>                                                                                                                                                                                                                                                                 |  |  |

| R0 functions as an index register in the indirect indexed<br>register addressing mode and indirect indexed GBR<br>addressing mode. In some instructions, R0 functions as<br>a fixed source register or destination register.<br>R15 functions as a hardware stack pointer (SP) during<br>exception processing. |  |  |

#### Figure 2.1 General Registers (SH-1 and SH-2)

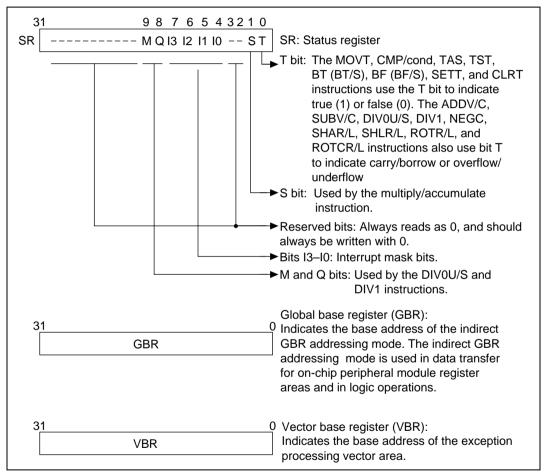

## 2.2 Control Registers

The 32-bit control registers consist of the 32-bit status register (SR), global base register (GBR), and vector base register (VBR). The status register indicates processing states. The global base register functions as a base address for the indirect GBR addressing mode to transfer data to the registers of on-chip peripheral modules. The vector base register functions as the base address of the exception processing vector area (including interrupts).

Figure 2.2 Control Registers

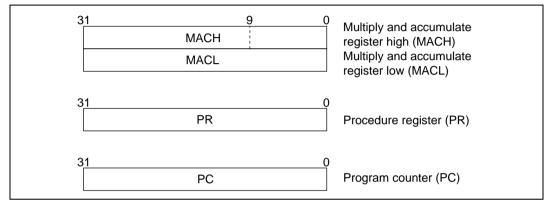

#### 2.3 System Registers

System registers consist of four 32-bit registers: high and low multiply and accumulate registers (MACH and MACL), the procedure register (PR), and the program counter (PC). The multiply and accumulate registers store the results of multiply and multiply and accumulate operations. The procedure register stores the return address from the subroutine procedure. The program counter indicates the address of the program executing and controls the flow of the processing.

Figure 2.3 Organization of the System Registers

## 2.4 Floating-Point Registers

There are sixteen 32-bit floating-point registers, designated FR0 to FR15, which are used by floating-point instructions. FR0 functions as the index register for the FMAC instruction. These registers are incorporated into the floating-point unit (FPU). For details, see section 4, Floating-Point Unit (FPU).

| 31 |      | 0                                                             |

|----|------|---------------------------------------------------------------|

|    | FR0  | FR0 functions as the index register for the FMAC instruction. |

|    | FR1  |                                                               |

|    | FR2  |                                                               |

|    | FR3  |                                                               |

|    | FR4  |                                                               |

|    | FR5  |                                                               |

|    | FR6  |                                                               |

|    | FR7  |                                                               |

|    | FR8  |                                                               |

|    | FR9  |                                                               |

|    | FR10 |                                                               |

|    | FR11 |                                                               |

|    | FR12 |                                                               |

|    | FR13 |                                                               |

|    | FR14 |                                                               |

|    | FR15 |                                                               |

Figure 2.4 Floating-Point Registers

#### 2.5 Floating-Point System Registers

There are two 32-bit floating-point system registers: the floating-point communication register (FPUL) and the floating-point status/control register (FPSCR). FPUL is used for communication between the CPU and the floating-point unit (FPU). FPSCR indicates and stores status/control information relating to FPU exceptions.

These registers are incorporated into the floating-point unit (FPU). For details, see section 4, Floating-Point Unit (FPU).

| 31    | 0 |        |                                                                               |

|-------|---|--------|-------------------------------------------------------------------------------|

| FPUL  |   | FPUL:  | Floating-point communication register<br>Used for communication between       |

|       |   |        | the CPU and the FPU.                                                          |

| 31    | 0 |        |                                                                               |

| FPSCR |   | FPSCR: | Floating-point status/control register<br>Indicates and stores status/control |

|       |   |        | information relating to FPU exceptions.                                       |

Figure 2.5 Floating-Point System Registers

#### 2.6 Initial Values of Registers

Table 2.1 lists the values of the registers after reset.

#### Table 2.1Initial Values of Registers

| Classification                  | Register       | Initial Value                                                                |

|---------------------------------|----------------|------------------------------------------------------------------------------|

| General registers               | R0–R14         | Undefined                                                                    |

|                                 | R15 (SP)       | Value of the stack pointer in the vector address table                       |

| Control registers               | SR             | Bits I3–I0 are 1111 (H'F), reserved bits are 0, and other bits are undefined |

|                                 | GBR            | Undefined                                                                    |

|                                 | VBR            | H'0000000                                                                    |

| System registers                | MACH, MACL, PR | Undefined                                                                    |

|                                 | PC             | Value of the program counter in the vector address table                     |

| Floating-point registers        | FR0–FR15       | Undefined                                                                    |

| Floating-point system registers | FPUL           | Undefined                                                                    |

|                                 | FPSCR          | H'00040001                                                                   |

# Section 3 Data Formats

#### **3.1 Data Format in Registers**

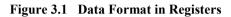

Register operands are always longwords (32 bits). When data in memory is loaded to a register and the memory operand is only a byte (8 bits) or a word (16 bits), it is sign-extended into a longword when stored into a register.

| 3 | 1 (      |  |

|---|----------|--|

|   | Longword |  |

|   |          |  |

#### **3.2** Data Format in Memory

Memory data formats are classified into bytes, words, and longwords. Byte data can be accessed from any address, but an address error will occur if you try to access word data starting from an address other than 2n or longword data starting from an address other than 4n. In such cases, the data accessed cannot be guaranteed. The hardware stack area, which is referred to by the hardware stack pointer (SP, R15), uses only longword data starting from address 4n because this area stores the program counter (PC) and status register (SR). See the hardware manual for more information on address errors.

Figure 3.2 Data Format in Memory

## 3.3 Immediate Data Format

Byte immediate data is located in an instruction code. Immediate data accessed by the MOV, ADD, and CMP/EQ instructions is sign-extended and is handled in registers as longword data. Immediate data accessed by the TST, AND, OR, and XOR instructions is zero-extended and is handled as longword data. Consequently, AND instructions with immediate data always clear the upper 24 bits of the destination register.

Word or longword immediate data is not located in the instruction code but rather is stored in a memory table. The memory table is accessed by a immediate data transfer instruction (MOV) using the PC relative addressing mode with displacement. Specific examples are given in 5.1 Immediate Data in Section 5, Instruction Features.

# Section 4 Floating-Point Unit (FPU)

## 4.1 Overview

The SH-2E has an on-chip floating-point unit (FPU), The FPU's register configuration is shown in figure 4.1.

| 31 0                                            |                                                                                                              |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| FR0                                             | FR0 functions as the index register                                                                          |

| FR1                                             | for the FMAC instruction.                                                                                    |

| FR2                                             |                                                                                                              |

| FR3                                             |                                                                                                              |

| FR4                                             |                                                                                                              |

| FR5                                             |                                                                                                              |

| FR6                                             |                                                                                                              |

| FR7                                             |                                                                                                              |

| FR8                                             |                                                                                                              |

| FR9                                             |                                                                                                              |

| FR10                                            |                                                                                                              |

| FR11                                            |                                                                                                              |

| FR12                                            |                                                                                                              |

| FR13                                            |                                                                                                              |

| FR14                                            |                                                                                                              |

| FR15                                            |                                                                                                              |

| Floating-point system registers<br>31 0<br>FPUL | Floating-point communication register<br>Specifies buffer as communication register between<br>CPU and FPU*. |

| 31 0                                            | Floating-point status/control register<br>Indicates status/control information relating to FPU               |

| FPSCR                                           | exceptions*.                                                                                                 |

(Floating-Point Registers and Floating-Point System Registers)

## 4.2 Floating-Point Registers and Floating-Point System Registers

#### 4.2.1 Floating-Point Register File

The SH-2E has sixteen 32-bit single-precision floating-point registers. Register specifications are always made as 4 bits. In assembly language, the floating-point registers are specified as FR0, FR1, FR2, and so on. FR0 functions as the index register for the FMAC instruction.

#### 4.2.2 Floating-Point Communication Register (FPUL)

Information for transfer between the FPU and the CPU is transferred via the FPUL communication register, which resembles MACL and MACH in the integer unit. The SH-2E is provided with this communication register since the integer and floating-point formats are different. The 32-bit FPUL is a system register, and is accessed by the CPU by means of LDS and STS instructions.

#### 4.2.3 Floating-Point Status/Control Register (FPSCR)

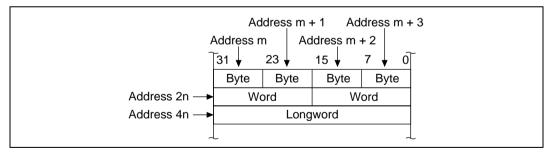

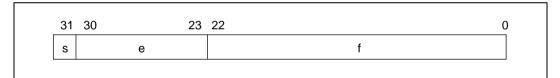

The SH-2E has a floating-point status/control register (FPSCR) that functions as a system register accessed by means of LDS and STS instructions (figure 4.2). FPSCR can be written to by a user program. This register is part of the process context, and must be saved when the context is switched. It may also be necessary to save this register when a procedure call is made.

FPSCR is a 32-bit register that controls the storage of detailed information relating to the rounding mode, asymptotic underflow (denormalized numbers), and FPU exceptions. The module stop bit that disables the FPU itself is provided in the module standby control register (MSTCR). For details, refer to hardware manual. After a reset start, the FPU is enabled.

Table 4.1 shows the flags corresponding the five kinds of FPU exception. A sixth flag is also provided as an FPU error flag that indicates an floating-point unit error state not covered by the other five flags.

| Flag | Meaning                         | Support in SH-2E |

|------|---------------------------------|------------------|

| E    | FPU error                       | _                |

| V    | Invalid operation               | Yes              |

| Z    | Division by zero                | Yes              |

| 0    | Overflow (value not expressed)  | _                |

| U    | Underflow (value not expressed) | _                |

|      | Inexact (result not expressed)  | _                |

#### Table 4.1Floating-Point Exception Flags

The bits in the cause field indicate the exception cause for the instruction executing at the time. The cause bits are modified by a floating-point instruction. These bits are set to 1 or cleared to 0 according to whether or not an exception state occurred during execution of a single instruction.

The bits in the enable field specify the kinds of exception to be enabled, allowing the flow to be changed to exception processing. If the cause bit corresponding to an enable bit is set by the currently executing instruction, an exception occurs.

The bits in the flag field are used to keep a tally of all exceptions that occur during a series of instructions. Once one of these bits is set by an instruction, it is not reset by a subsequent instruction. The bits in this field can only be reset by the explicit execution of a store operation on FPSCR.

| 31    | 19         18         17         16         15         14         13         12         11         10         9         8         7         6         5         4         3         2         1           Cause field         Enable field         Flag field           Reserved         DN CE CV CZ CO CU CI EV EZ EO EU EI FV FZ FO FU FI RM |