# RZ/N1D Group, RZ/N1S Group, RZ/N1L Group

User's Manual: R-IN Engine and Ethernet Peripherals

RZ Family RZ/N Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### **Notice**

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products

and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your

product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of

these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="https://www.renesas.com/contact/">www.renesas.com/contact/</a>.

# General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

- 1. Precaution against Electrostatic Discharge (ESD)

- A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

- 2. Processing at power-on

- The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

- Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements.

Follow the guideline for input signal during power-off state as described in your product documentation.

- 4. Handling of unused pins

- Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

- 5. Clock signals

- After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

- 6. Voltage application waveform at input pin

- Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

- 7. Prohibition of access to reserved addresses

- Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

- 8. Differences between products

- Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

# How to Use This Manual

### 1. Objective and Target Users

This manual was written to explain the hardware functions and electrical characteristics of this LSI to the target users, i.e. those who will be using this LSI in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logic circuits, and microcomputers.

This manual is organized in the following items: an overview of the product, descriptions of the CPU, system control functions, and peripheral functions, electrical characteristics of the device, and usage notes.

When designing an application system that includes this LSI, take all points to note into account. Points to note are given in their contexts and at the final part of each section, and in the section giving usage notes.

The list of revisions is a summary of major points of revision or addition for earlier versions. It does not cover all revised items. For details on the revised points, see the actual locations in the manual.

The following documents have been prepared for reference.

#### ■ Documents related to RZ/N1

| Document Name                                                                                                                    | Document Number                  |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group DATASHEET                                                                               | R01DS0323EJ****                  |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: System Introduction, Multiplexing, Electrical and Mechanical Information | R01UH0750EJ****                  |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: System Control and Peripheral                                            | R01UH0751EJ****                  |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: Peripherals                                                              | R01UH0752EJ****                  |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: R-IN Engine and Ethernet Peripherals                                     | R01UH0753EJ****<br>(this manual) |

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's Manual: PWMTimer                                                                 | R01UH0913EJ****                  |

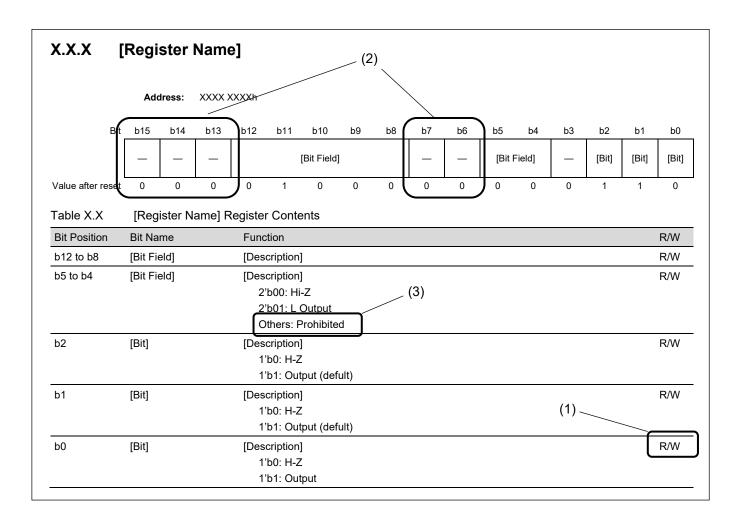

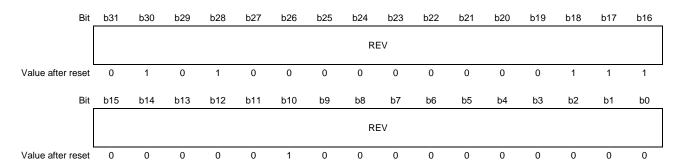

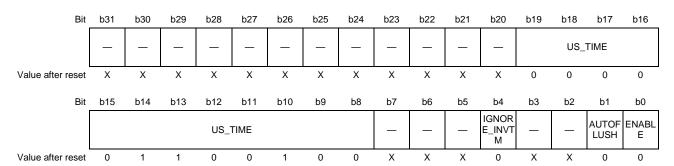

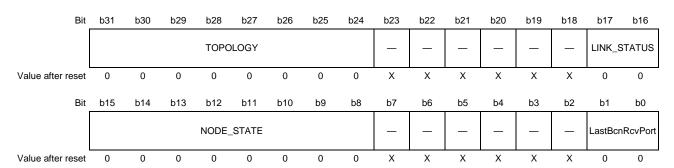

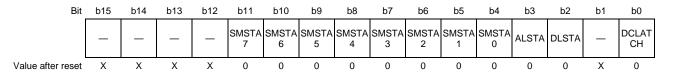

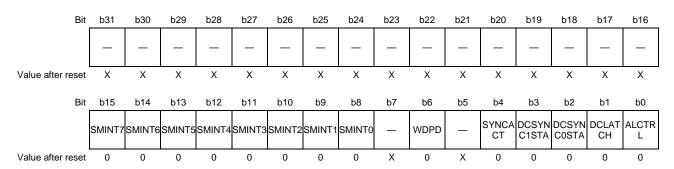

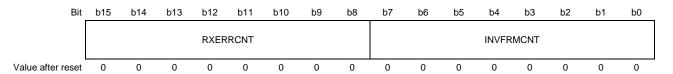

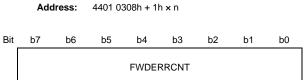

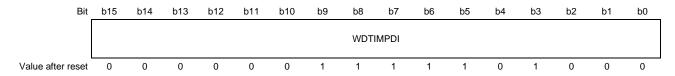

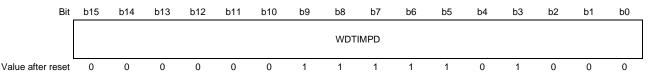

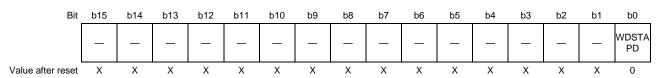

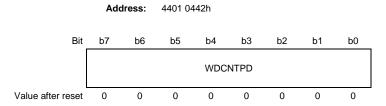

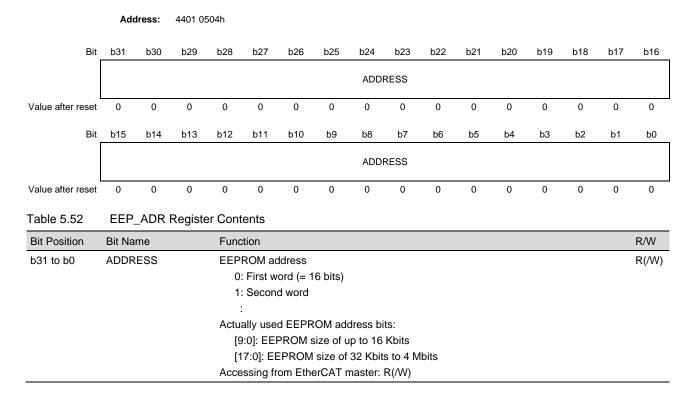

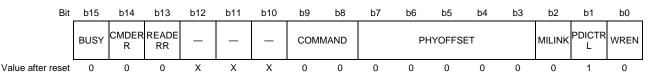

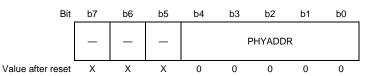

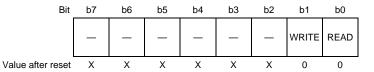

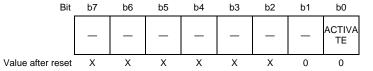

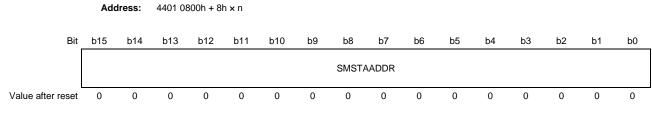

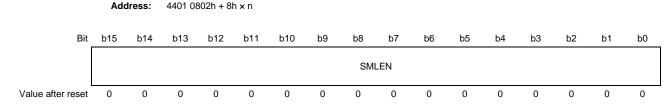

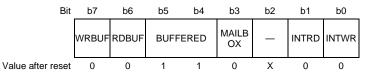

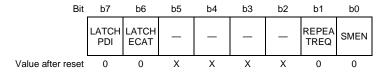

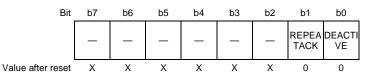

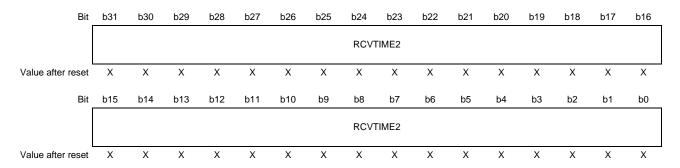

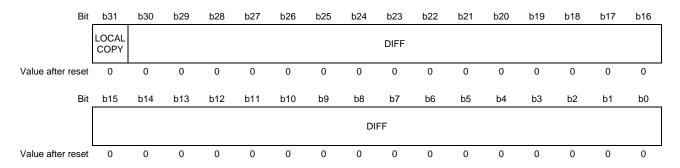

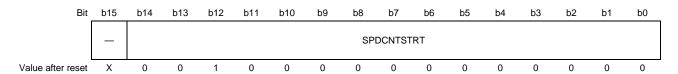

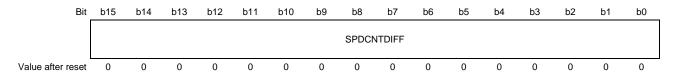

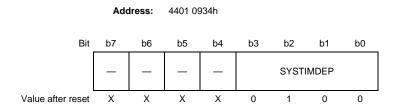

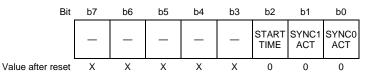

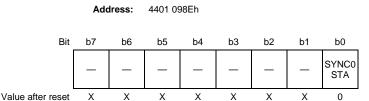

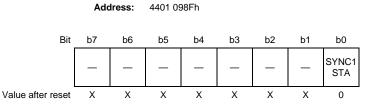

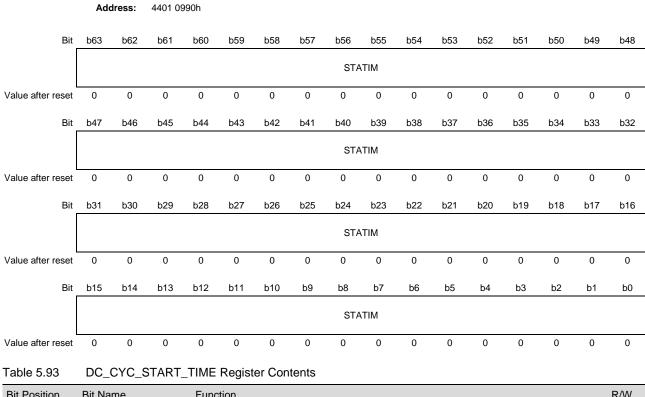

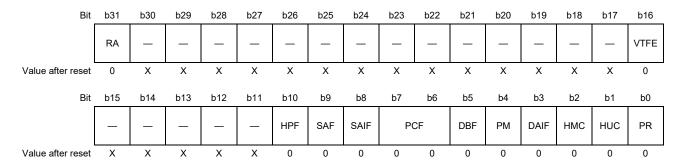

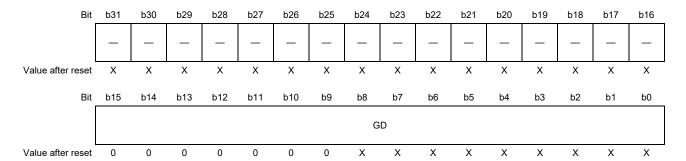

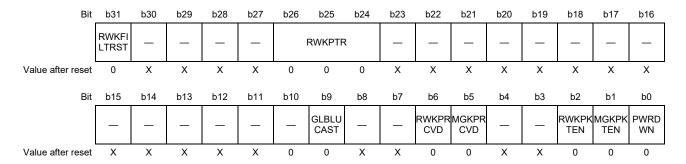

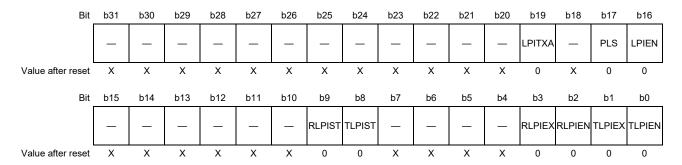

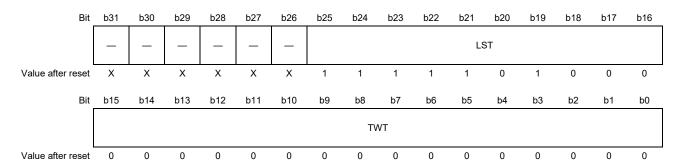

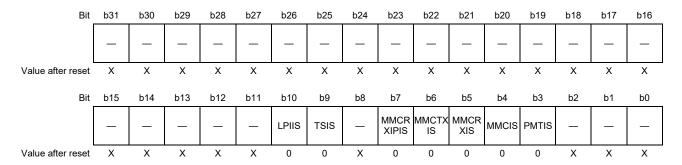

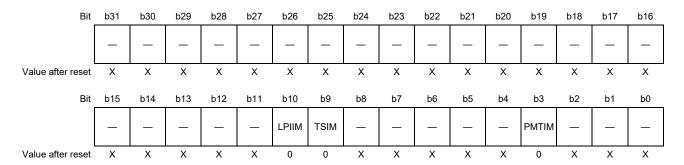

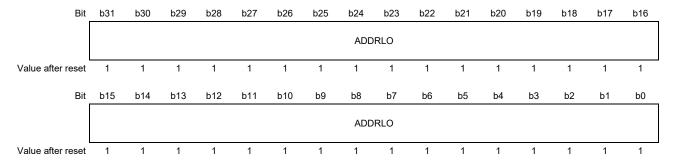

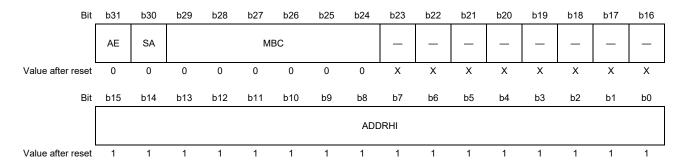

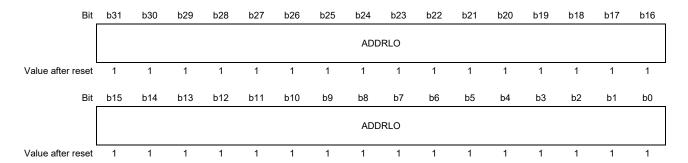

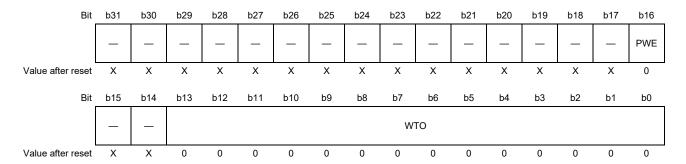

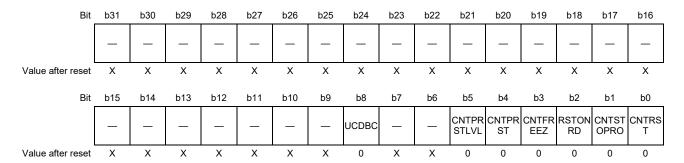

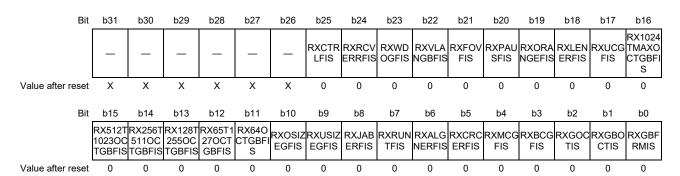

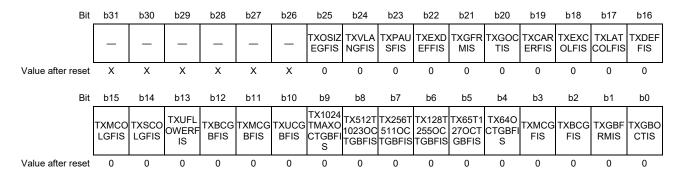

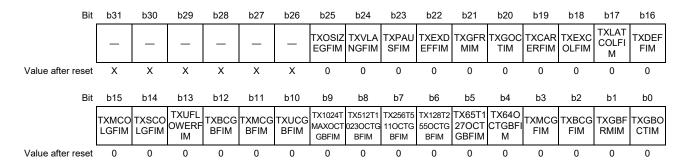

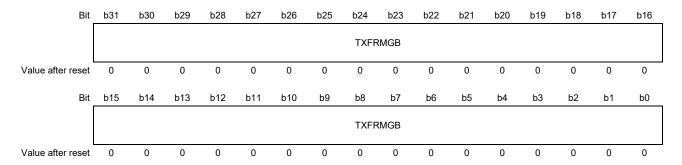

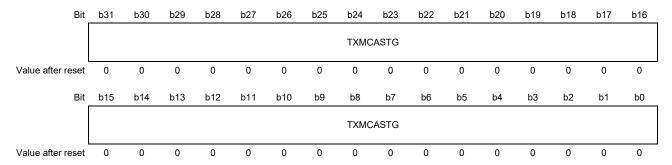

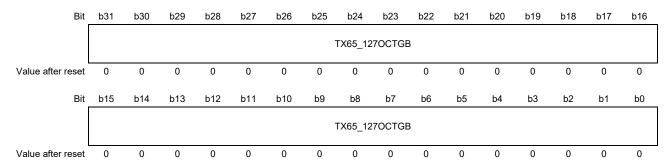

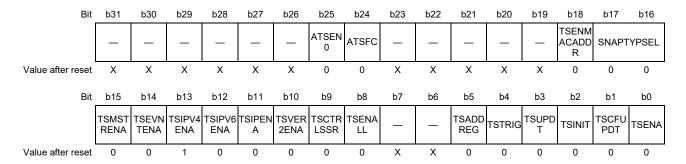

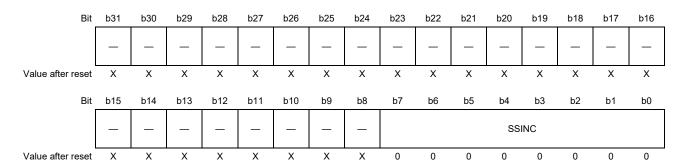

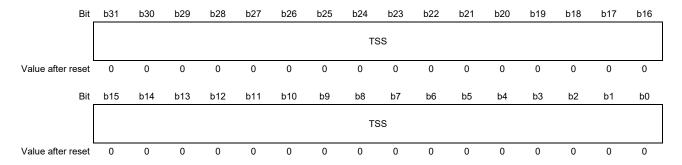

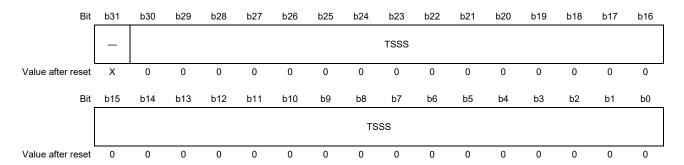

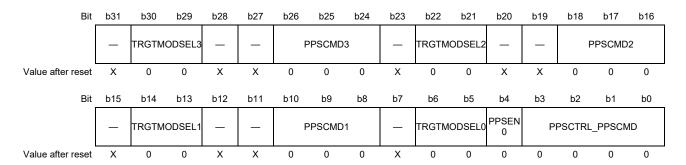

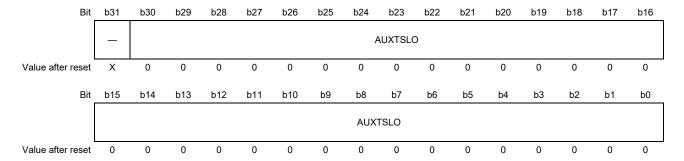

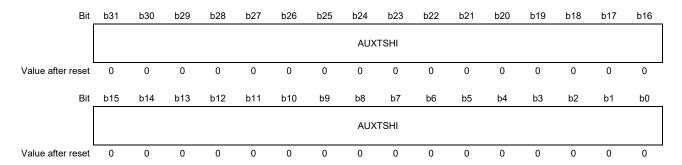

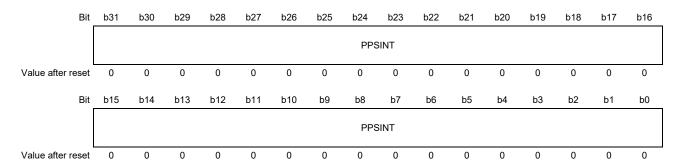

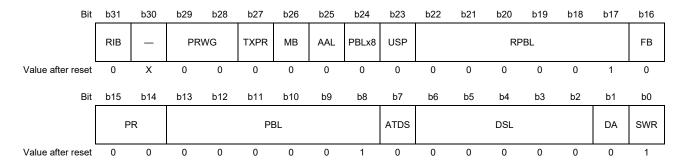

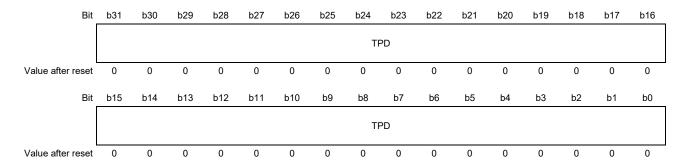

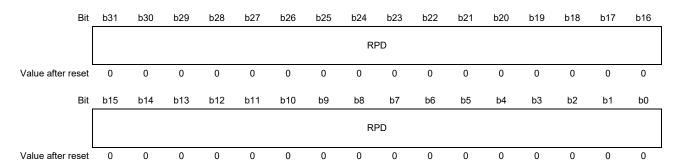

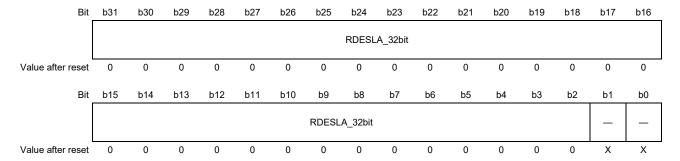

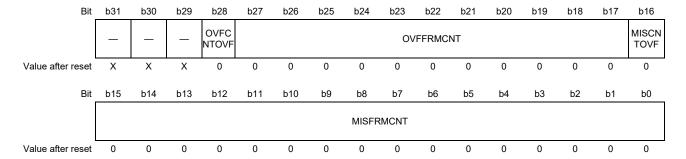

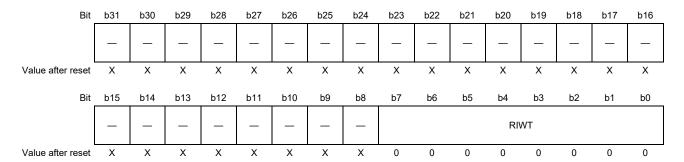

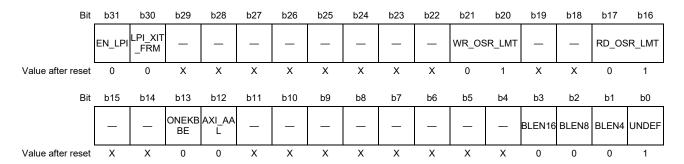

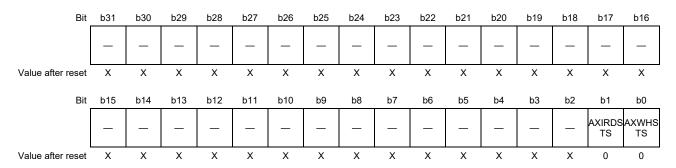

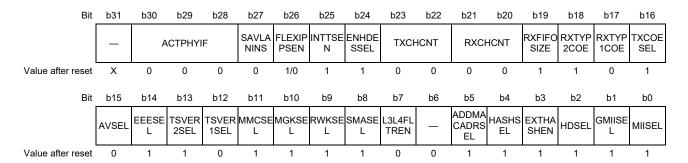

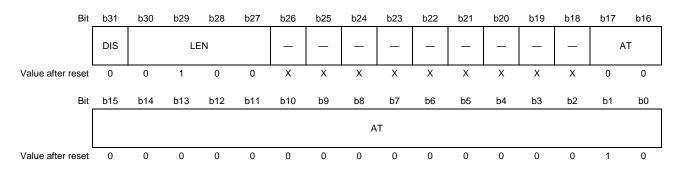

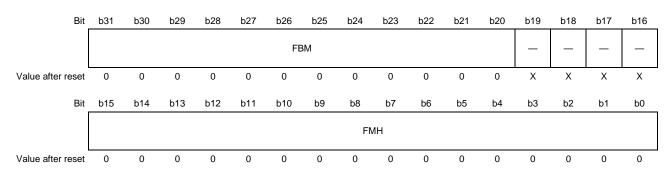

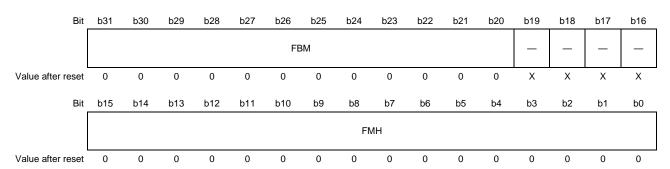

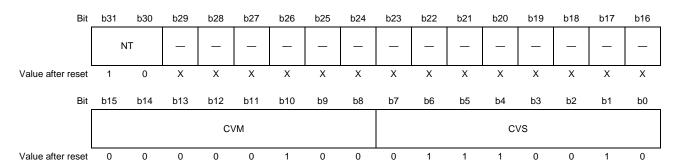

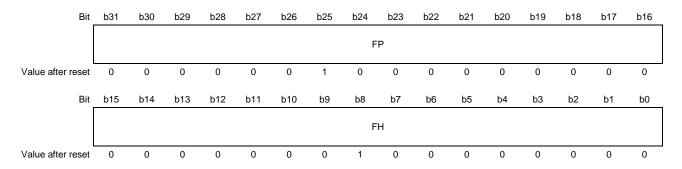

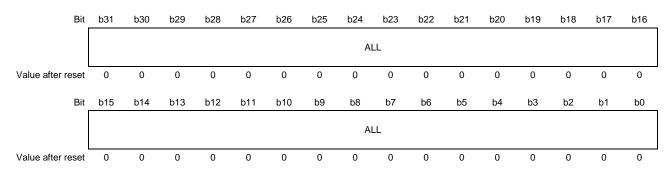

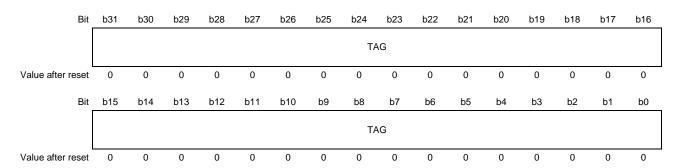

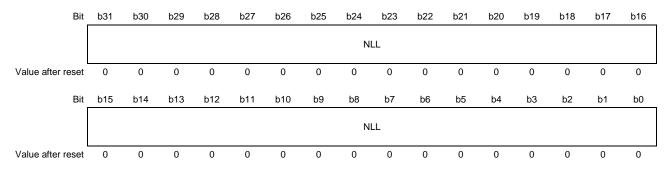

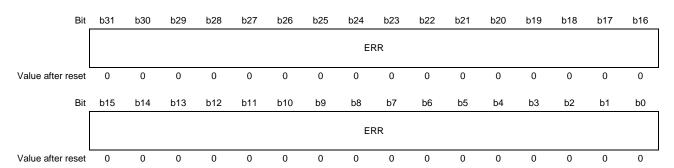

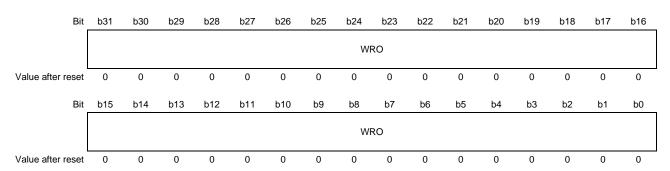

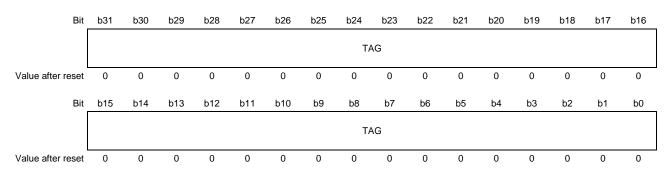

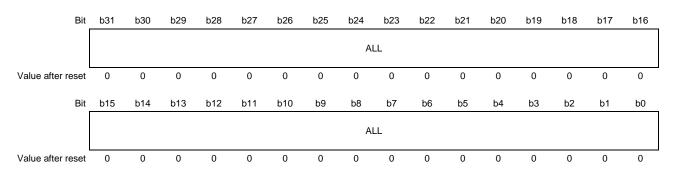

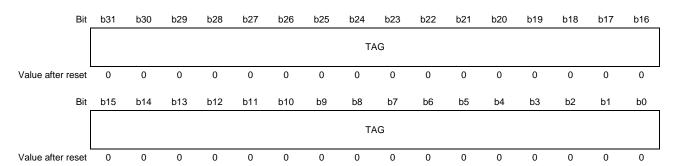

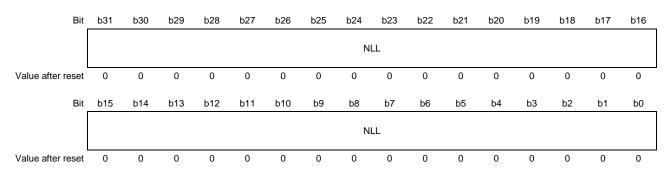

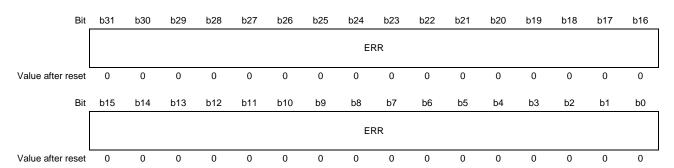

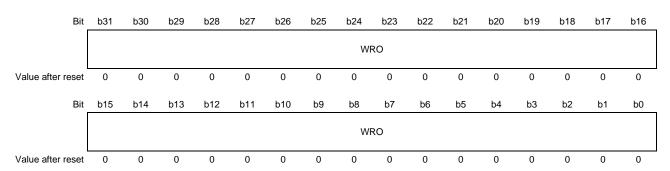

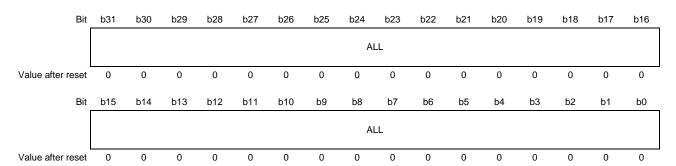

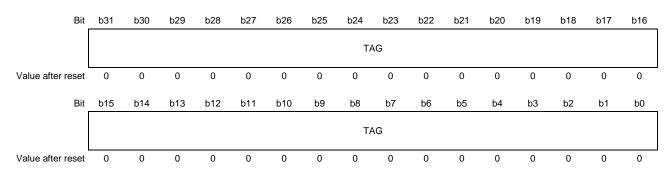

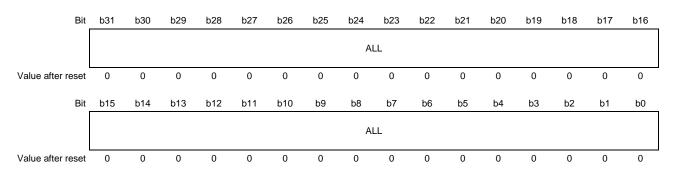

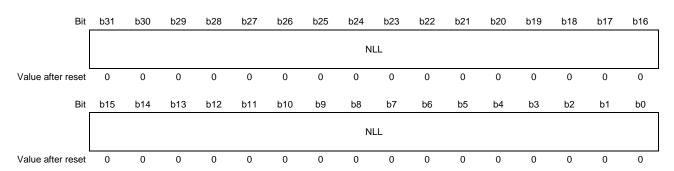

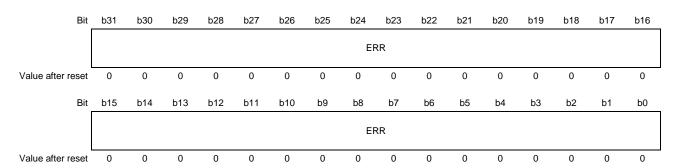

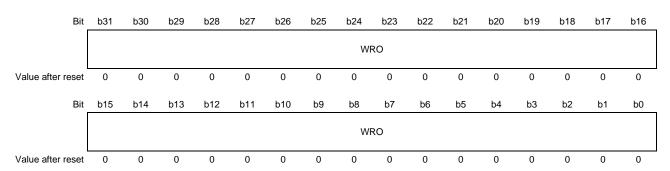

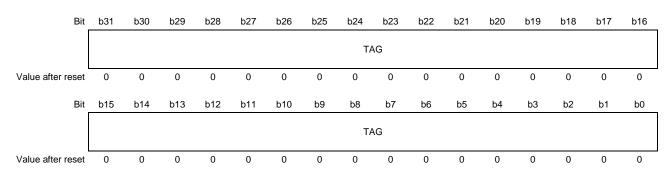

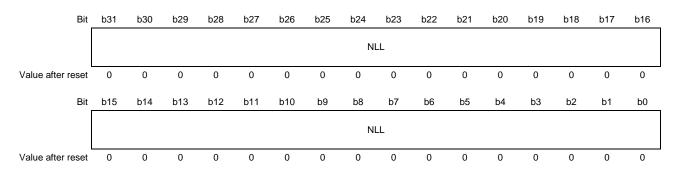

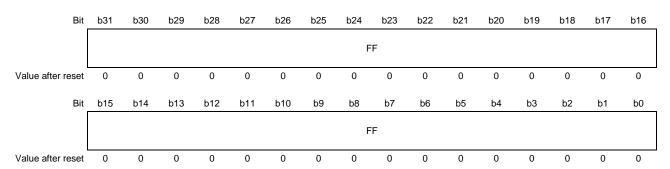

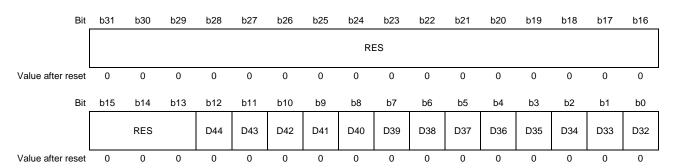

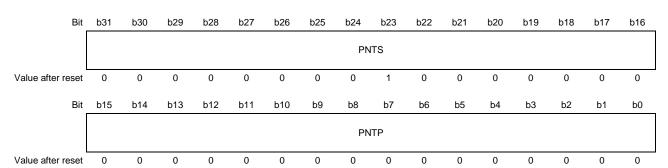

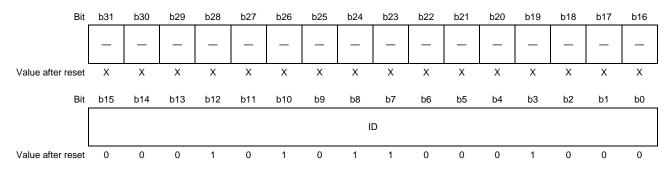

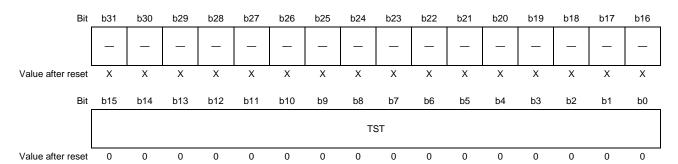

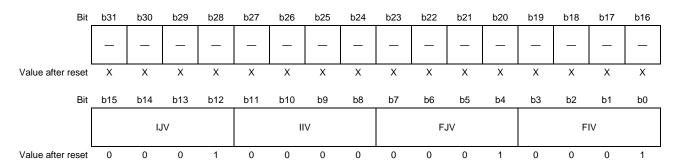

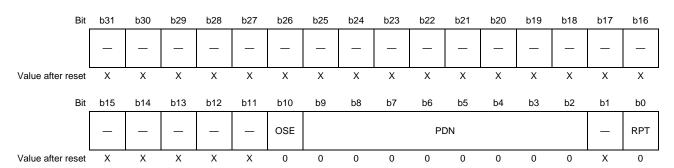

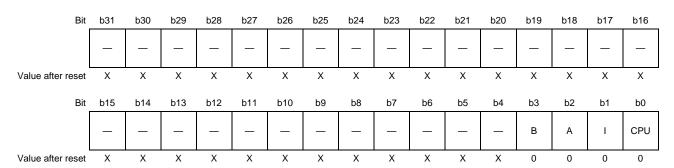

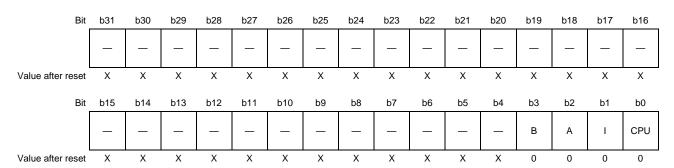

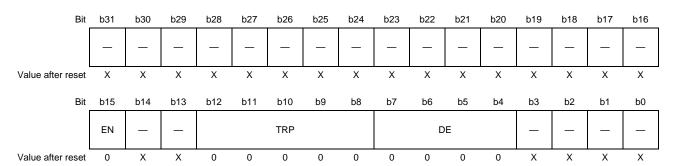

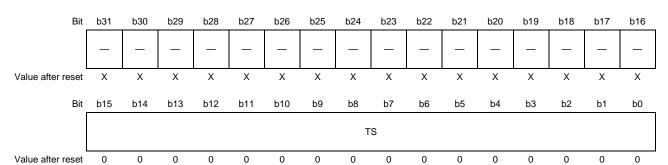

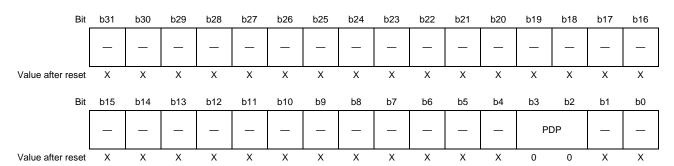

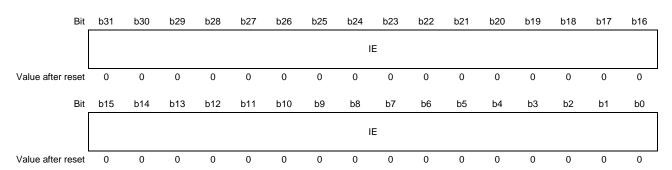

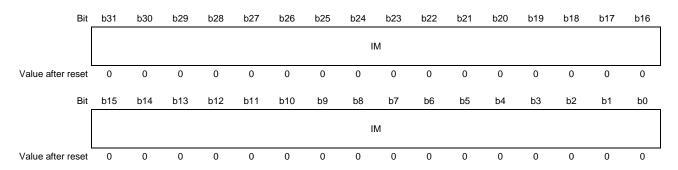

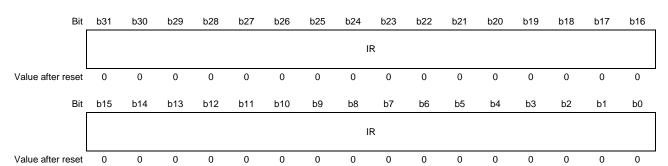

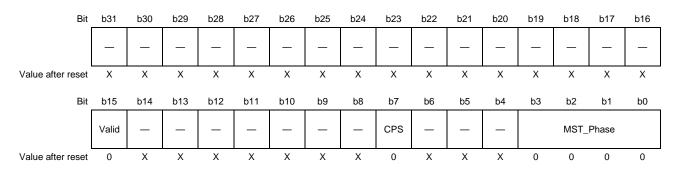

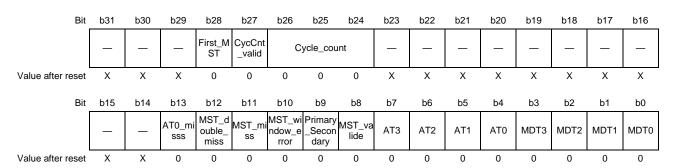

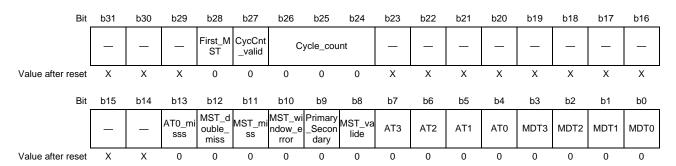

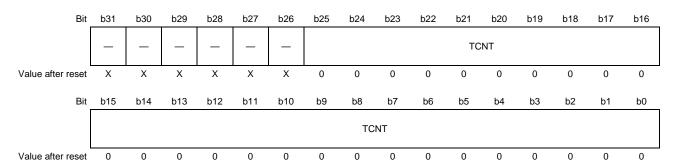

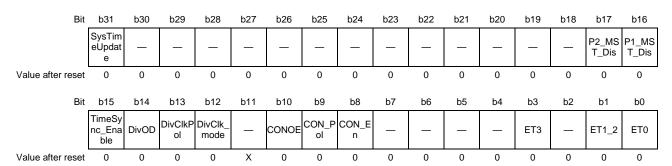

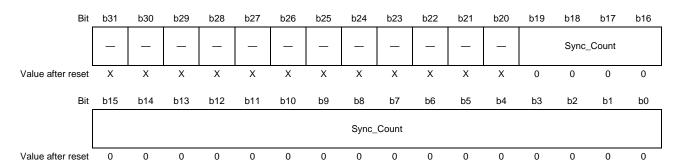

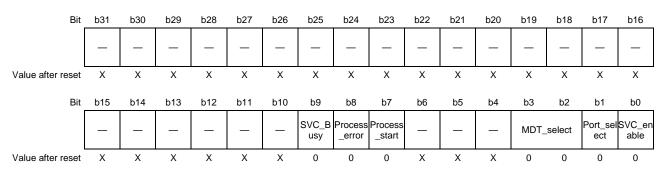

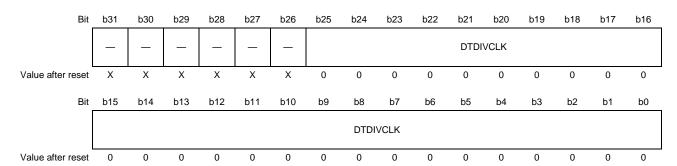

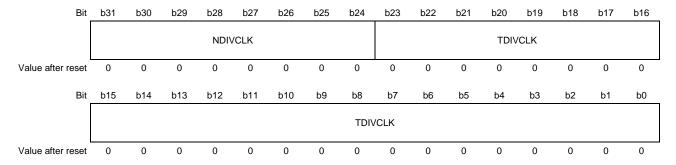

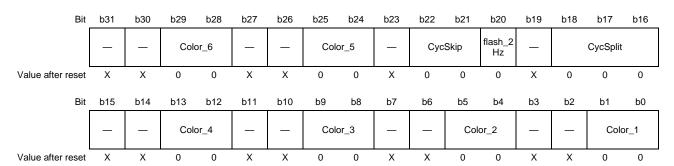

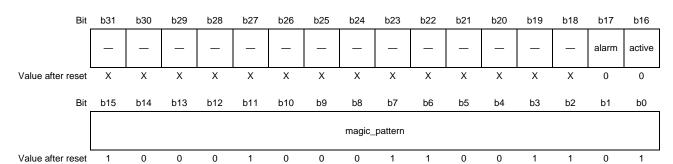

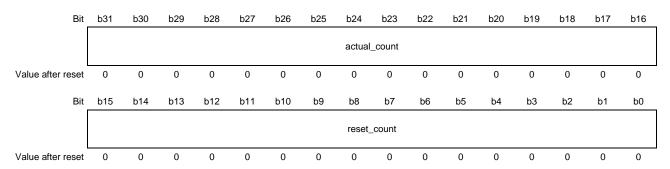

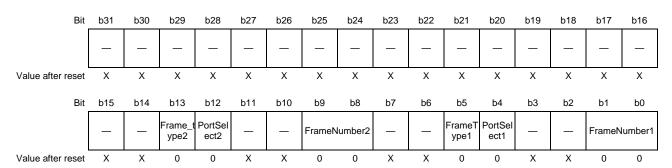

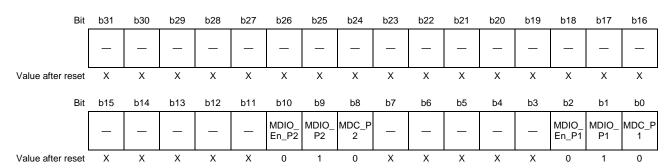

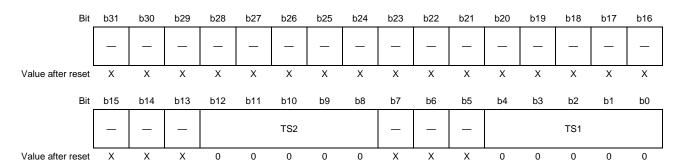

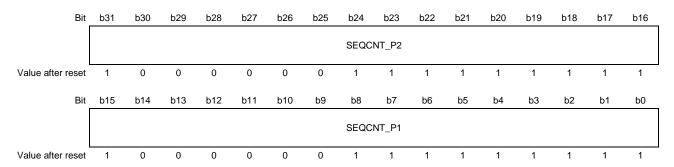

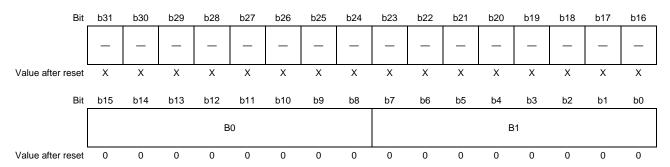

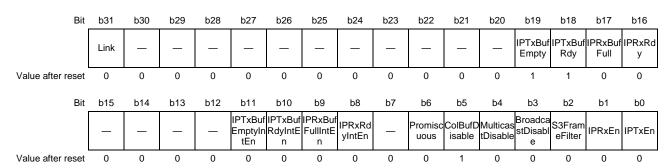

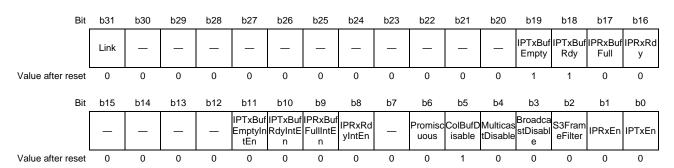

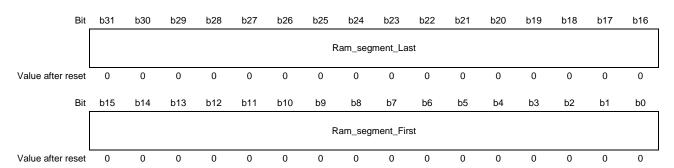

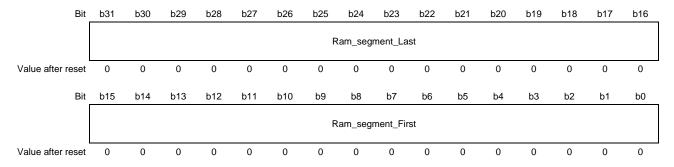

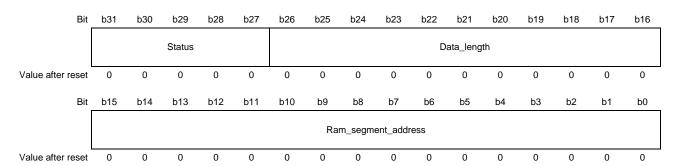

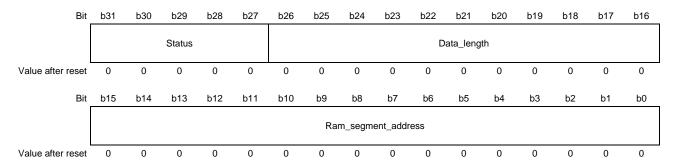

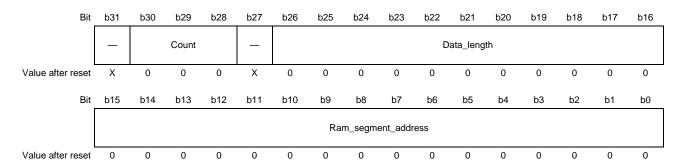

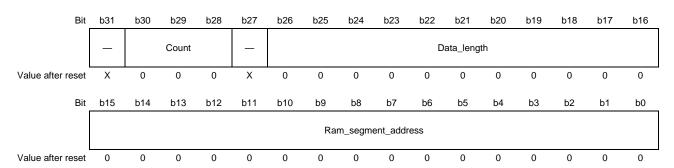

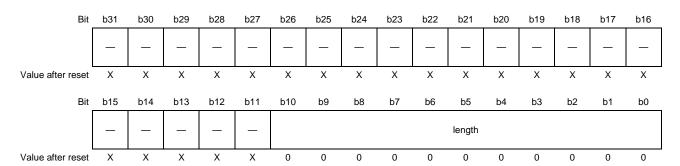

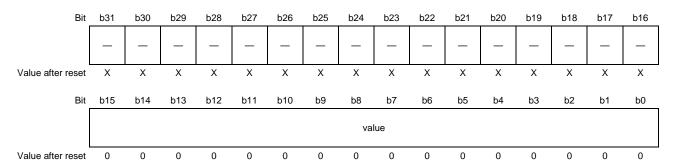

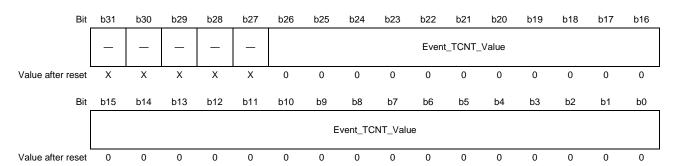

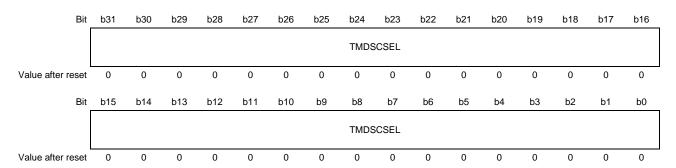

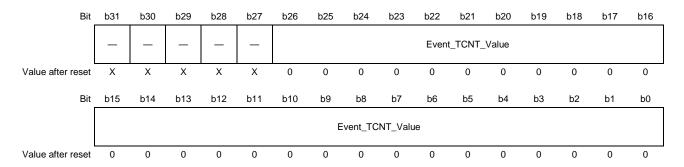

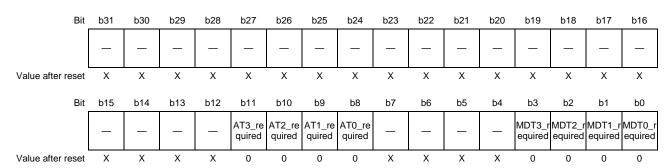

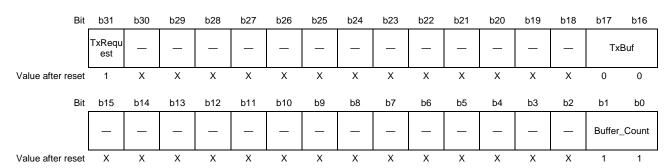

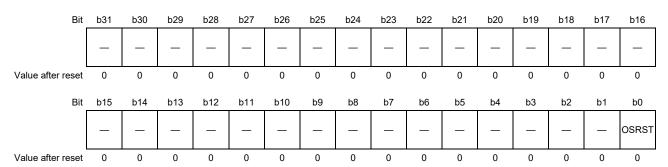

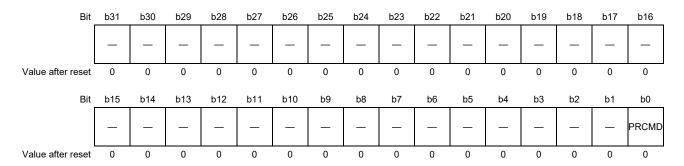

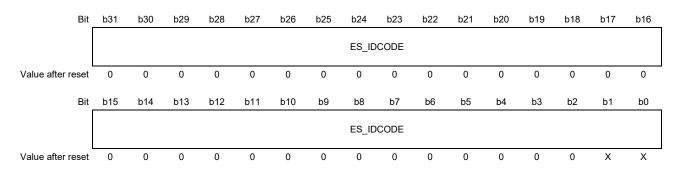

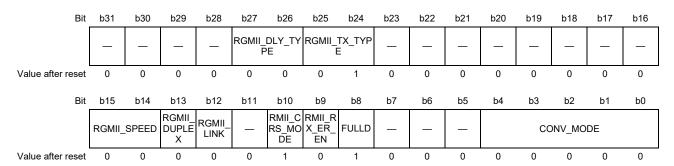

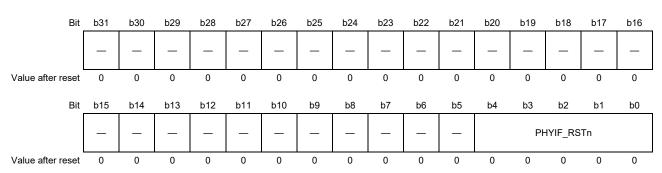

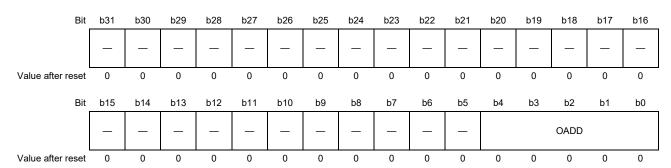

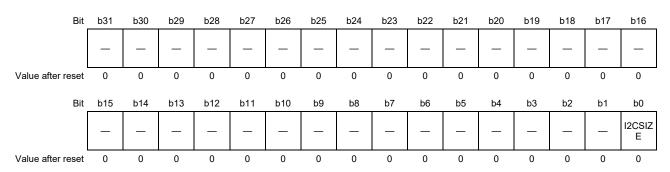

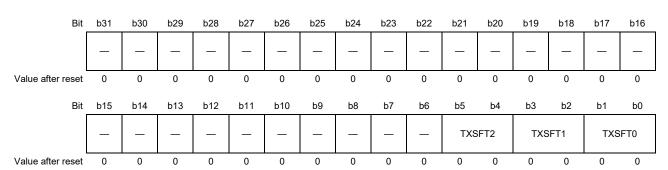

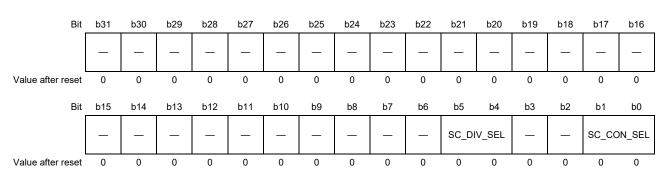

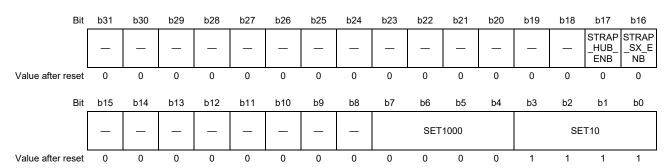

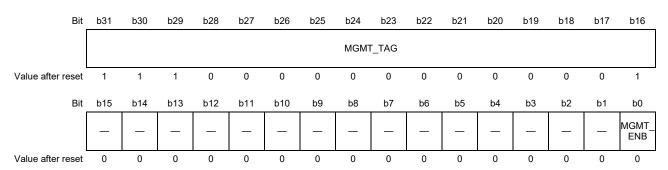

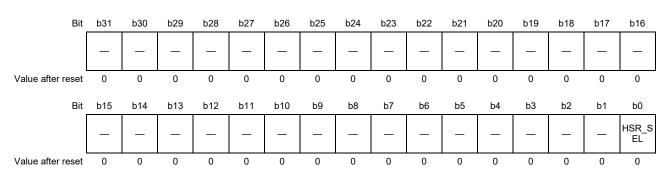

### 2. Description of Registers

Each register description includes a bit chart, illustrating the arrangement of bits, and a table of bits, describing the meanings of the bit settings. The standard format and notation for bit charts and tables are described below.

(1) R/W: The bit or field is readable and writable.

R/(W): The bit or field is readable and writable. However, writing to this bit or field has some limitations. For details on the limitations, see the description or notes of respective registers.

R: The bit or field is readable. Writing to this bit or field has no effect.

W: The bit or field is writable. Reading to this bit or field is not guaranteed.

- (2) Reserved. Make sure to use the specified value when writing to this bit or field; otherwise, the correct operation is not guaranteed.

- (3) Setting prohibited. The correct operation is not guaranteed if such a setting is performed.

# 3. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                   |

|--------------|---------------------------------------------|

| AHB          | Arm Advanced High-performance Bus           |

| APB          | Arm Advanced Peripheral Bus                 |

| AXI          | Arm Advanced eXtensible Interface           |

| bps          | bits per second                             |

| CA7          | Arm Cortex-A7 module                        |

| CM3          | Arm Cortex-M3 module                        |

| CRC          | Cyclic Redundancy Check                     |

| DMA          | Direct Memory Access                        |

| DMAC         | Direct Memory Access Controller             |

| Hi-Z         | High Impedance                              |

| HSR          | High-availability Seamless Redundancy       |

| HW-RTOS      | Hard Ware Real Time OS                      |

| I/O          | Input/Output                                |

| LSB          | Least Significant Bit                       |

| MSB          | Most Significant Bit                        |

| NC           | Non-Connect                                 |

| NoC          | Network-on-Chip                             |

| PLL          | Phase Locked Loop                           |

| PWM          | Pulse Width Modulation                      |

| UART         | Universal Asynchronous Receiver/Transmitter |

| OTP          | One Time Programmable ROM                   |

| PTP          | Precision Time Protocol                     |

| PRP          | Parallel Redundancy Protocol                |

| SoC          | System On Chip                              |

# 4. Description of the Access Size

Access size:

8 bits = Byte

16 bits = Halfword

32 bits = Word

EtherCAT is registered trademark and patented technology, licensed by Beckhoff Automation GmbH, Germany. Sercos is a registered trademark of Sercos International e.V.

ETHERNET Powerlink is the registered trademark of ETHERNET Powerlink Standardization Group (EPSG). Arm is a registered trademark of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

# **Table of Contents**

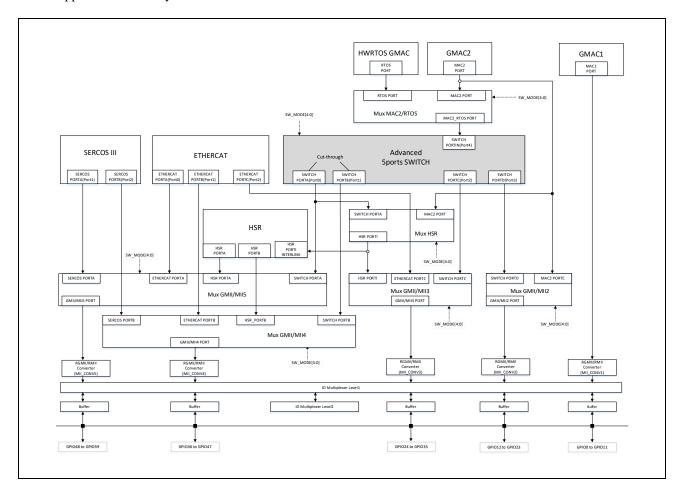

| Section 1 R-IN E | ngine Outline                                             | 31 |

|------------------|-----------------------------------------------------------|----|

| 1.1 Overview     |                                                           | 31 |

| 0 ( 0 11 1       | D 17: 00 (IIIV DT00)                                      | 00 |

|                  | are Real Time OS (HW-RTOS)                                |    |

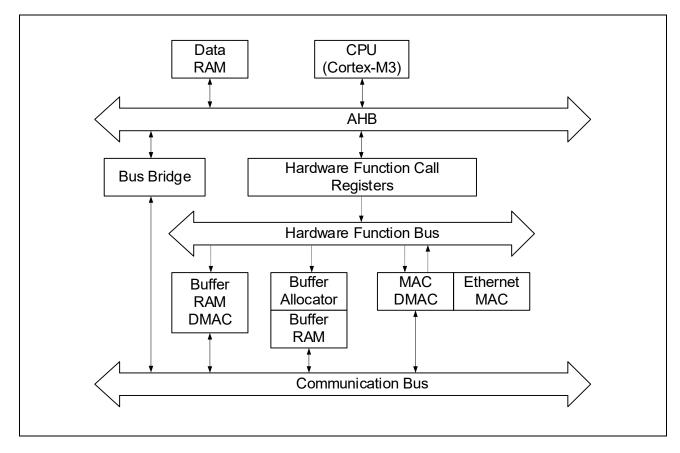

| 2.1 Overview     |                                                           | 33 |

| Section 3 Gigabi | t Ethernet MAC (HW-RTOS GMAC)                             | 34 |

| _                |                                                           |    |

| 3.2 Signal Into  | erface                                                    | 35 |

| •                | Мар                                                       |    |

|                  | ·<br>V-RTOS HWFC (Hardware Function Call) Register Map    |    |

|                  | V-RTOS GMAC (Gigabit Ethernet MAC) Register Map           |    |

| 3.4 Register [   | Description                                               | 37 |

|                  | V-RTOS HWFC (Hardware Function Call) Register Description |    |

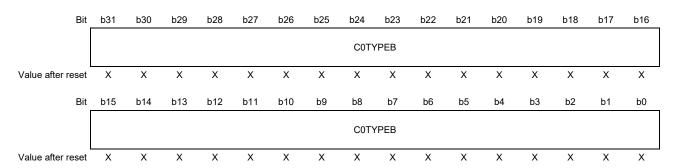

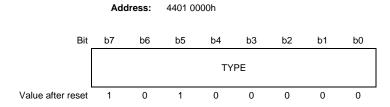

| 3.4.1.1          | C0TYPE — Hardware Function Type Register                  | 37 |

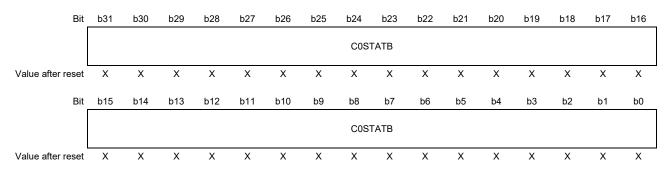

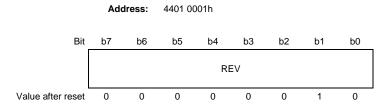

| 3.4.1.2          |                                                           |    |

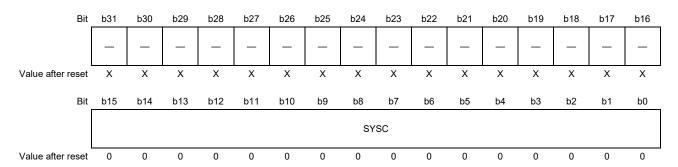

| 3.4.1.3          | SYSC — Hardware Function System Call Register             | 38 |

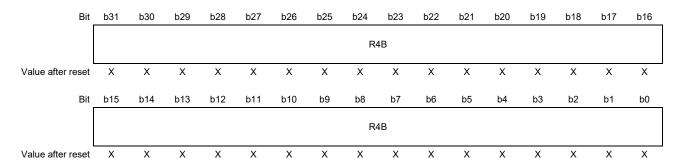

| 3.4.1.4          | R4 — Hardware Function Argument Register 4                | 39 |

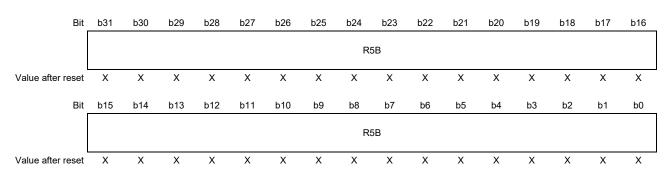

| 3.4.1.5          | R5 — Hardware Function Argument Register 5                | 39 |

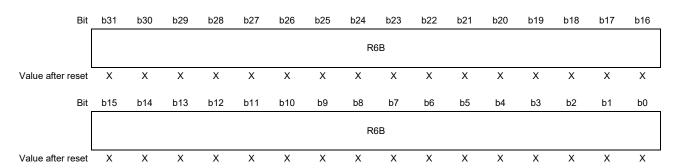

| 3.4.1.6          | R6 — Hardware Function Argument Register 6                | 40 |

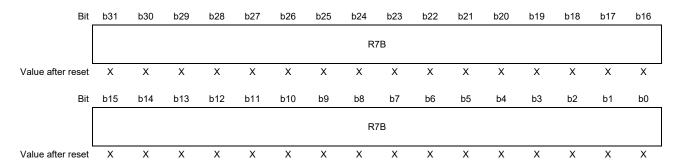

| 3.4.1.7          | R7 — Hardware Function Argument Register 7                | 40 |

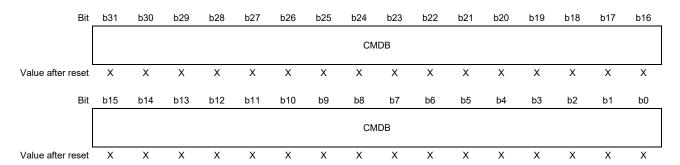

| 3.4.1.8          | CMD — Hardware Function Command Register                  | 41 |

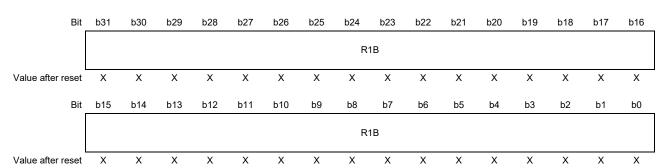

| 3.4.1.9          | R0 — Hardware Function Return Value Register 0            | 41 |

| 3.4.1.10         | 0 R1 — Hardware Function Return Value Register 1          | 42 |

| 3.4.2 HW         | V-RTOS GMAC (Gigabit Ethernet MAC) Register Description   | 43 |

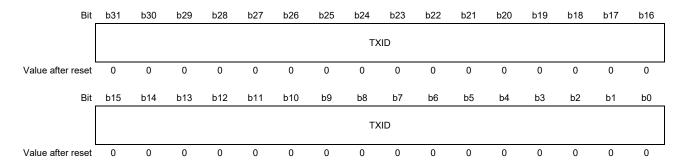

| 3.4.2.1          | GMAC_TXID — TX ID Register                                | 43 |

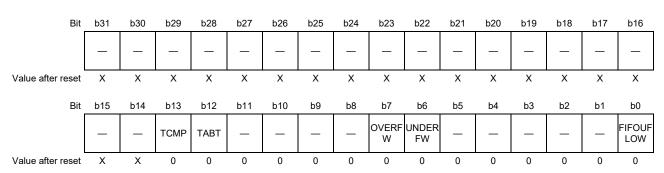

| 3.4.2.2          | <del>_</del>                                              |    |

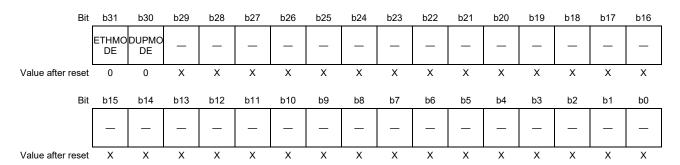

| 3.4.2.3          |                                                           |    |

| 3.4.2.4          |                                                           |    |

| 3.4.2.5          |                                                           |    |

| 3.4.2.6          | GMAC_RESET — Reset Register                               | 48 |

| 3.4.2.7          |                                                           |    |

| 3.4.2.8          |                                                           |    |

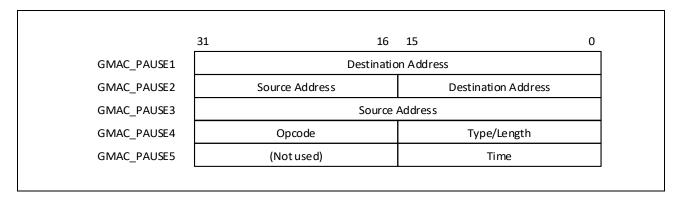

| 3.4.2.9          | GMAC_PAUSPKT — Pause Packet Register                      | 49 |

| 3.4.2.10         | 0 GMAC_MIIM — MIIM Register                               | 50 |

| 3.4.2.1          | 1 GMAC_ADR[m]A — MAC Address Register [m]A (m = 1 to 16)  | 51 |

| 3.4.2.12         | 2 GMAC_ADR[m]B — MAC Address Register [m]B (m = 1 to 16)  | 51 |

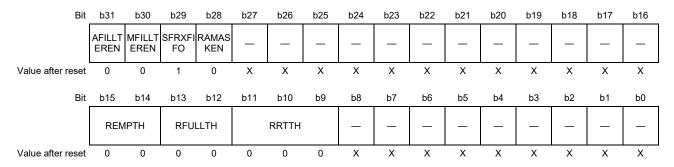

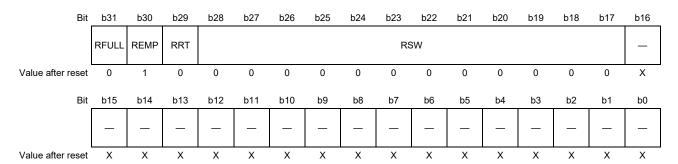

| 3.4.2.13         | 3 GMAC_RXFIFO — RX FIFO Status Register                   | 52 |

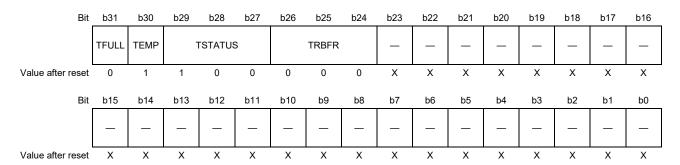

| 3.4.2.14         | 4 GMAC_TXFIFO — TX FIFO Status Register                   | 53 |

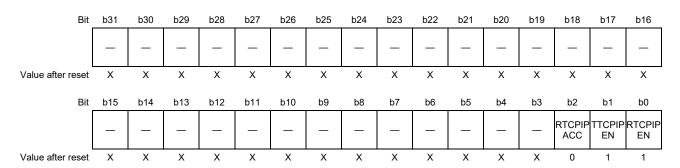

| 3.4.2.15         |                                                           |    |

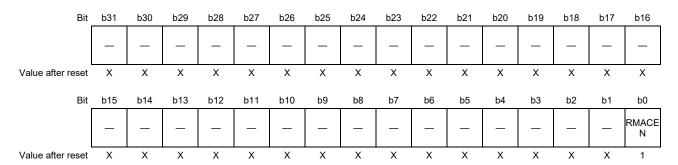

| 3.4.2.16         |                                                           |    |

| 3.4.2.17         |                                                           |    |

| 3.5 Operation    | 1                                                         | 57 |

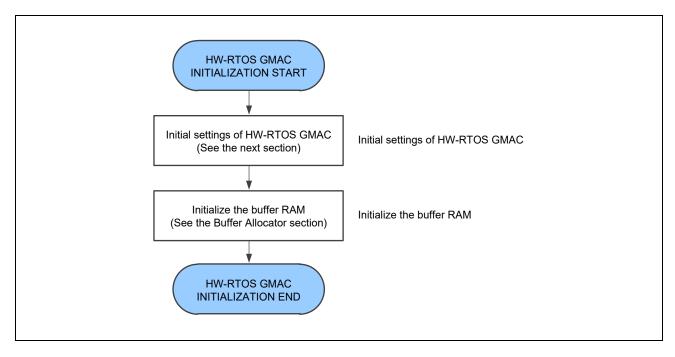

| 3.5.1 Init       | ialization                                                | 57 |

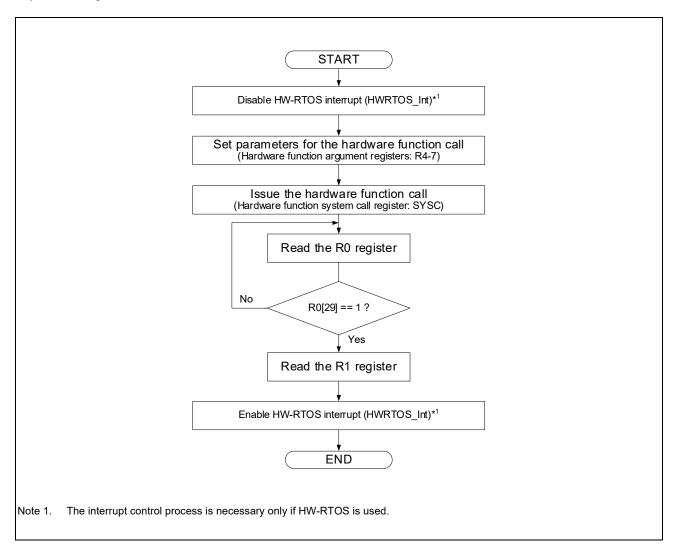

| 3.5.2 Ha         | rdware Functions (HWF)                                    | 59 |

|                  |                                                           |    |

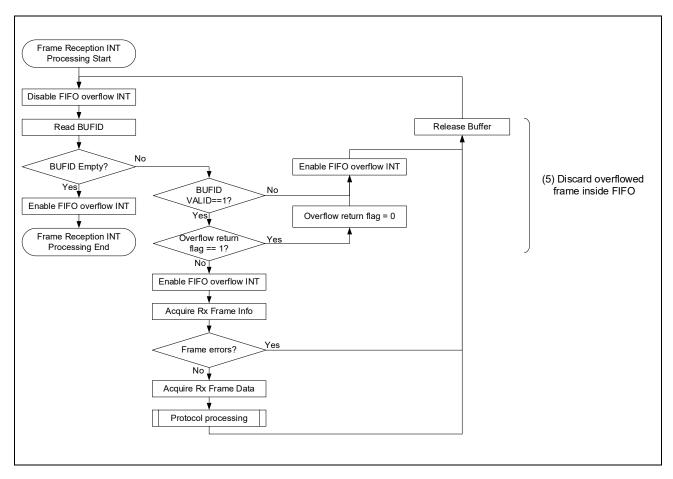

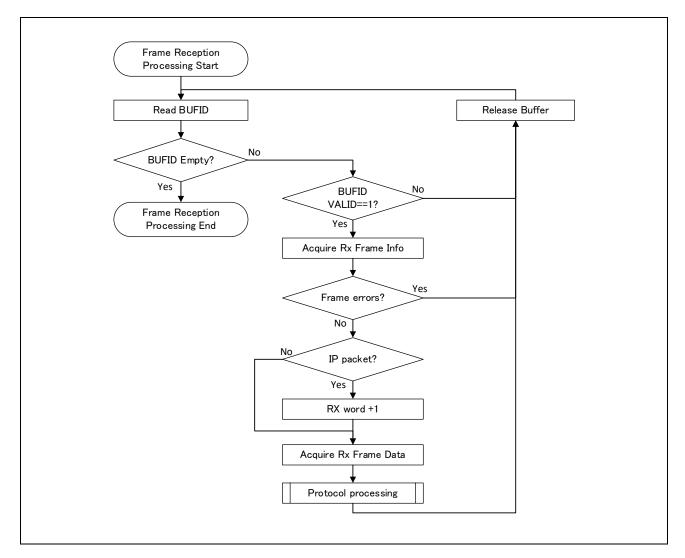

|        |         | 5.2.1             | Processing Flow                                                                                                                   |      |

|--------|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|

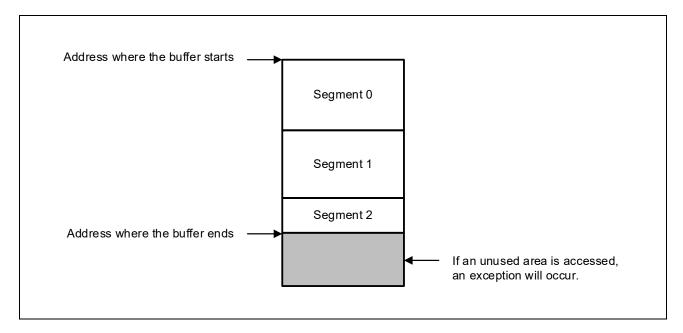

|        |         | 5.2.2             | Buffer Allocator                                                                                                                  |      |

|        |         | 5.2.3<br>5.2.4    | MAC DMA Controller                                                                                                                |      |

|        |         |                   |                                                                                                                                   |      |

|        | 3.5.3   |                   | pts                                                                                                                               |      |

|        | 3.5.4   |                   | net Frame Transmission Function                                                                                                   |      |

|        |         | 5.4.1             | Get a Transmit Buffer                                                                                                             |      |

|        |         | 5.4.2             | Create Transmit Data                                                                                                              |      |

|        |         | 5.4.3<br>5.4.4    | Create Transmit Descriptors                                                                                                       |      |

|        |         | 5.4.5             | Completing Transmission                                                                                                           |      |

|        | 3.5.5   |                   | net Frame Reception Function                                                                                                      |      |

|        |         | 5.5.1             | Enable Reception MAC                                                                                                              |      |

|        |         | 5.5.2             | Enable Reception DMA                                                                                                              |      |

|        |         | 5.5.3             | Receive a Frame and Get a Buffer                                                                                                  |      |

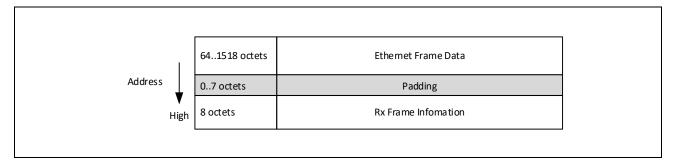

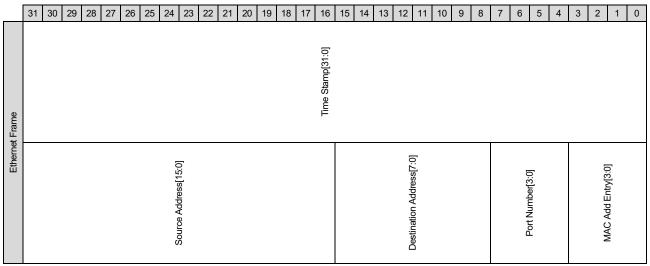

|        | 3.5     | 5.5.4             | Get Receive Buffer Information                                                                                                    | 92   |

|        | 3.5     | 5.5.5             | Format of Receive Data                                                                                                            | 92   |

|        | 3.5.6   | TCPIF             | Accelerator Function                                                                                                              | 101  |

| 3.6    | Usag    | ge Notes          |                                                                                                                                   | 103  |

|        | 3.6.1   | Giga E            | Bit Ethernet MAC (HW-RTOS GMAC) Control Register                                                                                  | 103  |

|        | 3.6     | 6.1.1             | MIIM Register (GMAC_MIIM)                                                                                                         | 103  |

|        |         | 5.1.2             | TX ID Register (GMAC_TXID)                                                                                                        |      |

|        |         | 5.1.3             | TX Result Register (GMAC_TXRESULT)                                                                                                |      |

|        |         | 5.1.4             | TX Mode Register (GMAC_TXMODE)                                                                                                    |      |

|        |         | 3.1.5             | Reset Register (GMAC_RESET)                                                                                                       |      |

|        |         | 3.1.6             | Pause Packet Data Register [m] (GMAC_PAUSE[m])                                                                                    |      |

|        | 3.6.2   |                   | vare Function Call Register                                                                                                       |      |

|        | 3.6.3   | `                 | gement TAG Control                                                                                                                |      |

|        | 3.6.4   |                   |                                                                                                                                   |      |

|        |         | 6.4.1<br>6.4.2    | Padding Added to the MAC Header in the Transmit Frame                                                                             |      |

|        |         | 5.4.2<br>5.4.3    | Erroneous Judgment about Checksum Validation at Specific Frame Reception.  Error of Receive Frame Information at Rx FIFO Overflow |      |

|        |         | 5.4.4             | Error of Rx Frame Information at Reception of the Frame More than 64 bytes                                                        | 100  |

|        | 0.0     |                   | with Padding                                                                                                                      | 112  |

|        | 3.6     | 6.4.5             | About Jumbo Frame                                                                                                                 |      |

| Cootio | n 1 1 1 |                   | d Enant Christop (AEDCIMI)                                                                                                        | 111  |

|        |         |                   | d 5port Switch (A5PSW)                                                                                                            |      |

| 4.1    |         |                   |                                                                                                                                   |      |

| 4.2    | Ū       |                   | ace                                                                                                                               |      |

| 4.3    | Regi    | ster Map          | )                                                                                                                                 | 119  |

| 4.4    | Regi    | ster Des          | cription                                                                                                                          | 125  |

|        | 4.4.1   |                   | SION — Switch Core Version                                                                                                        |      |

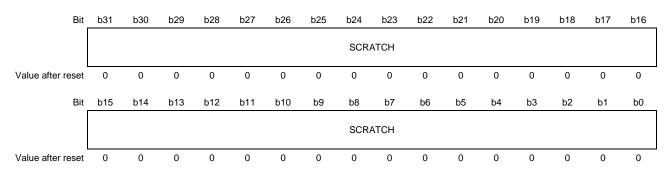

|        | 4.4.2   |                   | TCH — Scratch Register                                                                                                            |      |

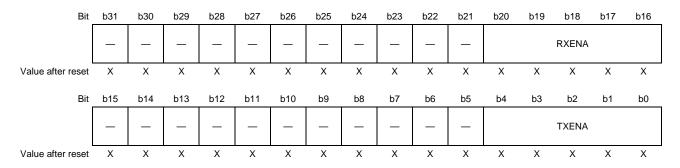

|        | 4.4.3   | PORT              | _ENA — Port Enable Register                                                                                                       | 126  |

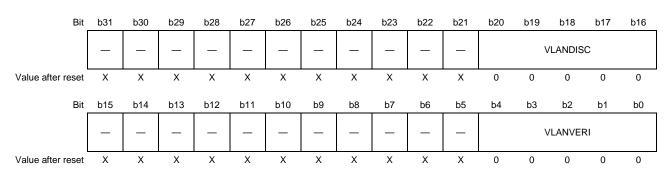

|        | 4.4.4   | UCAS              | T_DEFAULT_MASK — Unicast Default Mask Register                                                                                    | .127 |

|        | 4.4.5   | VLAN <sub>.</sub> | _VERIFY — Verify VLAN Domain                                                                                                      | .127 |

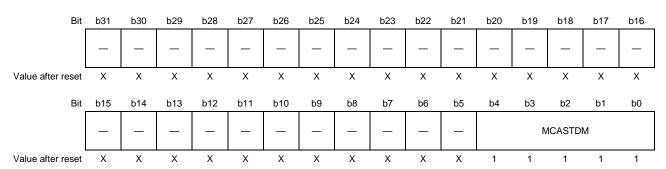

|        | 4.4.6   | BCAS              | T_DEFAULT_MASK — Broadcast Default Mask Register                                                                                  | .128 |

| 4.4.7                                                                                                                                                                  | MCAST_DEFAULT_MASK — Multicast Default Mask Register                                                                                                                                                                                                                  | 128                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 4.4.8                                                                                                                                                                  | INPUT_LEARN_BLOCK — Input Learning Block Register                                                                                                                                                                                                                     | 129                                                  |

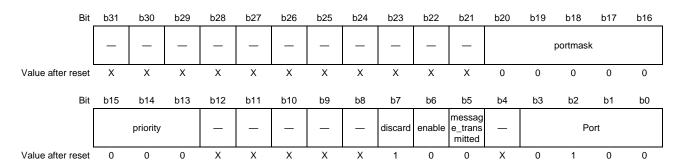

| 4.4.9                                                                                                                                                                  | MGMT_CONFIG — Management Configuration Register                                                                                                                                                                                                                       | 130                                                  |

| 4.4.10                                                                                                                                                                 | MODE_CONFIG — Mode Configuration Register                                                                                                                                                                                                                             | 131                                                  |

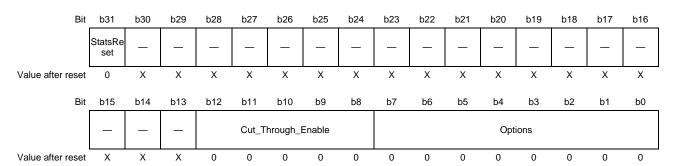

| 4.4.11                                                                                                                                                                 | VLAN_IN_MODE — VLAN Input Manipulation Mode Register                                                                                                                                                                                                                  | 132                                                  |

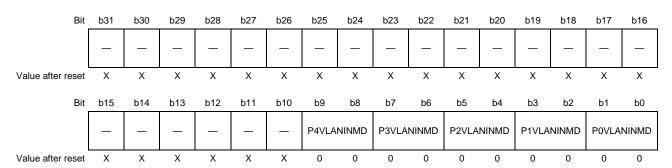

| 4.4.12                                                                                                                                                                 | VLAN_OUT_MODE — VLAN Output Manipulation Mode Register                                                                                                                                                                                                                | 133                                                  |

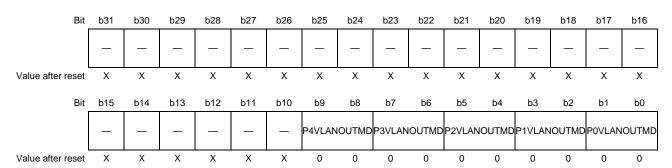

| 4.4.13                                                                                                                                                                 | VLAN_IN_MODE_ENA — VLAN Input Mode Enable Register                                                                                                                                                                                                                    | 134                                                  |

| 4.4.14                                                                                                                                                                 | VLAN_TAG_ID — VLAN Tag ID Register                                                                                                                                                                                                                                    | 134                                                  |

| 4.4.15                                                                                                                                                                 | BCAST_STORM_LIMIT — Broadcast Storm Protection Register                                                                                                                                                                                                               | 135                                                  |

| 4.4.16                                                                                                                                                                 | MCAST_STORM_LIMIT — Multicast Storm Protection Register                                                                                                                                                                                                               | 135                                                  |

| 4.4.17                                                                                                                                                                 | MIRROR_CONTROL — Port Mirroring Configuration Register                                                                                                                                                                                                                | 136                                                  |

| 4.4.18                                                                                                                                                                 | MIRROR_EG_MAP — Port Mirroring Egress Port Definition                                                                                                                                                                                                                 | 137                                                  |

| 4.4.19                                                                                                                                                                 | MIRROR_ING_MAP — Port Mirroring Ingress Port Definition                                                                                                                                                                                                               | 137                                                  |

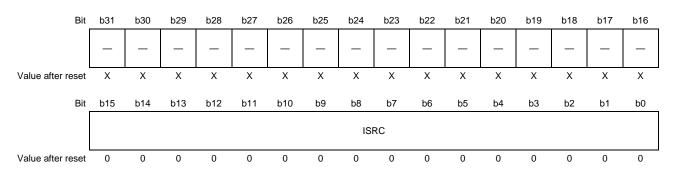

| 4.4.20                                                                                                                                                                 | MIRROR_ISRC_0 — Ingress Source MAC Address for Mirror Filtering 0                                                                                                                                                                                                     | 138                                                  |

| 4.4.21                                                                                                                                                                 | MIRROR_ISRC_1 — Ingress Source MAC Address for Mirror Filtering 1                                                                                                                                                                                                     |                                                      |

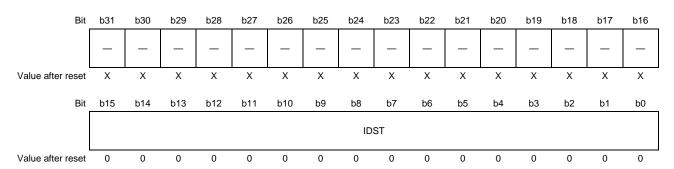

| 4.4.22                                                                                                                                                                 | MIRROR_IDST_0 — Ingress Destination MAC Address for Mirror Filtering 0                                                                                                                                                                                                | 139                                                  |

| 4.4.23                                                                                                                                                                 | MIRROR_IDST_1 — Ingress Destination MAC Address for Mirror Filtering 1                                                                                                                                                                                                | 139                                                  |

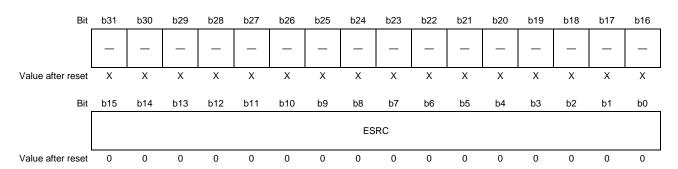

| 4.4.24                                                                                                                                                                 | MIRROR_ESRC_0 — Egress Source MAC Address for Mirror Filtering 0                                                                                                                                                                                                      | 140                                                  |

| 4.4.25                                                                                                                                                                 | MIRROR_ESRC_1 — Egress Source MAC Address for Mirror Filtering 1                                                                                                                                                                                                      | 140                                                  |

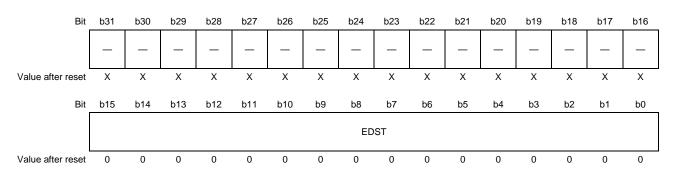

| 4.4.26                                                                                                                                                                 | MIRROR_EDST_0 — Egress Destination MAC Address for Mirror Filtering 0                                                                                                                                                                                                 | 141                                                  |

| 4.4.27                                                                                                                                                                 | MIRROR_EDST_1 — Egress Destination MAC Address for Mirror Filtering 1                                                                                                                                                                                                 | 141                                                  |

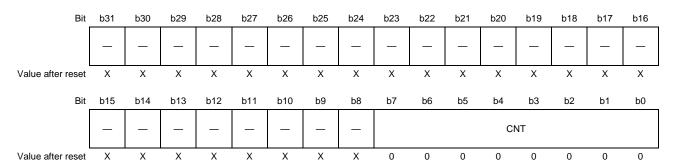

| 4.4.28                                                                                                                                                                 | MIRROR_CNT — Mirror Filtering Count Value Register                                                                                                                                                                                                                    | 142                                                  |

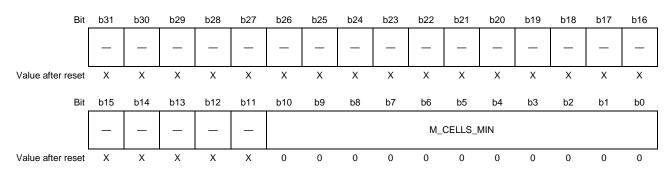

| 4.4.29                                                                                                                                                                 | QMGR_ST_MINCELLS — Output Queue Minimum Memory Statistics Register                                                                                                                                                                                                    | 142                                                  |

|                                                                                                                                                                        |                                                                                                                                                                                                                                                                       |                                                      |

| 4.4.30                                                                                                                                                                 | QMGR_RED_MIN4 — RED Minimum Threshold Register                                                                                                                                                                                                                        | 143                                                  |

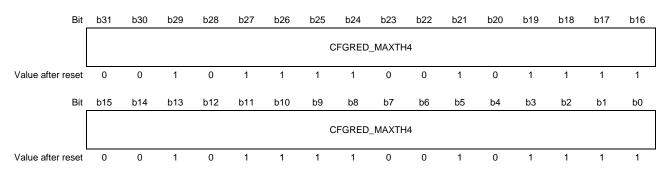

| 4.4.30<br>4.4.31                                                                                                                                                       | QMGR_RED_MIN4 — RED Minimum Threshold RegisterQMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                          |                                                      |

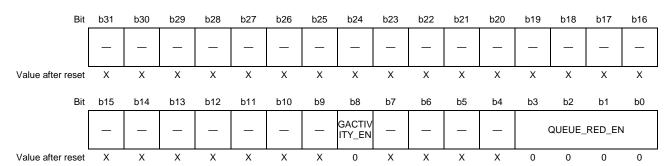

|                                                                                                                                                                        |                                                                                                                                                                                                                                                                       | 143                                                  |

| 4.4.31                                                                                                                                                                 | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143<br>144                                           |

| 4.4.31<br>4.4.32                                                                                                                                                       | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143<br>144<br>145                                    |

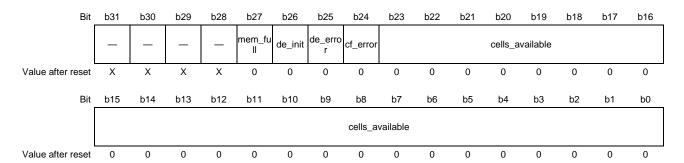

| 4.4.31<br>4.4.32<br>4.4.33                                                                                                                                             | QMGR_RED_MAX4 — RED Maximum Threshold Register  QMGR_RED_CONFIG — RED Configuration Register  IMC_STATUS — Input Memory Controller Status Register                                                                                                                    | 143<br>144<br>145<br>146                             |

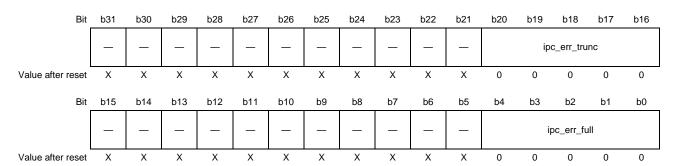

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34                                                                                                                                   | QMGR_RED_MAX4 — RED Maximum Threshold Register  QMGR_RED_CONFIG — RED Configuration Register  IMC_STATUS — Input Memory Controller Status Register  IMC_ERR_FULL — Input Port Memory Full and Truncation Indicator                                                    | 143<br>144<br>145<br>146<br>147                      |

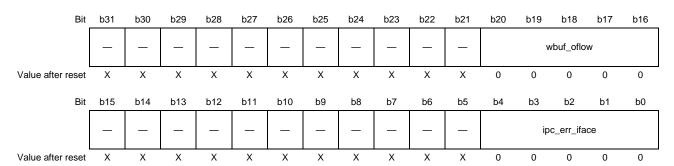

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34<br>4.4.35                                                                                                                         | QMGR_RED_MAX4 — RED Maximum Threshold Register  QMGR_RED_CONFIG — RED Configuration Register  IMC_STATUS — Input Memory Controller Status Register  IMC_ERR_FULL — Input Port Memory Full and Truncation Indicator  IMC_ERR_IFACE — Input Port Memory Error Indicator | 143<br>144<br>145<br>146<br>147                      |

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34<br>4.4.35<br>4.4.36                                                                                                               | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143<br>144<br>145<br>146<br>147<br>148               |

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34<br>4.4.35<br>4.4.36<br>4.4.37                                                                                                     | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143<br>144<br>145<br>146<br>147<br>148<br>148        |

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34<br>4.4.35<br>4.4.36<br>4.4.37<br>4.4.38                                                                                           | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143<br>144<br>145<br>146<br>147<br>148<br>148<br>149 |

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34<br>4.4.35<br>4.4.36<br>4.4.37<br>4.4.38<br>4.4.39                                                                                 | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143144145146147148148149151                          |

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34<br>4.4.35<br>4.4.36<br>4.4.37<br>4.4.38<br>4.4.39<br>4.4.40                                                                       | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143144145146147148148149151152                       |

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34<br>4.4.35<br>4.4.36<br>4.4.37<br>4.4.38<br>4.4.39<br>4.4.40<br>4.4.41                                                             | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143144145146147148149151152 ) .154155                |

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34<br>4.4.35<br>4.4.36<br>4.4.37<br>4.4.38<br>4.4.39<br>4.4.40<br>4.4.41<br>4.4.42                                                   | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143144145146147148148149151152 ) .154155156          |

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34<br>4.4.35<br>4.4.36<br>4.4.37<br>4.4.38<br>4.4.39<br>4.4.40<br>4.4.41<br>4.4.42<br>4.4.43                                         | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143144145146147148149151152 ) .154155156157          |

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34<br>4.4.35<br>4.4.36<br>4.4.37<br>4.4.38<br>4.4.39<br>4.4.40<br>4.4.41<br>4.4.42<br>4.4.43<br>4.4.44                               | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143144145146147148149151152 ) .154155156157          |

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34<br>4.4.35<br>4.4.36<br>4.4.37<br>4.4.38<br>4.4.39<br>4.4.40<br>4.4.41<br>4.4.42<br>4.4.43<br>4.4.44<br>4.4.45                     | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143144145146147148149151152 ) .154155156157158       |

| 4.4.31<br>4.4.32<br>4.4.33<br>4.4.34<br>4.4.35<br>4.4.36<br>4.4.37<br>4.4.38<br>4.4.39<br>4.4.40<br>4.4.41<br>4.4.42<br>4.4.43<br>4.4.44<br>4.4.45<br>4.4.45<br>4.4.46 | QMGR_RED_MAX4 — RED Maximum Threshold Register                                                                                                                                                                                                                        | 143144145146147148149151152 ) .154155156157158159160 |

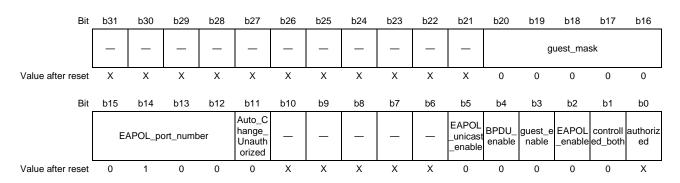

| 4.4.50 | AUTH_PORT[n] — PORT[n] Authentication Control and Configuration (n = 04)    | 162 |

|--------|-----------------------------------------------------------------------------|-----|

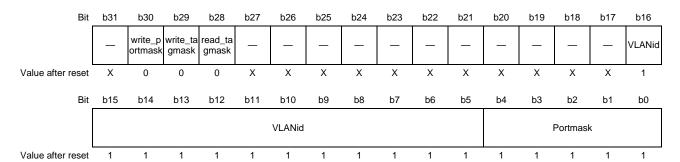

| 4.4.51 | VLAN_RES_TABLE[n] — 32 VLAN Domain Entries (n = 031)                        | 164 |

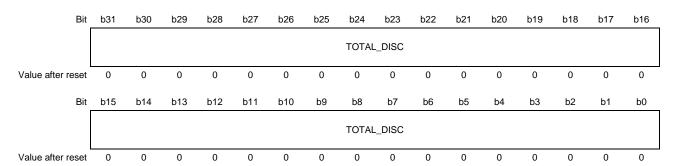

| 4.4.52 | TOTAL_DISC — Discarded Frame Total Number Register                          | 165 |

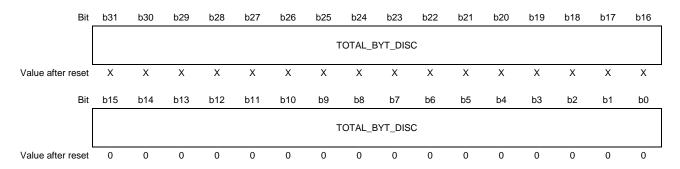

| 4.4.53 | TOTAL_BYT_DISC — Discarded Frame Total Bytes Register                       | 165 |

| 4.4.54 | TOTAL_FRM — Processed Frame Total Number Register                           | 166 |

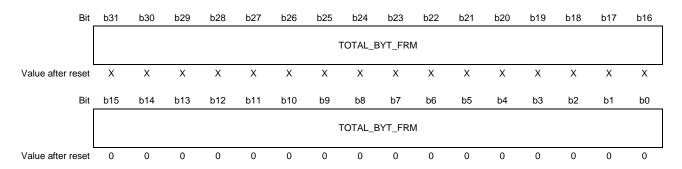

| 4.4.55 | TOTAL_BYT_FRM — Processed Frame Total Bytes Register                        | 166 |

| 4.4.56 | ODISC[n] — PORT[n] Discarded Outgoing Frame Count Register (n = 04)         | 167 |

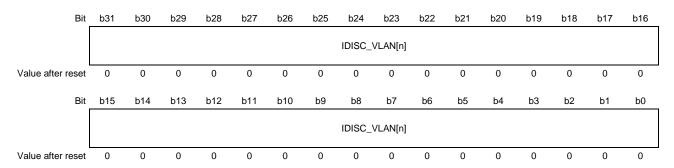

| 4.4.57 | IDISC_VLAN[n] — PORT[n] Discarded Incoming VLAN Tagged Frame Count Register |     |

|        | (n = 04)                                                                    | 167 |

| 4.4.58 | IDISC_UNTAGGED[n] — PORT[n] Discarded Incoming VLAN Untagged Frame Count    | İ   |

|        | Register (n = 04)                                                           | 168 |

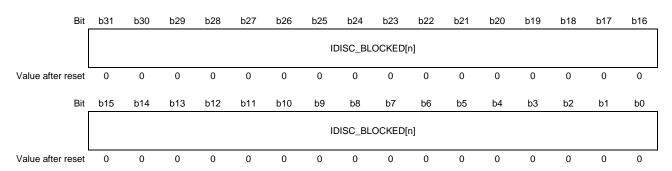

| 4.4.59 | IDISC_BLOCKED[n] — PORT[n] Discarded Incoming Blocked Frame Count Register  |     |

|        | (n = 04)                                                                    | 168 |

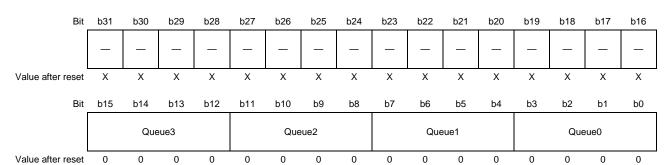

| 4.4.60 | IMC_QLEVEL_P[n] — PORT[n] Queued Frame Count Register (n = 04)              | 169 |

| 4.4.61 | LK_CTRL — Learning/Lookup Function Global Configuration Register            | 170 |

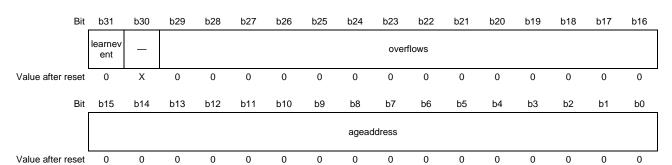

| 4.4.62 | LK_STATUS — Status Bits and Table Overflow Counter                          | 172 |

| 4.4.63 | LK_ADDR_CTRL — Address Table Transaction Control and Read/Write Address     | 173 |

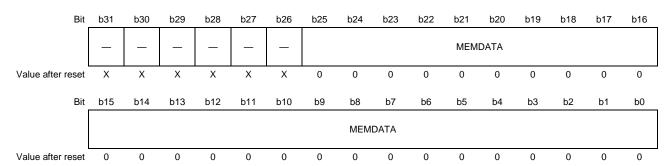

| 4.4.64 | LK_DATA_LO — Lower 32-Bit Data of Lookup Memory Entry                       | 175 |

| 4.4.65 | LK_DATA_HI — Higher 26-Bit Data of Lookup Memory Entry                      | 175 |

| 4.4.66 | LK_LEARNCOUNT — Learned Address Count Register                              | 176 |

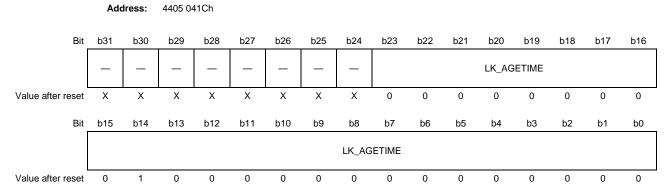

| 4.4.67 | LK_AGETIME — Period of the Aging Timer                                      | 177 |

| 4.4.68 | MGMT_TAG_CONFIG — Management Tag Configuration Register                     | 178 |

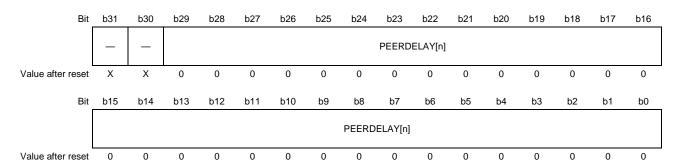

| 4.4.69 | PEERDELAY[n] — Peer Delay Value for Port [n] (n = 03)                       | 179 |

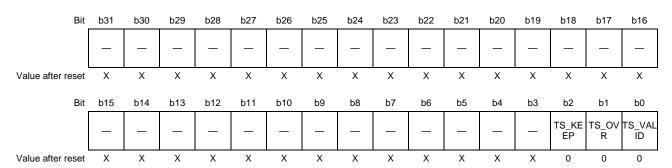

| 4.4.70 | PORT[n]_CTRL — PORT[n] Timestamp Control/Status (n = 03)                    | 180 |

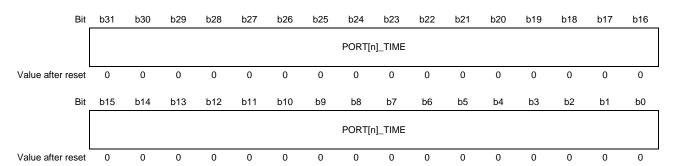

| 4.4.71 | PORT[n]_TIME — PORT[n] Memorized Transmit Timestamp (n = 03)                | 181 |

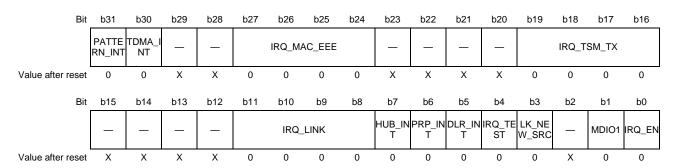

| 4.4.72 | INT_CONFIG — Interrupt Enable Configuration Register                        | 182 |

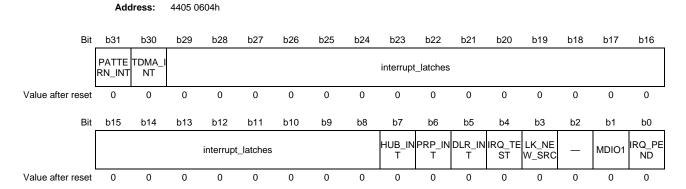

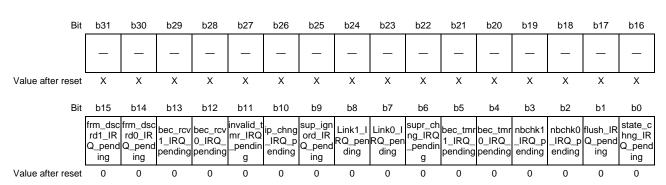

| 4.4.73 | INT_STAT_ACK — Interrupt Status/ACK Register                                | 184 |

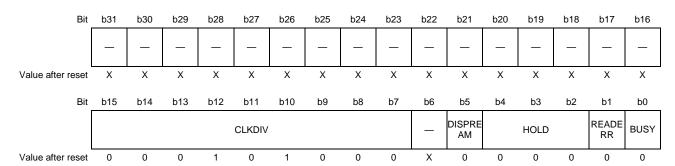

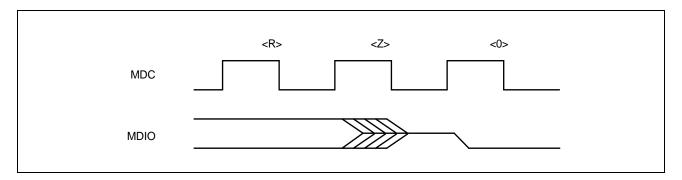

| 4.4.74 | MDIO_CFG_STATUS — MDIO Configuration and Status Register                    | 186 |

| 4.4.75 | MDIO_COMMAND — MDIO PHY Command Register                                    | 187 |

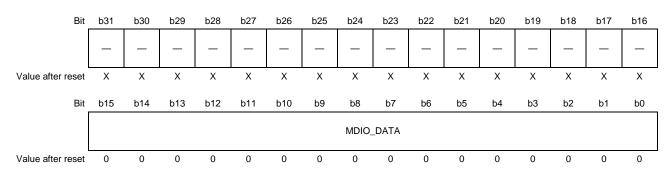

| 4.4.76 | MDIO_DATA — MDIO Data Register                                              | 187 |

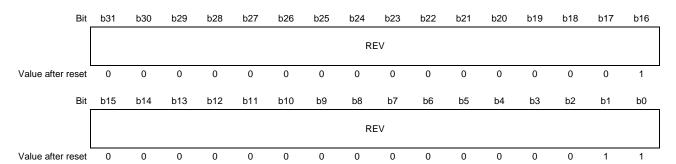

| 4.4.77 | REV_P[n] — PORT[n] MAC Core Revision (n = 04)                               | 188 |

| 4.4.78 | COMMAND_CONFIG_P[n] — Port[n] Command Configuration Register (n = 04)       | 189 |

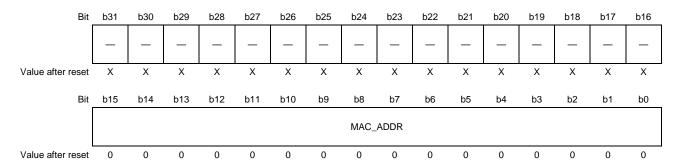

| 4.4.79 | MAC_ADDR_0_P[n] — Port[n] MAC Address Register 0 (n = 03)                   | 191 |

| 4.4.80 | MAC_ADDR_1_P[n] — Port[n] MAC Address Register 1 (n = 03)                   | 191 |

| 4.4.81 | FRM_LENGTH_P[n] — PORT[n] Maximum Frame Length Register (n = 04)            | 192 |

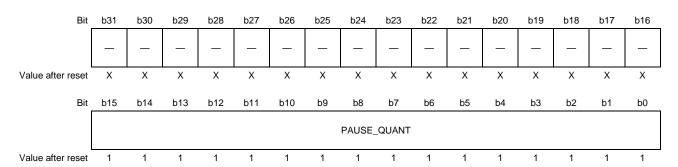

| 4.4.82 | PAUSE_QUANT_P[n] — PORT[n] MAC Pause Quanta (n = 04)                        | 192 |

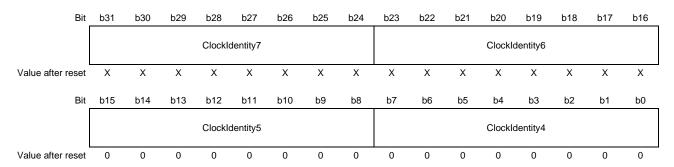

| 4.4.83 | PTPClockIdentity1_P[n] — PORT[n] PTP Clock Identity1 Register (n = 03)      | 193 |

| 4.4.84 | PTPClockIdentity2_P[n] — PORT[n] PTP Clock Identity2 Register (n = 03)      | 193 |

| 4.4.85 | PTPAutoResponse_P[n] — PORT[n] PTP Auto Response Register (n = 03)          | 194 |

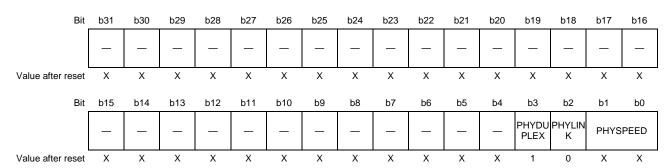

| 4.4.86 | STATUS_P[n] — PORT[n] Port Status Register (n = 04)                         | 195 |

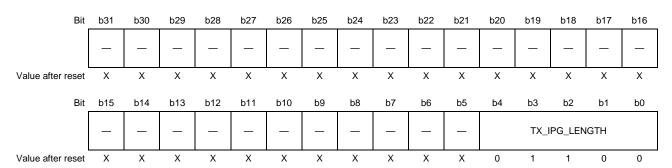

| 4.4.87 | TX_IPG_LENGTH_P[n] — PORT[n] Transmit IPG Length Register (n = 04)          | 196 |

| 4.4.88 | EEE_CTL_STAT_P[n] — PORT[n] MAC EEE Functions Control and Status (n = 03).  | 197 |

| 4.4.89 | EEE_IDLE_TIME_P[n] — PORT[n] EEE Idle Time Register (n = 03)                | 199 |

|        |                                                                             |     |

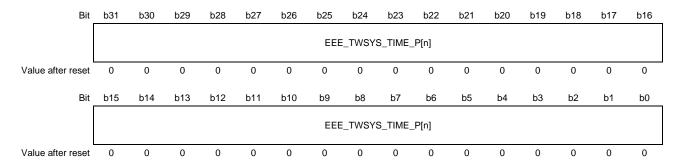

| 4.4.90  | EEE_TWSYS_TIME_P[n] — PORT[n] EEE Wake Up Time Register (n = 03)                 | 199   |

|---------|----------------------------------------------------------------------------------|-------|

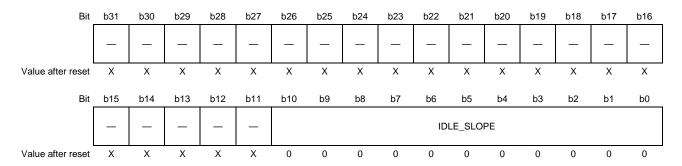

| 4.4.91  | IDLE_SLOPE_P[n] — PORT[n] MAC Traffic Shaper Bandwidth Control (n = 04)          | 200   |

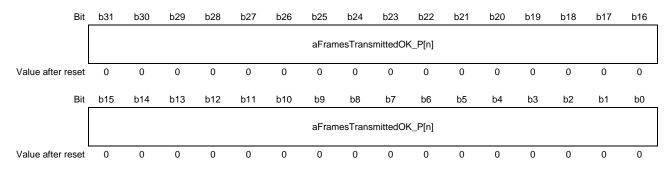

| 4.4.92  | aFramesTransmittedOK_P[n] — PORT[n] MAC Transmitted Valid Frame Count            |       |

|         | Register (n = 04)                                                                | 200   |

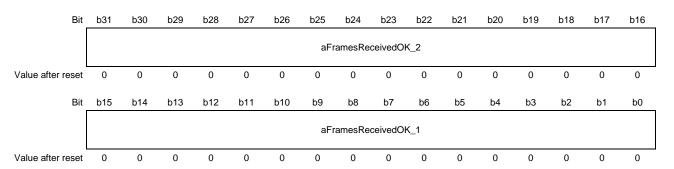

| 4.4.93  | aFramesReceivedOK_P[n] —PORT[n] MAC Received Valid Frame Count Register          |       |

|         | (n = 04)                                                                         | 201   |

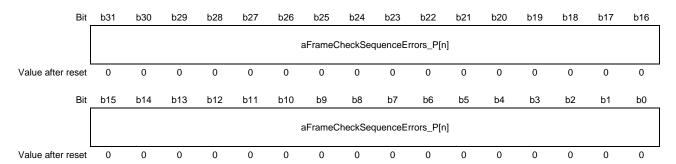

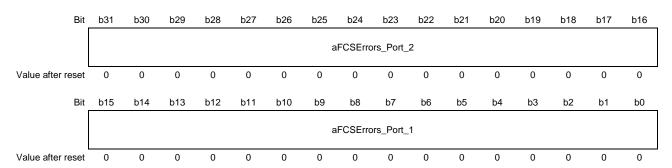

| 4.4.94  | aFrameCheckSequenceErrors_P[n] —PORT[n] MAC FCS Error Frame Count Register       |       |

|         | (n = 04)                                                                         | 201   |

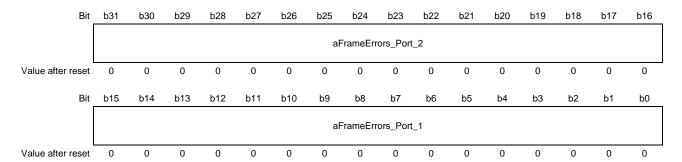

| 4.4.95  | aAlignmentErrors_P[n] —PORT[n] MAC Alignment Error Frame Count Register          |       |

|         | (n = 04)                                                                         | 202   |

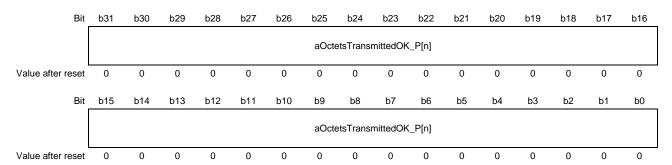

| 4.4.96  | aOctetsTransmittedOK_P[n] —PORT[n] MAC Transmitted Valid Frame Octets Register   |       |

|         | (n = 04)                                                                         | 202   |

| 4.4.97  | aOctetsReceivedOK_P[n] —PORT[n] MAC Received Valid Frame Octets Register         |       |

|         | (n = 04)                                                                         | 203   |

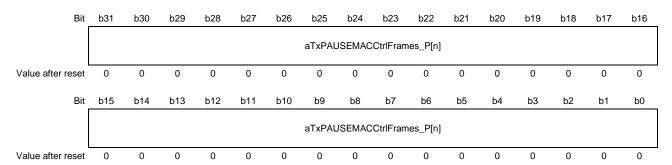

| 4.4.98  | aTxPAUSEMACCtrlFrames_P[n] —PORT[n] MAC Transmitted Pause Frame Count            |       |

|         | Register (n = 04)                                                                | 203   |

| 4.4.99  | aRxPAUSEMACCtrlFrames_P[n] — PORT[n] MAC Received Pause Frame Count              |       |

|         | Register (n = 04)                                                                | 204   |

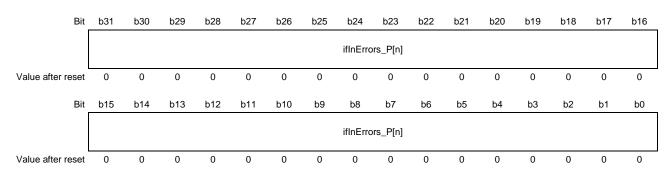

| 4.4.100 | ifInErrors_P[n] — PORT[n] MAC Input Error Count Register (n = 04)                | 204   |

| 4.4.101 | ifOutErrors_P[n] — PORT[n] MAC Output Error Count Register (n = 04)              | 205   |

| 4.4.102 | ifInUcastPkts_P[n] — PORT[n] MAC Received Unicast Frame Count Register           |       |

|         | (n = 04)                                                                         | 205   |

| 4.4.103 | ifInMulticastPkts_P[n] — PORT[n] MAC Received Multicast Frame Count Register     |       |

|         | (n = 04)                                                                         | 206   |

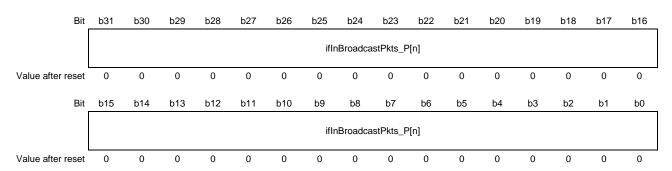

| 4.4.104 | ifInBroadcastPkts_P[n] — PORT[n] MAC Received Broadcast Frame Count Register     |       |

|         | (n = 04)                                                                         | 206   |

| 4.4.105 | ifOutDiscards P[n] — PORT[n] MAC Discarded Outbound Frame Count Register         |       |

|         | (n = 04)                                                                         | 207   |

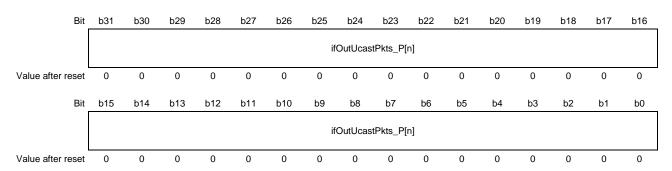

| 4.4.106 | ifOutUcastPkts_P[n] — PORT[n] MAC Transmitted Unicast Frame Count Register       |       |

|         | (n = 04)                                                                         | 207   |

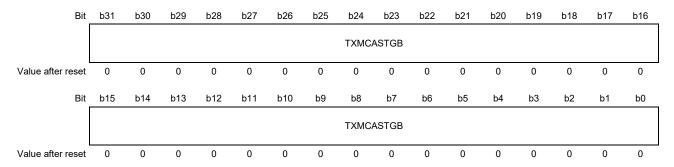

| 4.4.107 | ifOutMulticastPkts_P[n] — PORT[n] MAC Transmitted Multicast Frame Count Register |       |

|         | (n = 04)                                                                         | 208   |

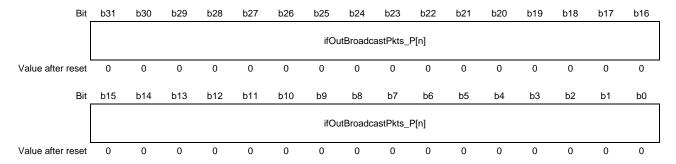

| 4.4.108 | ifOutBroadcastPkts P[n] — PORT[n] MAC Transmitted Broadcast Frame Count          |       |

|         | Register (n = 04)                                                                | 208   |

| 4.4.109 | etherStatsDropEvents_P[n] — PORT[n] MAC Dropped Frame Count Register             |       |

|         | (n = 04)                                                                         | 209   |

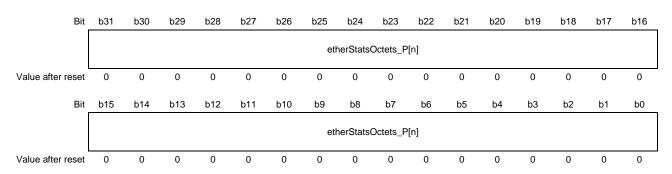

| 4.4.110 | etherStatsOctets P[n] — PORT[n] MAC All Frame Octets Register (n = 04)           |       |

| 4.4.111 |                                                                                  |       |

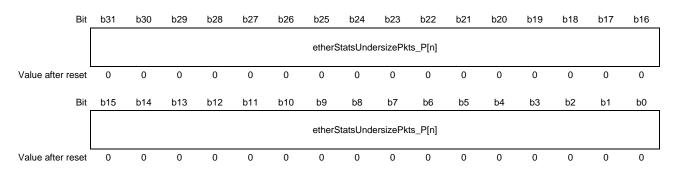

|         | etherStatsUndersizePkts_P[n] — PORT[n] MAC Too Short Frame Count Register        |       |

|         | (n = 04)                                                                         | 210   |

| 4 4 113 | etherStatsOversizePkts P[n] — PORT[n] MAC Too Long Frame Count Register          | _ 10  |

|         | (n = 04)                                                                         | 211   |

|         | (11                                                                              | - ' ' |

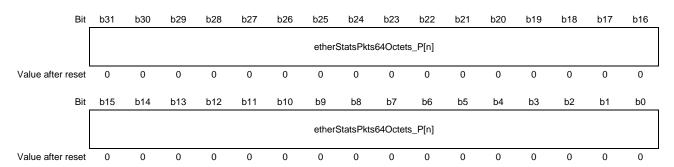

| 4.4.114 | etherStatsPkts64Octets_P[n] — PORT[n] MAC 64 Octets Frame Count Register                                   | 211 |

|---------|------------------------------------------------------------------------------------------------------------|-----|

| 4.4.115 | (n = 04)etherStatsPkts65to127Octets_P[n] — PORT[n] MAC 65 to 127 Octets Frame Count                        | 211 |

| 4.4.113 | Register (n = 04)                                                                                          | 212 |

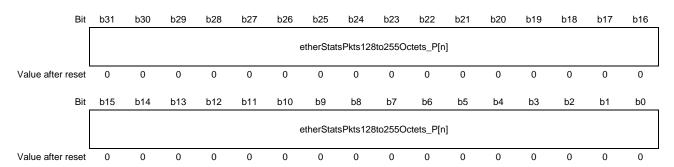

| 4.4.116 | etherStatsPkts128to255Octets_P[n] — PORT[n] MAC 128 to 255 Octets Frame Count                              |     |

|         | Register (n = 04)                                                                                          | 212 |

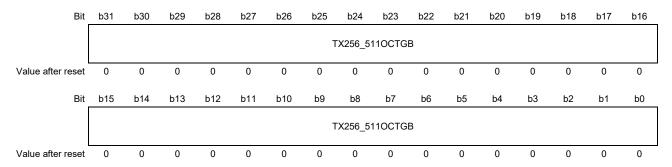

| 4.4.117 | etherStatsPkts256to511Octets_P[n] — PORT[n] MAC 256 to 511 Octets Frame Count                              |     |

|         | Register (n = 04)                                                                                          | 213 |

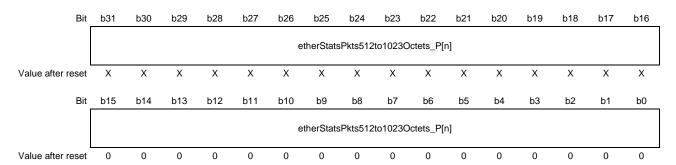

| 4.4.118 | etherStatsPkts512to1023Octets_P[n] — PORT[n] MAC 512 to 1023 Octets Frame                                  |     |

|         | Count Register (n = 04)                                                                                    | 213 |

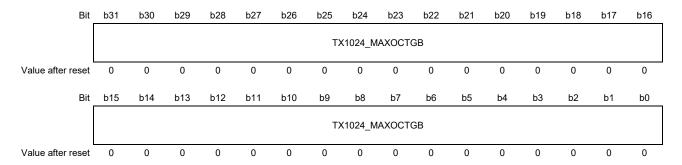

| 4.4.119 | etherStatsPkts1024to1518Octets_P[n] — PORT[n] MAC 1024 to 1519 Octets Frame                                |     |

|         | Count Register (n = 04)                                                                                    | 214 |

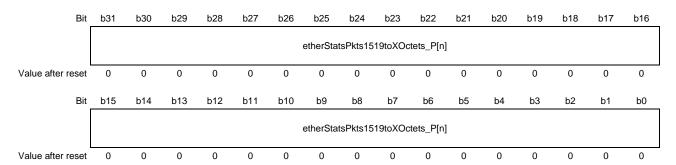

| 4.4.120 | etherStatsPkts1519toXOctets_P[n] — PORT[n] MAC Over 1519 Octets Frame Count                                |     |

|         | Register (n = 04)                                                                                          | 214 |

| 4.4.121 | etherStatsJabbers_P[n] — PORT[n] MAC Jabbers Frame Count Register (n = 04)                                 | 215 |

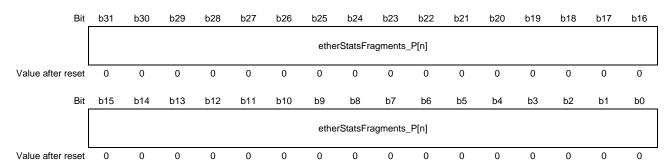

| 4.4.122 | etherStatsFragments_P[n] — PORT[n] MAC Fragment Frame Count Register                                       |     |

|         | (n = 04)                                                                                                   | 215 |

| 4.4.123 | VLANReceivedOK_P[n] — PORT[n] MAC Received VLAN Tagged Frame Count                                         |     |

|         | Register (n = 04)                                                                                          | 216 |

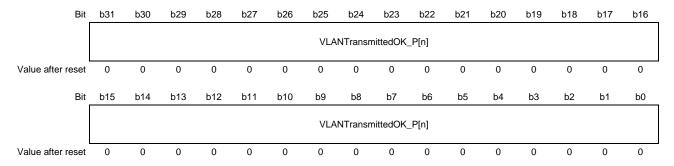

| 4.4.124 | VLANTransmittedOK_P[n] — PORT[n] MAC Transmitted VLAN Tagged Frame Count                                   |     |

|         | Register (n = 04)                                                                                          | 216 |

| 4.4.125 | FramesRetransmitted_P[n] — PORT[n] MAC Retransmitted Frame Count Register                                  |     |

|         | (n = 04)                                                                                                   | 217 |

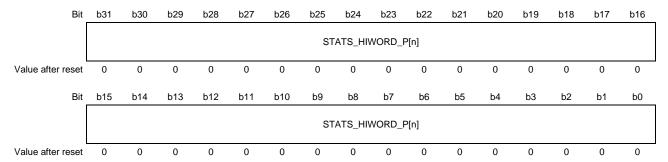

| 4.4.126 | STATS_HIWORD_P[n] — PORT[n] MAC Statistics Counter High Word Register                                      |     |

|         | (n = 04)                                                                                                   | 218 |

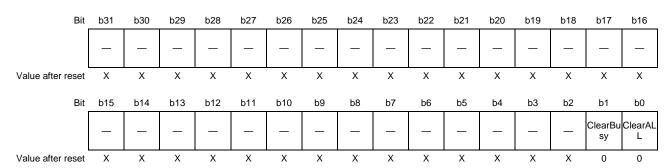

| 4.4.127 | STATS_CTRL_P[n] — PORT[n] MAC Statistics Control Register (n = 04)                                         | 219 |

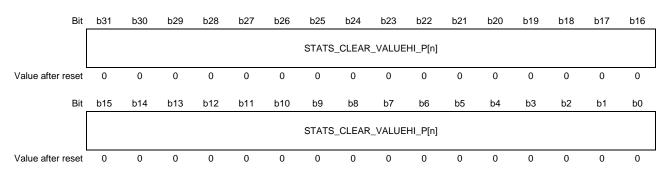

| 4.4.128 | STATS_CLEAR_VALUELO_P[n] — PORT[n] MAC Statistics Clear Value Lower                                        |     |

|         | Register (n = 04)                                                                                          | 220 |

| 4.4.129 | STATS_CLEAR_VALUEHI_P[n] — PORT[n] MAC Statistics Clear Value Higher                                       |     |

|         | Register (n = 04)                                                                                          | 220 |

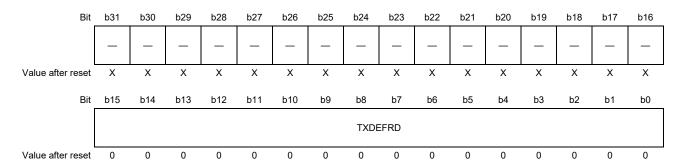

| 4.4.130 | aDeferred_P[n] — PORT[n] MAC Deferred Count Register (n = 03)                                              | 221 |

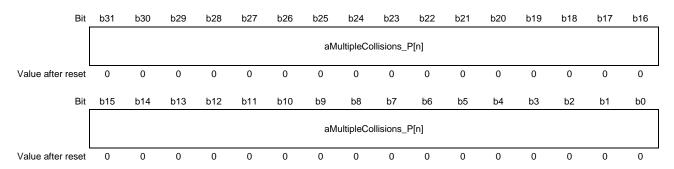

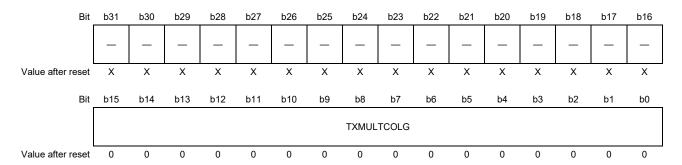

| 4.4.131 | $a {\tt Multiple Collisions\_P[n] PORT[n] \ MAC \ Multiple \ Collision \ Count \ Register \ (n=03) \dots}$ | 221 |

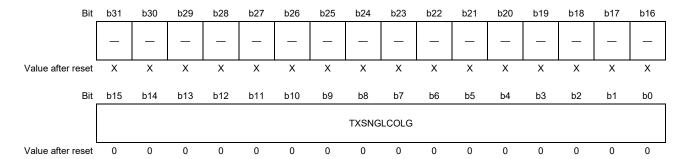

| 4.4.132 | $a Single Collisions\_P[n] \ \ PORT[n] \ MAC \ Single \ Collision \ Count \ Register \ (n=03)$             | 222 |

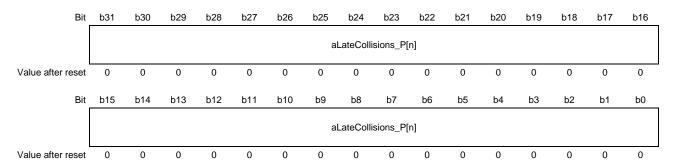

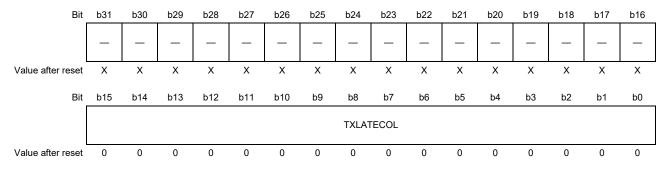

| 4.4.133 | aLateCollisions_P[n] — PORT[n] MAC Late Collision Count Register (n = 03)                                  | 222 |

| 4.4.134 | aExcessiveCollisions_P[n] — PORT[n] MAC Excessive Collision Count Register                                 |     |

|         | (n = 03)                                                                                                   | 223 |

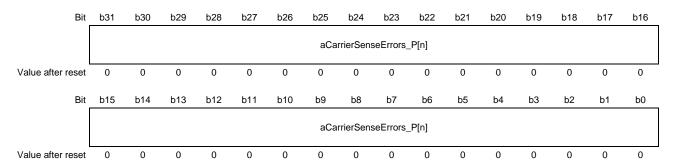

| 4.4.135 | aCarrierSenseErrors_P[n] — PORT[n] MAC Carrier Sense Error Count Register                                  |     |

|         | (n = 03)                                                                                                   | 223 |

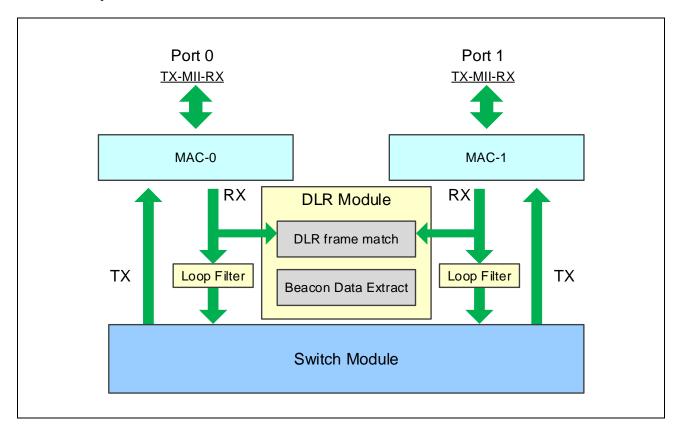

| 4.4.136 | DLR_CONTROL — DLR Control Register                                                                         | 224 |

| 4.4.137 | DLR_STATUS — DLR Status Register                                                                           | 225 |

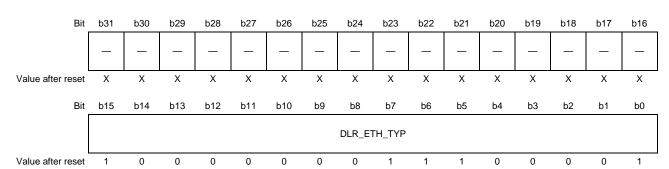

| 4.4.138 | DLR_ETH_TYP — DLR Ethernet Type Register                                                                   | 226 |

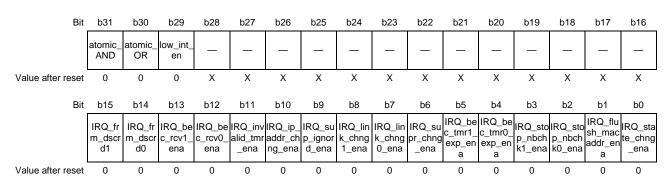

| 4.4.139 | DLR_IRQ_CONTROL — DLR Interrupt Control Register                                                           | 227 |

| 4.4.140 | DLR_IRQ_STAT_ACK — DLR Interrupt Status/ACK Register                                                       | 228 |

|         |                                                                                                            |     |

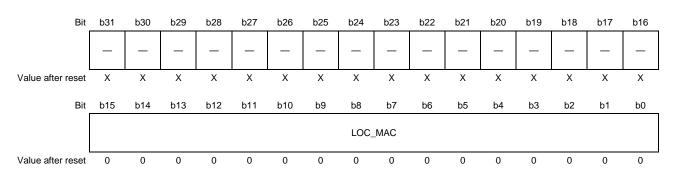

| 4.4.141 | DLR_LOC_MAClo — DLR Local MAC Address Low Register                 | 230 |

|---------|--------------------------------------------------------------------|-----|

| 4.4.142 | DLR_LOC_MAChi — DLR Local MAC Address High Register                | 230 |

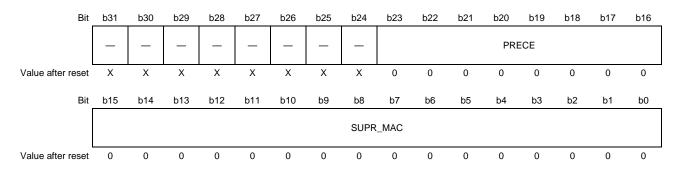

| 4.4.143 | DLR_SUPR_MACIo — DLR Supervisor MAC Address Low Register           | 231 |

| 4.4.144 | DLR_SUPR_MAChi — DLR Supervisor MAC Address High Register          | 231 |

| 4.4.145 | DLR_STATE_VLAN — DLR Ring Status/VLAN Register                     | 232 |

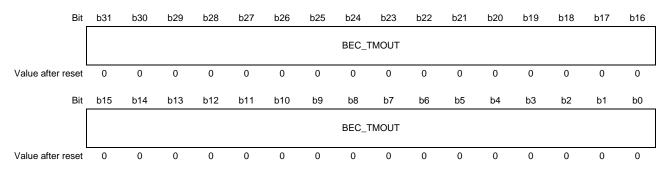

| 4.4.146 | DLR_BEC_TMOUT — DLR Beacon Timeout Register                        | 232 |

| 4.4.147 | DLR_BEC_INTRVL — DLR Beacon Interval Register                      | 233 |

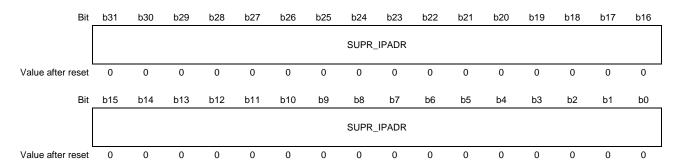

| 4.4.148 | DLR_SUPR_IPADR — DLR Supervisor IP Address Register                | 233 |

| 4.4.149 | DLR_ETH_STYP_VER — DLR Sub Type/Protocol Version Register          | 234 |

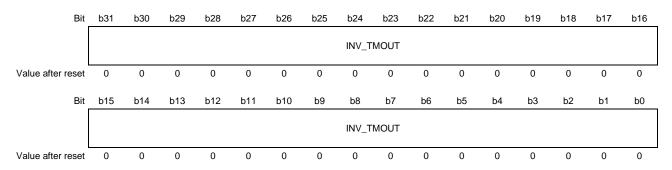

| 4.4.150 | DLR_INV_TMOUT — DLR Beacon Timeout Timer Register                  | 234 |

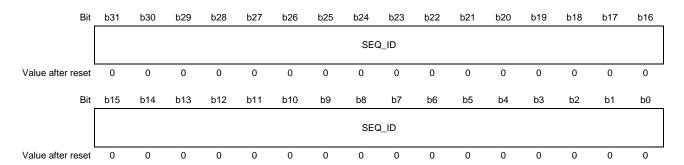

| 4.4.151 | DLR_SEQ_ID — DLR Sequence ID Register                              | 235 |

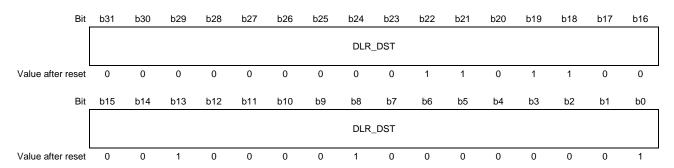

| 4.4.152 | DLR_DSTIo — DLR Beacon Destination Address Low Register            | 235 |

| 4.4.153 | DLR_DSThi — DLR Beacon Destination Address High Register           | 236 |

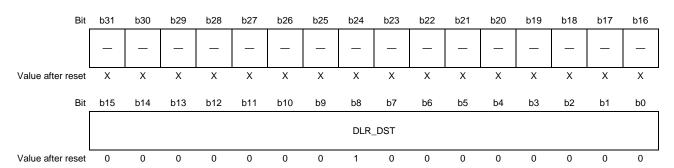

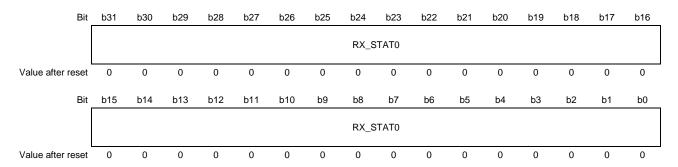

| 4.4.154 | DLR_RX_STAT0 — DLR Received Frame Statistic Register 0             | 236 |

| 4.4.155 | DLR_RX_ERR_STAT0 — DLR Received Frame Error Statistic Register 0   | 237 |

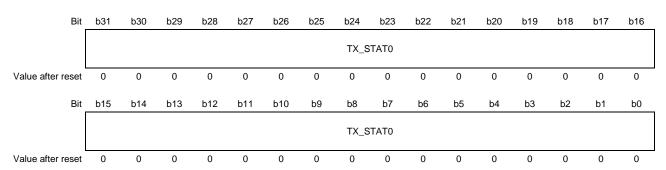

| 4.4.156 | DLR_TX_STAT0 — DLR Transmitted Frame Statistic Register 0          | 237 |

| 4.4.157 | DLR_RX_STAT1 — DLR Received Frame Statistic Register 1             | 238 |

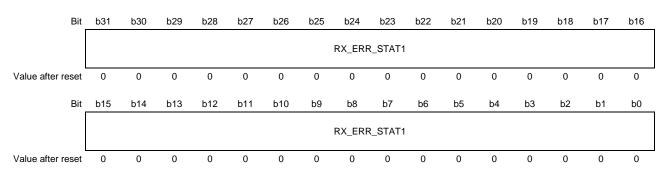

| 4.4.158 | DLR_RX_ERR_STAT1 — DLR Received Frame Error Statistic Register 1   | 238 |

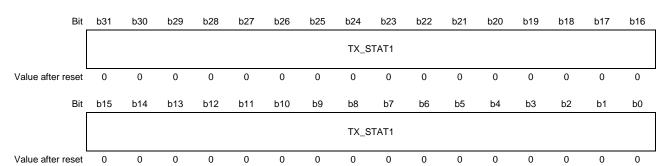

| 4.4.159 | DLR_TX_STAT1 — DLR Transmitted Frame Statistic Register 1          | 239 |

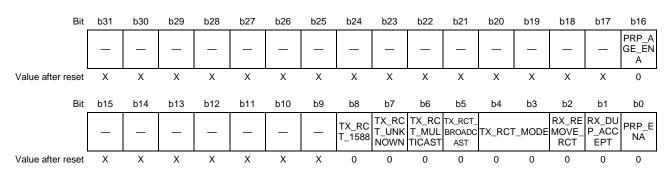

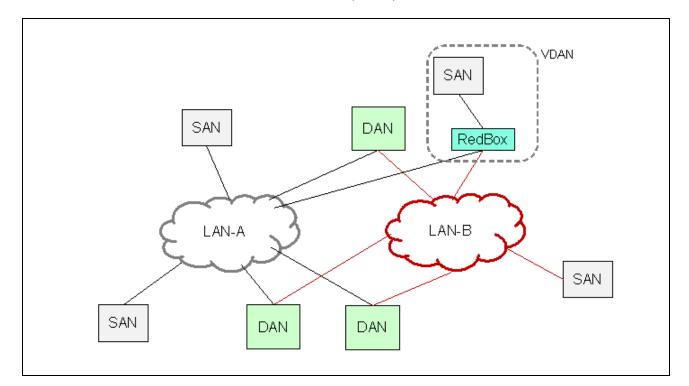

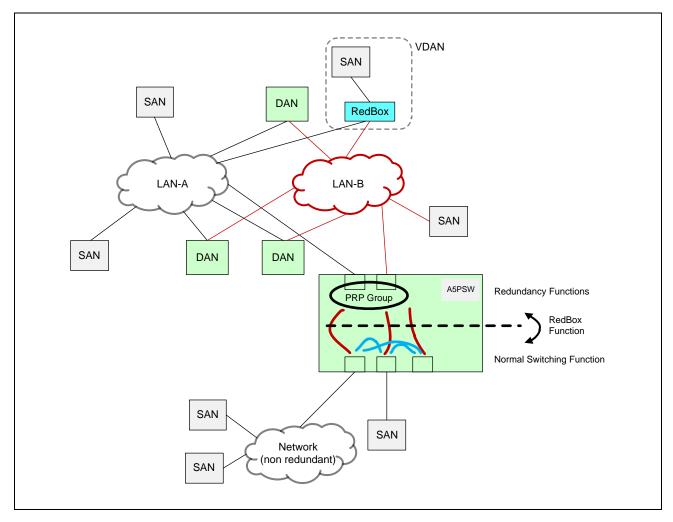

| 4.4.160 | PRP_CONFIG — PRP Configuration Register                            | 240 |

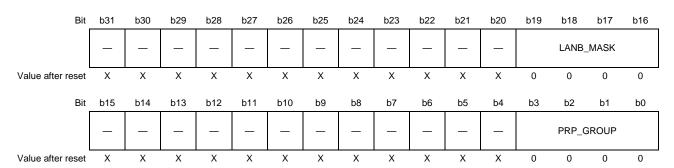

| 4.4.161 | PRP_GROUP — PRP Port Group Register                                | 242 |

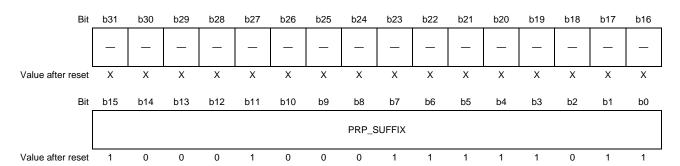

| 4.4.162 | PRP_SUFFIX — PRP RCT Suffix                                        | 243 |

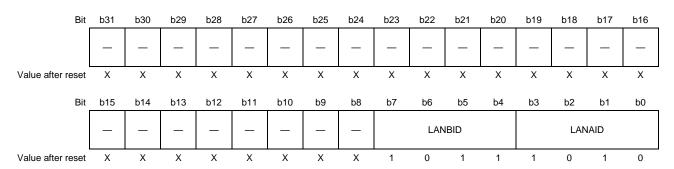

| 4.4.163 | PRP_LANID — PRP LAN Identifier                                     | 243 |

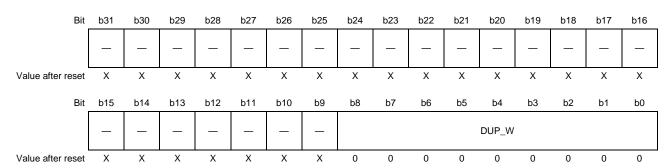

| 4.4.164 | DUP_W — PRP Max Duplicate Detection Window Size                    | 244 |

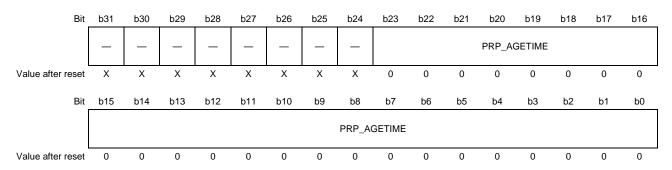

| 4.4.165 | PRP_AGETIME — PRP Aging Time Define Register                       | 244 |

| 4.4.166 | PRP_IRQ_CONTROL — PRP Interrupt Control Register                   | 245 |

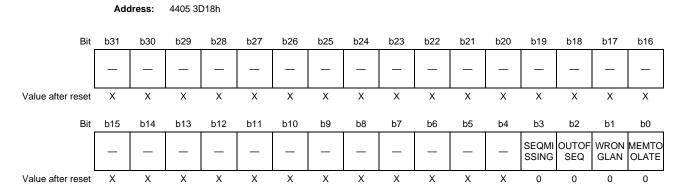

| 4.4.167 | PRP_IRQ_STAT_ACK — PRP Interrupt Status/ACK Register               | 246 |

| 4.4.168 | RM_ADDR_CTRL — PRP History Memory Transactions Control Register    | 247 |

| 4.4.169 | RM_DATA — PRP Memory Data Register                                 | 248 |

| 4.4.170 | RM_STATUS — PRP Memory Controller Status Indication                | 248 |

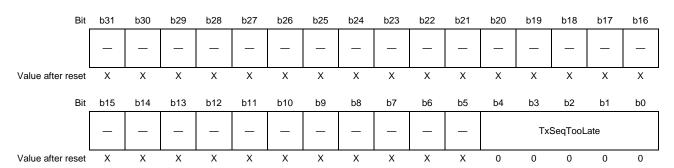

| 4.4.171 | TxSeqTooLate — PRP Frame Transmission Retrieval of Failed Sequence | 249 |

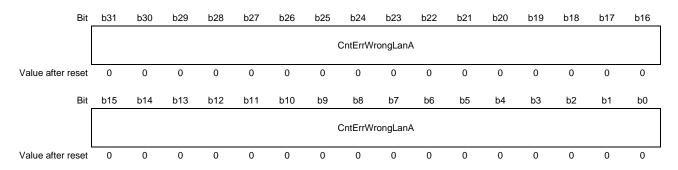

| 4.4.172 | CntErrWrongLanA — PRP Wrong ID LAN-A Count Register                | 249 |

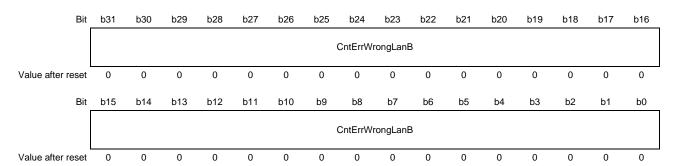

| 4.4.173 | CntErrWrongLanB — PRP Wrong ID LAN-B Count Register                | 250 |

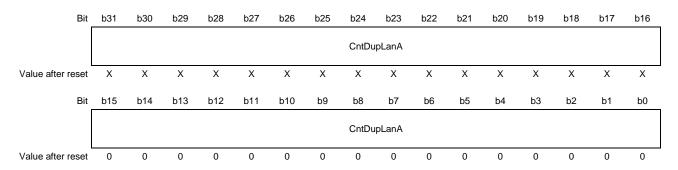

| 4.4.174 | CntDupLanA — PRP Duplicate LAN-A Count Register                    | 250 |

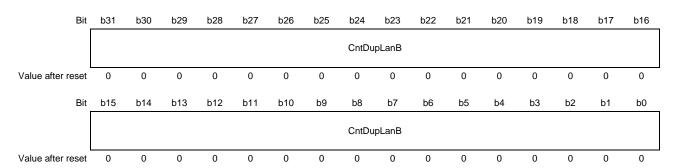

| 4.4.175 | CntDupLanB — PRP Duplicate LAN-B Count Register                    | 251 |

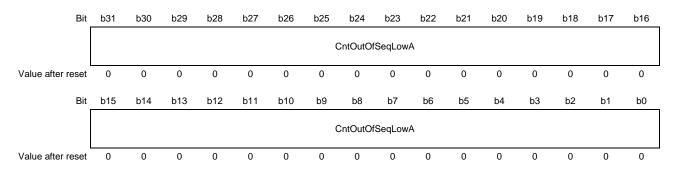

| 4.4.176 | CntOutOfSeqLowA — PRP Sequence Error Low LAN-A Count Register      | 251 |

| 4.4.177 | CntOutOfSeqLowB — PRP Sequence Error Low LAN-B Count Register      | 252 |

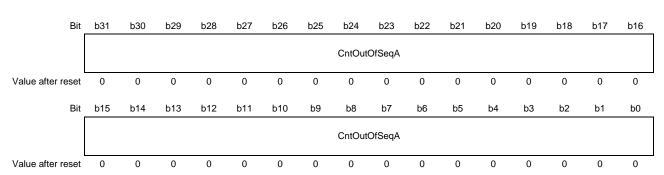

| 4.4.178 | CntOutOfSeqA — PRP Sequence Error LAN-A Count Register             | 252 |

| 4.4.179 | CntOutOfSeqB — PRP Sequence Error LAN-B Count Register             |     |

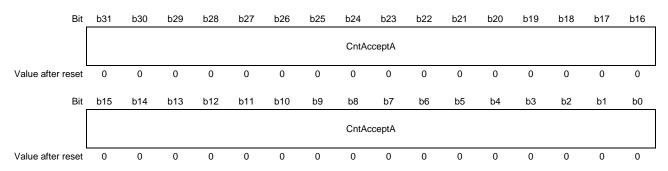

| 4.4.180 | CntAcceptA — PRP Valid Frame LAN-A Count Register                  | 253 |

| 4.4.181 | CntAcceptB — PRP Valid Frame LAN-B Count Register                  |     |

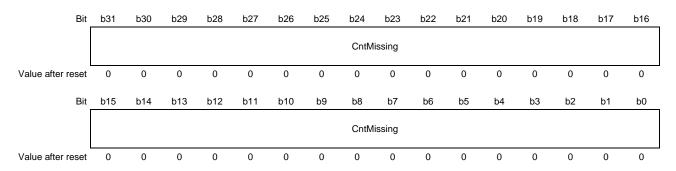

| 4.4.182 | CntMissing — PRP Drop history Adjustment Count                     | 254 |

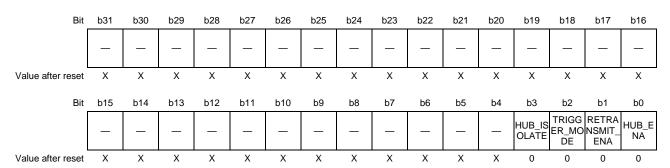

| 4.4.183 | HUB_CONFIG — HUB Configuration Register                            | 255 |

|         |                                                                    |     |

|     | 4.4.184      | HUB_   | GROUP — HUB Port Group Register                                         | 256 |

|-----|--------------|--------|-------------------------------------------------------------------------|-----|

|     | 4.4.185      | HUB_   | DEFPORT — HUB Default Port Selection Register                           | 257 |

|     | 4.4.186      | HUB_   | TRIGGER_IMMEDIATE — HUB Transmission Trigger Immediate Register         | 258 |

|     | 4.4.187      | HUB_   | TRIGGER_AT — HUB Transmission Trigger At Register                       | 259 |

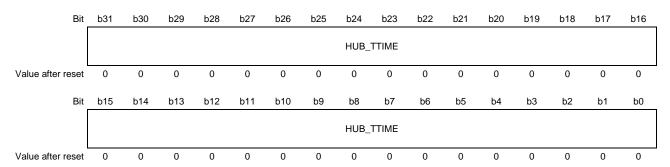

|     | 4.4.188      | HUB_   | TTIME — HUB Transmission Time Define Register                           | 259 |

|     | 4.4.189      | HUB_   | IRQ_CONTROL — HUB Interrupt Control Register                            | 260 |

|     | 4.4.190      | HUB_   | IRQ_STAT_ACK — HUB Interrupt Status/ACK Register                        | 261 |

|     | 4.4.191      | HUB_   | STATUS — HUB Status Register                                            | 262 |

|     | 4.4.192      | HUB_   | OPORT_STATUS — HUB Output Port Status Register                          | 263 |

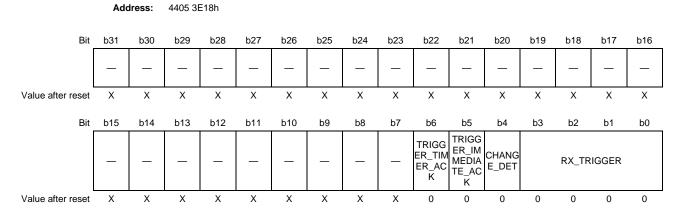

|     | 4.4.193      | RXMA   | TCH_CONFIG[n] — RX Pattern Match Configuration for PORT[n] (n = 04)     | 263 |

|     | 4.4.194      | PATTI  | ERN_CTRL[n] — RX Pattern Match Function Control for Pattern[n] (n = 07) | 264 |

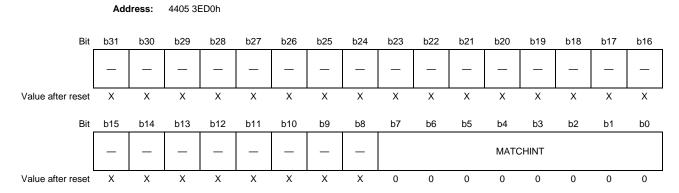

|     | 4.4.195      | PTN_I  | RQ_CONTROL — RX Pattern Match Interrupt Control Register                | 266 |

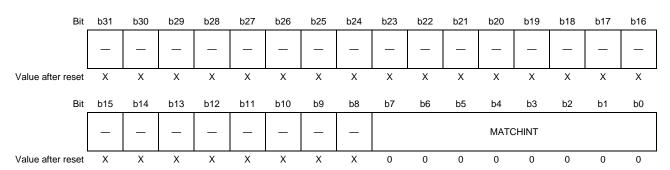

|     | 4.4.196      | PTN_I  | RQ_STAT_ACK — RX Pattern Match Interrupt Status/ACK Register            | 267 |

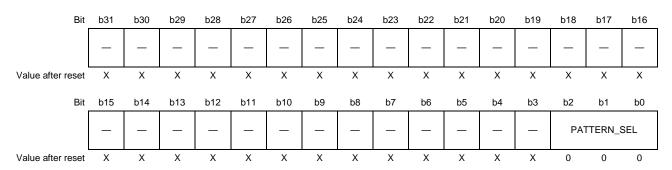

|     | 4.4.197      | PATTI  | ERN_SEL — RX Pattern Number Selection Register                          | 267 |

|     | 4.4.198      | PTRN   | _CMP_30 — Pattern Compare Value Bytes 3 0                               | 268 |

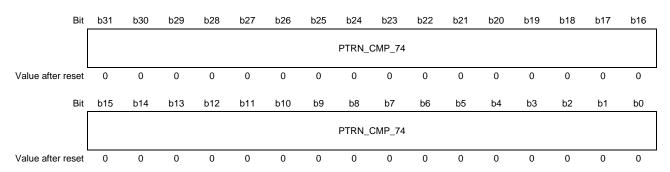

|     | 4.4.199      | PTRN   | _CMP_74 — Pattern Compare Value Bytes 7 4                               | 268 |

|     | 4.4.200      | PTRN   | _CMP_118 — Pattern Compare Value Bytes 11 8                             | 269 |

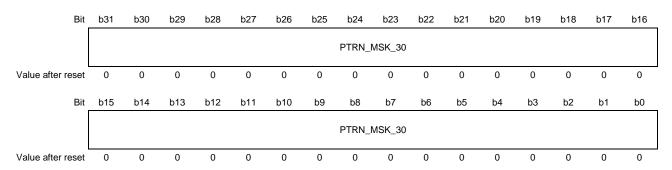

|     | 4.4.201      | PTRN   | _MSK_30 — Pattern Mask for Bytes 3 0                                    | 269 |

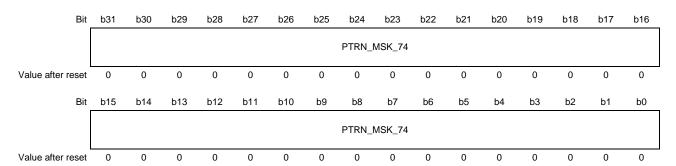

|     | 4.4.202      | PTRN   | _MSK_74 — Pattern Mask for Bytes 7 4                                    | 270 |

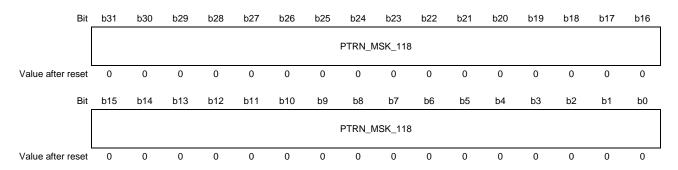

|     | 4.4.203      | PTRN   | _MSK_118 — Pattern Mask for Bytes 11 8                                  | 270 |

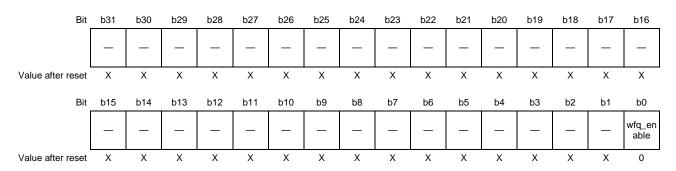

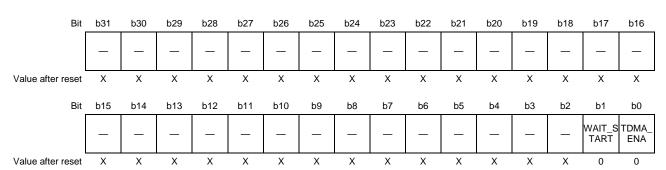

|     | 4.4.204      | TDMA   | _CONFIG — TDMA Configuration Register                                   | 271 |

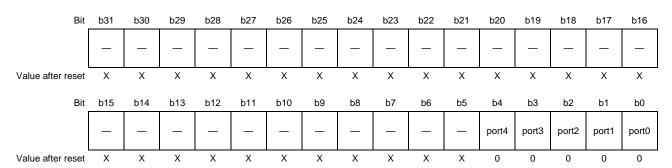

|     | 4.4.205      | TDMA   | _PORTS — TDMA Scheduling Enable Register                                | 272 |

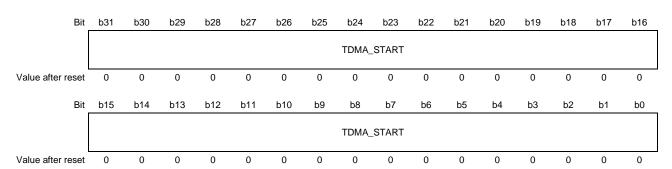

|     | 4.4.206      | TDMA   | _START — TDMA Start Time Set Register                                   | 272 |

|     | 4.4.207      | TDMA   | _MODULO — TDMA System Timer Modulo                                      | 273 |

|     | 4.4.208      | TDMA   | _CYCLE — TDMA Periodic Cycle Set Register                               | 273 |

|     | 4.4.209      | TDMA   | _T1 — TDMA 1st Time Offset                                              | 274 |

|     | 4.4.210      | TDMA   | _T2 — TDMA 2nd Time Offset                                              | 274 |

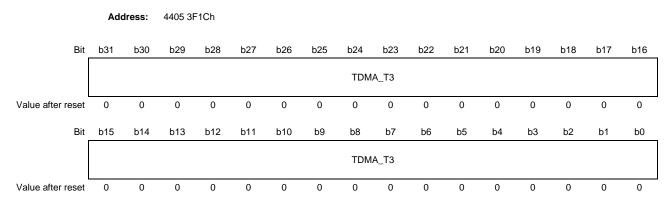

|     | 4.4.211      | TDMA   | _T3 — TDMA 3rd Time Offset                                              | 275 |

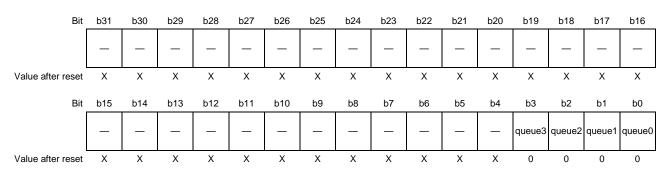

|     | 4.4.212      | QUEU   | JES_TS — TDMA 1st Slot Transmit Enable                                  | 276 |

|     | 4.4.213      | QUEU   | JES_T1 — TDMA 2nd Slot Transmit Enable                                  | 276 |

|     | 4.4.214      | QUEU   | JES_T2 — TDMA 3rd Slot Transmit Enable                                  | 277 |

|     | 4.4.215      | QUEU   | JES_T3 — TDMA Last Slot Transmit Enable                                 | 277 |

|     | 4.4.216      | QUEU   | JES_START — TDMA First Cycle Transmit Enable                            | 278 |

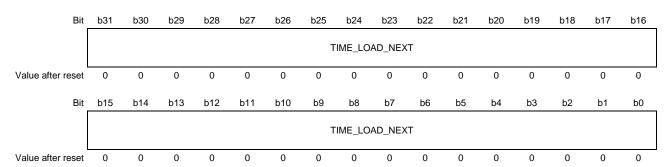

|     | 4.4.217      | TIME_  | LOAD_NEXT — TDMA Calculated Next Loading Time                           | 278 |

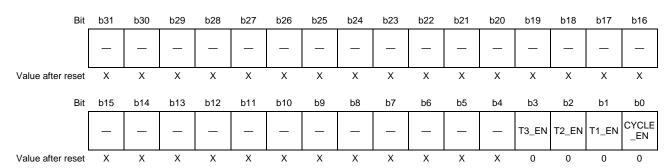

|     | 4.4.218      | TDMA   | _IRQ_CONTROL — TDMA Interrupt Control Register                          | 279 |

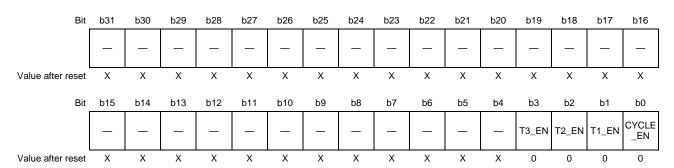

|     | 4.4.219      | TDMA   | _IRQ_STAT_ACK — TDMA Interrupt Status/ACK Register                      | 280 |

| 4.5 | Opera        | ation  |                                                                         | 281 |

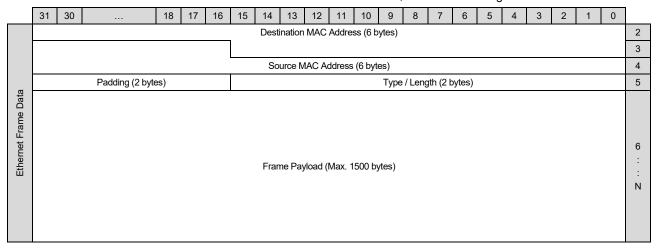

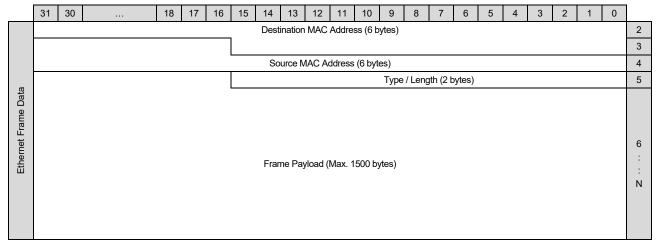

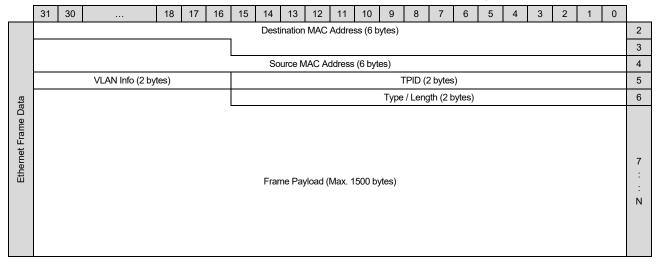

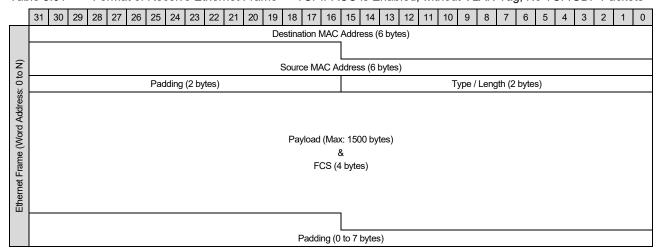

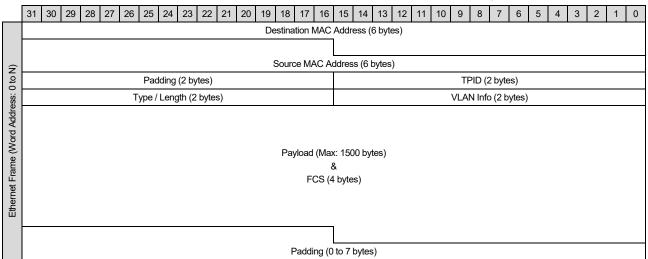

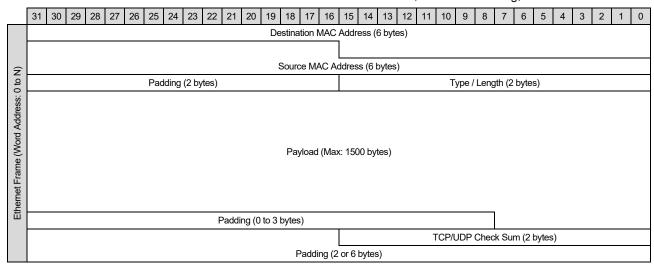

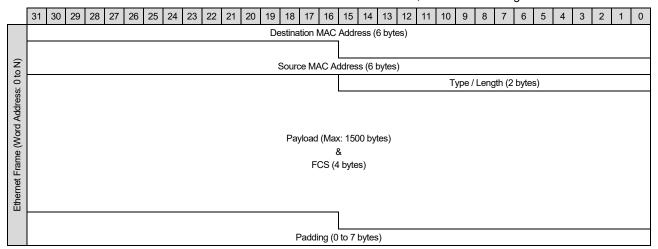

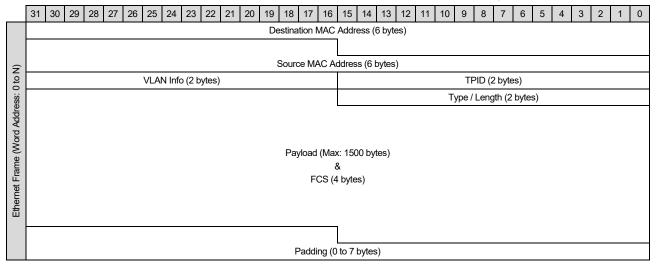

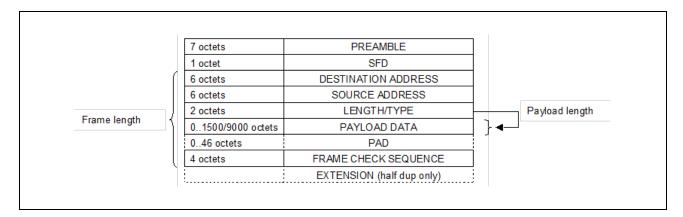

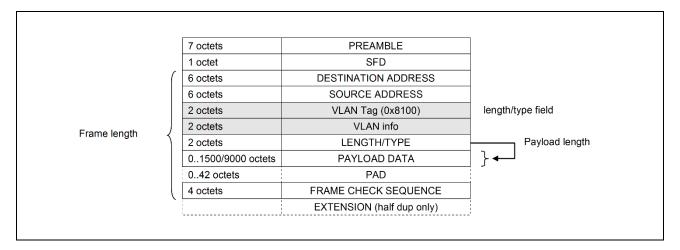

|     | 4.5.1        | Ethern | net Frame Format Overview                                               | 281 |

|     | 4.5          |        | Overview                                                                |     |

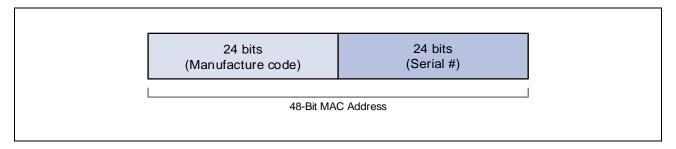

|     |              | .1.2   | MAC Address Overview                                                    |     |

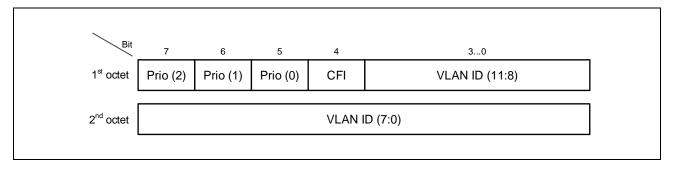

|     | 4.5.<br>4.5. | .1.3   | VLAN Tag Overview  Pause Frames                                         |     |

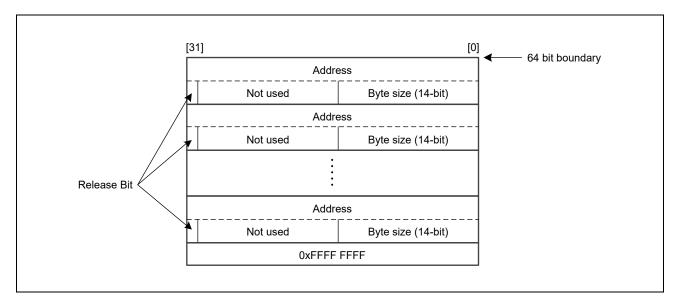

|     | 4.5.2        |        | me Format                                                               |     |

|     | 4.5.2        |        | Definitions                                                             |     |

|     |              |        |                                                                         | 55  |

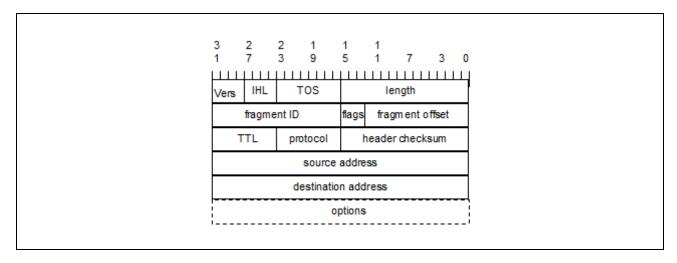

| 4.5.2.2    | Ethernet Types                                    | 285 |

|------------|---------------------------------------------------|-----|