# R-IN32M3 Series

User's Manual: Peripheral Modules

- R-IN32M3-EC

- R-IN32M3-CL

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Document Number: R18UZ0007EJ1100 Issue date: Dec. 28, 2018

Renesas Electronics

www.renesas.com

### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment;

and visual equipment, nome electronic appliances, machine tools, personal electronic equipment, and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### **General Precautions in the Handling of Products**

The following usage notes are applicable to CMOS devices from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

- 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- Arm® and Cortex® are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

- Ethernet is a registered trademark of Fuji Xerox Co., Ltd.

- IEEE is a registered trademark of the Institute of Electrical and Electronics Engineers Inc.

- TRON is an acronym for "The Real-time Operation system Nucleus".

- ITRON is an acronym for "Industrial TRON".

- μITRON is an acronym for "Micro Industrial TRON".

- TRON, ITRON, and  $\mu ITRON$  do not refer to any specific product or products.

- EtherCAT® and TwinCAT® are registered trademark and patented technology, licensed by Beckhoff Automation GmbH, Germany.

- CC-Link and CC-Link IE Field are registered trademarks of the CC-Link Partner Association (CLPA).

- Additionally all product names and service names in this document are a trademark or a registered trademark which belongs to the respective owners.

## How to Use This Manual

### 1. Purpose and Target Readers

This manual is intended for users who wish to understand the functions of industrial Ethernet communications ASSP (Application Specific Standard Product) "R-IN32M4-CL2" (R9J03G019GBG) and design application systems using it. Target users are expected to understand the fundamentals of electrical circuits, logic circuits, and microcomputers.

When designing an application system that includes this MCU, take all points to note into account. Points to note are given in their contexts and at the final part of each section, and in the section giving usage notes.

The list of revisions is a summary of major points of revision or addition for earlier versions. It does not cover all revised items. For details on the revised points, see the actual locations in the manual.

The mark "<R>" in the text indicates the major revisions to this version. You can easily find these revisions by copying "<R>" and entering it in the search-string box for the PDF file.

#### Literature

Literature may be preliminary versions. Note, however, that the following descriptions do not indicate "Preliminary". Some documents on cores were created when they were planned or still under development. So, they may be directed to specific customers. Last four digits of document number (described as \*\*\*\*) indicate version information of each document. Please download the latest document from our web site and refer to it.

### Documents Related to R-IN32M3

| Document Name                                     | Document No.    |

|---------------------------------------------------|-----------------|

| R-IN32M3 Series Data Sheet                        | R18DS0008EJ**** |

| R-IN32M3-EC User's Manual                         | R18UZ0003EJ**** |

| R-IN32M3-CL User's Manual                         | R18UZ0005EJ**** |

| R-IN32M3 Series Programming Manual: OS            | R18UZ0011EJ**** |

| R-IN32M3 Series Programming Manual: Driver        | R18UZ0009EJ**** |

| R-IN32M3 Series User's Manual: Peripheral Modules | This manual     |

## 2. Numbers and Symbols

Data significance: Higher digits on the left and lower digits on the right

Active low representation:

xxxZ (capital letter Z after pin or signal name)

or xxx\_N (capital letter \_N after pin or signal name)

or xxnx (pin or signal name contains small letter n)

Note:

Footnote for item marked with Note in the text

Caution:

Information requiring particular attention

Remark:

Supplementary information

Numeric representation:

Binary: xxxx, xxxxB or n'bxxxx (n bits)

Decimal: xxxx

Hexadecimal: xxxxH or n'hxxxx (n bits)

Prefix indicating the power of 2 (address space, memory capacity):

K (kilo):  $2^{10} = 1024$

M (mega):  $2^{20} = 1024^2$

G (giga):  $2^{30} = 1024^3$

Data type:

Word: 32 bits

Half word: 16 bits

Byte: 8 bits

## Contents

| 1. | Intro | duction                                     | 1-1 |

|----|-------|---------------------------------------------|-----|

|    | 1.1   | Type Names of R-IN32M3-Series Products      | 1-1 |

|    | 1.2   | Base Addresses of the System Registers Area | 1-1 |

|    |       |                                             |     |

| 2. | Clock | s and Resets                                | 2-1 |

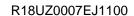

|    | 2.1   | Clock Configuration                         | 2-1 |

|    | 2.1.1 | Description of Internal Clocks              | 2-1 |

|    | 2.1.2 | Clock Configuration Diagram                 | 2-2 |

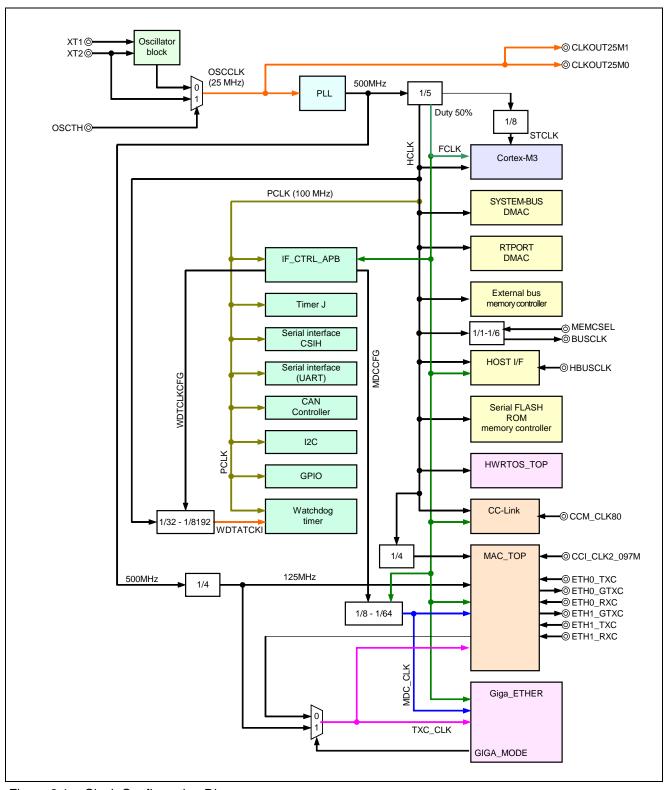

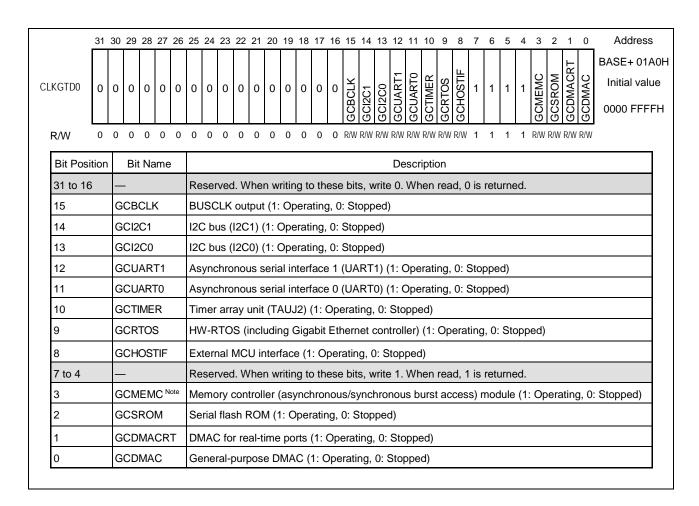

|    | 2.2   | Stopping of Clock Supply                    | 2-3 |

|    | 2.2.1 | Overview                                    | 2-3 |

|    | 2.2.2 | Clock Control Registers (CLKGTD0, CLKGTD1)  | 2-4 |

|    | 2.3   | Reset                                       | 2-6 |

|    | 2.3.1 | Overview                                    | 2-6 |

|    | 2.3.2 | Features                                    | 2-6 |

|    | 2.3.3 | Reset Control Registers                     | 2-8 |

|    | 2.4   | Operations for Reset                        | 2-9 |

| _  | ODL   | and the transfer of PAMs                    | 0.4 |

| 3. | CPU   | and Internal RAMs                           |     |

|    | 3.1   | CPU-Core Information                        |     |

|    | 3.2   | CPU-Core Configuration Information          |     |

|    | 3.3   | Restrictions                                | 3-2 |

|    | 3.4   | Internal Instruction RAM                    | 3-3 |

|    | 3.4.1 | Outline of Features                         | 3-3 |

|    | 3.4.2 | Read Buffer                                 | 3-3 |

|    | 3.4.3 | Write Interface                             | 3-3 |

|    | 3.5   | Internal Data RAM                           | 3-4 |

|    | 3.5.1 | Outline of Features                         | 3-4 |

|    | 3.6   | Buffer RAM                                  | 3-5 |

|    | 3.6.1 | Outline of Features                         | 3-5 |

| 4. | Rue / | Architecture                                | 1_1 |

|    |       |                                             |     |

|    | 4.1   | Bus Occupancy by the Cortex-M3              | 4-2 |

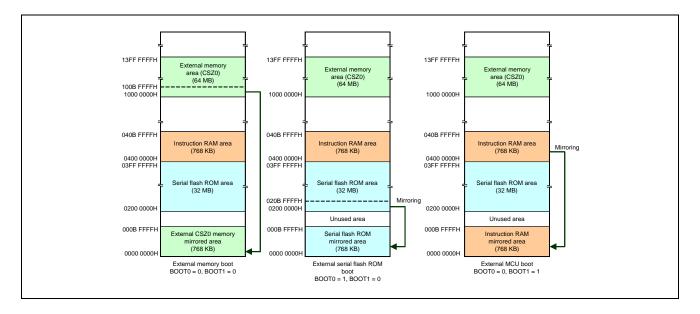

| 5. | Booti | ng Procedure                                | 5-1 |

|    | 5.1   | Selecting the Boot Mode                     |     |

|    |       | <i>6</i>                                    |     |

| 5.2      | Initializing the Internal RAM                                                           | 5-2  |

|----------|-----------------------------------------------------------------------------------------|------|

| 5.3      | Memory Map in Each Boot Mode                                                            | 5-2  |

| 5.4      | Booting Sequence                                                                        | 5-3  |

| 5.4.1    | When Booting from an External Memory                                                    | 5-3  |

| 5.4.2    | When Booting from the External Serial Flash ROM                                         | 5-4  |

| 5.4.3    | When Downloading the Program from the External MCU and Booting the CPU                  | 5-4  |

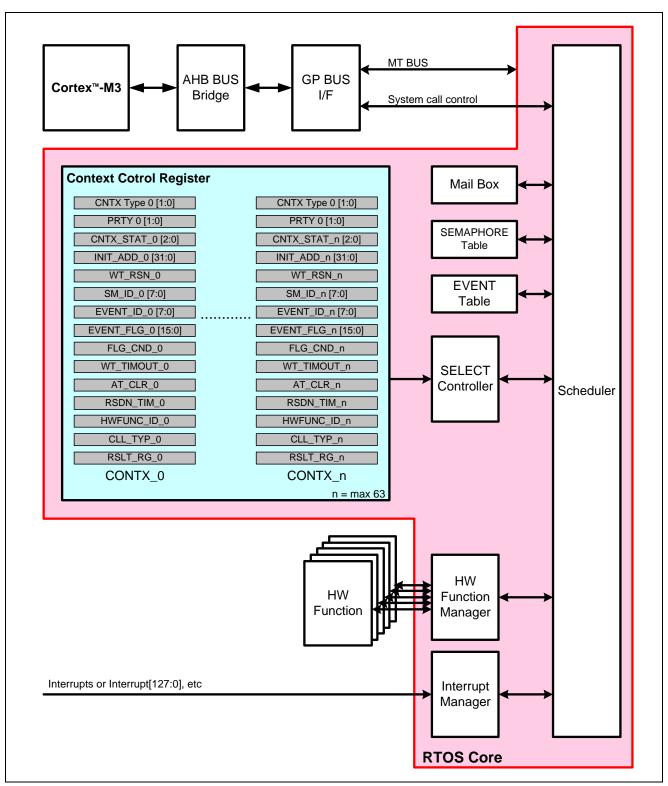

| 6. Hard  | ware Real-Time OS (HW-RTOS)                                                             | 6-1  |

| 6.1      | Outline of Features                                                                     | 6-1  |

| 6.2      | Semaphores                                                                              | 6-1  |

| 6.3      | Events                                                                                  | 6-1  |

| 6.4      | Mailboxes                                                                               | 6-2  |

| 6.5      | Operation of HW-RTOS                                                                    | 6-2  |

| 7. Gigal | pit Ethernet MAC                                                                        | 7-1  |

| 7.1      | Overview                                                                                | 7-1  |

| 7.1.1    | Ethernet Interface Architecture                                                         | 7-2  |

| 7.2      | Features                                                                                | 7-3  |

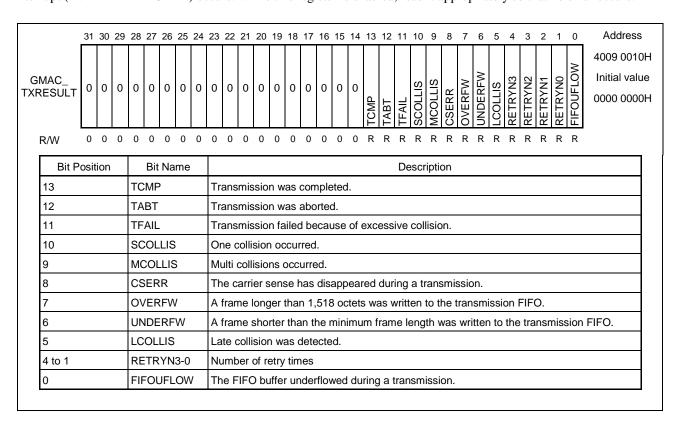

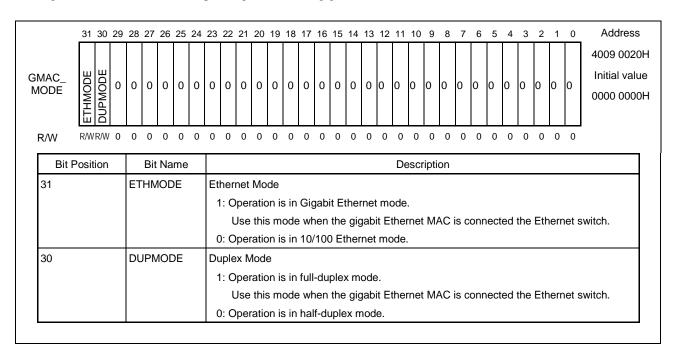

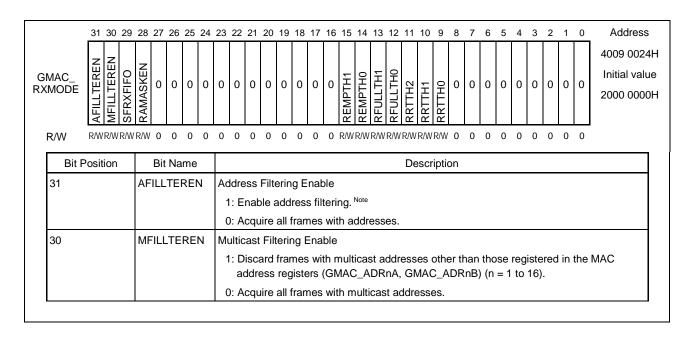

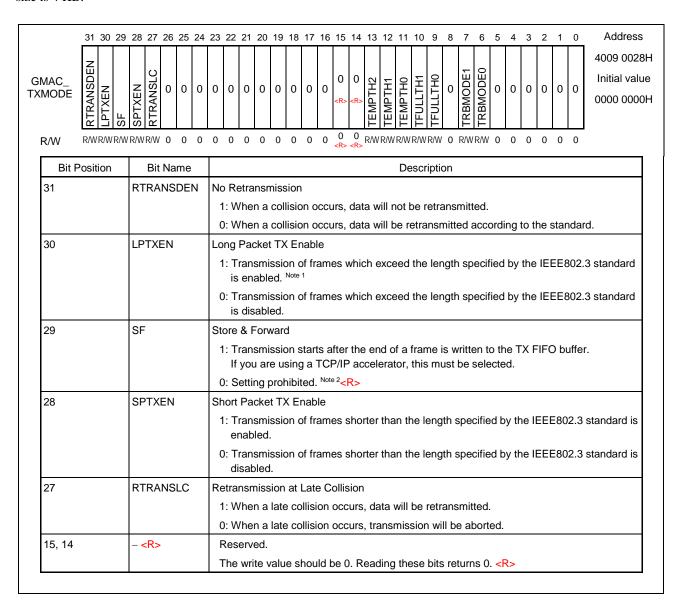

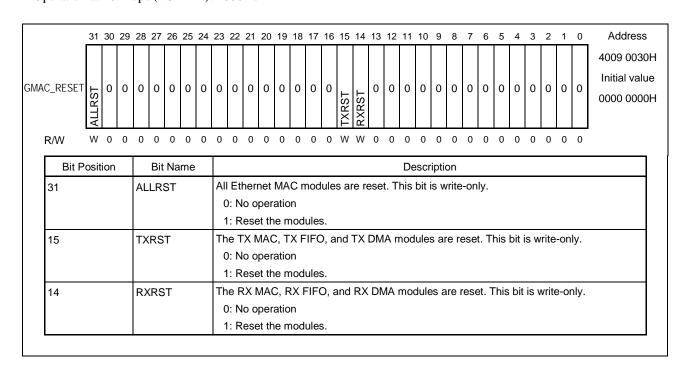

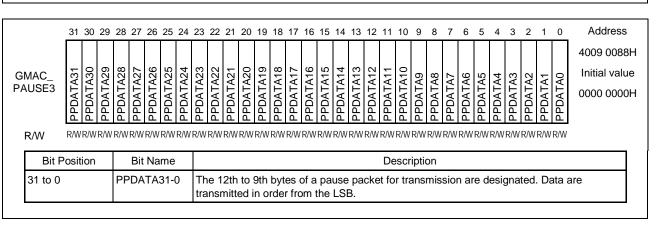

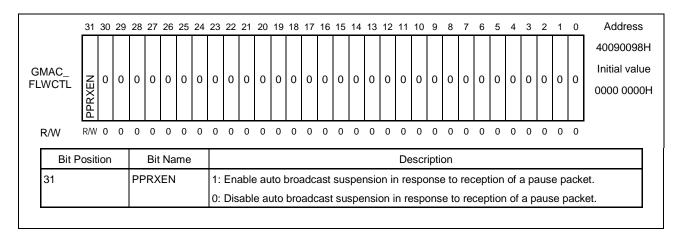

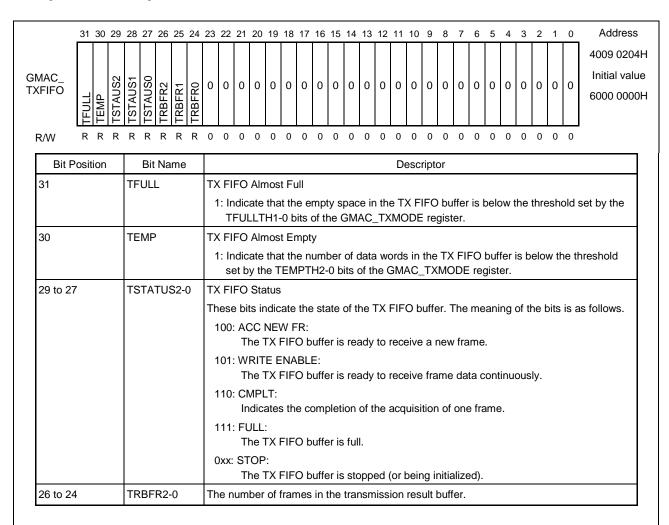

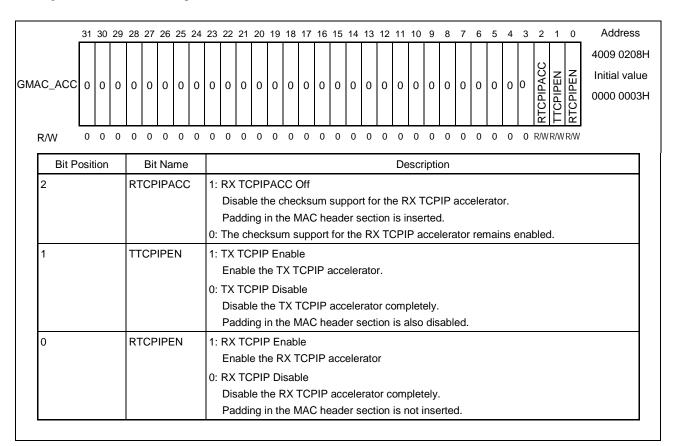

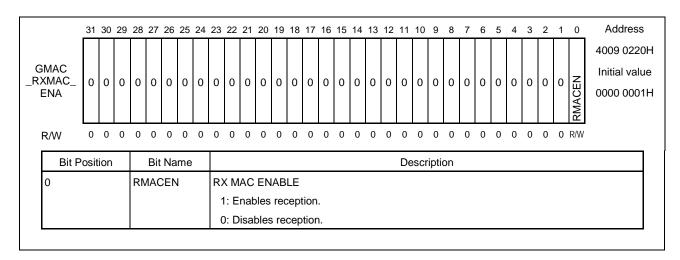

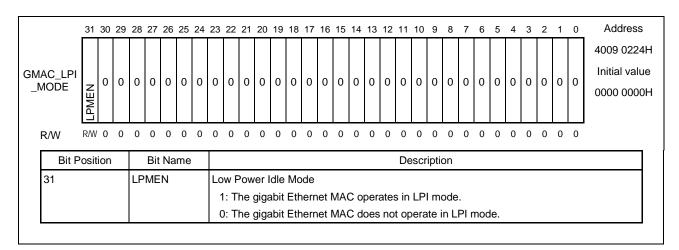

| 7.3      | Control Registers                                                                       | 7-4  |

| 7.3.1    | List of Registers                                                                       | 7-4  |

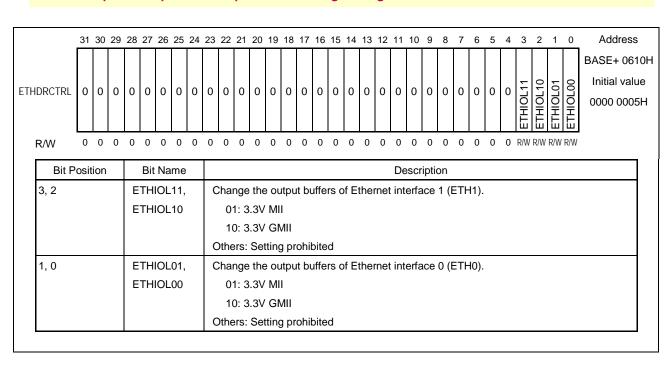

| 7.3.2    | Ethernet Interface Select Register                                                      | 7-6  |

| 7.3.3    | Ethernet Interface Mode Registers                                                       | 7-7  |

| 7.3.4    | Gigabit Ethernet MAC Control Register                                                   | 7-9  |

| 7.3.5    | Hardware Function Call Register                                                         | 7-26 |

| 7.4      | Functions                                                                               | 7-31 |

| 7.4.1    | Hardware Functions                                                                      | 7-31 |

| 7.4.2    | Interrupts                                                                              | 7-58 |

| 7.4.3    | Transmitting Ethernet Frames                                                            | 7-61 |

| 7.4.4    | Receiving Ethernet Frames                                                               | 7-71 |

| 7.4.5    | TCPIP Accelerator Function                                                              | 7-80 |

| 7.5      | Notes                                                                                   | 7-82 |

| 7.5.1    | Appending Padding to the MAC Header Section within the TX Frame                         | 7-82 |

| 7.5.2    | Erroneous Judgment about Checksum Validation at Specific Packet Reception               | 7-82 |

| 7.5.3    | Error of Rx Frame Information at RX FIFO Overflow                                       | 7-83 |

| 7.5.4    | Error of Rx Frame Information at Reception of the Frame more than 64 Bytes with Padding | 7-86 |

| 7.5.5    | Transmitting Data in Cut-Through Mode <r></r>                                           | 7-87 |

| 7.5.6    | Jumbo Frames <r></r>                                                                    | 7-87 |

| 8. | . Ether | net Switch                                             | 8-1   |

|----|---------|--------------------------------------------------------|-------|

|    | 8.1     | Overview                                               | 8-1   |

|    | 8.2     | Characteristics                                        | 8-2   |

|    | 8.3     | Control Registers                                      | 8-3   |

|    | 8.3.1   | List of Registers                                      | 8-3   |

|    | 8.3.2   | Operating Mode Setting Registers                       | 8-6   |

|    | 8.3.3   | Switch Configuration Registers                         | 8-10  |

|    | 8.3.4   | Learning Interface Registers                           | 8-30  |

|    | 8.3.5   | Mac Port Registers                                     | 8-32  |

|    | 8.3.6   | Timer Module Registers                                 | 8-41  |

|    | 8.3.7   | DLR Module Registers                                   | 8-51  |

|    | 8.4     | Function Details                                       | 8-63  |

|    | 8.4.1   | Switching Engine                                       | 8-63  |

|    | 8.4.2   | Hub Module Supporting Cut-Through                      | 8-73  |

|    | 8.4.3   | DLR Module                                             | 8-79  |

|    | 8.4.4   | IEEE 1588 Timer & Control Module                       | 8-85  |

|    | 8.4.5   | Management Port (Internal Port) Specific Frame Tagging | 8-93  |

|    | 8.5     | Overview of Control Software                           | 8-96  |

|    | 8.5.1   | Overview                                               | 8-96  |

|    | 8.5.2   | Switch Initialization                                  | 8-96  |

|    | 8.5.3   | Address Table Setting                                  | 8-101 |

| 9. | . Asyn  | chronous SRAM Memory Controller (ROM/SRAM)             | 9-1   |

|    | 9.1     | Overview                                               | 9-1   |

|    | 9.2     | Features                                               | 9-2   |

|    | 9.3     | Bus Control                                            | 9-3   |

|    | 9.3.1   | Overview of Registers                                  | 9-3   |

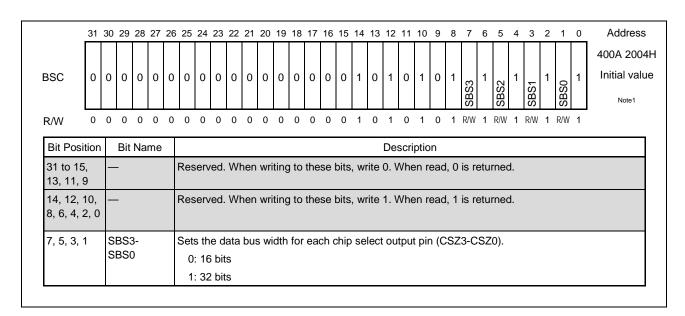

|    | 9.3.2   | Bus Size Control Register (BSC)                        | 9-4   |

|    | 9.3.3   | Static Memory Control Registers 0 to 3 (SMC0 to SMC3)  | 9-5   |

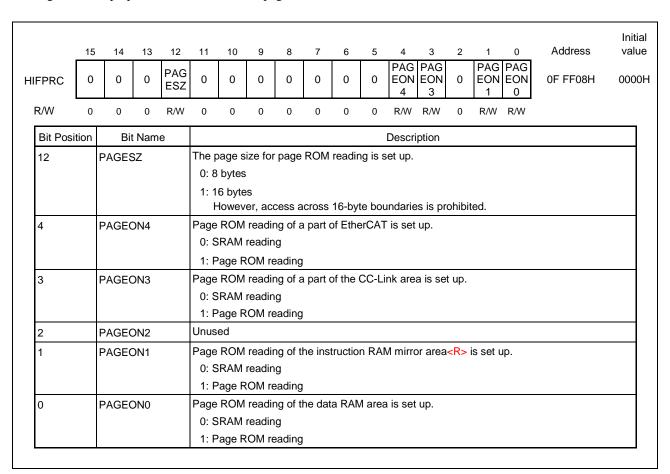

|    | 9.3.4   | Page ROM Control Register (PRC)                        | 9-8   |

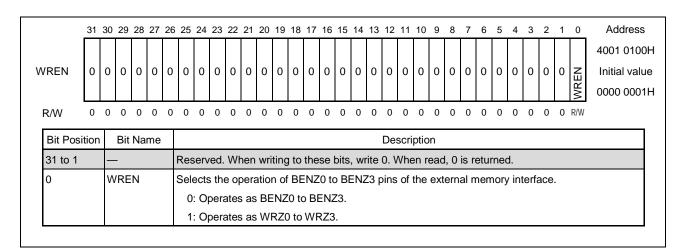

|    | 9.3.5   | Write Enable Switching Register (WREN)                 | 9-11  |

|    | 9.4     | Memory Connection Examples                             | 9-12  |

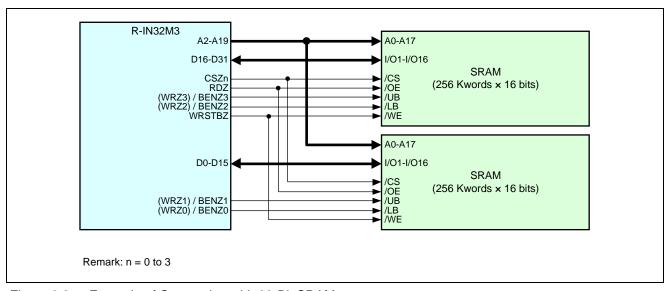

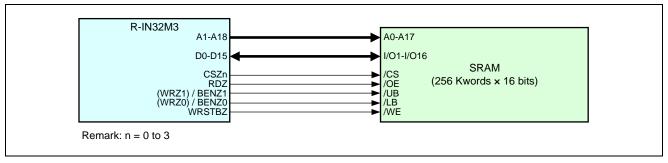

|    | 9.4.1   | SRAM Connection Example                                | 9-12  |

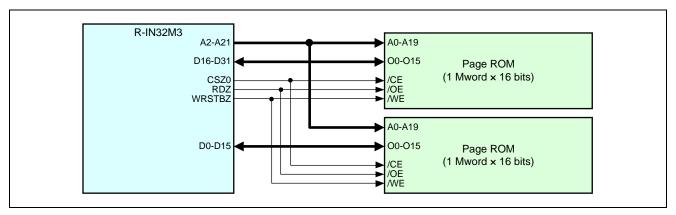

|    | 9.4.2   | Page ROM Connection Example                            |       |

|    | 9.5     | Procedure for Setting the Control Registers            | 9-14  |

|    | 9.6     | External Wait Function                                 | 9-15  |

|    | 9.7     | Memory Access Timing Examples                          | 9-16  |

| 10. Syn  | chronous Burst Access Memory Controller                                                | 10-1   |

|----------|----------------------------------------------------------------------------------------|--------|

| 10.1     | Features                                                                               | 10-1   |

| 10.2     | Control Registers                                                                      | 10-3   |

| 10.2     | .1 Wait Signals Selection Register (WAITZSEL)                                          | 10-4   |

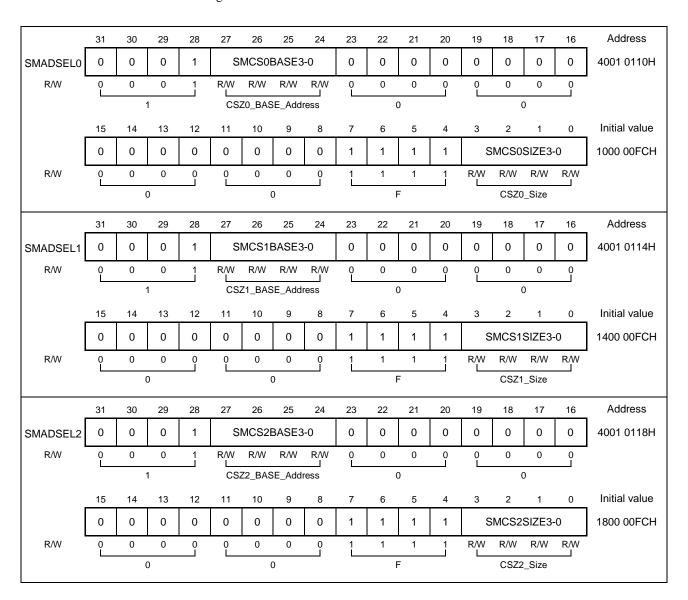

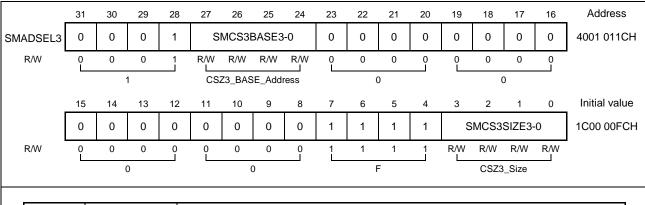

| 10.2     | .2 Synchronous Burst Access Memory Controller Area Select Registers (SMADSEL0 to SMADS | EL3)   |

|          |                                                                                        | 10-6   |

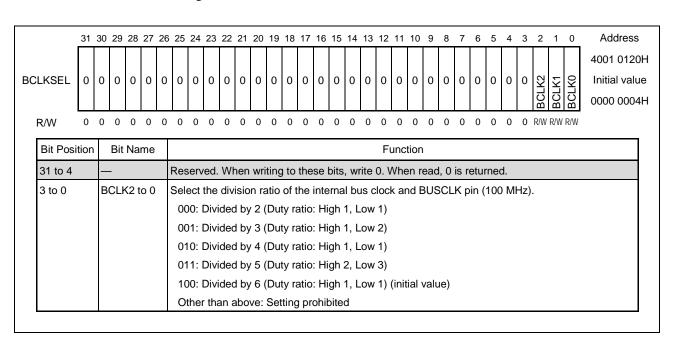

| 10.2     | .3 Bus Clock Division Setting Register (BCLKSEL)                                       | 10-8   |

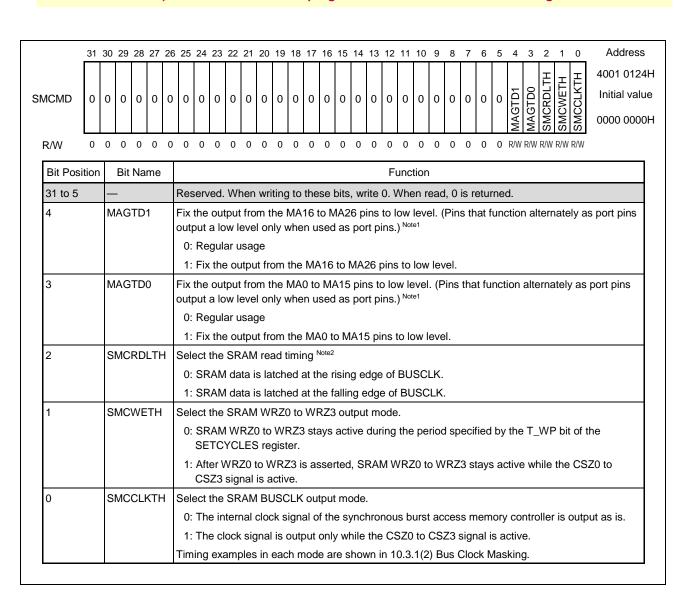

| 10.2     | .4 Synchronous Burst Access Memory Controller Operation Mode Setting Register (SMCMD)  | 10-9   |

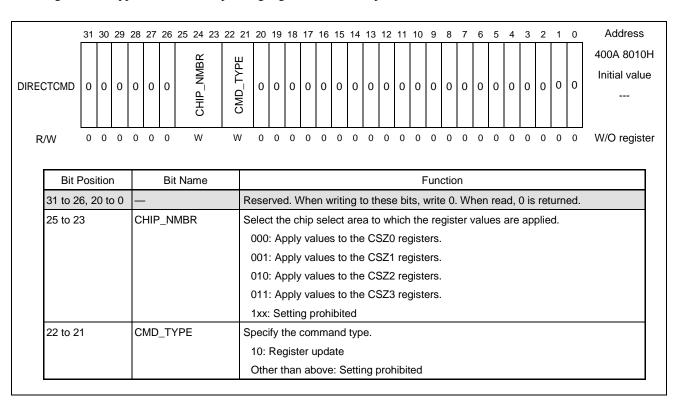

| 10.2     | .5 Synchronous Burst Access Memory Controller Direct Command Register (DIRECTCMD)      | 10-10  |

| 10.2     | .6 Synchronous Burst Access Memory Controller Cycle Setting Register (SETCYCLES)       | 10-11  |

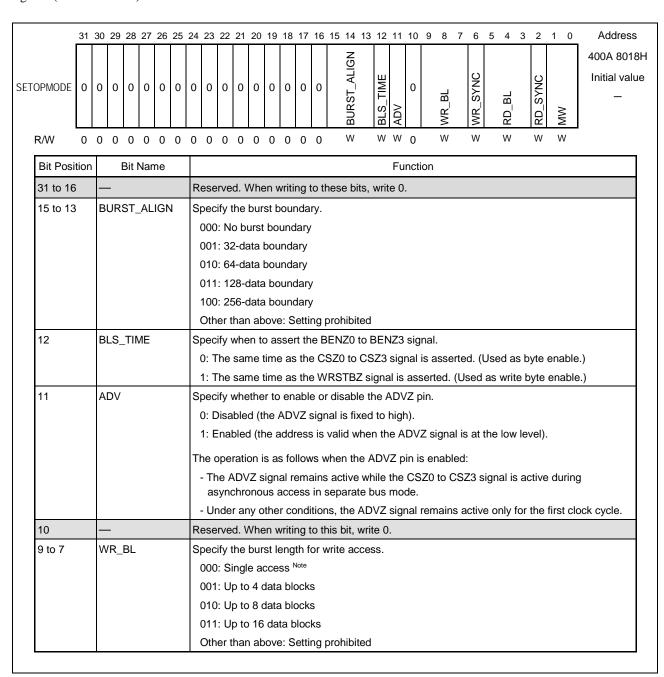

| 10.2     | .7 Synchronous Burst Access Memory Controller Mode Setting Register (SETOPMODE)        | 10-13  |

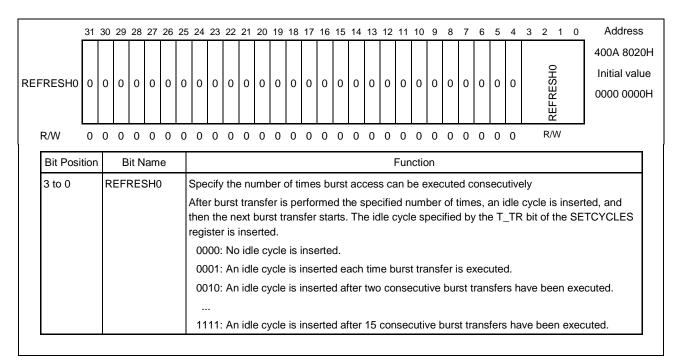

| 10.2     | .8 Synchronous Burst Access Memory Controller Refresh Setting Register (REFRESH0)      | 10-15  |

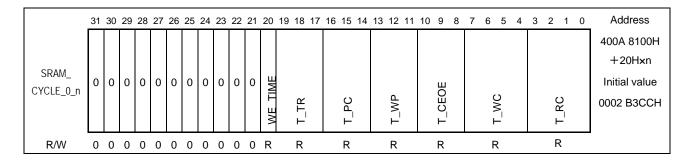

| 10.2     | .9 Synchronous Burst Access Memory Controller CSZn Cycle Setting Registers (SRAM_CYCLE | ESO_n) |

|          |                                                                                        | 10-15  |

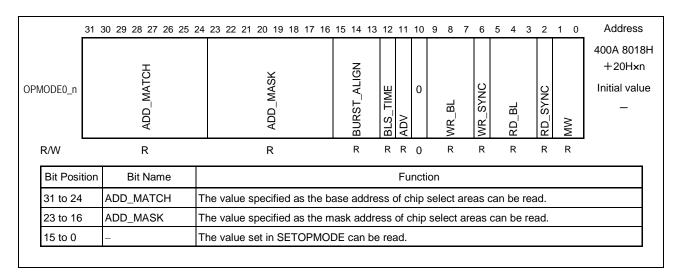

| 10.2     | .10 Synchronous Burst Access Memory Controller CSZn Mode Registers (OPMODE0_n)         | 10-16  |

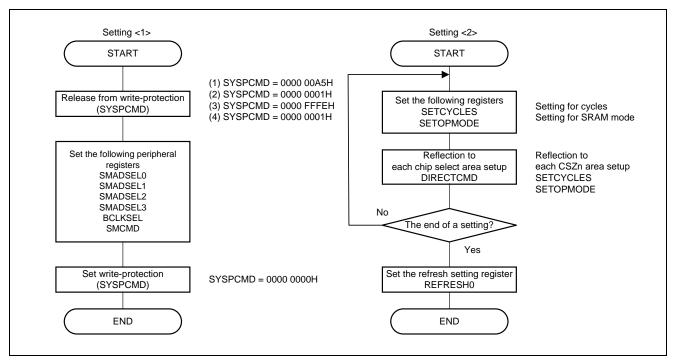

| 10.2     | .11 Register Setup Procedure                                                           | 10-17  |

| 10.3     | Function Details                                                                       | 10-18  |

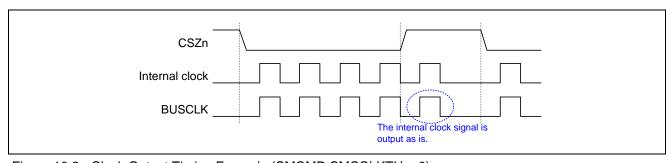

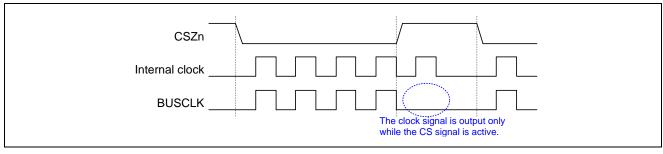

| 10.3     | .1 Bus Clock Control                                                                   | 10-18  |

| 10.3     | .2 Address Output                                                                      | 10-19  |

| 10.3     | .3 Address/Data Multiplexing Feature                                                   | 10-19  |

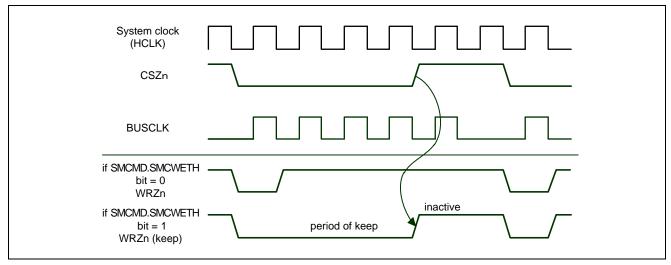

| 10.3     | .4 Write Enable Signal (WRZn) Cycle Extension                                          | 10-20  |

| 10.3     | .5 Controlling the Data Read Timing                                                    | 10-21  |

| 10.3     | .6 Wait Signals Control                                                                | 10-22  |

| 10.3     | .7 Specify the Operating Mode of the Synchronous Burst Access Memory Controller        | 10-25  |

| 10.3     | .8 Switching External Memory Area Mapping                                              | 10-26  |

| 10.4     | Memory Access Timing Example                                                           | 10-27  |

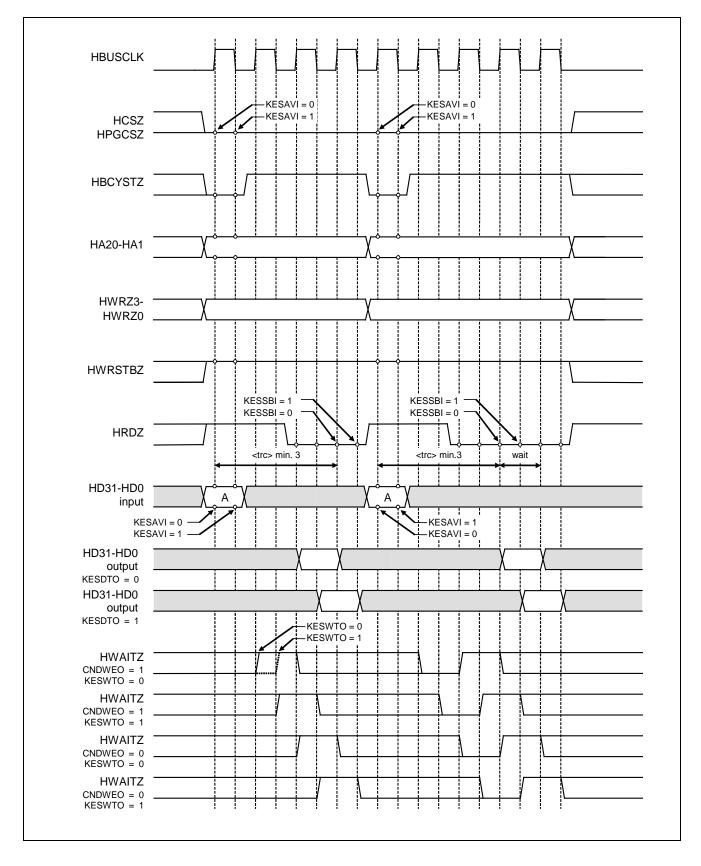

| 10.4     | .1 Asynchronous Access Timing                                                          | 10-28  |

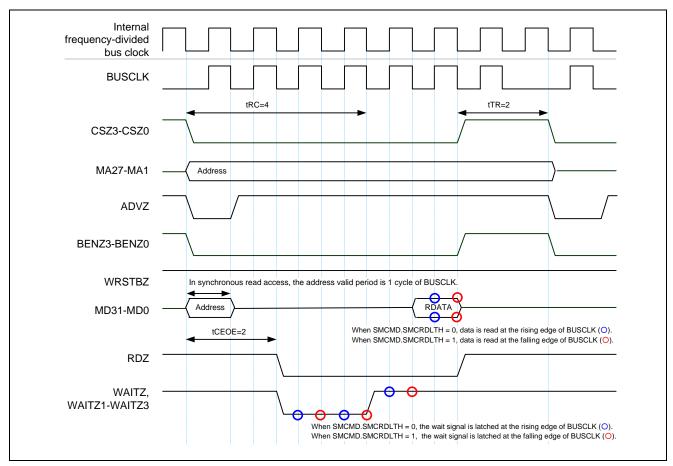

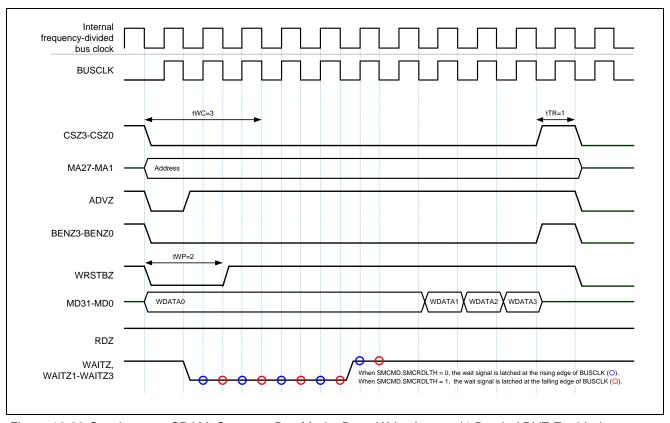

| 10.4     | .2 Synchronous Access Timing                                                           | 10-36  |

| 10.4     | .3 Wait Timing                                                                         | 10-43  |

| 11. Exte | ernal MCU Interface                                                                    | 11-1   |

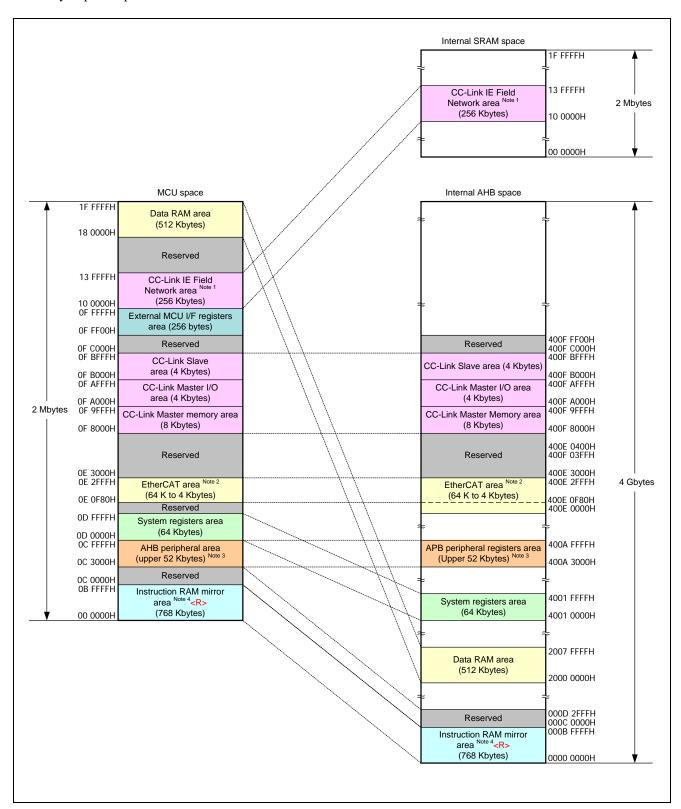

| 11.1     | Memory Map                                                                             | 11-3   |

| 11.2     | Synchronous/Asynchronous SRAM Interface Mode                                           | 11-5   |

| 11.2     | .1 Functional Overview                                                                 | 11-5   |

| 11.2     | .2 Operation                                                                           | 11-6   |

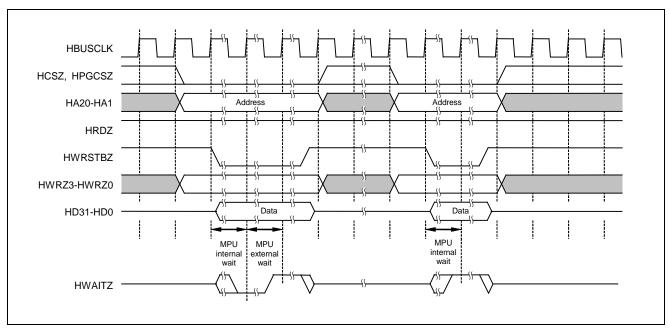

| 11.2     | .3 Basic Operation Timing of the External MCU Interface                                | 11-9   |

| 11.2     | .4 Timing Adjustment of the External MCU Interface                                     | 11-12  |

| 11.2     | .5 Control Registers                                                                   | 11-16  |

| 11.2     | 6 Precautions                                                                          | 11-26  |

| 11.3 Sy             | nchronous SRAM Type Transfer Mode                             | 11-27 |

|---------------------|---------------------------------------------------------------|-------|

| 11.3.1              | Functional Overview.                                          | 11-27 |

| 11.3.2              | Selection of Operational Mode                                 | 11-27 |

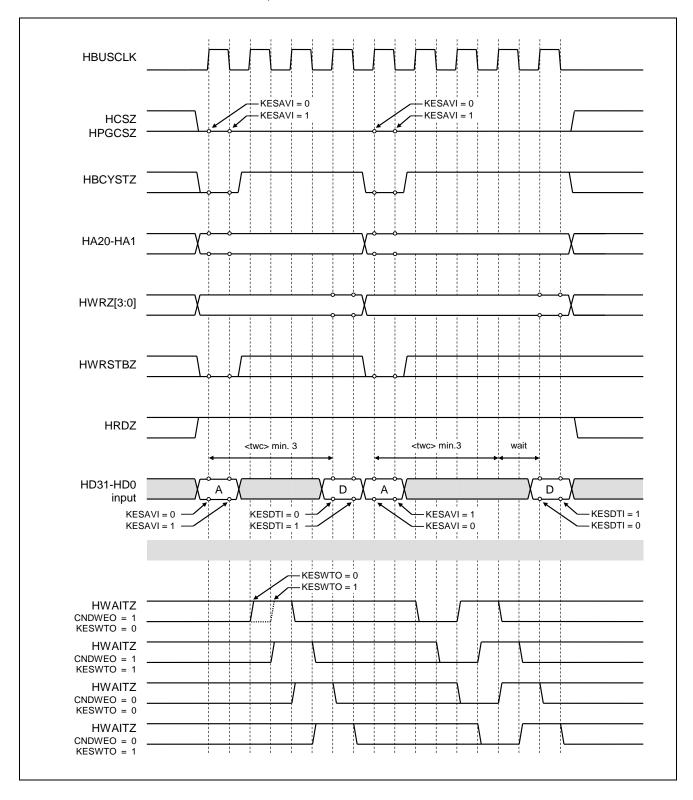

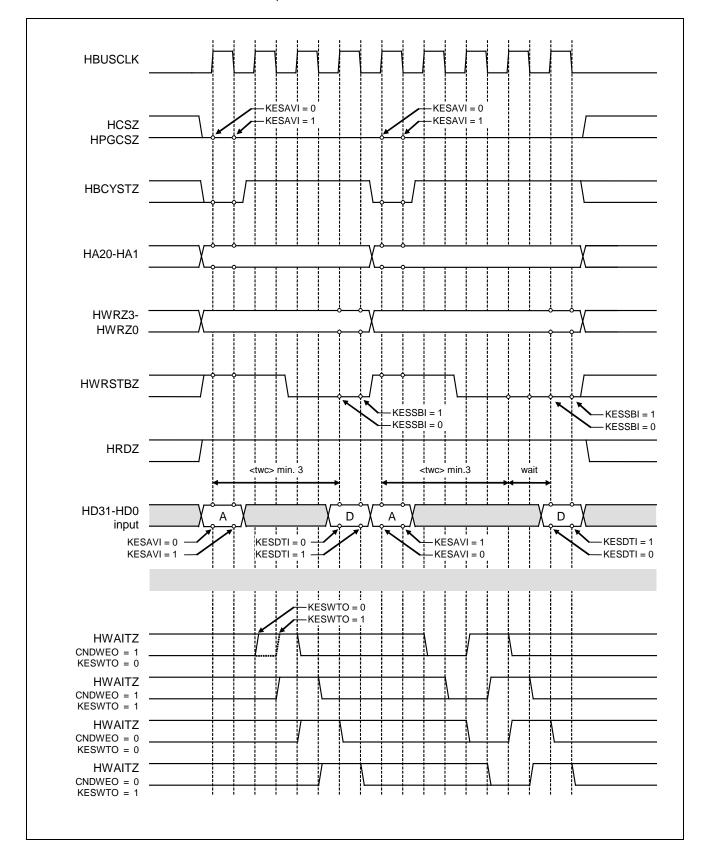

| 11.3.3              | Write Status Mode and Write Strobe Mode                       | 11-28 |

| 11.3.4              | Control Registers                                             | 11-28 |

| 11.3.5              | Basic Operation Timing in Synchronous SRAM Type Transfer Mode | 11-31 |

| 11.3.6              | Precautions                                                   | 11-34 |

| l2. Serial F        | lash ROM Memory Controller                                    | 12-1  |

| 12.1 Fe             | eatures                                                       | 12-1  |

|                     | ontrol Registers                                              |       |

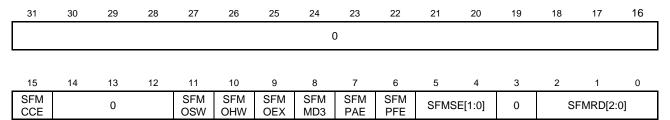

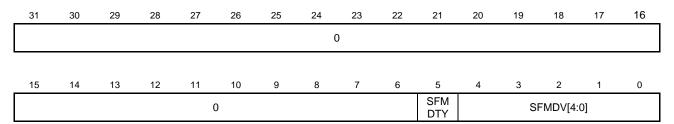

| 12.2.1              | Transfer Mode Control Register (SFMSMD)                       | 12-3  |

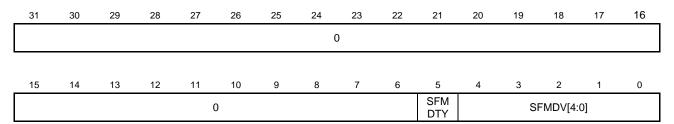

| 12.2.2              | Chip Selection Control Register (SFMSSC)                      | 12-5  |

| 12.2.3              | Clock Control Register (SFMSKC)                               | 12-6  |

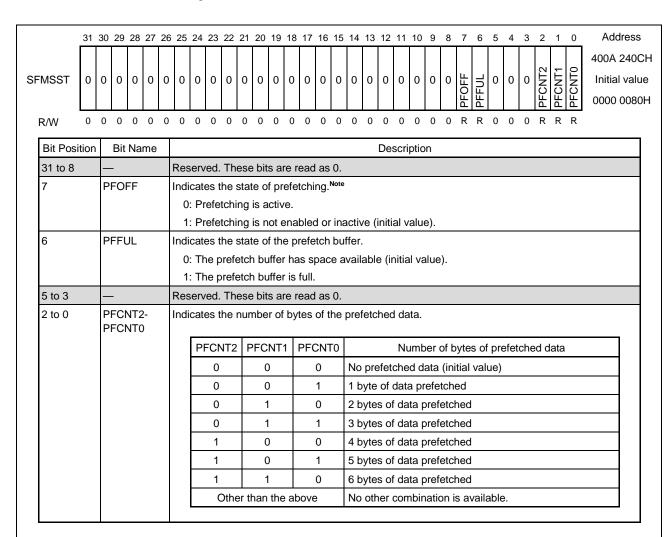

| 12.2.4              | Status Register (SFMSST)                                      | 12-8  |

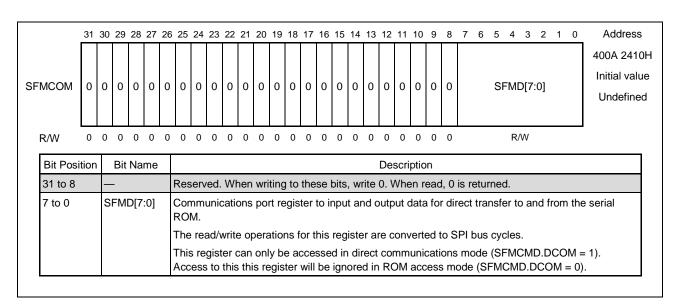

| 12.2.5              | Communications Port Register (SFMCOM)                         | 12-9  |

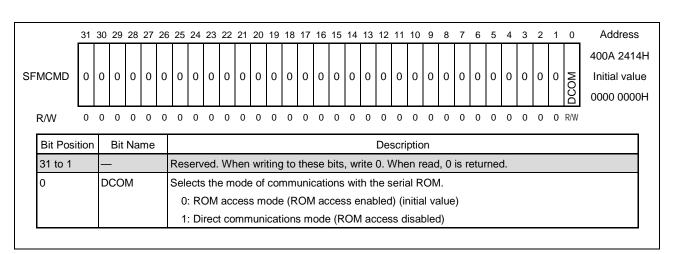

| 12.2.6              | Communications Mode Control Register (SFMCMD)                 | 12-10 |

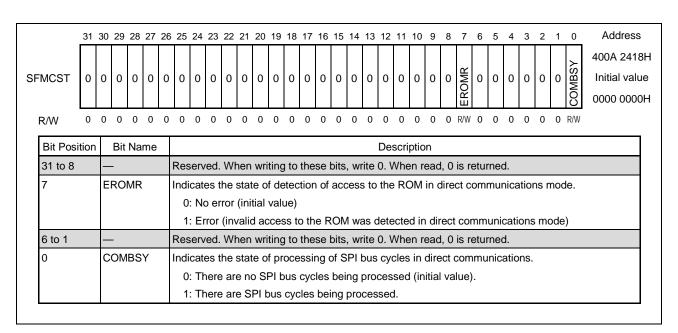

| 12.2.7              | Communications Status Register (SFMCST)                       | 12-11 |

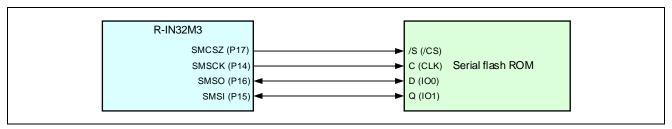

| 12.3 Co             | onnection with Serial Flash ROM                               | 12-12 |

| 12.4 O <sub>j</sub> | peration                                                      | 12-13 |

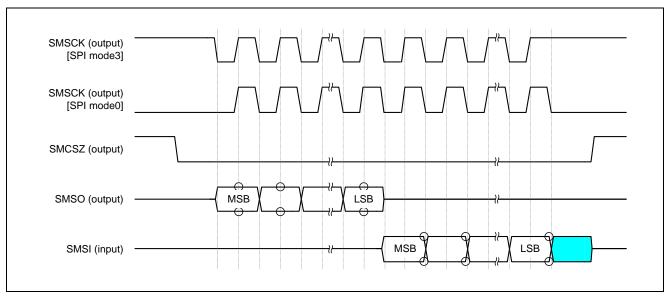

| 12.4.1              | SPI Bus Operation                                             | 12-13 |

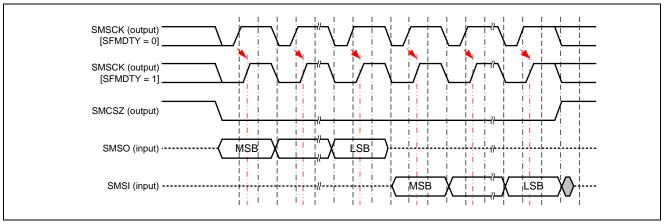

| 12.4.2              | SPI Bus Timing Adjustment                                     | 12-14 |

| 12.4.3              | SPI Instruction Set for Use in Access to the Serial Flash ROM | 12-18 |

| 12.4.4              | Modifying the SPI Bus Cycle                                   | 12-21 |

| 12.4.5              | Automatic Release from the Deep Power-Down State              | 12-24 |

| 12.4.6              | Direct Communications                                         | 12-25 |

| 12.5 Ex             | cample of Configuration                                       | 12-26 |

| 12.5.1              | Standard Reading                                              | 12-27 |

| 12.5.2              | Fast Read Dual I/O                                            | 12-31 |

| 3. DMA C            | ontrollers                                                    | 13-1  |

| 13.1 Fe             | eatures                                                       | 13-2  |

| 13.1.1              | Overview                                                      |       |

|                     | elation between DMA Units/Channels and DMA Triggers           |       |

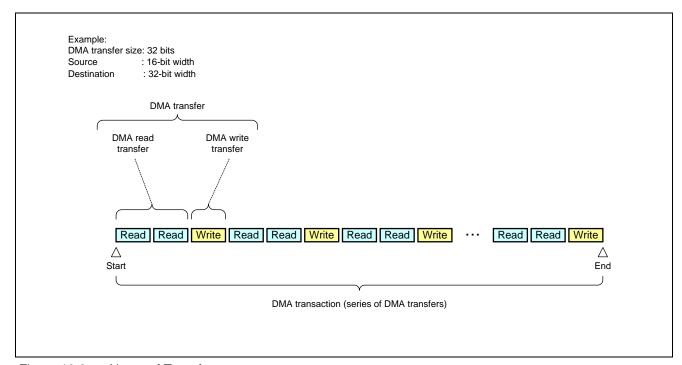

|                     | erms and Definition                                           |       |

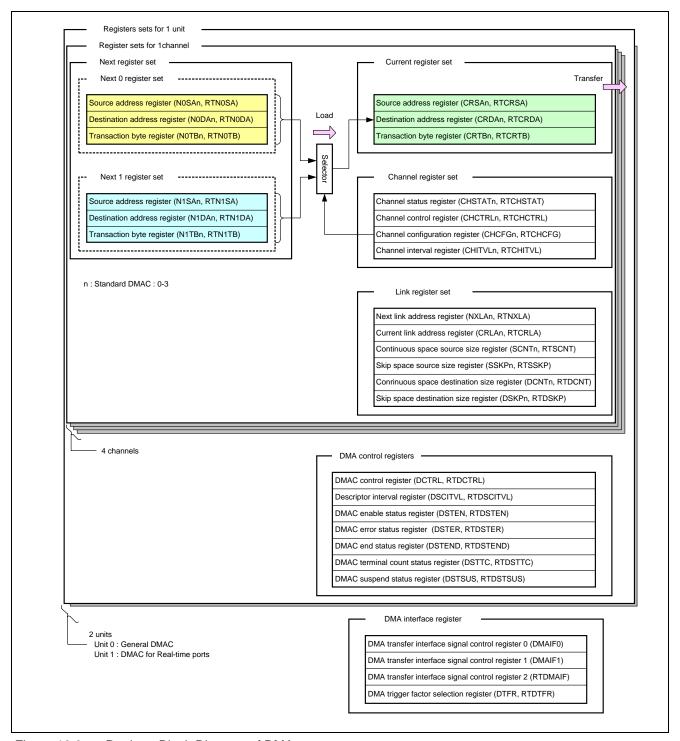

|                     | MA Controller Registers                                       |       |

| 13.4.1              | Register Configuration                                        |       |

| 13.4.2              | Control Register Outline                                      |       |

| 13.4.3              | General DMA Controller Register Set                           |       |

|                     | 0                                                             |       |

| 13.4.4       | Register Set of DMA Controller for Real-Time Ports                                  | 13-47   |

|--------------|-------------------------------------------------------------------------------------|---------|

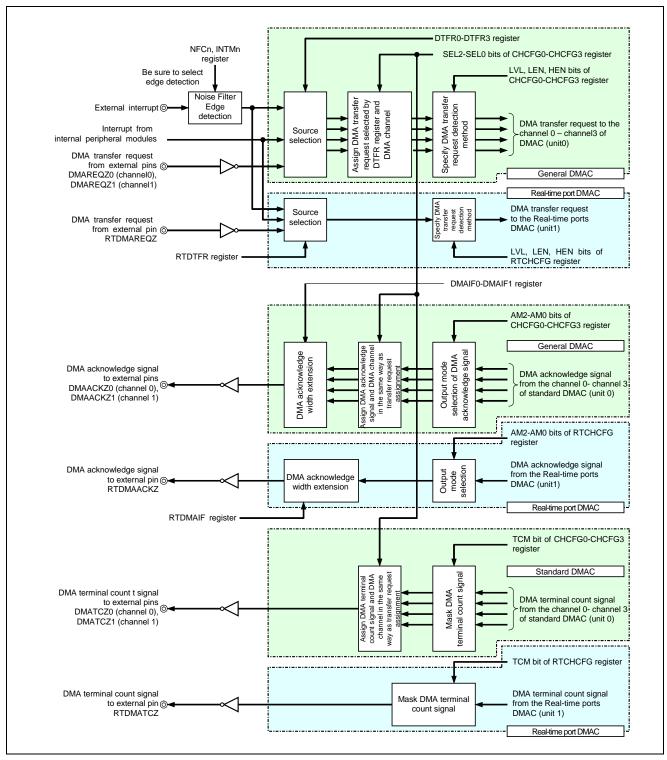

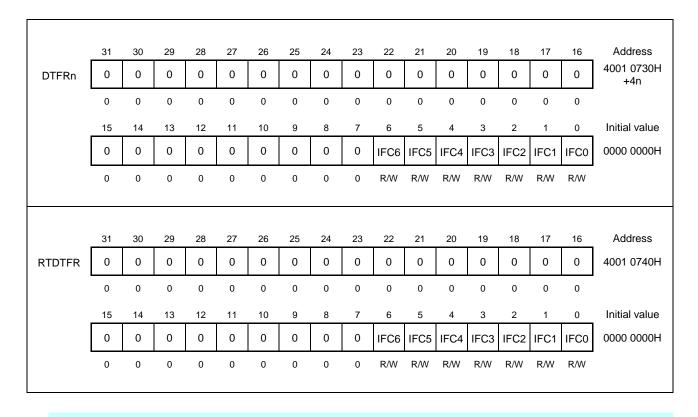

| 13.4.5       | DMA Transfer Interface Signal Control Registers (DMAIFC0, DMAIFC1, RTDMAIFC         | ) 13-78 |

| 13.4.6       | DMA Trigger Source Selection Registers (DTFRn, RTDTFR)                              | 13-84   |

| 13.5 DM      | IA Interface Pins                                                                   | 13-88   |

| 13.5.1       | BUSCLK Synchronization                                                              | 13-88   |

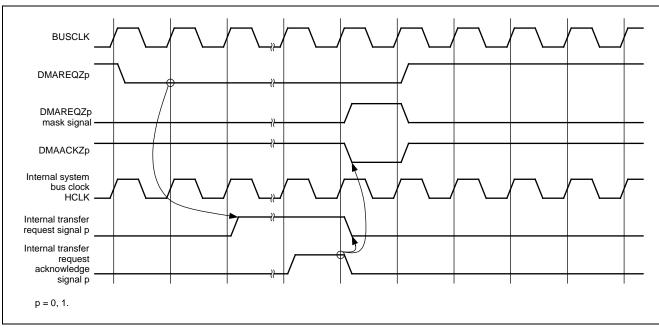

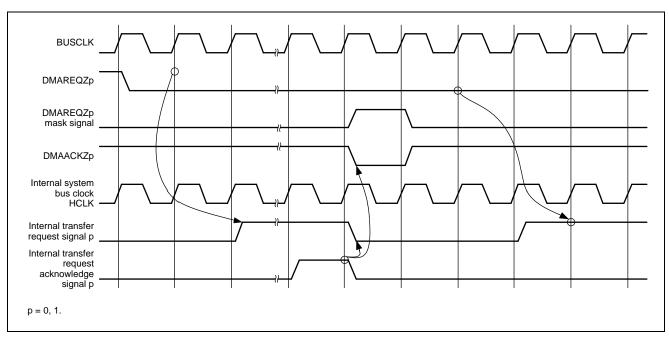

| 13.5.2       | Transfer Request and Acknowledge                                                    | 13-88   |

| 13.6 Inte    | errupt Output                                                                       | 13-89   |

| 13.7 DM      | IAC Operation Setting                                                               | 13-90   |

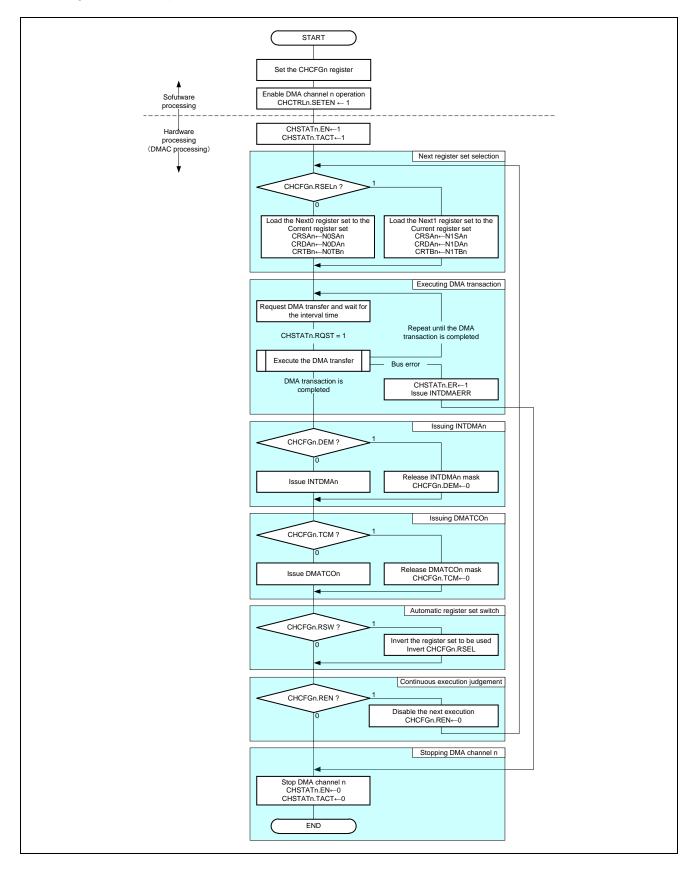

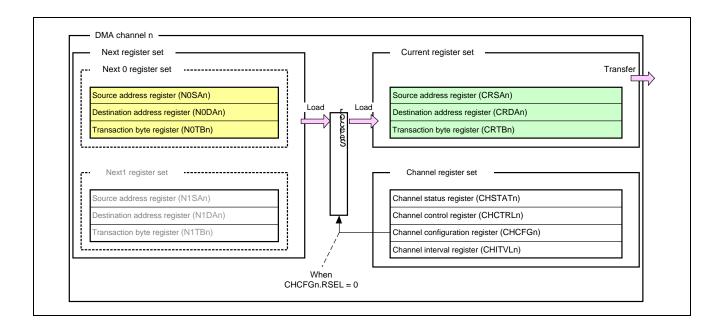

| 13.7.1       | Register Mode and Link Mode Selection                                               | 13-90   |

| 13.7.2       | Register Mode                                                                       | 13-91   |

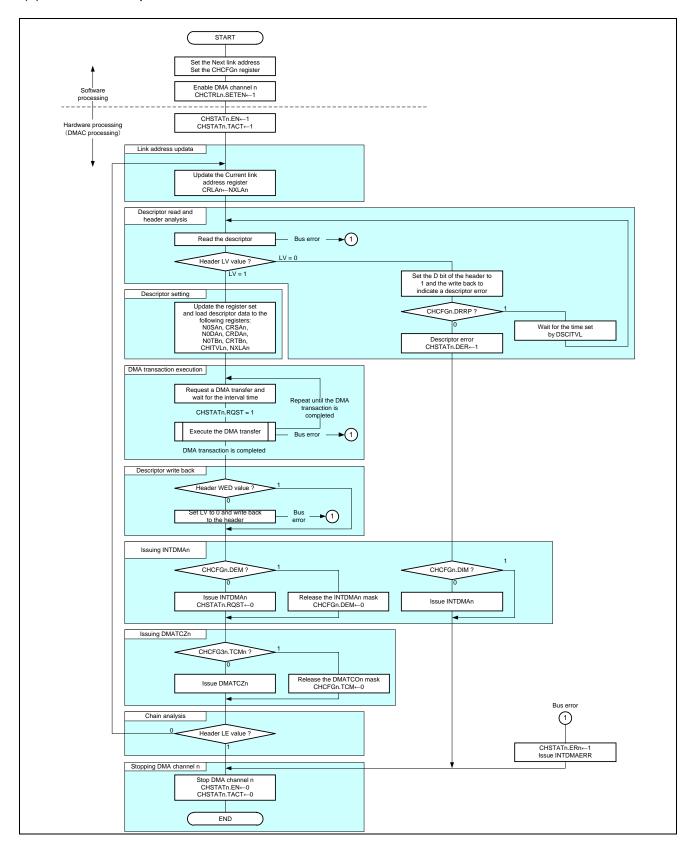

| 13.7.3       | Link Mode                                                                           | 13-98   |

| 13.7.4       | Write-Only Mode                                                                     | 13-110  |

| 13.8 DM      | IAC Operation                                                                       | 13-111  |

| 13.8.1       | Transfer Mode                                                                       | 13-111  |

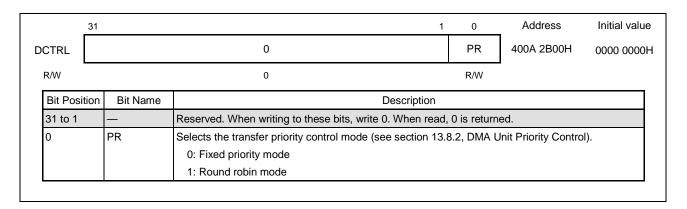

| 13.8.2       | DMA Unit Priority Control                                                           | 13-114  |

| 13.8.3       | DMA Transfer Request                                                                | 13-117  |

| 13.8.4       | DMA Acknowledge Output                                                              | 13-120  |

| 13.8.5       | DMA Transfer Completion Interrupt                                                   | 13-125  |

| 13.8.6       | DMA Terminal Count Output                                                           | 13-127  |

| 13.8.7       | Forced Dumping                                                                      | 13-129  |

| 13.8.8       | DMA Error Interrupt                                                                 | 13-129  |

| 13.8.9       | Interval Counting                                                                   | 13-129  |

| 13.8.10      | Differences in Operation by Transfer Size                                           | 13-130  |

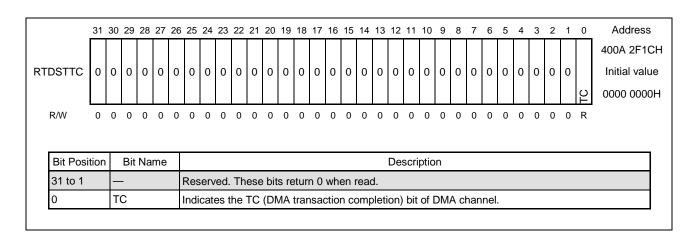

| 13.8.11      | Transfer Status                                                                     | 13-133  |

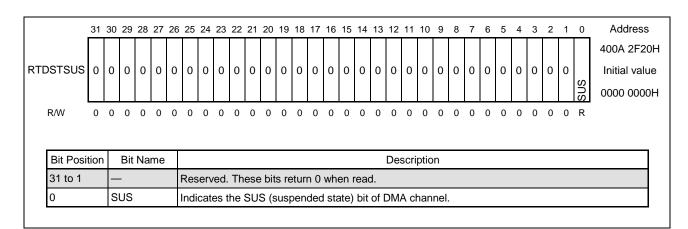

| 13.8.12      | Suspension                                                                          | 13-133  |

| 13.8.13      | Suspending Transfer                                                                 | 13-134  |

| 13.9 DM      | IA Transfer Setting Examples                                                        | 13-135  |

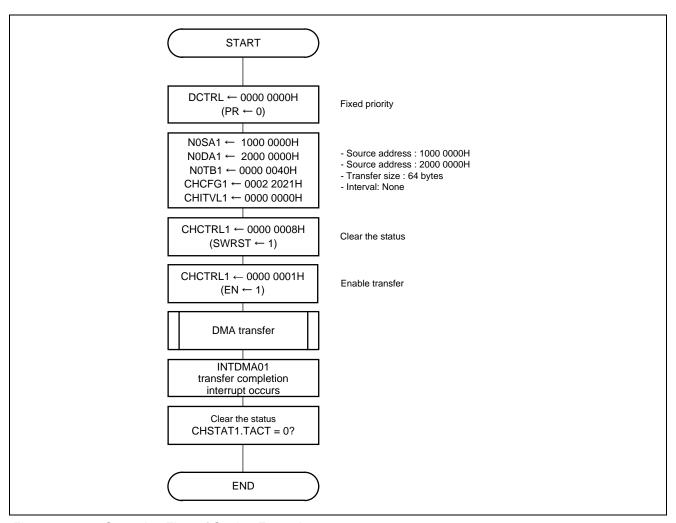

| 13.9.1       | Setting Example 1 (Register Mode, Single Transfer Mode, and Hardware Trigger)       | 13-135  |

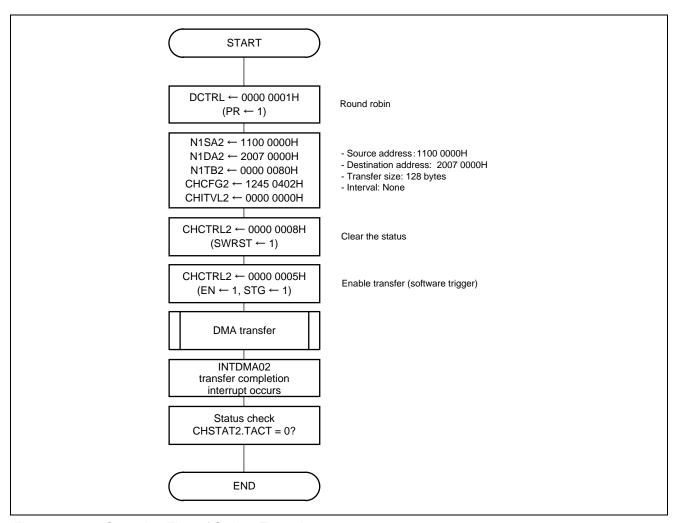

| 13.9.2       | Setting Example 2 (Register Mode, Block Transfer Mode, and Software Trigger)        | 13-138  |

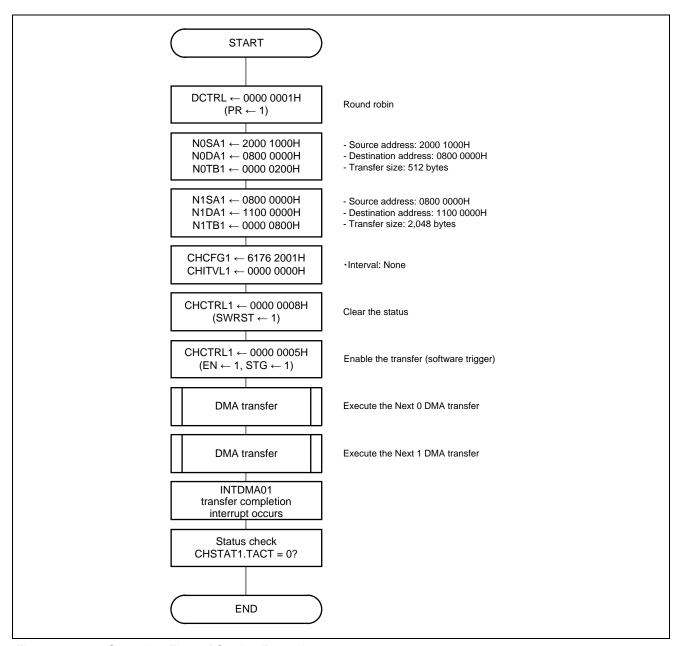

| 13.9.3       | Setting Example 3 (Register Mode: Continuous Execution, Block Transfer Mode, and So | -       |

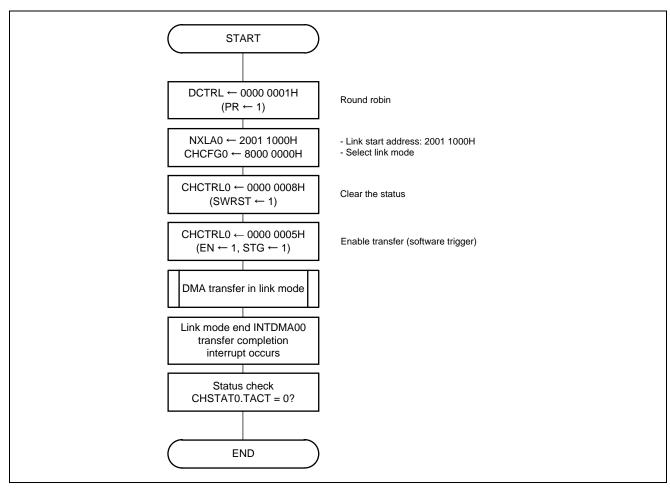

| 13.9.4       | Setting Example 4 (Link Mode, Block Transfer Mode, and Software Trigger)            |         |

| 13.10 No     | tes                                                                                 | 13-147  |

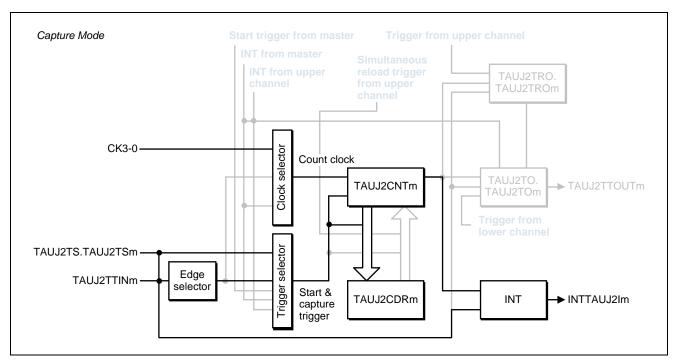

| 14. Timer Ar | ray Unit (TAUJ2)                                                                    | 14-1    |

| 14.1 Fea     | tures of TAUJ2                                                                      | 14-1    |

| 14.1.1       | Functional List of Timer Operations                                                 | 14-3    |

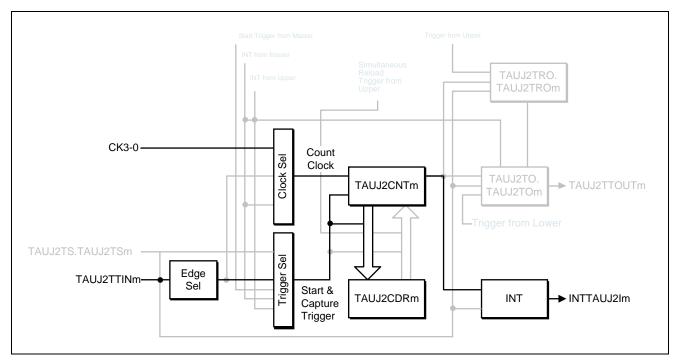

| 14.2 Fur     | actional Overview                                                                   | 14-4    |

| 14.2.1       | Terms                                                                               | 14-4    |

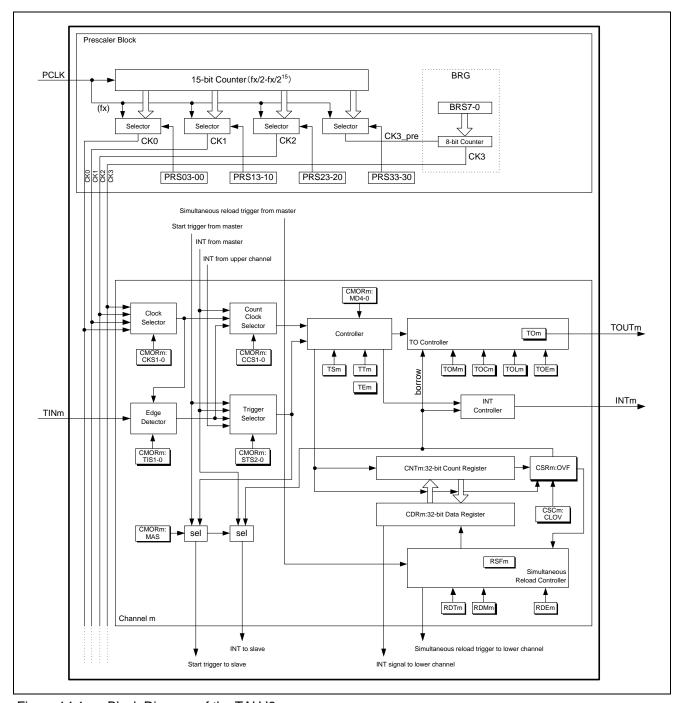

| 14.2.2       | Description of Blocks                                         | 14-6  |

|--------------|---------------------------------------------------------------|-------|

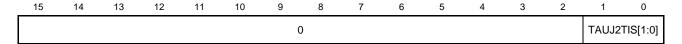

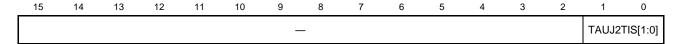

| 14.3 Reg     | isters                                                        | 14-7  |

| 14.3.1       | TAUJ2 Registers Overview                                      | 14-7  |

| 14.3.2       | TAUJ2 Prescaler Registers Details                             | 14-9  |

| 14.3.3       | TAUJ2 Control Registers Details                               | 14-14 |

| 14.3.4       | TAUJ2 Simultaneous Reload Registers Details                   | 14-24 |

| 14.3.5       | TAUJ2 Output Registers Details                                | 14-26 |

| 14.4 Gen     | neral Operating Procedure                                     | 14-30 |

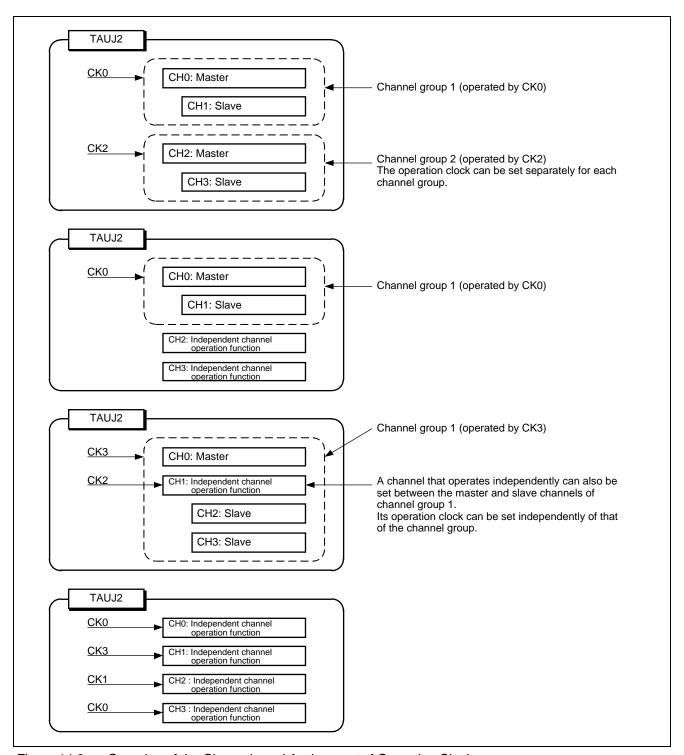

| 14.5 Ove     | erview of Synchronous Channel Operation                       | 14-31 |

| 14.5.1       | Basic Rules of Synchronous Channel Operation                  | 14-31 |

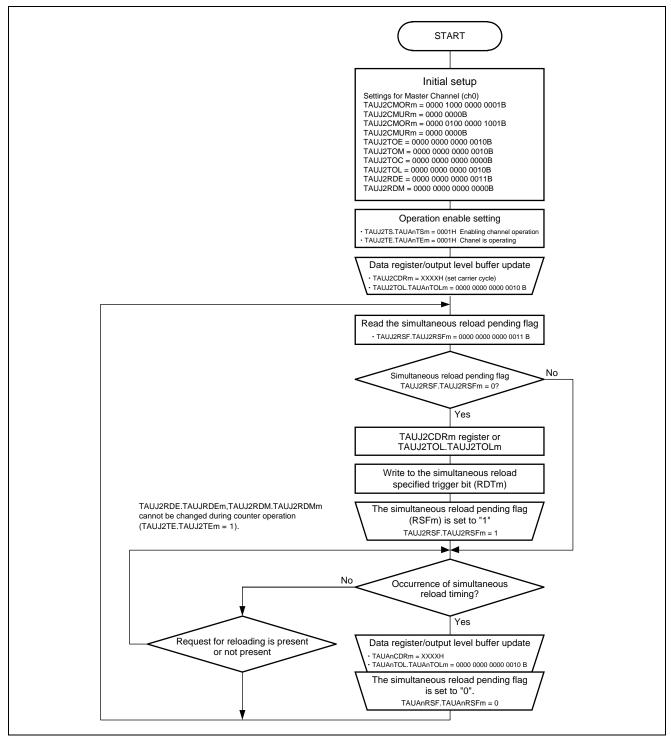

| 14.6 Sim     | ultaneous Reloading                                           | 14-33 |

| 14.6.1       | Outline of Operation                                          | 14-33 |

| 14.6.2       | How to Control Simultaneous Reloading (in Case of PWM Output) | 14-34 |

| 14.6.3       | Other General Rules of Simultaneous Reloading                 | 14-35 |

| 14.7 Inde    | ependent Channel Operation                                    | 14-36 |

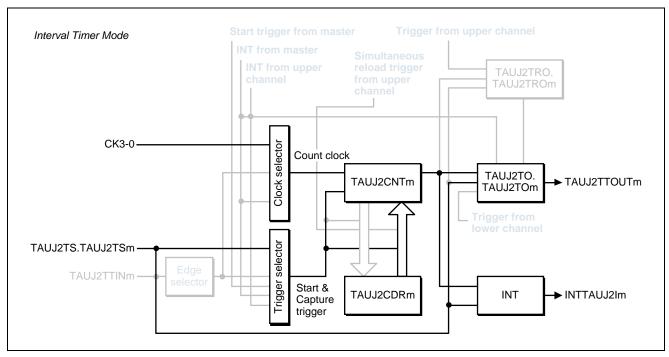

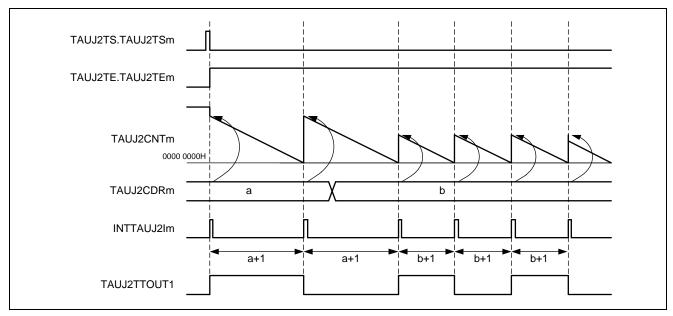

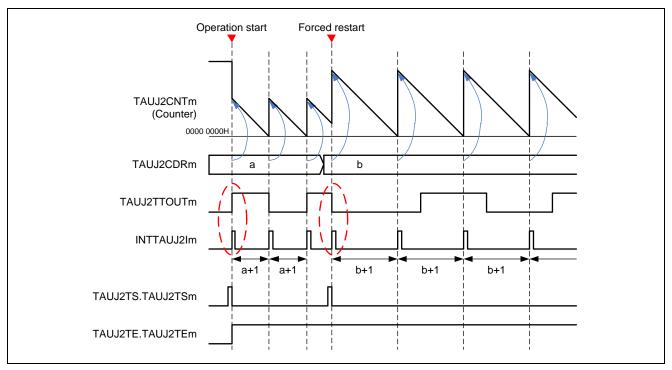

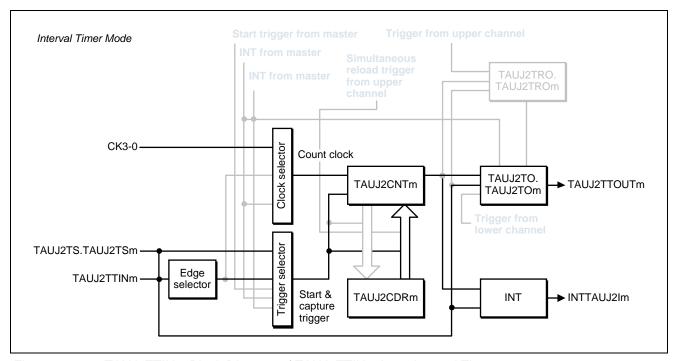

| 14.7.1       | Interval Timer                                                | 14-37 |

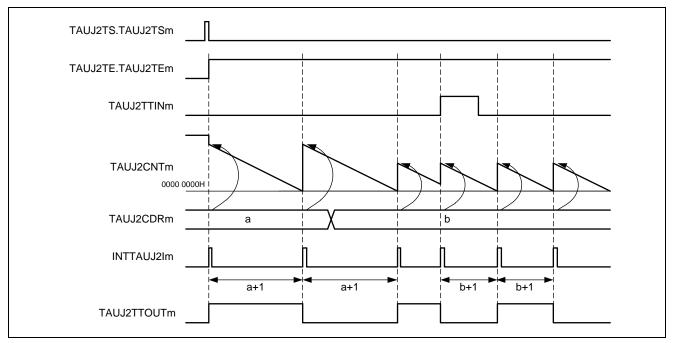

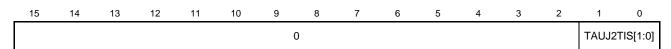

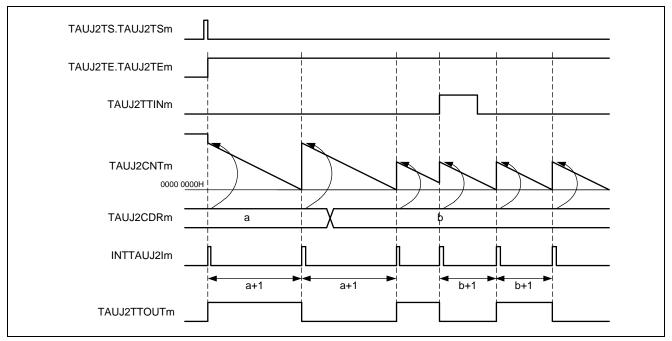

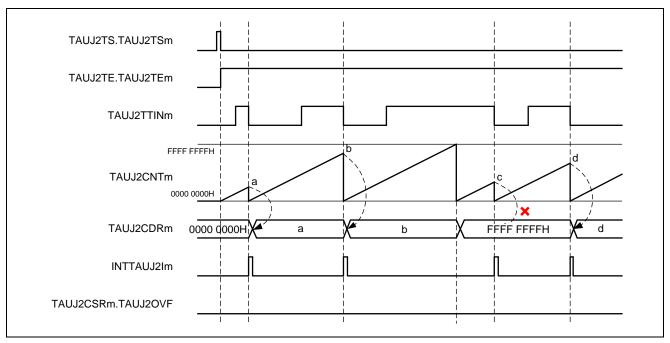

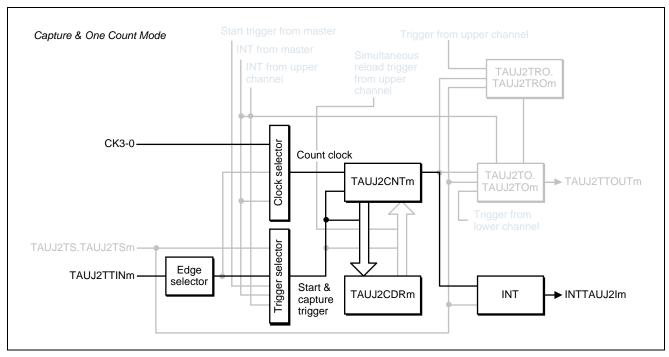

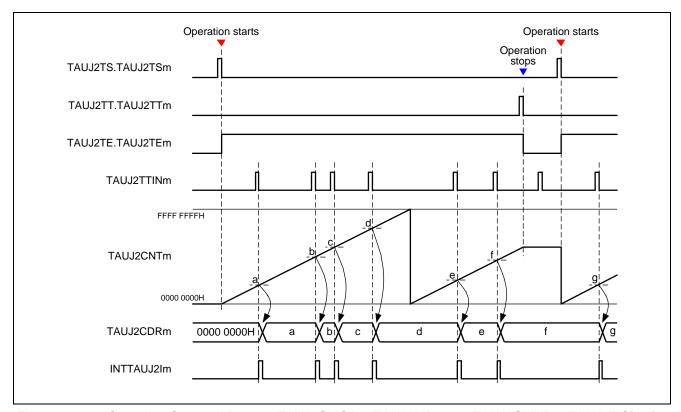

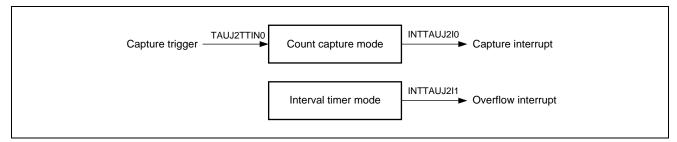

| 14.7.2       | TAUJ2TTINm Input Interval Timer                               | 14-46 |

| 14.7.3       | Delay Counting                                                | 14-52 |

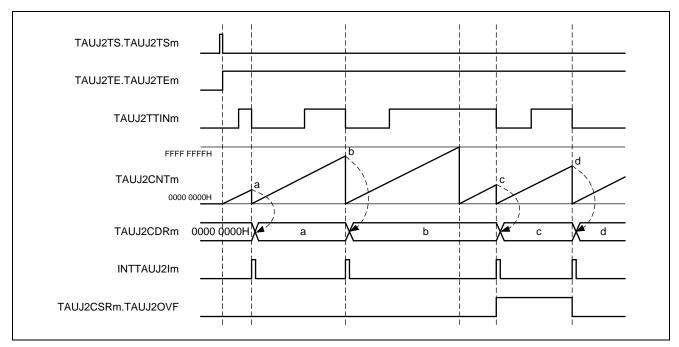

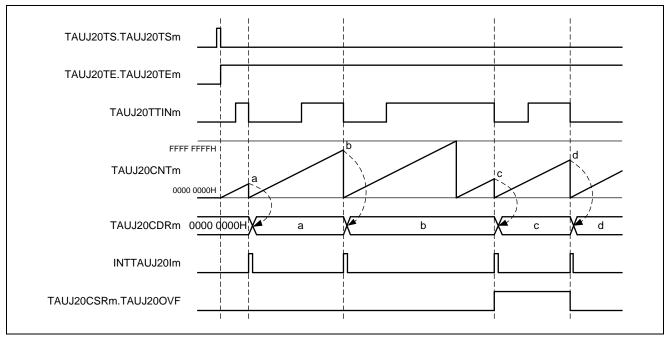

| 14.7.4       | TAUJ2TTINm Input Pulse Interval Measurement                   | 14-57 |

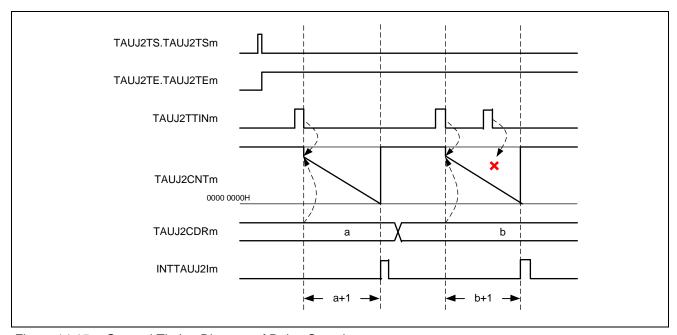

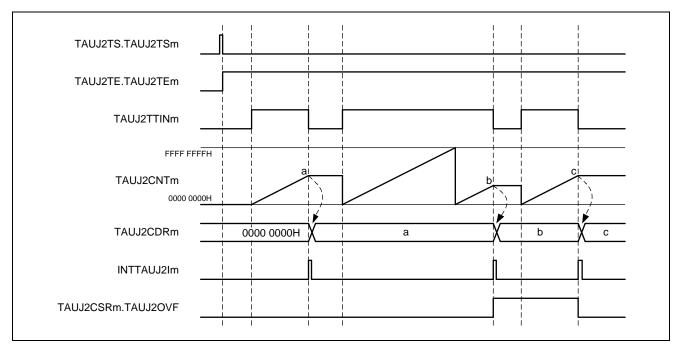

| 14.7.5       | TAUJ2TTINm Input Signal Width Measurement                     | 14-64 |

| 14.7.6       | External Event Counting                                       | 14-76 |

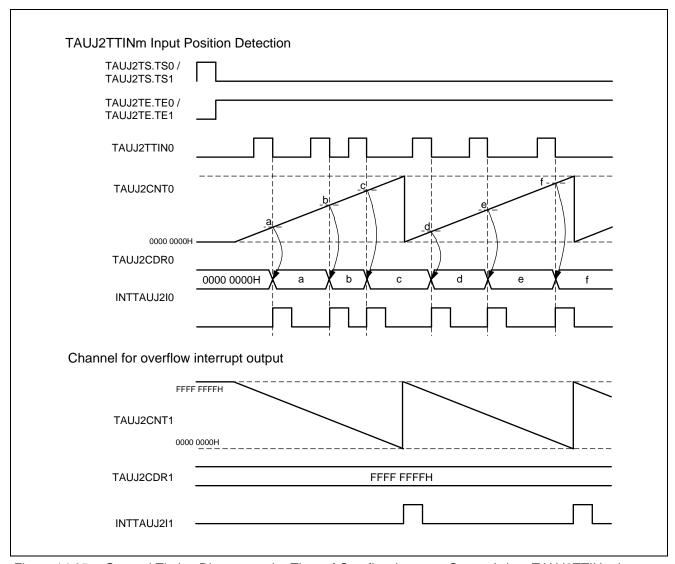

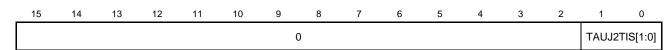

| 14.7.7       | TAUJ2TTINm Input Position Detection                           | 14-82 |

| 14.8 Syn     | chronous Channel Operation                                    | 14-93 |

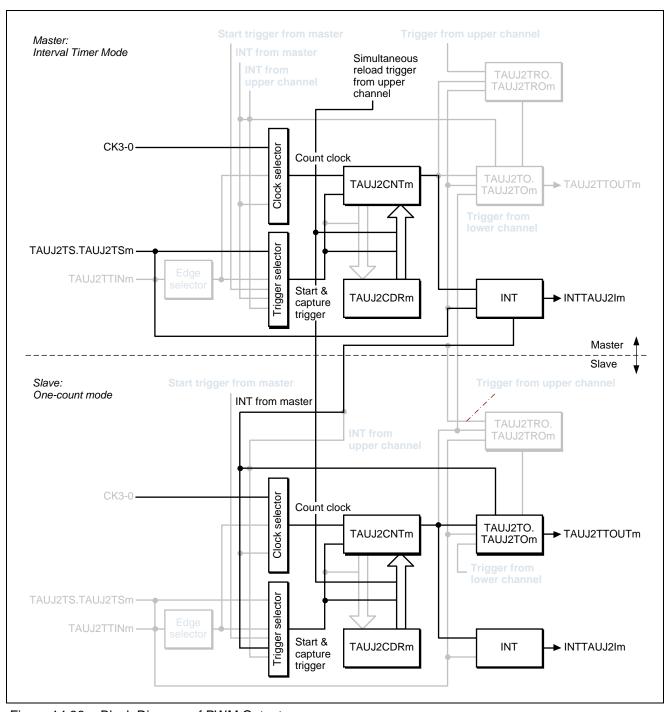

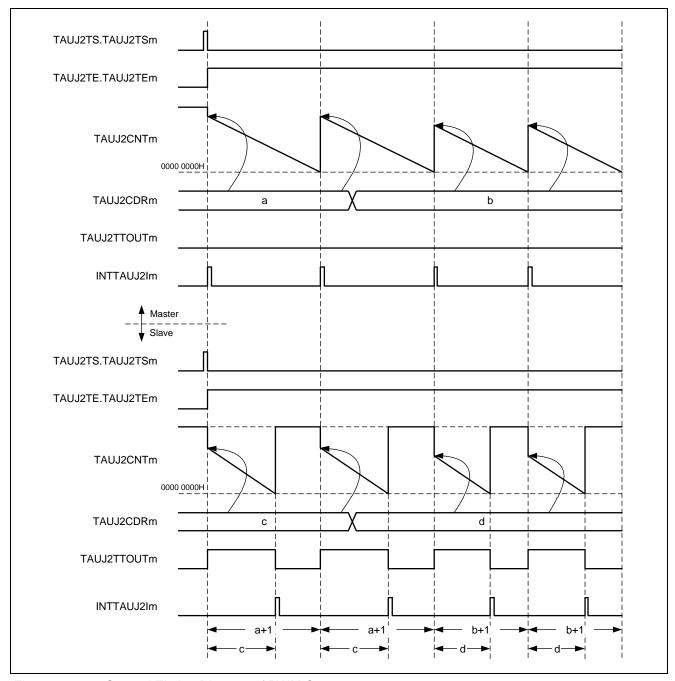

| 14.8.1       | PWM Output                                                    | 14-93 |

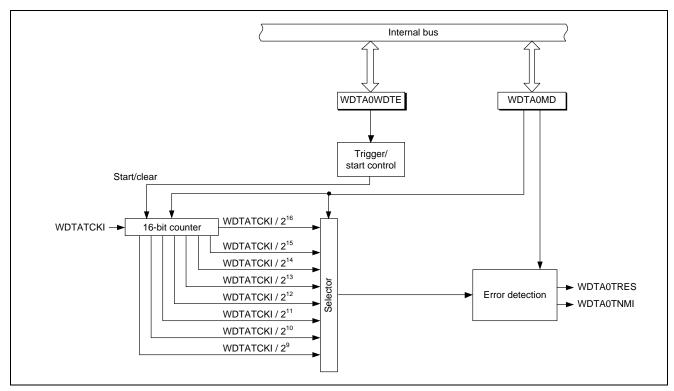

| 15. Window \ | Watchdog Timer A (WDTA)                                       | 15-1  |

| 15.1 Fear    | tures of WDTA                                                 | 15-1  |

| 15.2 Fun     | ctional Overview                                              | 15-2  |

| 15.3 Reg     | isters                                                        | 15-3  |

| 15.3.1       | Overview of WDTA Registers                                    | 15-3  |

| 15.3.2       | Details of WDTA Registers                                     | 15-3  |

| 15.4 Fun     | ctional Description                                           | 15-6  |

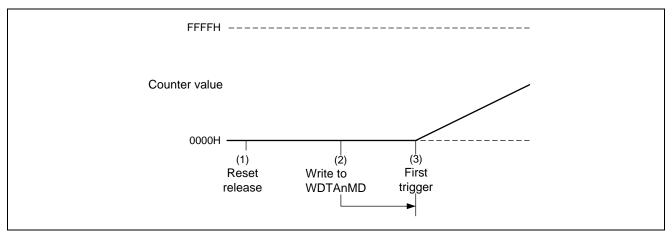

| 15.4.1       | WDTA after Release from the Reset State                       | 15-6  |

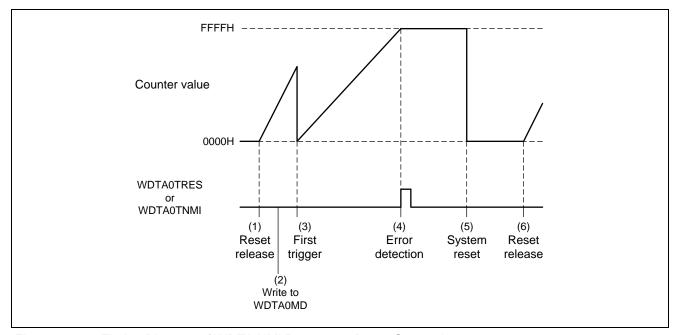

| 15.4.2       | WDTA Trigger                                                  | 15-8  |

| 15.4.3       | Error Detection                                               |       |

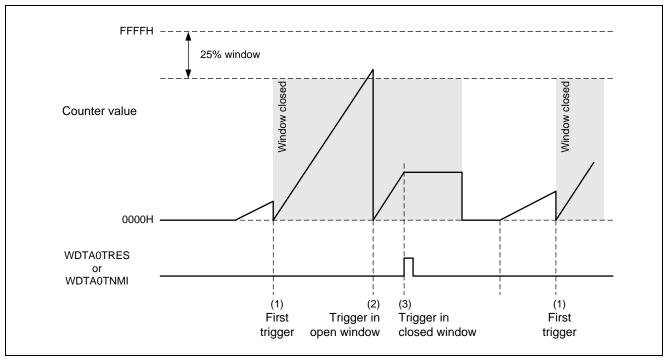

| 15.4.4       | Window Function                                               | 15-10 |

| 15.5 WD      | TOUTZ Output                                                  | 15-11 |

| 15.6 Not     | es                                                            | 15-11 |

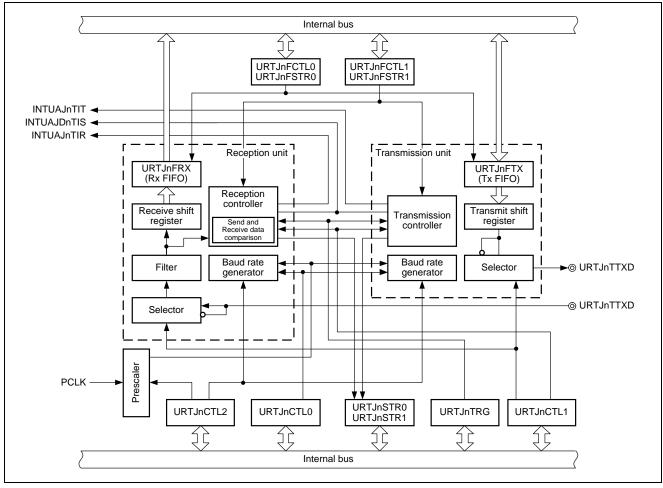

| 16. Asynchr | ronous Serial Interface J (UARTJ)         | 16-1  |

|-------------|-------------------------------------------|-------|

| 16.1 Fe     | eatures of UARTJn                         | 16-1  |

| 16.2 Fu     | unctional Overview                        | 16-3  |

| 16.3 Co     | onfiguration                              | 16-4  |

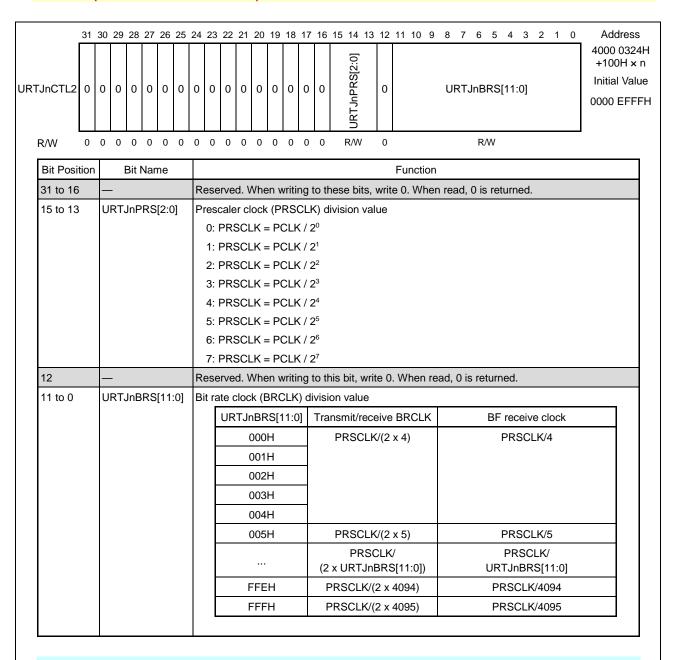

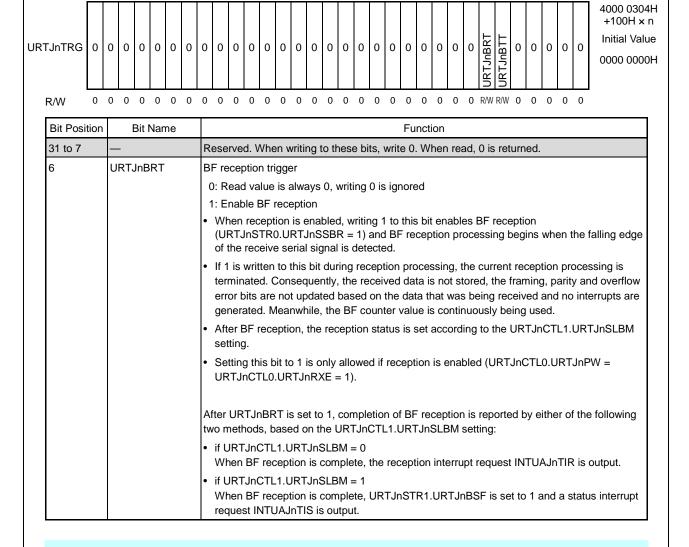

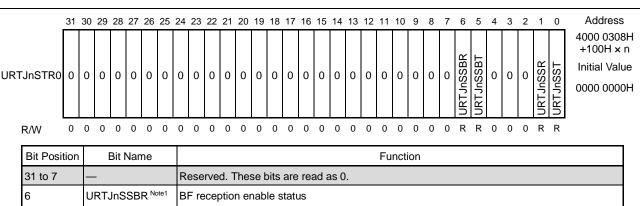

| 16.4 UA     | ARTJn Registers                           | 16-5  |

| 16.5 Int    | terrupt Request Signals                   | 16-27 |

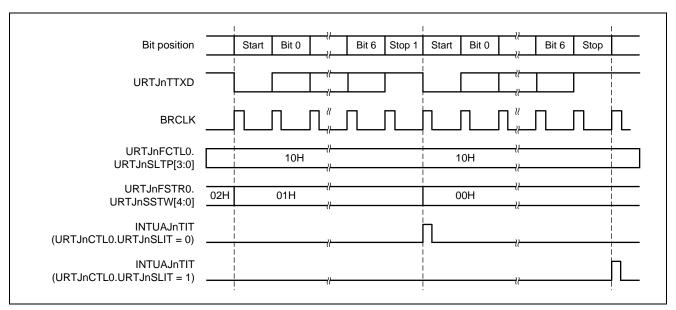

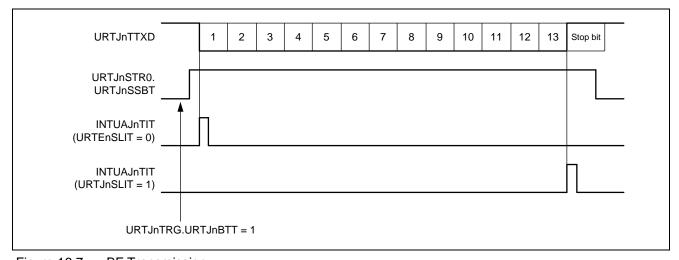

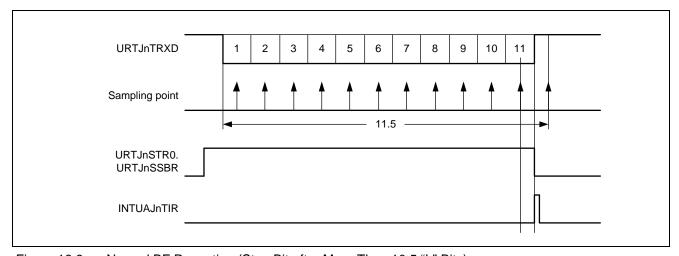

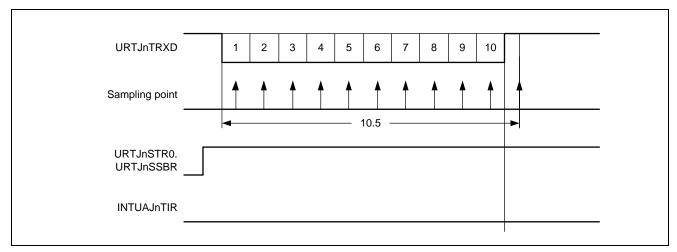

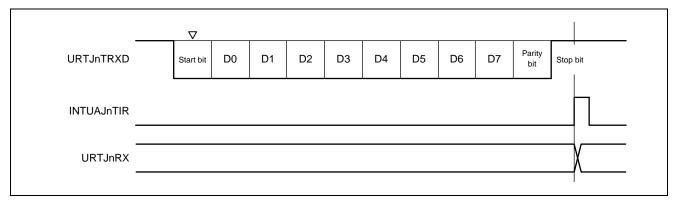

| 16.5.1      | Transmission Interrupt Request INTUAJnTIT | 16-27 |

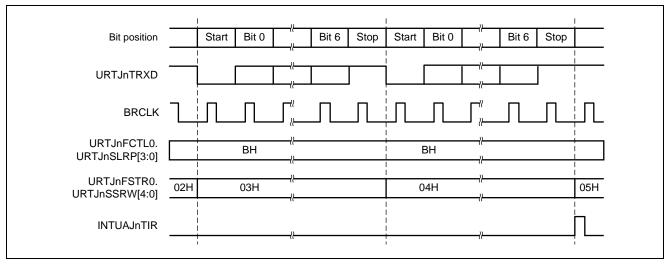

| 16.5.2      | Reception Interrupt Request INTUAJnTIR    | 16-29 |

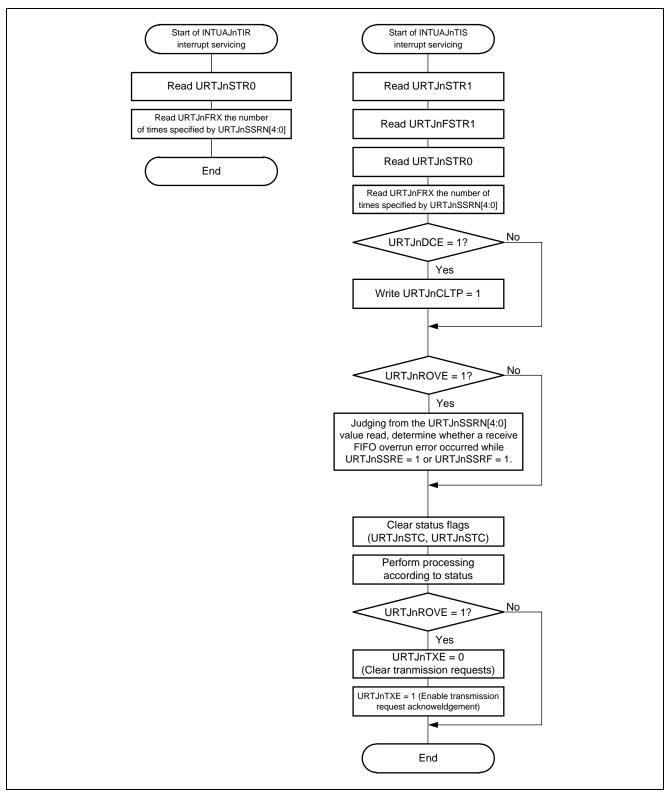

| 16.5.3      | Status Interrupt Request INTUAJnTIS       | 16-30 |

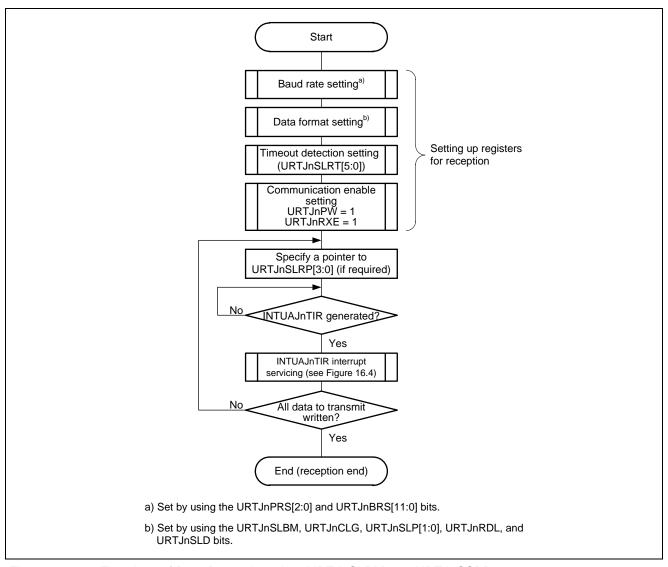

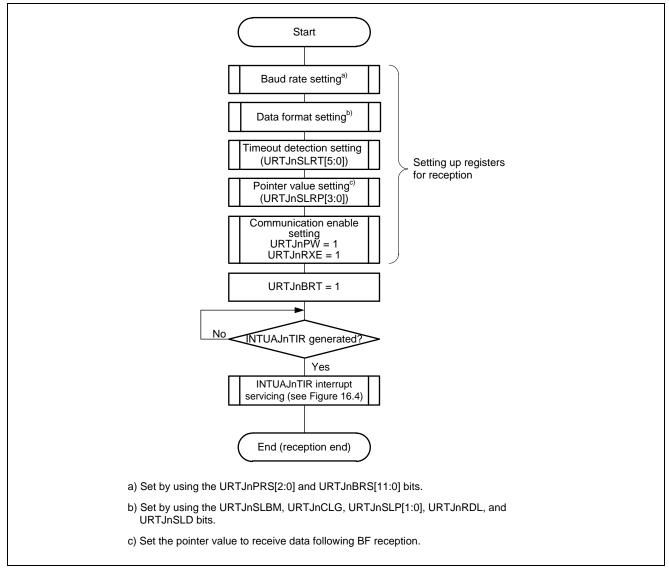

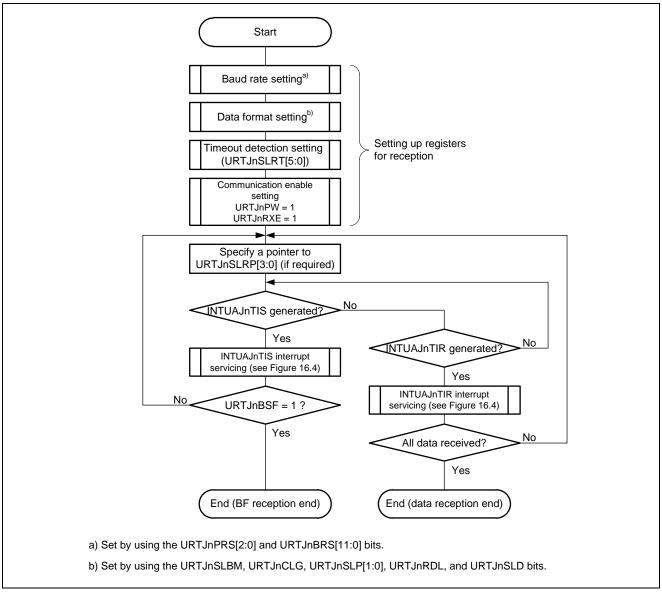

| 16.6 Op     | peration                                  |       |

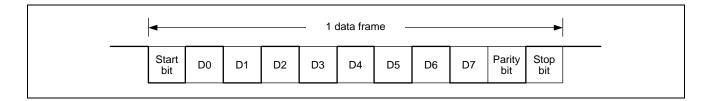

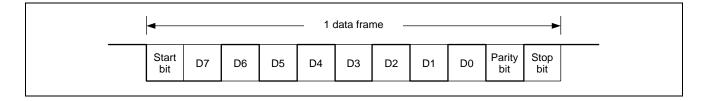

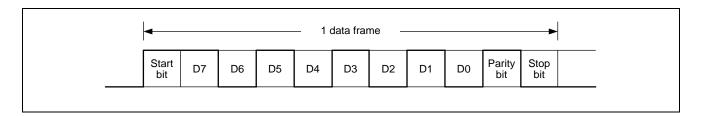

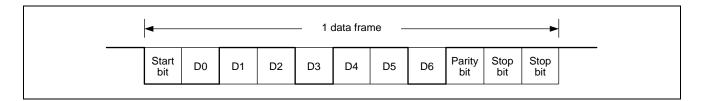

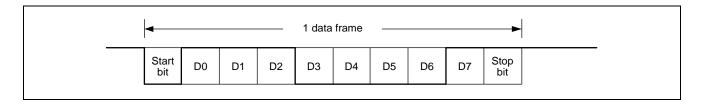

| 16.6.1      | Data Formats                              |       |

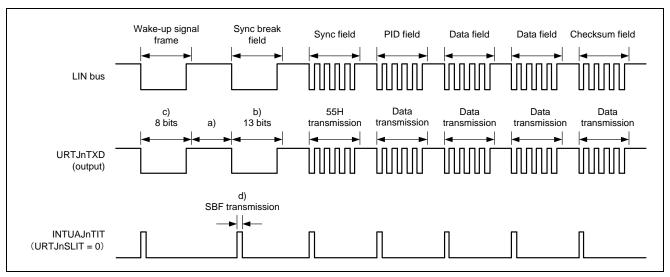

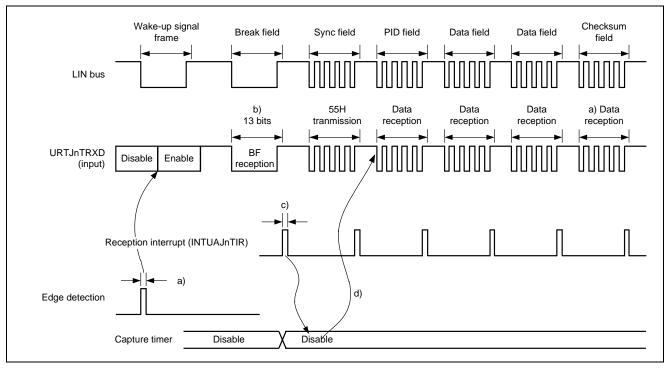

| 16.6.2      | BF Transmission/Reception Format          |       |

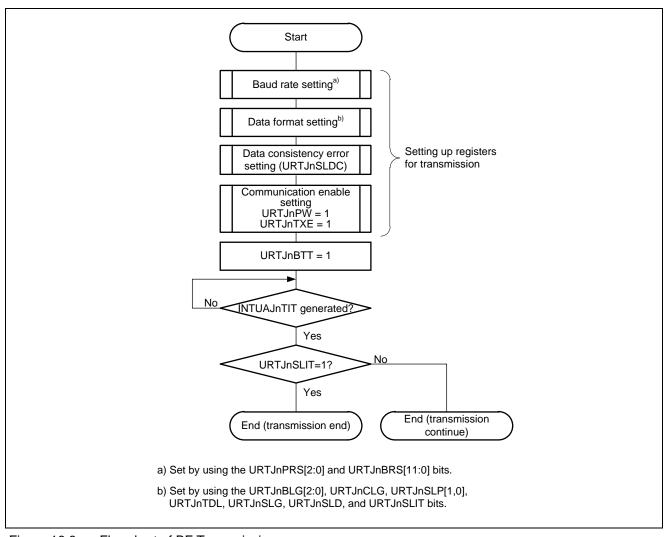

| 16.6.3      | BF Transmission                           |       |

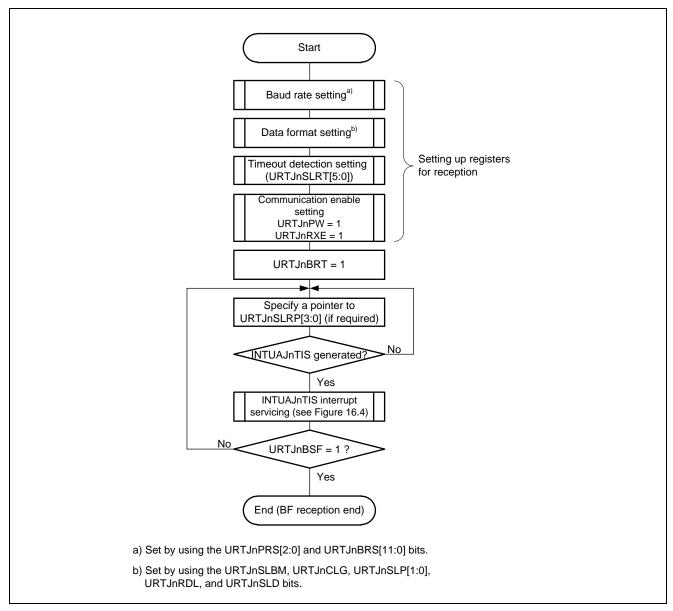

| 16.6.4      | BF Reception                              |       |

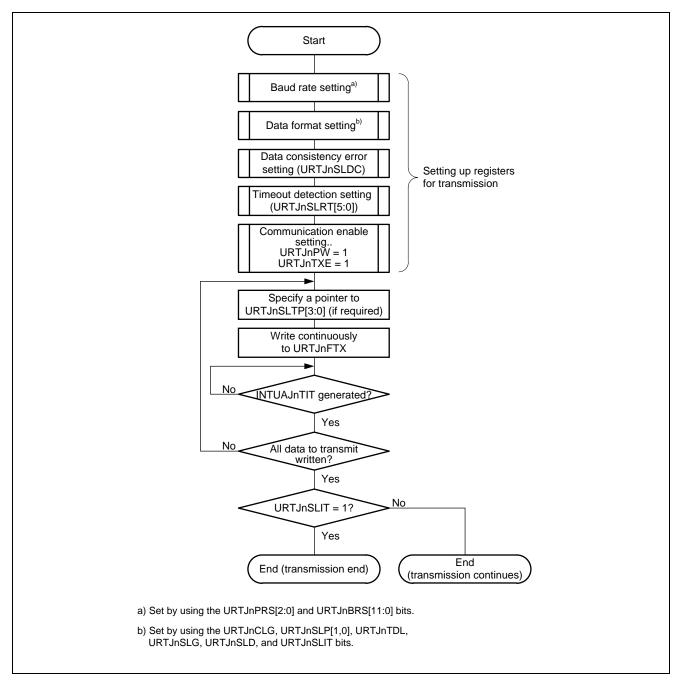

| 16.6.5      | UARTJn Transmission                       |       |

| 16.6.6      | UARTJn Reception                          |       |

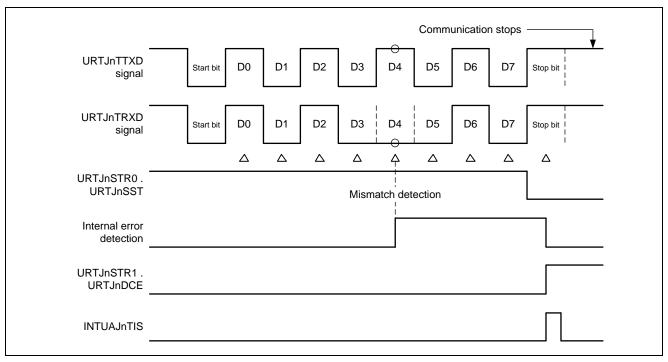

| 16.6.7      | Reception Errors                          |       |

| 16.6.8      | Parity Types and Operations               |       |

| 16.6.9      | Digital Receive Data Noise Filter         |       |

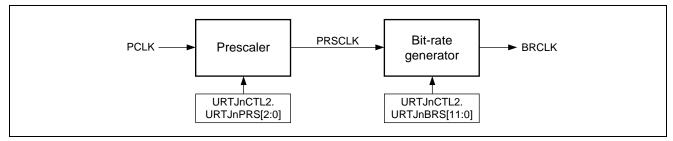

| 16.7 Bi     | it-Rate Generator                         |       |

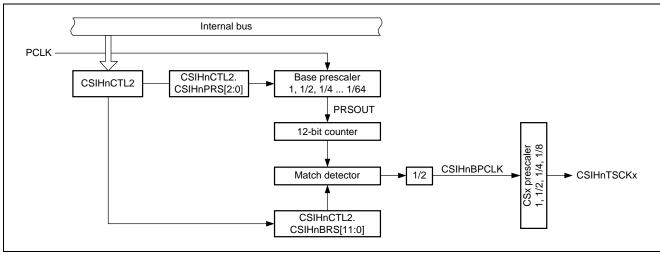

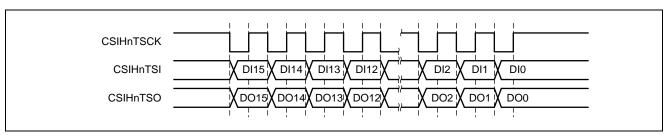

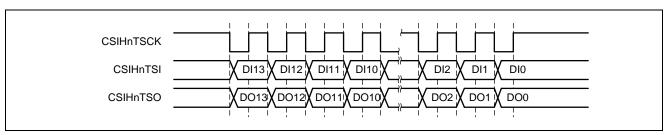

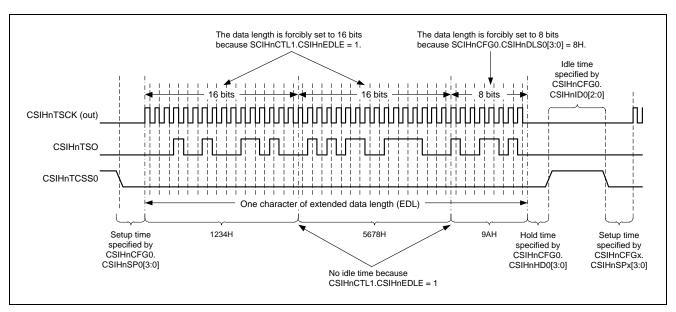

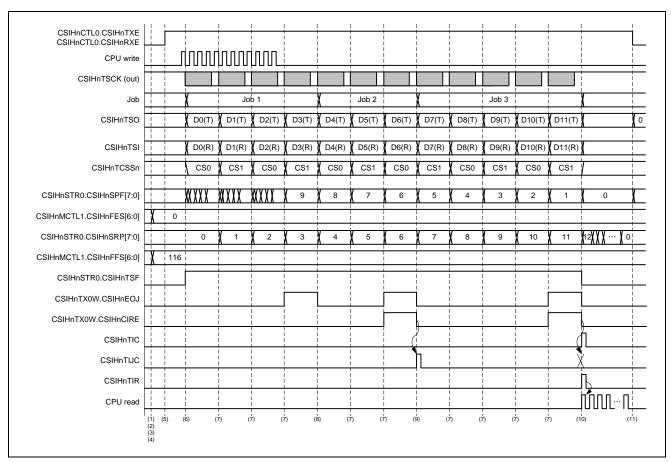

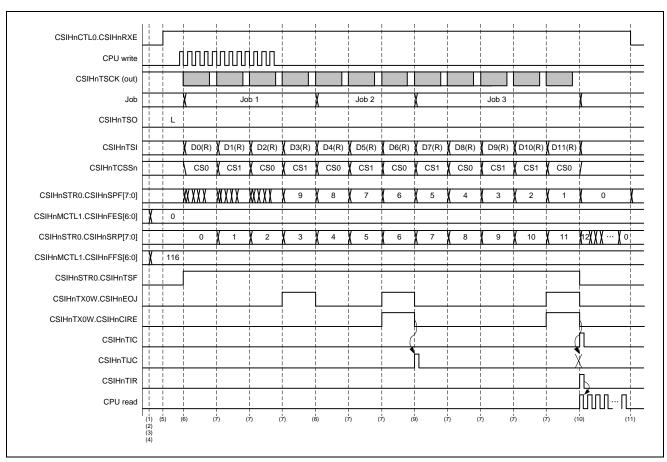

| 17 Clocked  | d Serial Interface H (CSIH)               | 17 1  |

|             |                                           |       |

|             | eatures of CSIH                           |       |

|             | ınctional Overview                        |       |

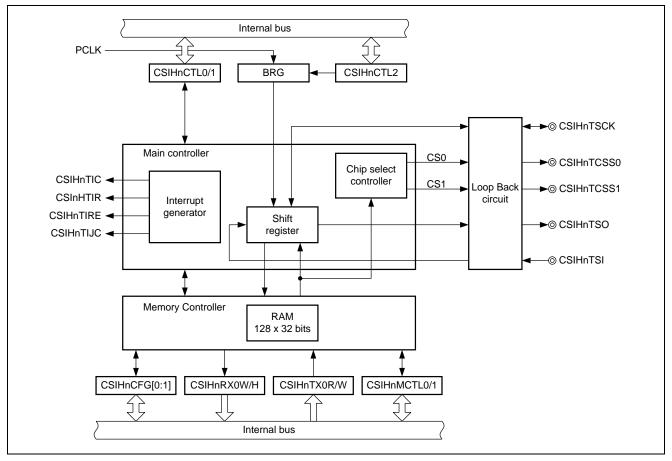

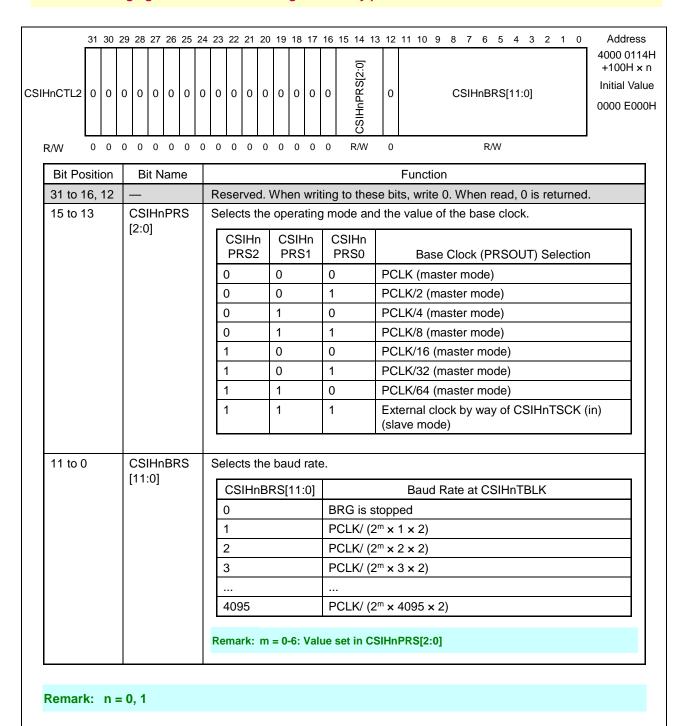

|             | SIH Control Registers                     |       |

| 17.3.1      | CSIH Register Details                     |       |

|             | inctional Description                     |       |

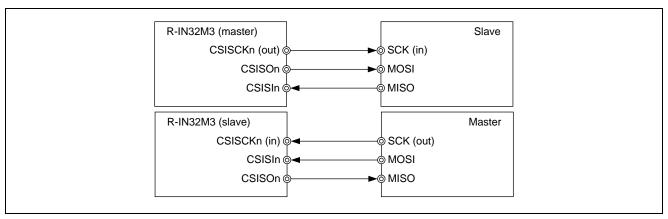

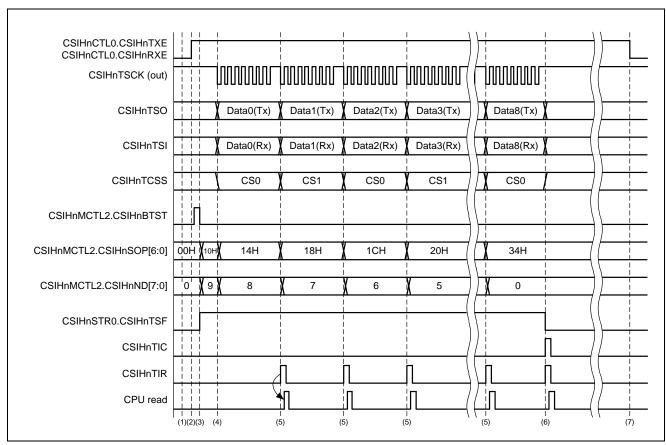

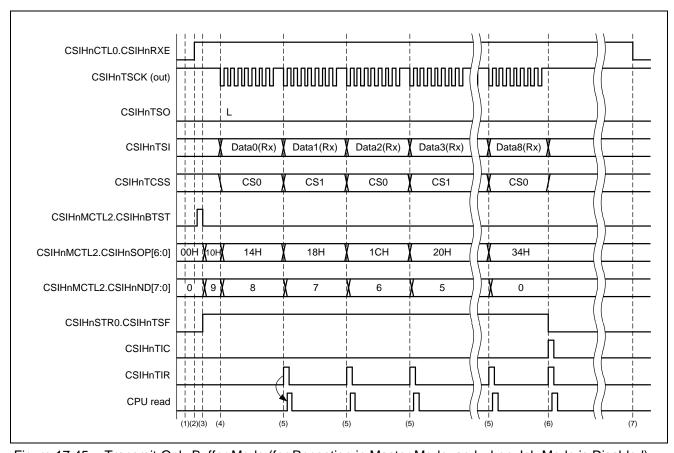

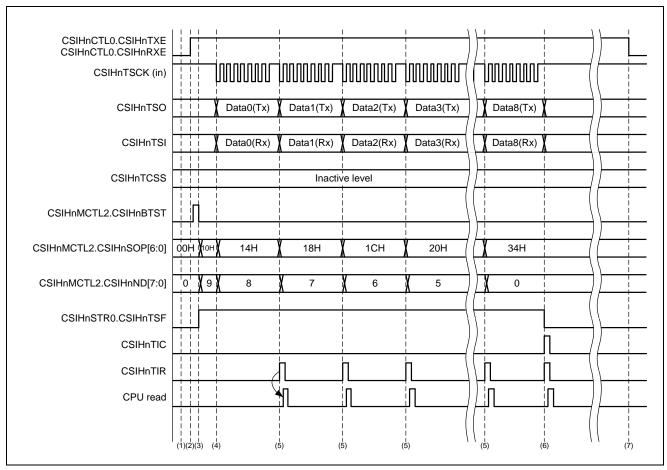

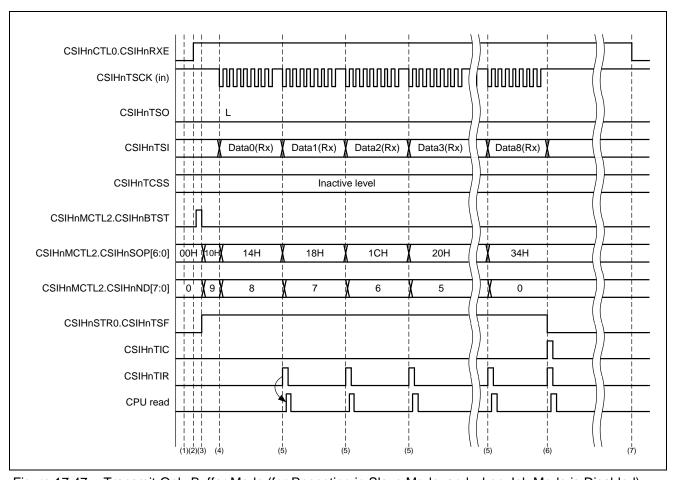

| 17.4.1      | Operating Modes (Master/Slave)            |       |

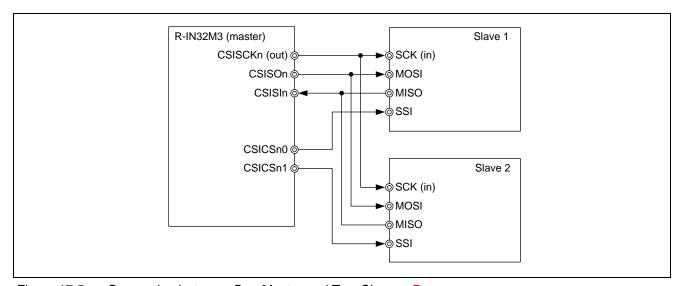

| 17.4.2      | Master/Slave Connections                  |       |

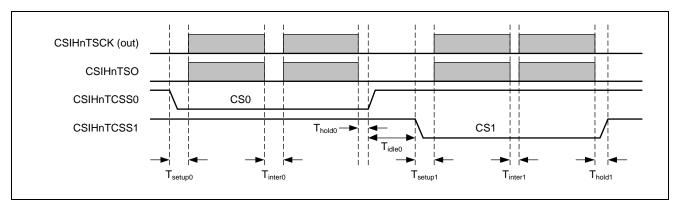

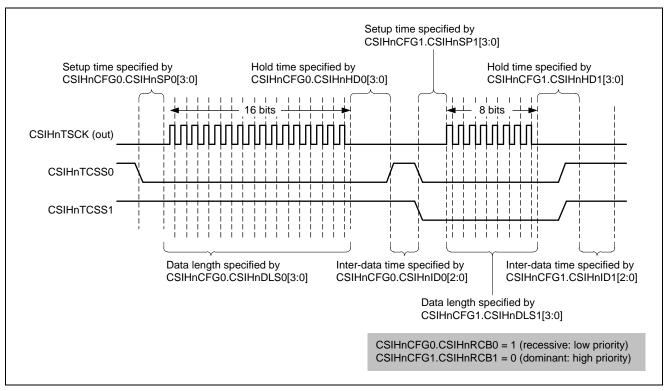

| 17.4.3      | Chip Selection (CS) Features              |       |

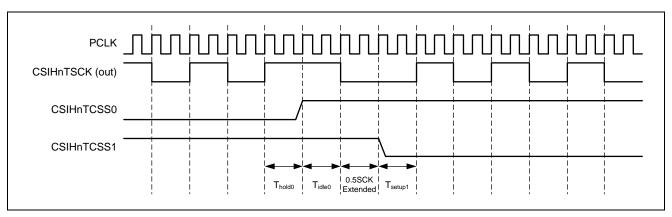

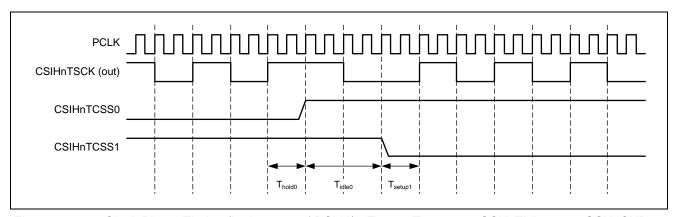

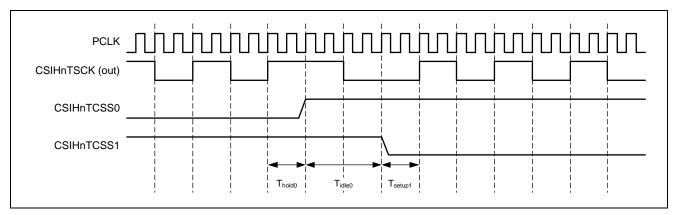

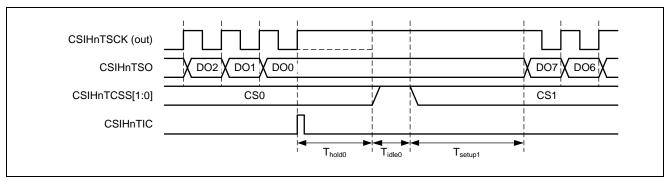

| 17.4.4      | Chip Select Timing Details                |       |

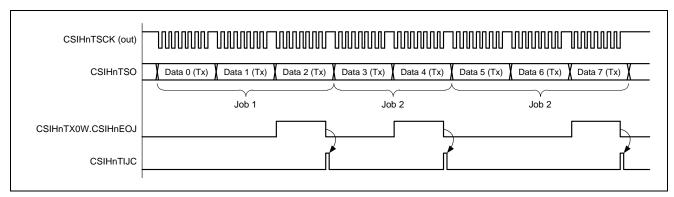

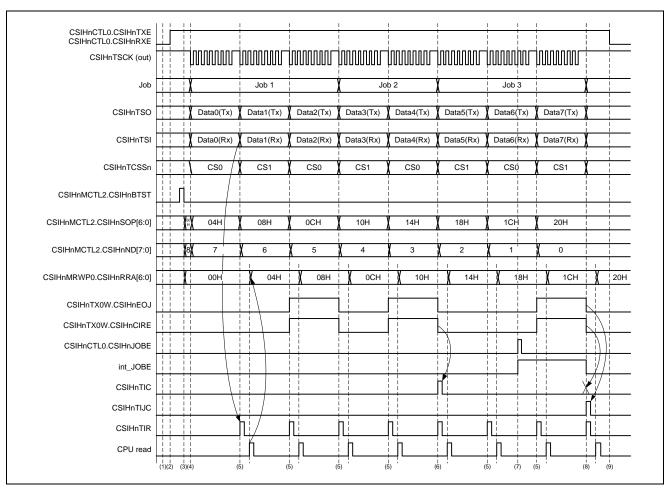

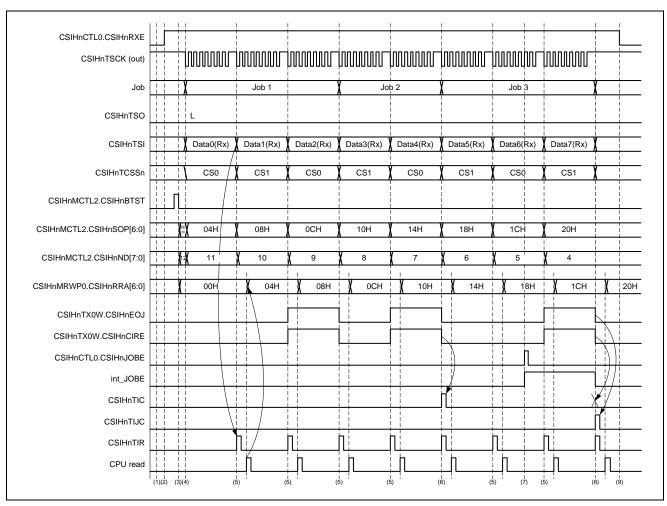

| 17.4.5      | Job Concept                               |       |

| 17.4.6      | Serial Clock Selection                    |       |

| 17.4.7      | CSIH Buffer Memory                        |       |

| 17.4.8      | Data Transfer Modes                       |       |

| 17.4.9      | Data Length Selection                     |       |

| 17.4.10     | Serial Data Direction Selection           |       |

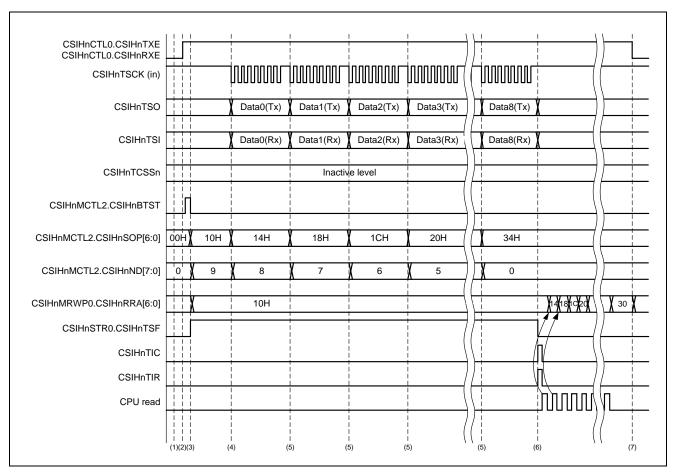

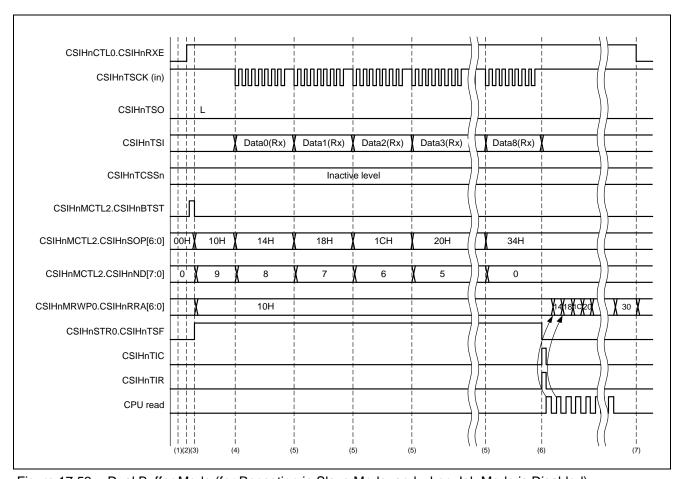

| 17.4.11     | Communication in Slave Mode               | 17-56 |

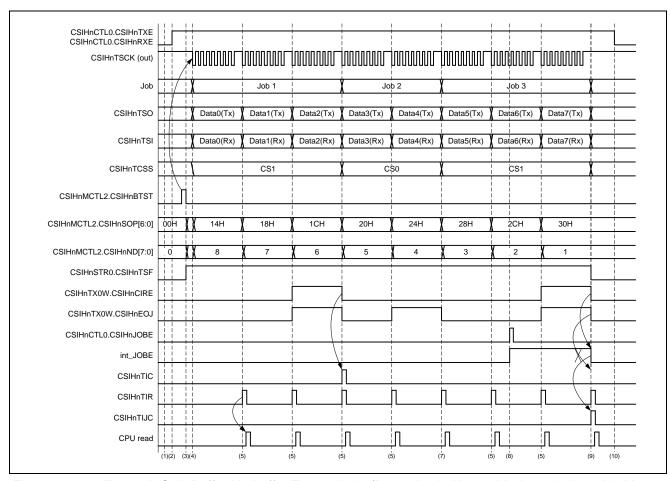

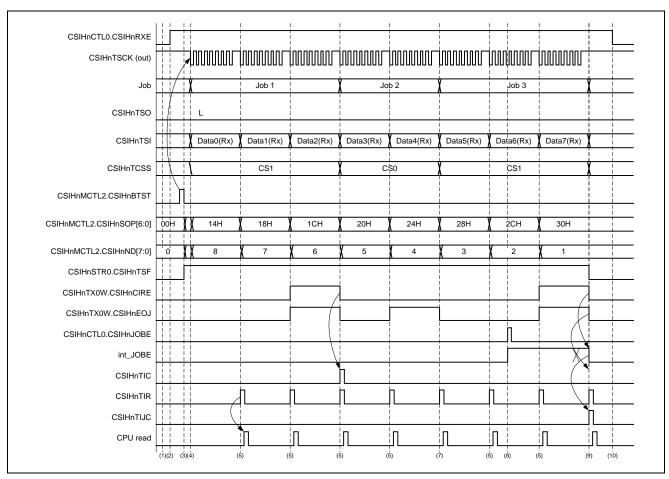

| 17.4.12                  | CSIH Interrupt Requests                                                      | 17-57  |

|--------------------------|------------------------------------------------------------------------------|--------|

| 17.4.13                  | Error Detection                                                              | 17-66  |

| 17.4.14                  | Loop-Back Mode                                                               | 17-75  |

| 17.5 O <sub>J</sub>      | perating Procedures                                                          | 17-76  |

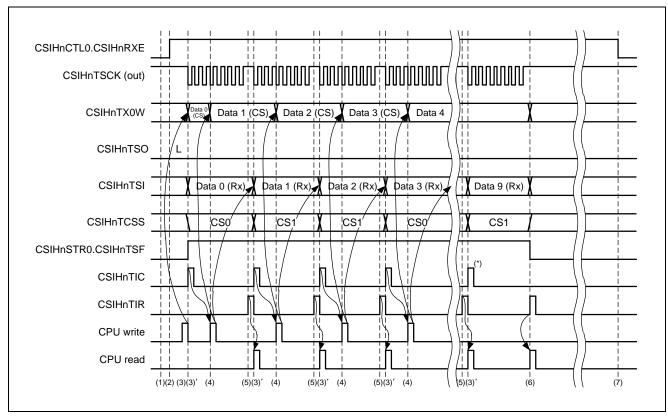

| 17.5.1                   | Procedures in Direct Access Mode                                             | 17-76  |

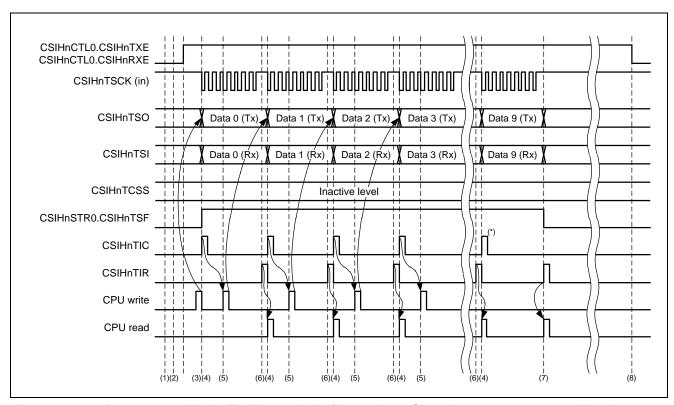

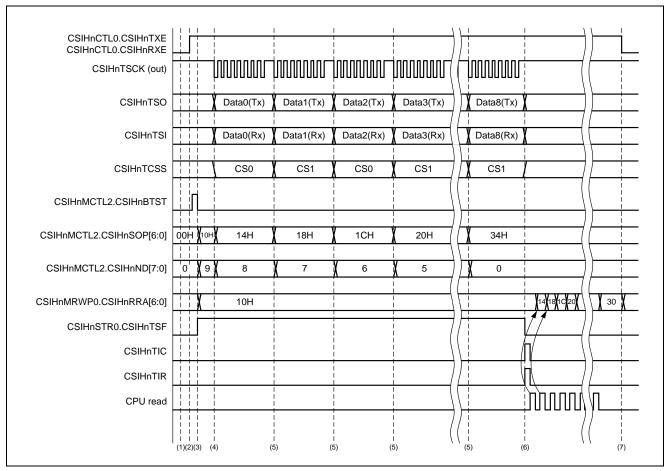

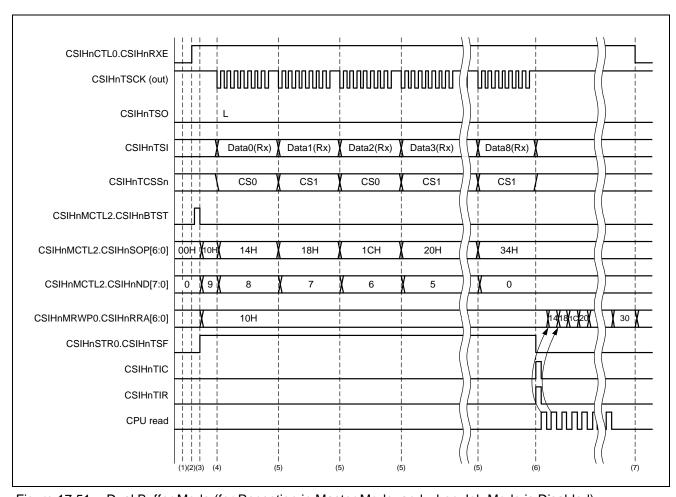

| 17.5.2                   | Procedures in Transmit-Only Buffer Mode                                      | 17-88  |

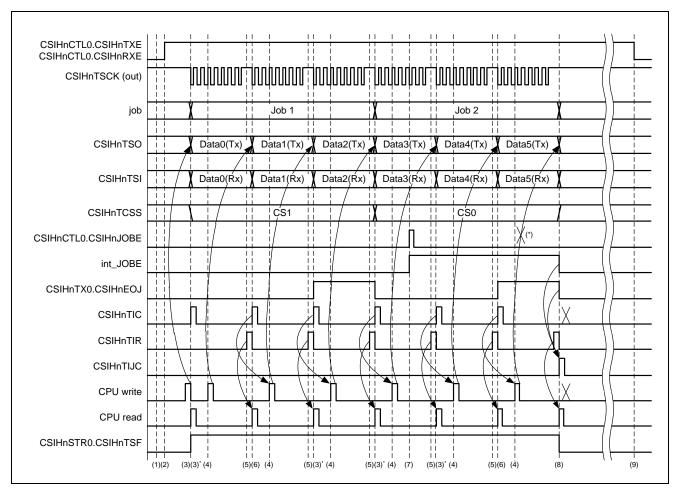

| 17.5.3                   | Procedures in Dual Buffer Mode                                               | 17-100 |

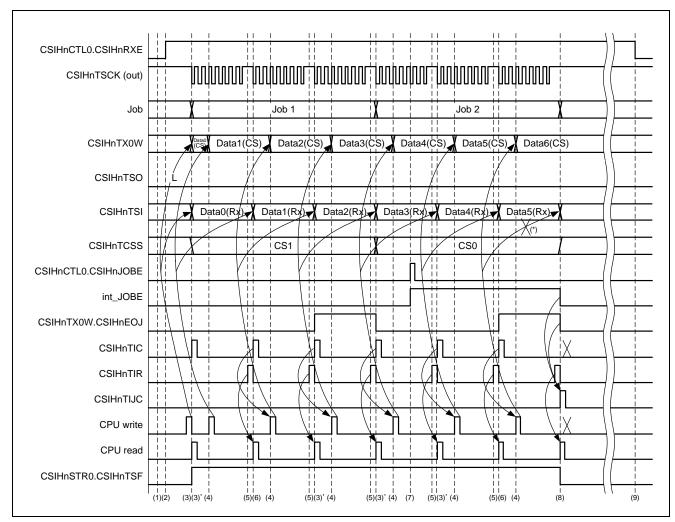

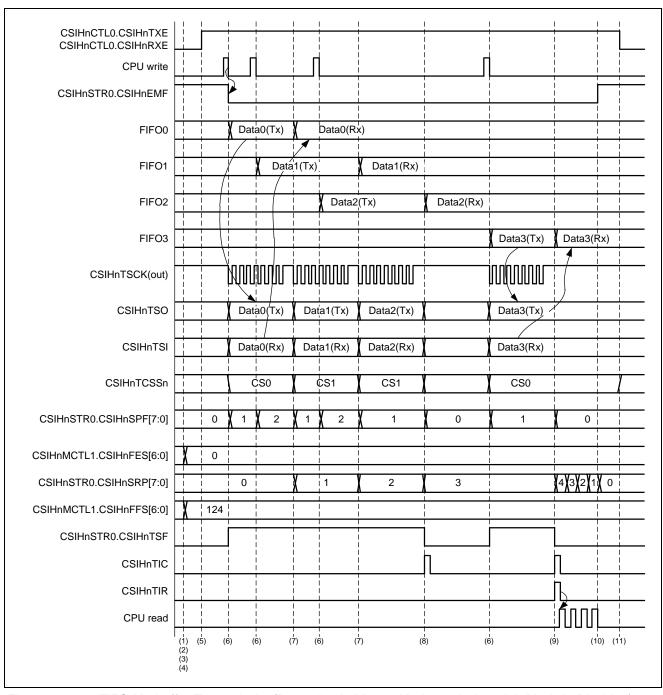

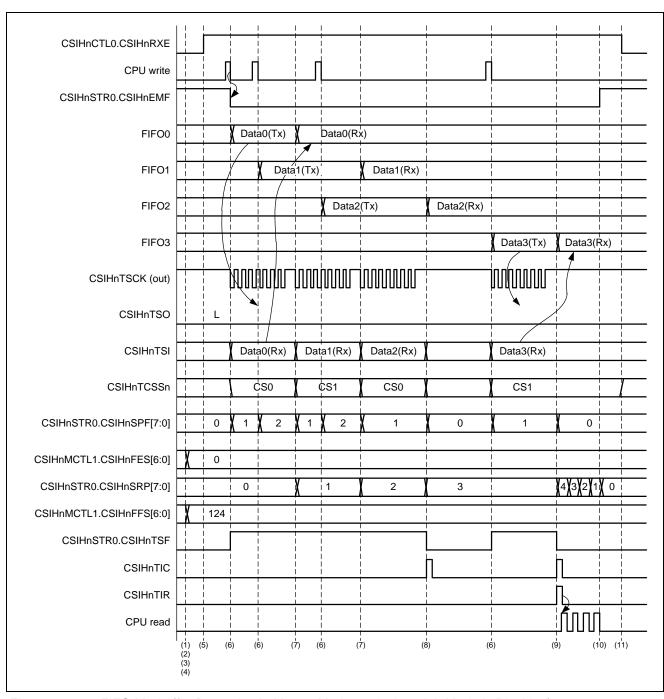

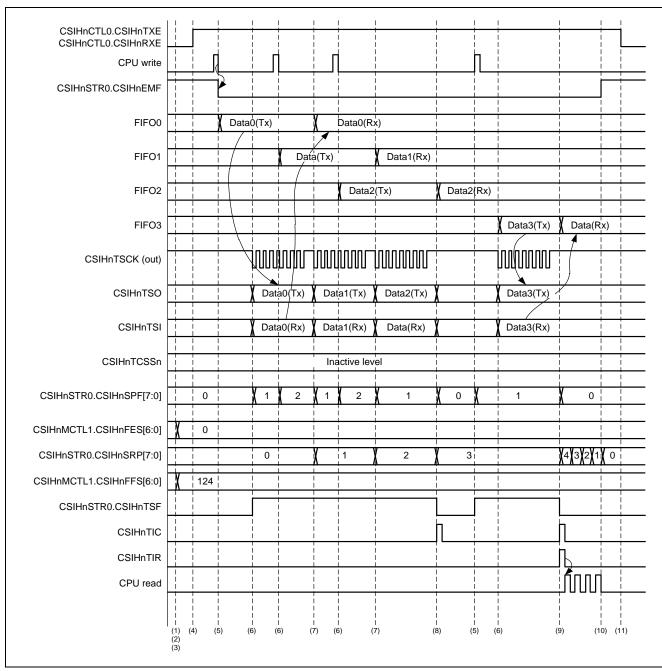

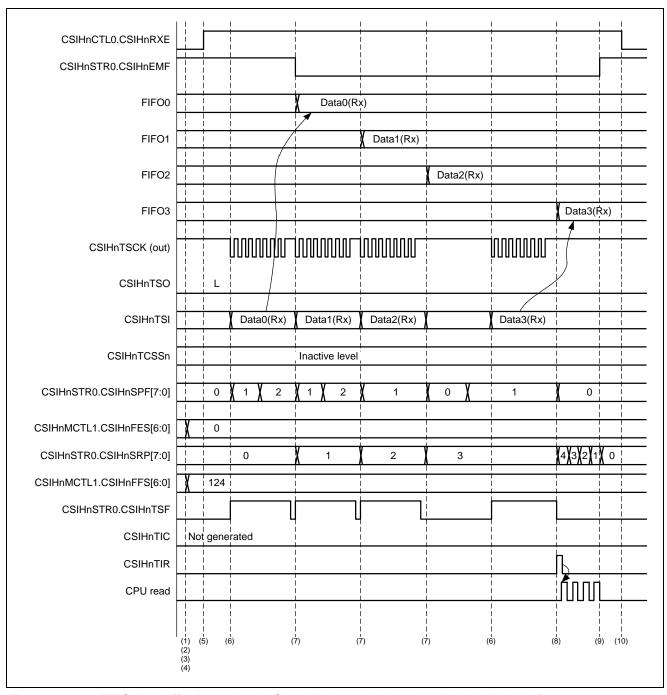

| 17.5.4                   | Procedures in FIFO Mode                                                      | 17-112 |

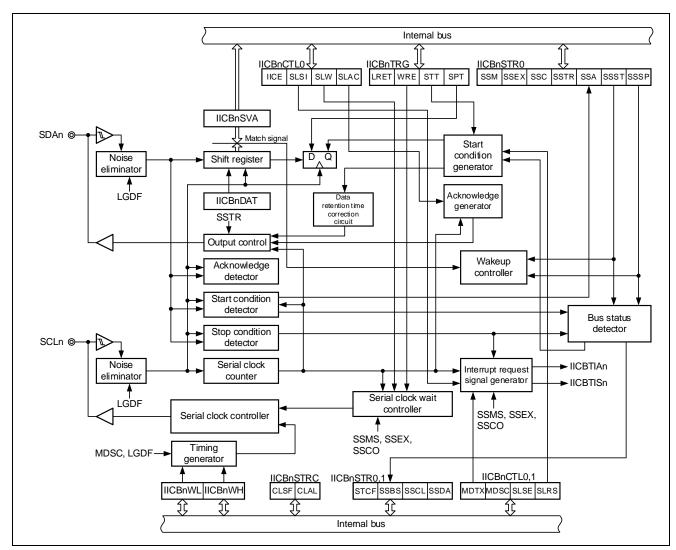

| 18. I <sup>2</sup> C BUS | s (IICB)                                                                     | 18-1   |

| 18.1 Fe                  | atures of IICB                                                               | 18-1   |

| 18.2 Fu                  | nctional Overview                                                            | 18-2   |

| 18.3 Re                  | gisters                                                                      | 18-3   |

| 18.4 IIO                 | C Bus Mode Functions                                                         | 18-30  |

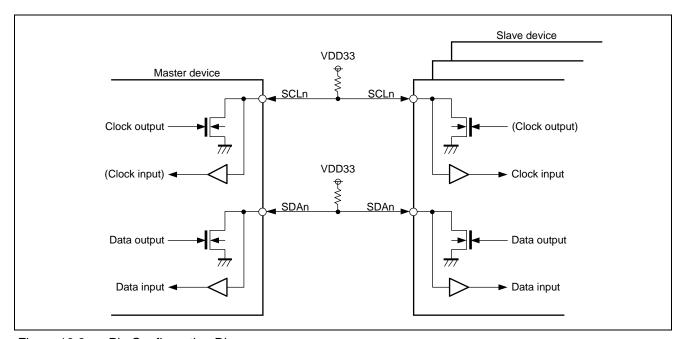

| 18.4.1                   | Pin Configuration.                                                           | 18-30  |

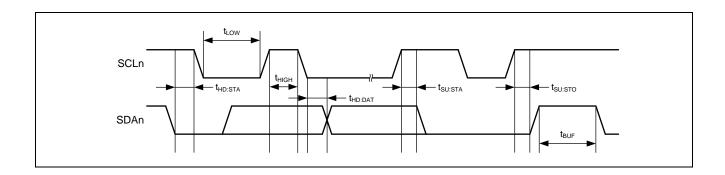

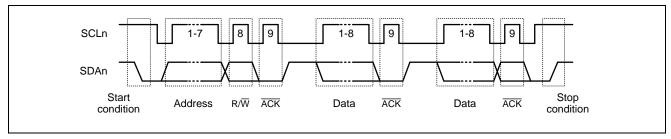

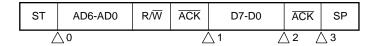

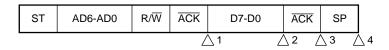

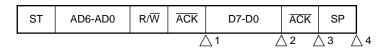

| 18.5 IIC                 | C Bus Definition                                                             | 18-31  |

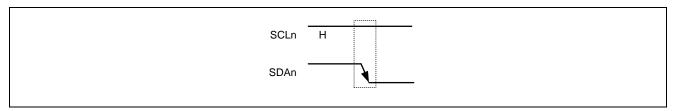

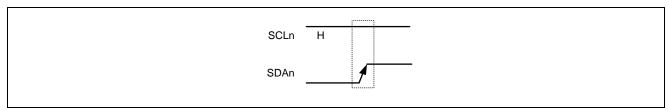

| 18.5.1                   | Start Condition                                                              | 18-31  |

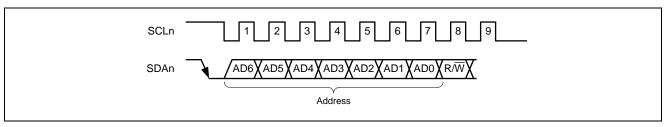

| 18.5.2                   | Addresses                                                                    | 18-32  |

| 18.5.3                   | Extension Code                                                               | 18-32  |

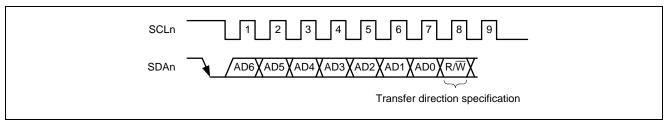

| 18.5.4                   | Transfer Direction Specification                                             | 18-33  |

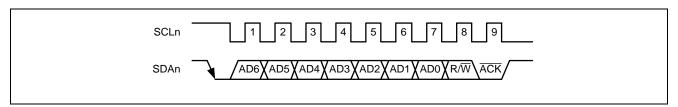

| 18.5.5                   | Acknowledge (ACK)                                                            | 18-33  |

| 18.5.6                   | Data                                                                         | 18-34  |

| 18.5.7                   | Stop Condition                                                               | 18-34  |

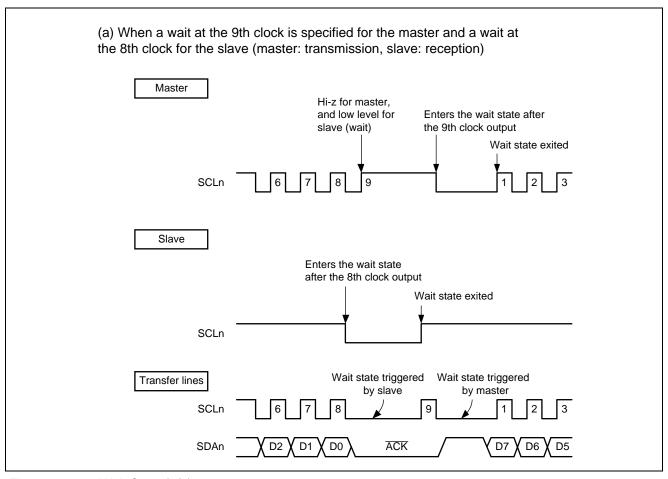

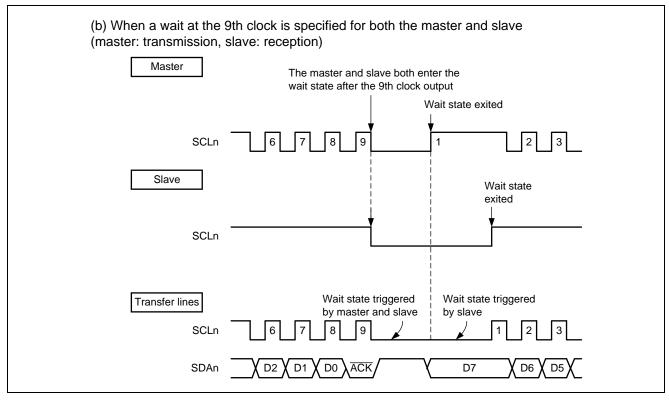

| 18.5.8                   | Wait State                                                                   | 18-35  |

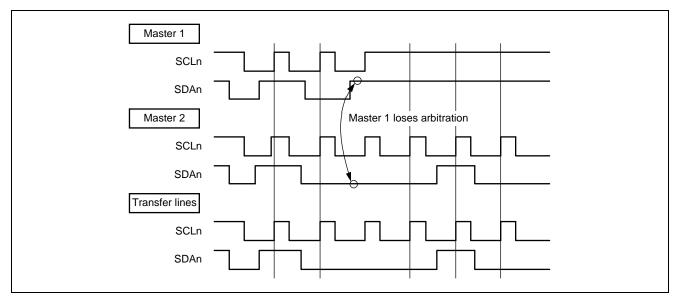

| 18.5.9                   | Arbitration                                                                  | 18-37  |

| 18.6 O <sub>J</sub>      | peration                                                                     | 18-38  |

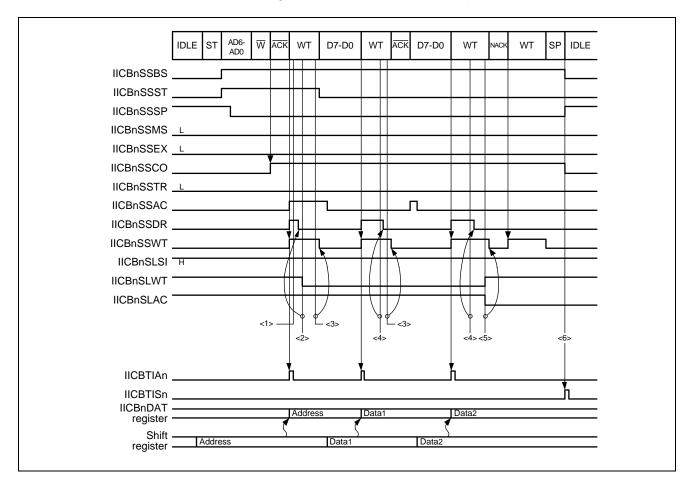

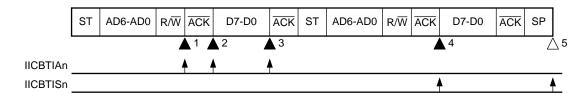

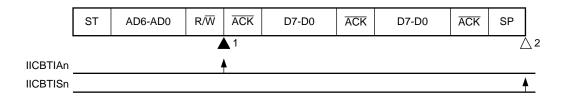

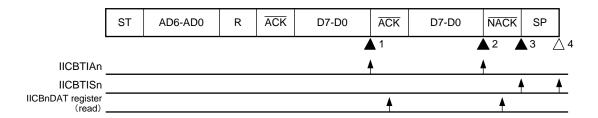

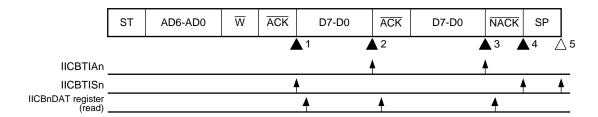

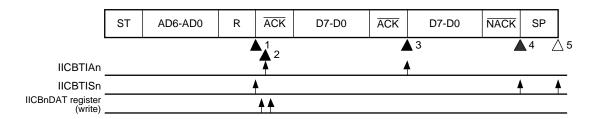

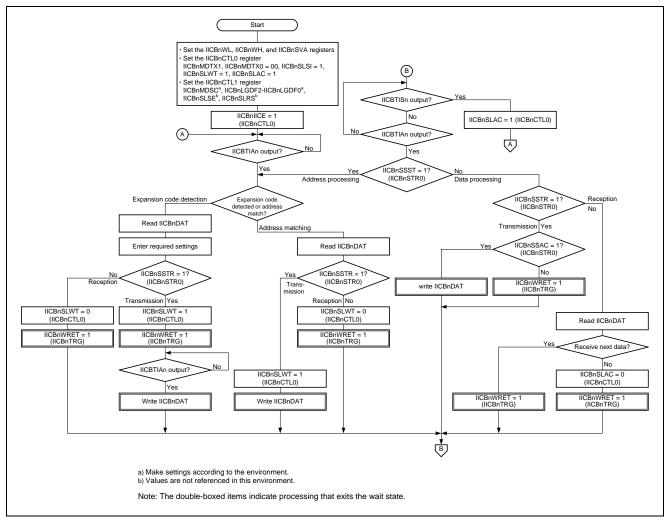

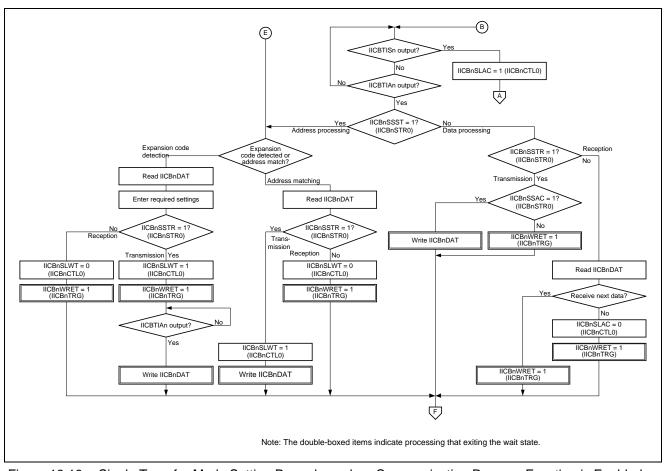

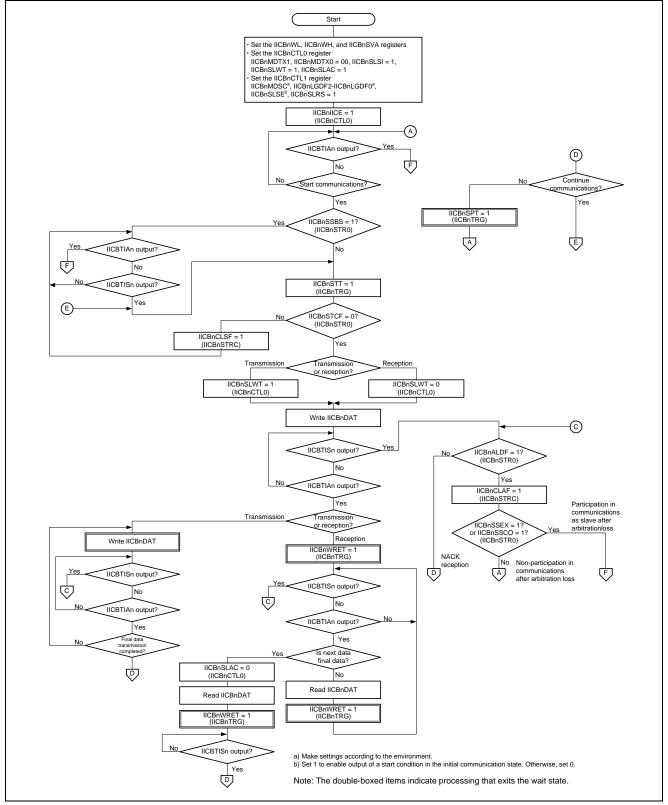

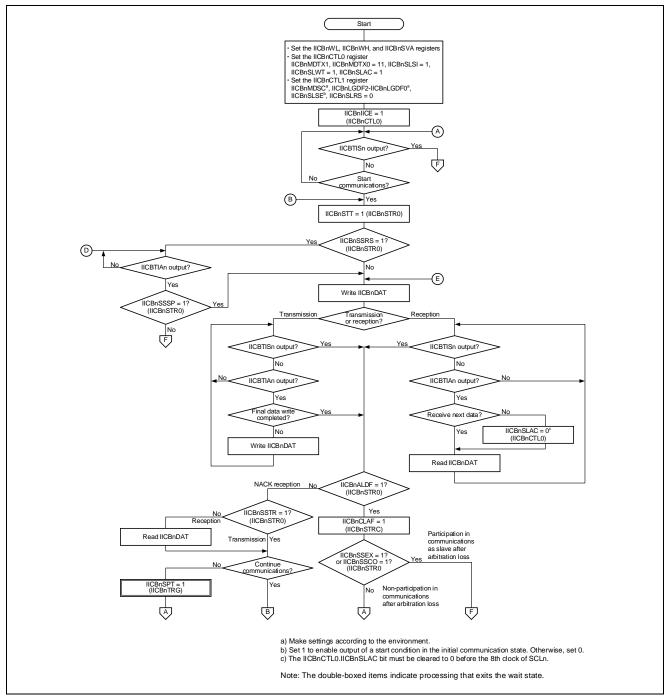

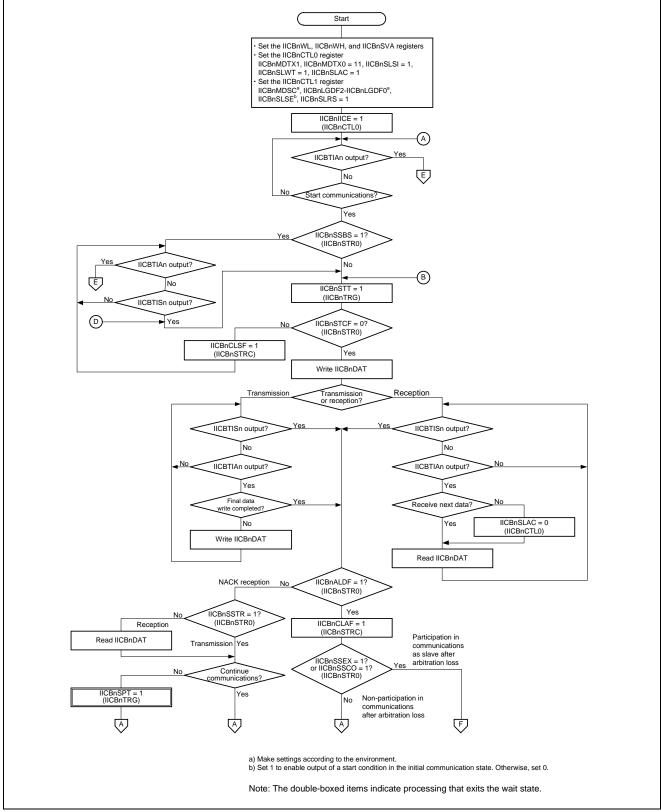

| 18.6.1                   | Single Transfer Mode                                                         | 18-38  |

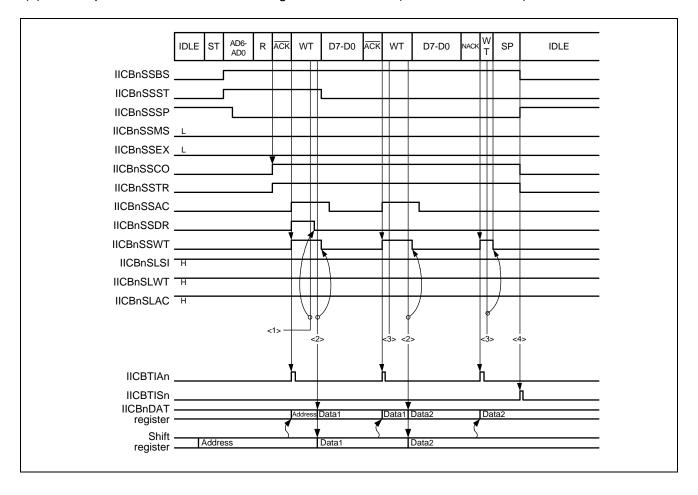

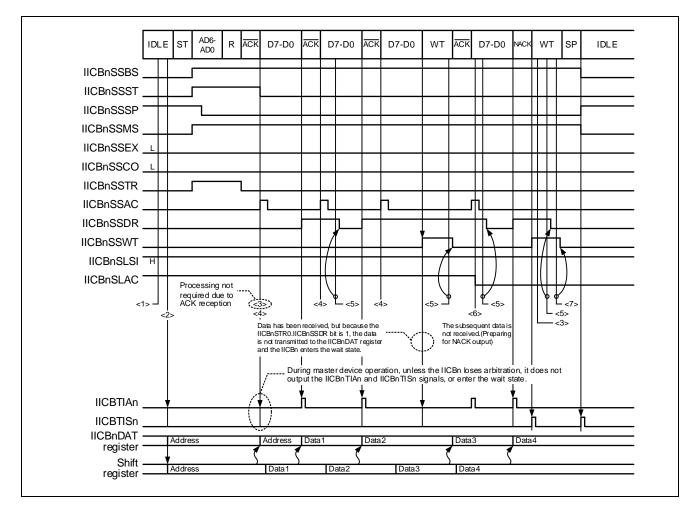

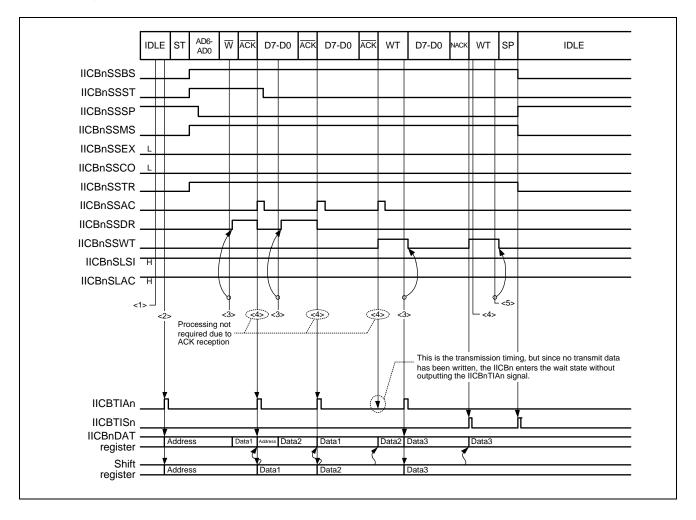

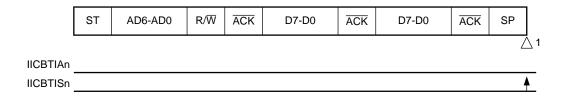

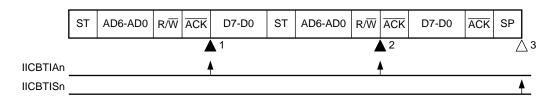

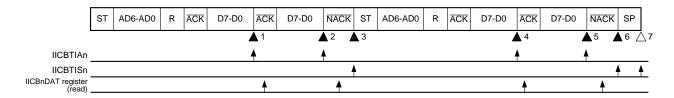

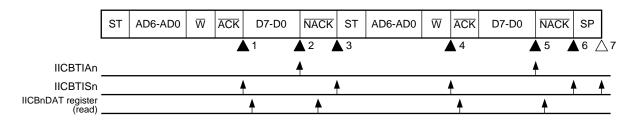

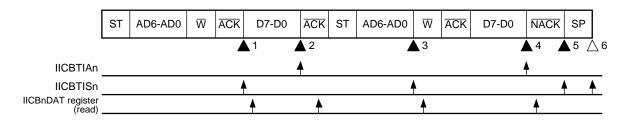

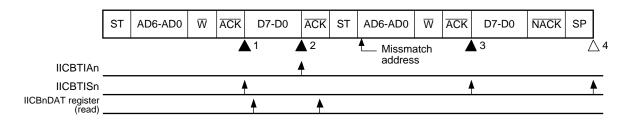

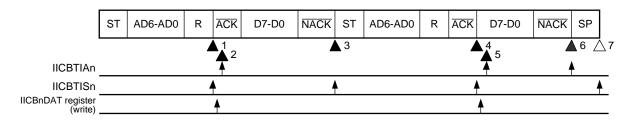

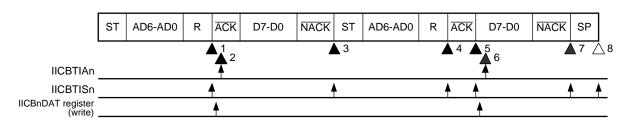

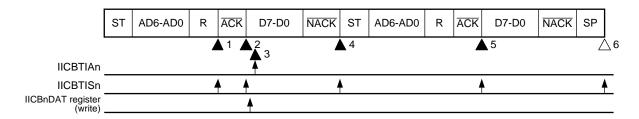

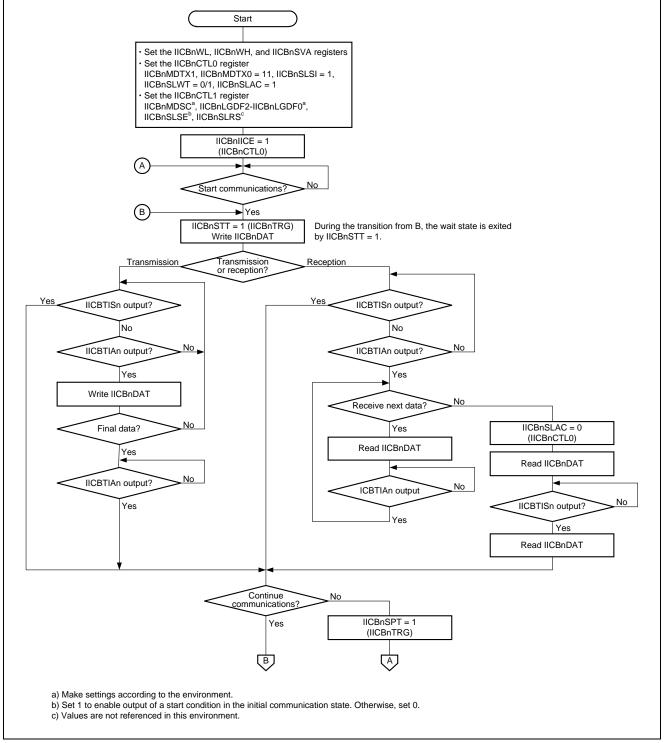

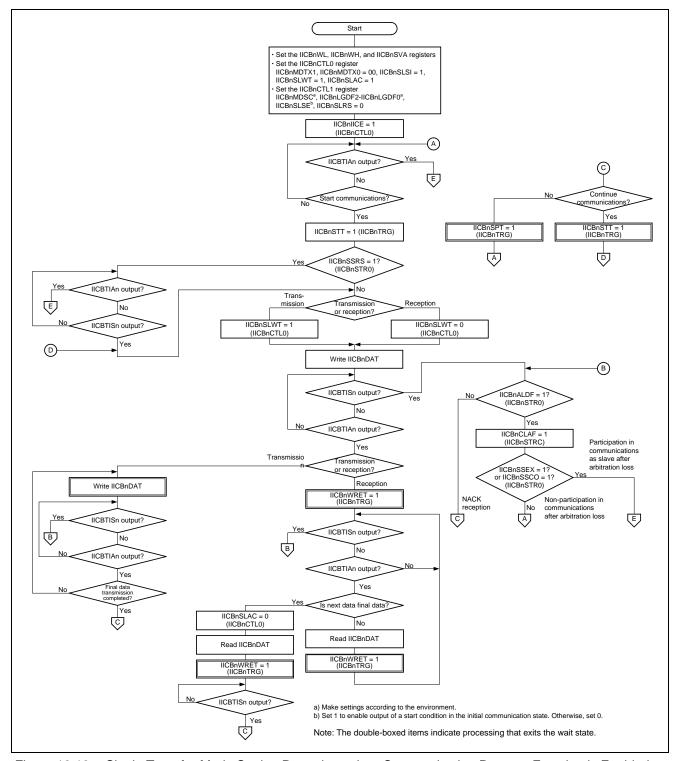

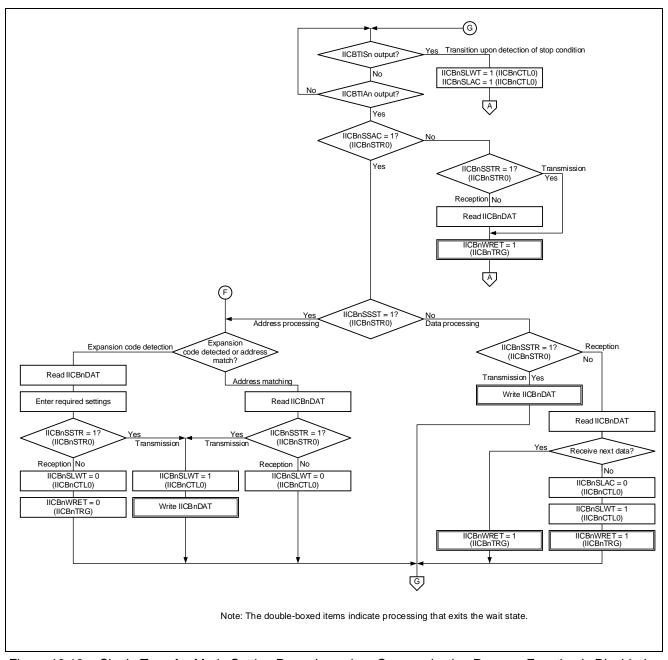

| 18.6.2                   | Continuous Transfer Mode                                                     | 18-43  |

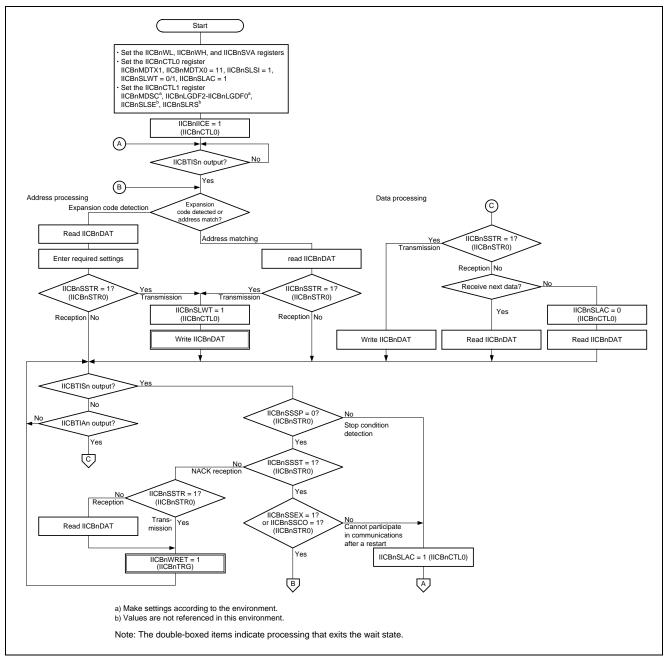

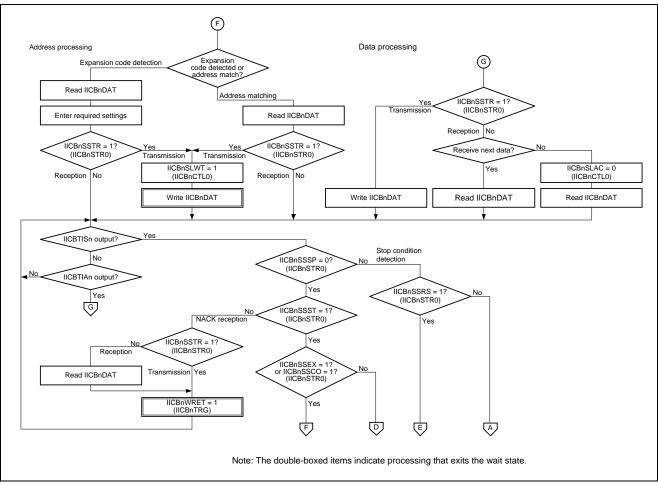

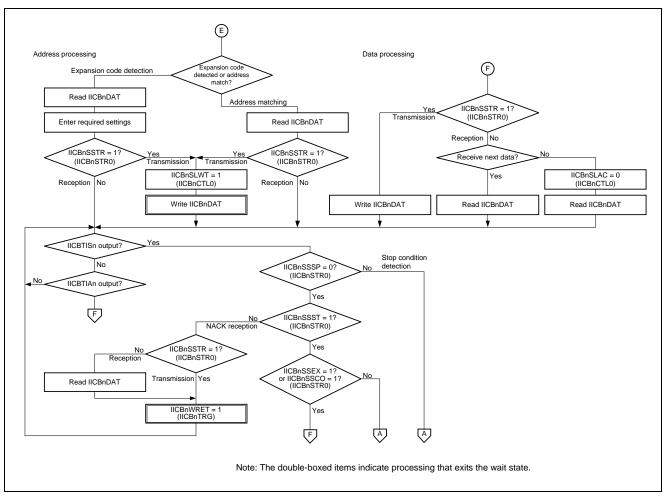

| 18.6.3                   | Arbitration                                                                  | 18-48  |

| 18.6.4                   | Entering and Exiting Wait State                                              | 18-49  |

| 18.6.5                   | Extension Code                                                               | 18-54  |

| 18.7 In                  | errupt Request Signals                                                       | 18-55  |

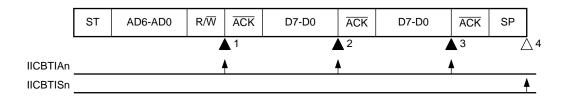

| 18.7.1                   | Single Transfer Mode                                                         | 18-55  |

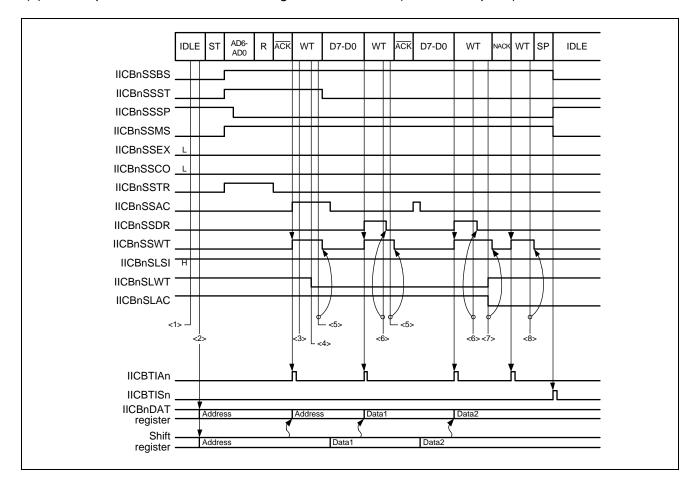

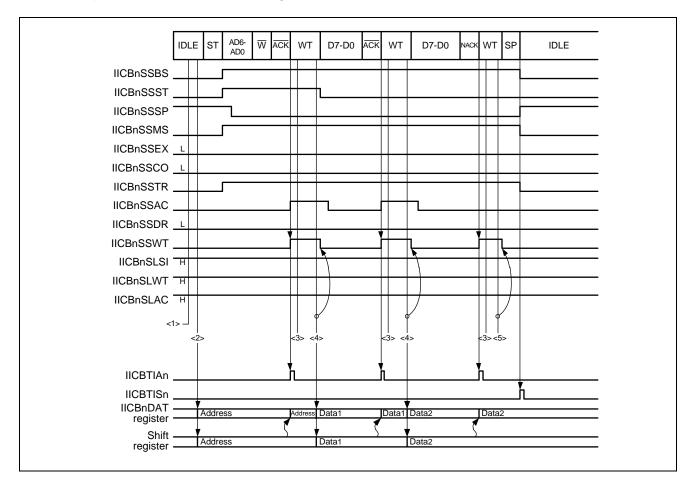

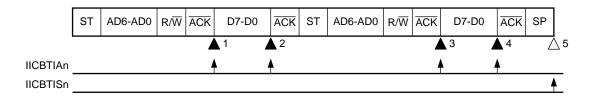

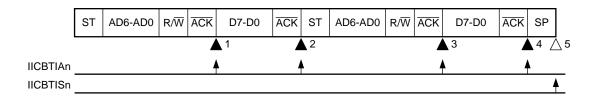

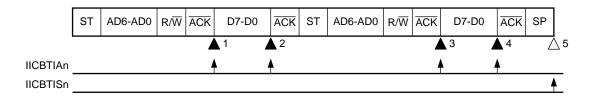

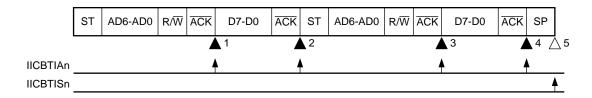

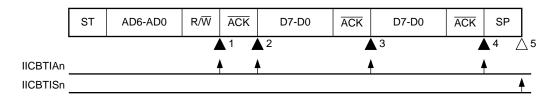

| 18.7.2                   | Continuous Transfer Mode                                                     | 18-58  |

| 18.8 In                  | errupt Outputs and States                                                    | 18-63  |

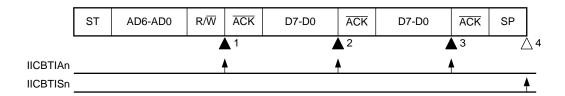

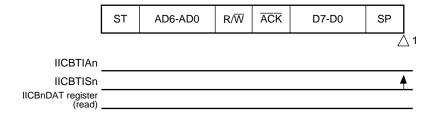

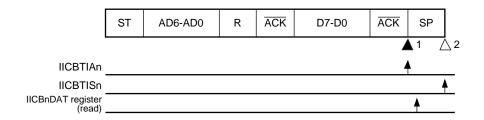

| 18.8.1                   | Single Transfer Mode (Master Device Operation)                               | 18-64  |

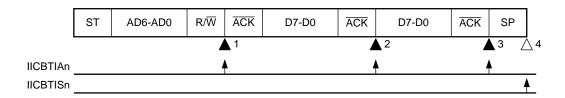

| 18.8.2                   | Single Transfer Mode (Slave Device Operation: during Slave Address Reception |        |

|                          | (IICBnSTR0.IICBnSSC0 bit = 1))                                               | 18-67  |

| 18.8.3    | Single Transfer Mode (Stave Device Operation: during Extension Code Reception  (IICBnSTR0.IICBnSSEX bit = 1))                             | 71  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 18.8.4    | Single Transfer Mode (Non-Participation in Communications)                                                                                |     |

| 18.8.5    | Single Transfer Mode (Arbitration Loss Operation (IICBnSTR0.IICBnALDF bit = 1): Operation as                                              | 13  |

| 10.0.3    | Slave after Arbitration Loss)                                                                                                             | 76  |

| 18.8.6    | Single Transfer Mode (Arbitration Loss Operation (IICBnSTR0.IICBnALDF bit = 1): Non-Participati in Communications after Arbitration Loss) | on  |

| 18.8.7    | Single Transfer Mode (Arbitration Loss Operation (IICBnSTR0.IICBnALDF bit = 1): Non-Participati                                           | on  |

|           | in Communications after Arbitration Loss (during Extension Code Transfer))                                                                | 84  |

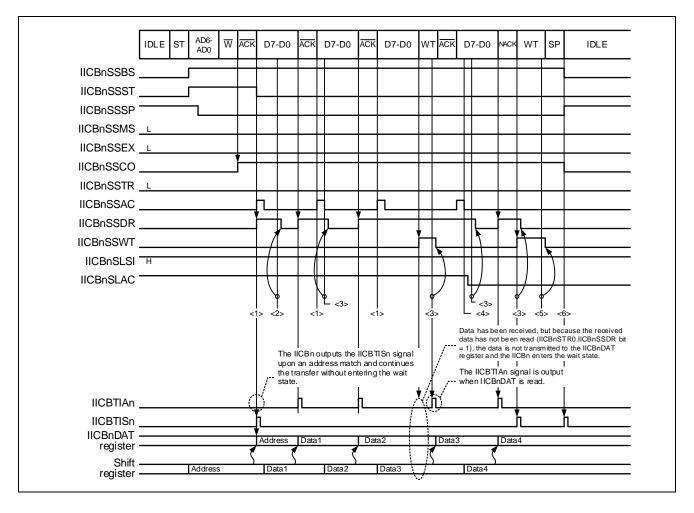

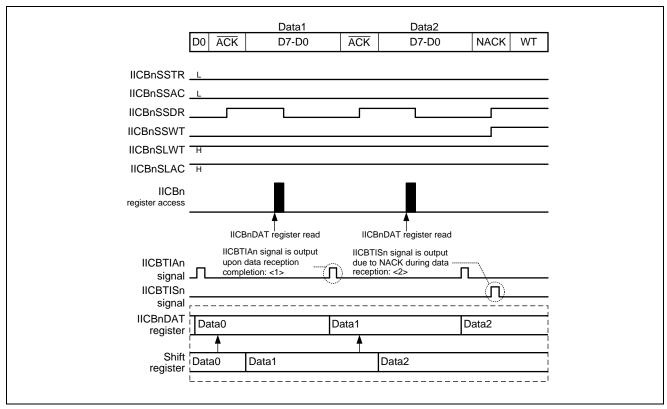

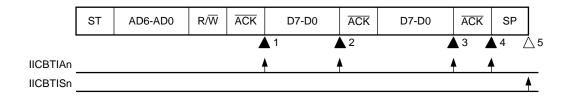

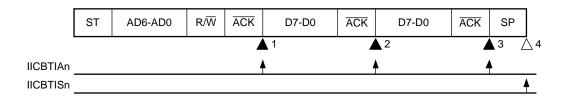

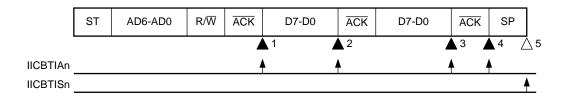

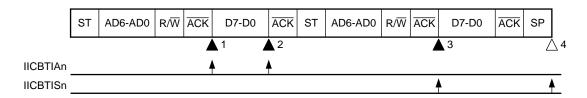

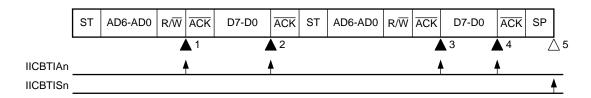

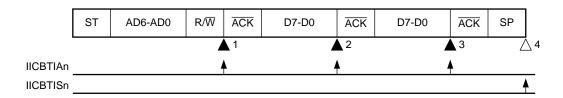

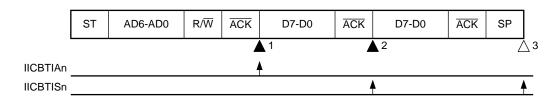

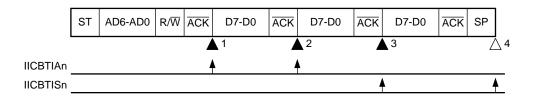

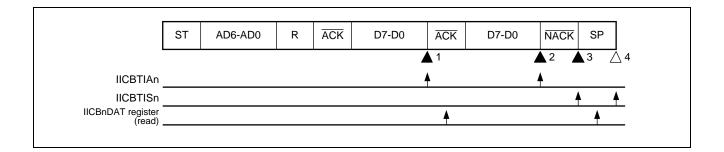

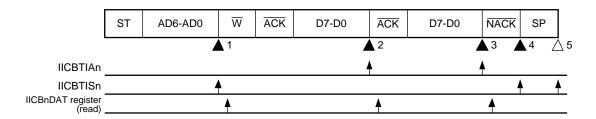

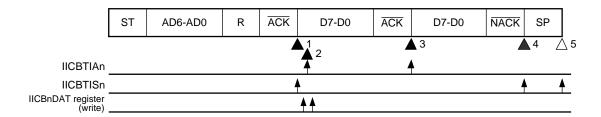

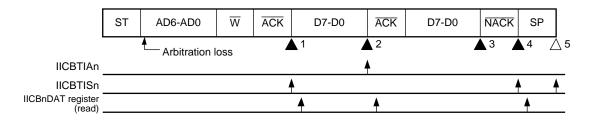

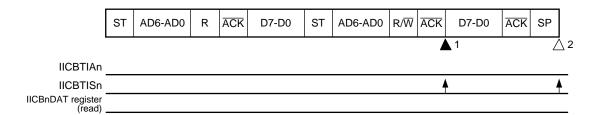

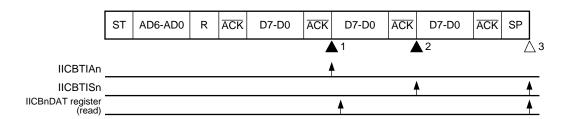

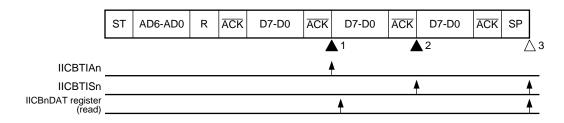

| 18.8.8    | Continuous Transfer Mode (Master Device Operation (Reception))                                                                            | 85  |

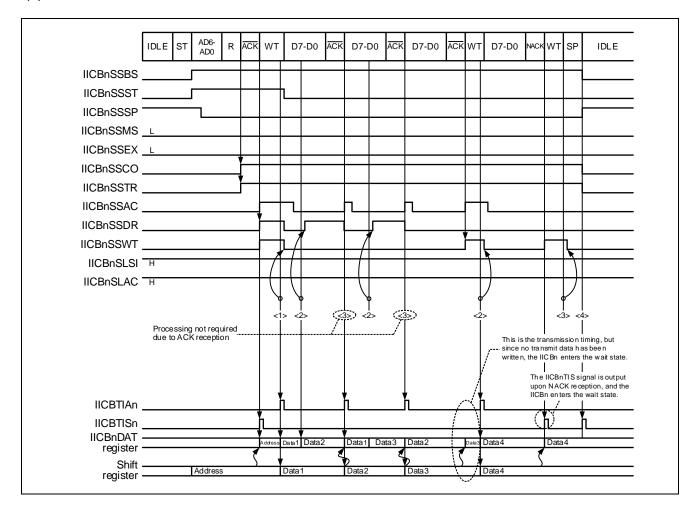

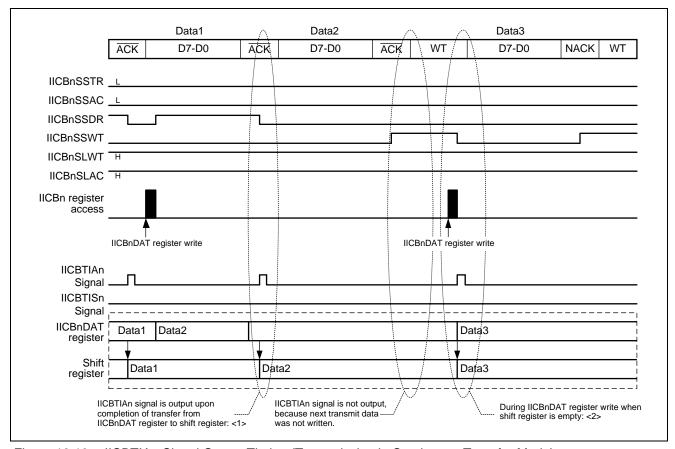

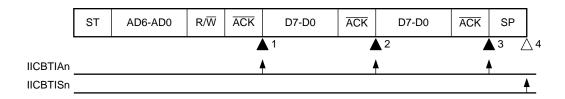

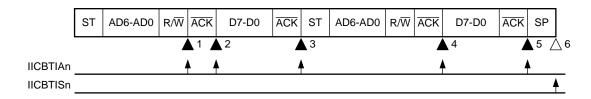

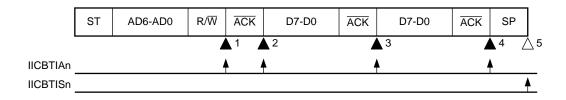

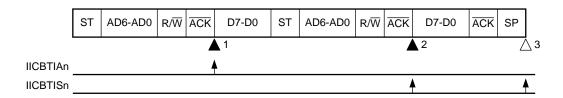

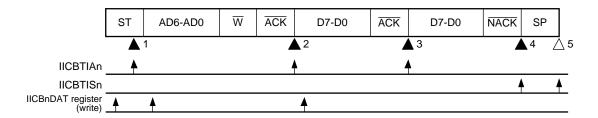

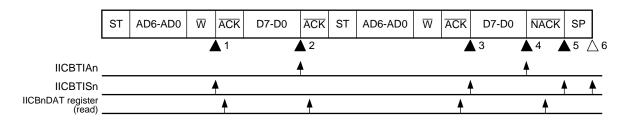

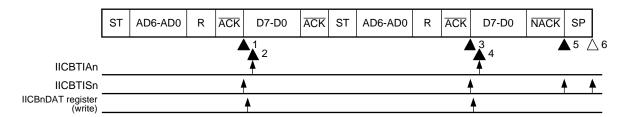

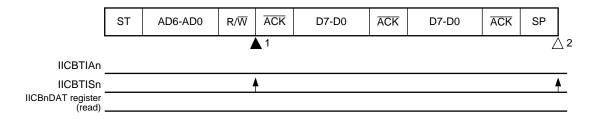

| 18.8.9    | Continuous Transfer Mode (Master Device Operation (Transmission))                                                                         | 88  |

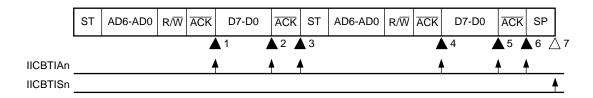

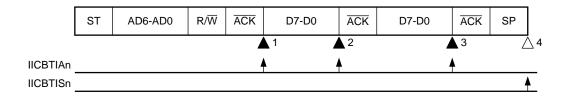

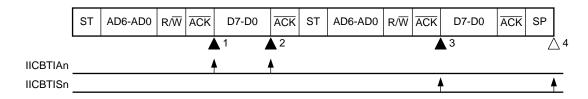

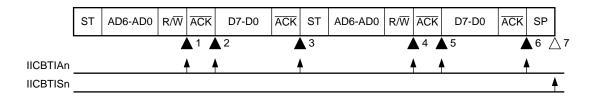

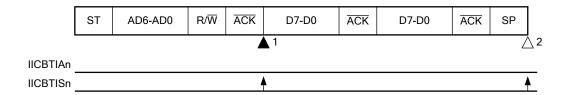

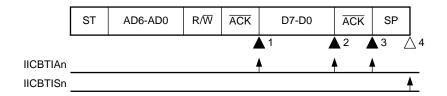

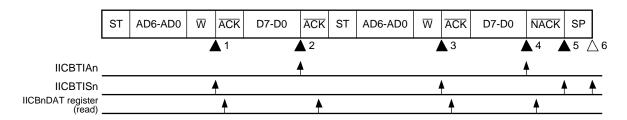

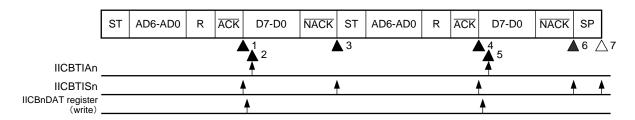

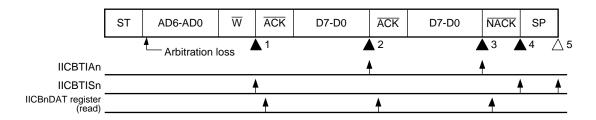

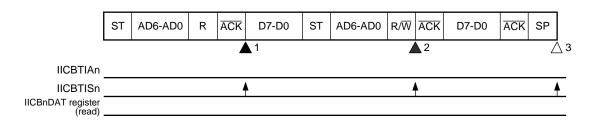

| 18.8.10   | Continuous Transfer Mode (Slave Device Operation (Reception): during Slave Address Reception (IICBnSTR0.IICBnSSC0 bit = 1))               | 91  |

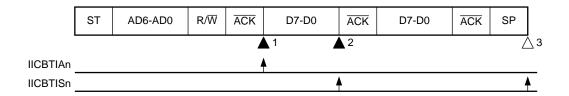

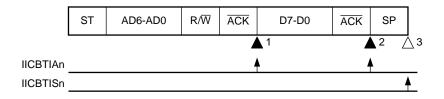

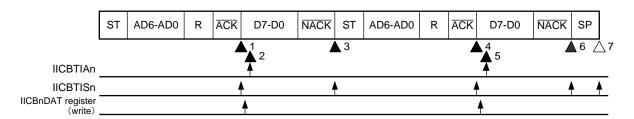

| 18.8.11   | Continuous Transfer Mode (Slave Device Operation (Reception): during Extension Code Reception (IICBnSTR0.IICBnSSEX bit = 1))              | 95  |

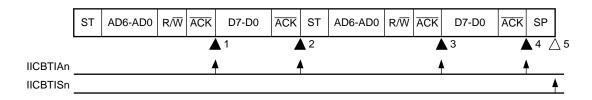

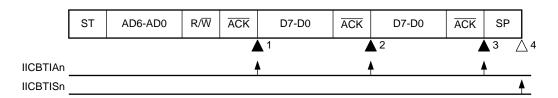

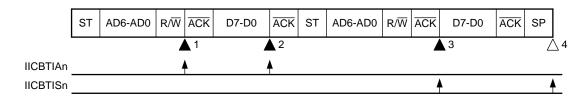

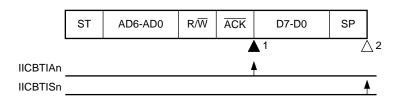

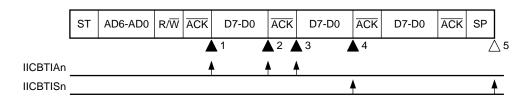

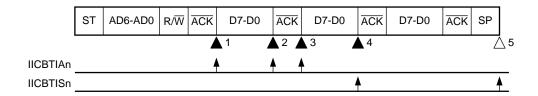

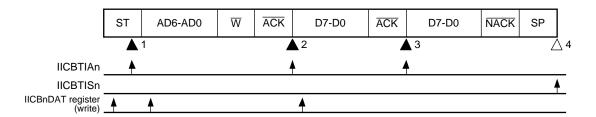

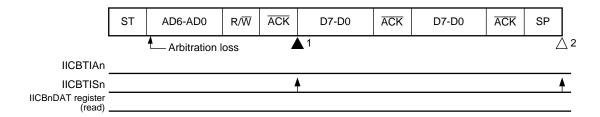

| 18.8.12   | Continuous Transfer Mode (Slave Device Operation (Transmission): during Slave Address Reception (IICBnSTR0.IICBnSSC0 bit = 1))            | 99  |

| 18.8.13   | Continuous Transfer Mode (Slave Device Operation (Transmission): during Extension Code Receptio (IICBnSTR0.IICBnSSEX bit = 1))            |     |

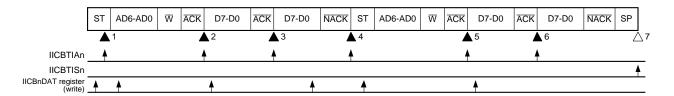

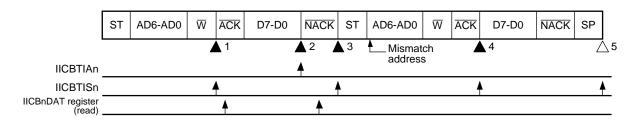

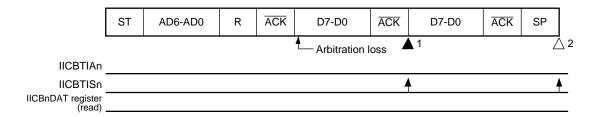

| 18.8.14   |                                                                                                                                           |     |

| 18.8.15   |                                                                                                                                           |     |

|           | address was transferred during reception): Operation as Slave after Arbitration Loss)                                                     | 08  |

| 18.8.16   | Continuous Transfer Mode (Arbitration Loss Operation (IICBnSTR0.IICBnALDF bit = 1) (when                                                  |     |

|           | address was transferred during reception): Non-Participation in Communications after Arbitration Los                                      |     |

| 18.8.17   | Continuous Transfer Mode (Arbitration Loss Operation (IICBnSTR0.IICBnALDF bit = 1) (when                                                  |     |

|           | address was transferred during reception): Non-Participation in Communications after Arbitration Los                                      | S   |

|           | (during Extension Code Transfer))                                                                                                         | 15  |

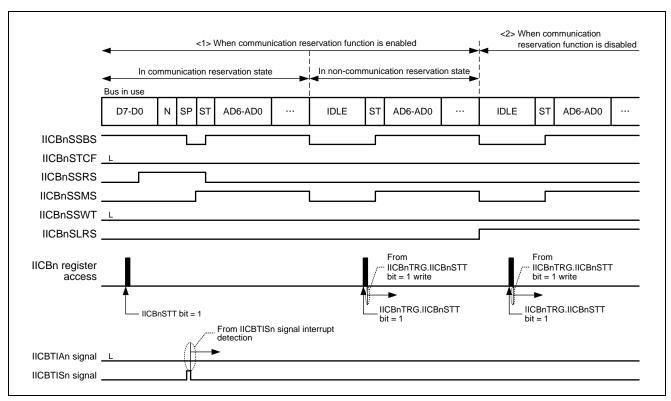

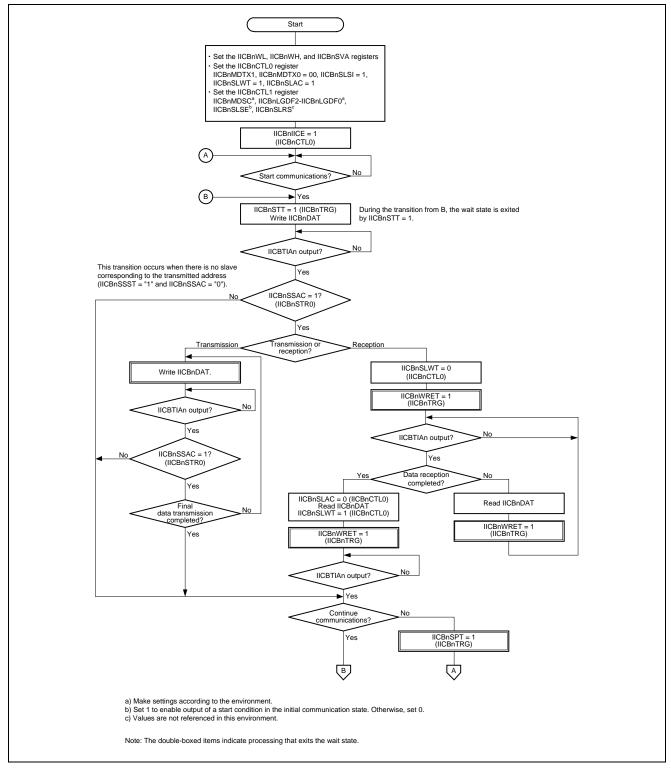

| 18.9 S    | etting Procedure                                                                                                                          | 17  |

| 18.9.1    | Single Master Environment                                                                                                                 | 17  |

| 18.9.2    | Multi-Master Environment                                                                                                                  | 21  |

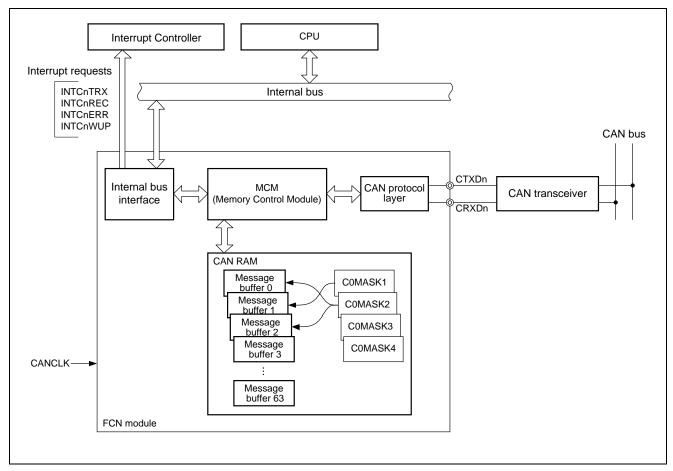

| 19. CAN C | ontroller (FCN)                                                                                                                           | )-1 |

| 19.1 F    | eatures of FCN                                                                                                                            | )-1 |

| 19.2 F    | eatures                                                                                                                                   | )-4 |

| 19.2.1    | Overview of Functions                                                                                                                     | )-5 |

| 19.2.2    | Configuration19                                                                                                                           | )-6 |

| 19.3 Ir   | nternal Registers of FCN                                                                                                                  | )-7 |

| 19.3.1    | CAN Controller Configuration                                                                                                              | )-7 |

| 19.3.2    | CAN Controller Registers Overview                                                                                                         | 9-9 |

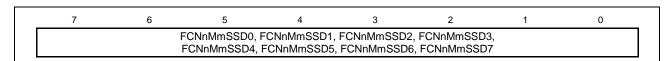

| 19.3.3    | Bit Configuration of Registers                        |        |

|-----------|-------------------------------------------------------|--------|

| 19.4 Set  | ting or Clearing of Bits                              | 19-19  |

| 19.5 Co   | ntrol Registers                                       | 19-21  |

| 19.5.1    | FCN Global Registers                                  | 19-21  |

| 19.5.2    | FCN Module Registers                                  | 19-30  |

| 19.5.3    | FCN Message Buffer Registers                          | 19-55  |

| 19.6 Ini  | tialization of CAN Controller                         | 19-67  |

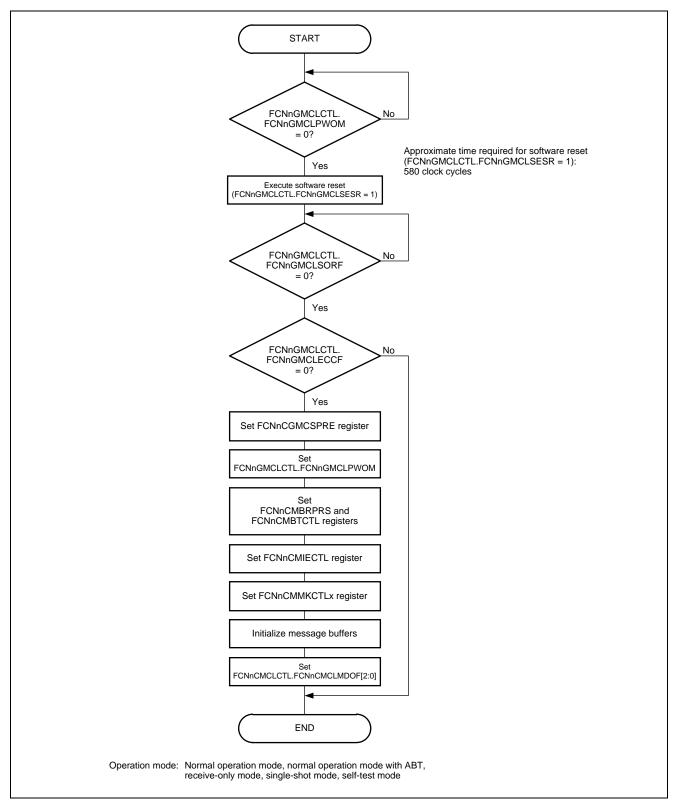

| 19.6.1    | Initialization of FCN Module                          | 19-67  |

| 19.6.2    | Initialization of Message Buffer                      | 19-67  |

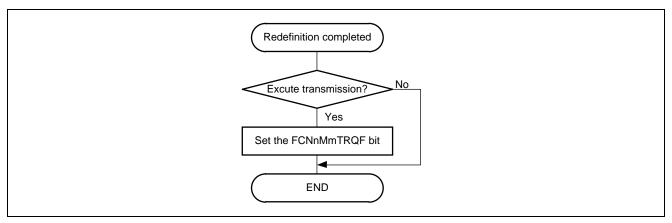

| 19.6.3    | Redefinition of Message Buffer                        | 19-67  |

| 19.6.4    | Transition from Initialization Mode to Operation Mode | 19-69  |

| 19.7 Me   | essage Reception                                      | 19-71  |

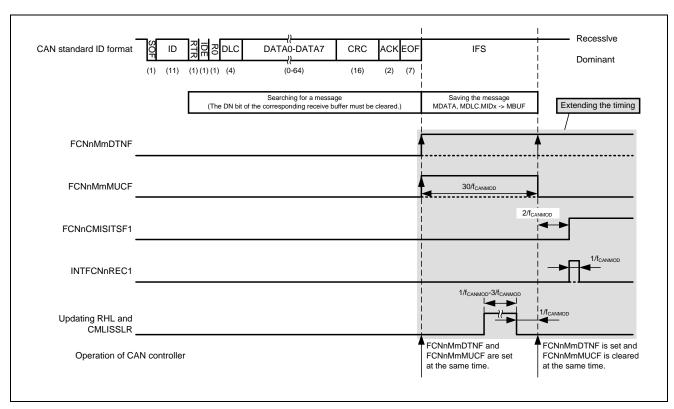

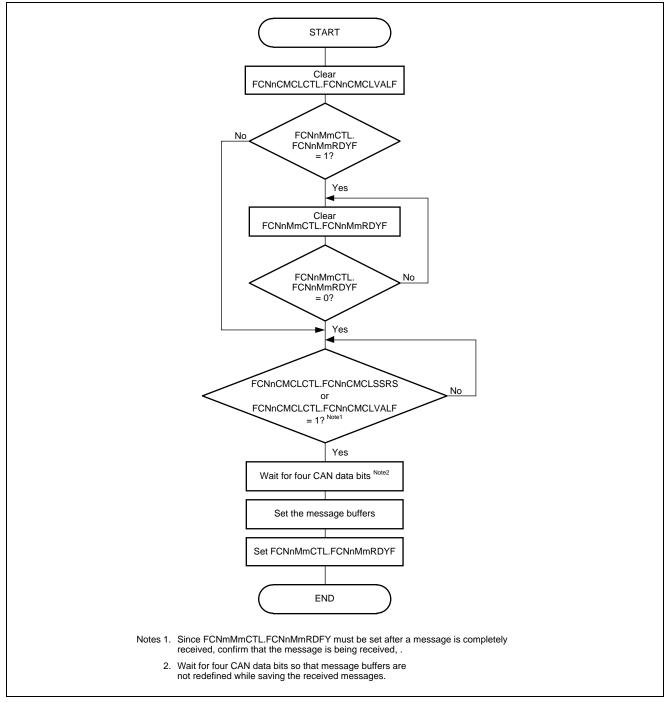

| 19.7.1    | Message Reception                                     | 19-71  |

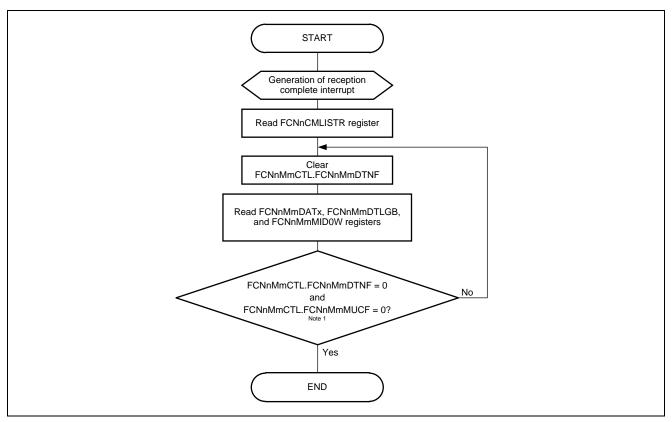

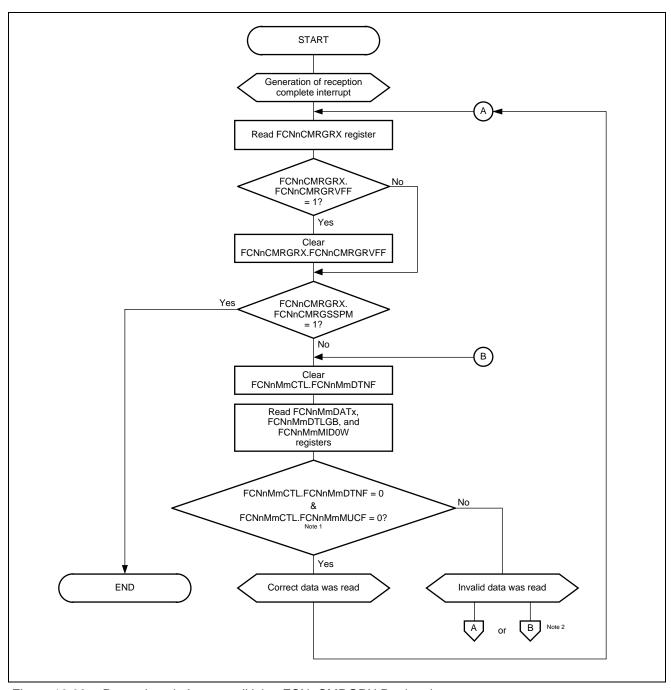

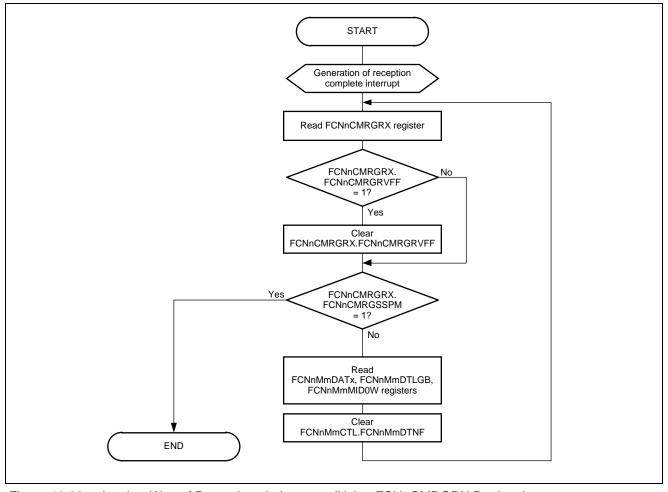

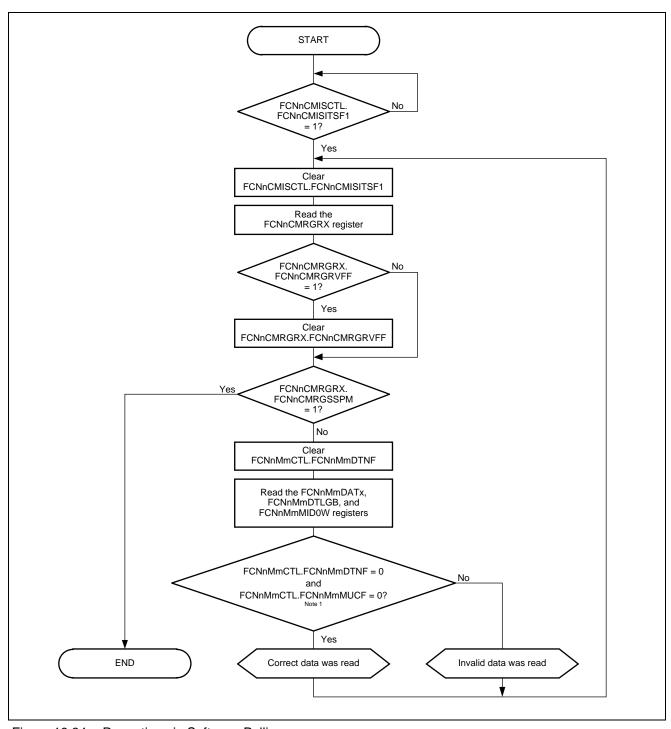

| 19.7.2    | Receive Data Read                                     | 19-72  |

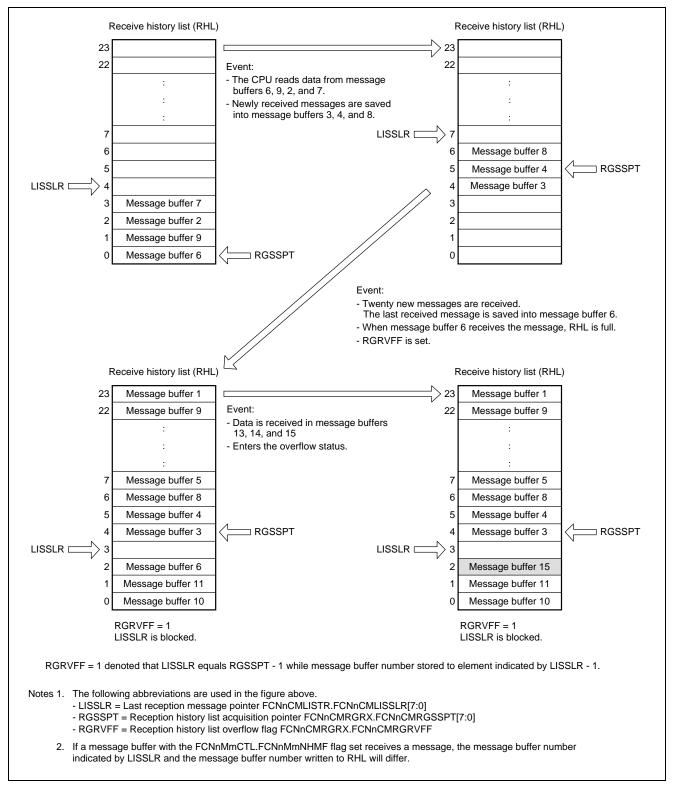

| 19.7.3    | Receive History List Function                         | 19-73  |

| 19.7.4    | Mask Function                                         | 19-75  |

| 19.7.5    | Multi-Buffer Reception Blocking                       | 19-76  |

| 19.7.6    | Remote Frame Reception                                | 19-77  |

| 19.8 Me   | essage Transmission                                   | 19-79  |

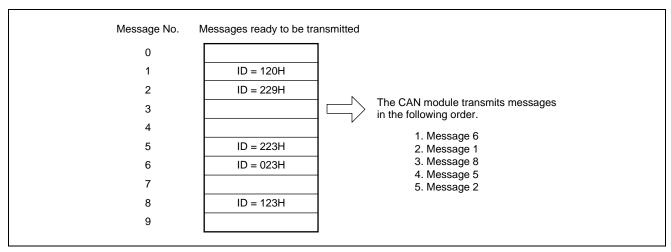

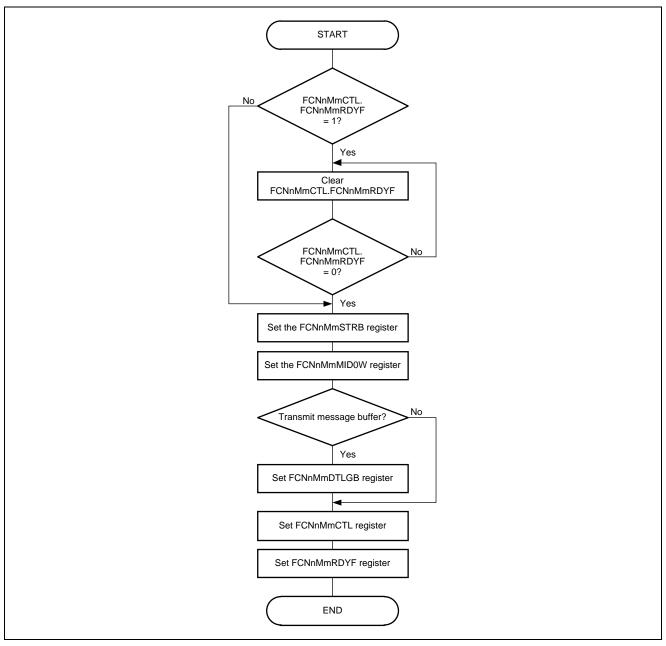

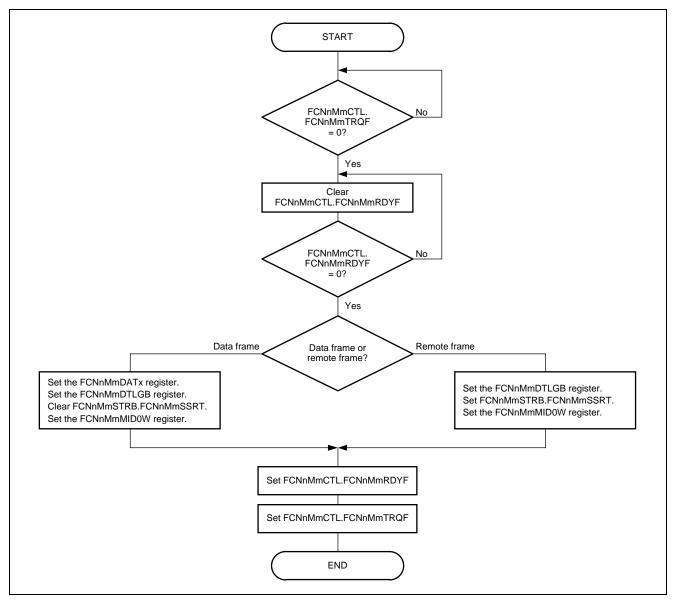

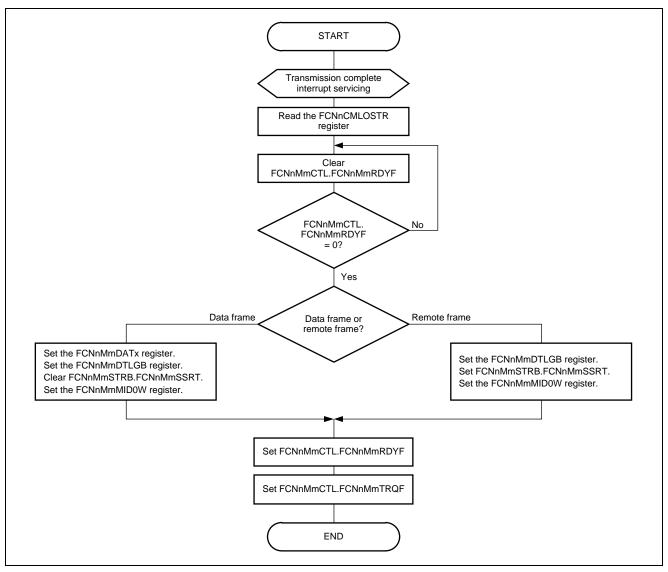

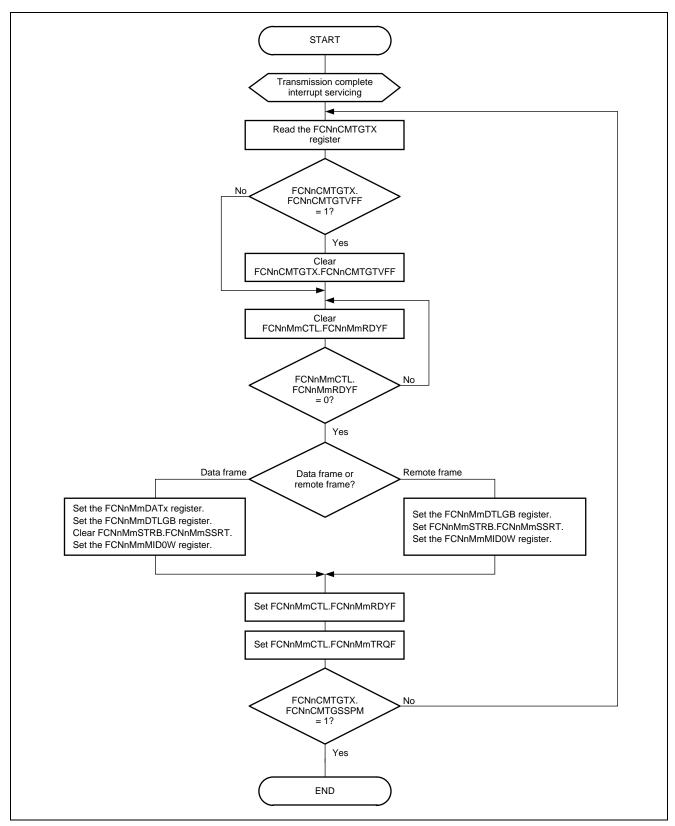

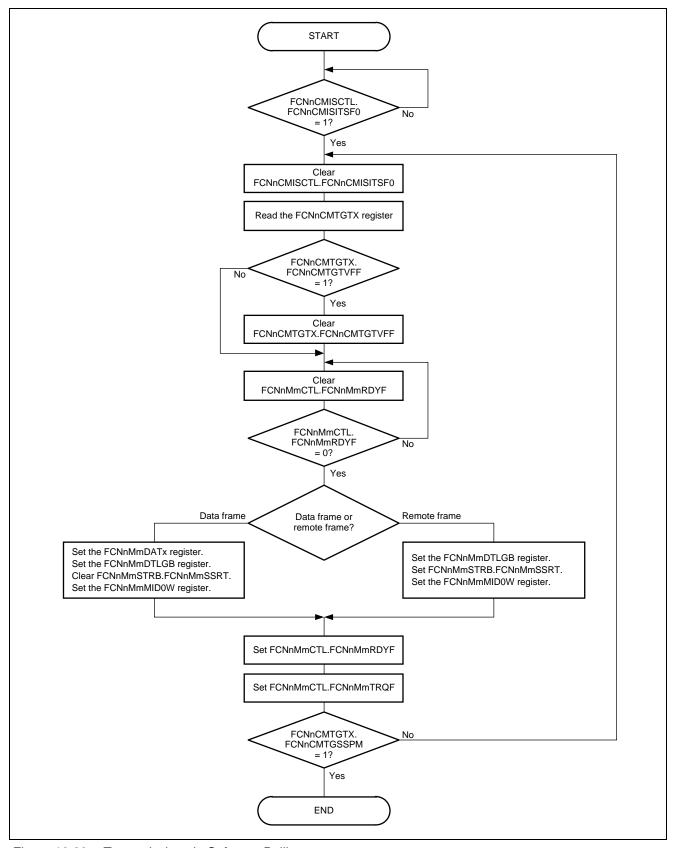

| 19.8.1    | Transmission of Messages                              | 19-79  |

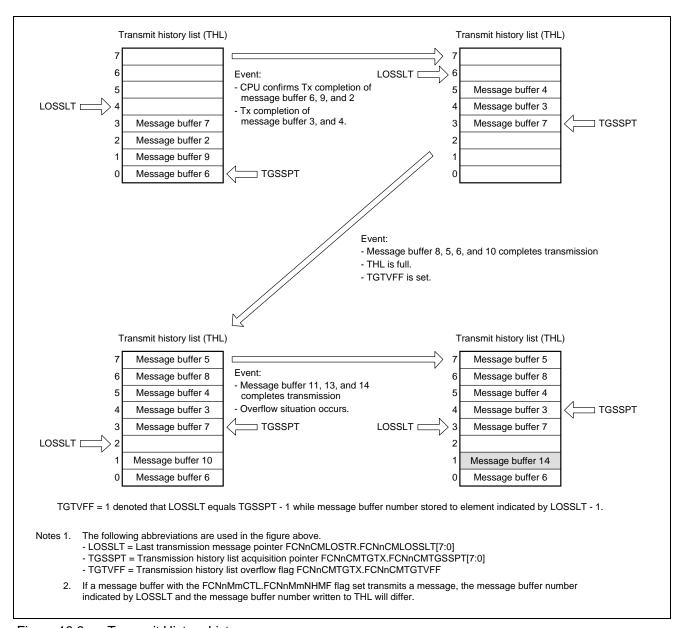

| 19.8.2    | Transmit History List Function                        | 19-81  |

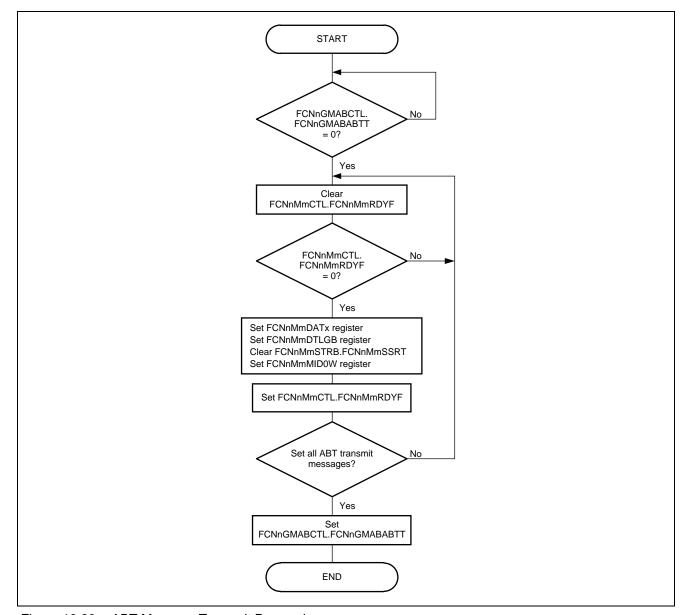

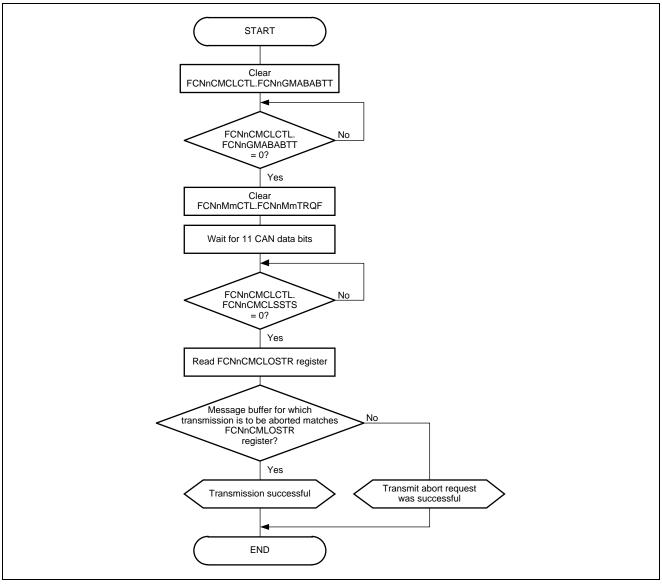

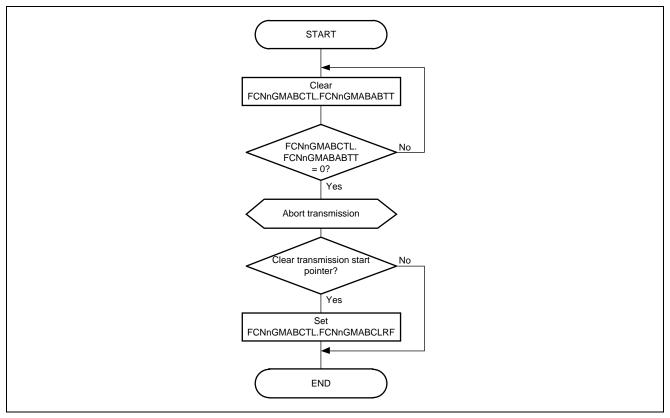

| 19.8.3    | Automatic Block Transmission (ABT)                    | 19-83  |

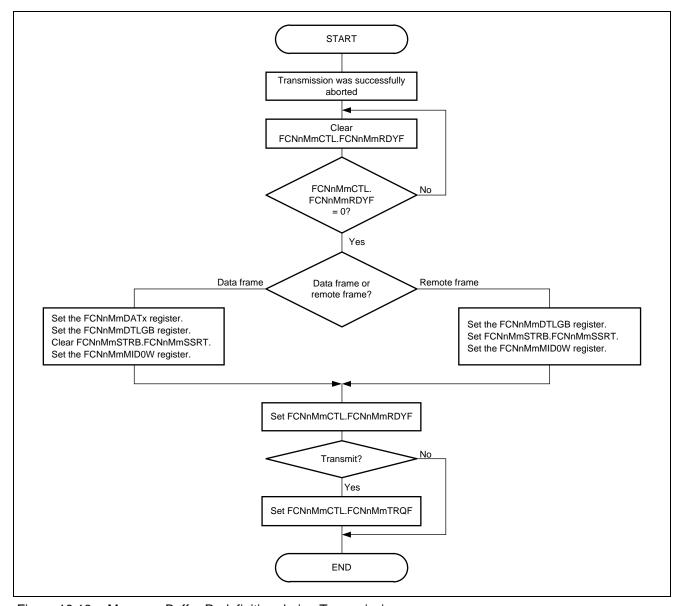

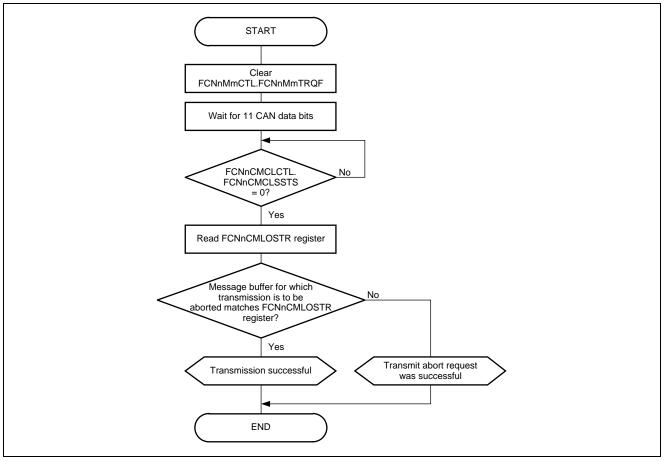

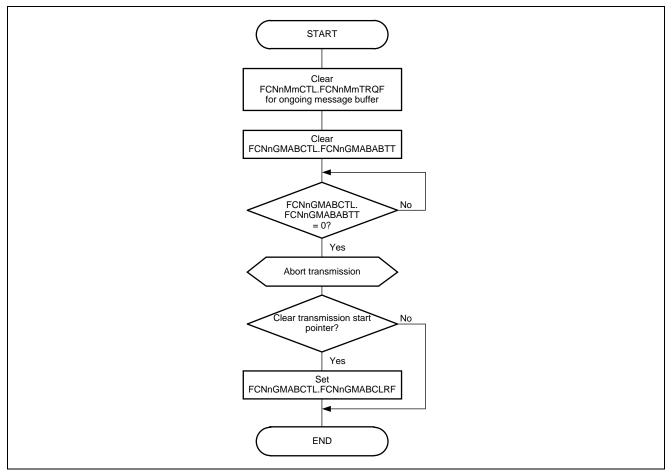

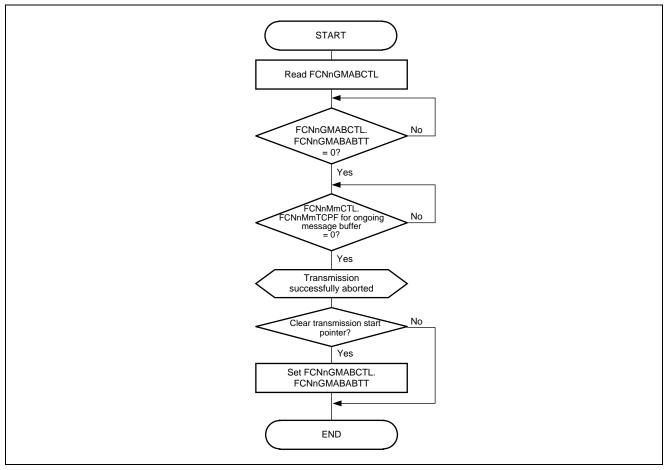

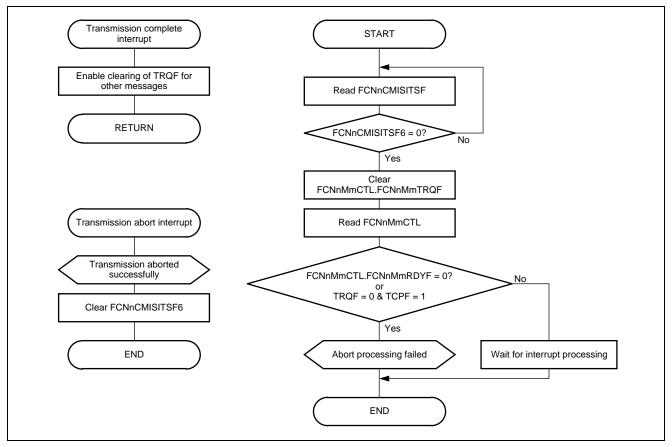

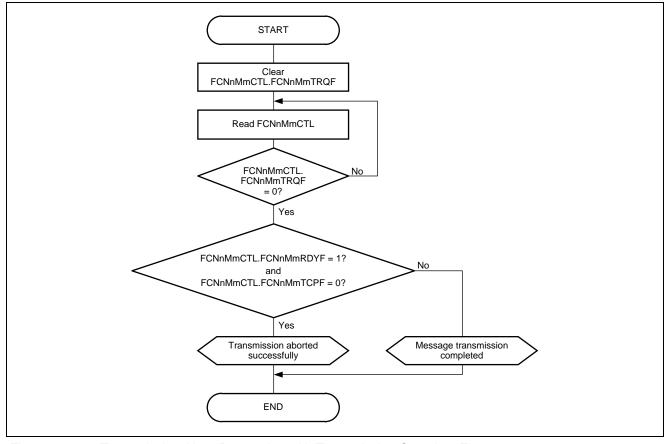

| 19.8.4    | Aborting Transmission                                 | 19-85  |

| 19.8.5    | Remote Frame Transmission                             | 19-86  |

| 19.9 Po   | wer Saving Modes                                      | 19-87  |

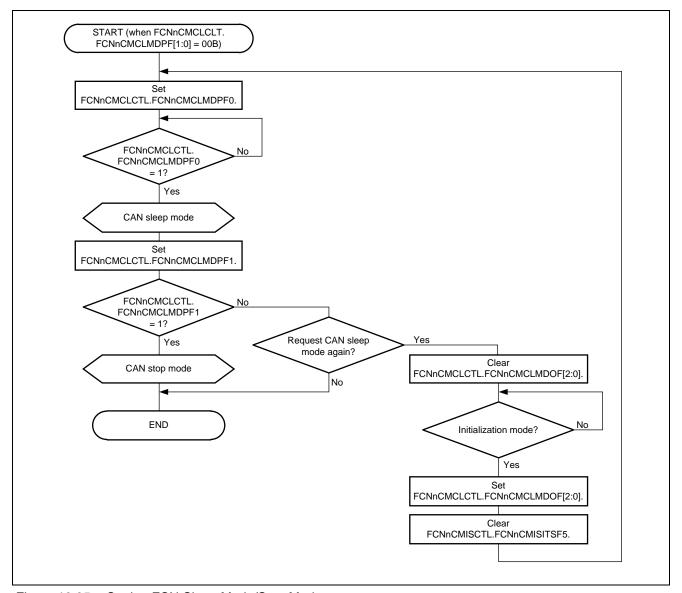

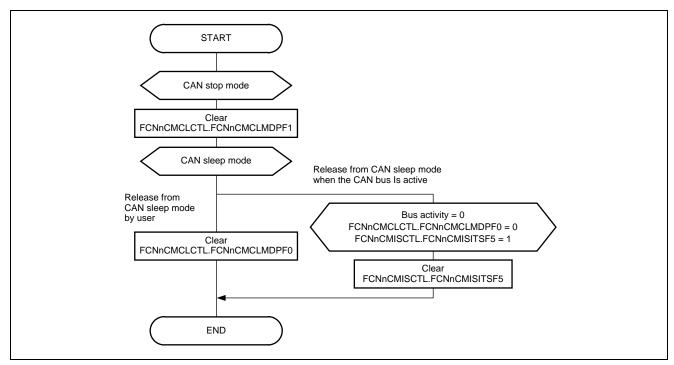

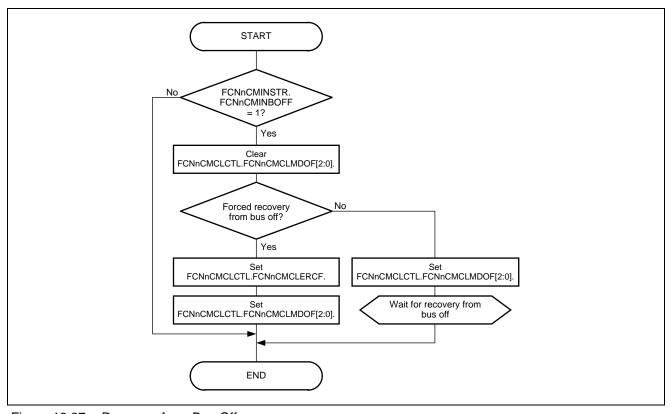

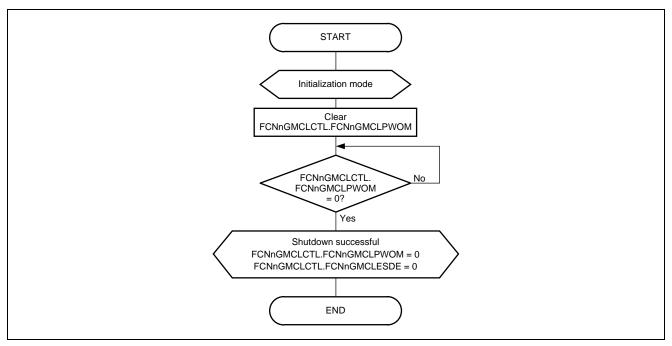

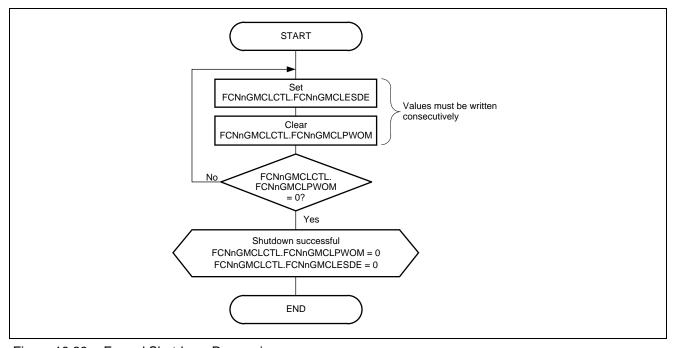

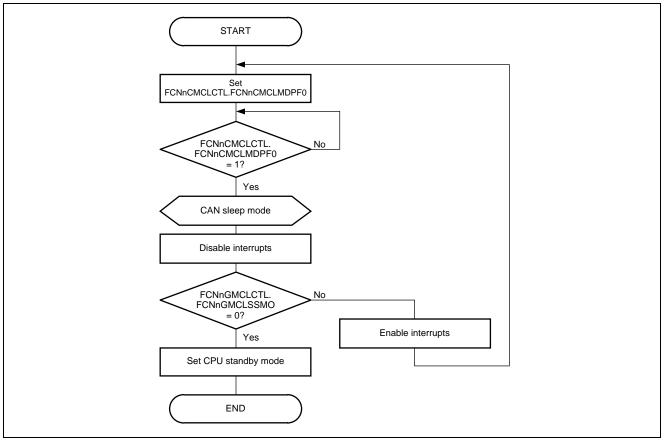

| 19.9.1    | FCN Sleep Mode                                        | 19-87  |

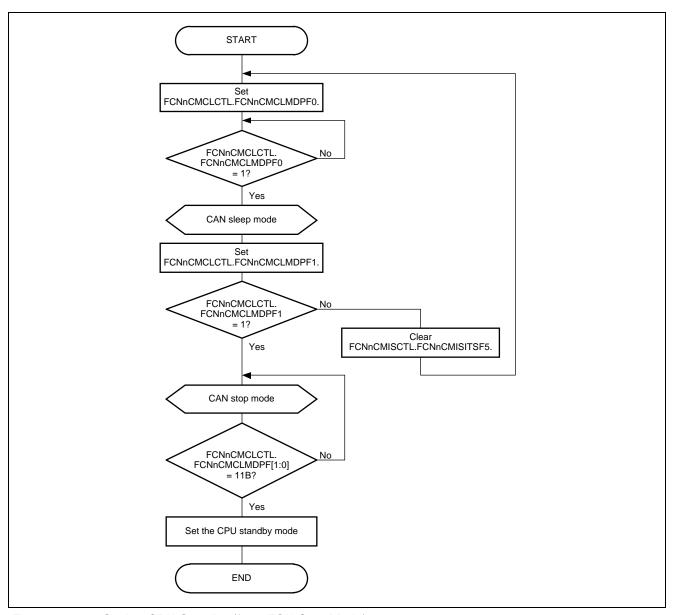

| 19.9.2    | FCN Stop Mode                                         | 19-90  |

| 19.9.3    | Example of Using Power Saving Mode                    | 19-91  |

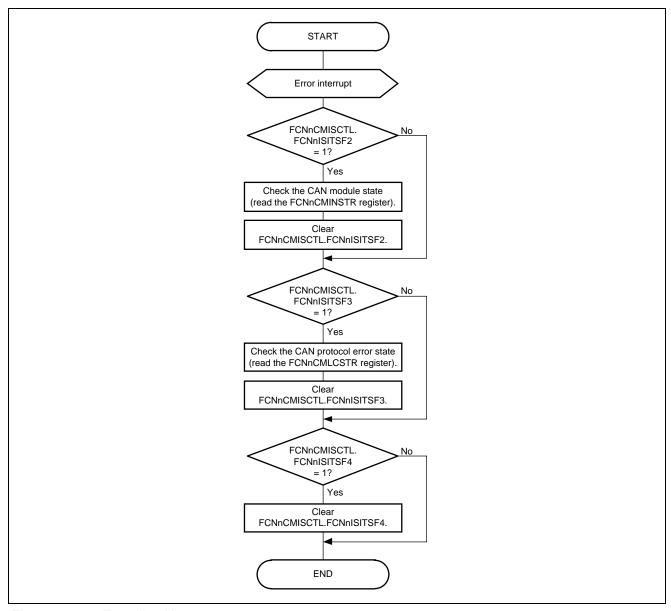

| 19.10 Int | errupts                                               | 19-92  |

| 19.11 Dia | agnosis and Special Operation Modes                   | 19-93  |

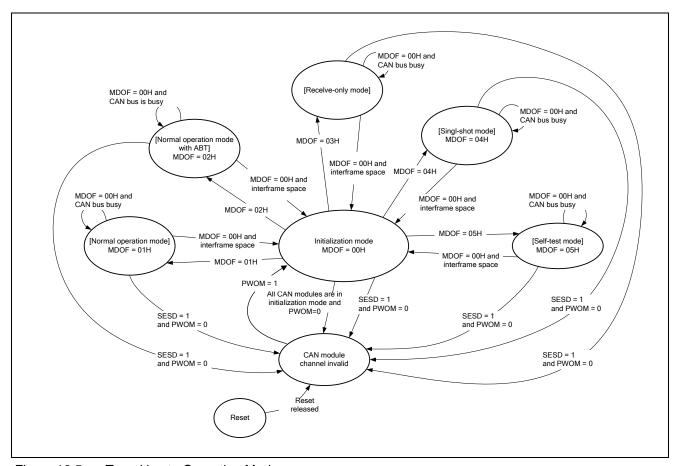

| 19.11.1   | Receive-Only Mode                                     | 19-93  |

| 19.11.2   | Single-Shot Mode                                      | 19-94  |

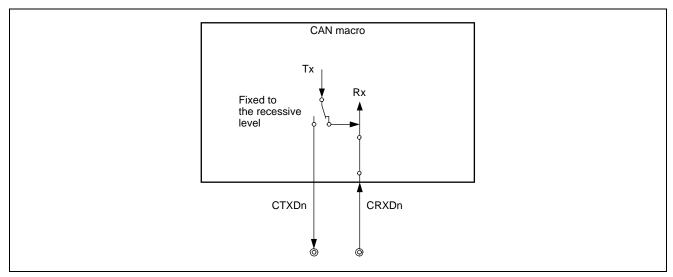

| 19.11.3   | Self-Test Mode                                        | 19-95  |

| 19.11.4   | Receive/Transmit Operation in Each Operation Mode     | 19-96  |

| 19.12 Tir | nestamping                                            | 19-97  |

| 19.12.1   | Timestamping                                          | 19-97  |

| 19.13 Ba  | ud Rate Settings                                      | 19-99  |

| 19.13.1   | Baud Rate Setting Conditions                          | 19-99  |

| 19.13.2   | Representative Examples of Baud Rate Settings         | 19-103 |

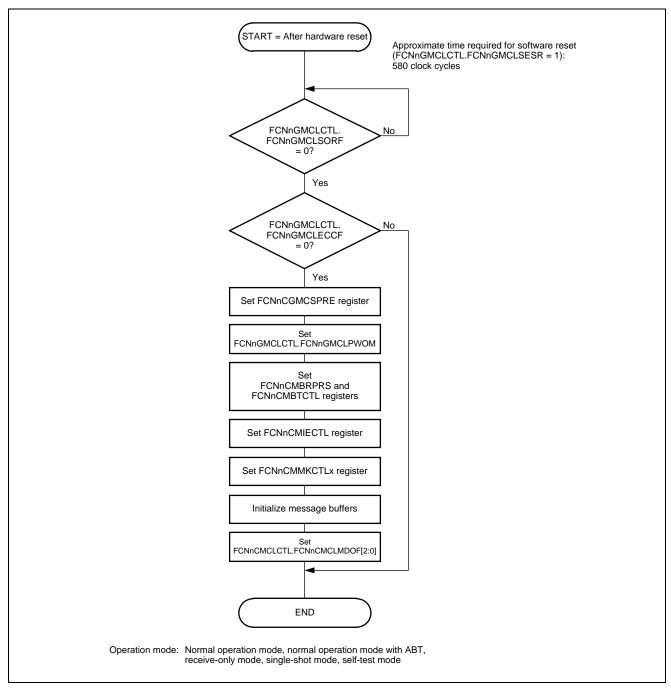

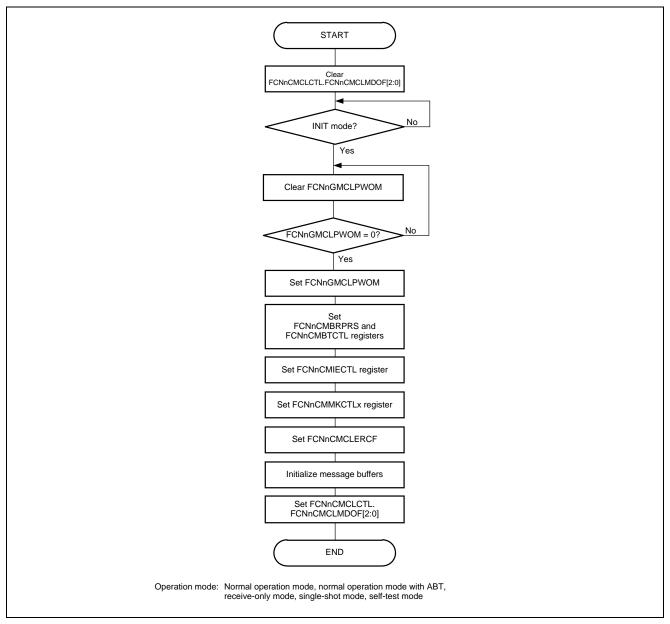

| 19.14   | Ope     | ration of the CAN Controller                                 | 19-105 |

|---------|---------|--------------------------------------------------------------|--------|

| 19.1    | 14.1    | Initialization                                               | 19-105 |

| 19.1    | 14.2    | Message Transmission                                         | 19-111 |

| 19.1    | 14.3    | Message Reception                                            | 19-125 |

| 19.1    | 14.4    | Power Safe Mode                                              | 19-131 |

| 20. CC- | -Link I | nterface                                                     | 20-1   |

| 20.1    | Reg     | isters                                                       | 20-1   |

| 20.1    | 1.1     | List of Registers                                            | 20-1   |

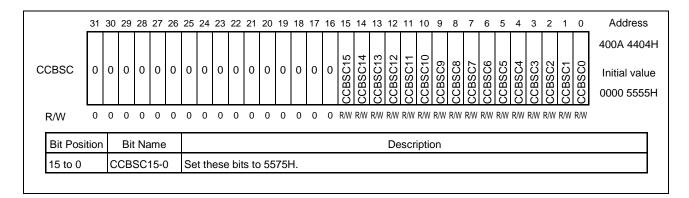

| 20.1    | 1.2     | CC-Link Bus Size Control Register (CCBSC)                    | 20-2   |

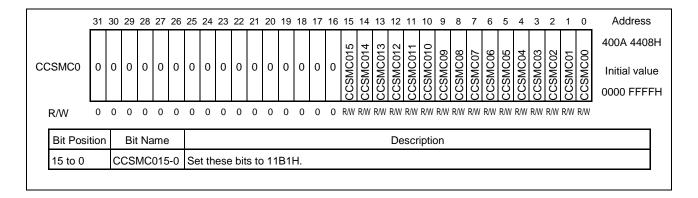

| 20.1    | 1.3     | CC-Link Bus Bridge Control Register 0 (CCSMC0)               | 20-2   |

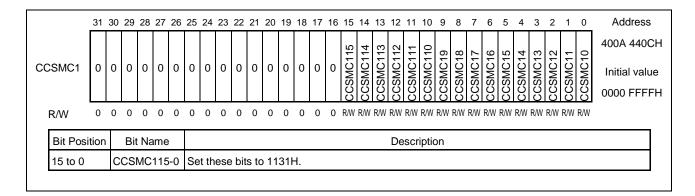

| 20.1    | 1.4     | CC-Link Bus Bridge Control Register 1 (CCSMC1)               | 20-3   |

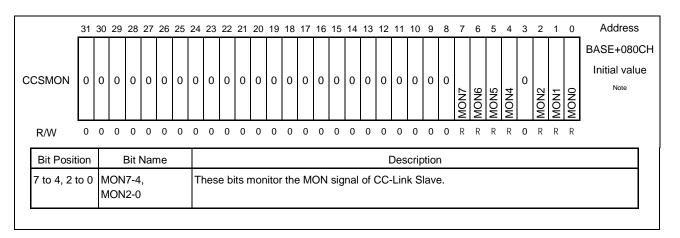

| 20.1    | 1.5     | CC-Link Monitor Register (CCSMON)                            | 20-3   |

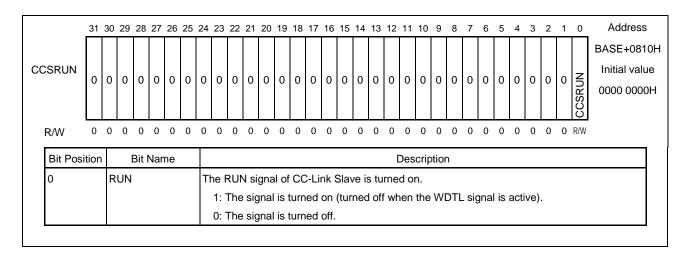

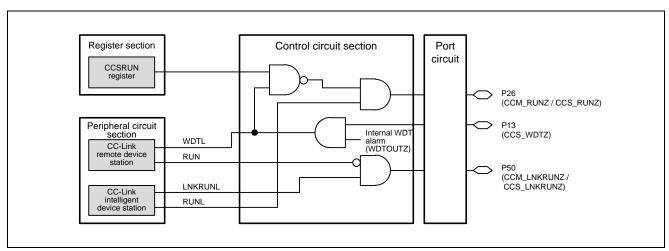

| 20.1    | 1.6     | CC-Link Slave RUN LED Control Register (CCSRUN)              | 20-4   |

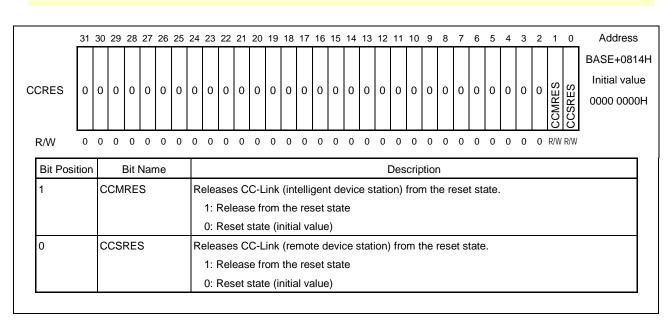

| 20.1    | 1.7     | CC-Link Reset Register (CCRES)                               | 20-5   |

| 20.1    | 1.8     | CC-Link Slave Operating Mode Setting Register (CCSMD)        | 20-6   |

| 21. Sys | stem R  | Registers (APB Peripheral Registers Area)                    | 21-1   |

| 21.1    | List    | of Registers                                                 | 21-1   |

| 21.2    | Ope     | erating Mode Monitor Register (MDMNT)                        | 21-3   |

| 21.3    | IDC     | CODE Register (IDCODE)                                       | 21-3   |

| 21.4    | Ver     | sion Register (RINVER)                                       | 21-4   |

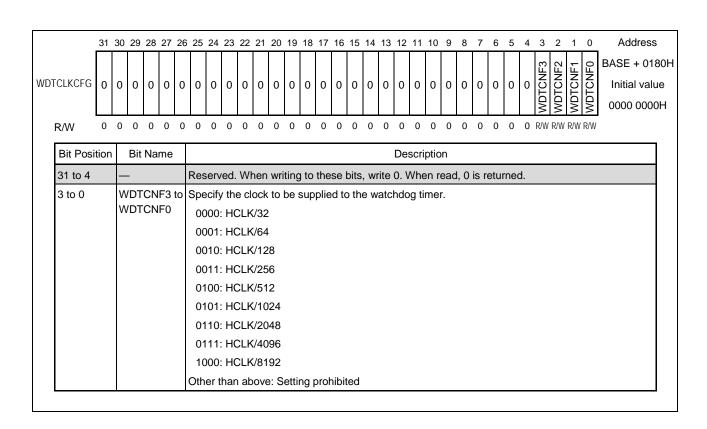

| 21.5    | Wat     | cchdog Timer Input Clock Selection Register (WDTCLKCFG)      | 21-5   |

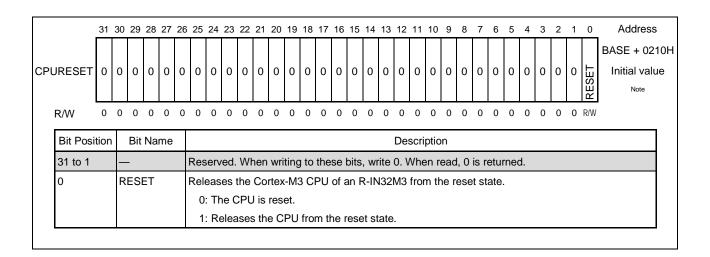

| 21.6    | CPU     | JRESET Register (CPURESET)                                   | 21-6   |

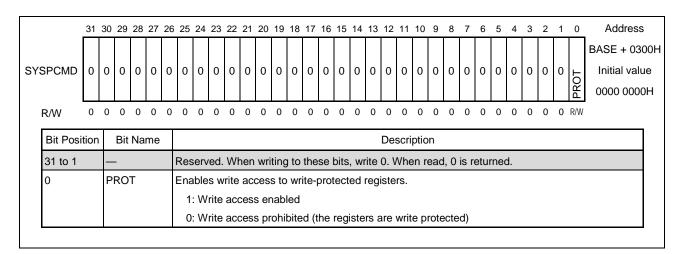

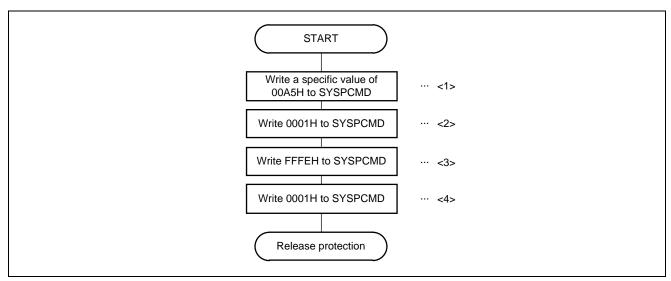

| 21.7    | Syst    | tem Protect Command Register (SYSPCMD)                       | 21-7   |

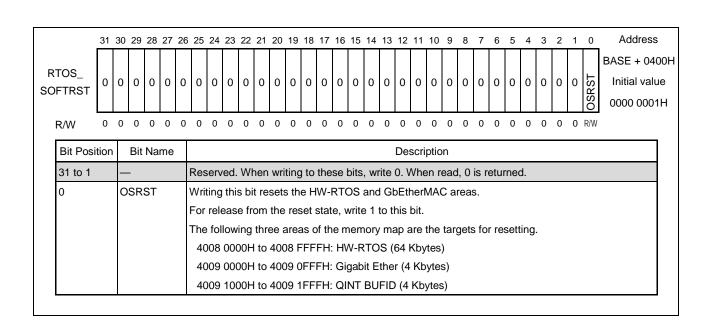

| 21.8    | HW      | -RTOS Reset Register (RTOS_SOFTRST)                          | 21-8   |

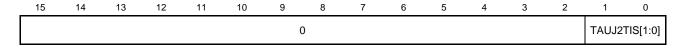

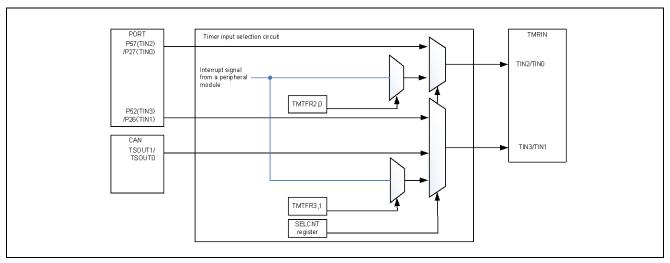

| 21.9    | Tim     | er Input Selection                                           | 21-9   |

| 21.9    | 9.1     | Timer Input Function Selection Register (SELCNT)             | 21-10  |

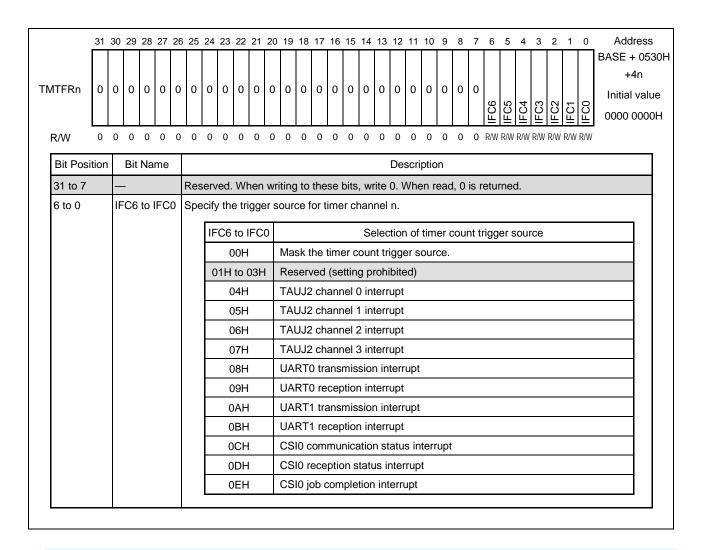

| 21.9    | 9.2     | Timer Trigger Source Registers (TMTFR0 to TMTFR03)           | 21-12  |

| 21.10   | Noi     | se Eliminator                                                | 21-16  |

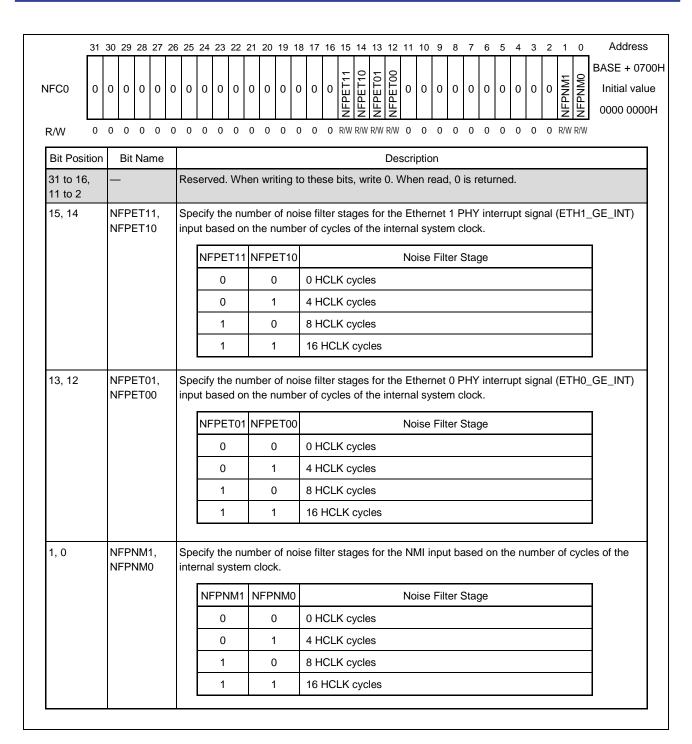

| 21.1    | 10.1    | Noise Filter Setting Registers 0 to 3 (NFC0 to NFC3)         | 21-16  |

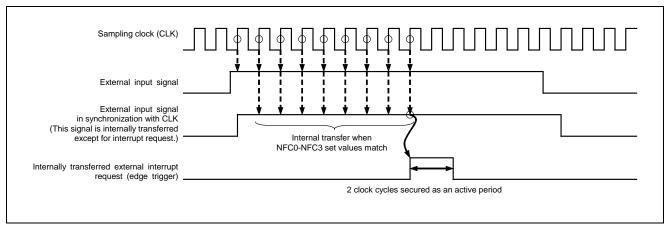

| 21.1    | 10.2    | Noise Filtering Operation                                    | 21-20  |

| 21.11   | Exte    | ernal Interrupt Mode Registers 0, 1, 2 (INTM0, INTM1, INTM2) | 21-21  |

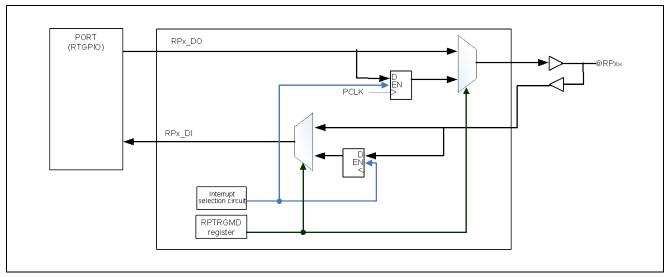

| 21.12   | Trig    | ger-Synchronous Ports                                        | 21-24  |

| 21.1    | 12.1    | Trigger-Synchronous Port Control Mode Register (RPTRGMD)     | 21-25  |

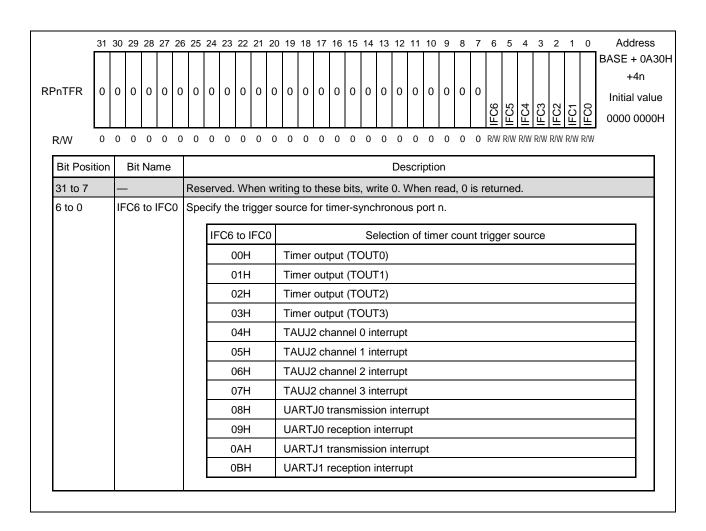

| 21.1    | 12.2    | Trigger-Synchronous Port Source Registers (RP0TFR to RP3TFR) | 21-26  |

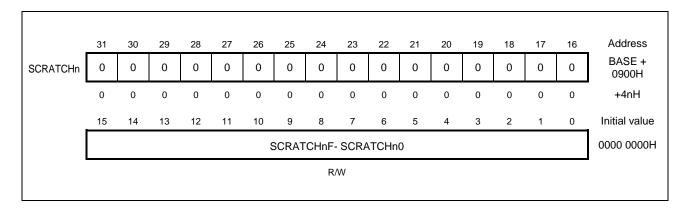

| 21.13   | Scra    | atch Registers (SCRATCH0 to SCRATCHD)                        | 21-30  |

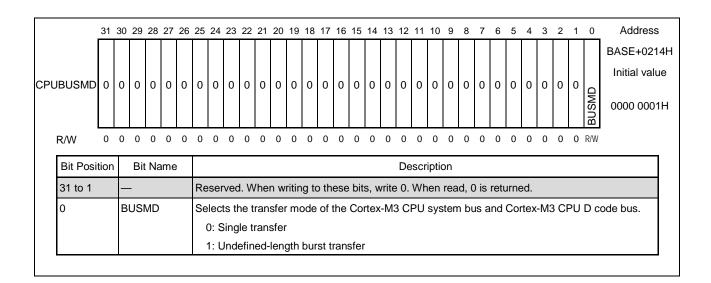

| 21.14   | CPU     | J Bus Operating Mode Register (CPUBUSMD)                     | 21-31  |

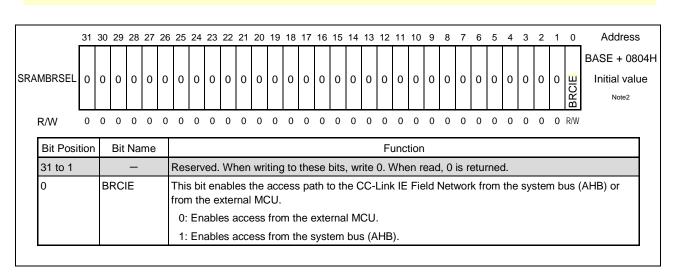

| 21.15   | SRA     | AM Bridge Select Register (SRAMBRSEL)                        | 21-32  |

| 22. Deb | ugging               | 22-1 |

|---------|----------------------|------|

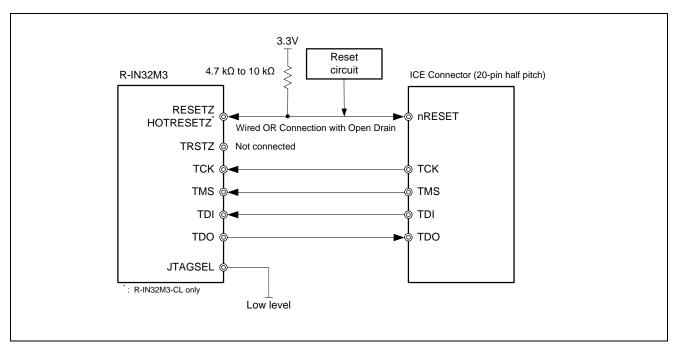

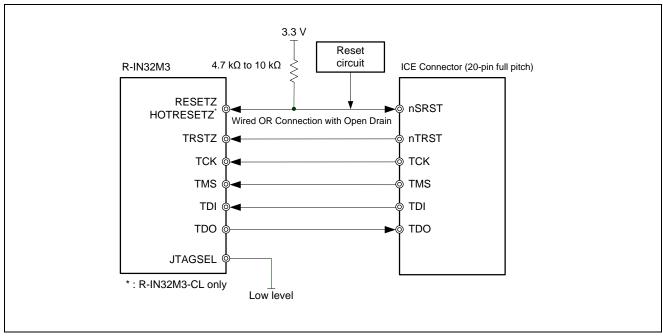

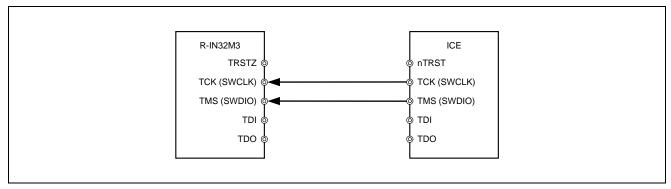

| 22.1    | JTAG Interface       | 22-1 |

| 22.2    | SWD Interface        | 22-4 |

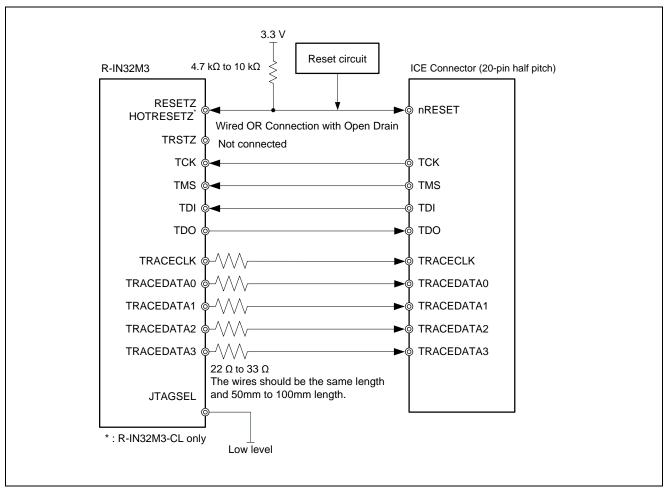

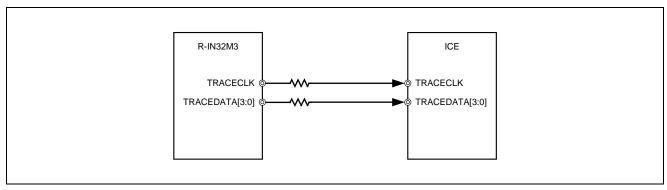

| 22.3    | Trace Port Interface | 22-4 |

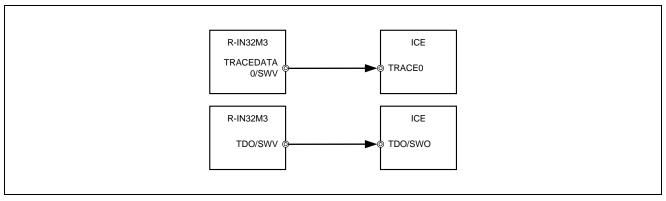

| 22.4    | SWV Interface        | 22-5 |

# List of Figures

| Figure 2.1  | Clock Configuration Diagram                                                                | 2-2     |

|-------------|--------------------------------------------------------------------------------------------|---------|

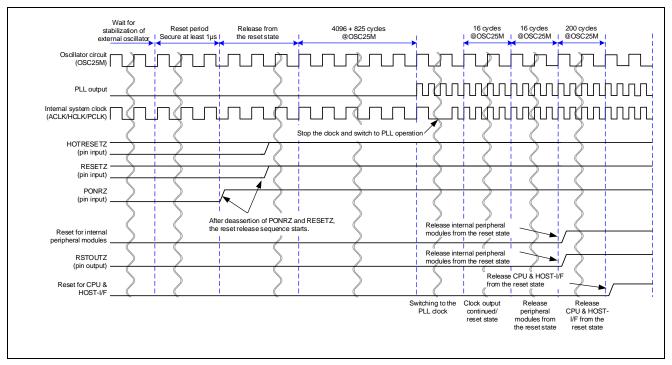

| Figure 2.2  | Timing of Reset at Power On <r></r>                                                        | 2-9     |

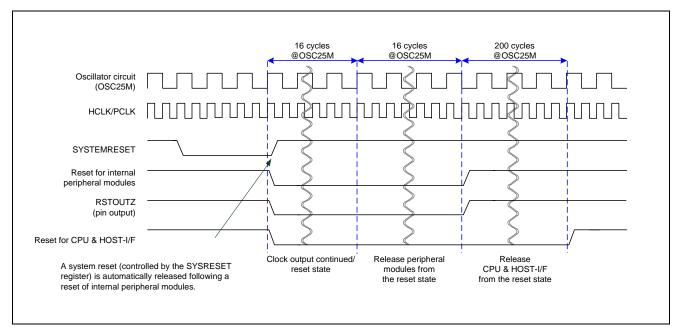

| Figure 2.3  | Timing of Reset at System Reset <r></r>                                                    | 2-9     |

| Figure 6.1  | Overall Structure of Hardware Real-Time OS (HW-RTOS)                                       | 6-3     |

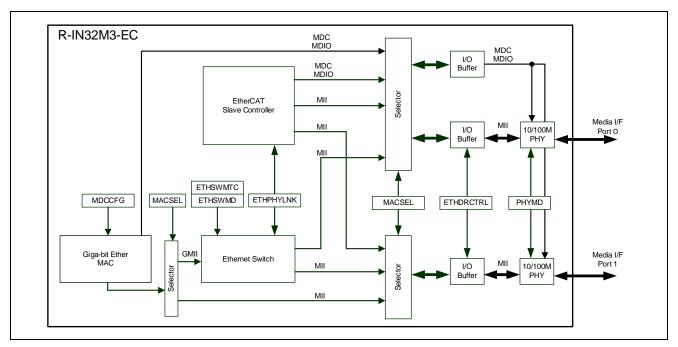

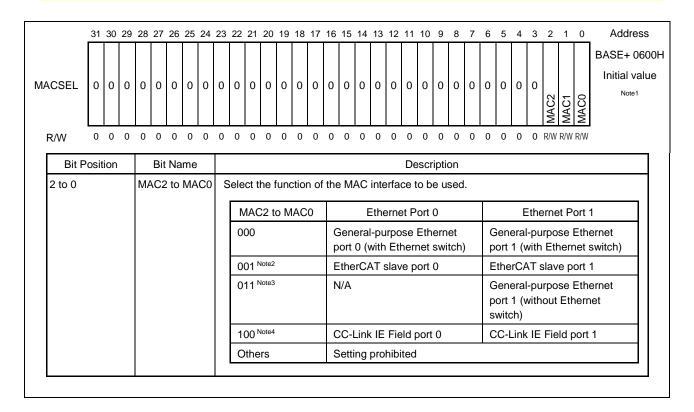

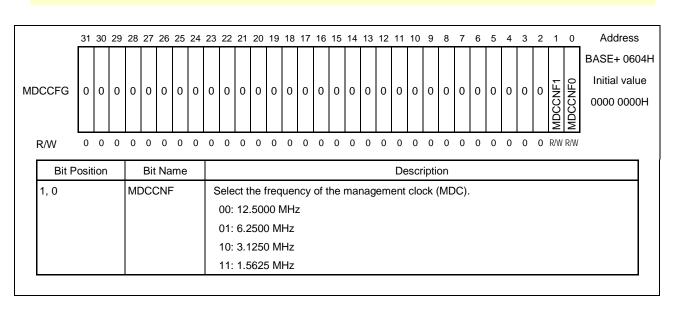

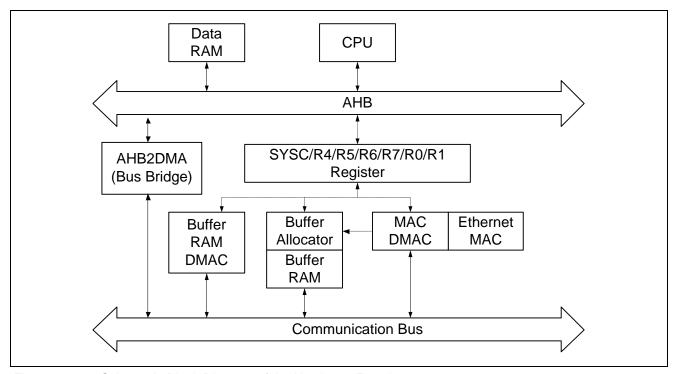

| Figure 7.1  | Ethernet Interface Peripheral Architecture (R-IN32M3-EC)                                   | 7-2     |

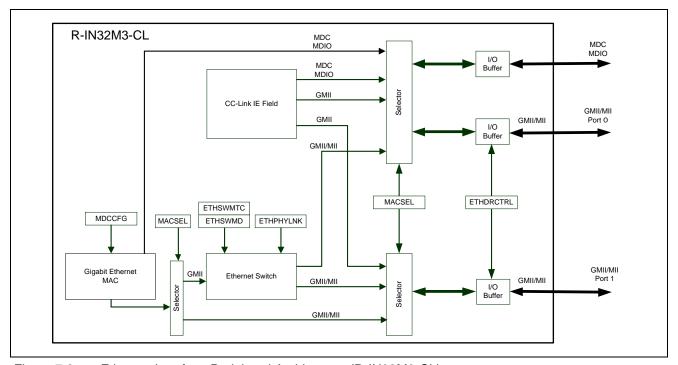

| Figure 7.2  | Ethernet Interface Peripheral Architecture (R-IN32M3-CL)                                   | 7-2     |

| Figure 7.3  | Schematic Block Diagram of the Hardware Functions                                          | 7-31    |

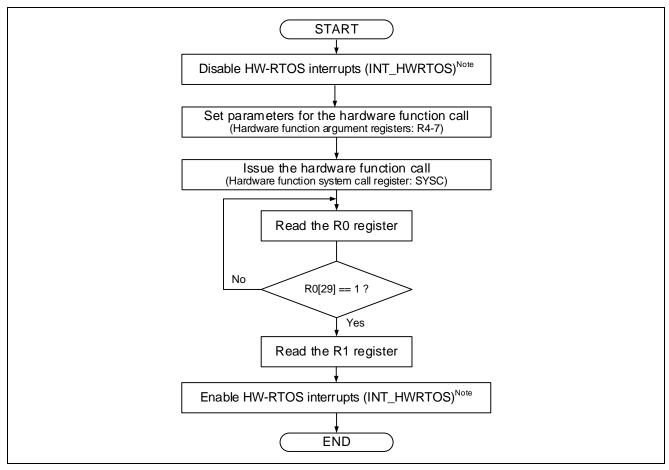

| Figure 7.4  | Flow of Processing for Issuing the Hardware Function <r></r>                               | 7-33    |

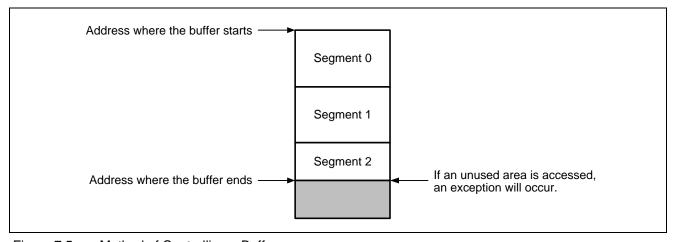

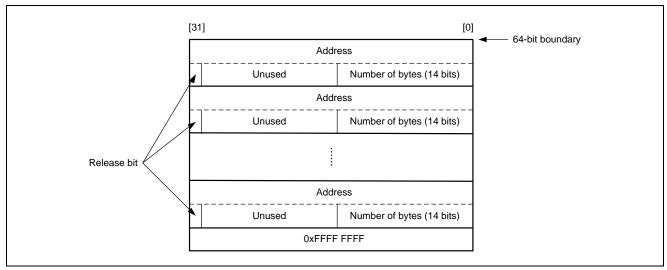

| Figure 7.5  | Method of Controlling a Buffer                                                             | 7-34    |

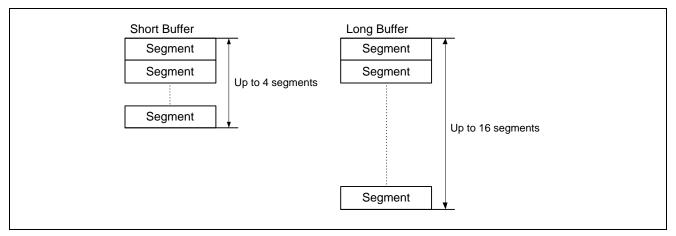

| Figure 7.6  | Buffer Structure                                                                           | 7-35    |

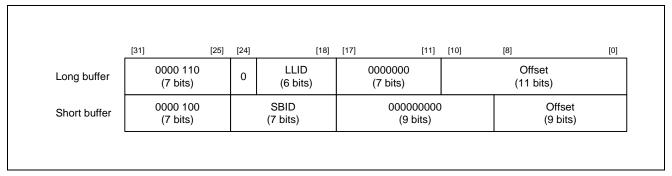

| Figure 7.7  | Address Structure of Buffers                                                               | 7-36    |

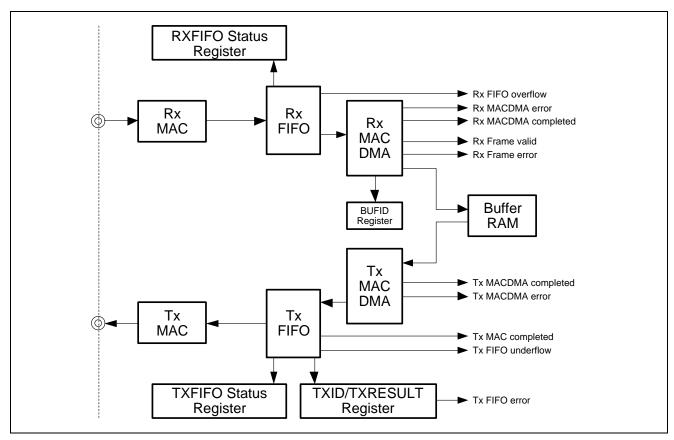

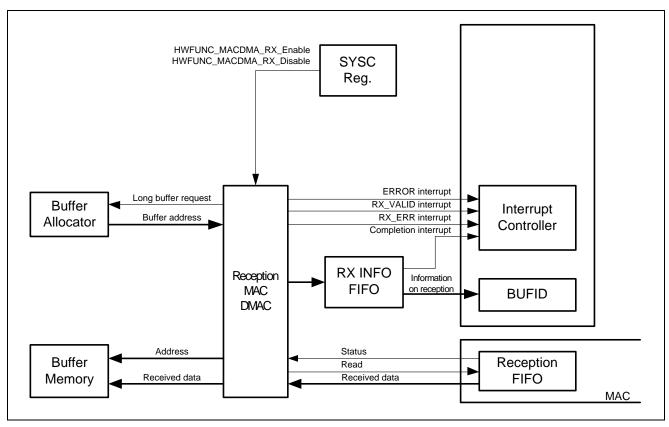

| Figure 7.8  | Block Diagram of the MACDMAC in Context and Interrupt Signals                              | 7-41    |

| Figure 7.9  | Outline of Processing by the Reception MACDMAC                                             | 7-42    |

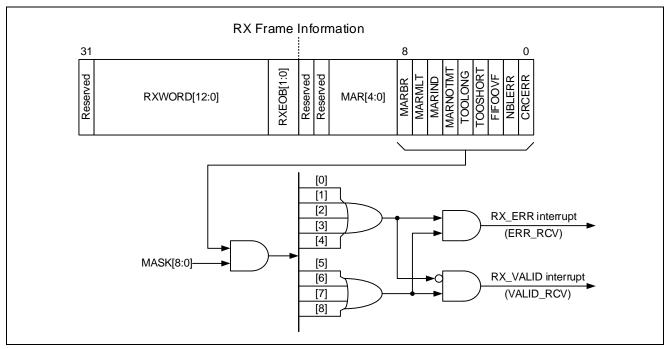

| Figure 7.10 | Conceptual Diagram of Judging Whether a Received Frame is Valid or Invalid                 | 7-44    |

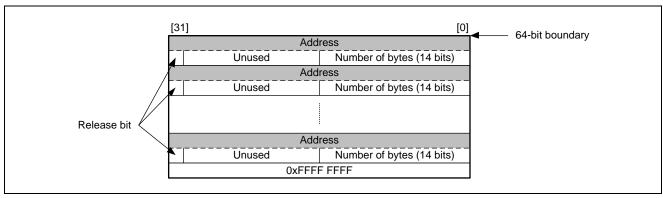

| Figure 7.11 | Transmission Descriptor                                                                    | 7-49    |

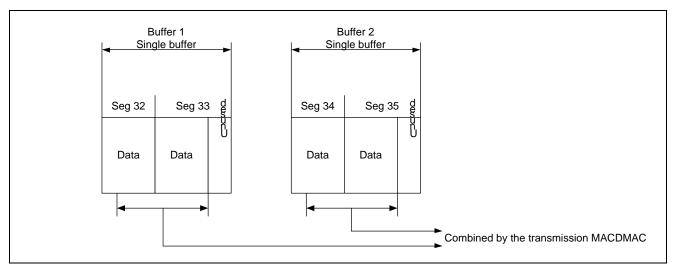

| Figure 7.12 | Example of Transmission as One Frame by Combining Multiple Buffers                         | 7-50    |

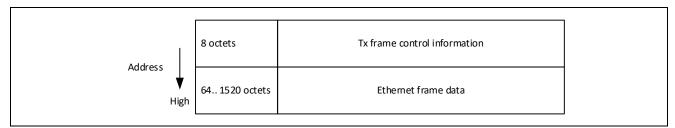

| Figure 7.13 | TX Data Format                                                                             | 7-63    |

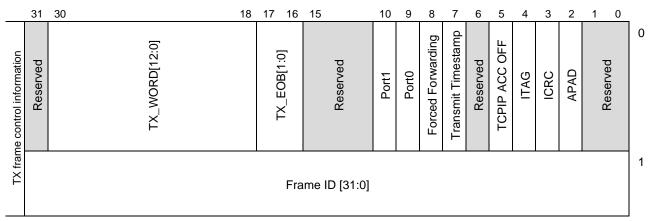

| Figure 7.14 | Tx Frame Control Information Format                                                        | 7-64    |

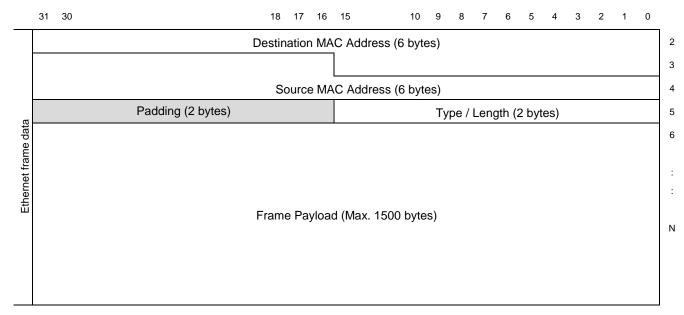

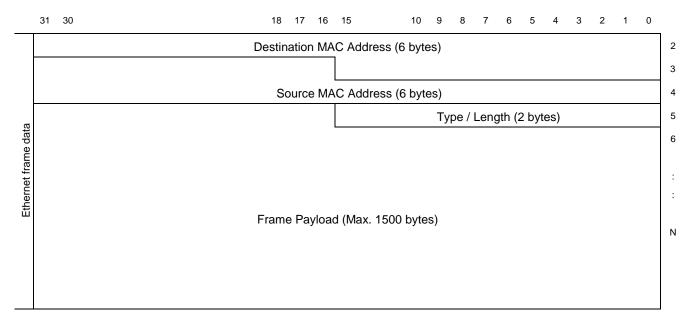

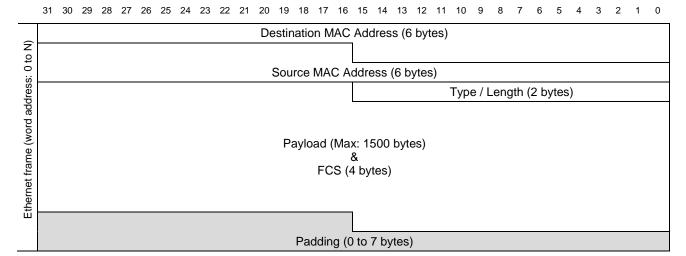

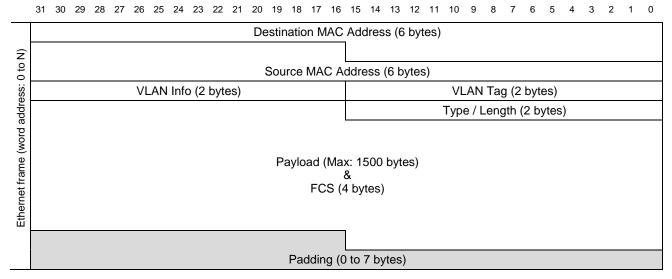

| Figure 7.15 | Tx Ethernet Frame Data Format – TCPIPACC is enabled, without VLAN tag                      | 7-67    |

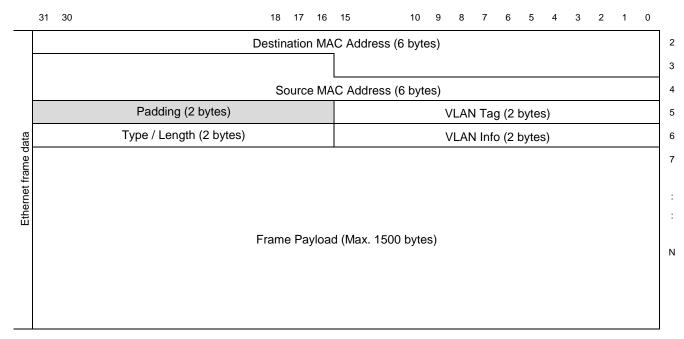

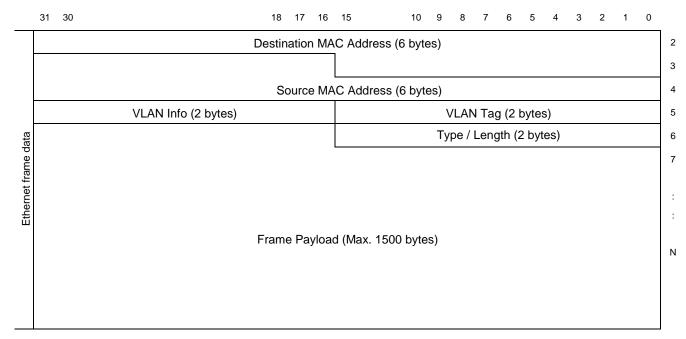

| Figure 7.16 | Tx Ethernet Frame Data Format – TCPIPACC is enabled, with VLAN tag                         | 7-67    |

| Figure 7.17 | Tx Ethernet Frame Data Format – TCPIPACC is disabled, without VLAN tag                     | 7-68    |

| Figure 7.18 | Tx Ethernet Frame Data Format – TCPIPACC is disabled, with VLAN tag                        | 7-68    |

| Figure 7.19 | Structure of the TX Descriptor                                                             | 7-69    |

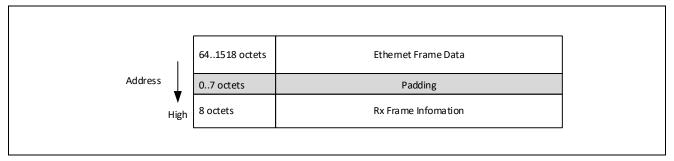

| Figure 7.20 | Rx Data Format                                                                             | 7-72    |

| Figure 7.21 | Rx frame Information                                                                       | 7-73    |

| Figure 7.22 | Destination MAC Address Field (when insertion of management tag is permitted)              | 7-76    |

| Figure 7.23 | Format of Receive Ethernet Frame – TCPIPACC is enabled, without VLAN Tag, no TCP/UD        | P       |

| packets     | 7-77                                                                                       |         |

| Figure 7.24 | Format of Receive Ethernet Frame – TCPIPACC is enabled, with VLAN Tag, no TCP/UDP p 7-77   | ackets  |

| Figure 7.25 | Format of Receive Ethernet Frame – TCPIPACC is enabled, without VLAN Tag, with TCP/U       | DP      |

| packets     | 7-78                                                                                       |         |

| Figure 7.26 | Format of Receive Ethernet Frame – TCPIPACC is enabled, with VLAN Tag, with TCP/UDP        |         |

| packets     | 7-78                                                                                       |         |

| Figure 7.27 | Format of Receive Ethernet Frame – TCPIPACC is disabled, without VLAN Tag                  | 7-79    |

| Figure 7.28 | Format of Receive Ethernet Frame – TCPIPACC is disabled, with VLAN Tag                     | 7-79    |

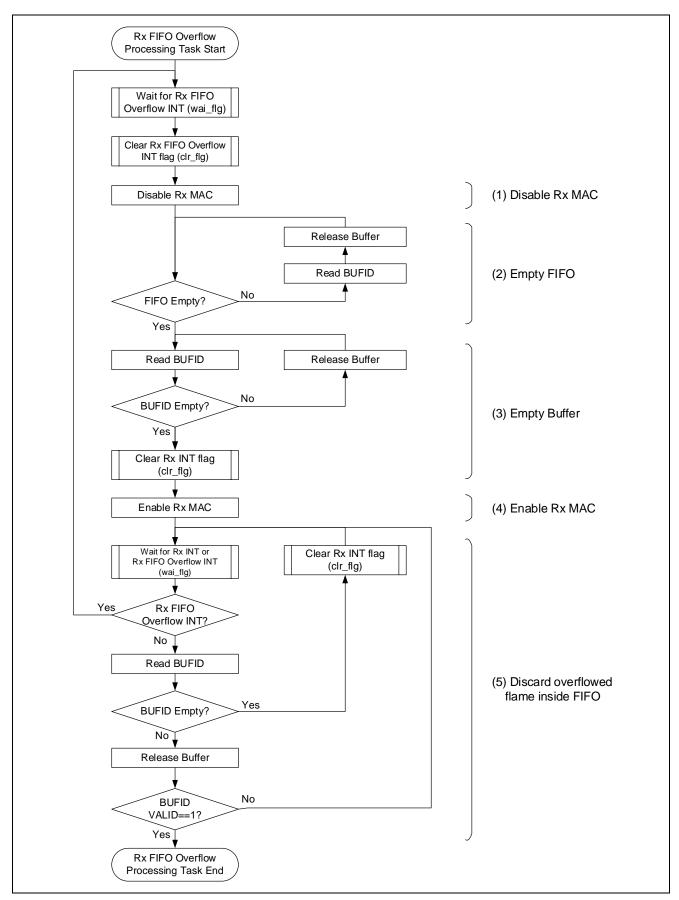

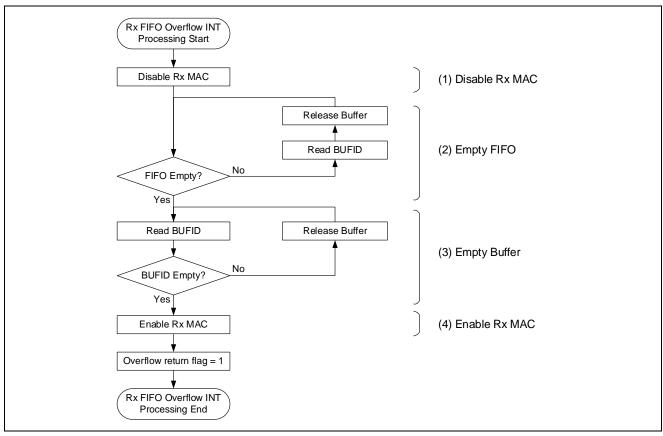

| Figure 7.29 | Flowchart of RX FIFO Overflow Processing Task (In case the hardware real-time OS is used)  | 7-84    |

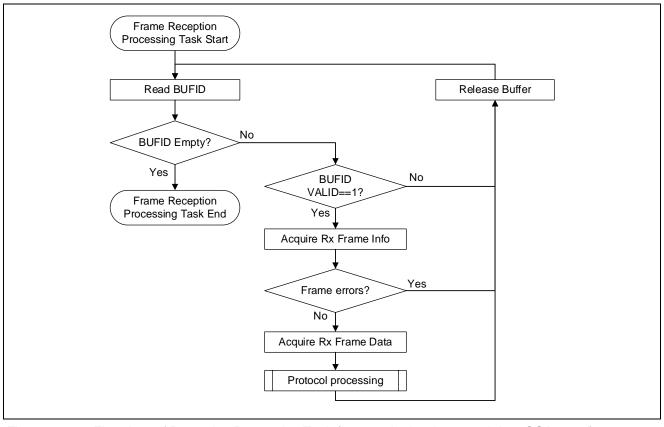

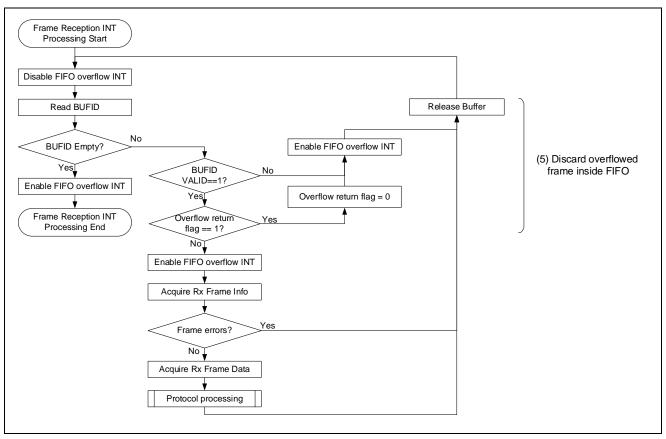

| Figure 7.30 | Flowchart of Reception Processing Task (In case the hardware real-time OS is used)         | 7-85    |

| Figure 7.31 | Flowchart of RX FIFO Overflow INT Processing (In case the hardware real-time OS is not use | ed)7-85 |

| Figure 7.32 | Flowchart of Reception Processing (In case the hardware real-time OS is not used)          | 7-86    |

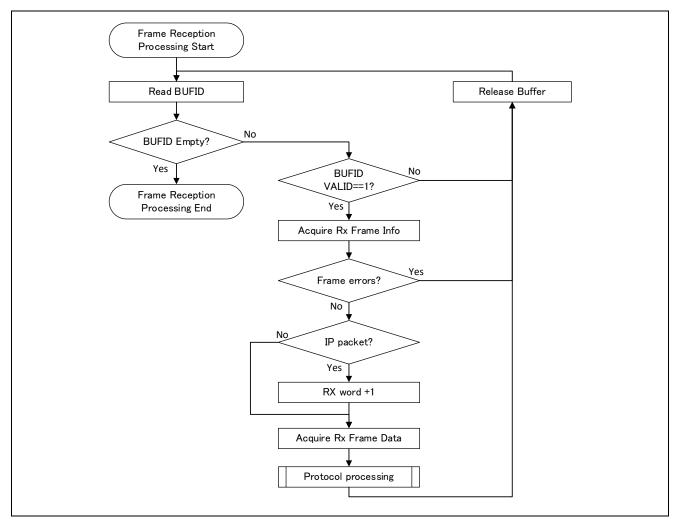

| Figure 7.33 | Flowchart of Reception Processing                                            | 7-87  |

|-------------|------------------------------------------------------------------------------|-------|

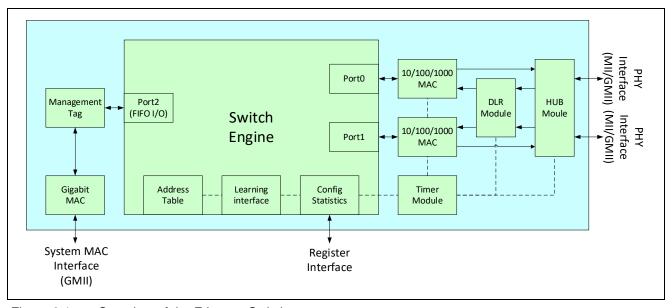

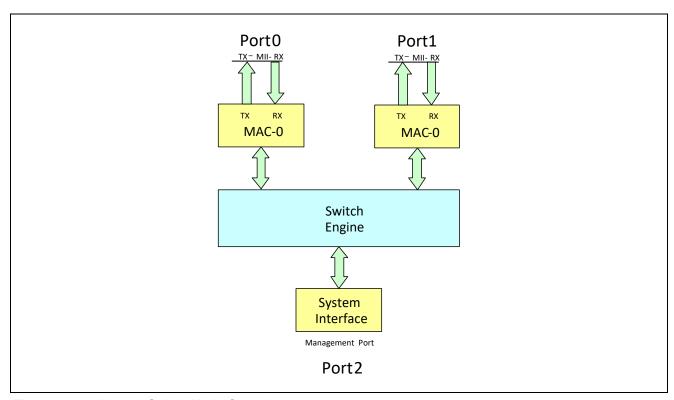

| Figure 8.1  | Overview of the Ethernet Switch                                              | 8-1   |

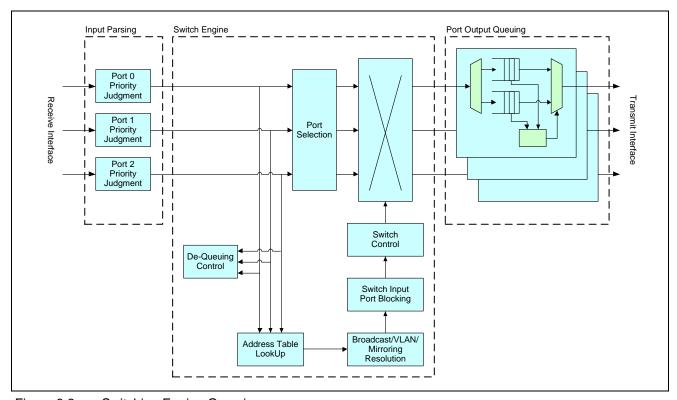

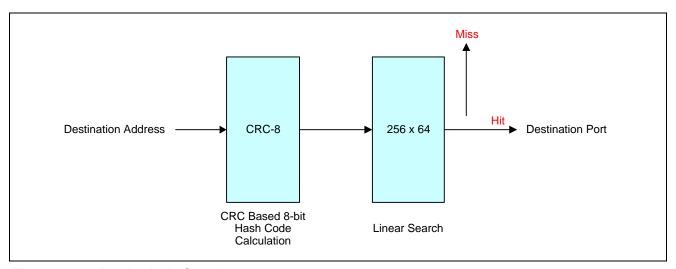

| Figure 8.2  | Switching Engine Overview                                                    | 8-63  |

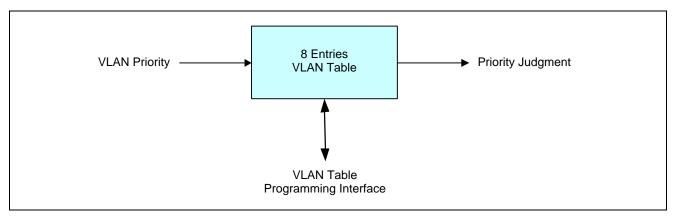

| Figure 8.3  | VLAN Priority Table Overview                                                 | 8-64  |

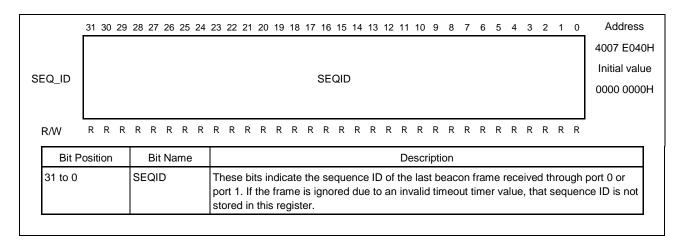

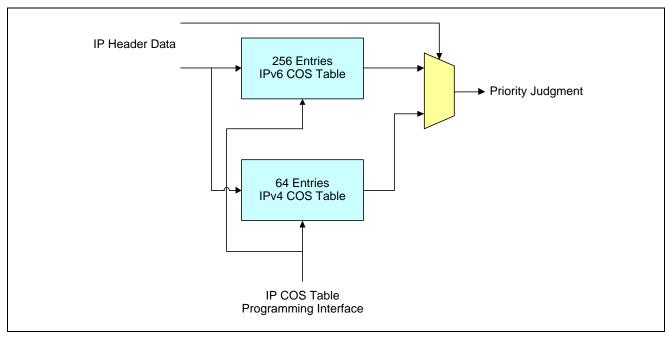

| Figure 8.4  | IP COS Tables Overview                                                       | 8-65  |

| Figure 8.5  | Port Look-Up Overview                                                        | 8-66  |

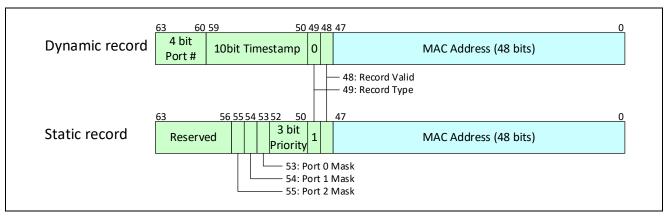

| Figure 8.6  | Record Types of Address Memory                                               | 8-67  |

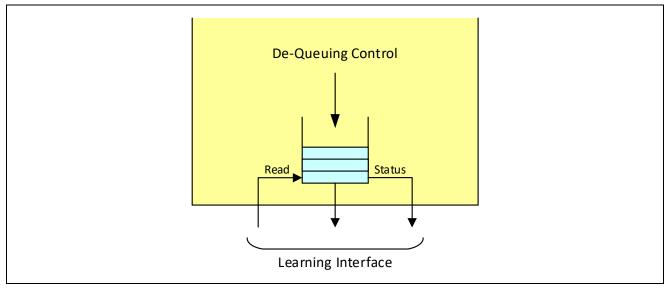

| Figure 8.7  | Learning Interface Overview                                                  | 8-68  |

| Figure 8.8  | Record Formats                                                               | 8-68  |

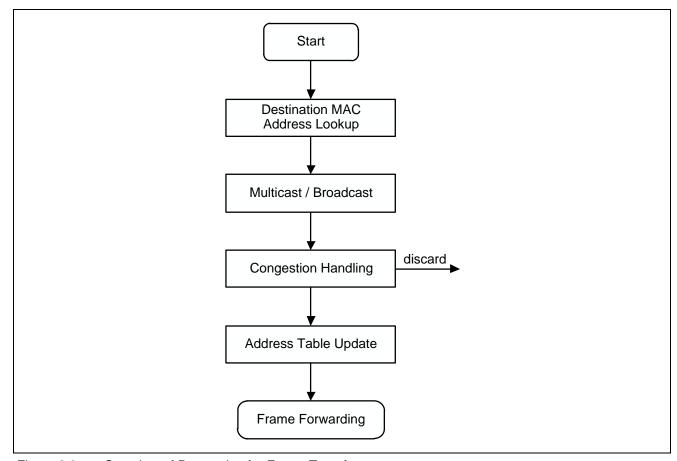

| Figure 8.9  | Overview of Processing for Frame Transfer                                    | 8-69  |

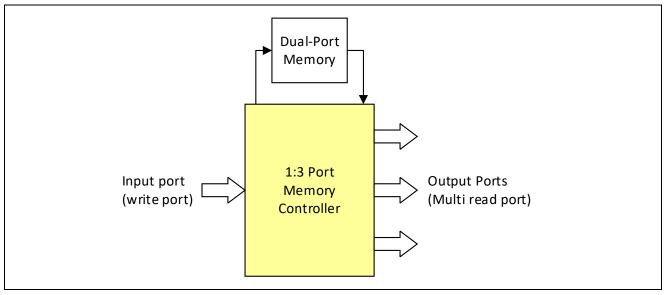

| Figure 8.10 | Overview of Output Port Memory Controller                                    | 8-72  |

| Figure 8.11 | Normal Switch Mode Operation                                                 | 8-73  |

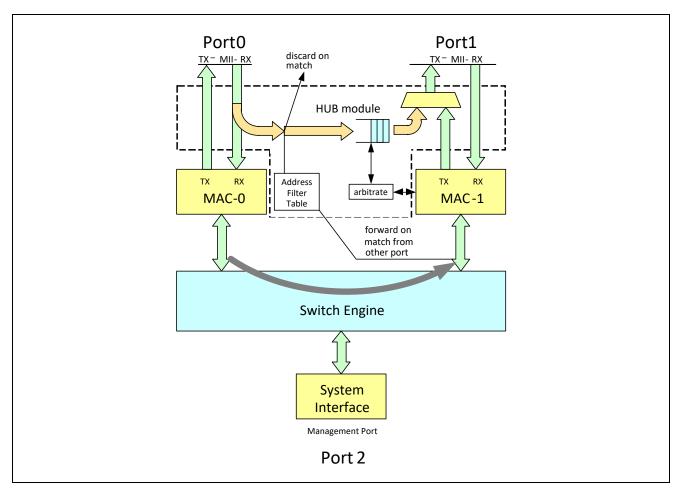

| Figure 8.12 | Operation of the Hub when Transfer from Port 0 to Port 1 is Enabled          | 8-74  |

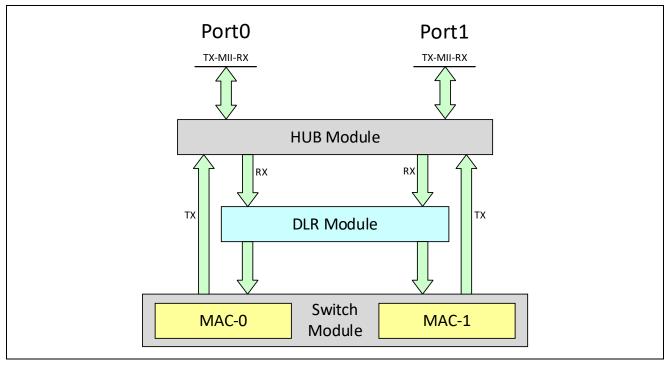

| Figure 8.13 | Connection between the Hub Module and the DLR Module                         | 8-79  |

| Figure 8.14 | Beacon Frame Format                                                          | 8-80  |

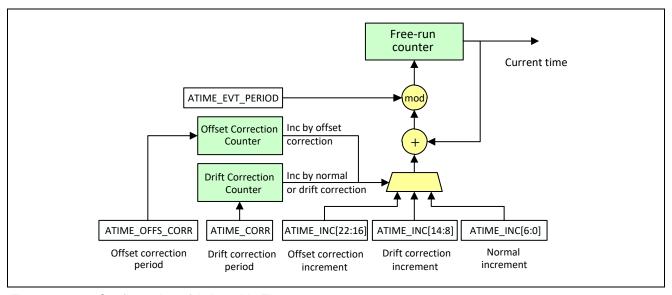

| Figure 8.15 | Configuration of Adjustable Timer                                            | 8-89  |

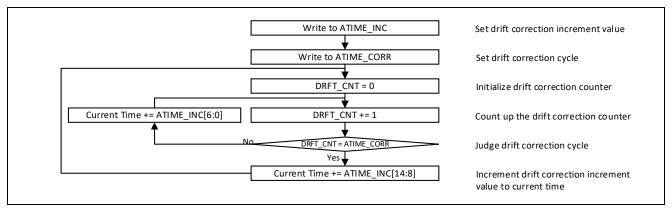

| Figure 8.16 | Drift Correction                                                             | 8-90  |

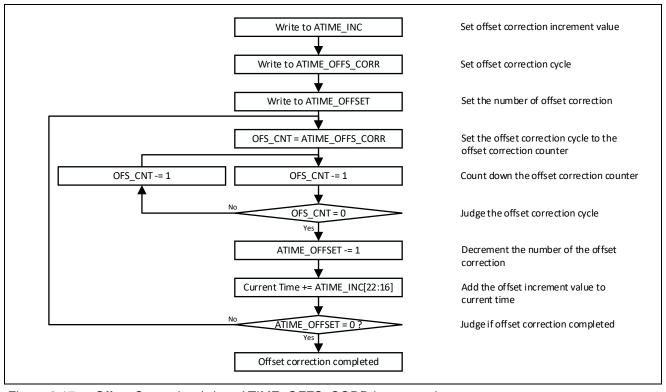

| Figure 8.17 | Offset Correction (when ATIME_OFFS_CORR is not zero)                         | 8-90  |

| Figure 8.18 | Format of Frame with Management Tag in Internal Port                         | 8-93  |

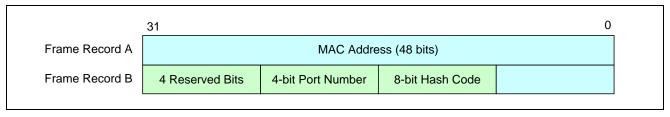

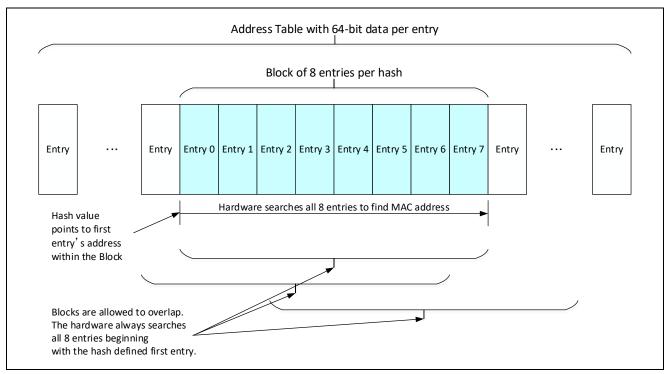

| Figure 8.19 | Entries of Address Table and Definition of Hash Block                        | 8-101 |

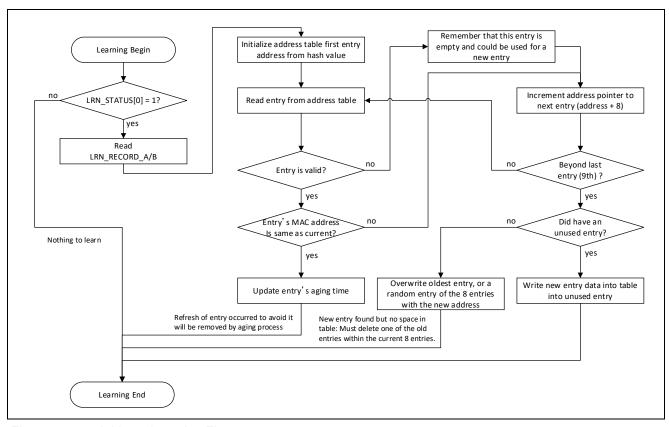

| Figure 8.20 | Address Learning Flow                                                        | 8-102 |

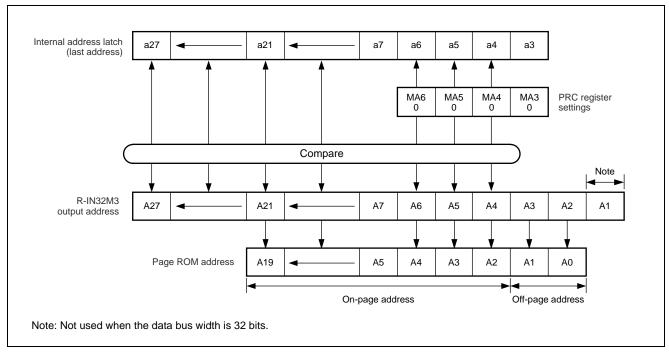

| Figure 9.1  | Example of Control Using the MA6 to MA3 Bits of the PRC Register             | 9-10  |

| Figure 9.2  | Example of Connection with 32-Bit SRAM                                       | 9-12  |

| Figure 9.3  | Example of Connection with 16-Bit SRAM                                       | 9-12  |

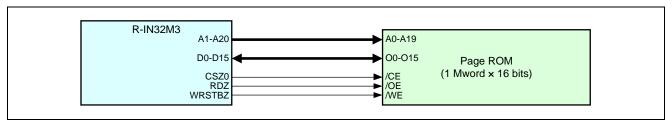

| Figure 9.4  | Example of Connection with 32-Bit Page ROM                                   | 9-13  |

| Figure 9.5  | Example of Connection with 16-Bit Page ROM                                   | 9-13  |

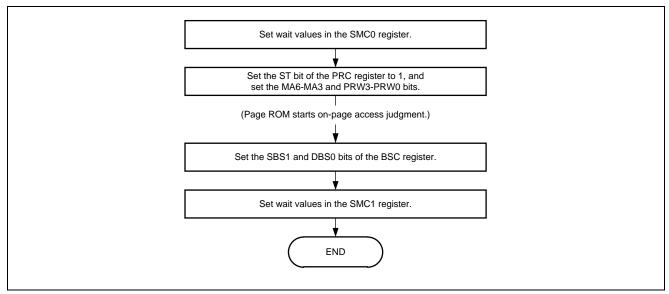

| Figure 9.6  | Example Procedure for Setting the Control Registers of the Memory Controller | 9-14  |

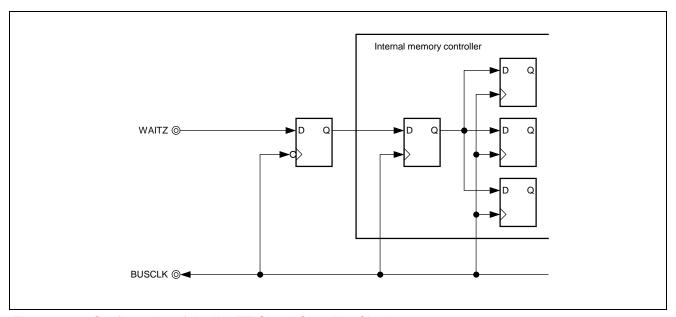

| Figure 9.7  | Configuration of the WAITZ Signal Sampling Circuit                           | 9-15  |

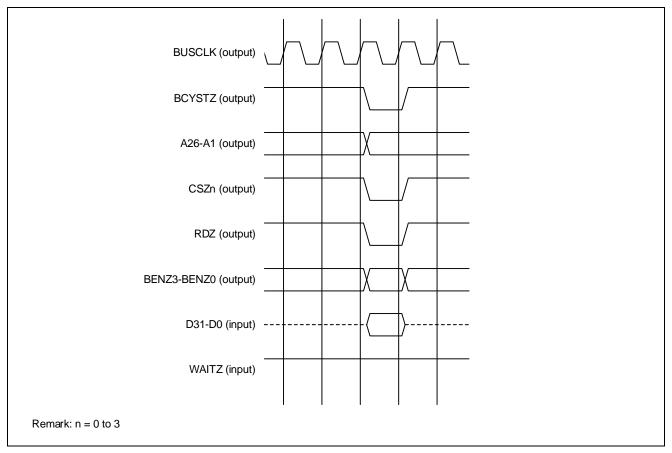

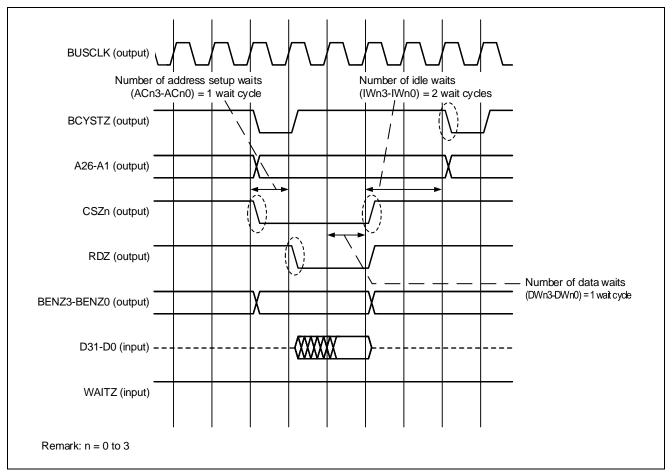

| Figure 9.8  | SRAM Read Cycles <r></r>                                                     | 9-17  |

| Figure 9.9  | SRAM Read Cycles (with Wait Settings) <r></r>                                | 9-18  |

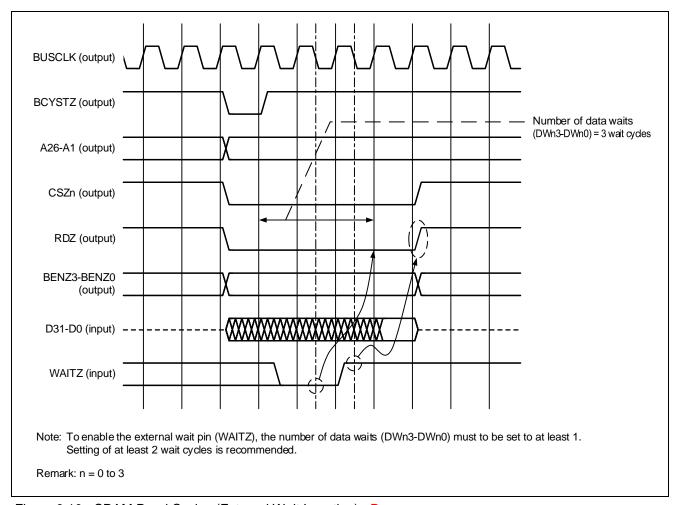

| Figure 9.10 | SRAM Read Cycles (External Wait Insertion) < R>                              | 9-19  |

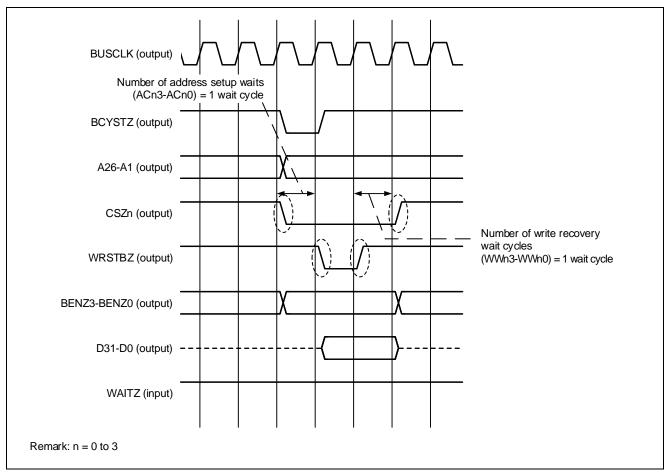

| Figure 9.11 | SRAM Write Cycles (with No Wait) < R>                                        | 9-20  |

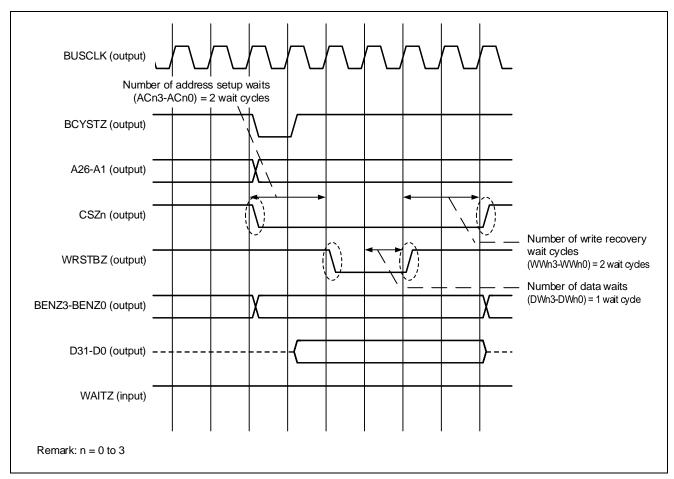

| Figure 9.12 | SRAM Write Cycles (with Wait States) < R>                                    | 9-21  |

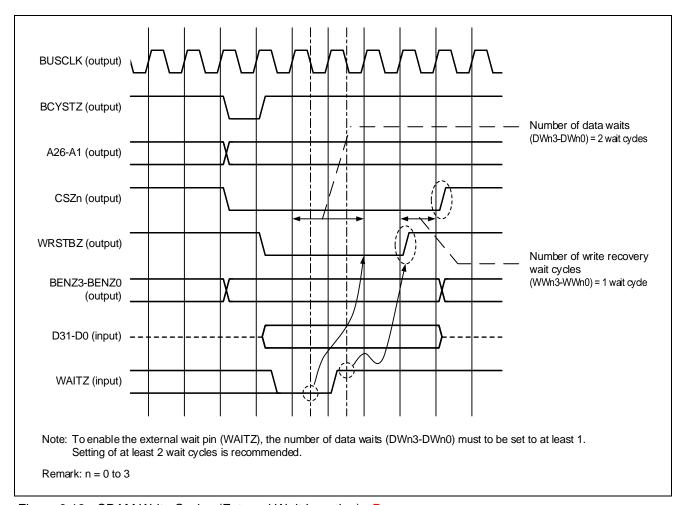

| Figure 9.13 | SRAM Write Cycles (External Wait Insertion) <r></r>                          | 9-22  |

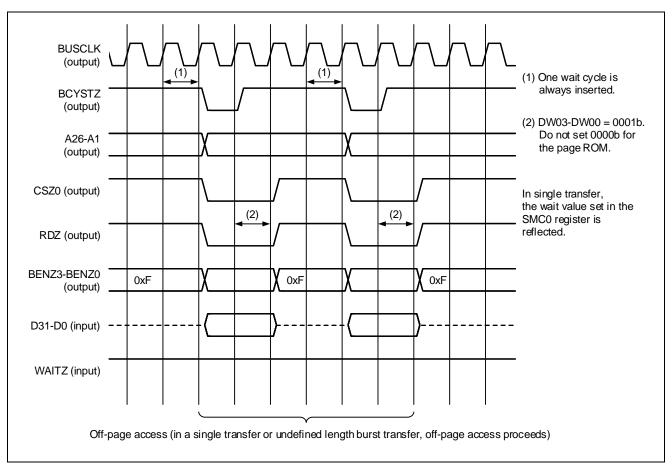

| Figure 9.14 | Page ROM Read Cycles (Single Transfer) < R>                                  | 9-23  |

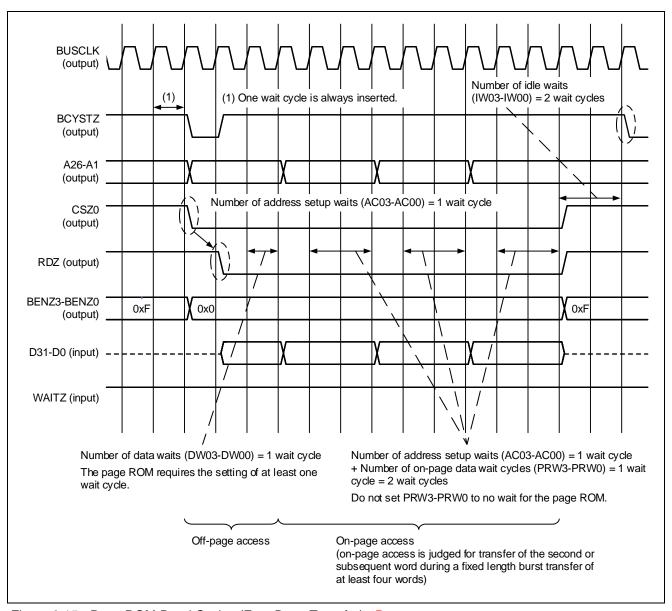

| Figure 9.15 | Page ROM Read Cycles (Four Burst Transfer) < R>                              | 9-24  |

| Figure 10.1 | Register Setup Procedure                                                     | 10-17 |

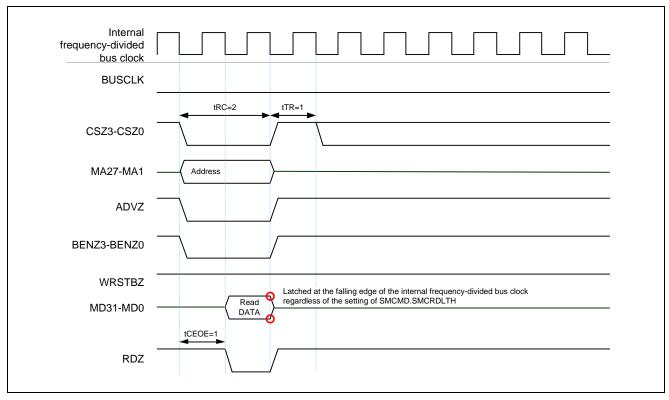

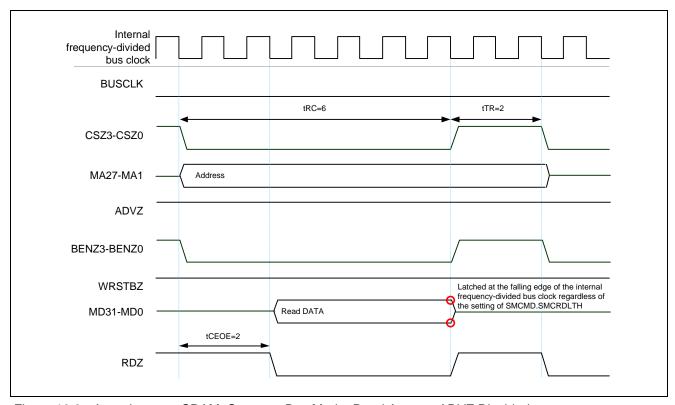

| Figure 10.2 | Clock Output Timing Example (SMCMD.SMCCLKTH = 0)                             | 10-18 |

| Figure 10.3 | Clock Output Timing Example (SMCMD.SMCCLKTH = 1)                             | 10-18 |

| Figure 10.4 | Write Enable Signal Operation                                                | 10-20 |

| Figure 10.5 | Read Data Timing Control                                                     | 10-21 |

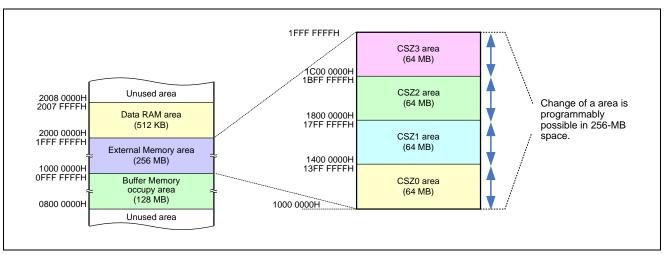

| Figure 10.6 | External Memory Space                                                        | 10-26 |

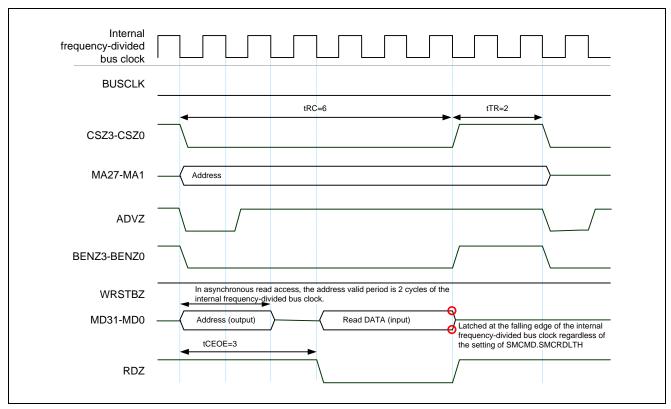

| Figure 10.7 | Asynchronous SRAM, Separate Bus Mode, Read Access, ADVZ Enabled              |       |

| Figure 10.8  | Asynchronous SRAM, Separate Bus Mode, Read Access, ADVZ Disabled                    | 10-29   |

|--------------|-------------------------------------------------------------------------------------|---------|

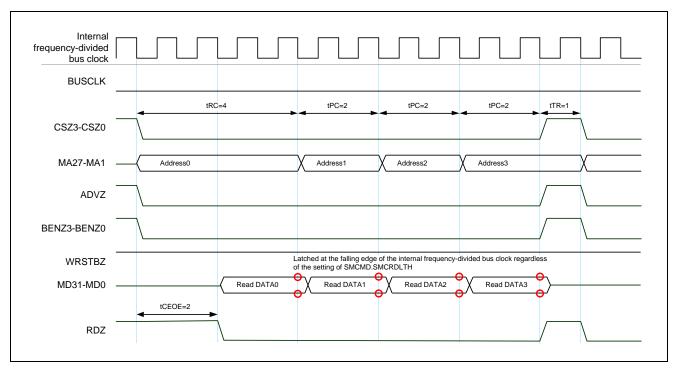

| Figure 10.9  | Asynchronous Page ROM, Separate Bus Mode, Read Access, ADVZ Enabled                 | 10-30   |

| Figure 10.10 | Asynchronous SRAM, Multiplexed Bus Mode, Read Access, ADVZ Enabled                  | 10-31   |

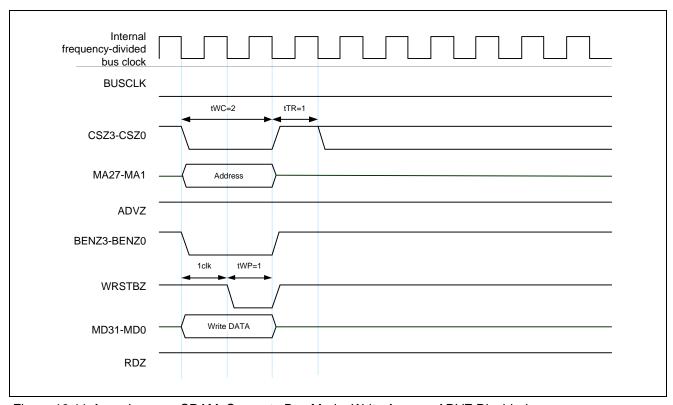

| Figure 10.11 | Asynchronous SRAM, Separate Bus Mode, Write Access, ADVZ Disabled                   | 10-32   |

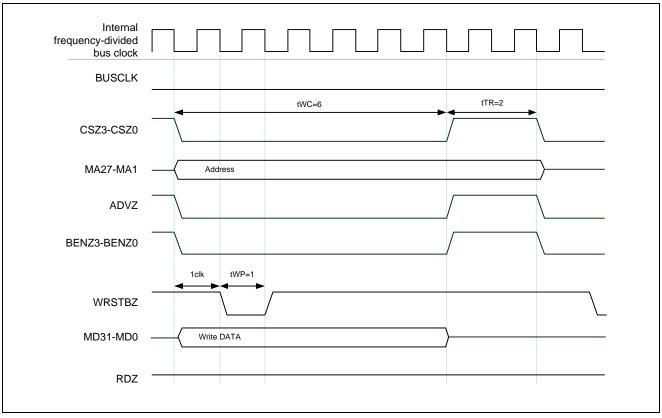

| Figure 10.12 | Asynchronous SRAM, Separate Bus Mode, Write Access, ADVZ Enabled                    | 10-33   |

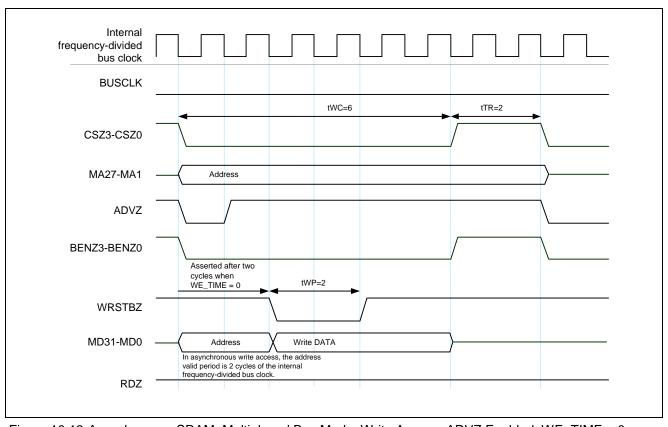

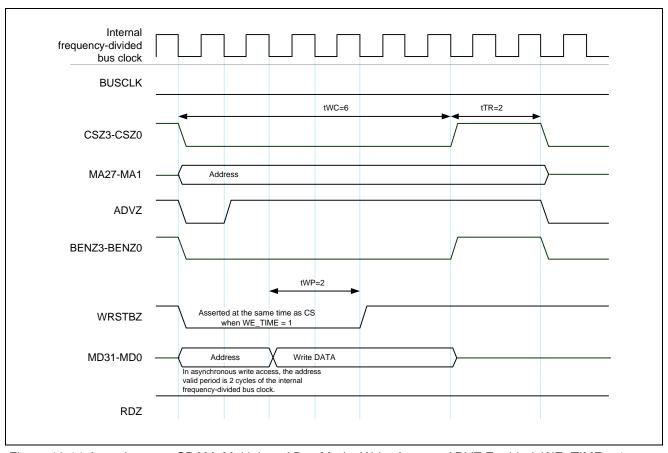

| Figure 10.13 | Asynchronous SRAM, Multiplexed Bus Mode, Write Access, ADVZ Enabled, WE_TIME =      | 0 10-34 |

| Figure 10.14 | Asynchronous SRAM, Multiplexed Bus Mode, Write Access, ADVZ Enabled, WE_TIME =      | 1 10-35 |

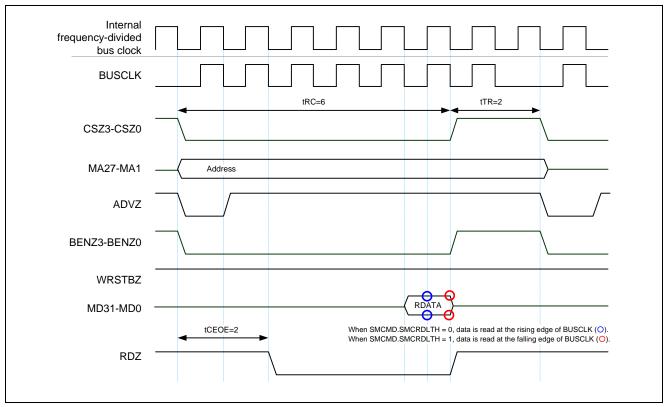

| Figure 10.15 | Synchronous SRAM, Separate Bus Mode, Read Access, ADVZ Enabled                      | 10-36   |

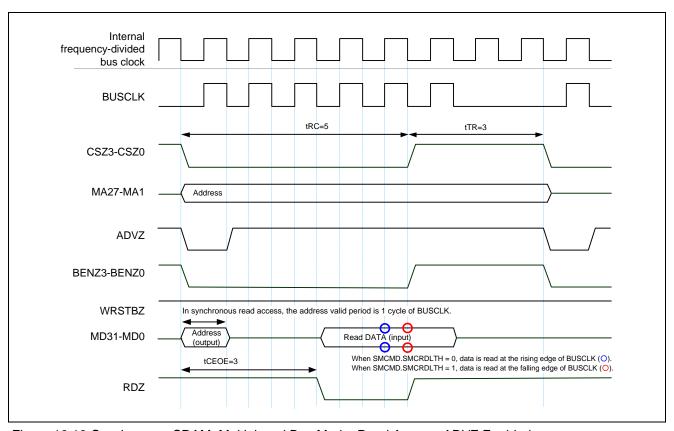

| Figure 10.16 | Synchronous SRAM, Multiplexed Bus Mode, Read Access, ADVZ Enabled                   | 10-37   |

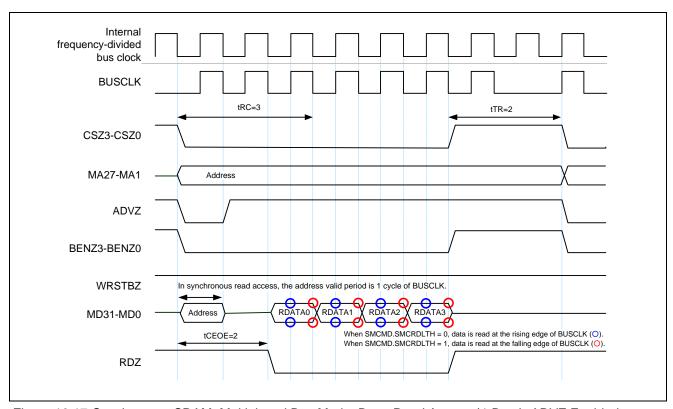

| Figure 10.17 | Synchronous SRAM, Multiplexed Bus Mode, Burst Read Access (4-Beat), ADVZ Enabled .  | 10-38   |

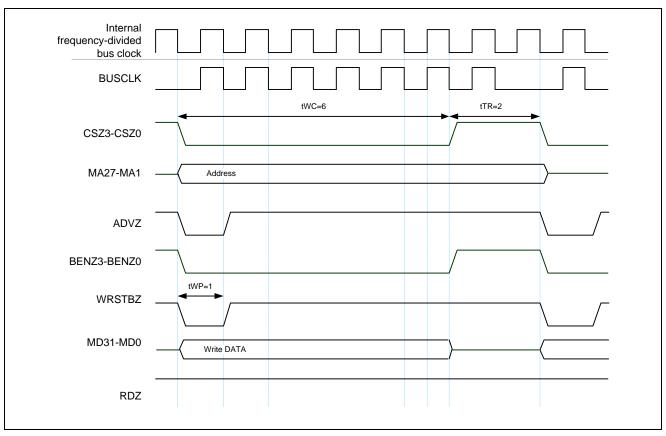

| Figure 10.18 | Synchronous SRAM, Separate Bus Mode, Write Access, ADVZ Enabled                     | 10-39   |

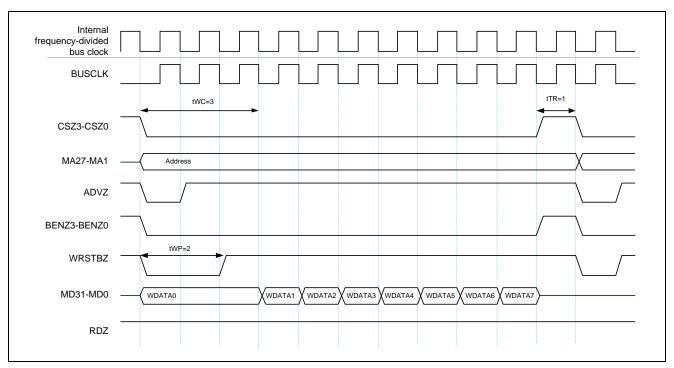

| Figure 10.19 | Synchronous SRAM, Separate Bus Mode, Burst Write Access (8-Beat), ADVZ Enabled      | 10-40   |

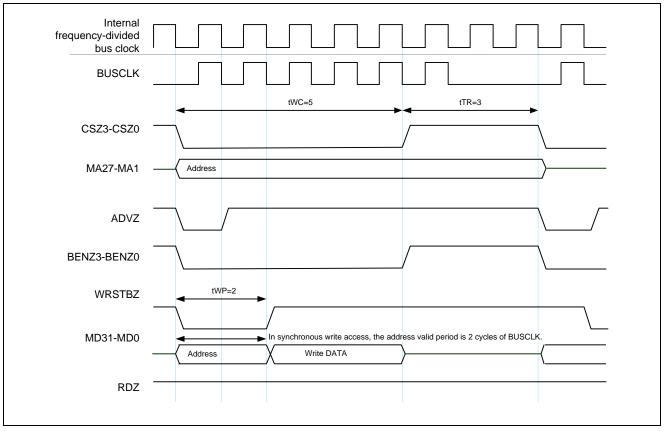

| Figure 10.20 | Synchronous SRAM, Multiplexed Bus Mode, Write Access, ADVZ Enabled                  | 10-41   |

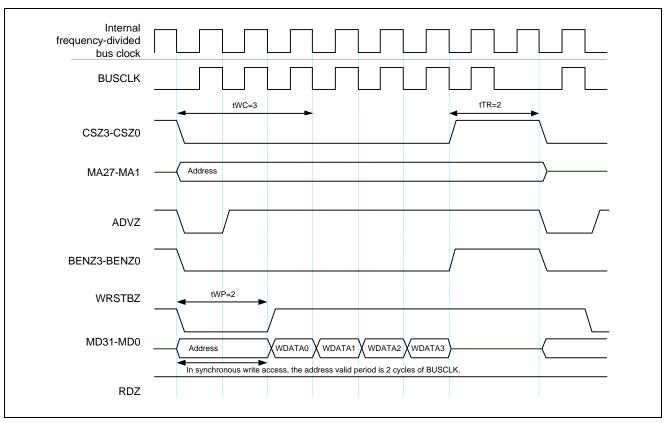

| Figure 10.21 | Synchronous SRAM, Multiplexed Bus Mode, Burst Write Access (4-Beat), ADVZ Enabled   | 10-42   |

| Figure 10.22 | Synchronous SRAM, Multiplexed Bus Mode, Read Access, ADVZ Enabled                   | 10-43   |

| Figure 10.23 | Synchronous SRAM, Separate Bus Mode, Burst Write Access (4-Beat), ADVZ Enabled      | 10-44   |

| Figure 11.1  | External MCU Interface Space                                                        | 11-3    |

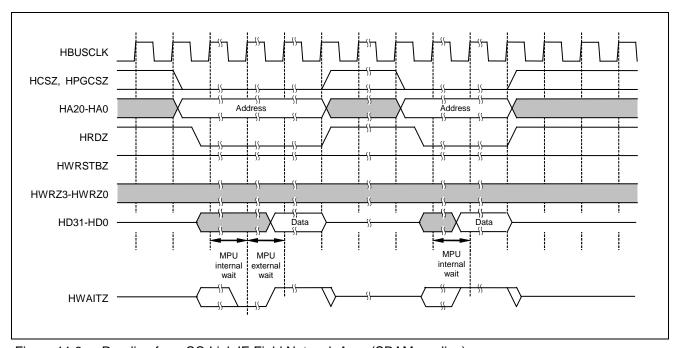

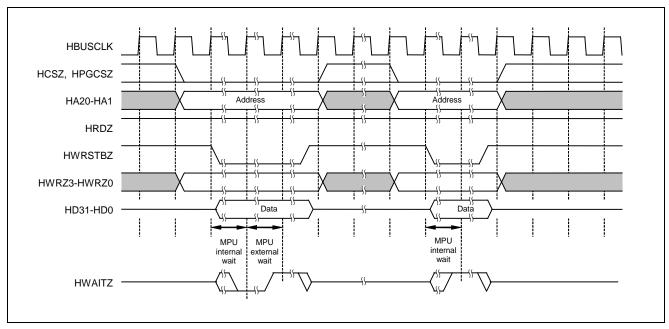

| Figure 11.2  | Writing to the CC-Link IE Field Network Area (SRAM writing)                         | 11-9    |

| Figure 11.3  | Reading from CC-Link IE Field Network Area (SRAM reading)                           |         |

| Figure11.4   | Writing to the External MCU Interface Register Area (SRAM writing)                  | 11-10   |

| Figure 11.5  | Reading from External MCU Interface Register Area (SRAM reading)                    | 11-10   |

| Figure 11.6  | Writing to Other Areas (SRAM writing)                                               | 11-11   |

| Figure 11.7  | Reading from Other Areas (SRAM reading)                                             |         |

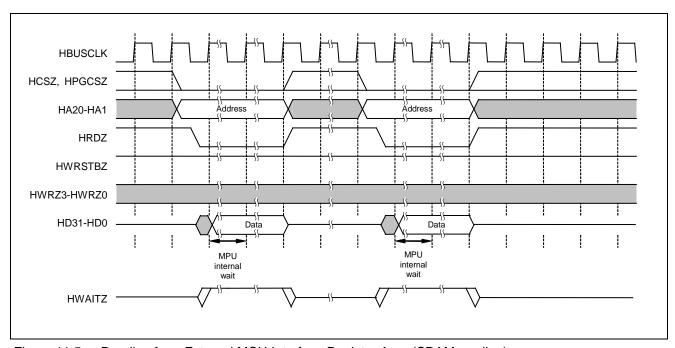

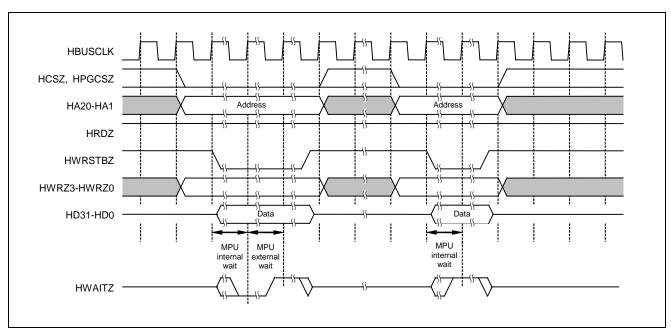

| Figure 11.8  | Timing Adjustment (SRAM writing)                                                    | 11-13   |

| Figure 11.9  | Timing Adjustment (SRAM reading, page ROM reading)                                  | 11-14   |

| Figure 11.10 | Timing Adjustment (page ROM reading)                                                |         |

| Figure 12.1  | Connection with Serial Flash ROM <r></r>                                            |         |

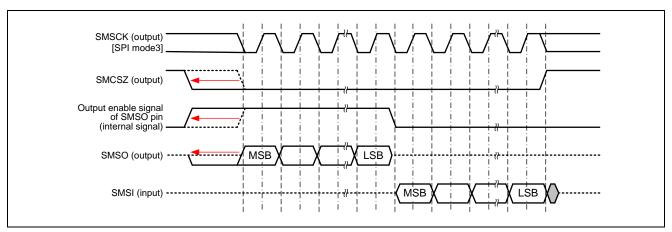

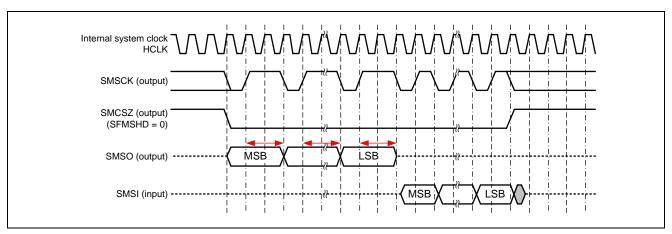

| Figure 12.2  | Basic Operation of SPI Bus.                                                         | 12-13   |

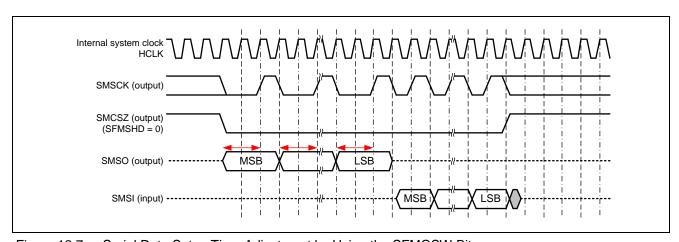

| Figure 12.3  | Correction of the SMSCK Signal Duty Factor by Using the SFMDTY Bit (Example of HCLK |         |

| C            | 12-14                                                                               | ,       |

| Figure 12.4  | SMCSZ Signal Setup Time Adjustment by Using the SFMSLD Bit                          | 12-15   |

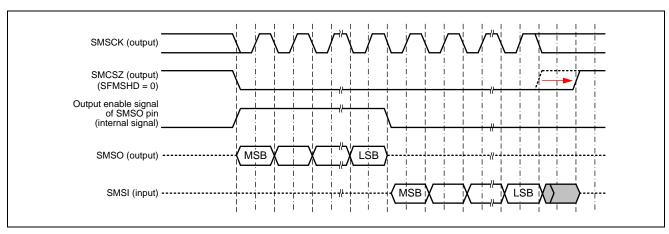

| Figure 12.5  | SMCSZ Signal Hold Time Adjustment by Using the SFMSHD Bit                           |         |

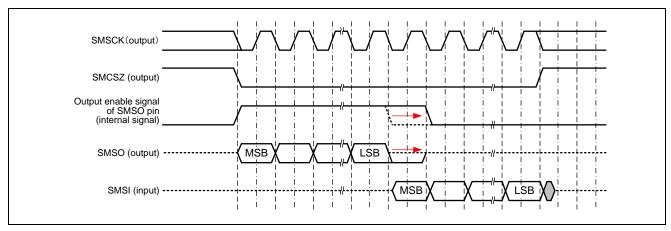

| Figure 12.6  | Output Enable Time Adjustment by Using the SFMOEX Bit                               |         |

| Figure 12.7  | Serial Data Setup Time Adjustment by Using the SFMOSW Bit                           |         |

| Figure 12.8  | Serial Data Hold Time Adjustment by Using the SFMOHW Bit                            |         |

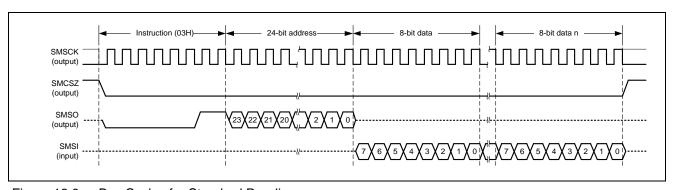

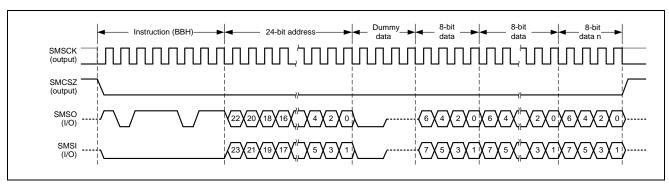

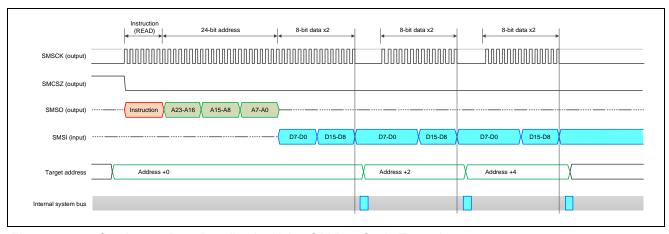

| Figure 12.9  | Bus Cycles for Standard Reading                                                     |         |

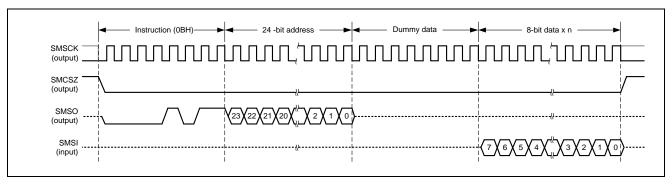

| Figure 12.10 | Bus Cycles for Fast Read                                                            |         |

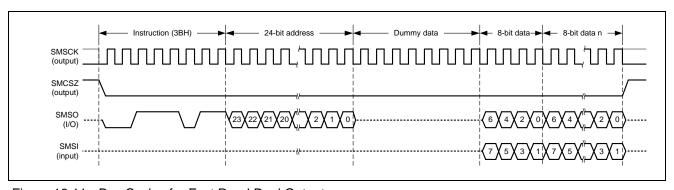

| Figure 12.11 | Bus Cycles for Fast Read Dual Output                                                |         |

| Figure 12.12 | Bus Cycles for Fast Read Dual I/O                                                   |         |

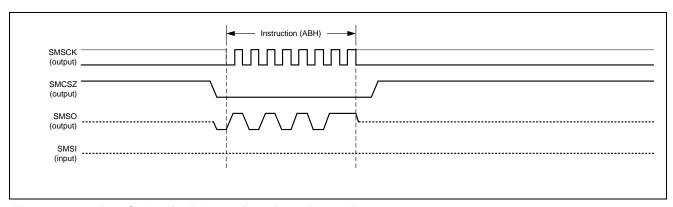

| Figure 12.12 | Bus Cycles for Release from Deep Power-Down                                         |         |

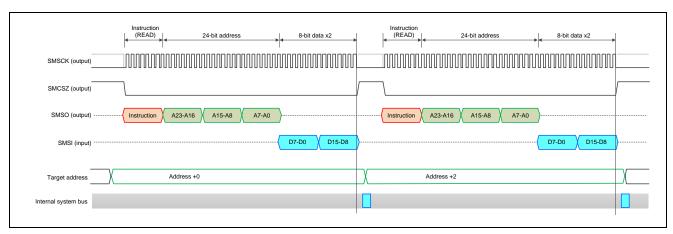

| Figure 12.14 | Continuous Data Reading by Individual Conversion                                    |         |

| <del> </del> |                                                                                     |         |

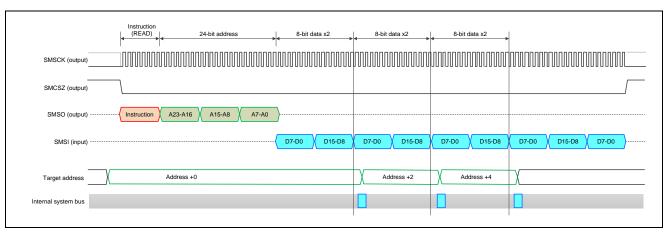

| Figure 12.15 | Continuous Data Reading by Using Prefetching                                        | /:=//   |

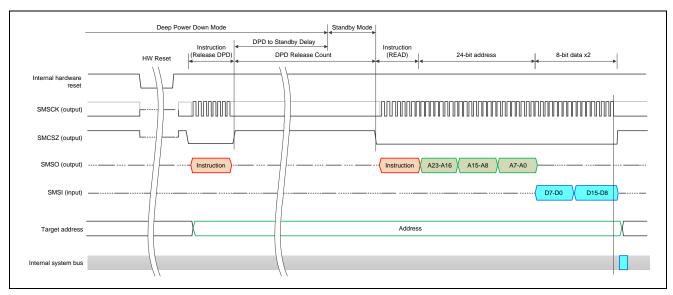

| Figu  | re 12.17 | Operation for Automatic Release from the Deep Power-Down State               | 12-24  |

|-------|----------|------------------------------------------------------------------------------|--------|

| Figu  | re 13.1  | Relation between DMA Units/Channels and DMA Triggers                         | 13-5   |

| Figu  | re 13.2  | Name of Transfers                                                            | 13-6   |

| Figu  | re 13.3  | Register Block Diagram of DMA                                                | 13-8   |

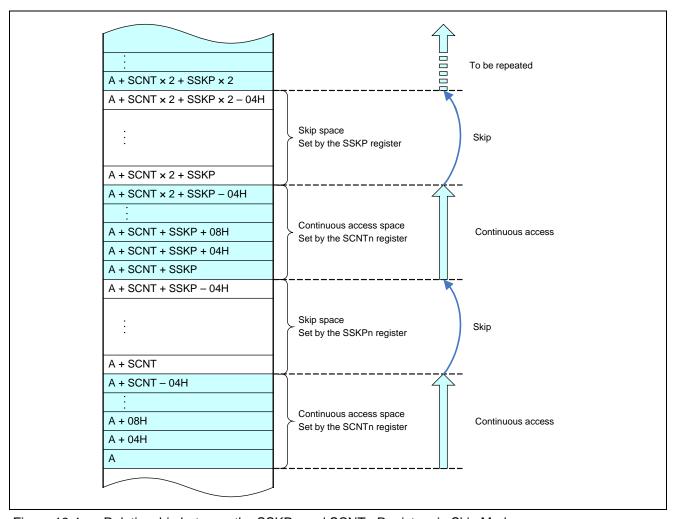

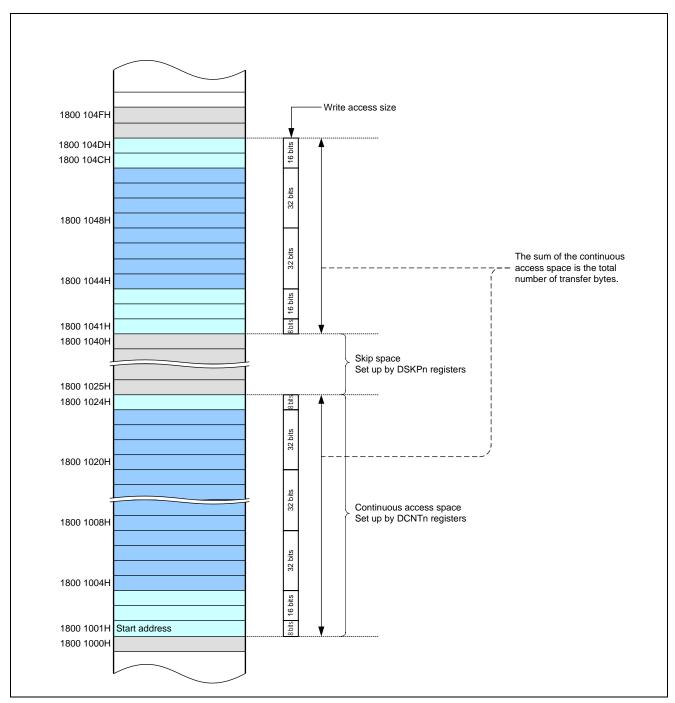

| Figu  | re 13.4  | Relationship between the SSKPn and SCNTn Registers in Skip Mode              | 13-38  |

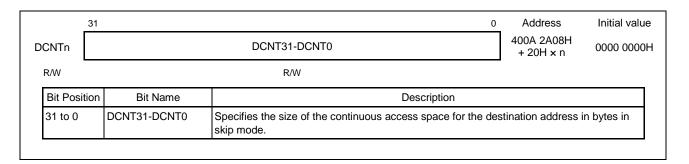

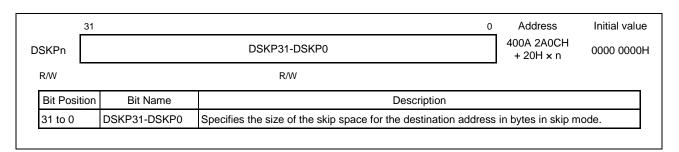

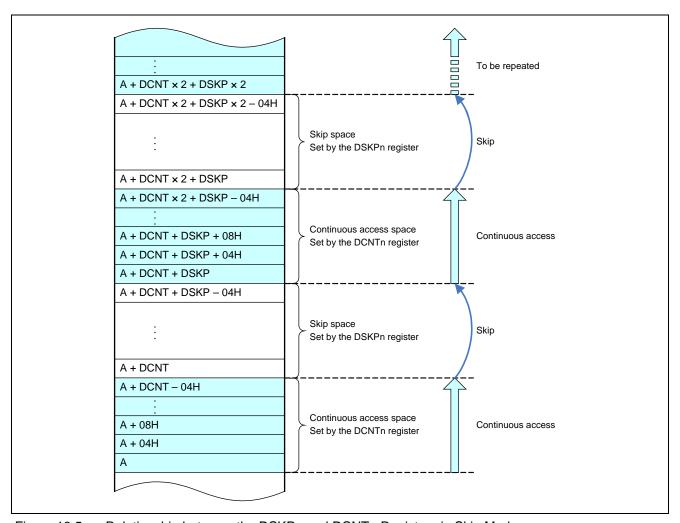

| Figu  | re 13.5  | Relationship between the DSKPn and DCNTn Registers in Skip Mode              | 13-40  |

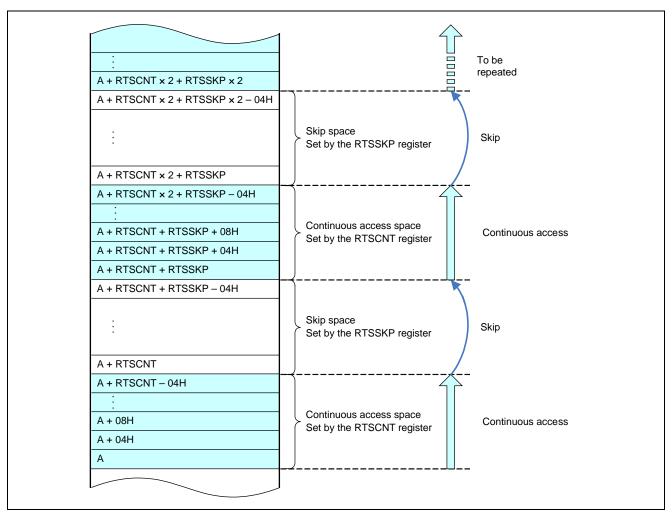

| Figu  | re 13.6  | Relationship between the RTSSKP and RTSCNT Registers in Skip Mode            | 13-70  |

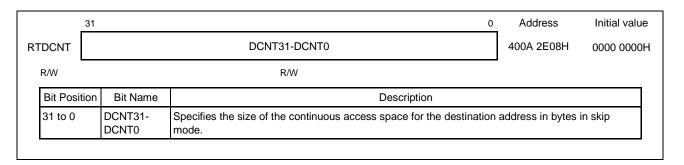

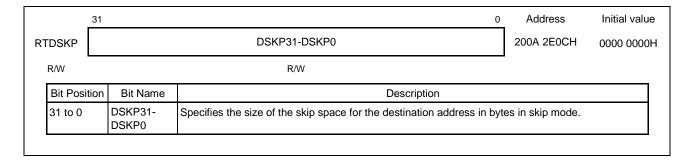

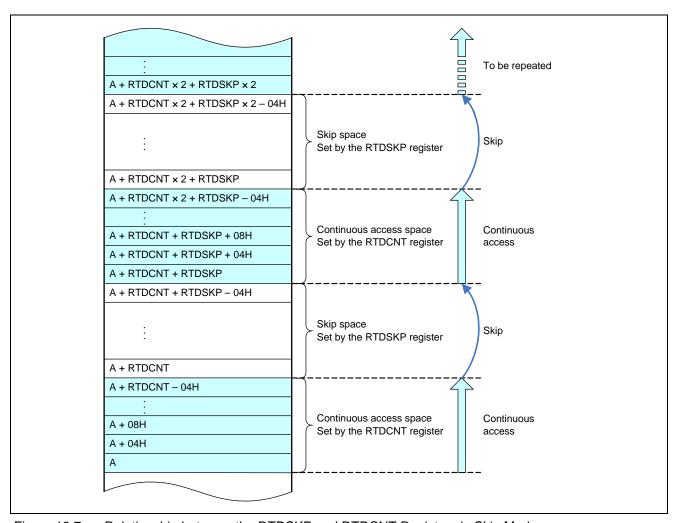

| Figu  | re 13.7  | Relationship between the RTDSKP and RTDCNT Registers in Skip Mode            | 13-72  |

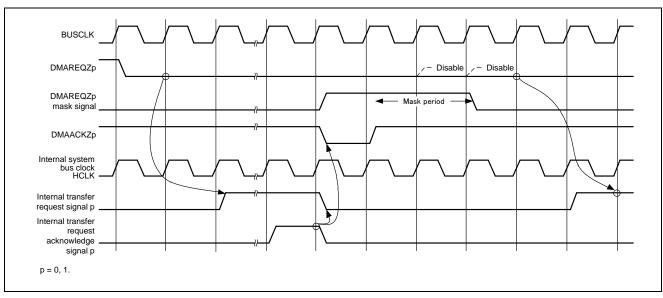

| Figu  | re 13.8  | DMA Pin Signals and Internal Signals (1) (DMAIFCp = 8000 0000H)              | 13-81  |

| Figu  | re 13.9  | DMA Pin Signals and Internal Signals (2) (DMAIFCp = 8000 0000H)              | 13-81  |

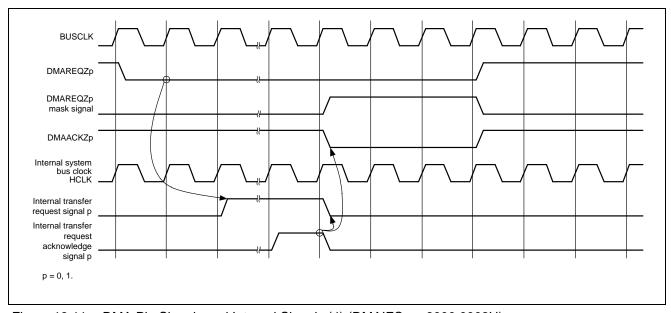

| Figu  | re 13.10 | DMA Pin Signals and Internal Signals (3) (DMAIFCp = 8000 0200H)              | 13-82  |

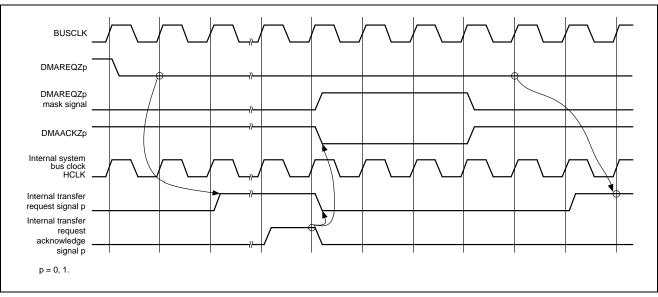

| Figu  | re 13.11 | DMA Pin Signals and Internal Signals (4) (DMAIFCp = 8000 0002H)              | 13-82  |

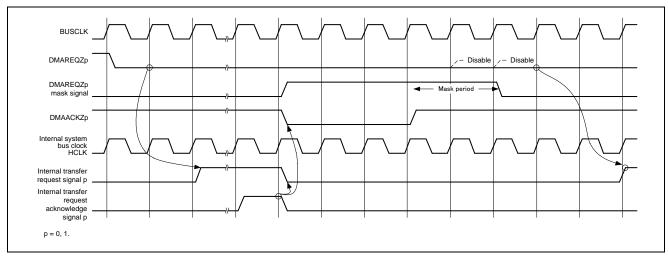

| Figu  | re 13.12 | DMA Pin Signals and Internal Signals (5) (DMAIFCp = 8000 0002H)              | 13-83  |

| Figu  | re 13.13 | DMA Pin Signals and Internal Signals (6) (DMAIFCp = 8000 0202H)              | 13-83  |

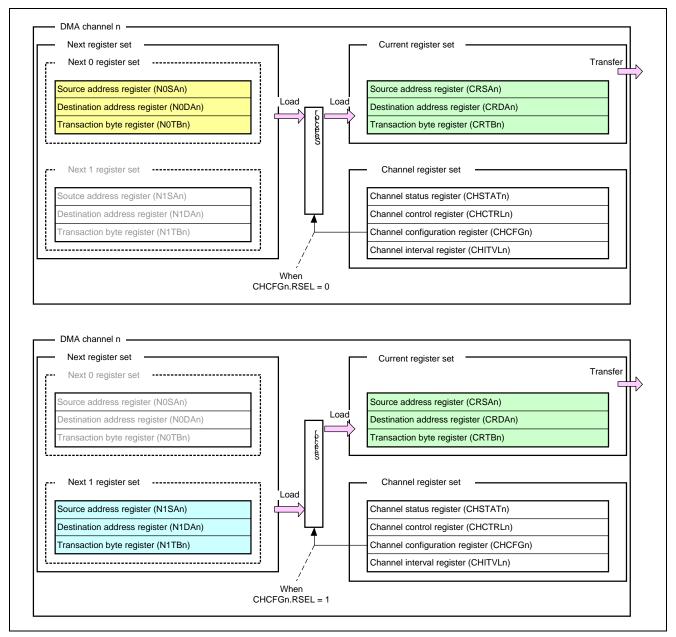

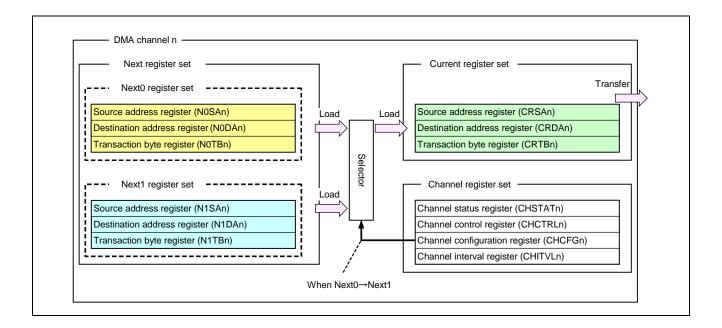

| Figu  | re 13.14 | Outline of the Register Mode Operation                                       | 13-91  |

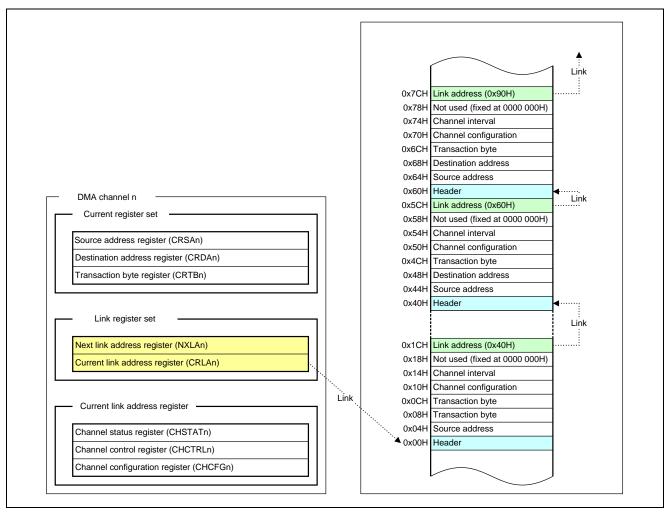

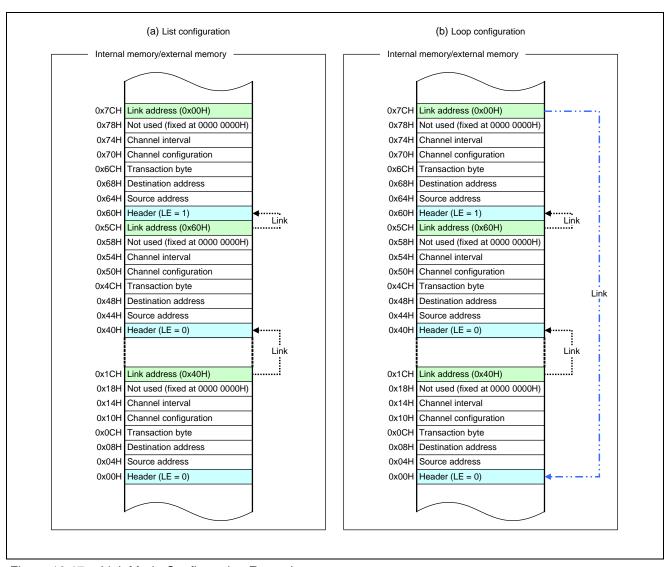

| Figu  | re 13.15 | Outline of Link Mode                                                         | 13-98  |

| Figu  | re 13.16 | Outline of the Descriptor Area and DMA Transfer Area                         | 13-106 |

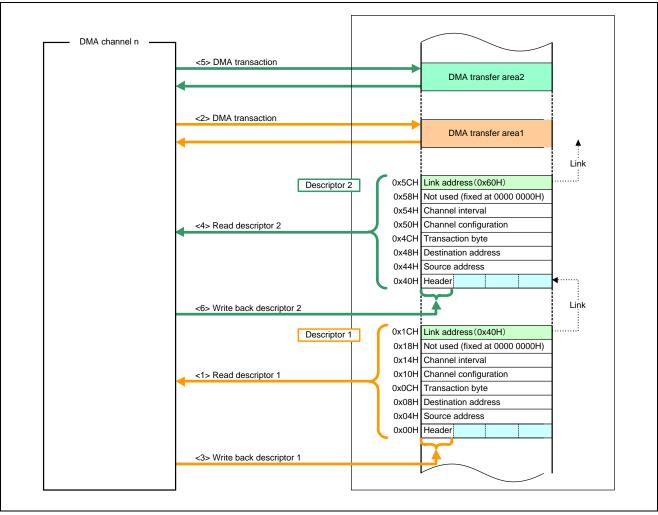

| Figu  | re 13.17 | Link Mode Configuration Example                                              | 13-109 |

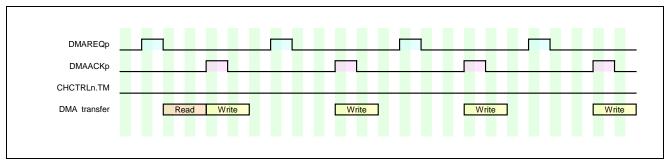

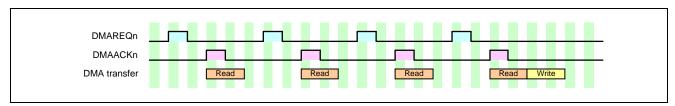

| •     | re 13.18 | Single Transfer Mode Example                                                 |        |

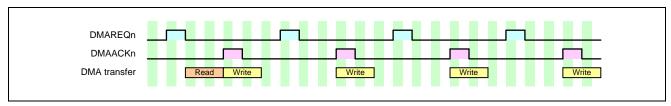

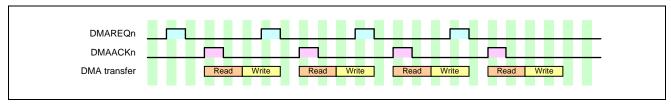

| •     | re 13.19 | Block Transfer Mode Example                                                  |        |

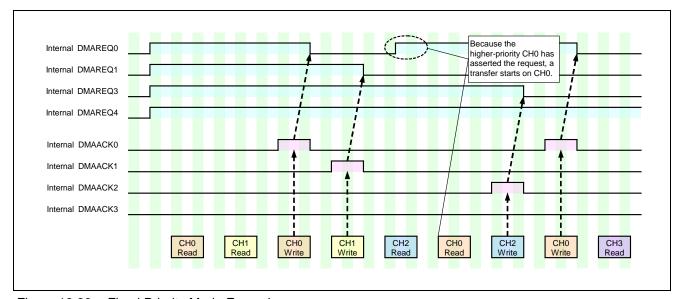

| Figu  | re 13.20 | Fixed Priority Mode Example                                                  | 13-115 |

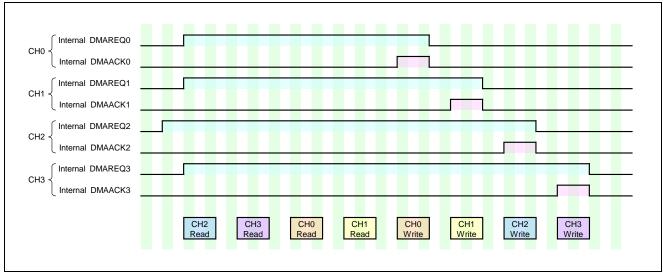

| Figu  | re 13.21 | Round Robin Mode                                                             | 13-116 |

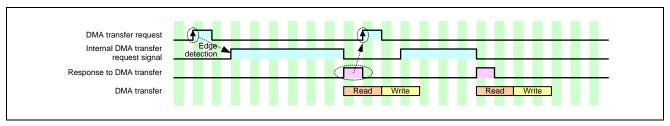

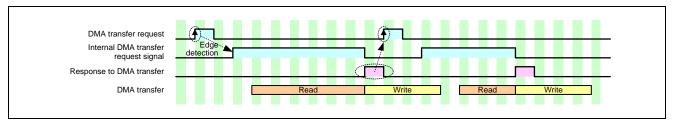

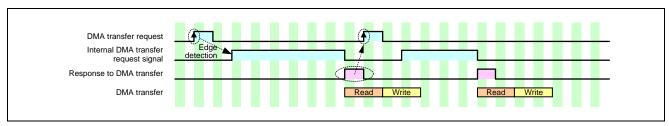

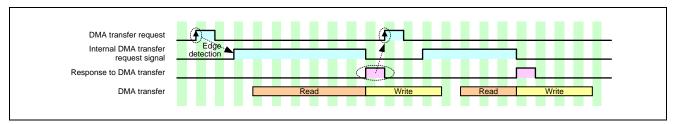

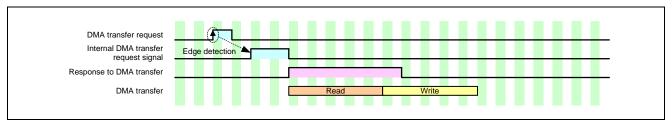

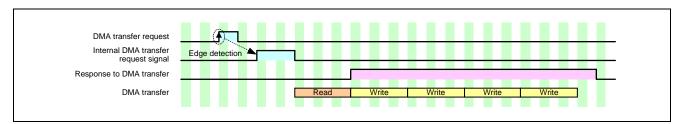

| Figu  | re 13.22 | Edge Detection Mode Operation Example 1                                      | 13-118 |

| Figu  | re 13.23 | Edge Detection Mode Operation Example 2                                      | 13-118 |

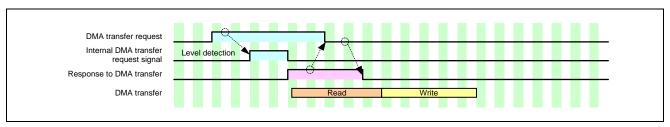

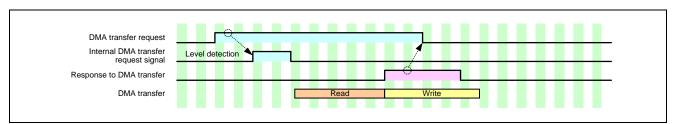

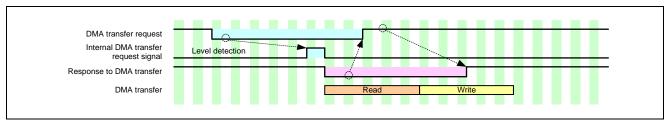

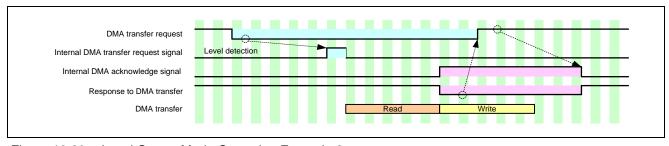

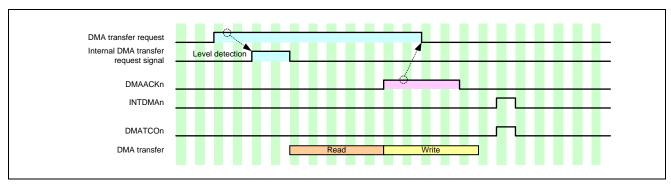

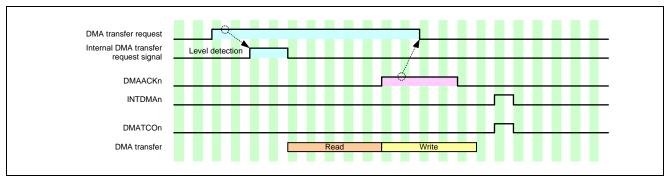

| Figu  | re 13.24 | Level Detection Mode Operation Example 1                                     |        |

| Figu  | re 13.25 | Level Detection Mode Operation Example 2                                     |        |

| Figu  | re 13.26 | Pulse Output Mode Operation Example 1                                        | 13-122 |

| Figu  | re 13.27 |                                                                              |        |

| Figu  | re 13.28 | Level Output Mode Operation Example 1                                        |        |

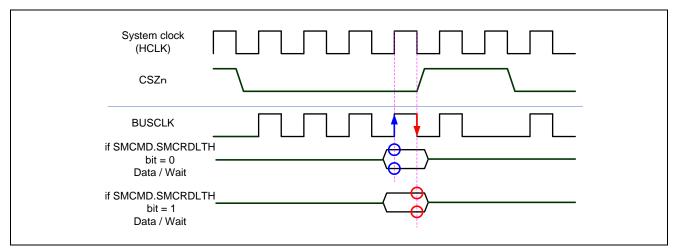

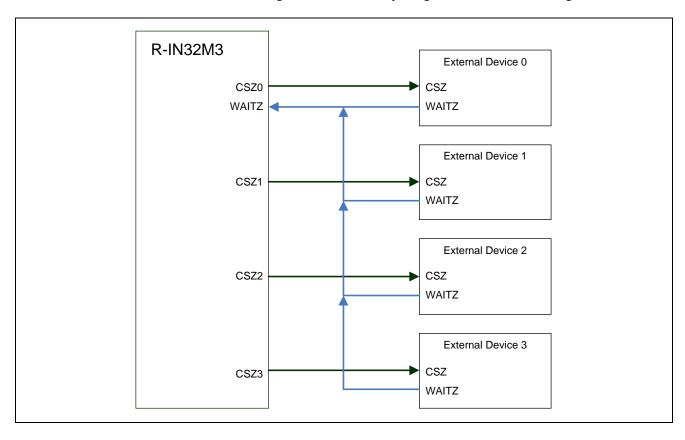

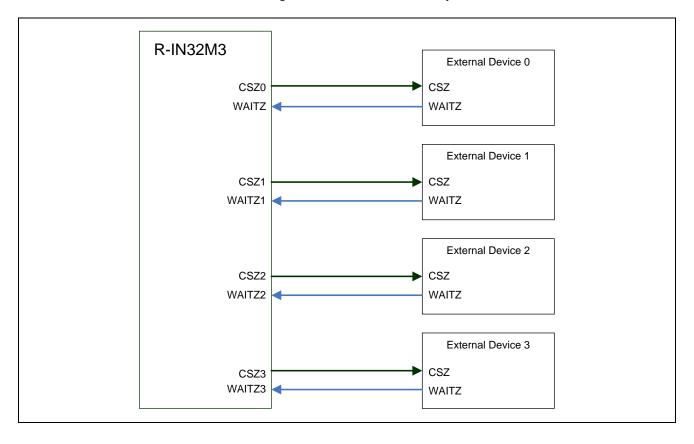

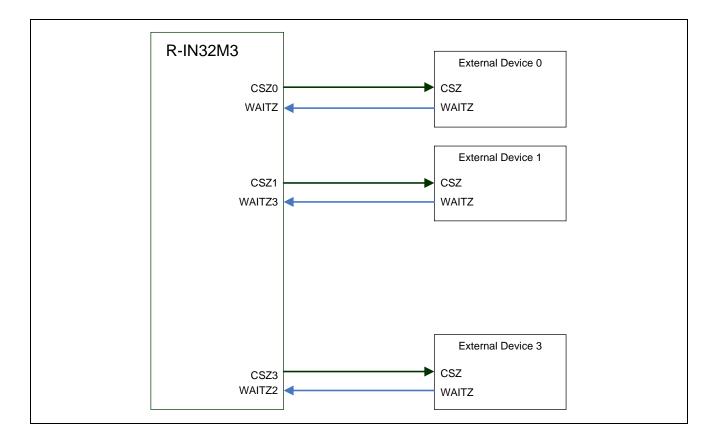

| Figu  | re 13.29 | Level Output Mode Operation Example 2                                        | 13-123 |