# 16

# R8C/M13B Group

## User's Manual: Hardware

RENESAS MCU R8C Family / R8C/Mx Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Renesas Electronics www.renesas.com

Rev.2.00 Mar 2012

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

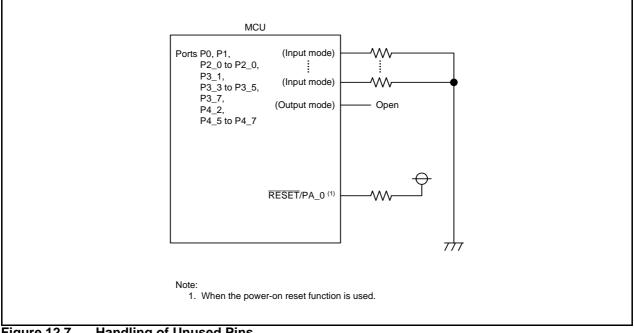

1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

- In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do

not access these addresses; the correct operation of LSI is not guaranteed if they are

accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

# How to Use This Manual

## 1. Purpose and Target Readers

This manual is designed to provide the user with an understanding of the hardware functions and electrical characteristics of the MCU. It is intended for users designing application systems incorporating the MCU. A basic knowledge of electric circuits, logical circuits, and MCUs is necessary in order to use this manual.

The manual comprises an overview of the product; descriptions of the CPU, system control functions, peripheral functions, and electrical characteristics; and usage notes.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. For details, see the text of the manual.

The following documents apply to the R8C/M13B Group. Make sure to see the latest versions of these documents. The newest versions of the documents listed may be obtained from the Renesas Electronics Web site.

| Document Type              | Description                                                                                                                                                                                                                                                | Document Title                               | Document No.       |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------|

| Datasheet                  | Hardware overview and electrical characteristics                                                                                                                                                                                                           | R8C/M13B Group<br>Datasheet                  | R01DS0005EJ0100    |

| User's manual:<br>Hardware | Hardware specifications (pin assignments, memory<br>maps, peripheral function specifications, electrical<br>characteristics, timing charts) and operation<br>description<br>Note: For details on using peripheral functions, see<br>the application notes. | R8C/M13B Group<br>User's Manual:<br>Hardware | This User's manual |

| User's manual:<br>Software | Description of CPU instruction set                                                                                                                                                                                                                         | R8C/Tiny Series<br>Software Manual           | REJ09B0001         |

| Application note           | Information on using peripheral functions and<br>application examples<br>Sample programs<br>Information on writing programs in assembly<br>language and C                                                                                                  | Available from Ren<br>Web site.              | esas Electronics   |

| Renesas technical update   | Product specifications, updates on documents, etc.                                                                                                                                                                                                         |                                              |                    |

## 2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below.

| (1) | Registers, bits<br>"bit," or "pin"<br>Examples | es, Bit Names, and Pin Names<br>, and pins are referred to in the text by symbols. The symbol is accompanied by the word "register,"<br>to distinguish the three categories.<br>the SRST bit in the PM0 register<br>P3_5 pin, VCC pin                                                                          |

|-----|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (2) | values of sing<br>appended to n<br>Examples    | umbers<br>n "b" is appended to numeric values given in binary format. However, nothing is appended to the<br>le bits. The indication "h" is appended to numeric values given in hexadecimal format. Nothing is<br>umeric values given in decimal format.<br>Binary: 11b<br>Hexadecimal: EFA0h<br>Decimal: 1234 |

## 3. Register Notation

The symbols and terms used in register diagrams are described below.

| Address XXXXh<br><u>Bit</u> <u>b7</u> <u>b6</u> <u>b5</u> <u>b4</u> <u>b3</u> <u>b2</u> <u>b1</u> <u>b0</u><br><u>After Reset</u> <u>0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | x.x.x                                                                                                                                              | XXX                                                                                                                                 | Regi                                                              | ster (Sy                                 | mbol)                                    |              |                               |                    |               |               |            |         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------|------------------------------------------|--------------|-------------------------------|--------------------|---------------|---------------|------------|---------|

| Symbol       XXX7       XXX6       XXS5       -       -       -       XXX1       XXX0       *1         After Reset       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                              | Address XXXXXh                                                                                                                                     |                                                                                                                                     |                                                                   |                                          |                                          |              |                               |                    |               |               |            |         |

| After Reset       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <th< td=""><td></td><td></td><td></td><td>b6</td><td>b5</td><td>b4</td><td>b3</td><td>b2</td><td>b1</td><td>b0</td><td></td><td></td></th<>                                                                                                         |                                                                                                                                                    |                                                                                                                                     |                                                                   | b6                                       | b5                                       | b4           | b3                            | b2                 | b1            | b0            |            |         |

| Bit       Symbol       Bit Name       Function       R/W         bit       0 0: XXX       0 0: XXX       R/W         b1       XX1       0 1: XXX       R/W         b2       -       Nothing is assigned. The write value must be 0. The read value is undefined.       -         b3       -       Reserved       Set to 0.       W         b4       -       .       W       W         b6       XXX6       XXX bits       Function varies depending on the operating mode.       R/W         b7       XXX7       XXX bit       0: XXX       R       R/W         b7       XXX7       XXX bit       0: XXX       R       R/W         b7       XXX7       XX bit       0: XXX       R       R/W         b7       XXX7       XX bit       0: XXX       R       R/W         b7       XXX7       XX bit       0: XXX       R       R/W         r       R/W       R       0: XXX       R       R/W         r       R                                                                                                                                                                                  | Sy                                                                                                                                                 | mbol X                                                                                                                              | XX7                                                               | XXX6                                     | XXX5                                     | —            | —                             | —                  | XXX1          | XXX0          |            | *1      |

| b0       XXX0       XXX bit       b1 to       0: XXX       RWW         b1       XXX1       VX bit       0: XXX       0: XXX       RWW         b1       XXX1       VX bit       0: XXX       0: XXX       RWW         b2       -       Nothing is assigned. The write value must be 0. The read value is undefined.       -       -         b3       -       Reserved       Set to 0.       W       W         b4       -       -       Set to 0.       W         b6       XXX5       XXX bits       Function varies depending on the operating mode.       R/W         b6       XXX6       IV       0: XXX       R       R/W         b7       XX7       XXX bit       0: XXX       R       R/W         b7       XX7       XXX bit       0: XXX       R/W       R/W         k7/W: Read and write.       R:       R:       R:       R       R/W         k7/W: Sead and write. </td <td>After F</td> <td>Reset</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td></td> <td></td> | After F                                                                                                                                            | Reset                                                                                                                               | 0                                                                 | 0                                        | 0                                        | 0            | 0                             | 0                  | 0             | 0             |            |         |

| b1       XXX1       0 0: XXX       RW         b1       XXX1       0 1: XXX       0 1: XXX         0 D: XXX       0 1: XXX       0 1: XXX         b2       -       Nothing is assigned. The write value must be 0. The read value is undefined.       -         b3       -       Reserved       Set to 0.       W         b6       XXX6       Function varies depending on the operating mode.       RW         b7       XXX7       XXX bits       Function varies depending on the operating mode.       RW         b7       XXX7       XX bit       0: XXX       R         *1       R/W: Read and write.       R:       Read only.       *2       *3         *1       R/W: Read and write.       R:       Read only.       *2       *3         *2       *3       *3       *1       *2       *3         *3       •Nothing is assigned.       Nothing is assigned.       Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.         •Do not set.       Operation is not guaranteed when a value is set.       •The function of the bit varies with the peripheral function mode. For information on the individual modes, see the                                                      | Bit                                                                                                                                                | Symbol                                                                                                                              |                                                                   | В                                        | it Name                                  |              |                               |                    | Function      |               |            | R/W     |

| b1       XXX1       01: XXX       RW         10: Do not set.       11: XXX       10: Do not set.       11: XXX         b2       -       Nothing is assigned. The write value must be 0. The read value is undefined.       -         b3       -       Reserved       Set to 0.       W         b6       XXX5       XXX bits       Function varies depending on the operating mode.       RW         b6       XXX6       XXX bits       0: XXX       R         b7       XXX7       XXX bit       0: XXX       R         *1       R/W: Read and write.       R: Read only.       *         *2       *3       *       *       *         *1       Nothing is assigned.       *       *         *2       *3       *       *       *         *2       *3       *       *       *         *3       •       •       •       •       •         *3       •       •       •       •       •         •       •       •       •       •       •         •       •       •       •       •       •         •       •       •       •       •                                                                                                                                                                                                          | b0                                                                                                                                                 | XXX0                                                                                                                                | XXX                                                               | bit                                      |                                          |              |                               | v                  |               |               |            | R/W     |

| b3       —       Reserved       Set to 0.       W         b4       —       Set to 0.       W         b5       XXX5       XXX bits       Function varies depending on the operating mode.       R/W         b6       XXX6       W       R/W       R/W         b7       XXX7       XXX bit       0: XXX       R         b7       XX7       XXX bit       0: XXX       R         *2       *3       *3       *1       R/W Read and write.         *2       *3       *3       *1       *3         • Nothing is assigned.       *3       *1000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                    | XXX1                                                                                                                                |                                                                   |                                          |                                          |              | 0 1: XX<br>1 0: Do<br>1 1: XX | X<br>not set.<br>X |               |               |            | R/W     |

| b4       -         b5       XXX5         b6       XXX6         b7       XXX7         b7       XXX7         xxx       bit         b7       XXX7         xxx       0: XXX         b7       XXX7         xxx       0: XXX         b7       XXx7         xxx bit       0: XXX         1: XXX       R         *2       *3         *1       R/W: Read and write.         R: Read only.       *2         *2       *3         *1       R/W: Read and write.         R: Read only.       *2         *2       *3         *1       Reserved         Reserved       Reserved         Reserved       Reserved         Reserved       Set to the specified value.         *3       Nothing is assigned.         Nothing is assigned.       Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.         *Do not set.       Operation is not guaranteed when a value is set.         *Function varies depending on the operating mode.       For information on the individual modes, see the                                                                                                                                                                                                          | b2                                                                                                                                                 | —                                                                                                                                   |                                                                   |                                          | ned. The w                               | rite value   |                               |                    | value is un   | defined.      |            | —       |

| b5       XXX5       XXX bits       Function varies depending on the operating mode.       R/W         b6       XXX6       R       R         b7       XXX7       XXX bit       0: XXX       R         b7       XXX7       XXX bit       0: XXX       R         *2       *3         *1       R/W: Read and write.       R: Read only.       *2       *3         *2       *3       *2       *3         *1       R/W: Read and write.       R: Read only.       *2       *3         *2       *3       *1       *2       *3         *1       R/W: Read and write.       R: Read only.       *2       *3         *2       *3       *3       *1       *3       *1         *3       *10 thing is assigned.       Nothing is assigned.       Nothing is assigned.       *0 on to set.         Operation is not guaranteed when a value is set.       *1       *1       *1       *1         • Function or aries depending on the operating mode.       *1       *1       *1       *1         *1       R       *2       *3       *3       *2       *3       *3         • Nothing is assigned.       Nothing is assigned.                                                                                                                           |                                                                                                                                                    | —                                                                                                                                   | Rese                                                              | rved                                     |                                          |              | Set to 0.                     |                    |               |               |            | W       |

| b6       XXX6       R/W         b7       XXX7       XXX bit       0: XXX         *2       *3         *1       R/W: Read and write.         R: Read only.       *2         *2       *3         *1       R/W: Read and write.         R: Read only.       *2         *3       *1         *3       *1         *3       *3         *3       *3         *10       Nothing is assigned.         Nothing is assigned.       Nothing is assigned.         Nothing is assigned.       Nothing is assigned.         *4       *3         • Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.         • Do not set.       Operation is not guaranteed when a value is set.         • Function varies depending on the operating mode.       The function of the bit varies with the peripheral function mode. For information on the individual modes, see the                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                    | —                                                                                                                                   |                                                                   | <u> </u>                                 |                                          |              |                               |                    |               |               |            |         |

| b7       XXX7       XXX bit       0: XXX<br>1: XXX       R         *2       *3         *1       R/W: Read and write.         R: Read only.       *2       *3         *1       R/W: Read and write.       R: Read only.         W: Write only.       -: Nothing is assigned.       *3         *2       *3       *1         *3       • Nothing is assigned.       *3         Nothing is assigned.       Nothing is assigned.         *0 portation is not guaranteed when a value is set.       *1         • Function varies depending on the operating mode.       The function of the bit varies with the peripheral function mode. For information on the individual modes, see the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                  |                                                                                                                                     |                                                                   | bits                                     |                                          |              | Function                      | i varies de        | pending on    | the operation | ing mode.  |         |

| <ul> <li>1: XXX</li> <li>*2</li> <li>*3</li> <li>*1 R/W: Read and write. R: Read only. W: Write only. —: Nothing is assigned. </li> <li>*2</li> <li>• Reserved Reserved Reserved Reserved to the specified value. </li> <li>*3 • Nothing is assigned. Nothing is assigned. Nothing is assigned. Do not set. Operation is not guaranteed when a value is set. • Function varies depending on the operating mode. The function of the bit varies with the peripheral function mode. For information on the individual modes, see the</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                    |                                                                                                                                     | VVV                                                               | L :4                                     | $ \rightarrow -$                         |              | 0. VVV                        |                    | $\setminus$ — |               |            |         |

| <ul> <li>*2 *3</li> <li>*1 R/W: Read and write. R: Read only. W: Write only. —: Nothing is assigned. </li> <li>*2 </li> <li>*2 </li> <li>*2 </li> <li>*3 Nothing is assigned. Nothing is assigned. Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0. *3 • Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0. • Do not set. Operation is not guaranteed when a value is set. • Function varies depending on the operating mode. The function of the bit varies with the peripheral function mode. For information on the individual modes, see the</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 07                                                                                                                                                 | ~~~/                                                                                                                                | ~~~                                                               | DIT                                      |                                          |              |                               |                    | $\backslash$  |               |            | ĸ       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W: RG<br>R: Read<br>W: Writ<br>—: Noth<br>*2<br>• Reserve<br>Reserve<br>*3<br>• Nothing<br>Nothin<br>• Do not s<br>Opera<br>• Function<br>The fu | only.<br>e only.<br>hing is ass<br>d<br>ved bits. S<br>is assigne<br>ng is assig<br>et.<br>tion is not<br>n varies de<br>unction of | igned.<br>et to th<br>d.<br>ned to<br>guaran<br>pendin<br>the bit | the bit. As<br>nteed wher<br>ng on the o | the bit may<br>a value is<br>perating mo | set.<br>ode. |                               |                    | -             |               | ual modes, | see the |

## 4. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                    |

|--------------|----------------------------------------------|

| ACIA         | Asynchronous Communication Interface Adapter |

| bps          | bits per second                              |

| CRC          | Cyclic Redundancy Check                      |

| DMA          | Direct Memory Access                         |

| DMAC         | Direct Memory Access Controller              |

| GSM          | Global System for Mobile Communications      |

| Hi-Z         | High Impedance                               |

| IEBus        | Inter Equipment Bus                          |

| I/O          | Input/Output                                 |

| IrDA         | Infrared Data Association                    |

| LSB          | Least Significant Bit                        |

| MSB          | Most Significant Bit                         |

| NC           | Non-Connect                                  |

| PLL          | Phase Locked Loop                            |

| PWM          | Pulse Width Modulation                       |

| SIM          | Subscriber Identity Module                   |

| UART         | Universal Asynchronous Receiver/Transmitter  |

| VCO          | Voltage Controlled Oscillator                |

## Table of Contents

| SFR Pag | e Reference E                                              | 3 - 1 |

|---------|------------------------------------------------------------|-------|

| 1. Ov   | erview                                                     | 1     |

| 1.1     | Features                                                   | 1     |

| 1.1.1   | Applications                                               | 1     |

| 1.1.2   | Specifications                                             | 2     |

| 1.2     | Product List                                               |       |

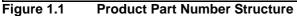

| 1.3     | Block Diagram                                              | 5     |

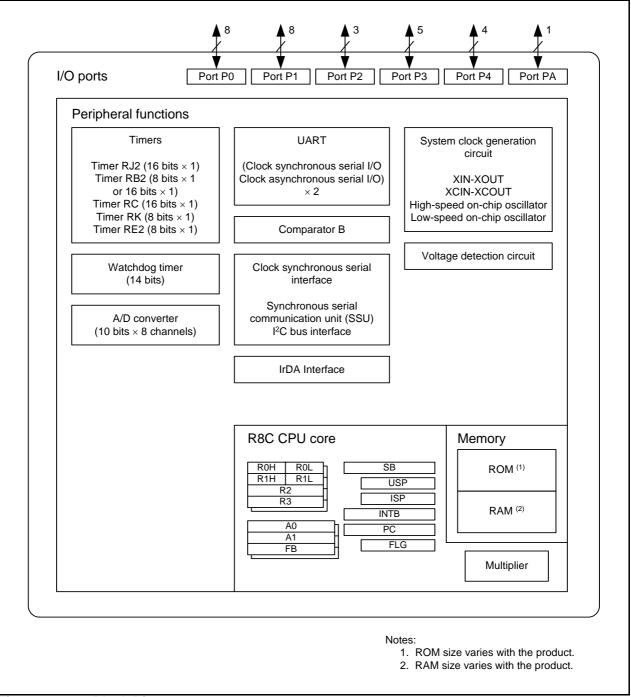

| 1.4     | Pin Assignment                                             | 6     |

| 1.5     | Pin Functions                                              | 8     |

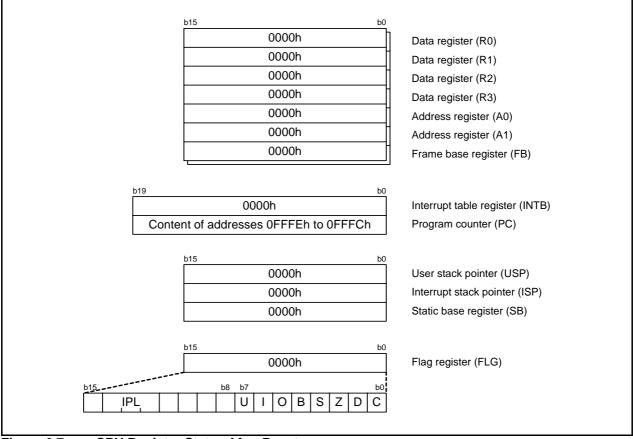

| 2. Ce   | ntral Processing Unit (CPU)                                | . 10  |

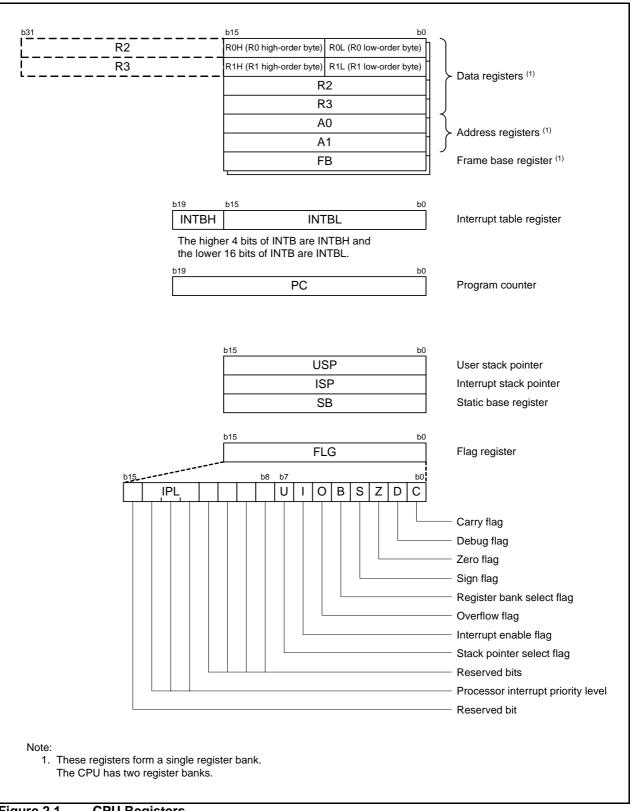

| 2.1     | Data Registers (R0, R1, R2, and R3)                        |       |

| 2.2     | Address Registers (A0 and A1)                              |       |

| 2.3     | Frame Base Register (FB)                                   |       |

| 2.4     | Interrupt Table Register (INTB)                            |       |

| 2.5     | Program Counter (PC)                                       |       |

| 2.6     | User Stack Pointer (USP) and Interrupt Stack Pointer (ISP) |       |

| 2.7     | Static Base Register (SB)                                  |       |

| 2.8     | Flag Register (FLG)                                        |       |

| 2.8.1   | Carry Flag (C)                                             |       |

| 2.8.2   | Debug Flag (D)                                             |       |

| 2.8.3   | Zero Flag (Z)                                              |       |

| 2.8.4   | Sign Flag (S)                                              |       |

| 2.8.5   | Register Bank Select Flag (B)                              |       |

| 2.8.6   | Overflow Flag (O)                                          |       |

| 2.8.7   | Interrupt Enable Flag (I)                                  |       |

| 2.8.8   | Stack Pointer Select Flag (U)                              |       |

| 2.8.9   | Processor Interrupt Priority Level (IPL)                   |       |

| 2.8.10  | Reserved Bit                                               | 12    |

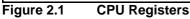

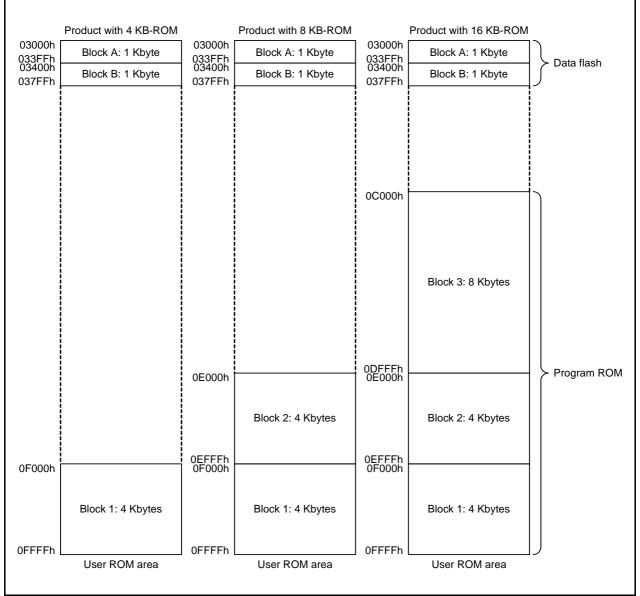

| 3. Ac   | dress Space                                                | . 13  |

| 3.1     | Memory Map                                                 | 13    |

| 3.2     | Special Function Registers (SFRs)                          |       |

| 4. Bu   | s Control                                                  | . 23  |

| 5. Sy   | stem Control                                               | . 24  |

| 5.1     | Overview                                                   | 24    |

| 5.2     | Registers                                                  | 24    |

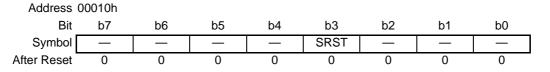

| 5.2.1   | Processor Mode Register 0 (PM0)                            | 25    |

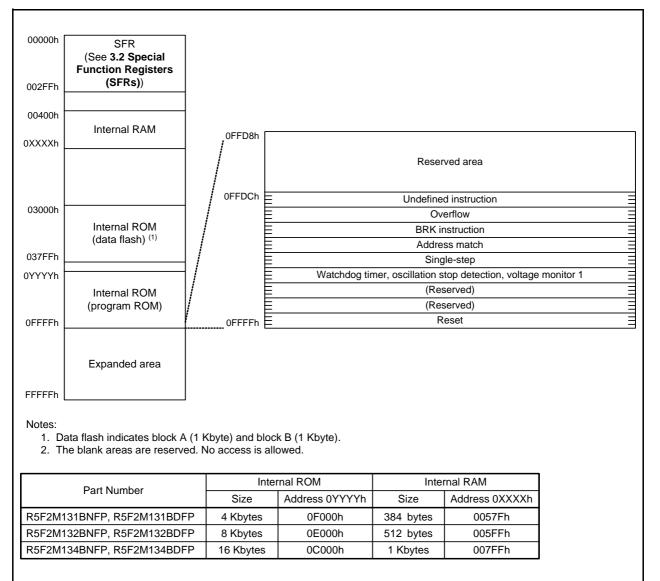

| 5.2.2   | Module Standby Control Register (MSTCR)                    | 26    |

| 5.2.3   | Protect Register (PRCR)                                    | 27    |

| 5.2.4   | Hardware Reset Protect Register (HRPR)                     | 27    |

| 5.2.5   | Module Standby Control Register 1 (MSTCR1)                 | 28    |

| 5.2.6   | Reset Source Determination Register (RSTFR)                | 29    |

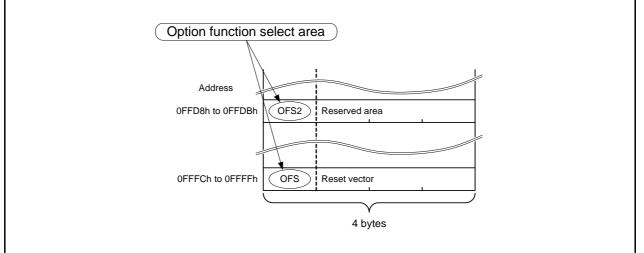

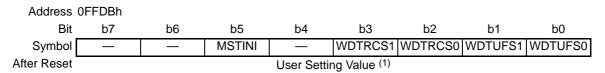

| 5.2.7   | Option Function Select Register 2 (OFS2)                   | 31    |

| 5.2.8   | Option Function Select Register (OFS)                      | 32    |

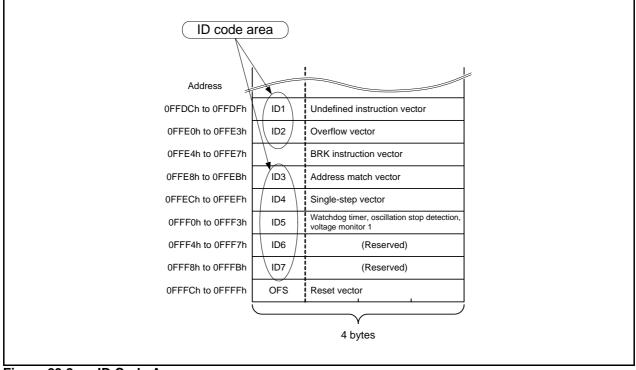

| 5.3     | ID Code Check Function                                     | 33    |

| 5.4                                                                                                                                                     | Register Access Protect Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 5.5                                                                                                                                                     | Option Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34                   |

| 5.6                                                                                                                                                     | Notes on System Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35                   |

| 5.6.1                                                                                                                                                   | Option Function Select Area Setting Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35                   |

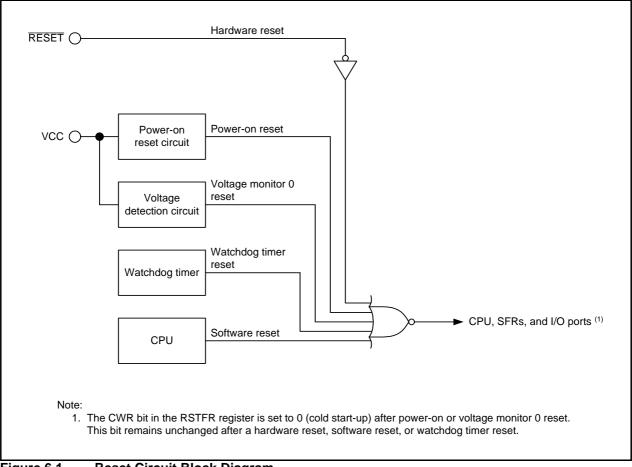

| 6. Re                                                                                                                                                   | esets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36                   |

| 6.1                                                                                                                                                     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36                   |

| 6.2                                                                                                                                                     | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37                   |

| 6.2.1                                                                                                                                                   | Processor Mode Register 0 (PM0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37                   |

| 6.2.2                                                                                                                                                   | Reset Source Determination Register (RSTFR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38                   |

| 6.2.3                                                                                                                                                   | Option Function Select Register 2 (OFS2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40                   |

| 6.2.4                                                                                                                                                   | Option Function Select Register (OFS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 41                   |

| 6.3                                                                                                                                                     | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42                   |

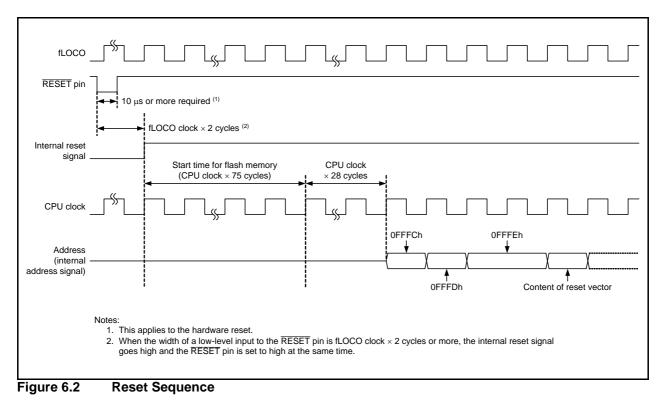

| 6.3.1                                                                                                                                                   | Reset Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42                   |

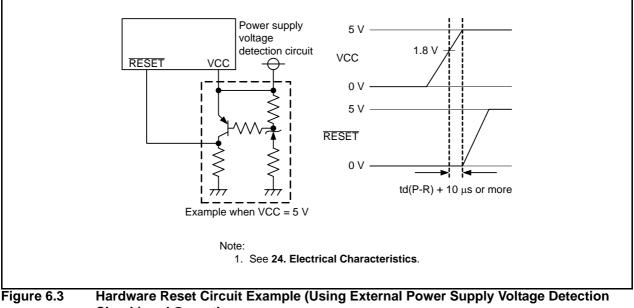

| 6.3.2                                                                                                                                                   | Hardware Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43                   |

| 6.3.3                                                                                                                                                   | Power-On Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44                   |

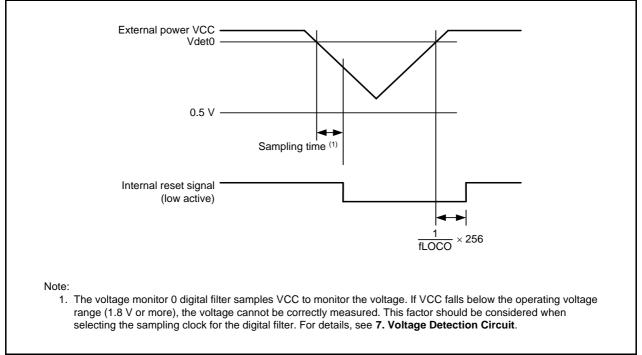

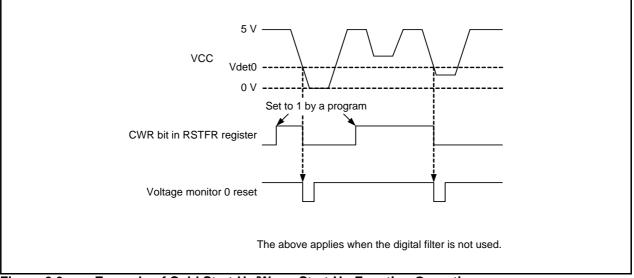

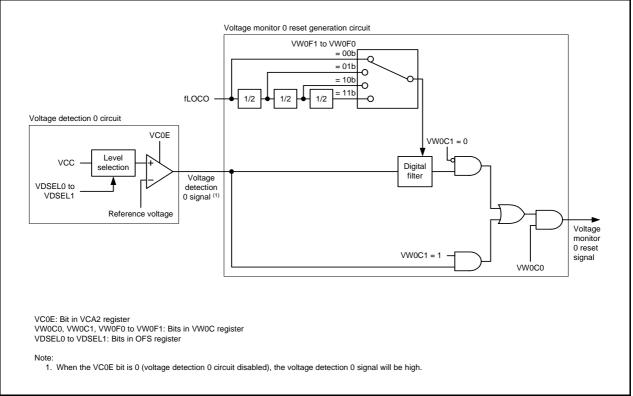

| 6.3.4                                                                                                                                                   | Voltage Monitor 0 Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45                   |

| 6.3.5                                                                                                                                                   | Watchdog Timer Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46                   |

| 6.3.6                                                                                                                                                   | Software Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46                   |

| 6.3.7                                                                                                                                                   | Cold Start-Up/Warm Start-Up Determination Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| 6.3.8                                                                                                                                                   | Reset Source Determination Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47                   |

| 6.4                                                                                                                                                     | States during Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48                   |

| 6.4.1                                                                                                                                                   | Pin States While RESET Pin Level is Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48                   |

| 6.4.2                                                                                                                                                   | CPU Register States After Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49                   |

|                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |

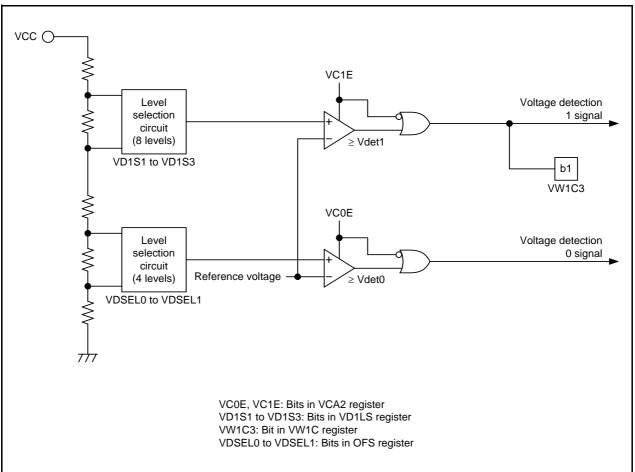

| 7. Vo                                                                                                                                                   | Itage Detection Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50                   |

| 7. Vo<br>7.1                                                                                                                                            | Itage Detection Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |

|                                                                                                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50                   |

| 7.1                                                                                                                                                     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50<br>53             |

| 7.1<br>7.2                                                                                                                                              | Overview<br>Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50<br>53<br>53       |

| 7.1<br>7.2<br>7.2.1                                                                                                                                     | Overview<br>Registers<br>Voltage Monitor Circuit Edge Select Register (VCAC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50<br>53<br>53<br>54 |

| 7.1<br>7.2<br>7.2.1<br>7.2.2                                                                                                                            | Overview<br>Registers<br>Voltage Monitor Circuit Edge Select Register (VCAC)<br>Voltage Detect Register 2 (VCA2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3                                                                                                                   | Overview<br>Registers<br>Voltage Monitor Circuit Edge Select Register (VCAC)<br>Voltage Detect Register 2 (VCA2)<br>Voltage Detection 1 Level Select Register (VD1LS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4                                                                                                          | Overview<br>Registers<br>Voltage Monitor Circuit Edge Select Register (VCAC)<br>Voltage Detect Register 2 (VCA2)<br>Voltage Detection 1 Level Select Register (VD1LS)<br>Voltage Monitor 0 Circuit Control Register (VW0C)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5                                                                                                 | Overview<br>Registers<br>Voltage Monitor Circuit Edge Select Register (VCAC)<br>Voltage Detect Register 2 (VCA2)<br>Voltage Detection 1 Level Select Register (VD1LS)<br>Voltage Monitor 0 Circuit Control Register (VW0C)<br>Voltage Monitor 1 Circuit Control Register (VW1C)                                                                                                                                                                                                                                                                                                                                                                                                         |                      |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.3                                                                                          | Overview<br>Registers<br>Voltage Monitor Circuit Edge Select Register (VCAC)<br>Voltage Detect Register 2 (VCA2)<br>Voltage Detection 1 Level Select Register (VD1LS)<br>Voltage Monitor 0 Circuit Control Register (VW0C)<br>Voltage Monitor 1 Circuit Control Register (VW1C)                                                                                                                                                                                                                                                                                                                                                                                                         |                      |