# RENESAS

## IPS2200

## Contents

| 1. | 1. Introduction |          |                                                  | 5  |

|----|-----------------|----------|--------------------------------------------------|----|

| 2. | IPS2            | 200 Bloc | k Diagram                                        | 6  |

| 3. | Mem             | ory Arch | itecture                                         | 7  |

|    | 3.1             | Nonvola  | atile Memory (NVM)                               | 7  |

|    | 3.2             | Shadow   | / Register Bank                                  | 8  |

|    | 3.3             | Special  | Function Register                                | 8  |

|    | 3.4             | Main Re  | egisters Overview                                | 9  |

|    | 3.5             | Registe  | r Descriptions                                   | 10 |

|    |                 | 3.5.1.   | System Configuration 1                           | 10 |

|    |                 | 3.5.2.   | System Configuration 2                           | 11 |

|    |                 | 3.5.3.   | Receiver 1/2 Gain                                | 12 |

|    |                 | 3.5.4.   | System Configuration 3                           | 13 |

|    |                 | 3.5.5.   | R2 Coil Offset                                   | 14 |

|    |                 | 3.5.6.   | R1 Coil Offset                                   | 15 |

|    |                 | 3.5.7.   | Transmitter Current Calibration                  | 16 |

|    |                 | 3.5.8.   | Transmitter Frequency Time Base                  | 18 |

|    |                 | 3.5.9.   | Transmitter Lower Limit                          | 19 |

|    |                 | 3.5.10.  | Transmitter Upper Limit                          | 19 |

|    |                 | 3.5.11.  | Interrupt Enable 1                               | 20 |

|    |                 | 3.5.12.  | Interrupt Enable 2                               | 21 |

|    |                 | 3.5.13.  | <b>.</b>                                         |    |

|    |                 | 3.5.14.  | IRQN Watchdog 2                                  | 23 |

|    |                 | 3.5.15.  | R1 Fine Gain                                     | 24 |

|    |                 | 3.5.16.  | R2 Fine Gain                                     | 24 |

|    |                 | 3.5.17.  | Product Identification                           | 25 |

|    |                 | 3.5.18.  | Interrupt Clear 1                                | 25 |

|    |                 | 3.5.19.  | Interrupt Clear 2                                | 26 |

|    |                 | 3.5.20.  | Interrupt State 1                                |    |

|    |                 | 3.5.21.  | Interrupt State 2                                | 29 |

|    |                 | 3.5.22.  | Transmitter Counter State                        |    |

|    |                 | 3.5.23.  | NVM ECC Fail State                               | 31 |

|    |                 | 3.5.24.  | SFR Internal Registers                           | 31 |

| 4. | -               |          | 32                                               |    |

|    | 4.1             | Half-Du  | plex SPI Interface                               | 32 |

|    |                 | 4.1.1.   | Interfacing the IPS2200 with a 4-Wire SPI Master |    |

|    |                 | 4.1.2.   | Bit Error Checks                                 | 34 |

|    |                 | 4.1.3.   | Burst READ Operation                             | 35 |

|    |                 | 4.1.4.   | Burst WRITE Operation                            | 35 |

|    | 4.2   | SPI Data  | a Word Definition                                    | . 36 |

|----|-------|-----------|------------------------------------------------------|------|

|    |       | 4.2.1.    | SPI Data Integrity Check                             | . 36 |

|    | 4.3   | Half-Dup  | ex SPI Interface with Interrupt (Programming Option) | . 37 |

|    | 4.4   | I2C Inter | face                                                 | . 39 |

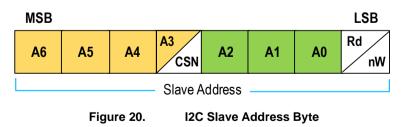

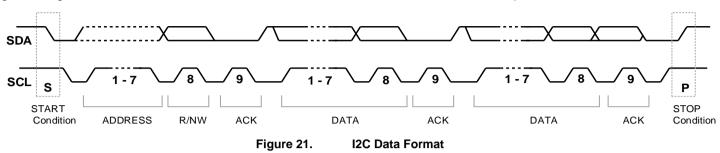

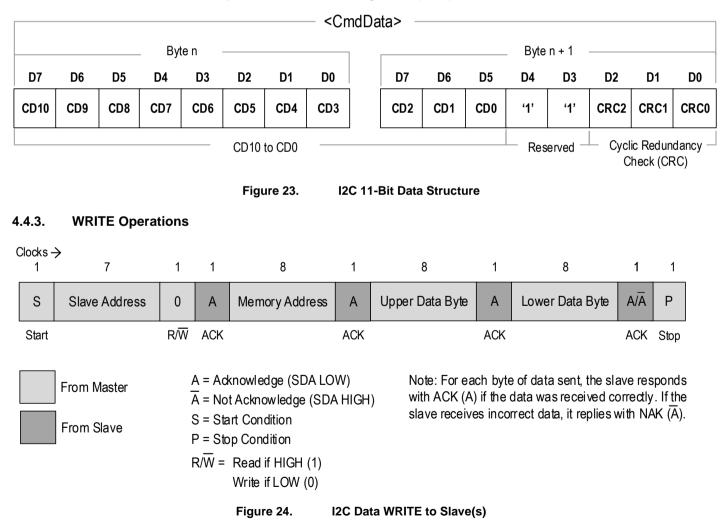

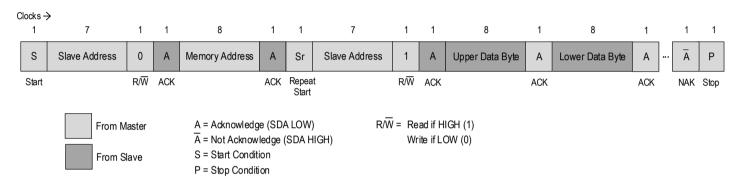

|    |       | 4.4.1.    | I2C Data Format                                      | . 40 |

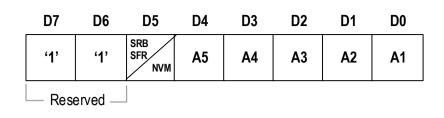

|    |       | 4.4.2.    | I2C Data Frame Structure                             | . 41 |

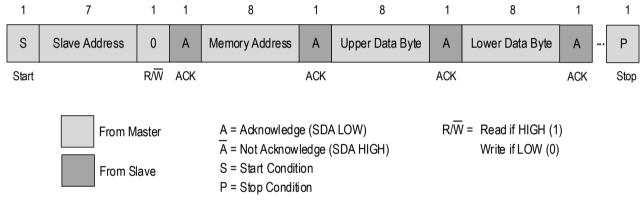

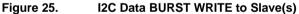

|    |       | 4.4.3.    | WRITE Operations                                     |      |

|    |       | 4.4.4.    | READ Operations                                      | .44  |

|    |       | 4.4.5.    | I2C Integrity Check                                  | . 45 |

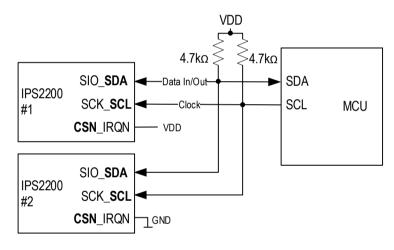

|    |       | 4.4.6.    | I2C with Address Selection (Programming Option)      | . 46 |

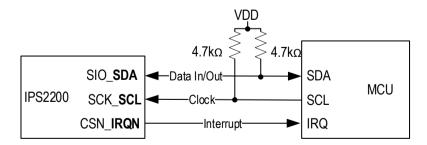

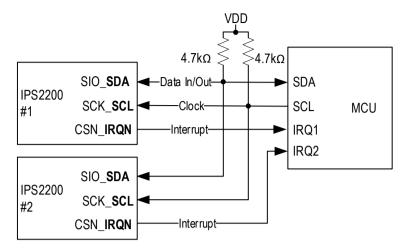

|    |       | 4.4.7.    | I2C Interface with Interrupt (Programming Option)    | .46  |

| 5. | Gloss | sary      |                                                      | . 48 |

| 6. | Revis | ion Histe | ory                                                  | . 48 |

## Figures

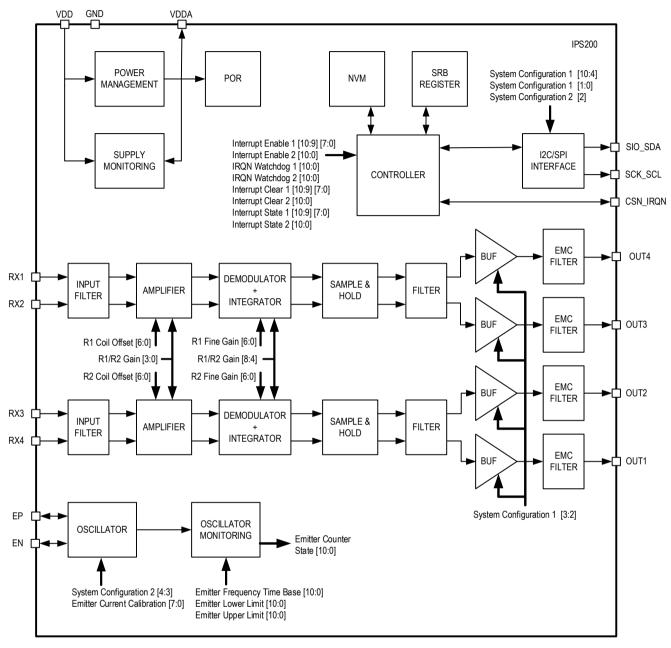

| Figure 1.  | Block Diagram                                                              | 6  |

|------------|----------------------------------------------------------------------------|----|

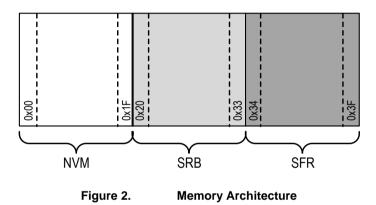

| Figure 2.  | Memory Architecture                                                        | 7  |

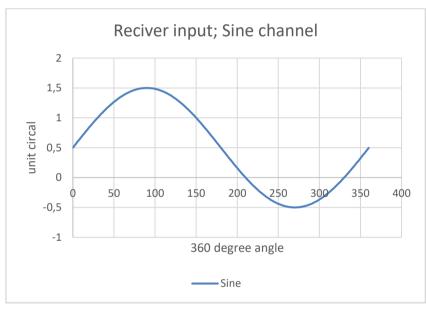

| Figure 3.  | Receiver Input Signal with 0.5 Offset                                      | 14 |

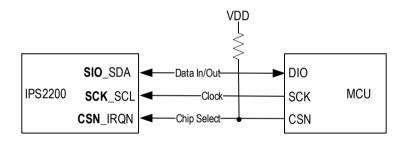

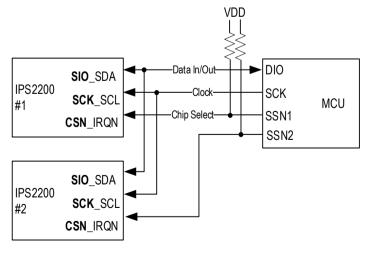

| Figure 4.  | Half Duplex 3-3 Wire SPI Interface                                         | 32 |

| Figure 5.  | Half Duplex 3-3 Wire SPI Multi-slave Interface                             | 32 |

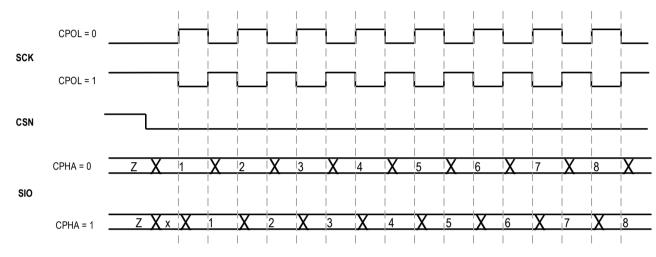

| Figure 6.  | SPI 3-Wire Operating Mode                                                  | 33 |

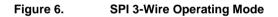

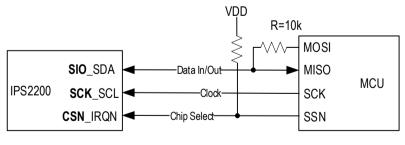

| Figure 7.  | Half Duplex 3-4 Wire SPI Interface                                         | 33 |

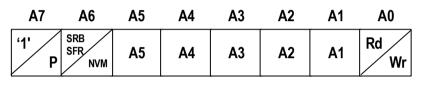

| Figure 8.  | SPI 3-Wire Address/Command Byte                                            | 34 |

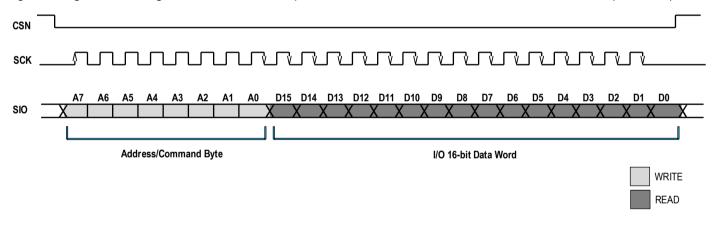

| Figure 9.  | SPI Single Word Read                                                       | 34 |

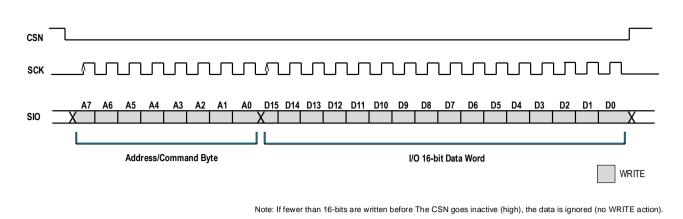

| Figure 10. | SPI Single Word Write                                                      | 35 |

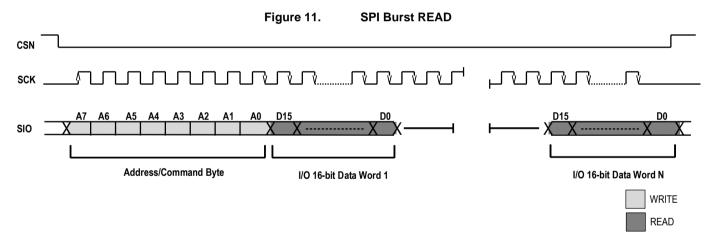

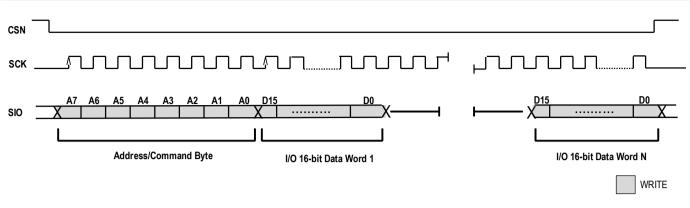

| Figure 11. | SPI Burst READ                                                             | 35 |

| Figure 12. | SPI Burst WRITE                                                            | 36 |

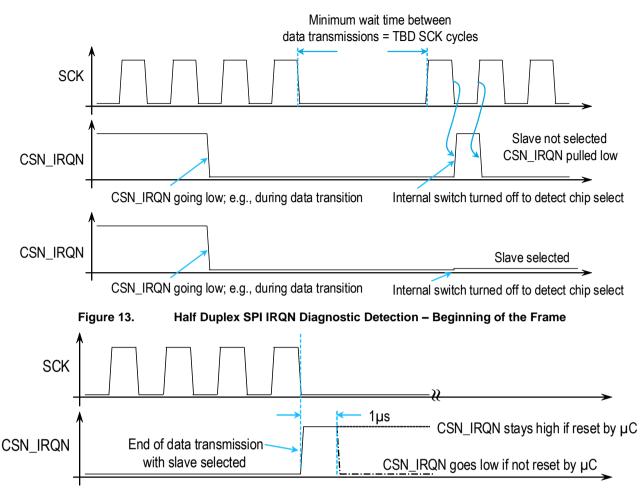

| Figure 13. | Half Duplex SPI IRQN Diagnostic Detection – Beginning of the Frame         | 38 |

| Figure 14. | Half Duplex SPI IRQN Diagnostic Detection – End of the Frame               |    |

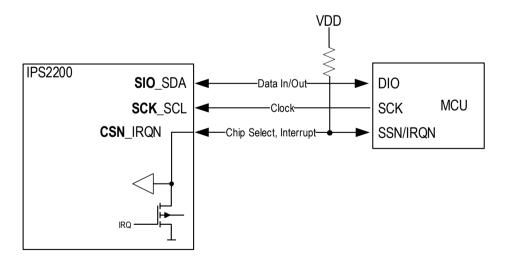

| Figure 15. | Half Duplex 3-3 Wire SPI Interface with Interrupt                          |    |

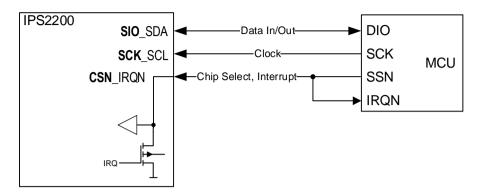

| Figure 16. | Half Duplex 3-3 Wire SPI Interface with CSN_IRQN and IRQN Separated at MCU |    |

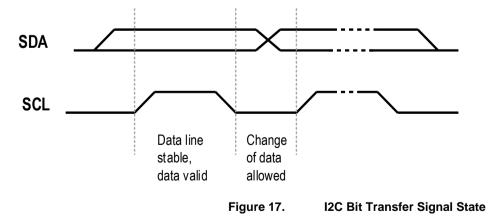

| Figure 17. | I2C Bit Transfer Signal State                                              |    |

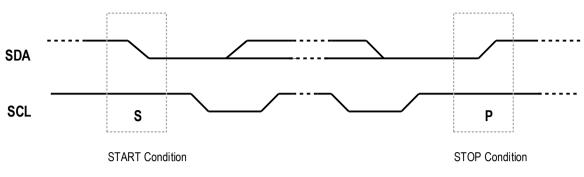

| Figure 18. | I2C START and STOP Conditions                                              | 40 |

| Figure 19. | I2C Acknowledge Signal State                                               | 40 |

| Figure 20. | I2C Slave Address Byte                                                     | 40 |

| Figure 21. | I2C Data Format                                                            | 41 |

| Figure 22. | Memory Address in Selected I2C Slave                                       | 42 |

| Figure 23. | I2C 11-Bit Data Structure                                                  | 42 |

| Figure 24. | I2C Data WRITE to Slave(s)                                                 | 42 |

| Figure 25. | I2C Data BURST WRITE to Slave(s)                                           | 43 |

| Figure 26. | I2C Data READ from Slave(s) with Repeated START                            | 44 |

| Figure 27. | Memory Address of Selected I2C Slave with Integrity Check                  | 45 |

| Figure 28. | I2C Interface with Address Select                                          | 46 |

| Figure 29. | I2C Interface Configuration with Interrupt on a Single Slave               | 46 |

| Figure 30. | I2C Interface Configuration with Multi-slave Interrupt47 |

|------------|----------------------------------------------------------|

|            |                                                          |

## Tables

| Table 1.  | NVM to SRB Address Mapping                                | 8  |

|-----------|-----------------------------------------------------------|----|

| Table 2.  | SFR Address Mapping                                       | 9  |

| Table 3.  | Register Overview                                         | 9  |

| Table 4.  | System Configuration 1 Register Details                   | 10 |

| Table 5.  | System Configuration 1 Register Bit Descriptions          | 10 |

| Table 6.  | I2C Slave Address Configuration                           | 11 |

| Table 7.  | System Configuration 2 Register Details                   | 11 |

| Table 8.  | System Configuration 2 Register Bit Descriptions          | 11 |

| Table 9.  | Receiver 1/2 Gain Register Details                        | 12 |

| Table 10. | Receiver 1/2 Gain                                         | 12 |

| Table 11. | System Configuration 3 Register Details                   | 13 |

| Table 12. | System Configuration 3 Register Bit Definitions           | 13 |

| Table 13. | R2 Coil Offset Register Details                           | 14 |

| Table 14. | R2 Coil Offset Register Bit Definitions                   | 14 |

| Table 15. | R1 Coil Offset Register Details                           | 15 |

| Table 16. | R1 Coil Offset Register Bit Definitions                   | 15 |

| Table 17. | Transmitter Current Calibration Register Details          | 16 |

| Table 18. | Transmitter Current Calibration Register Bit Definitions  |    |

| Table 19. | Transmitter Bias Current Settings                         | 17 |

| Table 20. | Transmitter Frequency Time Base Register Details          | 18 |

| Table 21. | Transmitter Frequency Time Base Register Bit Descriptions | 19 |

| Table 22. | Transmitter Lower Limit Register Details                  | 19 |

| Table 23. | Transmitter Lower Limit Register Bit Descriptions         | 19 |

| Table 24. | Transmitter Upper Limit Register Details                  | 19 |

| Table 25. | Transmitter Upper Limit Register Bit Descriptions         | 20 |

| Table 26. | Interrupt Enable 1 Register Details                       | 20 |

| Table 27. | Interrupt Enable 1 Register Bit Descriptions              | 20 |

| Table 28. | Interrupt Enable 2 Register Details                       | 21 |

| Table 29. | Interrupt Enable 2 Register Bit Descriptions              | 22 |

| Table 30. | IRQN Watchdog 1 Register Details                          | 22 |

| Table 31. | IRQN Watchdog 1 Register Bit Descriptions                 | 23 |

| Table 32. | IRQN Watchdog 2 Register Details                          | 23 |

| Table 33. | IRQN Watchdog 2 Register Bit Descriptions                 | 23 |

| Table 34. | R1 Fine Gain Register Details                             | 24 |

| Table 35. | R1 Fine Gain Register Bit Definitions                     | 24 |

| Table 36. | R2 Fine Gain Register Details                             | 24 |

| Table 37. | R2 Fine Gain Register Bit Definitions                     | 24 |

| Table 38. | Interrupt Clear 1 Register Details                        | 25 |

| Table 39. | Interrupt Clear 1 Register Bit Definitions                | 25 |

| Table 40. | Interrupt Clear 2 Register Details                        | 26 |

| Table 41. | Interrupt Clear 2 Register Bit Definitions                | 26 |

| Table 42. | Interrupt State 1 Register Details                        | 28 |

| Table 43. | Interrupt State 1 Register Bit Definitions                      | .28  |

|-----------|-----------------------------------------------------------------|------|

| Table 44. | Interrupt State 2 Register Details                              | .29  |

| Table 45. | Interrupt State 2 Register Bit Definitions                      | .29  |

| Table 46. | Transmitter Counter State Register Details                      | . 30 |

| Table 47. | Transmitter Counter State Register Bit Definitions              | . 30 |

| Table 48. | NVM ECC Status Register Details                                 | . 31 |

| Table 49. | NVM ECC Status Register Bit Definitions                         | .31  |

| Table 50. | SPI Address / Command Byte Integrity Check                      | .37  |

| Table 51. | I2C Single WRITE to Memory                                      | .43  |

| Table 52. | I2C Burst WRITE to Memory                                       | .43  |

| Table 53. | I2C Burst READ from Memory with Repeated Start                  | .44  |

| Table 54. | I2C Slave Address Byte and Memory Address Field Integrity Check | .46  |

## 1. Introduction

The IPS2200 inductive position sensor ICs is used for high-speed absolute position sensing in automotive, industrial, medical, and consumer applications. The default configuration can be adapted for specific applications via programming.

The Non-Volatile Memory (NVM) of IPS2200 can be accessed through two independent interfaces: I2C or SPI. These two interfaces can be used only to program the IPS2200 settings or read the diagnostic flags.

The target position can be read through the sine and cosine output interface, which can be single ended or differential.

With a specific IC setting, it is possible to turn the sine and cosine signals into a quadrature signals providing 4 positions per electrical rotation (for more details, see the IPS2200 Datasheet).

This document provides instructions for programming the IPS2200 via the I2C and SPI interfaces and utilizing the diagnostic features.

The programming of the IPS2200 is needed for the Transmitter settings, the complete signal path, the output configuration, the diagnostics and the communication protocol to ensure excellent sensing performance.

**Recommendation**: Before using this document, read the *IPS2200 Datasheet* for product details, such as features, pin descriptions, functionality, and circuit descriptions and the IPS2200 Eval Kit User Manual before reading this Manual.

## Default configuration:

- The default interface is I2C with pin 1 (CSn\_IRQN) configured as address input.

- The default I2C slave address is 24dec (18hex) if address in is 'high', and 16dec (10 hex) if the address pin is 'low'.

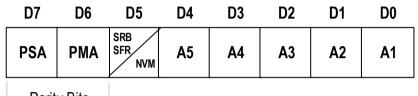

Note that for the I2C interface, the most significant two bits of the memory address are always '1' (D7,D6) and register address bits are D5...D0. For details see section 4.4.2.2.

## 2. IPS2200 Block Diagram

The block diagram below shows the main blocks associated with the registers described in this document.

Figure 1.

**Block Diagram**

## 3. Memory Architecture

The memory architecture of the IPS2200 consists of three different storage blocks with a total address range of 6 bits as describe below:

- Nonvolatile Memory (NVM)

00<sub>HEX</sub> through 1F<sub>HEX</sub>

- Shadow Register Bank (SRB) 20HEX through 33HEX

- Special Function Register (SFR)

34<sub>HEX</sub> through 3F<sub>HEX</sub>

All storage blocks are accessible by read/write access via the I2C and SPI interface.

Note that some registers can be modified by internal processes.

After power-on-reset (POR); the NVM contents of the address range  $00_{HEX}$  to  $12_{HEX}$  are copied to the SRB address range  $20_{HEX}$  to  $32_{HEX}$  within the startup time window of 3ms.

Note: after writing to an FTP register, a programming time of minimum 3ms is required before a new command can be sent.

## 3.1 Nonvolatile Memory (NVM)

The nonvolatile memory has a size of 32 words  $\times$  16-bits. For enhanced reliability, the stored information can be checked for bit-errors. This has been implemented by adding a redundant 5-bit parity word concatenated with the stored information. The parity word can be considered as an error-correction code (ECC, even-parity Hamming code).

If a bit error in the NVM occurs in the addressed word, an automatic single-error correction is performed providing correct data to the outputs and flagged as a diagnostics SED (single-error detection) warning. If two bits in the addressed word have errors, a warning flag DED (double-error detection) is asserted.

The NVM memory organization is as follows:

N = n + p

Where:

N= code-word length (16 bit)

n = information length (11 bit)

p = parity length (5 bit)

The maximum parameter length that can be stored in one NVM word is 11 bits. The parity bit extension, single-bit error correction, and double-bit error check are done automatically with each write/read access to the corresponding address range.

Only the 11-bit word (Data 10 to Data 0; see Table 1) can be read/written by the I2C/SPI interface with the exception of register addresses 0F<sub>HEX</sub> to 1F<sub>HEX</sub>, which are read only.

## 3.2 Shadow Register Bank

Some parameters of the NVM (see Table 3) are copied into the corresponding Shadow Register Bank (SRB) address range after a POR within the startup time window of 3ms. All these parameters are protected by error correction and detection mechanisms, which calculate a 5-bit error code (see section 3.1). If these parameters are modified by the external communication interface (I2C, SPI), the error-code is evaluated automatically and concatenated. Single-bit errors are corrected and flagged, double-bit errors are flagged.

Only the 11-bit word (Data 10 to Data 0) can be read/written by the I2C/SPI interface with the exception of read-only register addresses 20<sub>HEX</sub>, 21<sub>HEX</sub>, 2F<sub>HEX</sub>, 30<sub>HEX</sub>, and 31<sub>HEX</sub>.

|                   |                   |                                          |                  | Bit Position     |                   |  |

|-------------------|-------------------|------------------------------------------|------------------|------------------|-------------------|--|

| NVM Address       | SRB Address       | Description                              | Bits 15 to 12    | Bit 11           | Bits 10 to 0      |  |

| 00 <sub>HEX</sub> | 20 <sub>HEX</sub> | System configuration 1                   | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 01 <sub>HEX</sub> | 21 <sub>HEX</sub> | System configuration 2                   | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 02 <sub>HEX</sub> | 22 <sub>HEX</sub> | R1/R2 gain                               | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 03 <sub>HEX</sub> | 23 <sub>HEX</sub> | System configuration 3                   | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 04 <sub>HEX</sub> | 24 <sub>HEX</sub> | R2 coil offset                           | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 05 <sub>HEX</sub> | 25 <sub>HEX</sub> | internal use                             | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 06 <sub>HEX</sub> | 26 <sub>HEX</sub> | R1 coil offset                           | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 07 <sub>HEX</sub> | 27 <sub>HEX</sub> | Transmitter calibration                  | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 08 <sub>HEX</sub> | 28 <sub>HEX</sub> | Transmitter frequency timebase           | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 09 <sub>HEX</sub> | 29 <sub>HEX</sub> | Transmitter frequency lower limit        | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 0A <sub>HEX</sub> | 2A <sub>HEX</sub> | Transmitter frequency upper limit        | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 0B <sub>HEX</sub> | 2B <sub>HEX</sub> | Iren 1                                   | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 0C <sub>HEX</sub> | 2C <sub>HEX</sub> | Iren 2                                   | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 0D <sub>HEX</sub> | 2D <sub>HEX</sub> | IRQN watchdog 1                          | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 0E <sub>HEX</sub> | 2E <sub>HEX</sub> | IRQN watchdog 2                          | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 0F <sub>HEX</sub> | 2F <sub>HEX</sub> | Renesas internal configuration registers | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 10 <sub>HEX</sub> | 30 <sub>HEX</sub> | Renesas internal configuration registers | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 11 <sub>HEX</sub> | 31 <sub>HEX</sub> | Renesas internal configuration registers | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 12 <sub>HEX</sub> | 32 <sub>HEX</sub> | R1 fine gain                             | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 13 <sub>HEX</sub> | 33 <sub>HEX</sub> | R2 fine gain                             | ECC              | P <sub>DED</sub> | Data 10 to Data 0 |  |

| 14 <sub>HEX</sub> |                   | Not used                                 | Read as 'x       |                  |                   |  |

| 15 <sub>HEX</sub> |                   | Not used                                 | Read as 'x       |                  |                   |  |

| 16 <sub>HEX</sub> |                   | Not used                                 | Read as 'x       |                  |                   |  |

| 17 <sub>HEX</sub> |                   | Not used                                 | Read as 'x       |                  |                   |  |

| 18 <sub>HEX</sub> |                   | Not used                                 | Read as 'x       |                  |                   |  |

| 19 <sub>HEX</sub> | n.a.              | Product identifier                       | Renesas intern   | al               |                   |  |

| 1A <sub>HEX</sub> | n.a.              | Product identifier                       | Renesas intern   | al               |                   |  |

| 1B <sub>HEX</sub> | n.a.              | Product identifier                       | Renesas intern   | al               |                   |  |

| 1C <sub>HEX</sub> | n.a.              | Product identifier                       | Renesas intern   | al               |                   |  |

| 1D <sub>HEX</sub> | n.a.              | Product identifier                       | Renesas internal |                  |                   |  |

| 1E <sub>HEX</sub> | n.a.              | Product identifier                       | Renesas internal |                  |                   |  |

| 1F <sub>HEX</sub> | n.a.              | Product identifier                       | Renesas intern   | al               |                   |  |

#### Table 1. NVM to SRB Address Mapping

## 3.3 Special Function Register

Special Function Register (SFR) has all the diagnostic registers. It can be used in real-time and has two main functions:

- If there is an interrupt state, a diagnostic flag (dependent on the failure event) is asserted.

- If the failure event disappears, SFR updates the register and clears the flag only when the NMV is set to: Addr: 0x03 bit [10] - intr\_volatile\_mode

Depending on this bit setting the flags in the interrupt registers either clear automatically after some debounce timeout or have to be cleared externally by writing 1 to irclr (interrupt clear) register.

The NVM is not copied to the SFR during the power up of IC. The flags, write and read can be effected dynamically without interruption of the sensor functionality. Volatile parameters (for example, transmitter counter state) are not protected by an error-code and are stored in the SFR. The contents of these registers can be modified during operation by internal processes and by the digital interface (I2C, SPI) read/write access.

The product identifier version code (address 3EHEX) is hardcoded and does not change.

#### Table 2. SFR Address Mapping

|                                                                    |                           | Bit Position  |                   |  |  |

|--------------------------------------------------------------------|---------------------------|---------------|-------------------|--|--|

| Address                                                            | Description               | Bits 15 to 11 | Bits 10 to 0      |  |  |

| 34 <sub>HEX</sub>                                                  | Interrupt clear 1         | Not used      | Data 10 to Data 0 |  |  |

| 35 <sub>HEX</sub>                                                  | Interrupt clear 2         | Not used      | Data 10 to Data 0 |  |  |

| 36 <sub>HEX</sub>                                                  | Interrupt state 1         | Not used      | Data 10 to Data 0 |  |  |

| 37 <sub>HEX</sub>                                                  | Interrupt state 2         | Not used      | Data 10 to Data 0 |  |  |

| 38 <sub>HEX</sub>                                                  | Transmitter counter state | Not used      | Data 10 to Data 0 |  |  |

| 3A <sub>HEX</sub>                                                  | NVM ECC state             | Not used      | Data 10 to Data 0 |  |  |

| [a] SFR addresses 39, 3B, 3C, 3D, 3E, and 3F are Renesas internal. |                           |               |                   |  |  |

## 3.4 Main Registers Overview

#### Table 3. Register Overview

| NVM Address       | SRB Address       | Description                       | Main Functions                                                                                                                                                                                                        |

|-------------------|-------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00 <sub>HEX</sub> | 20 <sub>HEX</sub> | System configuration 1            | I2C and SPI mode settings.<br>The default interface is I2C with pin 1 (CSn_IRQN)<br>configured as address input.                                                                                                      |

| 01 <sub>HEX</sub> | 21 <sub>HEX</sub> | System configuration 2            | <ul> <li>Output Interrupt – mode and signal type</li> <li>Quadrature mode selection</li> <li>Security of reading/writing via I2C/SPI</li> <li>Transmitter settings</li> <li>Supply voltage range selection</li> </ul> |

| 02 <sub>HEX</sub> | 22 <sub>HEX</sub> | R1/R2 gain                        | Sets the gain stage and the number of integration cycles of the integrator.                                                                                                                                           |

| 03 <sub>HEX</sub> | 23 <sub>HEX</sub> | System configuration 3            | Used for dynamic interrupt signal by 1-bit setting.                                                                                                                                                                   |

| 04 <sub>HEX</sub> | 24 <sub>HEX</sub> | R2 coil offset                    | Sets the offset value for R2 coil and its sign.                                                                                                                                                                       |

| 06 <sub>HEX</sub> | 26 <sub>HEX</sub> | R1 coil offset                    | Sets the offset value for R1 coil and its sign.                                                                                                                                                                       |

| 07 <sub>HEX</sub> | 27 <sub>HEX</sub> | Transmitter current calibration   | Used for LC oscillator current settings.                                                                                                                                                                              |

| 08 <sub>HEX</sub> | 28 <sub>HEX</sub> | Transmitter frequency timebase    | Used for counter settings.                                                                                                                                                                                            |

| 09 <sub>HEX</sub> | 29 <sub>HEX</sub> | Transmitter frequency lower limit | Used for lower limit of counter.                                                                                                                                                                                      |

| 0A <sub>HEX</sub> | 2A <sub>HEX</sub> | Transmitter frequency upper limit | Used for upper limit of counter.                                                                                                                                                                                      |

| 0B <sub>HEX</sub> | 2B <sub>HEX</sub> | Interrupt1 Enables                | Used for diagnostics of:<br>• VDD upper and lower voltage<br>• SPI and I2C fails<br>• SRB error detection<br>• NVM error detection<br>• LC oscillator detection range<br>• Oscillator stuck check                     |

| 0C <sub>HEX</sub> | 2C <sub>HEX</sub> | Interrupt2 Enables                | Used for diagnostics of:<br>• VDDA under-voltage<br>• Low amplitude<br>• Bus transfer<br>• Mechanical failure<br>• Sin/Cosine voltage levels<br>• Coils short                                                         |

| 0D <sub>HEX</sub> | 2D <sub>HEX</sub> | IRQN watchdog 1                   |                                                                                                                                                                                                                       |

| NVM Address       | SRB Address       | Description        | Main Functions                                                                              |

|-------------------|-------------------|--------------------|---------------------------------------------------------------------------------------------|

| 0E <sub>HEX</sub> | 2E <sub>HEX</sub> | IRQN watchdog 2    |                                                                                             |

| 12 <sub>HEX</sub> | 32 <sub>HEX</sub> | R1 fine gain       | Sets the amplitude of the R1 channel for correcting the mismatch between the two receivers. |

| 13 <sub>HEX</sub> | 33 <sub>HEX</sub> | R2 fine gain       | Sets the amplitude of the R2 channel for correcting the mismatch between the two receivers. |

| 19 <sub>HEX</sub> | n.a.              | Product identifier |                                                                                             |

| 1A <sub>HEX</sub> | n.a.              | Product identifier |                                                                                             |

| 1B <sub>HEX</sub> | n.a.              | Product identifier |                                                                                             |

| 1C <sub>HEX</sub> | n.a.              | Product identifier |                                                                                             |

| 1D <sub>HEX</sub> | n.a.              | Product identifier |                                                                                             |

| 1E <sub>HEX</sub> | n.a.              | Product identifier |                                                                                             |

| 1F <sub>HEX</sub> | n.a.              | Product identifier |                                                                                             |

## 3.5 Register Descriptions

## 3.5.1. System Configuration 1

This register configures the interface protocol, the SPI or I2C selection, and the output mode (Analog or Digital Quadrature mode, see *IPS2200 Datasheet* for detailed explanation on output modes).

## Table 4. System Configuration 1 Register Details

| Block   | NVM                 | SRB                 | SFR |

|---------|---------------------|---------------------|-----|

| Address | 00 <sub>HEX</sub>   | 20 <sub>HEX</sub>   | -   |

| Default | 0323 <sub>HEX</sub> | 0323 <sub>HEX</sub> | -   |

| Access  | READ/WRITE          | READ/WRITE          | -   |

.

| Table 5. System | n Configuration 1 | <b>Register Bit</b> | Descriptions |

|-----------------|-------------------|---------------------|--------------|

|-----------------|-------------------|---------------------|--------------|

| Bit          | Symbol                | Default             | Туре | Description                                                                                        |

|--------------|-----------------------|---------------------|------|----------------------------------------------------------------------------------------------------|

| sys_conf1.15 | ECC                   | 0000 <sub>BIN</sub> | R    | Parity word for error correction. For the internal use of the IC.                                  |

| sys_conf1.14 |                       |                     |      |                                                                                                    |

| sys_conf1.13 |                       |                     |      |                                                                                                    |

| sys_conf1.12 |                       |                     |      |                                                                                                    |

| sys_conf1.11 | P <sub>DED</sub>      | 0 <sub>BIN</sub>    |      | Parity bit for double-bit error detection.                                                         |

| sys_conf1.10 | SPI data order        | 0 <sub>BIN</sub>    | R/W  | SPI data order (DORD):                                                                             |

|              |                       |                     |      | $O_{BIN} = MSB$ (Most Significant Bit?) received first; LSB (Least Significant Bit?) received last |

|              |                       |                     |      | 1 <sub>BIN</sub> = LSB received first; MSB received last                                           |

| sys_conf1.9  | SPI modes             | 11 <sub>BIN</sub>   | R/W  | Clock polarity (CPOL) and clock phase (CPHA) of SPI                                                |

| sys_conf1.8  |                       |                     |      | interface.                                                                                         |

|              |                       |                     |      | sys_conf1.9 = CPHA                                                                                 |

|              |                       |                     |      | sys_conf1.8 = CPOL                                                                                 |

|              |                       |                     |      | CPHA: $0_{BIN}$ = first data bit written at CSN falling edge                                       |

|              |                       |                     |      | CPHA and CPOL:                                                                                     |

|              |                       |                     |      | $00_{BIN}$ = sample edge rising, drive edge falling                                                |

|              |                       |                     |      | 01 <sub>BIN</sub> = sample edge falling, drive edge rising                                         |

|              |                       |                     |      | $10_{BIN}$ = sample edge falling, drive edge rising                                                |

|              |                       |                     |      | 11 <sub>BIN</sub> = sample edge rising, drive edge falling                                         |

| sys_conf1.7  | I2C MSN slave address | 0010 <sub>BIN</sub> | R/W  | I2C slave programmable address bits, see Table 6 for                                               |

| sys_conf1.6  |                       |                     |      | details.[a]                                                                                        |

| sys_conf1.5  |                       |                     |      |                                                                                                    |

| sys_conf1.4  |                       |                     |      |                                                                                                    |

| Bit         | Symbol                | Default           | Туре | Description                                                |

|-------------|-----------------------|-------------------|------|------------------------------------------------------------|

| sys_conf1.3 | Outputs mode protocol | 00 <sub>BIN</sub> | R/W  | Outputs have two protocol modes:                           |

| sys_conf1.2 |                       |                   |      | Analog:                                                    |

|             |                       |                   |      | <ul> <li>00<sub>BIN</sub>: SIN, SINN, COS; COSN</li> </ul> |

|             |                       |                   |      | ○ 01 <sub>BIN</sub> : SIN, REF, COS, REF                   |

|             |                       |                   |      | Digital Quadrature Mode                                    |

|             |                       |                   |      | о 10 <sub>віл</sub> : А, АN, В, BN                         |

|             |                       |                   |      | ∘ 11 <sub>BIN</sub> : A, B                                 |

| sys_conf1.1 | System protocol       | 11 <sub>BIN</sub> | R/W  | Protocol mode of communication interface between sensor    |

| sys_conf1.0 |                       |                   |      | and processing unit:                                       |

|             |                       |                   |      | $00_{BIN} = SPI$ half duplex                               |

|             |                       |                   |      | $01_{BIN} = SPI$ half duplex and interrupt                 |

|             |                       |                   |      | $10_{BIN} = I2C$ and interrupt                             |

|             |                       |                   |      | $11_{BIN} = I2C$ and addressing pin                        |

[a] If modifying the I2C MSN address field, there are two restricted address groups: 0000<sub>BIN</sub> and 1111<sub>BIN</sub> (refer to section 3.5.1).

#### Table 6. I2C Slave Address Configuration

| Configuration <sup>[a]</sup>      | A6                         | A5                                                    | A4 | A3 | A2 | A1 | A0 |

|-----------------------------------|----------------------------|-------------------------------------------------------|----|----|----|----|----|

| Protocol mode = 10 <sub>BIN</sub> | sys_conf1.7 to sys_conf1.4 |                                                       |    | 0  | 0  | 0  |    |

| Protocol mode = 11 <sub>BIN</sub> | sys_conf1.7                | sys_conf1.7 to sys_conf1.5 Pin 1 state <sup>[b]</sup> |    |    | 0  | 0  | 0  |

[a] Protocol mode = sys\_conf1.1 and sys\_conf1.0, see Table 5.

[b] Pin 1 state = logical state of Pin 1 input pin (CSN\_IRQN).

## 3.5.2. System Configuration 2

The main functions of this register is to define the following settings:

- · Output interrupt enable interrupt by using the output SIN/COSINE

- · Quadrature mode selection

- · Security of reading/writing via I2C or SPI

- Transmitter settings

- SPI/I2C Protocol integrity check

- Supply voltage range selection

## Table 7. System Configuration 2 Register Details

| Block         | NVM                 | SRB                 | SFR |

|---------------|---------------------|---------------------|-----|

| Address       | 01 <sub>HEX</sub>   | 21 <sub>HEX</sub>   | -   |

| Default Value | 0101 <sub>HEX</sub> | 0101 <sub>HEX</sub> | -   |

| Access        | READ/WRITE          | READ/WRITE          | -   |

#### Table 8. System Configuration 2 Register Bit Descriptions

| Bit                        | Symbol                         | Default             | Туре | Description                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------|--------------------------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sys_conf2.15               | ECC                            | 0000 <sub>BIN</sub> | R    | Parity word for error correction. For the internal use of the IC.                                                                                                                                                                                                                                                                                                                 |

| sys_conf2.14               |                                |                     |      |                                                                                                                                                                                                                                                                                                                                                                                   |

| sys_conf2.13               |                                |                     |      |                                                                                                                                                                                                                                                                                                                                                                                   |

| sys_conf2.12               |                                |                     |      |                                                                                                                                                                                                                                                                                                                                                                                   |

| sys_conf2.11               | P <sub>DED</sub>               | 0 <sub>BIN</sub>    |      | Parity bit for double bit error detection. For the internal use of                                                                                                                                                                                                                                                                                                                |

|                            |                                |                     |      | the IC.                                                                                                                                                                                                                                                                                                                                                                           |

| sys_conf2.10               | Pulse mode configuration       | Obin                | R/W  | <ul> <li>Function of Pulse Output. For this function the Output Mode must be set to Quadrature Differential (set sys_conf1.3, sys_conf1.2 to 10BIN: A, AN, B, BN) and Pulse Mode (sys_conf2.5) must be enabled (sys_conf2.5 = 1<sub>BIN</sub>).</li> <li>0<sub>BIN</sub> = 1 pulse per phase (signal A)</li> <li>1<sub>BIN</sub> = 2 pulses per phase (signal A XOR B)</li> </ul> |

| sys_conf2.9<br>sys_conf2.8 | Renesas internal configuration | 01 <sub>BIN</sub>   | R/W  | Renesas internal feature. Do not change the default setting.                                                                                                                                                                                                                                                                                                                      |

| Bit          | Symbol                         | Default          | Туре     | Description                                                                                                                                                            |

|--------------|--------------------------------|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sys_conf2.7  | Output interrupt enable        | 0 <sub>BIN</sub> | R/W      | Enable Interrupt signaling at output interface:                                                                                                                        |

|              |                                |                  |          | <ul> <li>0<sub>BIN</sub> = interrupt signaling disabled</li> </ul>                                                                                                     |

|              |                                |                  |          | <ul> <li>1<sub>BIN</sub> = interrupt signaling enabled</li> </ul>                                                                                                      |

|              |                                |                  |          | If the interface is not used, the output is also intended for the interrupts.<br>If the interrupt is enabled and a failure occurs, the output has                      |

|              |                                |                  |          | the following values:<br>• SIN/A = 0 <sub>DEC/</sub> 0bit                                                                                                              |

|              |                                |                  |          |                                                                                                                                                                        |

|              |                                |                  |          | • SINN/AN =0 <sub>DEC</sub> /0bit                                                                                                                                      |

|              |                                |                  |          | • $COS/B = 1_{DEC}/1bit$                                                                                                                                               |

|              |                                |                  |          | COSN/BN =1 <sub>DEC</sub> /1bit                                                                                                                                        |

| sys_conf2.6  | Cyber security                 | O <sub>BIN</sub> | R/W      | The cyber security bit determines the transfer direction of the allowed I2C/SPI access mode.                                                                           |

|              |                                |                  |          | 0 <sub>BIN</sub> = I2C/SPI read/write access                                                                                                                           |

|              |                                |                  |          | 1 <sub>BIN</sub> = I2C/SPI read-only access                                                                                                                            |

| sys_conf2.5  | Quadrature Mode protocol       | O <sub>BIN</sub> | R/W      | Select between AB and Pulse mode. For this function the<br>Output Mode must be set to Quadrature Differential (set<br>sys_conf1.3, sys_conf1.2 to 10BIN: A, AN, B, BN) |

|              |                                |                  |          | $O_{BIN} = AB \text{ mode: } A, AN, B, BN \text{ signals at output pins}$                                                                                              |

|              |                                |                  |          | $1_{\text{BIN}}$ = Pulse mode; Pulse output at SINN pin 13                                                                                                             |

| sys_conf2.4  | Transmitter cp enable          | O <sub>BIN</sub> | R/W      | Transmitter charge pump enable.                                                                                                                                        |

| SyS_COIII2.4 | Transmitter op enable          | UBIN             |          | $O_{BIN} = Off$                                                                                                                                                        |

|              |                                |                  |          | $1_{\text{BIN}} = 0$                                                                                                                                                   |

|              |                                |                  |          | It must be on, if $VDD = 3.3V$ .                                                                                                                                       |

| sys_conf2.3  | Transmitter amplitude control  | O <sub>BIN</sub> | R/W      | Transmitter amplitude control                                                                                                                                          |

| 3y3_00112.0  | Transmitter amplitude control  | OBIN             | 1.7, 4.4 | O <sub>BIN</sub> = Off                                                                                                                                                 |

|              |                                |                  |          | 1 <sub>BIN</sub> = On                                                                                                                                                  |

| sys conf2.2  | Protocol integrity check       | O <sub>BIN</sub> | R/W      | I2C/SPI interface support integrity check of the serial data                                                                                                           |

| 393_00112.2  | Thouseon megnity check         | OBIN             | 1.7, 4.4 | stream (Rx and Tx).                                                                                                                                                    |

|              |                                |                  |          | O <sub>BIN</sub> = integrity check off                                                                                                                                 |

|              |                                |                  |          | $1_{\text{BIN}}$ = integrity check on                                                                                                                                  |

| sys_conf2.1  | Renesas internal configuration | O <sub>BIN</sub> | R/W      | Renesas internal feature. Do not change the default setting.                                                                                                           |

| sys_conf2.0  | Supply voltage                 | 1 <sub>BIN</sub> | R/W      | Supply voltage mode for VDD regulator:                                                                                                                                 |

| .,           |                                | אום              |          | • $0_{BIN} = 3.3V$ typical VDD supply, the result on VDDA is 4V<br>The 'Transmitter cp enable' must be set to $1_{BIN}$ to use this feature.                           |

|              |                                |                  |          | • 1 <sub>BIN</sub> = 5.0V typical VDD supply, the result on VDDA is 4V                                                                                                 |

#### 3.5.3. Receiver 1/2 Gain

This register is used for setting the gain stage and the number of integration cycles of the integrator.

The gain stage and the integration cycles are used for increasing or decreasing the amplitude of the input signal.

#### Table 9. Receiver 1/2 Gain Register Details

| Block         | NVM                 | SRB                 | SFR |

|---------------|---------------------|---------------------|-----|

| Address       | 02 <sub>HEX</sub>   | 22 <sub>HEX</sub>   | -   |

| Default value | 0056 <sub>HEX</sub> | 0056 <sub>HEX</sub> | -   |

| Access        | READ/WRITE          | READ/WRITE          | -   |

## Table 10.Receiver 1/2 Gain

| Bit         | Symbol           | Default             | Туре | Description                                                       |

|-------------|------------------|---------------------|------|-------------------------------------------------------------------|

| r12_gain.15 | ECC              | 0000 <sub>BIN</sub> |      | Parity word for error correction. For the internal use of the IC. |

| r12_gain.14 |                  |                     |      |                                                                   |

| r12_gain.13 |                  |                     |      |                                                                   |

| r12_gain.12 |                  |                     |      |                                                                   |

| r12_gain.11 | P <sub>DED</sub> | 0 <sub>BIN</sub>    |      | Parity bit for double bit error detection.                        |

| r12_gain.10 | Renesas internal | 00 <sub>BIN</sub>   | R/W  | Renesas internal feature. Do not change the default setting.      |

| r12_gain.9  | configuration    |                     |      |                                                                   |

| Bit                                                                | Symbol             | Default              | Туре |                                                                                                                                                                                            | Description |

|--------------------------------------------------------------------|--------------------|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| r12_gain.8<br>r12_gain.7<br>r12_gain.6<br>r12_gain.5<br>r12_gain.4 | Integration cycles | 00101 <sub>BIN</sub> | R/W  | The integration cycles par<br>the integrator in excitation<br>The minimum setting is 5<br>Setting<br>$00000_{BIN}$ to $00101_{BIN}$<br>$00110_{BIN}$<br>$00111_{BIN}$<br><br>$11111_{BIN}$ |             |

| r12_gain.3<br>r12_gain.2<br>r12_gain.1<br>r12_gain.0               | gain stage         | 0110 <sub>BIN</sub>  | R/W  | integrator by this formula:<br>$Gain = 2^{\frac{n}{2}}$                                                                                                                                    | 1           |

## 3.5.4. System Configuration 3

Only used for dynamic interrupt signaling by the sys\_conf3.10 bit. All other bits are for Renesas internal usage.

## Table 11. System Configuration 3 Register Details

| Block         | NVM               | SRB                 | SFR |

|---------------|-------------------|---------------------|-----|

| Address       | 03 <sub>HEX</sub> | 23 <sub>HEX</sub>   | -   |

| Default value |                   | 0000 <sub>HEX</sub> | -   |

| Access        | READ/WRITE        | READ/WRITE          | _   |

#### Table 12. System Configuration 3 Register Bit Definitions

| Bit          | Symbol              | Default          | Туре | Description                                                                         |

|--------------|---------------------|------------------|------|-------------------------------------------------------------------------------------|

| sys_conf3.15 | ECC                 |                  |      | Parity word for error correction. For the internal use of the                       |

| sys_conf3.14 |                     |                  |      | IC.                                                                                 |

| sys_conf3.13 |                     |                  |      |                                                                                     |

| sys_conf3.12 |                     |                  |      |                                                                                     |

| sys_conf3.11 | P <sub>DED</sub>    |                  |      | Parity bit for double bit error detection.                                          |

| sys_conf3.10 | dynamic_intr_enable | O <sub>BIN</sub> | R/W  | Enable volatile interrupt signaling:                                                |

|              |                     |                  |      | <ul> <li>0<sub>BIN</sub> = Disable; IRQN cleared by microcontroller host</li> </ul> |

|              |                     |                  |      | <ul> <li>1<sub>BIN</sub> = Enable; IRQN event type</li> </ul>                       |

| sys_conf3.9  | Renesas internal    | O <sub>BIN</sub> | R/W  | Renesas internal feature. Do not change the default                                 |

|              | configuration       |                  |      | setting.                                                                            |

| sys_conf3.8  | Renesas internal    | O <sub>BIN</sub> | R/W  | Renesas internal feature. Do not change the default                                 |

|              | configuration       |                  |      | setting.                                                                            |

| sys_conf3.7  | _                   | -                | -    | Not used; read as 0.                                                                |

| Bit                                       | Symbol                         | Default                 | Туре | Description                                                  |

|-------------------------------------------|--------------------------------|-------------------------|------|--------------------------------------------------------------|

| sys_conf3.6<br>sys_conf3.5<br>sys_conf3.4 | Renesas internal configuration | 000 0000 <sub>BIN</sub> | R/W  | Renesas internal feature. Do not change the default setting. |

| sys_conf3.3<br>sys_conf3.2                |                                |                         |      |                                                              |

| sys_conf3 1<br>sys_conf3.0                |                                |                         |      |                                                              |

## 3.5.5. R2 Coil Offset

The coil offset is defined as the constant volt value added or subtracted to the input signal. This offset is generated from the non-ideality of the coil design and non-uniformity of the electromagnetic field. This register enables to set the offset value and its sign (positive or negative).

The offset can be cancelled by adding or subtracting a constant value on the input signal.

For example:

During a complete sweep of the target, the offset on the receiver is seen as a shift of the signal with respect to the x-axis, see Figure 3 where the sine with peak amplitude 1 is shifted by +0.5.

The compensation in this example should be

Offset compensation = - 0.5

Figure 3. Receiver Input Signal with 0.5 Offset

| Block         | NVM               | SRB                 | SFR |

|---------------|-------------------|---------------------|-----|

| Address       | 04 <sub>HEX</sub> | 24 <sub>HEX</sub>   | -   |

| Default value | -                 | 0000 <sub>HEX</sub> | -   |

| Access        | READ/WRITE        | READ/WRITE          | -   |

## Table 14. R2 Coil Offset Register Bit Definitions

| Bit               | Symbol           | Default | Туре | Description                                               |

|-------------------|------------------|---------|------|-----------------------------------------------------------|

| r2_coil_offset.15 | ECC              | -       | -    | Parity word for error correction. For the internal use of |

| r2_coil_offset.14 |                  |         |      | the IC.                                                   |

| r2_coil_offset.13 |                  |         |      |                                                           |

| r2_coil_offset.12 |                  |         |      |                                                           |

| r2_coil_offset.11 | P <sub>DED</sub> | -       | _    | Parity bit for double-bit error detection.                |

#### IPS2200 Programming Guide

| Bit               | Symbol             | Default                | Туре | Description                                       |

|-------------------|--------------------|------------------------|------|---------------------------------------------------|

| r2_coil_offset.10 | -                  | -                      | -    | Not used; read as 0.                              |

| r2_coil_offset.9  | _                  | -                      | -    | Not used; read as 0.                              |

| r2_coil_offset.8  | -                  | -                      | -    | Not used; read as 0.                              |

| r2_coil_offset.7  | _                  | -                      | -    | Not used; read as 0.                              |

| r2_coil_offset.6  | R2 offset polarity | O <sub>BIN</sub>       | R/W  | Define the applied offset polarity:               |

|                   |                    |                        |      | • 0 <sub>BIN</sub> = Addition                     |

|                   |                    |                        |      | • 1 <sub>BIN</sub> = Subtraction                  |

| r2_coil_offset.5  | R2 offset value    | 00 0000 <sub>BIN</sub> | R/W  | The R2 offset compensation value, relative to the |

| r2_coil_offset.4  |                    |                        |      | Transmitter LC oscillator voltage amplitude is:   |

| r2_coil_offset.3  |                    |                        |      | 0x00 - no correction                              |

| r2_coil_offset.2  |                    |                        |      | • 0x01 - 0.003%                                   |

| r2_coil_offset 1  |                    |                        |      | • 0x02 - 0.006%                                   |

| r2_coil_offset.0  |                    |                        |      | • 0x03 - 0.009%                                   |

|                   |                    |                        |      | until                                             |

|                   |                    |                        |      | • 0x3E - 0.197%                                   |

|                   |                    |                        |      | • 0x3F - 0.200%                                   |

|                   |                    |                        |      | Overall range is 0.2%, step is 0.003%             |

## 3.5.6. R1 Coil Offset

The Coil offset is defined as the constant volt value added or subtracted to the input signal. This offset is generated from the non-ideality of the coil design and non-uniformity of the electromagnetic field. This register enables to set the offset value and its sign (positive or negative).

The offset can be cancelled by adding or subtracting a constant value on the input signal.

#### Table 15. R1 Coil Offset Register Details

| Block         | NVM               | SRB                 | SFR |

|---------------|-------------------|---------------------|-----|

| Address       | 06 <sub>HEX</sub> | 26 <sub>HEX</sub>   | -   |

| Default value | -                 | 0000 <sub>HEX</sub> | -   |

| Access        | READ/WRITE        | READ/WRITE          | -   |

#### Table 16. R1 Coil Offset Register Bit Definitions

| Bit               | Symbol             | Default                | Туре | Description                                               |

|-------------------|--------------------|------------------------|------|-----------------------------------------------------------|

| r1_coil_offset.15 | ECC                | -                      | -    | Parity word for error correction. For the internal use of |

| r1_coil_offset.14 |                    |                        |      | the IC.                                                   |

| r1_coil_offset.13 |                    |                        |      |                                                           |

| r1_coil_offset.12 |                    |                        |      |                                                           |

| r1_coil_offset.11 | P <sub>DED</sub>   |                        | -    | Parity bit for double bit error detection.                |

| r1_coil_offset.10 | -                  | -                      |      | Not used; read as 0.                                      |

| r1_coil_offset.9  | -                  |                        | -    | Not used; read as 0.                                      |

| r1_coil_offset.8  | -                  | _                      | -    | Not used; read as 0.                                      |

| r1_coil_offset.7  |                    | -                      | -    | Not used; read as 0.                                      |

| r1_coil_offset.6  | R1 offset polarity | O <sub>BIN</sub>       | R/W  | Define the applied offset polarity:                       |

|                   |                    |                        |      | • 0 <sub>BIN</sub> = Addition                             |

|                   |                    |                        |      | • 1 <sub>BIN</sub> = Subtraction                          |

| r1_coil_offset.5  | R1 offset value    | 00 0000 <sub>BIN</sub> | R/W  | The R1 offset compensation value, relative to the         |

| r1_coil_offset.4  |                    |                        |      | Transmitter LC oscillator voltage amplitude is:           |

|                   |                    |                        |      | 0x00 - no correction                                      |

| r1_coil_offset.3  |                    |                        |      | • 0x01 - 0.003%                                           |

| r1_coil_offset.2  |                    |                        |      | • 0x02 - 0.006%                                           |

| r1_coil_offset 1  |                    |                        |      | • 0x03 - 0.009%                                           |

| r1 coil offset.0  |                    |                        |      | until                                                     |

|                   |                    |                        |      | • 0x3E - 0.197%                                           |

|                   |                    |                        |      | • 0x3F - 0.200%"                                          |

|                   |                    |                        |      | Overall range is 0.2%, step is 0.003%                     |

## 3.5.7. Transmitter Current Calibration

The Transmitter current bias ( $I_{BIAS}$ ) influences the AC current of the LC oscillator. Increasing the AC current, increases proportionally the magnitude of the transmitter signal. The  $I_{BIAS}$  optimum setting can be calculated according to the following formula:

$$_{BIAS} = VDD / (35 \times L \times Q \times F)$$

Where:

I

VDD = Supply voltage in Volt

L = Inductance of transmit coil in Henry

F = Transmit oscillator frequency in Hz

Q = Quality factor of the Transmitter coil, it is calculated according to the following formula:

$$Q = \frac{1}{R} \sqrt{\frac{L}{C}}$$

Where:

R = Resistance of the Transmitter Coil

C = Capacitance of the transmitter resonator

For Example:

If L = 6 $\mu$ H, R = 10hm, C = 345pF (such that the transmitter oscillates at F = 3.5MHz) and VDD = 5V

According to the formula above:

Q = 132

$I_{BIAS} = 51.5 \mu A$

As shown in Table 19, the closest  $I_{BIAS}$  setting to 51.5µA is 52µA corresponding to the following setting:

LC Current Multiplication = 01BIN

LC Current Base = 001101BIN

#### Table 17. Transmitter Current Calibration Register Details

| Block         | NVM               | SRB                 | SFR |

|---------------|-------------------|---------------------|-----|

| Address       | 07 <sub>HEX</sub> | 27 <sub>HEX</sub>   | -   |

| Default value | 00BE HEX          | 00BE <sub>HEX</sub> | -   |

| Access        | READ/WRITE        | READ/WRITE          | -   |

#### Table 18. Transmitter Current Calibration Register Bit Definitions

| Bit                  | Symbol                    | Default             | Туре | Description                                                   |

|----------------------|---------------------------|---------------------|------|---------------------------------------------------------------|

| transmitter_calib.15 | ECC                       | 0000 <sub>BIN</sub> | -    | Parity word for error correction. For the internal use of the |

| transmitter_calib.14 |                           |                     |      | IC.                                                           |

| transmitter_calib.13 |                           |                     |      |                                                               |

| transmitter_calib.12 |                           |                     |      |                                                               |

| transmitter_calib.11 | P <sub>DED</sub>          | 0 <sub>BIN</sub>    | -    | Parity bit for double-bit error detection.                    |

| transmitter_calib.10 | -                         | O <sub>BIN</sub>    | -    | Not used; read as 0.                                          |

| transmitter_calib.9  | _                         | O <sub>BIN</sub>    | -    | Not used; read as 0.                                          |

| transmitter_calib.8  | -                         | 0 <sub>BIN</sub>    | -    | Not used; read as 0.                                          |

| transmitter_calib.7  | LC current multiplication | 10 <sub>HEX</sub>   | R/W  | See Table 19.                                                 |

| transmitter_calib.6  |                           |                     |      |                                                               |

| Bit                 | Symbol          | Default               | Туре | Description   |  |

|---------------------|-----------------|-----------------------|------|---------------|--|

| transmitter_calib.5 | LC current base | 111110 <sub>BIN</sub> | R/W  | See Table 19. |  |

| transmitter_calib.4 |                 |                       |      |               |  |

| transmitter_calib.3 |                 |                       |      |               |  |

| transmitter_calib.2 |                 |                       |      |               |  |

| transmitter_calib.1 |                 |                       |      |               |  |

| transmitter_calib.0 |                 |                       |      |               |  |

#### Table 19. Transmitter Bias Current Settings

| 0                           | LC Current<br>Multiplication = 00 | LC Current<br>Multiplication = 01 | LC Current<br>Multiplication = 10 | LC Current<br>Multiplication = 11 |

|-----------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

| LC Current Base = 000000BIN | 0μΑ                               | ΟμΑ                               | ΟμΑ                               | ΟμΑ                               |

| LC Current Base = 000001BIN | 0.5µA                             | 2μΑ                               | 8μΑ                               | 32µA                              |

| LC Current Base = 000010BIN | 1µA                               | 4µA                               | 16µA                              | 64µA                              |

| LC Current Base = 000011BIN | 1.5µA                             | 6µА                               | 24µA                              | 96µA                              |

| LC Current Base = 000100BIN | 2μΑ                               | 8μΑ                               | 32µA                              | 128µA                             |

| LC Current Base = 000101BIN | 2.5µA                             | 10µA                              | 40µA                              | 160µA                             |

| LC Current Base = 000110BIN | ЗμΑ                               | 12µA                              | 48µA                              | 192µA                             |

| LC Current Base = 000111BIN | 3.5µA                             | 14µA                              | 56µA                              | 224µA                             |

| LC Current Base = 001000BIN | 4µA                               | 16µA                              | 64µA                              | 256µA                             |

| LC Current Base = 001001BIN | 4.5µA                             | 18µA                              | 72µA                              | 288µA                             |

| LC Current Base = 001010BIN | 5μΑ                               | 20µA                              | 80µA                              | 320µA                             |

| LC Current Base = 001011BIN | 5.5µA                             | 22µA                              | 88µA                              | 352µA                             |

| LC Current Base = 001100BIN | 6µA                               | 24µA                              | 96µA                              | 384µA                             |

| LC Current Base = 001101BIN | 6.5µA                             | 26µA                              | 104µA                             | 416µA                             |

| LC Current Base = 001110BIN | 7μΑ                               | 28µA                              | 112µA                             | 448µA                             |

| LC Current Base = 001111BIN | 7.5µA                             | 30µA                              | 120µA                             | 480µA                             |

| LC Current Base = 010000BIN | 8μΑ                               | 32µA                              | 128µA                             | 512µA                             |

| LC Current Base = 010001BIN | 8.5µA                             | 34µA                              | 136µA                             | 544µA                             |

| LC Current Base = 010010BIN | 9µA                               | 36µA                              | 144µA                             | 576µA                             |

| LC Current Base = 010011BIN | 9.5µA                             | 38µA                              | 152µA                             | 608µA                             |

| LC Current Base = 010100BIN | 10µA                              | 40µA                              | 160µA                             | 640µA                             |

| LC Current Base = 010101BIN | 10.5µA                            | 42µA                              | 168µA                             | 672µA                             |

| LC Current Base = 010110BIN | 11µA                              | 44µA                              | 176µA                             | 704µA                             |