# RENESAS

# ISL81801

80V Bidirectional 4-Switch Synchronous Buck-Boost Controller

The <u>ISL81801</u> is a true bidirectional 4-switch synchronous buck-boost controller with peak and average current sensing and monitoring at both ends. With wide input and output voltage ranges, the controller is suitable for industrial, telecommunication, and after-market automotive applications.

The ISL81801 uses a proprietary buck-boost control algorithm with valley current modulation for Boost mode and peak current modulation for Buck mode control.

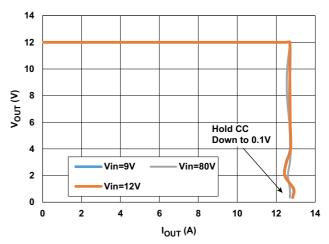

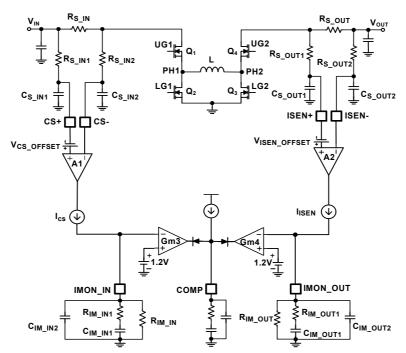

The ISL81801 has four independent control loops for input and output voltages and currents. Inherent peak current sensing at both ends and cycle-by-cycle current limit of this family of products ensures high operational reliability by providing instant current limit in fast transient conditions at either end and in both directions. It also has two current monitoring pins at both input and output to facilitate Constant Current (CC) limit and other system management functions. CC operation down to low voltages avoids any runaway condition at over load or short-circuit conditions. In addition to multilayer overcurrent protection, it also provides full protection features such as OVP, UVP, OTP, average and peak current limit on both input and output to ensure high reliability in both unidirectional and bidirectional operation.

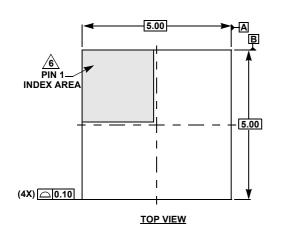

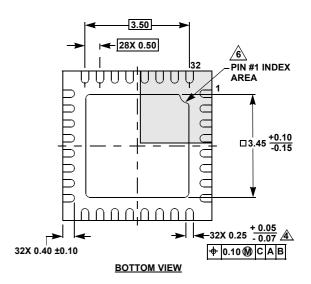

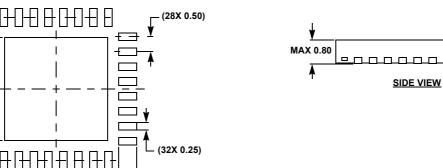

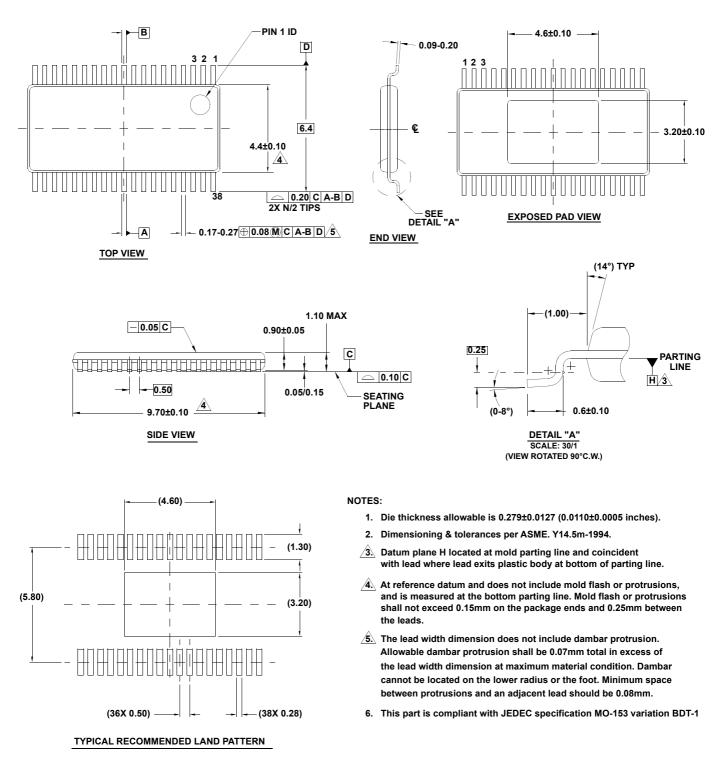

The IC is packaged in a space-conscious 32 LD 5mm x5mm TQFN package or easy to assemble 4.4mm x9.7mm 38 LD HTSSOP package. Both packages use an EPAD to improve thermal performance and noise immunity. Low pin count, fewer external components, and default internal values make the ISL81801 an ideal solution for time to market simple power supply designs. The unique DE/Burst mode at light-load dramatically lowers standby power consumption with consistent output ripple over different load levels.

## Features

- · Single inductor 4-switch buck-boost controller

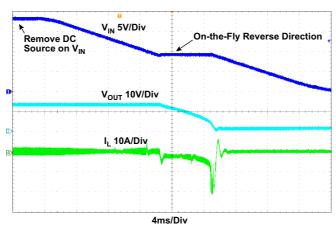

- On-the-fly bidirectional operation with independent control of voltage and current on both ends

- Proprietary algorithm for smoothest mode transition

- MOSFET drivers with adaptive shoot-through protection

- Wide input voltage range: 4.5V to 80V

- Wide output voltage range: 0.8V to 80V

- · Supports startup into pre-biased rails

- Programmable frequency: 100kHz to 600kHz

- Supports parallel operation current sharing with cascade phase interleaving

- · External sync with clock out or frequency dithering

- External bias for higher efficiency for 8V to 36V input

- Output and input current monitor

- Selectable PWM mode operation between PWM/DE/Burst modes

- Accurate EN/UVLO and PGOOD indicator

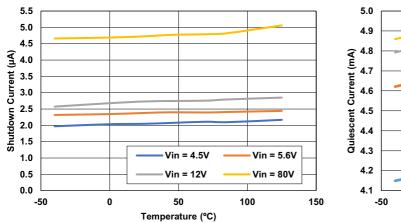

- Low shutdown current: 2.7µA

- Complete protection: OCP, SCP, OVP, OTP, and UVP

- Dual-level OCP with average current and pulse-by-pulse peak current limit, also provides Short Circuit Protection (SCP)

- Selectable OCP response with either hiccup or constant current mode

- Negative pulse-by-pulse peak current limit

### Applications

- Battery backup

- UPS/storage systems

- · Battery powered industrial applications

- Renewable energy

- Aftermarket automotive

- Redundant power supplies

- Robots and drones

- Medical equipment

- · Building and industrial automation

- Security surveillance

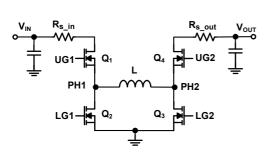

Figure 2. Buck-Boost Power Train Topology

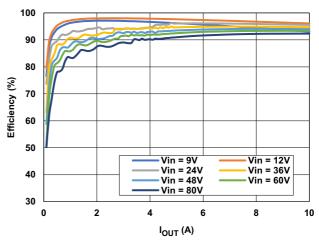

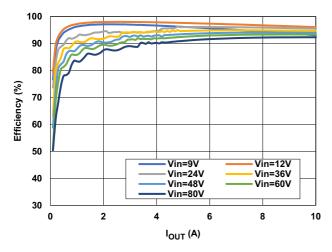

Figure 3. Efficiency (V<sub>OUT</sub> = 12V, DE Mode)

# Contents

| 1.         | Overview                                                                                    | 5    |

|------------|---------------------------------------------------------------------------------------------|------|

| 1.1        | Typical Application Schematics                                                              | 5    |

| 1.2        | Block Diagram                                                                               | 7    |

| 1.3        | Ordering Information                                                                        | 8    |

| 2.         | Pin Information.                                                                            | 9    |

| 2.1        | Pin Assignments                                                                             | 9    |

| 2.2        | Pin Descriptions                                                                            | 9    |

| 3.         | Specifications.                                                                             | . 12 |

| 3.1        | Absolute Maximum Ratings                                                                    | . 12 |

| 3.2        | Thermal Information.                                                                        | . 12 |

| 3.3        | Recommended Operating Conditions                                                            | . 12 |

| 3.4        | Electrical Specifications                                                                   | . 13 |

| 4.         | Typical Performance Graphs                                                                  | . 19 |

| 5.         | Functional Description                                                                      | . 25 |

| 5.1        | General Description                                                                         |      |

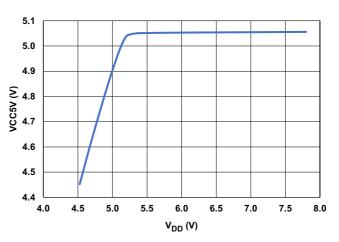

| 5.2        | Internal 8V Linear Regulator (VDD), External Bias Supply (EXTBIAS), and 5V Linear Regulator |      |

| <b>F</b> 0 |                                                                                             |      |

| 5.3        | Enable (EN/UVLO) and Soft-Start Operation                                                   |      |

| 5.4<br>5.5 | Tracking Operation                                                                          |      |

| 5.5<br>5.6 | Buck-Boost Conversion Topology and Control Algorithm                                        |      |

| 5.7        | Light-Load Efficiency Enhancement                                                           |      |

| 5.8        | Prebiased Power-Up                                                                          |      |

| 5.9        | Frequency Selection                                                                         |      |

| 5.10       |                                                                                             |      |

| 5.11       |                                                                                             |      |

| 5.12       |                                                                                             |      |

| 5.13       | Gate Drivers                                                                                | . 38 |

| 5.14       | Power-Good Indicator                                                                        | . 39 |

| 6.         | Protection Circuits                                                                         | . 40 |

| 6.1        | Input Undervoltage Lockout (UVLO)                                                           | . 40 |

| 6.2        | VCC5V Power-On Reset (POR)                                                                  | . 40 |

| 6.3        | Overcurrent Protection (OCP)                                                                | . 40 |

| 6.4        | Overvoltage Protection (OVP)                                                                |      |

| 6.5        | Over-Temperature Protection (OTP)                                                           | . 41 |

| 7.         | Layout Guidelines                                                                           | . 42 |

| 7.1        | Layout Considerations                                                                       |      |

| 7.2        | General EPAD Design Considerations                                                          | . 43 |

| 8.         | Component Selection Guideline                                                               | . 44 |

| 8.1        | MOSFET Considerations                                                                       |      |

| 8.2        | Inductor Selection                                                                          |      |

| 8.3        | Output Capacitor Selection                                                                  |      |

| 8.4        | Input Capacitor Selection                                                                   | . 46 |

| 9.  | Revision History         | 47 |

|-----|--------------------------|----|

| 10. | Package Outline Drawings | 48 |

### 1. Overview

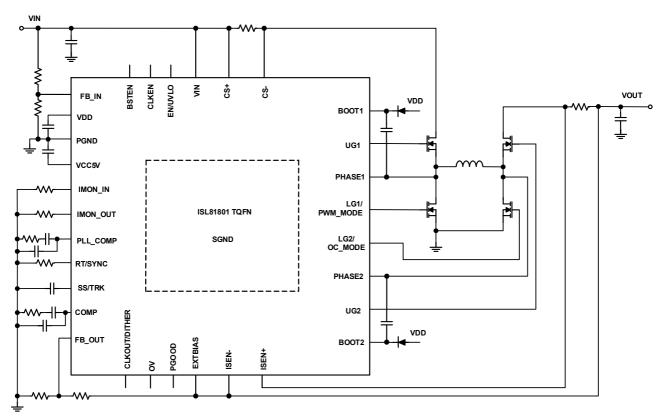

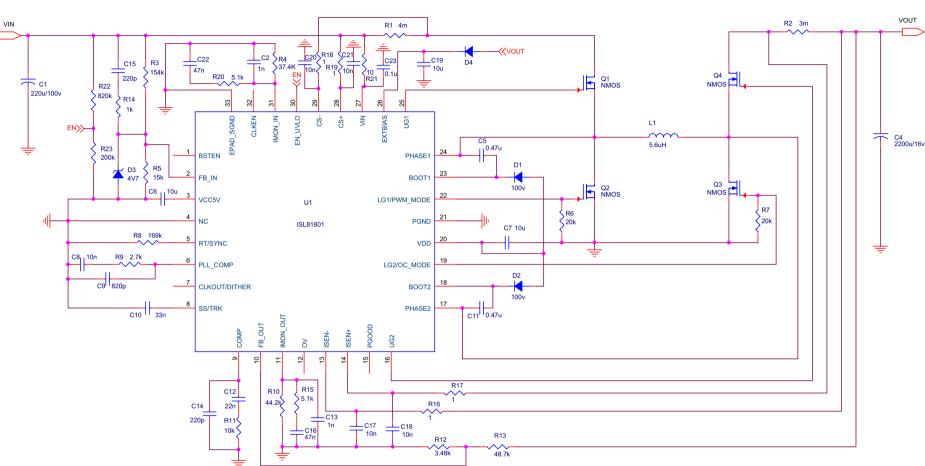

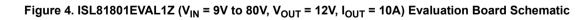

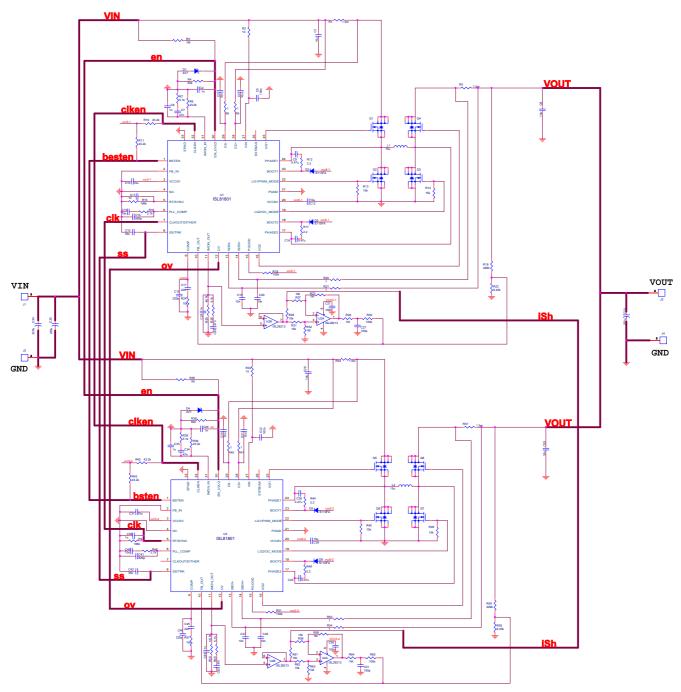

1.1 Typical Application Schematics

FN8937 Rev.1.4 Mar 8, 2024

RENESAS

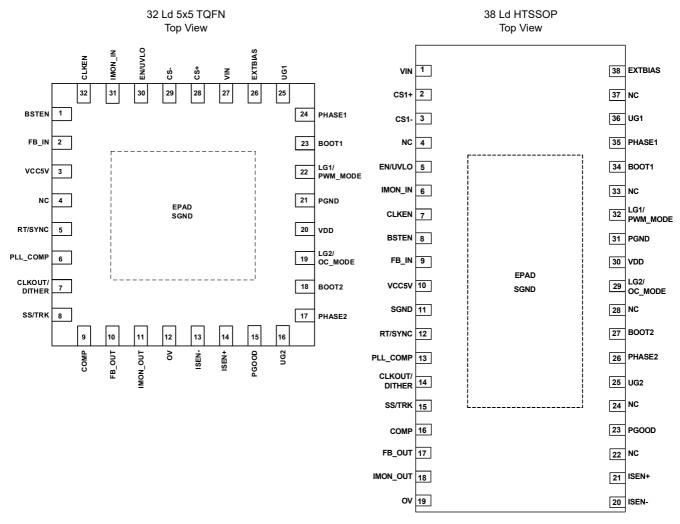

Figure 5. ISL81801EVAL2Z (V<sub>IN</sub> = 32V to 80V, V<sub>OUT</sub> = 48V, I<sub>OUT</sub> = 5A) Evaluation Board Schematic

Page 6 of 49

ISL81801

1. Overview

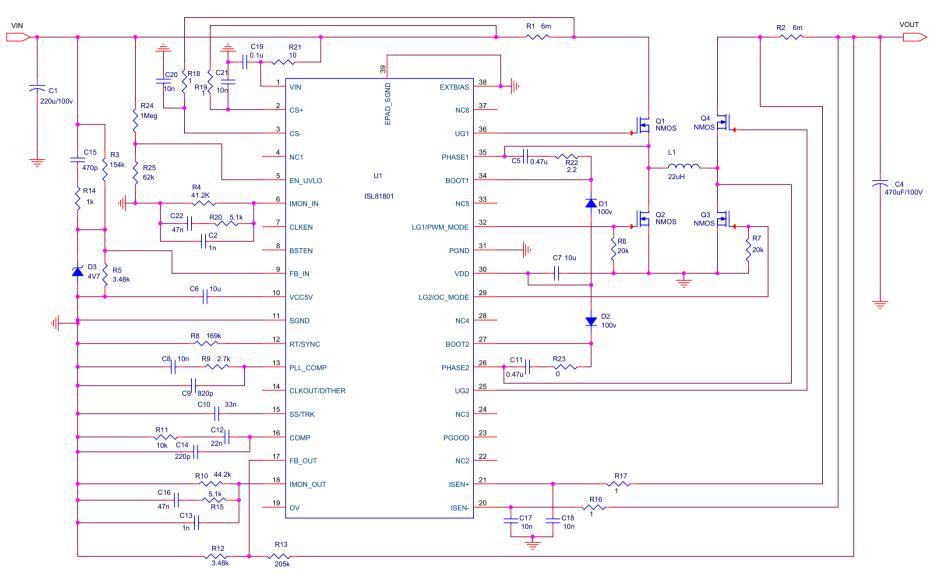

#### Figure 6. Block Diagram

### 1.3 Ordering Information

| Part Number<br>( <u>Notes 2, 3</u> ) | Part Marking         | Package Description<br>(RoHS Compliant) | Pkg. Dwg. #     | Carrier Type<br>( <u>Note 1</u> ) | Temp. Range   |  |  |

|--------------------------------------|----------------------|-----------------------------------------|-----------------|-----------------------------------|---------------|--|--|

| ISL81801FRTZ-T                       | 81801                | 32 Ld 5x5 TQFN                          | L32.5x5A        | Reel, 6k                          | -40 to +125°C |  |  |

| ISL81801FRTZ-T7A                     | FRTZ                 |                                         |                 | Reel, 250                         |               |  |  |

| ISL81801FVEZ-T                       | ISL81801             | 38 Ld HTSSOP <u>M38.</u>                | <u>M38.173C</u> | Reel, 2.5k                        |               |  |  |

| ISL81801FVEZ-T7A                     | FVEZ                 |                                         |                 | Reel, 250                         |               |  |  |

| ISL81801EVAL1Z                       | Evaluation Board for | valuation Board for TQFN                |                 |                                   |               |  |  |

| ISL81801EVAL2Z                       | Evaluation Board for | valuation Board for HTSSOP              |                 |                                   |               |  |  |

Notes:

1. See <u>TB347</u> for details about reel specifications.

These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

3. For Moisture Sensitivity Level (MSL), see the <u>ISL81801</u> device page. For more information about MSL, see <u>TB363</u>.

Table 1.

Key Differences Between Family of Parts

| Part Number | V <sub>IN</sub> Op/ Max (V) | $V_{DD}(V)$ | Current Control | Parallelable | Dithering | Removed Pins                 | Pin 12 |

|-------------|-----------------------------|-------------|-----------------|--------------|-----------|------------------------------|--------|

| ISL81801    | 80/80                       | 8           | Bidirectional   | Yes          | Yes       | None                         | OV     |

| ISL81601    | 60/70                       | 8           | Bidirectional   | Yes          | Yes       | None                         | OV     |

| ISL81401    | 40/45                       | 5.3         | Bidirectional   | Yes          | Yes       | BSTEN, CLKEN                 | MODE   |

| ISL81401A   | 40/45                       | 5.3         | Unidirectional  | No           | No        | BSTEN, CLKEN, FIB_IN, CLKOUT | MODE   |

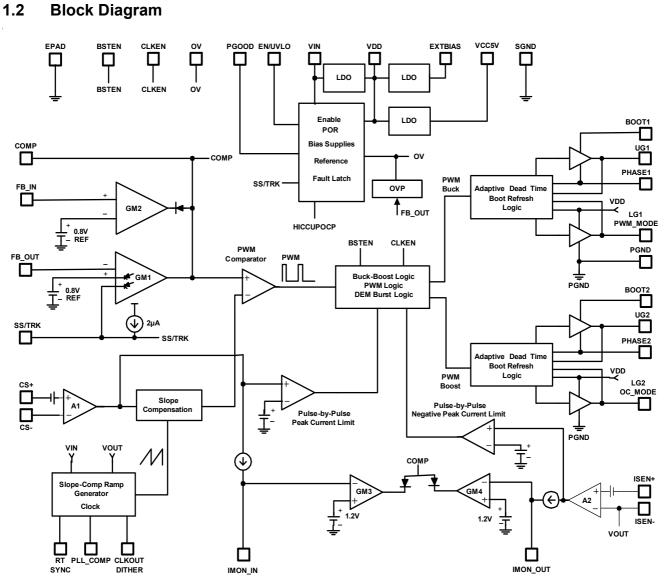

## 2. Pin Information

### 2.1 Pin Assignments

### 2.2 Pin Descriptions

| Pin #<br>(TQFN) | Pin #<br>(HTSSOP)        | Pin<br>Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|--------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | 8                        | BSTEN       | DE Burst mode enable signal. The pin is pulled up to 5V by an internal 250k resistor in PWM and DE mode. It is pulled low in Burst mode. The pull-down MOSFET $r_{DS(ON)}$ resistance is about 4.5k. Connect this pin together in the multi-chip parallel operation application to sync all the chips together for Burst mode operation.                                                                                                                                                                                                                                  |

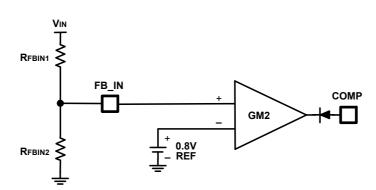

| 2               | 9                        | FB_IN       | Input voltage feedback pin for reverse direction operation. Use a resistor divider to feed the input voltage back to this pin. When the input voltage drops and pulls the pin voltage below 0.8V, the internal control loop reduces the duty cycle to sink in current from output to input to keep the pin voltage regulated at 0.8V.<br>Keep the pin voltage below 0.3V to disable the reverse direction operation.<br>When the reverse operation function is not used, tie this pin to VCC5V or SGND to set up the phase shift for the interleaving parallel operation. |

| 3               | 10                       | VCC5V       | Output of the internal 5V linear regulator. This output supplies bias for the IC. The VCC5V pin must always be decoupled to SGND with a minimum of 4.7µF ceramic capacitor placed close to the pin.                                                                                                                                                                                                                                                                                                                                                                       |

| 4               | 4, 22, 24,<br>28, 33, 37 | NC          | No connection pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pin #<br>(TQFN) | Pin #<br>(HTSSOP) | Pin<br>Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

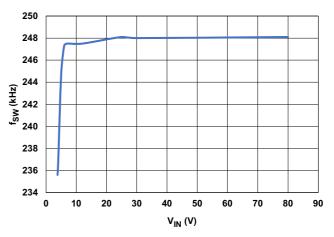

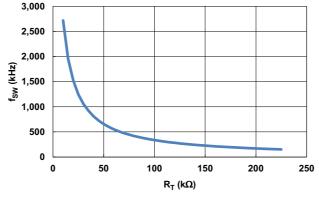

| 5               | 12                | RT/SYNC           | A resistor from this pin to ground adjusts the default switching frequency from 100kHz to 600kHz. The default switching frequency of the PWM controller is determined by the resistor $R_T$ as shown in Equation 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |                   |                   | (EQ. 1) $R_{T} = \left(\frac{34.7}{f_{SW}} - 4.78\right) \cdot k\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 |                   |                   | where f <sub>SW</sub> is the switching frequency in MHz.<br>When this pin is open or tied to VCC5V, f <sub>SW</sub> is set to 120kHz. When this pin is tied to GND, f <sub>SW</sub> is set<br>to 575kHz.<br>When an external clock signal is applied to this pin, the internal frequency is synchronized to the<br>external clock frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

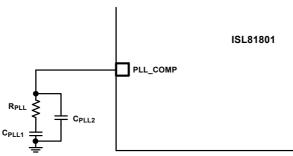

| 6               | 13                | PLL_COMP          | Compensation pin for the internal PLL circuit. A compensation network shown in the Figure 52 is required. $R_{PLL}(2.7k\Omega)$ , $C_{PLL1}$ (10nF), and $C_{PLL2}$ (820pF) are recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

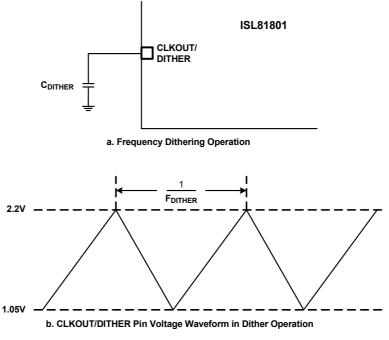

| 7               | 14                | CLKOUT/<br>DITHER | Dual function pin. When there is no capacitor connected to this pin, it provides a clock signal to synchronize the other ISL81801(s). The phase shift of the clock signal is set by the FB_IN and IMON_IN pin voltages. When a capacitor is connected to this pin, the clock out function is disabled and the frequency dither function is enabled before the soft-start. The capacitor is charged and discharged by internal current sources. As the voltage on the pin ramps up and down, the oscillator frequency dither function is disabled on the pin ramps up and down. The frequency dither function is disabled between -15% and +15% of the nominal frequency set by the $R_T$ resistor. The frequency dither function is disabled in the external Sync mode or if the RT pin is open or shorted.                                       |

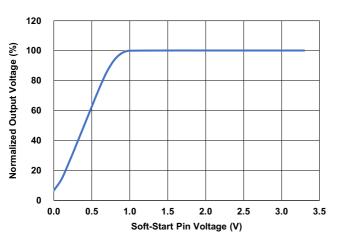

| 8               | 15                | SS/TRK            | Dual function pin. When used for soft-start control, a soft-start capacitor is connected from this pin to ground. A regulated 2µA current source charges up the soft-start capacitor. The value of the soft-start capacitor sets the output voltage ramp. When used for tracking control, an external supply rail is configured as the master, and the output voltage of the master supply is applied to this pin using a resistor divider. The output voltage tracks the master supply voltage.                                                                                                                                                                                                                                                                                                                                                  |

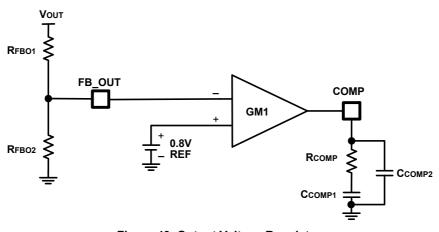

| 9               | 16                | COMP              | Voltage error GM amplifier output. It sets the reference of the inner current loop. The feedback compensation network is connected between the COMP and SGND pins. When the COMP pin is pulled below 1V, the PWM duty cycle reduces to 0%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10              | 17                | FB_OUT            | Output voltage feedback input. Connect FB_OUT to a resistive voltage divider between the output and SGND to adjust the output voltage. The FB_OUT pin voltage is regulated to the internal 0.8V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

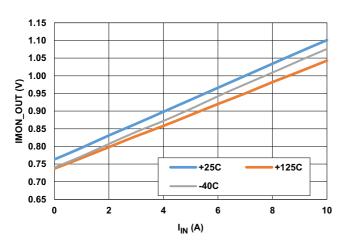

| 11              | 18                | IMON_OUT          | Output current monitor. The current from this pin is proportional to the differential voltage between the ISEN+ and ISEN- pins. Connect a resistor and capacitor network between this pin and SGND to make the pin voltage proportional to the average output current. When the pin voltage reaches 1.2V, the internal average current limit loop reduces the output voltage to keep the output current constant when constant current OCP mode is set or the converter shuts down when hiccup OCP mode is set. In DE Burst mode, when this pin voltage is less than 850mV, the controller runs in Burst mode. When this pin voltage is higher than 880mV, the controller exits Burst mode. When a higher resistance on this pin sets its voltage higher than 880mV at no load condition, the controller runs in DE mode with no burst operation. |

| 12              | 19                | OV                | OVP comparator output signal. The pin is pulled low to GND by an internal 250k resistor in normal operation. It is pulled high when output OVP trips. The pull-up MOSFET $r_{DS(ON)}$ resistance is about 4.5k. Connect this pin with other OV pins in multi-chip parallel operation applications to sync all of the OV indicators of the chips together for the OVP reaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 13              | 20                | ISEN-             | Output current sense signal negative input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14              | 21                | ISEN+             | Output current sense signal positive input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15              | 23                | PGOOD             | Power Good open-drain logic output that indicates the status of output voltage. This pin is pulled low when the output is not within $\pm 10\%$ of the nominal voltage or the EN pin is pulled LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16              | 25                | UG2               | High-side MOSFET gate driver output controlled by the boost PWM signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 17              | 26                | PHASE2            | Phase node connection of the boost converter. This pin is connected to the junction of the upper MOSFET source, filter inductor, and lower MOSFET drain of the boost converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

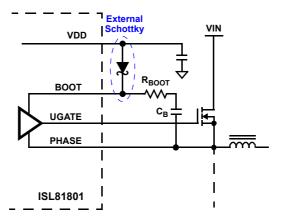

| 18              | 27                | BOOT2             | Bootstrap pin to provide bias for the boost high-side driver. The positive terminal of the bootstrap capacitor connects to this pin. Connect a bootstrap diode between this pin and VDD to create the bias for the high-side driver. The BOOT2 to PHASE2 voltage is monitored internally. When the voltage drops to 5.95V at no switching condition, a minimum off-time pulse is issued to turn off UG2 and turn on LG2 to refresh the bootstrap capacitor and maintain the high-side driver bias voltage.                                                                                                                                                                                                                                                                                                                                        |

| Pin #<br>(TQFN) | Pin #<br>(HTSSOP) | Pin<br>Name      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|-------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19              | 29                | LG2/<br>OC_MODE  | Low-side MOSFET gate driver output controlled by the boost PWM signal and OCP mode set pin. The OCP mode is set by a resistor connected between the pin and ground during the initialization period before soft-start. During the initialization period, the pin sources $10\mu$ A of current to set the voltage on the pin. If the pin voltage is less than 0.3V, OCP is set to constant current mode. If the pin voltage is greater than 0.3V, OCP is set to Hiccup mode.                                                                                                                                                                          |

| 20              | 30                | VDD              | Output of the internal 8V linear regulator supplied by either VIN or EXTBIAS. This output supplies bias for the IC low-side drivers and the boot circuitries for the high-side drivers. The VDD pin must always be decoupled to PGND pin with a minimum of $4.7\mu$ F ceramic capacitor placed close to the pin.                                                                                                                                                                                                                                                                                                                                     |

| 21              | 31                | PGND             | Power ground connection. Connect the pin to the sources of the lower MOSFETs and the (-) terminals of the VDD decoupling capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 22              | 32                | LG1/<br>PWM_MODE | Low-side MOSFET gate driver output controlled by the buck PWM signal and PWM mode set pin. The PWM mode is set by a resistor connected between the pin and ground during the initialization period before soft-start. During the initialization period, the pin sources $10\mu$ A of current to set the voltage on the pin. If the pin voltage is less than 0.3V, the converter is set to forced PWM mode. If the pin voltage is greater than 0.3V, the converter is set to Diode Emulation (DE) mode.                                                                                                                                               |

| 23              | 34                | BOOT1            | Bootstrap pin to provide bias for the buck high-side driver. The positive terminal of the bootstrap capacitor connects to this pin. Connect a bootstrap diode between this pin and VDD to create the bias for the high-side driver. The BOOT1 to PHASE1 voltage is monitored internally. When the voltage drops to 5.95V at no switching condition, a minimum off-time pulse is issued to turn off UG1 and turn on LG1 to refresh the bootstrap capacitor and maintain the high-side driver bias voltage.                                                                                                                                            |

| 24              | 35                | PHASE1           | Phase node connection of the buck converter. This pin is connected to the junction of the upper MOSFET source, filter inductor, and the lower MOSFET drain of the buck converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 25              | 36                | UG1              | High-side MOSFET gate driver output controlled by the buck PWM signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 26              | 38                | EXTBIAS          | External bias input for the optional VDD LDO. There is an internal switch to disconnect the VIN LDO when EXTBIAS voltage is higher than 7.5V. Decouple this pin to ground with a $10\mu$ F ceramic capacitor when it is in use, otherwise tie this pin to ground. DO NOT float this pin.                                                                                                                                                                                                                                                                                                                                                             |

| 27              | 1                 | VIN              | Tie this pin to the input rail using a 5-10 $\Omega$ resistor. It provides power to the internal LDO for VDD. Decouple this pin with a small ceramic capacitor (10nF to 1µF) to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 28              | 2                 | CS+              | Input current sense signal positive input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 29              | 3                 | CS-              | Input current sense signal negative input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

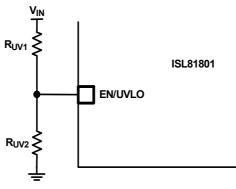

| 30              | 5                 | EN/<br>UVLO      | This pin provides enable/disable and accurate UVLO functions. The output is disabled when the pin is pulled to ground. When the voltage on the pin reaches 1.3V, the VDD and VCC5V LDOs become active. When the voltage on the pin reaches 1.8V, the PWM modulator is enabled. When the pin is floating, it is enabled by default by an internal pull-up. <b>Note</b> : The maximum current into the EN/UVLO pin should not exceed 100 $\mu$ A.                                                                                                                                                                                                      |

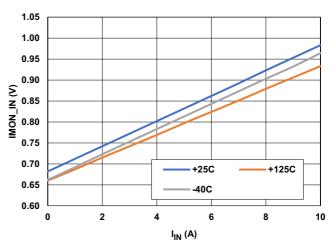

| 31              | 6                 | IMON_IN          | Input current monitor. The current from this pin is proportional to the differential voltage between the CS+ and CS- pins. Connect a resistor and capacitor network between the pin and SGND to make the pin voltage proportional to the average input current. When the pin voltage reaches 1.2V, the internal average current limit loop reduces the output voltage to keep the input current constant when constant current OCP mode is set or the converter shuts down when hiccup OCP mode is set. When the input current monitor function is not used, tie this pin to VCC5V or SGND to set up phase shift for interleaved parallel operation. |

| 32              | 7                 | CLKEN            | DE mode burst operation off state enable signal. The pin is pulled up to 5V by an internal 250k resistor in PWM and DE modes and burst mode on state. It is pulled low in Burst mode off state. The pull-down MOSFET $r_{DS(ON)}$ resistance is about 4.5k. Connect this pin with other CLKEN pins in multi-chip parallel operation applications to sync all the chips together for burst operation.                                                                                                                                                                                                                                                 |

| -               | 11                | SGND<br>EPAD     | Small-signal ground common to all control circuitries. Route this pin separately from the high current ground (PGND). Tie SGND and PGND together if there is one solid ground plane with no noisy currents around the chip. All voltage levels are measured with respect to this pin.<br>EPAD at ground potential. EPAD is connected to SGND internally. However, Renesas highly recommends soldering it directly to the ground plane for better thermal performance and noise immunity.                                                                                                                                                             |

# 3. Specifications

### 3.1 Absolute Maximum Ratings

| Parameter                                                                                                    | Minimum              | Maximum               | Unit |

|--------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|------|

| VCC5V, EN/UVLO, FB_IN to GND                                                                                 | -0.3                 | +5.9                  | V    |

| VDD to GND                                                                                                   | -0.3                 | +9                    | V    |

| EXTBIAS to GND                                                                                               | -0.3                 | +40                   | V    |

| VIN, CS+, CS-, ISEN+, ISEN- to GND                                                                           | -0.3                 | +85                   | V    |

| BOOT1, 2/UG1, 2 to PHASE1, 2                                                                                 | -0.3                 | +12                   | V    |

| PHASE1, 2 to GND                                                                                             | -5 (<20ns)/-0.3 (DC) | +85                   | V    |

| FB_OUT, SS/TRK, COMP, RT/SYNC, PLL_COMP, CLKOUT/DITHER,<br>BSTEN, CLKEN, OV, PGOOD, IMON_IN, IMON_OUT to GND | -0.3                 | VCC5V + 0.3           | V    |

| LG1/PWM_MODE, LG2/OC_MODE to GND                                                                             | -0.3                 | V <sub>DD</sub> + 0.3 | V    |

| CS+ to CS- and ISEN+ to ISEN-                                                                                | -0.3                 | +0.3                  | V    |

| VCC5V, VDD Short-Circuit to GND Duration                                                                     | 1                    |                       | s    |

| ESD Ratings                                                                                                  | Val                  | ue                    | Unit |

| Human Body Model (Tested per JS-001-2017)                                                                    | 2.                   | 2.5                   |      |

| Charge Device Model (Tested per JS-002-2014)                                                                 | 1                    | 1                     |      |

| Latch-Up (Tested per JESD78E; Class II, Level A, +125°C (T <sub>J</sub> ))                                   | 10                   | 0                     | mA   |

**CAUTION:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

### 3.2 Thermal Information

| Thermal Resistance (Typical)             | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|------------------------------------------|------------------------|------------------------|

| 32 Ld TQFN Package ( <u>Notes 4, 5</u> ) | 29                     | 1                      |

| 38 Ld HTSSOP ( <u>Notes 4, 5</u> )       | 29                     | 2                      |

Notes:

4. θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features. See <u>TB379</u>.

5. For  $\theta_{JC}$ , the case temperature location is the center of the exposed metal pad on the package underside.

| Parameter                 | Minimum | Maximum          | Unit |

|---------------------------|---------|------------------|------|

| Junction Temperature      | -55     | +150             | °C   |

| Operating Temperature     | -40     | +125             | °C   |

| Storage Temperature Range | -65     | +150             | °C   |

| Pb-Free Reflow Profile    |         | see <u>TB493</u> |      |

### 3.3 Recommended Operating Conditions

| Parameter                    | Minimum | Maximum | Unit |

|------------------------------|---------|---------|------|

| Temperature                  | -40     | +125    | °C   |

| VIN to GND                   | 4.5     | 80      | V    |

| VCC5V, EN/UVLO, FB_IN to GND | 0       | 5.4     | V    |

| VDD to GND                   | 0       | 8.4     | V    |

| EXTBIAS to GND               | 0       | 36      | V    |

### 3.4 Electrical Specifications

| Parameter                                                | Symbol                 | Test Conditions                                                | Min<br>( <u>Note 6</u> ) | Тур  | Max<br>( <u>Note 6</u> ) | Unit |

|----------------------------------------------------------|------------------------|----------------------------------------------------------------|--------------------------|------|--------------------------|------|

| V <sub>IN</sub> Supply                                   |                        | +                                                              | •                        |      | •                        |      |

| Input Voltage Range                                      | V <sub>IN</sub>        |                                                                | 4.5                      |      | 80.0                     | V    |

| V <sub>IN</sub> Supply Current                           |                        | -                                                              | •                        |      |                          |      |

| Shutdown Current (Note 7)                                | I <sub>VINQ</sub>      | EN = 0V, PGOOD is floating                                     |                          | 2.7  | 6.0                      | μA   |

| Operating Current ( <u>Note 8</u> )                      | IVINOP                 | PGOOD is floating, EXTBIAS = 0V                                |                          | 5    | 7                        | mA   |

|                                                          |                        | PGOOD is floating, EXTBIAS = 12V                               |                          | 50   |                          | μA   |

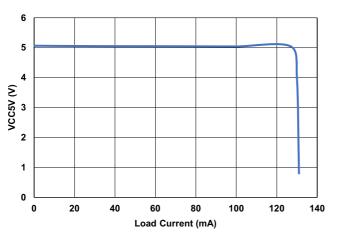

| VCC5V Supply                                             |                        | -                                                              | •                        |      |                          |      |

| Internal LDO Output Voltage                              | V <sub>CC5V</sub>      | V <sub>IN</sub> = 8V, I <sub>L</sub> = 0mA                     | 4.7                      | 5.0  | 5.4                      | V    |

|                                                          |                        | V <sub>IN</sub> = 80V, I <sub>L</sub> = 0mA                    | 4.7                      | 5.0  | 5.4                      | V    |

|                                                          |                        | V <sub>IN</sub> = 4.5V, I <sub>L</sub> = 5mA                   | 4.00                     | 4.25 |                          | V    |

|                                                          |                        | V <sub>IN</sub> > 5.6V, I <sub>L</sub> = 10mA                  | 4.65                     | 5.00 |                          | V    |

| Maximum Supply Current of<br>Internal LDO                | I <sub>VCC_MAX</sub>   | V <sub>VCC5V</sub> = 0V, V <sub>IN</sub> = 8V                  |                          | 120  |                          | mA   |

| V <sub>DD</sub> Supply                                   |                        | -                                                              | •                        |      |                          |      |

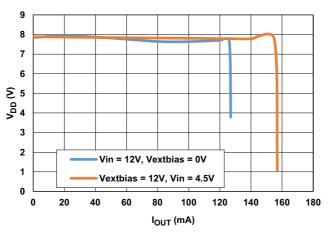

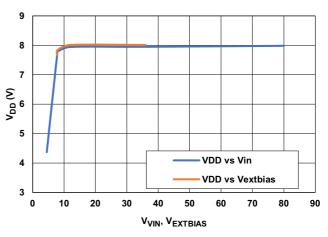

| Internal LDO Output Voltage                              | V <sub>DD</sub>        | V <sub>IN</sub> = 12V, EXTBIAS = 0V, I <sub>L</sub> = 0mA      | 7.5                      | 8.0  | 8.4                      | V    |

|                                                          |                        | V <sub>IN</sub> = 80V, EXTBIAS = 0V, I <sub>L</sub> = 0mA      | 7.5                      | 8.0  | 8.4                      | V    |

|                                                          |                        | V <sub>IN</sub> = 4.5V, EXTBIAS = 12V, I <sub>L</sub> = 0mA    | 7.5                      | 8.0  | 8.4                      | V    |

|                                                          |                        | V <sub>IN</sub> = 80V, EXTBIAS = 12V, I <sub>L</sub> = 0mA     | 7.5                      | 8.0  | 8.4                      | V    |

|                                                          |                        | V <sub>IN</sub> = 4.5V, EXTBIAS = 0V, I <sub>L</sub> = 30mA    | 3.9                      | 4.3  |                          | V    |

|                                                          |                        | V <sub>IN</sub> = 4.5V, EXTBIAS = 7.8V, I <sub>L</sub> = 30mA  | 7.4                      | 7.6  |                          | V    |

|                                                          |                        | V <sub>IN</sub> > 8.6V, EXTBIAS = 0V, I <sub>L</sub> = 75mA    | 7.30                     | 7.85 |                          | V    |

|                                                          |                        | V <sub>IN</sub> = 4.5V, EXTBIAS > 9.0V, I <sub>L</sub> = 75mA  | 7.30                     | 7.85 |                          | V    |

| Maximum Supply Current of                                | I <sub>VDD_MAX</sub>   | V <sub>VDD</sub> = 0V, EXTBIAS = 0V, V <sub>IN</sub> = 12V     |                          | 120  |                          | mA   |

| Internal LDO                                             |                        | V <sub>VDD</sub> = 4.5V, EXTBIAS = 12V, V <sub>IN</sub> = 4.5V |                          | 140  |                          | mA   |

| EXTBIAS Supply                                           |                        |                                                                |                          | 1    |                          |      |

| Switch Over Threshold Voltage, Rising                    | V <sub>EXT_THR</sub>   | EXTBIAS voltage                                                | 7.10                     | 7.38 | 7.55                     | V    |

| Switch Over Threshold Voltage,<br>Falling                | V <sub>EXT_THF</sub>   | EXTBIAS voltage                                                | 6.60                     | 6.85 | 7.10                     | V    |

| V <sub>IN</sub> UVLO                                     |                        |                                                                |                          |      |                          |      |

| V <sub>IN</sub> Rising UVLO Threshold ( <u>Note 10</u> ) | V <sub>UVLOTHR</sub>   | V <sub>IN</sub> voltage, 0mA on VCC5V and VDD                  |                          | 3.50 |                          | V    |

| V <sub>IN</sub> Falling UVLO Threshold                   | VUVLOTHF               | V <sub>IN</sub> voltage, 0mA on VCC5V and VDD                  | 3.0                      | 3.2  | 3.4                      | V    |

| VCC5V Power-On Reset                                     |                        |                                                                |                          | 1    |                          |      |

| VCC5V Rising POR Threshold                               | V <sub>PORTHR</sub>    | VCC5V voltage, 0mA on VCC5V and VDD                            | 3.7                      | 4.0  | 4.3                      | V    |

| VCC5V Falling POR Threshold                              | V <sub>PORTHF</sub>    | VCC5V voltage, 0mA on VCC5V and VDD                            | 3.30                     | 3.55 | 3.75                     | V    |

| EN/UVLO Threshold                                        |                        |                                                                |                          |      | •                        | L    |

| EN Rise Threshold                                        | V <sub>ENSS_THR</sub>  | V <sub>IN</sub> > 5.6V                                         | 0.75                     | 1.05 | 1.30                     | V    |

| EN Fall Threshold                                        | V <sub>ENSS_THF</sub>  | V <sub>IN</sub> > 5.6V                                         | 0.60                     | 0.90 | 1.10                     | V    |

| EN Hysteresis                                            | V <sub>ENSS_HYST</sub> | V <sub>IN</sub> > 5.6V                                         | 70                       | 150  | 300                      | mV   |

| UVLO Rise Threshold                                      | V <sub>UVLO_THR</sub>  | V <sub>IN</sub> > 5.6V                                         | 1.77                     | 1.80 | 1.83                     | V    |

| UVLO Hysteresis Current                                  | I <sub>UVLO_HYST</sub> | V <sub>IN</sub> = 12V, EN/UVLO = 1.815V                        | 2.5                      | 4.4  | 6.0                      | μA   |

| Parameter                                                              | Symbol                 | Test Conditions                                  | Min<br>( <u>Note 6</u> ) | Тур   | Max<br>( <u>Note 6</u> ) | Unit |

|------------------------------------------------------------------------|------------------------|--------------------------------------------------|--------------------------|-------|--------------------------|------|

| Soft-Start Current                                                     |                        |                                                  | ľ                        |       | 1                        |      |

| SS/TRK Soft-Start Charge Current                                       | I <sub>SS</sub>        | SS/TRK = 0V                                      |                          | 2.00  |                          | μA   |

| Default Internal Minimum Soft-Startin                                  | g                      |                                                  | I.                       |       | 1                        |      |

| Default Internal Output Ramping Time                                   | t <sub>SS_MIN</sub>    | SS/TRK open                                      |                          | 1.7   |                          | ms   |

| Power-Good Monitors                                                    |                        |                                                  | I                        |       | 1                        |      |

| PGOOD Upper Threshold                                                  | V <sub>PGOV</sub>      |                                                  | 107                      | 109   | 112                      | %    |

| PGOOD Lower Threshold                                                  | V <sub>PGUV</sub>      |                                                  | 87                       | 90    | 92                       | %    |

| PGOOD Low Level Voltage                                                | V <sub>PGLOW</sub>     | I_SINK = 2mA                                     |                          |       | 0.35                     | V    |

| PGOOD Leakage Current                                                  | I <sub>PGLKG</sub>     | PGOOD = 5V                                       |                          | 0     | 150                      | nA   |

| PGOOD Timing                                                           |                        |                                                  | I.                       |       | 1                        |      |

| V <sub>OUT</sub> Rising Threshold to PGOOD<br>Rising ( <u>Note 9</u> ) | t <sub>PGR</sub>       |                                                  |                          | 1.1   | 5                        | ms   |

| V <sub>OUT</sub> Falling Threshold to PGOOD<br>Falling                 | t <sub>PGF</sub>       |                                                  |                          | 80    |                          | μs   |

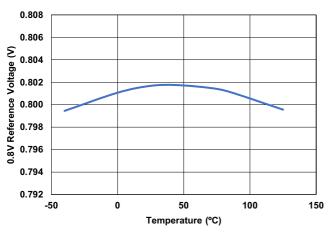

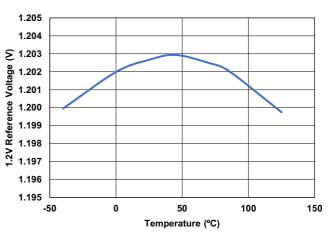

| Reference Section                                                      |                        |                                                  | I.                       |       | 1                        |      |

| Internal Voltage Loop Reference<br>Voltage                             | V <sub>REFV</sub>      |                                                  |                          | 0.800 |                          | V    |

| Reference Voltage Accuracy                                             |                        | $T_A = 0^{\circ}C \text{ to } +85^{\circ}C$      | -0.75                    |       | +0.75                    | %    |

|                                                                        |                        | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ | -1.00                    |       | +1.00                    | %    |

| Internal Current Loop Reference<br>Voltage                             | V <sub>REFI</sub>      |                                                  |                          | 1.200 |                          | V    |

| Reference Voltage Accuracy                                             |                        | $T_A = 0^{\circ}C \text{ to } +85^{\circ}C$      | -0.75                    |       | +0.75                    | %    |

|                                                                        |                        | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ | -1.00                    |       | +1.00                    | %    |

| PWM Controller Error Amplifiers                                        |                        | •                                                |                          |       | •                        |      |

| FB_OUT Pin Bias Current                                                | I <sub>FBOUTLKG</sub>  |                                                  | -50                      | 0     | +50                      | nA   |

| FB_OUT Error Amp GM                                                    | Gm1                    |                                                  |                          | 1.85  |                          | mS   |

| FB_OUT Error Amp Voltage Gain                                          | AV1                    |                                                  |                          | 82    |                          | dB   |

| FB_OUT Error Amp Gain-BW Product                                       | GBW1                   |                                                  |                          | 8     |                          | MHz  |

| FB_OUT Error Amp Output Current<br>Capability                          |                        |                                                  |                          | ±310  |                          | μA   |

| COMP Max High Voltage                                                  | V <sub>COMP_HIGH</sub> | FB_OUT = 0V                                      |                          | 3.8   |                          | V    |

| COMP Min Low Voltage                                                   | V <sub>COMP_LOW</sub>  | FB_OUT = 1V                                      |                          | 0.01  |                          | V    |

| FB_IN Pin Bias Current                                                 | I <sub>FBINLKG</sub>   |                                                  | -50                      | 0     | +50                      | nA   |

| FB_IN Error Amp GM                                                     | Gm2                    |                                                  |                          | 12    |                          | μS   |

| FB_IN Error Amp Voltage Gain                                           | AV2                    |                                                  |                          | 72    |                          | dB   |

| FB_IN Error Amp Gain-BW Product                                        | GBW2                   |                                                  |                          | 5     |                          | MHz  |

| FB_IN Active Range ( <u>Note 10</u> )                                  | $V_{FB_IN\_ACT}$       | VCC5V = 5V                                       | 0                        |       | 4.3                      | V    |

| FB_IN Logic Low Threshold ( <u>Note 10</u> )                           | $V_{FB_{IN}L}$         |                                                  | 0.2                      |       |                          | V    |

| FB_IN Logic High Threshold ( <u>Note 10</u> )                          | V <sub>FB_IN_H</sub>   | VCC5V = 5V                                       |                          |       | 4.7                      | V    |

| Parameter                                                       | Symbol                                  | Test Conditions                                                                                               | Min<br>( <u>Note 6</u> ) | Тур  | Max<br>( <u>Note 6</u> ) | Unit |

|-----------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|------|

| PWM Regulator                                                   |                                         |                                                                                                               |                          |      |                          |      |

| Buck Mode Minimum Off-Time                                      | t <sub>OFF_MIN1</sub>                   |                                                                                                               |                          | 200  |                          | ns   |

| Buck Mode Minimum On-Time                                       | t <sub>ON_MIN1</sub>                    |                                                                                                               |                          | 100  |                          | ns   |

| Boost Mode Minimum Off-Time                                     | t <sub>OFF_MIN2</sub>                   |                                                                                                               |                          | 150  |                          | ns   |

| Boost Mode Minimum On-Time                                      | t <sub>on min2</sub>                    |                                                                                                               |                          | 150  |                          | ns   |

| Buck Mode Peak-to-Peak Sawtooth<br>Amplitude                    | DV <sub>RAMP1</sub>                     | $V_{IN} = V_{OUT} = 12V$ , f <sub>SW</sub> = 300kHz                                                           |                          | 1.0  |                          | V    |

| Boost Mode Peak-to-Peak Sawtooth<br>Amplitude                   | DV <sub>RAMP2</sub>                     | V <sub>IN</sub> = V <sub>OUT</sub> = 12V, f <sub>SW</sub> = 300kHz                                            |                          | 0.9  |                          | V    |

| Buck Mode Ramp Offset                                           | V <sub>ROFFSET1</sub>                   |                                                                                                               | 0.88                     | 1.0  | 1.11                     | V    |

| Boost Mode Ramp Offset                                          | V <sub>ROFFSET2</sub>                   |                                                                                                               | 2.84                     | 3.3  | 3.7                      | V    |

| Current Sense, Current Monitors, and                            | d Average Curren                        | t Loop                                                                                                        | 1                        |      | 1                        | 1    |

| Input Current Sense Differential<br>Voltage Range               | V <sub>CS+</sub> - V <sub>CS-</sub>     |                                                                                                               | -80                      |      | +150                     | mV   |

| Input Current Sense Common-Mode<br>Voltage Range                | CMIR <sub>CS</sub>                      |                                                                                                               | 0                        |      | 80                       | V    |

| IMON_IN Offset Current                                          | ICSOFFSET                               | CS+ = CS- = 12V                                                                                               | 17                       | 19.5 | 21.5                     | μA   |

| Input Current Sense Voltage to<br>IMON_IN Current Source Gain   | Gm <sub>CS</sub>                        | 12V common-mode voltage applied to CS±     170     2       pins, 0 to 40mV differential voltage     170     2 |                          | 205  | 230                      | μS   |

| IMON_IN Error Amp GM                                            | Gm3                                     |                                                                                                               |                          | 12   |                          | μS   |

| IMON_IN Error Amp Voltage Gain                                  | AV3                                     |                                                                                                               |                          | 72   |                          | dB   |

| IMON_IN Active Range ( <u>Note 10</u> )                         | V <sub>IMON_IN_ACT</sub>                | VCC5V = 5V 0                                                                                                  |                          |      | 4.3                      | V    |

| IMON_IN Logic High Threshold (Note 10)                          | V <sub>IMON_IN_H</sub>                  | VCC5V = 5V                                                                                                    |                          |      | 4.7                      | V    |

| IMON_IN Error Amp Gain-BW Product                               | GBW3                                    |                                                                                                               |                          | 5    |                          | MHz  |

| Output Current Sense Differential<br>Voltage Range              | V <sub>ISEN+</sub> - V <sub>ISEN-</sub> |                                                                                                               | -80                      |      | +150                     | mV   |

| Output Current Sense Common-Mode<br>Voltage Range               | CMIR <sub>ISEN</sub>                    |                                                                                                               | 0                        |      | 80                       | V    |

| IMON_OUT Offset Current                                         | IISENOFFSET                             | ISEN+ = ISEN- = 12V                                                                                           | <b>17</b> 19.5           |      | 21                       | μA   |

| IMON_OUT Current                                                |                                         | ISEN+ = 12V. ISEN- = 11.96V                                                                                   | 25                       | 27.5 | 28.5                     | μA   |

| Output Current Sense Voltage to<br>IMON_OUT Current Source Gain | Gm <sub>ISEN</sub>                      | 12V common-mode voltage applied to ISEN± pins, 0mV to 40mV differential voltage                               | 170                      | 205  | 235                      | μS   |

| IMON_OUT Error Amp GM                                           | Gm4                                     |                                                                                                               |                          | 12   |                          | μS   |

| IMON_OUT Error Amp Voltage Gain                                 | AV4                                     |                                                                                                               |                          | 72   |                          | dB   |

| IMON_OUT Error Amp Gain-BW<br>Product                           | GBW4                                    |                                                                                                               |                          | 5    |                          | MHz  |

| Switching Frequency and Synchroniz                              | zation                                  | •                                                                                                             |                          |      |                          |      |

| Switching Frequency                                             | f <sub>SW</sub>                         | R <sub>T</sub> = 144kΩ                                                                                        | 220                      | 245  | 265                      | kHz  |

|                                                                 |                                         | R <sub>T</sub> = 72kΩ                                                                                         | 420                      | 450  | 485                      | kHz  |

|                                                                 |                                         | R <sub>T</sub> Open or to VCC5V                                                                               | 90                       | 120  | 145                      | kHz  |

|                                                                 |                                         | R <sub>T</sub> = 0V                                                                                           | 470                      | 575  | 650                      | kHz  |

| RT Voltage                                                      | V <sub>RT</sub>                         | R <sub>T</sub> = 72kΩ                                                                                         |                          | 560  |                          | mV   |

| SYNC Synchronization Range                                      | f <sub>SYNC</sub>                       |                                                                                                               | 140                      |      | 600                      | kHz  |

| SYNC Input Logic High (Note 10)                                 | V <sub>SYNCH</sub>                      |                                                                                                               | 3.2                      |      |                          | V    |

| SYNC Input Logic Low (Note 10)                                  | V <sub>SYNCL</sub>                      |                                                                                                               |                          |      | 0.5                      | V    |

| Parameter                                                        | Symbol                     | Test Conditions                                                                      | Min<br>( <u>Note 6</u> ) | Тур   | Max<br>( <u>Note 6</u> ) | Unit     |

|------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------|--------------------------|-------|--------------------------|----------|

| Clock Output and Frequency Dither                                |                            |                                                                                      | •                        |       |                          |          |

| CLKOUT Output High                                               | V <sub>CLKH</sub>          | I <sub>SOURCE</sub> = 1mA, VCC5V = 5V                                                | 4.55                     |       |                          | V        |

| CLKOUT Output Low                                                | V <sub>CLKL</sub>          | I <sub>SINK</sub> = 1mA                                                              |                          |       | 0.3                      | V        |

| CLKOUT Frequency                                                 | f <sub>CLK</sub>           | R <sub>T</sub> = 72kΩ                                                                | 420                      | 450   | 485                      | kHz      |

| Dither Mode Setting Current Source                               | IDITHER MODE SO            |                                                                                      |                          | 12    |                          | μA       |

| Dither Mode Setting Threshold Low                                | V <sub>DITHER_MODE_L</sub> |                                                                                      | 0.26                     |       |                          | V        |

| Dither Mode Setting Threshold High                               | V <sub>DITHER_MODE_H</sub> |                                                                                      |                          |       | 0.34                     | V        |

| Dither Source Current                                            | I <sub>DITHERSO</sub>      |                                                                                      |                          | 8     |                          | μA       |

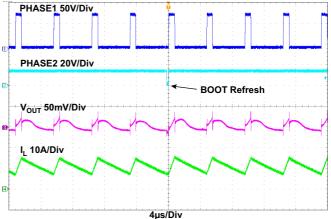

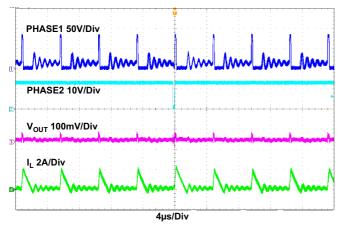

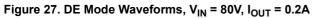

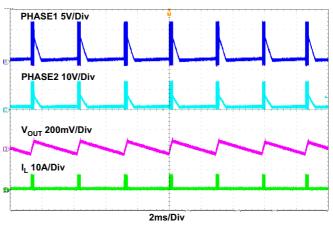

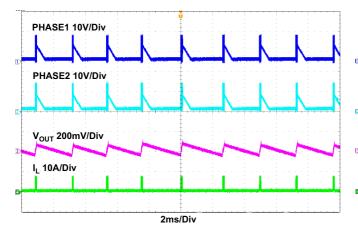

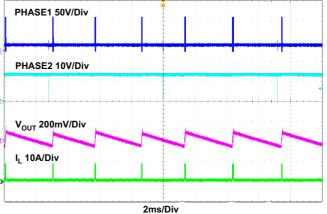

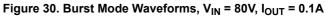

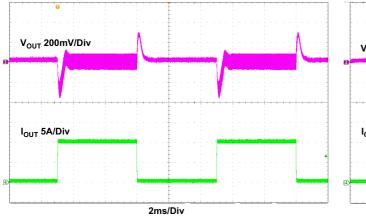

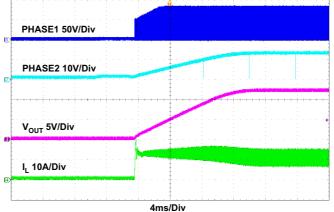

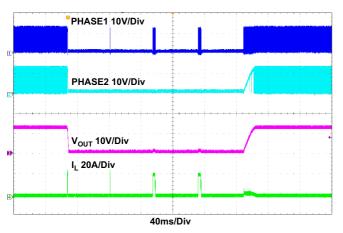

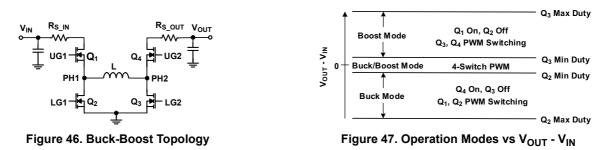

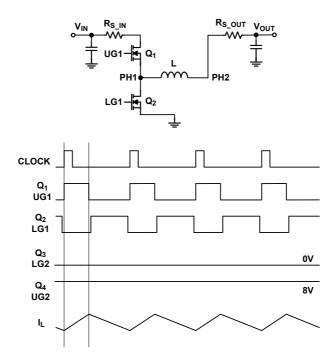

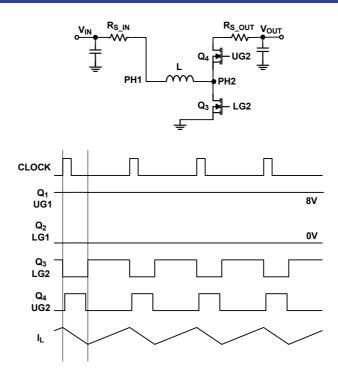

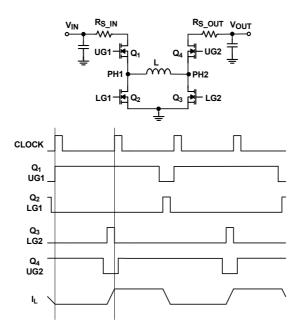

| Dither Sink Current                                              | I <sub>DITHERSI</sub>      |                                                                                      |                          | 10    |                          | μA       |