# EBU WAN PLL IDT82V32021

Version 3 April 24, 2015

6024 Silver Creek Valley Road, San Jose, CA 95138

Telephone: (800) 345-7015 • TWX: 910-338-2070 • FAX: (408) 284-2775

Printed in U.S.A.

© 2009 Integrated Device Technology, Inc.

| DISCLAIMER<br>ntegrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best pos-                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry escribed herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other ghts, of Integrated Device Technology, Inc.  LIFE SUPPORT POLICY  Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is exe- |

| ited between the manufacturer and an officer of IDT.  Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in ccordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.  A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its afety or effectiveness.                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# **Table of Contents**

| FE | EATU                                    | RES                                                   | 8  |

|----|-----------------------------------------|-------------------------------------------------------|----|

|    |                                         | HIGHLIGHTS                                            | 8  |

|    |                                         | MAIN FEATURES                                         | 8  |

|    |                                         | OTHER FEATURES                                        | 8  |

| ΑF | PLIC                                    | ATIONS                                                | 8  |

|    |                                         | IPTION                                                |    |

|    |                                         | ONAL BLOCK DIAGRAM                                    |    |

| 1  |                                         | ASSIGNMENT                                            |    |

| 2  |                                         | DESCRIPTION                                           |    |

|    |                                         |                                                       |    |

| 3  |                                         | CTIONAL DESCRIPTION                                   |    |

|    | 3.1                                     | RESET                                                 |    |

|    |                                         | MASTER CLOCK                                          |    |

|    | 3.3                                     | INPUT CLOCKS & FRAME SYNC SIGNALS                     |    |

|    |                                         | 3.3.1 Input Clocks                                    |    |

|    | 2.4                                     | 3.3.2 Frame SYNC Input Signals                        |    |

|    |                                         | INPUT CLOCK PRE-DIVIDERINPUT CLOCK QUALITY MONITORING |    |

|    | 3.3                                     | 3.5.1 Activity Monitoring                             |    |

|    |                                         | 3.5.2 Frequency Monitoring                            |    |

|    | 3.6                                     | DPLL INPUT CLOCK SELECTION                            |    |

|    | 3.0                                     | 3.6.1 External Fast Selection                         |    |

|    |                                         | 3.6.2 Forced Selection                                |    |

|    |                                         | 3.6.3 Automatic Selection                             |    |

|    | 3.7                                     | SELECTED INPUT CLOCK MONITORING                       |    |

|    | • • • • • • • • • • • • • • • • • • • • | 3.7.1 DPLL Locking Detection                          |    |

|    |                                         | 3.7.1.1 Fast Loss                                     |    |

|    |                                         | 3.7.1.2 Coarse Phase Loss                             |    |

|    |                                         | 3.7.1.3 Fine Phase Loss                               | 23 |

|    |                                         | 3.7.1.4 Hard Limit Exceeding                          | 23 |

|    |                                         | 3.7.2 Locking Status                                  | 23 |

|    |                                         | 3.7.3 Phase Lock Alarm                                | 23 |

|    | 3.8                                     | SELECTED INPUT CLOCK SWITCH                           | 25 |

|    |                                         | 3.8.1 Input Clock Validity                            | 25 |

|    |                                         | 3.8.2 Selected Input Clock Switch                     | 25 |

|    |                                         | 3.8.2.1 Revertive Switch                              |    |

|    |                                         | 3.8.2.2 Non-Revertive Switch                          |    |

|    |                                         | 3.8.3 Selected / Qualified Input Clocks Indication    |    |

|    |                                         | SELECTED INPUT CLOCK STATUS VS. DPLL OPERATING MODE   |    |

|    | 3.10                                    | DPLL OPERATING MODE                                   |    |

|    |                                         | 3.10.1 Six Operating Modes                            |    |

|    |                                         | 3.10.1.1 Free-Run Mode                                |    |

|    |                                         | 3.10.1.2 Pre-Locked Mode                              |    |

|    |                                         | 3.10.1.3 Locked Mode                                  |    |

|    |                                         | 3.10.1.3.1 Temp-Holdover Mode                         |    |

|    |                                         | 3.10.1.4 Lost-Phase Mode                              |    |

|    |                                         | 3.10.1.5 Holdover Mode                                | 29 |

|   |      | 3.10.1.5.1 Automatic Instantaneous                                    | 30  |

|---|------|-----------------------------------------------------------------------|-----|

|   |      | 3.10.1.5.2 Automatic Slow Averaged                                    | 30  |

|   |      | 3.10.1.5.3 Automatic Fast Averaged                                    |     |

|   |      | 3.10.1.5.4 Manual                                                     |     |

|   |      | 3.10.1.5.5 Holdover Frequency Offset Read                             |     |

|   |      | 3.10.1.6 Pre-Locked2 Mode                                             |     |

|   | 3.11 | DPLL OUTPUT                                                           |     |

|   |      | 3.11.1 PFD Output Limit                                               |     |

|   |      | 3.11.2 Frequency Offset Limit                                         | 32  |

|   |      | 3.11.3 PBO                                                            |     |

|   | 0.40 | 3.11.4 Four Paths of T0 DPLL Output                                   |     |

|   |      | TO APLL                                                               |     |

|   | 3.13 | OUTPUT CLOCK & FRAME SYNC SIGNALS                                     |     |

|   |      | 3.13.1 Output Clock                                                   |     |

|   | 21/  | INTERRUPT SUMMARY                                                     |     |

|   |      | TO SUMMARY                                                            |     |

|   |      | LINE CARD APPLICATION                                                 |     |

| 1 |      | PROGRAMMING INTERFACE                                                 |     |

| 7 |      | FUNCTION DESCRIPTION                                                  |     |

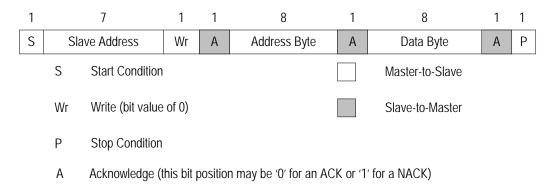

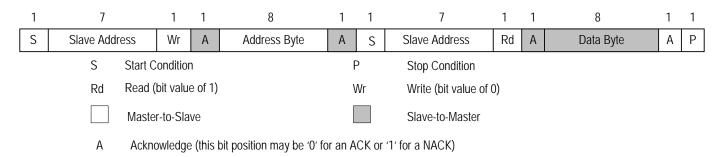

|   | 4.1  | 4.1.1 Data Transfer Format                                            |     |

|   |      | 4.1.1 Slave-receiver Mode (Write)                                     |     |

|   |      | 4.1.1.2 Slave-transmitter Mode (Read)                                 |     |

|   |      | 4.1.2 Address Assignment                                              |     |

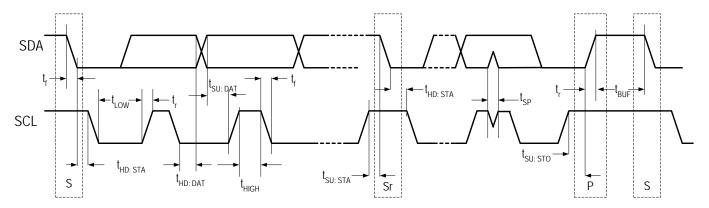

|   | 4.2  | TIMING DEFINITION                                                     |     |

| 5 |      | G                                                                     |     |

|   |      | OGRAMMING INFORMATION                                                 |     |

| U |      | REGISTER MAP                                                          |     |

|   |      | REGISTER WAS REGISTER DESCRIPTION                                     |     |

|   | 0.2  | 6.2.1 Global Control Registers                                        |     |

|   |      | 6.2.2 Interrupt Registers                                             |     |

|   |      | 6.2.3 Input Clock Frequency & Priority Configuration Registers        |     |

|   |      | 6.2.4 Input Clock Quality Monitoring Configuration & Status Registers |     |

|   |      | 6.2.5 T0 DPLL Input Clock Selection Registers                         |     |

|   |      | 6.2.6 TO DPLL State Machine Control Registers                         |     |

|   |      | 6.2.7 T0 DPLL & T0 APLL Configuration Registers                       |     |

|   |      | 6.2.8 Output Configuration Registers                                  |     |

|   |      | 6.2.9 PBO & Phase Offset Control Registers                            |     |

|   |      | 6.2.10 Synchronization Configuration Registers                        |     |

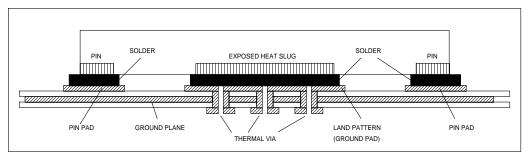

| 7 | THE  | RMAL MANAGEMENT                                                       |     |

|   | 7.1  | JUNCTION TEMPERATURE                                                  |     |

|   |      | EXAMPLE OF JUNCTION TEMPERATURE CALCULATION                           |     |

|   |      | HEATSINK EVALUATION                                                   |     |

| _ |      | VFQFPN EPAD THERMAL RELEASE PATH                                      |     |

| 8 |      | CTRICAL SPECIFICATIONS                                                |     |

|   |      | ABSOLUTE MAXIMUM RATING                                               |     |

|   |      | RECOMMENDED OPERATION CONDITIONS                                      |     |

|   | 8.3  | I/O SPECIFICATIONS                                                    |     |

|   |      | 8.3.1 CMOS Input / Output Port                                        |     |

|   |      | JITTER & WANDER PERFORMANCE                                           |     |

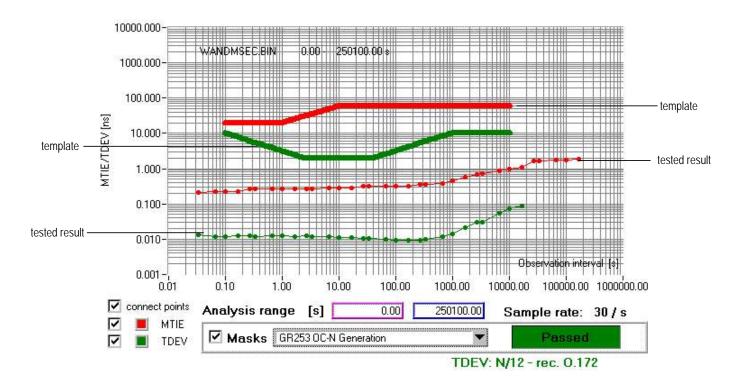

|   |      | OUTPUT WANDER GENERATION                                              |     |

|   | 86   | INPLIT / DITTPLIT CLOCK TIMING                                        | 100 |

| IDT82V32021                    | EBU WAN PLL |

|--------------------------------|-------------|

|                                |             |

| 8.7 OUTPUT CLOCK TIMING        |             |

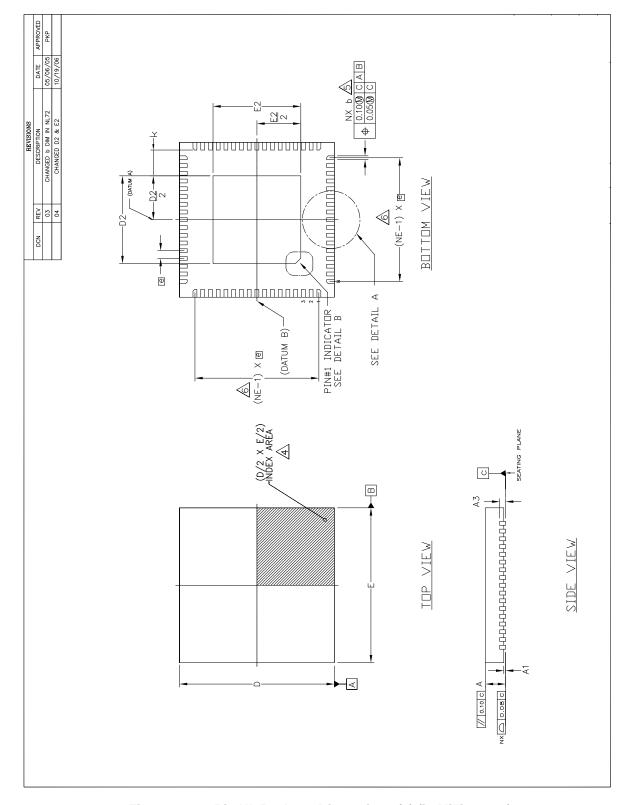

| PACKAGE DIMENSIONS - 68-PIN NL | 106         |

| ORDERING INFORMATION           | 108         |

| DATASHEET DOCUMENT HISTORY     | 108         |

5

April 24, 2015

# List of Tables

| Table 1: | Pin Description                                                                                | 12  |

|----------|------------------------------------------------------------------------------------------------|-----|

|          | Related Bit / Register in Chapter 3.2                                                          |     |

| Table 3: | Related Bit / Register in Chapter 3.3                                                          | 17  |

| Table 4: | Related Bit / Register in Chapter 3.4                                                          | 18  |

| Table 5: | Related Bit / Register in Chapter 3.5                                                          | 20  |

|          | Input Clock Selection                                                                          |     |

|          | External Fast Selection                                                                        |     |

|          | 'n' Assigned to the Input Clock                                                                |     |

|          | Related Bit / Register in Chapter 3.6                                                          |     |

|          | Coarse Phase Limit Programming (the selected input clock of 2 kHz, 4 kHz or 8 kHz)             |     |

|          | Coarse Phase Limit Programming (the selected input clock of other than 2 kHz, 4 kHz and 8 kHz) |     |

|          | Related Bit / Register in Chapter 3.7                                                          |     |

|          | Related Bit / Register in Chapter 3.8                                                          |     |

|          | TO DPLL Operating Mode Control                                                                 |     |

|          | Related Bit / Register in Chapter 3.9                                                          |     |

|          | Frequency Offset Control in Temp-Holdover Mode                                                 |     |

|          | Holdover Frequency Offset Read                                                                 |     |

|          | Related Bit / Register in Chapter 3.10                                                         |     |

|          | Related Bit / Register in Chapter 3.10                                                         |     |

|          | Related Bit / Register in Chapter 3.12                                                         |     |

|          | Output on OUT1 if Derived from T0 DPLL Output                                                  |     |

|          | Output on OUT1 if Derived from T0 APLL                                                         |     |

|          | Frame Sync Input Signal Selection                                                              |     |

|          | Synchronization Control                                                                        |     |

|          | Related Bit / Register in Chapter 3.13                                                         |     |

|          | Related Bit / Register in Chapter 3.14                                                         |     |

|          | Definition of S/Sr and P Conditions                                                            |     |

|          | Timing Definition for Standard Mode and Fast Mode(1)                                           |     |

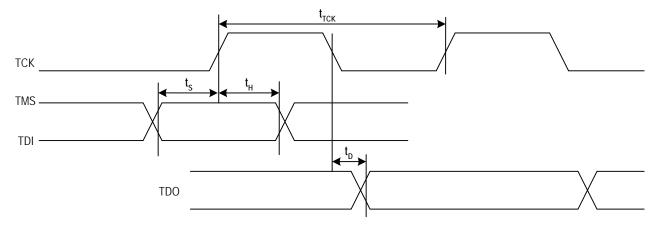

|          | JTAG Timing Characteristics                                                                    |     |

|          | Register List and Map                                                                          |     |

|          | Power Consumption and Maximum Junction Temperature                                             |     |

|          | Thermal Data                                                                                   |     |

|          | Absolute Maximum Rating                                                                        |     |

|          | Recommended Operation Conditions                                                               |     |

|          | CMOS Input Port Electrical Characteristics                                                     |     |

|          | CMOS Input Port with Internal Pull-Up Resistor Electrical Characteristics                      |     |

|          | CMOS Input Port with Internal Pull-Down Resistor Electrical Characteristics                    |     |

|          | Output Clock Jitter Generation                                                                 |     |

|          | Output Clock Phase Noise                                                                       |     |

|          | Input Jitter Tolerance (155.52 MHz)                                                            |     |

|          | Input Jitter Tolerance (1.544 MHz)                                                             |     |

|          | Input Jitter Tolerance (2.048 MHz)                                                             |     |

|          | Input Jitter Tolerance (8 kHz)                                                                 |     |

|          | TO DPLL Jitter Transfer & Damping Factor                                                       |     |

|          | Input/Output Clock Timing                                                                      |     |

|          | Output Clock Timing                                                                            | 101 |

# List of Figures

| Figure 1.  | Functional Block Diagram                                  | 10 |

|------------|-----------------------------------------------------------|----|

| Figure 2.  | Pin Assignment (Top View)                                 | 11 |

| Figure 3.  | Pre-Divider for An Input Clock                            | 18 |

| Figure 4.  | Input Clock Activity Monitoring                           | 19 |

| Figure 5.  | External Fast Selection                                   | 21 |

| Figure 6.  | TO Selected Input Clock vs. DPLL Automatic Operating Mode | 27 |

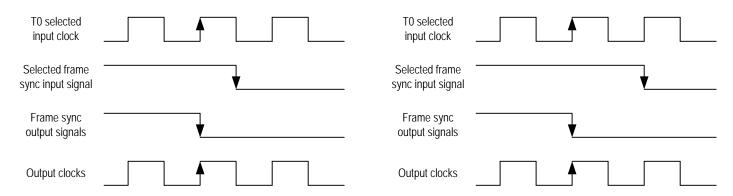

| Figure 7.  | On Target Frame Sync Input Signal Timing                  | 36 |

| Figure 8.  | 0.5 UI Early Frame Sync Input Signal Timing               | 36 |

| Figure 9.  | 0.5 UI Late Frame Sync Input Signal Timing                | 37 |

| Figure 10. | 1 UI Late Frame Sync Input Signal Timing                  | 37 |

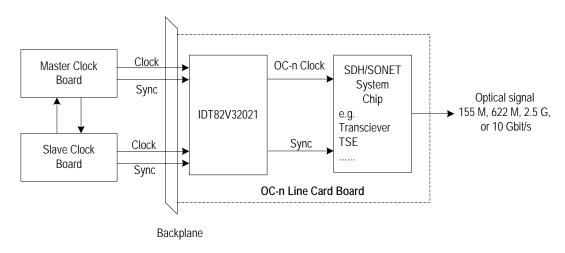

| Figure 11. | Line Card Application                                     | 39 |

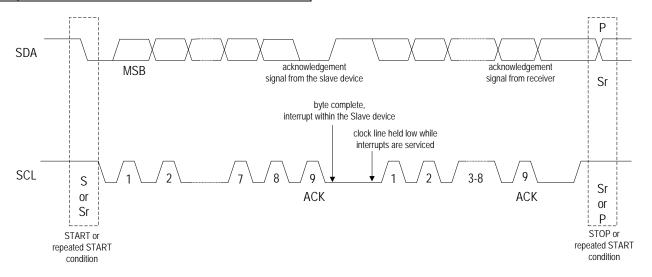

|            | Data Transfer on the I2C-bus                              |    |

|            | Slave-receiver Mode                                       |    |

| Figure 14. | Slave-transmitter Mode                                    | 41 |

|            | Address Assignment                                        |    |

| Figure 16. | Timing Definition of I2C-bus                              | 42 |

| Figure 17. | JTAG Interface Timing Diagram                             | 44 |

| Figure 18. | Assembly for Expose Pad thermal Release Path (Side View)  | 93 |

| Figure 19. | Output Wander Generation                                  | 99 |

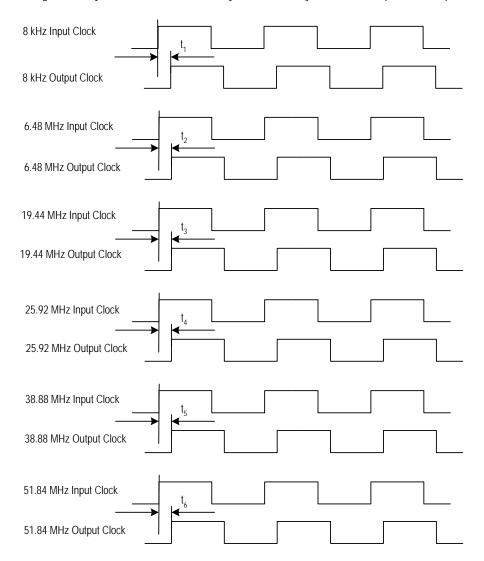

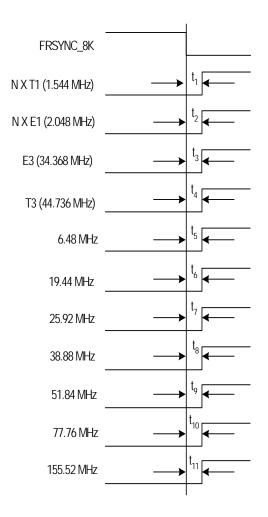

| Figure 20. | Input / Output Clock Timing                               | 00 |

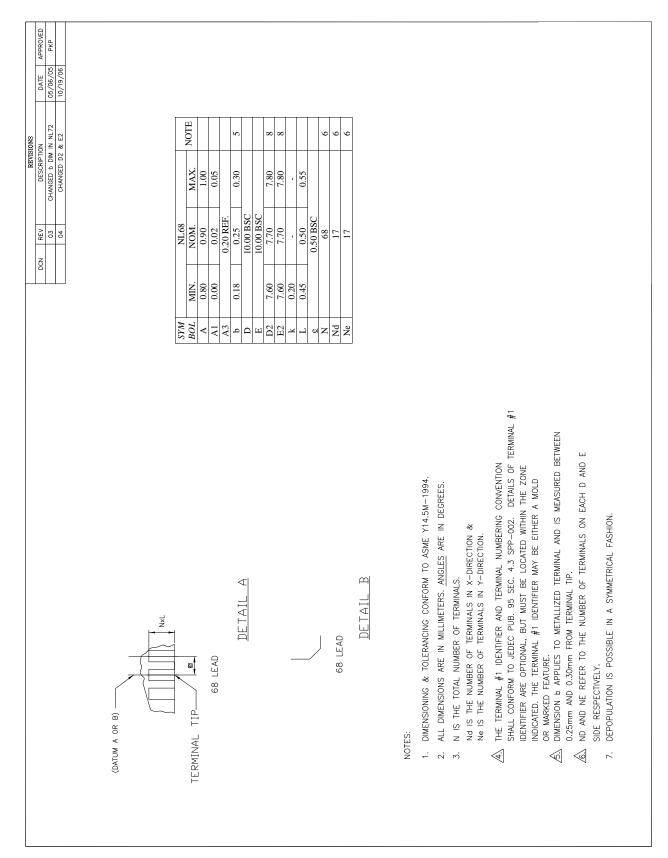

| Figure 21. | 68-Pin NL Package Dimensions (a) (in Millimeters)         | 06 |

| Figure 22. | 68-Pin NL Package Dimensions (b) (in Millimeters)         | 07 |

# **EBU WAN PLL**

IDT82V32021

### **FEATURES**

#### **HIGHLIGHTS**

- The first single PLL chip:

- Features 1.2 Hz to 560 Hz bandwidth

- Exceeds GR-253-CORE (OC-12) and ITU-T G.813 (STM-16/ Option I) jitter generation requirements

- Provides node clocks for Cellular and WLL base-station (GSM and 3G networks)

- Provides clocks for DSL access concentrators (DSLAM), especially for Japan TCM-ISDN network timing based ADSL equipments

#### MAIN FEATURES

- Provides an integrated single-chip solution for Synchronous Equipment Timing Source, including 4E and 4 clocks

- Employs DPLL and APLL to feature excellent jitter performance and minimize the number of the external components

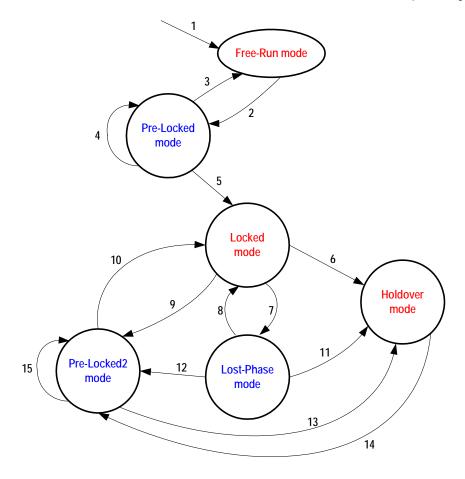

- Supports Forced or Automatic operating mode switch controlled by an internal state machine; the primary operating modes are Free-Run, Locked and Holdover

- Supports programmable DPLL bandwidth (1.2 Hz to 560 Hz in 8 steps) and damping factor (1.2 to 20 in 5 steps)

- Supports 1.1X10<sup>-5</sup> ppm absolute holdover accuracy and 4.4X10<sup>-8</sup> ppm instantaneous holdover accuracy

- Supports PBO to minimize phase transients on T0 DPLL output to be no more than 0.61 ns

- Supports phase absorption when phase-time changes on T0 selected input clock are greater than a programmable limit over an interval of less than 0.1 seconds

- Limits the phase and frequency offset of the output

- Supports manual and automatic selected input clock switch

- Supports automatic hitless selected input clock switch on clock failure

- Supports three types of input clock sources: recovered clock from STM-N or OC-n, PDH network synchronization timing and external synchronization reference timing

- Provides two 2 kHz, 4 kHz or 8 kHz frame sync input signals, and an 8 kHz frame sync output signal

- Provides two input clocks whose frequency cover from 2 kHz to 155.52 MHz

- Provides one output clock whose frequency covers from 1Hz to 155.52 MHz

- Provides output clocks for BITS, GPS, 3G, GSM, etc.

- Supports CMOS input/output

- Supports master clock calibration

- Supports Line Card application

- Meets Telcordia GR-1244-CORE, GR-253-CORE, ITU-T G.812, ITU-T G.813 and ITU-T G.783 criteria

#### OTHER FEATURES

- I<sup>2</sup>C programming interface

- IEEE 1149.1 JTAG Boundary Scan

- Single 3.3 V operation with 5 V tolerant CMOS I/Os

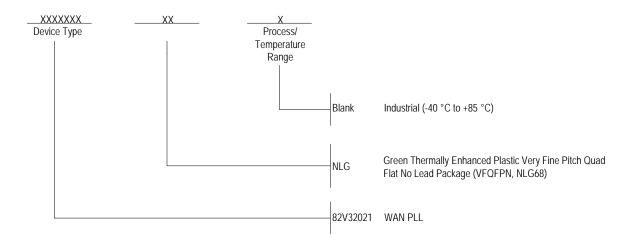

- 68-pin VFQFPN package, Green package options available

## **APPLICATIONS**

- BITS / SSU

- SMC / SEC (SONET / SDH)

- DWDM cross-connect and transmission equipments

- Central Office Timing Source and Distribution

- Core and access IP switches / routers

- Gigabit and Terabit IP switches / routers

- IP and ATM core switches and access equipments

- Cellular and WLL base-station node clocks

- Broadband and multi-service access equipments

- Any other telecom equipments that need synchronous equipment system timing

# **DESCRIPTION**

The IDT82V32021 is an integrated, single-chip solution for the Synchronous Equipment Timing Source for 4E and 4 clocks in SONET / SDH equipments, DWDM and Wireless base station, such as GSM, 3G, DSL concentrator, Router and Access Network applications.

The device supports three types of input clock sources: recovered clock from STM-N or OC-n, PDH network synchronization timing and external synchronization reference timing.

An input clock is automatically or manually selected for DPLL locking. The DPLL supports three primary operating modes: Free-Run, Locked and Holdover. In Free-Run mode, the DPLL refers to the master clock. In Locked mode, the DPLL locks to the selected input clock. In Holdover mode, the DPLL resorts to the frequency data acquired in

Locked mode. Whatever the operating mode is, the DPLL gives a stable performance without being affected by operating conditions or silicon process variations.

If the DPLL outputs are processed by T0 APLL, the outputs of the device will be in a better jitter/wander performance.

A high stable input is required for the master clock in different applications. The master clock is used as a reference clock for all the internal circuits in the device. It can be calibrated within  $\pm 741$  ppm.

All the read/write registers are accessed only through an  $I^2\mbox{C}$  programming interface.

The device can be used typically in Line Card application.

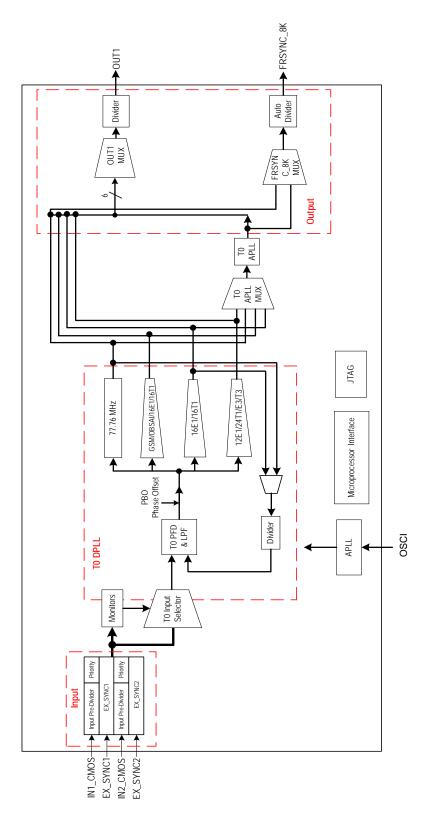

# FUNCTIONAL BLOCK DIAGRAM

Figure 1. Functional Block Diagram

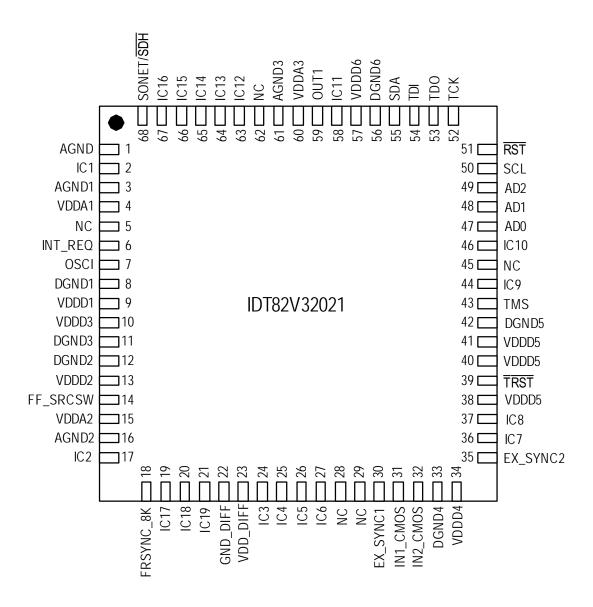

# 1 PIN ASSIGNMENT

Figure 2. Pin Assignment (Top View)

# 2 PIN DESCRIPTION

Table 1: Pin Description

| Name                  | Pin No.                             | I/O            | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Description <sup>1</sup>                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-----------------------|-------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Global Control Signal |                                     |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| OSCI                  | 7                                   | I              | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OSCI: Crystal Oscillator Master Clock A nominal 12.8000 MHz clock provided by a crystal oscillator is input on this pin. It is the master clock for the device.                                                                                                                                                    |  |  |  |  |

| - puil-down           |                                     | CMOS           | FF_SRCSW: External Fast Selection Enable  During reset, this pin determines the default value of the EXT_SW bit (b4, 0BH) <sup>2</sup> . The EXT_SW bit determines whether the External Fast Selection is enabled.  High: The default value of the EXT_SW bit (b4, 0BH) is '1' (External Fast selection is enabled);  Low: The default value of the EXT_SW bit (b4, 0BH) is '0' (External Fast selection is disabled).  After reset, this pin selects an input clock for the T0 DPLL if the External Fast selection is enabled:  High: IN1_CMOS is selected.  Low: IN2_CMOS is selected.  After reset, the input on this pin takes no effect if the External Fast selection is disabled. |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                       |                                     | l<br>pull-down | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SONET/SDH: SONET / SDH Frequency Selection During reset, this pin determines the default value of the IN_SONET_SDH bit (b2, 09H): High: The default value of the IN_SONET_SDH bit is '1' (SONET); Low: The default value of the IN_SONET_SDH bit is '0' (SDH). After reset, the value on this pin takes no effect. |  |  |  |  |

| RST                   | 51                                  | l<br>pull-up   | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RST: Reset A low pulse of at least 50 µs on this pin resets the device. After this pin is high, the device will still be held in reset state for 500 ms (typical).                                                                                                                                                 |  |  |  |  |

|                       |                                     | '              | Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Synchronization Input Signal                                                                                                                                                                                                                                                                                       |  |  |  |  |

| EX_SYNC1              | 30                                  | l<br>pull-down | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EX_SYNC1: External Sync Input 1 A 2 kHz, 4 kHz or 8 kHz signal is input on this pin.                                                                                                                                                                                                                               |  |  |  |  |

| EX_SYNC2              | 35                                  | l<br>pull-down | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EX_SYNC2: External Sync Input 2 A 2 kHz, 4 kHz or 8 kHz signal is input on this pin.                                                                                                                                                                                                                               |  |  |  |  |

|                       |                                     |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input Clock                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| IN1_CMOS              | 31                                  | l<br>pull-down | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IN1_CMOS: Input Clock 1  A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is input on this pin.                                                                                                   |  |  |  |  |

| IN2_CMOS              | 32                                  | l<br>pull-down | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IN2_CMOS: Input Clock 2  A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is input on this pin.                                                                                                   |  |  |  |  |

|                       | Output Frame Synchronization Signal |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| FRSYNC_8K             | 18                                  | 0              | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FRSYNC_8K: 8 kHz Frame Sync Output An 8 kHz signal is output on this pin.                                                                                                                                                                                                                                          |  |  |  |  |

|                       |                                     |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Output Clock                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| OUT1                  | 59                                  | 0              | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OUT1: Output Clock 1  A 1 Hz, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 (includes 65.536 MHz) <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup> , E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz or 155.52 MHz clock is output on this pin.           |  |  |  |  |

Table 1: Pin Description (Continued)

| Name    | Pin No.                                | I/O            | Туре | Description <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|---------|----------------------------------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         | I <sup>2</sup> C Programming Interface |                |      |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| INT_REQ | 6                                      | 0              | CMOS | INT_REQ: Interrupt Request This pin is used as an interrupt request. The output characteristics are determined by the HZ_EN bit (b1, 0CH) and the INT_POL bit (b0, 0CH).                                                                                                                                                                                                                         |  |  |  |

| AD0     | 47                                     |                |      | AD[2:0]: Address Input 2 to 0 The address is input on these pins.                                                                                                                                                                                                                                                                                                                                |  |  |  |

| AD1     | 48                                     | I              | CMOS | The dudress is input on these pins.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| AD2     | 49                                     |                |      |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| SCL     | 50                                     | 1              | CMOS | SCL: Serial Clock Line The serial clock is input on this pin. The clock is 100 kbit/s in Standard mode and 400 kbit/s in Fast mode. Should be pulled high via a 10 k $\Omega$ resistor.                                                                                                                                                                                                          |  |  |  |

| SDA     | 55                                     | I/O            | CMOS | SDA: Serial Data Input/Output This pin is used as the input/output for the serial data. Should be pulled high via a 10 k $\Omega$ resistor.                                                                                                                                                                                                                                                      |  |  |  |

|         |                                        |                | ,    | JTAG (per IEEE 1149.1)                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| TRST    | 39                                     | I<br>pull-down | CMOS | TRST: JTAG Test Reset (Active Low) A low signal on this pin resets the JTAG test port. This pin should be connected to ground when JTAG is not used.                                                                                                                                                                                                                                             |  |  |  |

| TMS     | 43                                     | l<br>pull-up   | CMOS | TMS: JTAG Test Mode Select The signal on this pin controls the JTAG test performance and is sampled on the rising edge of TCK.                                                                                                                                                                                                                                                                   |  |  |  |

| TCK     | 52                                     | l<br>pull-down | CMOS | TCK: JTAG Test Clock The clock for the JTAG test is input on this pin. TDI and TMS are sampled on the rising edge of TCK and TDO is updated on the falling edge of TCK.  If TCK is idle at a low level, all stored-state devices contained in the test logic will indefinitely retain their state.                                                                                               |  |  |  |

| TDI     | 54                                     | l<br>pull-up   | CMOS | TDI: JTAG Test Data Input The test data is input on this pin. It is clocked into the device on the rising edge of TCK.                                                                                                                                                                                                                                                                           |  |  |  |

| TDO     | 53                                     | 0              | CMOS | TDO: JTAG Test Data Output The test data is output on this pin. It is clocked out of the device on the falling edge of TCK. TDO pin outputs a high impedance signal except during the process of data scanning. This pin can indicate the interrupt of T0 selected input clock fail, as determined by the LOSFLAG_ON_TDO bit (b6, 0BH). Refer to Chapter 3.8.1 Input Clock Validity for details. |  |  |  |

|         |                                        |                |      | Power & Ground                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| VDDD1   | 9                                      |                |      | VDDDn: 3.3 V Digital Power Supply Each VDDDn should be paralleled with ground through a 0.1 µF capacitor.                                                                                                                                                                                                                                                                                        |  |  |  |

| VDDD2   | 13                                     |                |      | Zasi. 1222. Silona so paranosa inin grana anoagi. a sii pi sapasia.                                                                                                                                                                                                                                                                                                                              |  |  |  |

| VDDD3   | 10                                     | Power          |      |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| VDDD4   | 34                                     | Power          | -    |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| VDDD5   | 38, 40, 41                             |                |      |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| VDDD6   | 57                                     |                |      |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| VDDA1   | 4                                      |                |      | VDDAn: 3.3 V Analog Power Supply Each VDDAn should be paralleled with ground through a 0.1 µF capacitor.                                                                                                                                                                                                                                                                                         |  |  |  |

| VDDA2   | 15                                     | Power          | -    | Lacit νουλιτι οπουία με paralleled with ground through a σ.1 με capacitor.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| VDDA3   | 60                                     |                |      |                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

Table 1: Pin Description (Continued)

| Name     | Pin No. | I/O    | Туре | Description <sup>1</sup>     |

|----------|---------|--------|------|------------------------------|

| VDD_DIFF | 23      | Power  | -    | VDD_DIFF: 3.3 V Power Supply |

| DGND1    | 8       |        |      | DGNDn: Digital Ground        |

| DGND2    | 12      |        |      |                              |

| DGND3    | 11      |        |      |                              |

| DGND4    | 33      | Ground | -    |                              |

| DGND5    | 42      |        |      |                              |

| DGND6    | 56      |        |      |                              |

| AGND1    | 3       |        |      | AGNDn: Analog Ground         |

| AGND2    | 16      | Ground | -    |                              |

| AGND3    | 61      |        |      |                              |

| GND_DIFF | 22      | Ground | -    | GND_DIFF: Ground             |

| AGND     | 1       | Ground | -    | AGND: Analog Ground          |

Table 1: Pin Description (Continued)

| Name   | Pin No.           | I/O | Туре | Description <sup>1</sup>                                                                    |  |  |  |

|--------|-------------------|-----|------|---------------------------------------------------------------------------------------------|--|--|--|

| Others |                   |     |      |                                                                                             |  |  |  |

| IC1    | 2                 |     |      | IC: internally connected Internal Use. These pins should be left open for normal operation. |  |  |  |

| IC2    | 17                |     |      | internar ose. Triese pins snould be left open for normal operation.                         |  |  |  |

| IC3    | 24                |     |      |                                                                                             |  |  |  |

| IC4    | 25                |     |      |                                                                                             |  |  |  |

| IC5    | 26                |     |      |                                                                                             |  |  |  |

| IC6    | 27                |     |      |                                                                                             |  |  |  |

| IC7    | 36                |     |      |                                                                                             |  |  |  |

| IC8    | 37                |     |      |                                                                                             |  |  |  |

| IC9    | 44                |     |      |                                                                                             |  |  |  |

| IC10   | 46                | -   | -    |                                                                                             |  |  |  |

| IC11   | 58                |     |      |                                                                                             |  |  |  |

| IC12   | 63                |     |      |                                                                                             |  |  |  |

| IC13   | 64                |     |      |                                                                                             |  |  |  |

| IC14   | 65                |     |      |                                                                                             |  |  |  |

| IC15   | 66                |     |      |                                                                                             |  |  |  |

| IC16   | 67                |     |      |                                                                                             |  |  |  |

| IC17   | 19                |     |      |                                                                                             |  |  |  |

| IC18   | 20                |     |      |                                                                                             |  |  |  |

| IC19   | 21                |     |      |                                                                                             |  |  |  |

| NC     | 5, 28, 29, 45, 62 | -   | -    | NC: Not Connected                                                                           |  |  |  |

#### Noto

<sup>1.</sup> All the unused input pins should be connected to ground; the output of all the unused output pins are don't-care.

<sup>2.</sup> The contents in the brackets indicate the position of the register bit/bits.

**<sup>3</sup>**. N x 8 kHz: 1 ≤ N ≤ 19440.

<sup>4.</sup> N x E1: N = 1, 2, 3, 4, 6, 8, 12, 16, 24, 32, 48, 64.

<sup>5.</sup> N x T1: N = 1, 2, 3, 4, 6, 8, 12, 16, 24, 32, 48, 64, 96.

**<sup>6</sup>**. N x 13.0 MHz: N = 1, 2, 4.

<sup>7.</sup> N x 3.84 MHz: N = 1, 2, 4, 8, 16, 10, 20, 40.

# 3 FUNCTIONAL DESCRIPTION

## 3.1 RESET

The reset operation resets all registers and state machines to their default value or status.

After power on, the device must be reset for normal operation.

For a complete reset, the  $\overline{RST}$  pin must be asserted low for at least 50  $\mu$ s. After the  $\overline{RST}$  pin is pulled high, the device will still be in reset state for 500 ms (typical). If the  $\overline{RST}$  pin is held low continuously, the device remains in reset state.

#### 3.2 MASTER CLOCK

A nominal 12.8000 MHz clock, provided by a crystal oscillator, is input on the OSCI pin. This clock is provided for the device as a master clock. The master clock is used as a reference clock for all the internal circuits. A better active edge of the master clock is selected by the OSC\_EDGE bit to improve jitter and wander performance.

In fact, an offset from the nominal frequency may input on the OSCI pin. This offset can be compensated by setting the NOMINAL\_FRE-Q\_VALUE[23:0] bits. The calibration range is within ±741 ppm.

The performance of the master clock should meet GR-1244-CORE, GR-253-CORE, ITU-T G.812 and G.813 criteria.

Table 2: Related Bit / Register in Chapter 3.2

| Bit                      | Register                                                                  | Address (Hex) |

|--------------------------|---------------------------------------------------------------------------|---------------|

| NOMINAL_FREQ_VALUE[23:0] | NOMINAL_FREQ[23:16]_CNFG, NOMINAL_FREQ[15:8]_CNFG, NOMINAL_FREQ[7:0]_CNFG | 06, 05, 04    |

| OSC_EDGE                 | OSCI_CNFG                                                                 | 0A            |

## 3.3 INPUT CLOCKS & FRAME SYNC SIGNALS

Altogether two clocks and two frame sync signals are input to the device.

#### 3.3.1 INPUT CLOCKS

The device provides two CMOS input clock ports: IN1\_CMOS and IN2\_CMOS.

According to the input clock source, the following clock sources are supported:

- T1: Recovered clock from STM-N or OC-n

- · T2: PDH network synchronization timing

- T3: External synchronization reference timing

The clock sources can be from T1, T2 or T3.

For SDH and SONET networks, the default frequency is different. SONET / SDH frequency selection is controlled by the IN\_SONET\_SDH bit. During reset, the default value of the IN\_SONET\_SDH bit is deter-

mined by the SONET/SDH pin: high for SONET and low for SDH. After reset, the input signal on the SONET/SDH pin takes no effect.

#### 3.3.2 FRAME SYNC INPUT SIGNALS

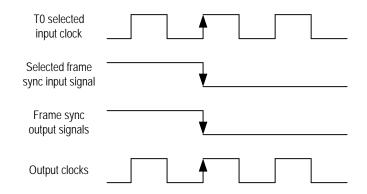

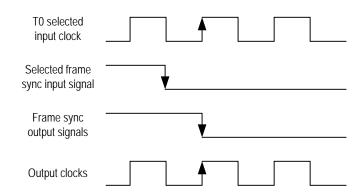

Two 2 kHz, 4 kHz or 8 kHz frame sync signals are input on the EX\_SYNC1 and EX\_SYNC2 pins respectively. They are CMOS inputs. The input frequency should match the setting in the SYNC\_FREQ[1:0] bits. The frame sync signals are only valid for the OC-n clock (6.48 MHz, 19.44 MHz, 38.88 MHz and 77.76 MHz) input.

Only one of the two frame sync input signals is used for frame sync output signal synchronization. Refer to Chapter 3.13.2 Frame SYNC Output Signal for details.

Table 3: Related Bit / Register in Chapter 3.3

| Bit            | Register             | Address (Hex) |

|----------------|----------------------|---------------|

| IN_SONET_SDH   | INPUT MODE CNFG      | 09            |

| SYNC_FREQ[1:0] | IIVI OT_INODE_CIVI O | 07            |

#### 3.4 INPUT CLOCK PRE-DIVIDER

Each input clock is assigned an internal Pre-Divider. The Pre-Divider is used to divide the clock frequency down to the DPLL required frequency, which is no more than 38.88 MHz. For each input clock, the DPLL required frequency is set by the corresponding IN\_FREQ[3:0] bits.

If the input clock is of 2 kHz, 4 kHz or 8 kHz, the Pre-Divider is bypassed automatically and the corresponding IN\_FREQ[3:0] bits should be set to match the input frequency; the input clock can be inverted, as determined by the IN\_2K\_4K\_8K\_INV bit.

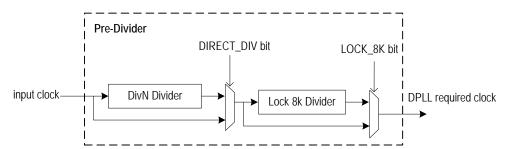

Each Pre-Divider consists of a DivN Divider and a Lock 8k Divider, as shown in Figure 3.

Either the DivN Divider or the Lock 8k Divider can be used or both can be bypassed, as determined by the DIRECT\_DIV bit and the LOCK\_8K bit.

When the DivN Divider is used, the division factor setting should observe the following order:

- 1. Select an input clock by the PRE\_DIV\_CH\_VALUE[3:0] bits;

- 2. Write the lower eight bits of the division factor to the PRE\_DIVN\_VALUE[7:0] bits;

- 3. Write the higher eight bits of the division factor to the PRE\_DIVN\_VALUE[14:8] bits.

Once the division factor is set for the input clock selected by the PRE\_DIV\_CH\_VALUE[3:0] bits, it is valid until a different division factor is set for the same input clock. The division factor is calculated as follows:

Division Factor = (the frequency of the clock input to the DivN Divider ÷ the frequency of the DPLL required clock set by the IN\_-FREQ[3:0] bits) - 1

The DivN Divider can only divide the input clock whose frequency is lower than (<) 155.52 MHz.

When the Lock 8k Divider is used, the input clock is divided down to 8 kHz automatically.

The Pre-Divider configuration and the division factor setting depend on the input clock on one of the clock input pin and the DPLL required clock. Here is an example:

The input clock on the IN2\_CMOS pin is 155.52 MHz; the DPLL required clock is 6.48 MHz by programming the IN\_FREQ[3:0] bits of register IN2\_CMOS\_CNFG to '0010'. Do the following to divide the input clock:

Use the DivN Divider to divide the clock down to 6.48 MHz: Set the PRE\_DIV\_CH\_VALUE[3:0] bits to '0011'; Set the DIRECT\_DIV bit in Register IN2\_CMOS\_CNFG to '1' and the LOCK\_8K bit in Register IN2\_CMOS\_CNFG to '0'; 155.52 ÷ 6.48 = 24; 24 - 1 = 23, so set the PRE\_DIVN\_VALUE[14:0] bits to '10111'.

Figure 3. Pre-Divider for An Input Clock

Table 4: Related Bit / Register in Chapter 3.4

| Bit                   | Register                                | Address (Hex) |

|-----------------------|-----------------------------------------|---------------|

| IN_FREQ[3:0]          |                                         |               |

| DIRECT_DIV            | IN1_CMOS_CNFG, IN2_CMOS_CNFG            | 16, 17        |

| LOCK_8K               |                                         |               |

| IN_2K_4K_8K_INV       | FR_SYNC_CNFG                            | 74            |

| PRE_DIV_CH_VALUE[3:0] | PRE_DIV_CH_CNFG                         | 23            |

| PRE_DIVN_VALUE[14:0]  | PRE_DIVN[14:8]_CNFG, PRE_DIVN[7:0]_CNFG | 25, 24        |

## 3.5 INPUT CLOCK QUALITY MONITORING

The qualities of the input clocks are always monitored in the following aspects:

- Activity

- Frequency

The qualified clocks are available for T0 DPLL selection. The T0 selected input clock has to be monitored further. Refer to Chapter 3.7 Selected Input Clock Monitoring for details.

#### 3.5.1 ACTIVITY MONITORING

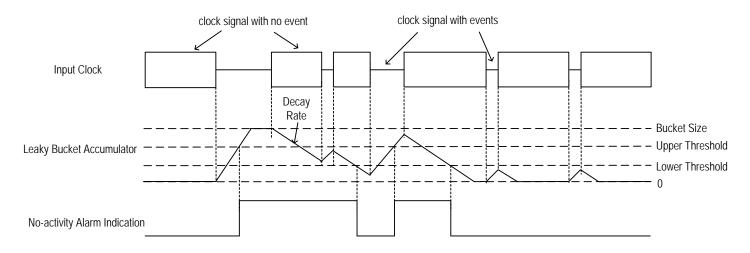

Activity is monitored by using an internal leaky bucket accumulator, as shown in Figure 4.

Each input clock is assigned an internal leaky bucket accumulator. The input clock is monitored for each period of 128 ms and the internal leaky bucket accumulator increases by 1 when an event is detected; it decreases by 1 if no event is detected within the period set by the decay rate. The event is that an input clock drifts outside (>)  $\pm 500$  ppm with respect to the master clock within a 128 ms period.

There are four configurations (0 - 3) for a leaky bucket accumulator. The leaky bucket configuration for an input clock is selected by the cor-

responding BUCKET\_SEL[1:0] bits. Each leaky bucket configuration consists of four elements: upper threshold, lower threshold, bucket size and decay rate.

The bucket size is the capability of the accumulator. If the number of the accumulated events reach the bucket size, the accumulator will stop increasing even if further events are detected. The upper threshold is a point above which a no-activity alarm is raised. The lower threshold is a point below which the no-activity alarm is cleared. The decay rate is a certain period during which the accumulator decreases by 1 if no event is detected.

The leaky bucket configuration is programmed by one of four groups of register bits: the BUCKET\_SIZE\_n\_DATA[7:0] bits, the UPPER\_ THRESHOLD\_n\_DATA[7:0] bits, the LOWER\_THRESHOLD\_n\_ DATA[7:0] bits and the DECAY\_RATE\_n\_DATA[1:0] bits respectively; 'n' is  $0 \sim 3$ .

The no-activity alarm status of the input clock is indicated by the  $INn\_CMOS\_NO\_ACTIVITY\_ALARM$  bit (n = 1 or 2).

The input clock with a no-activity alarm is disqualified for clock selection for T0 DPLL.

Figure 4. Input Clock Activity Monitoring

#### 3.5.2 FREQUENCY MONITORING

Frequency is monitored by comparing the input clock with a reference clock. The reference clock can be derived from the master clock or the output of T0 DPLL, as determined by the FREQ\_MON\_CLK bit.

A frequency hard alarm threshold is set for frequency monitoring. If the FREQ\_MON\_HARD\_EN bit is '1', a frequency hard alarm is raised when the frequency of the input clock with respect to the reference clock is above the threshold; the alarm is cleared when the frequency is below the threshold.

The frequency hard alarm threshold can be calculated as follows:

Frequency Hard Alarm Threshold (ppm) = (ALL\_FREQ\_HARD\_THRESHOLD[3:0] + 1) X FREQ\_MON\_FACTOR[3:0]

If the FREQ\_MON\_HARD\_EN bit is '1', the frequency hard alarm status of the input clock is indicated by the INn\_CMOS\_FRE-Q\_HARD\_ALARM bit (n = 1 or 2). When the FREQ\_MON\_HARD\_EN bit is '0', no frequency hard alarm is raised even if the input clock is above the frequency hard alarm threshold.

The input clock with a frequency hard alarm is disqualified for clock selection for T0 DPLL.

In addition, if the input clock is 2 kHz, 4 kHz or 8 kHz, its clock edges with respect to the reference clock are monitored. If any edge drifts outside  $\pm 5\%$ , the input clock is disqualified for clock selection for T0 DPLL. The input clock is qualified if any edge drifts inside  $\pm 5\%$ . This function is supported only when the IN\_NOISE\_WINDOW bit is '1'.

The frequency of each input clock with respect to the reference clock can be read by doing the following step by step:

- 1. Select an input clock by setting the IN\_FREQ\_READ\_CH[3:0] bits:

- 2. Read the value in the IN\_FREQ\_VALUE[7:0] bits and calculate as follows:

Input Clock Frequency (ppm) = IN\_FREQ\_VALUE[7:0] X FRE-Q\_MON\_FACTOR[3:0]

Note that the value set by the FREQ\_MON\_FACTOR[3:0] bits depends on the application.

Table 5: Related Bit / Register in Chapter 3.5

| Bit                                               | Register                                        | Address (Hex)  |

|---------------------------------------------------|-------------------------------------------------|----------------|

| BUCKET_SIZE_n_DATA[7:0] $(3 \ge n \ge 0)$         | BUCKET_SIZE_0_CNFG ~ BUCKET_SIZE_3_CNFG         | 33, 37, 3B, 3F |

| UPPER_THRESHOLD_n_DATA[7:0] (3 $\geq$ n $\geq$ 0) | UPPER_THRESHOLD_0_CNFG ~ UPPER_THRESHOLD_3_CNFG | 31, 35, 39, 3D |

| LOWER_THRESHOLD_n_DATA[7:0] $(3 \ge n \ge 0)$     | LOWER_THRESHOLD_0_CNFG ~ LOWER_THRESHOLD_3_CNFG | 32, 36, 3A, 3E |

| DECAY_RATE_n_DATA[1:0] $(3 \ge n \ge 0)$          | DECAY_RATE_0_CNFG ~ DECAY_RATE_3_CNFG           | 34, 38, 3C, 40 |

| BUCKET_SEL[1:0]                                   | IN1_CMOS_CNFG, IN2_CMOS_CNFG                    | 16, 17         |

| INn_CMOS_NO_ACTIVITY_ALARM (n = 1 or 2)           | IN1 IN2 CMOS STS                                | 44             |

| INn_CMOS_FREQ_HARD_ALARM (n = 1 or 2)             | 11V1_11V2_GIVIO3_313                            | 77             |

| FREQ_MON_CLK                                      | MON SW PBO CNFG                                 | 0B             |

| FREQ_MON_HARD_EN                                  | MON_SW_I BO_CNI G                               | OD             |

| ALL_FREQ_HARD_THRESHOLD[3:0]                      | ALL_FREQ_MON_THRESHOLD_CNFG                     | 2F             |

| FREQ_MON_FACTOR[3:0]                              | FREQ_MON_FACTOR_CNFG                            | 2E             |

| IN_NOISE_WINDOW                                   | PHASE_MON_PBO_CNFG                              | 78             |

| IN_FREQ_READ_CH[3:0]                              | IN_FREQ_READ_CH_CNFG                            | 41             |

| IN_FREQ_VALUE[7:0]                                | IN_FREQ_READ_STS                                | 42             |

#### 3.6 DPLL INPUT CLOCK SELECTION

The EXT\_SW bit and the T0\_INPUT\_SEL[3:0] bits determine the input clock selection, as shown in Table 6:

Table 6: Input Clock Selection

| Control Bits |                   | Input Clock Selection   |  |

|--------------|-------------------|-------------------------|--|

| EXT_SW       | T0_INPUT_SEL[3:0] |                         |  |

| 1            | don't-care        | External Fast selection |  |

| 0            | other than 0000   | Forced selection        |  |

|              | 0000              | Automatic selection     |  |

External Fast selection is done between IN1\_CMOS and IN2\_C-MOS.

Forced selection is done by setting the related registers.

Automatic selection is done based on the results of input clocks quality monitoring and the related registers configuration.

The selected input clock is attempted to be locked by T0 DPLL.

#### 3.6.1 EXTERNAL FAST SELECTION

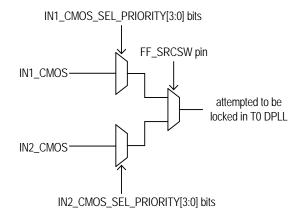

In External Fast selection, only IN1\_CMOS and IN2\_CMOS are available for selection. Refer to Figure 5. The results of input clocks

quality monitoring (refer to Chapter 3.5 Input Clock Quality Monitoring) do not affect input clock selection.

The T0 input clock selection is determined by the FF\_SRCSW pin after reset (this pin determines the default value of the EXT\_SW bit during reset, refer to Chapter 2 Pin Description), the IN1\_C-MOS\_SEL\_PRIORITY[3:0] bits and the IN2\_CMOS\_SEL\_PRIORITY[3:0] bits, as shown in Figure 5 and Table 7:

Figure 5. External Fast Selection

Table 7: External Fast Selection

| Control Pin & Bits                                                           |                 |                          | the Selected Input Clock |

|------------------------------------------------------------------------------|-----------------|--------------------------|--------------------------|

| FF_SRCSW (after reset) IN1_CMOS_SEL_PRIORITY[3:0] IN2_CMOS_SEL_PRIORITY[3:0] |                 | the Selected input Glock |                          |

| high                                                                         | other than 0000 | don't-care               | IN1_CMOS                 |

| low                                                                          | don't-care      | other than 0000          | IN2_CMOS                 |

#### 3.6.2 FORCED SELECTION

In Forced selection, the selected input clock is set by the T0\_IN-PUT\_SEL[3:0] bits. The results of input clocks quality monitoring (refer to Chapter 3.5 Input Clock Quality Monitoring) do not affect the input clock selection.

#### 3.6.3 AUTOMATIC SELECTION

In Automatic selection, the input clock selection is determined by its validity and priority. The validity depends on the results of input clock quality monitoring (refer to Chapter 3.5 Input Clock Quality Monitoring).

In the qualified input clocks, the one with the higher priority is selected. The priority is configured by the corresponding INn\_CMOS\_SEL\_PRIORITY[3:0] bits (n = 1 or 2). If more than one qualified input clock is available and has the same priority, the input clock with the smaller 'n' is selected. See Table 8 for the 'n' assigned to the input clock.

Table 8: 'n' Assigned to the Input Clock

| Input Clock | 'n' Assigned to the Input Clock |

|-------------|---------------------------------|

| IN1_CMOS    | 1                               |

| IN2_CMOS    | 3                               |

Table 9: Related Bit / Register in Chapter 3.6