### HIGH-SPEED 32K x 18 DUAL-PORT STATIC RAM

#### LEAD FINISH (SnPb) ARE IN EOL PROCESS - LAST TIME BUY EXPIRES JUNE 15, 2018

#### **Features**

- True Dual-Ported memory cells which allow simultaneous reads of the same memory location

- High-speed access

- Commercial: 15/20ns (max.)

- Low-power operation

- IDT7037L Active: 1W (typ.)

- Standby: 1mW (typ.)

- Dual chip enables allow for depth expansion without external logic

- IDT7037 easily expands data bus width to 36 bits or more using the Master/Slave select when cascading more than one device

- M/S = VIH for BUSY output flag on Master,

M/S = VIL for BUSY input on Slave

- Interrupt Flag

- On-chip port arbitration logic

- Full on-chip hardware support of semaphore signaling between ports

- Fully asynchronous operation from either port

- Separate upper-byte and lower-byte controls for multiplexed bus and bus matching compatibility

- TTL-compatible, single 5V (±10%) power supply

- Available in a 100-pin TQFP

- Industrial temperature range (-40°C to +85°C) is available for selected speeds

- Green parts available. See ordering information

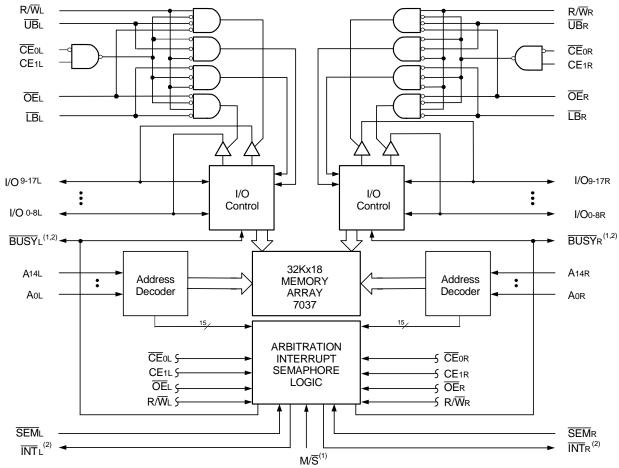

#### Functional Block Diagram

NOTES:

- 1.  $\overline{BUSY}$  is an input as a Slave (M/ $\overline{S}$  = VIL) and an output when it is a Master (M/ $\overline{S}$  = VIH).

- 2. BUSY and INT are non-tri-state totem-pole outputs (push-pull).

**JUNE 2018**

4838 drw 01

### Description

The IDT7037 is a high-speed 32K x 18 Dual-Port Static RAM. The IDT7037 is designed to be used as a stand-alone 576K-bit Dual-Port RAM or as a combination MASTER/SLAVE Dual-Port RAM for 36-bit-or-more word systems. Using the IDT MASTER/SLAVE Dual-Port RAM approach in 36-bit or wider memory system applications results in full-speed, error-free operation without the need for additional discrete logic.

This device provides two independent ports with separate control,

address, and I/O pins that permit independent, asynchronous access for reads or writes to any location in memory. An automatic power down feature controlled by the chip enables (CEo and CE1) permit the on-chip circuitry of each port to enter a very low standby power mode.

Fabricated using CMOS high-performance technology, these devices typically operate on only 1W of power.

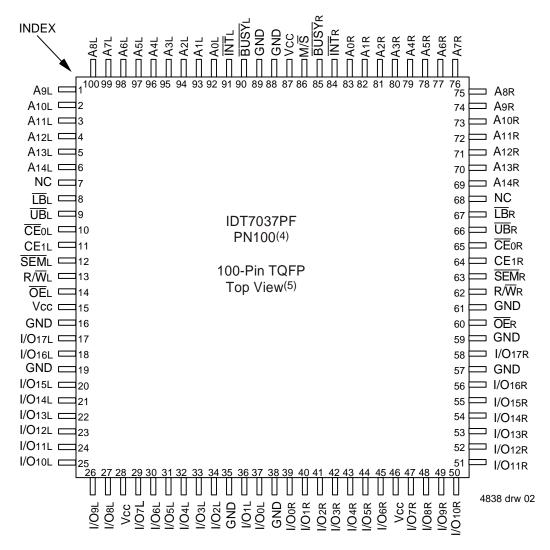

The IDT7037 is packaged in a 100-pin Thin Quad Flatpack (TQFP).

### Pin Configurations (1,2,3)

- 1. All Vcc pins must be connected to power supply.

- 2. All GND pins must be connected to ground supply.

- 3. Package body is approximately 14mm x 14mm x 1.4mm.

- 4. This package code is used to reference the package diagram.

- 5. This text does not indicate orientation of the actual part marking.

#### Pin Names

| Left Port          | Right Port                    | Names                  |  |

|--------------------|-------------------------------|------------------------|--|

| <u>C</u> E₀L, CE1L | Œ0R, CE1R                     | Chip Enables           |  |

| R/WL               | R/W̄R                         | Read/Write Enable      |  |

| ŌĒL                | <del>OE</del> R               | Output Enable          |  |

| Aol - A14L         | Aor - A14R                    | Address                |  |

| I/O0L - I/O17L     | I/O0R - I/O17R                | Data Input/Output      |  |

| SEML               | <del>SEM</del> R              | Semaphore Enable       |  |

| ŪB.                | Ū <b>B</b> R                  | Upper Byte Select      |  |

| <del>LB</del> L    | <del>LB</del> R               | Lower Byte Select      |  |

| ĪNTL               | <del>INT</del> R              | Interrupt Flag         |  |

| BUSYL              | <del>BUS</del> <del>Y</del> R | Busy Flag              |  |

| M/S                |                               | Master or Slave Select |  |

| Vcc                |                               | Power                  |  |

| G                  | ND                            | Ground                 |  |

4838 tbl 01

### Absolute Maximum Ratings<sup>(1)</sup>

| Symbol               | Rating                                     | Commercial<br>& Industrial | Military     | Unit |

|----------------------|--------------------------------------------|----------------------------|--------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +7.0               | -0.5 to +7.0 | V    |

| TBIAS                | Temperature<br>Under Bias                  | -55 to +125                | -65 to +135  | °C   |

| Tstg                 | Storage<br>Temperature                     | -65 to +150                | -65 to +150  | °C   |

| Іоит                 | DC Output Current                          | 50                         | 50           | mA   |

#### NOTES:

- 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

- 2. VTERM must not exceed Vcc + 10% for more than 25% of the cycle time or 10ns maximum, and is limited to  $\leq$  20mA for the period of VTERM  $\geq$  Vcc + 10%.

# Maximum Operating Temperature and Supply Voltage<sup>(1)</sup>

| <u>a a. a a la la </u> | ,                                     |     |                   |

|------------------------|---------------------------------------|-----|-------------------|

| Grade                  | Ambient<br>Temperature <sup>(2)</sup> | GND | Vcc               |

| Military               | -55°C to +125°C                       | 0V  | 5.0V <u>+</u> 10% |

| Commercial             | 0°C to +70°C                          | 0V  | 5.0V <u>+</u> 10% |

| Industrial             | -40°C to +85°C                        | 0V  | 5.0V <u>+</u> 10% |

#### NOTES:

- 1. Industrial Temperature: for specific speeds, packages and powers contact your

- 2. This is the parameter Ta. This is the "instant on" case temperature.

#### Recommended DC Operating Conditions

| Symbol | Parameter          | Min.                | Тур. | Max.   | Unit |

|--------|--------------------|---------------------|------|--------|------|

| Vcc    | Supply Voltage     | 4.5                 | 5.0  | 5.5    | V    |

| GND    | Ground             | 0                   | 0    | 0      | V    |

| Vıн    | Input High Voltage | 2.2                 | _    | 6.0(2) | V    |

| VIL    | Input Low Voltage  | -0.5 <sup>(1)</sup> | _    | 0.8    | V    |

4838 tbl 04

- 1.  $VIL \ge -1.5V$  for pulse width less than 10ns.

- 2. VTERM must not exceed Vcc + 10%.

### Capacitance

$(TA = +25^{\circ}C, f = 1.0MHz)$

| Symbol | Parameter <sup>(1)</sup> | Conditions <sup>(2)</sup> | Max. | Unit |

|--------|--------------------------|---------------------------|------|------|

| Cin    | Input Capacitance        | VIN = 3dV                 | 9    | pF   |

| Соит   | Output Capacitance       | Vout = 3dV                | 10   | pF   |

- 1. This parameter is determined by device characterization but is not production

- 2. 3dV represents the interpolated capacitance when the input and output signals switch from 0V to 3V or from 3V to 0V.

Truth Table I: Chip Enable (1,2)

| CE | ΣĒ₀              | CE1              | Mode                            |

|----|------------------|------------------|---------------------------------|

|    | VIL              | VIH              | Port Selected (TTL Active)      |

| L  | <u>&lt;</u> 0.2V | ≥Vcc -0.2V       | Port Selected (CMOS Active)     |

|    | VIH              | Χ                | Port Deselected (TTL Inactive)  |

|    | Х                | VIL              | Port Deselected (TTL Inactive)  |

| Н  | ≥Vcc -0.2V       | Х                | Port Deselected (CMOS Inactive) |

|    | Χ                | <u>&lt;</u> 0.2V | Port Deselected (CMOS Inactive) |

NOTES:

4838 tbl 06

- 1. Chip Enable references are shown above with the actual  $\overline{\text{CE}}_0$  and CE1 levels,  $\overline{\text{CE}}$  is a reference only.

- 2. 'H' = VIH and 'L' = VIL.

- 3. CMOS standby requires 'X' to be either  $\leq$  0.2V or  $\geq$  Vcc 0.2V.

### Truth Table II: Non-Contention Read/Write Control

|       |     | Inpu | uts <sup>(1)</sup> |    |     | Outputs             |                    |                          |

|-------|-----|------|--------------------|----|-----|---------------------|--------------------|--------------------------|

| CE(2) | R/₩ | ŌĒ   | ŪB                 | LВ | SEM | I/O <sub>9-17</sub> | I/O <sub>0-8</sub> | Mode                     |

| Н     | Х   | Χ    | Х                  | Х  | Н   | High-Z              | High-Z             | Deselected: Power-Down   |

| Х     | Х   | Χ    | Н                  | Н  | Н   | High-Z              | High-Z             | Both Bytes Deselected    |

| L     | L   | Х    | L                  | Н  | Н   | DATAIN              | High-Z             | Write to Upper Byte Only |

| L     | L   | Х    | Н                  | L  | Н   | High-Z              | DATAIN             | Write to Lower Byte Only |

| L     | L   | Χ    | L                  | L  | Н   | DATAIN              | DATAIN             | Write to Both Bytes      |

| L     | Н   | L    | L                  | Н  | Н   | DATAout             | High-Z             | Read Upper Byte Only     |

| L     | Н   | L    | Н                  | L  | Н   | High-Z              | DATAout            | Read Lower Byte Only     |

| L     | Н   | L    | L                  | L  | Н   | DATAout             | DATAout            | Read Both Bytes          |

| Х     | Х   | Н    | Х                  | Х  | Х   | High-Z              | High-Z             | Outputs Disabled         |

NOTES: 4838 tbl 07

- 1.  $A_{0L} A_{14L} \neq A_{0R} A_{14R}$ .

- 2. Refer to Chip Enable Truth Table.

### Truth Table III: Semaphore Read/Write Control<sup>(1)</sup>

|       | Inputs <sup>(1)</sup> |    |    |    |     |                     | puts               |                                |

|-------|-----------------------|----|----|----|-----|---------------------|--------------------|--------------------------------|

| CE(2) | R/ <b>W</b>           | ŌĒ | ŪB | LΒ | SEM | I/O <sub>9-17</sub> | I/O <sub>0-8</sub> | Mode                           |

| Н     | Н                     | L  | Х  | Χ  | L   | DATAout             | DATAout            | Read Data in Semaphore Flag    |

| Х     | Н                     | L  | Н  | Н  | L   | DATAout             | DATAout            | Read Data in Semaphore Flag    |

| Н     | 1                     | Х  | Х  | Х  | L   | DATAIN              | DATAIN             | Write I/Oo into Semaphore Flag |

| Х     | 1                     | Χ  | Н  | Н  | L   | DATAIN              | DATAIN             | Write I/Oo into Semaphore Flag |

| L     | Х                     | Χ  | L  | Χ  | L   |                     |                    | Not Allowed                    |

| L     | Х                     | Χ  | Х  | L  | L   |                     |                    | Not Allowed                    |

NOTES:

- 1. There are eight semaphore flags written to via I/Oo and read from all the I/Os (I/Oo-I/O17). These eight semaphore flags are addressed by Ao-A2.

- 2. Refer to Chip Enable Truth Table.

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(2)</sup> ( $Vcc = 5.0V \pm 10\%$ )

|        |                                      |                                                      | 7037L |      |      |

|--------|--------------------------------------|------------------------------------------------------|-------|------|------|

| Symbol | Parameter                            | Test Conditions                                      | Min.  | Max. | Unit |

| Iu     | Input Leakage Current <sup>(1)</sup> | Vcc = 5.5V, $VIN = 0V$ to $Vcc$                      | _     | 5    | μΑ   |

| llo    | Output Leakage Current               | $\overline{CE}$ = V <sub>IH</sub> , VouT = 0V to Vcc | -     | 5    | μΑ   |

| Vol    | Output Low Voltage                   | IoL = 4mA                                            | _     | 0.4  | V    |

| Vон    | Output High Voltage                  | IOH = -4mA                                           | 2.4   | _    | V    |

4838 tbl 09

#### NOTES:

- 1. At Vcc ≤ 2.0V, input leakages are undefined.

- 2. Refer to Chip Enable Truth Table.

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range $^{(1,6,7)}$ (Vcc = 5.0V ± 10%)

| Symbol            | Parameter                                                     | Test Condition                                                                                                                                                                                                                                                                                    | Version | 7037L15<br>Com'l Only<br>Typ. <sup>(1)</sup> Max |     | 7037L20<br>Com'l Only<br>Typ. <sup>(1)</sup> Max |     | Unit |

|-------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------|-----|--------------------------------------------------|-----|------|

| lcc               | Dynamic Operating<br>Current                                  | <u>CE</u> = V <sub>I</sub> L, Outputs Disabled<br><u>SEM</u> = V <sub>I</sub> H                                                                                                                                                                                                                   | COM'L L | 220                                              | 340 | 200                                              | 300 | mA   |

|                   | (Both Ports Active)                                           | $f = f_{MAX}^{(2)}$                                                                                                                                                                                                                                                                               | IND L   |                                                  |     | -                                                | —   |      |

| ls <sub>B</sub> 1 | Standby Current<br>(Both Ports - TTL Level                    | <u>CEL</u> = <u>CER</u> = VIH<br>SEMR = SEML = VIH                                                                                                                                                                                                                                                | COM'L L | 65                                               | 100 | 50                                               | 75  | mA   |

|                   | Inputs)                                                       | $f = f_{MAX}^{(2)}$                                                                                                                                                                                                                                                                               | IND L   | _                                                |     | _                                                |     |      |

| ISB2              | Standby Current<br>(One Port - TTL Level                      | CE"A" = VIL and CE"B" = VIH <sup>(4)</sup>                                                                                                                                                                                                                                                        | COM'L L | 145                                              | 225 | 130                                              | 195 | mA   |

|                   | Inputs)                                                       | Active Po <u>rt Outputs Disabled,</u><br>f=fmax <sup>(2)</sup> , SEMR = SEML = VIH                                                                                                                                                                                                                | IND L   | _                                                | _   |                                                  |     |      |

| ISB3              | Full Standby Current                                          | Both Ports CEL and                                                                                                                                                                                                                                                                                | COM'L L | 0.2                                              | 3.0 | 0.2                                              | 3.0 | mA   |

|                   | (Both Ports - All CMOS<br>Level Inputs)                       | $\begin{array}{l} \overline{\text{CER}} \geq \text{Vcc} - 0.2\text{V}, \ \text{Vin} \geq \text{Vcc} - 0.2\text{V} \\ \underline{\text{or}} \ \text{Vin} \leq \underline{0.2\text{V}}, \ f = 0^{(3)} \\ \overline{\text{SEMr}} = \overline{\text{SEML}} \geq \text{Vcc} - 0.2\text{V} \end{array}$ | IND L   |                                                  |     |                                                  |     |      |

| ISB4              | Full Standby Current<br>(One Port - All CMOS<br>Level Inputs) | $\overline{CE}$ 'A" $\leq 0.2V$ and $\overline{CE}$ B" $\geq V$ CC $\cdot 0.2V$ (d), $\overline{SEMR} = \overline{SEML} \geq V$ CC $\cdot 0.2V$ ,                                                                                                                                                 | COM'L L | 135                                              | 220 | 120                                              | 190 | mA   |

|                   | Level lipus)                                                  | SEIVIR = SEIVIL $\geq$ VCC - 0.2V,<br>VIN $\geq$ VCC - 0.2V or VIN $\leq$ 0.2V, Active Port<br>Outputs Disabled, f = fmax <sup>(2)</sup>                                                                                                                                                          | IND L   |                                                  |     | _                                                |     |      |

- 1. Vcc = 5V, TA = +25°C, and are not production tested. Icccc = 120mA (Typ.)

- 2. At f = fmax, address and control lines (except Output Enable) are cycling at the maximum frequency read cycle of 1/trc, and using "AC Test Conditions" of input levels of GND to 3V.

- 3. f = 0 means no address or control lines change.

- 4. Port "A" may be either left or right port. Port "B" is the opposite from port "A".

- 5. Refer to Chip Enable Truth Table.

- 6. Industrial Temperature: for specific speeds, packages and powers contact your sales office.

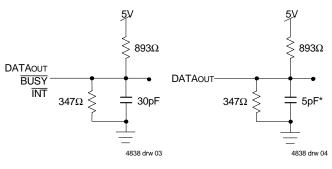

#### **AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V     |

|-------------------------------|-----------------|

| Input Rise/Fall Times         | 3ns Max.        |

| Input Timing Reference Levels | 1.5V            |

| Output Reference Levels       | 1.5V            |

| Output Load                   | Figures 1 and 2 |

|                               | 4838 tbl 11     |

Figure 1. AC Output Test Load

Figure 2. Output Test Load (for tLz, tHz, twz, tow) \* Including scope and jig.

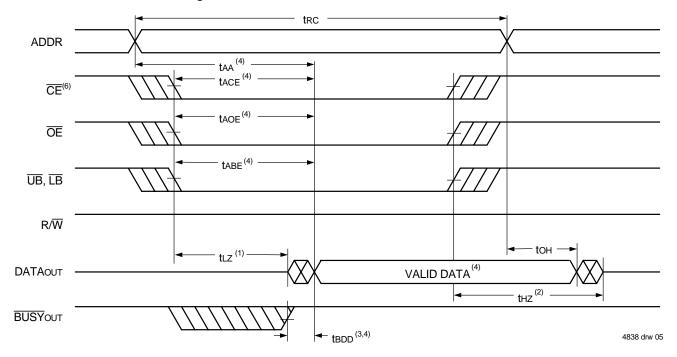

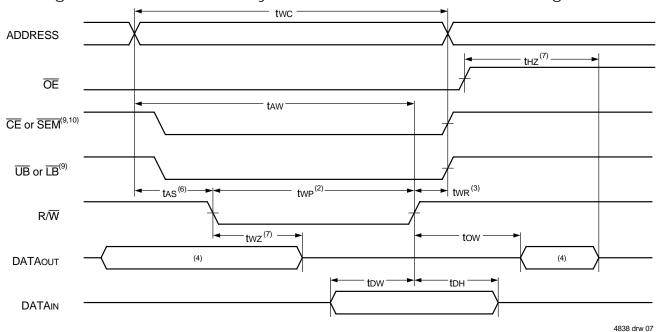

### Waveform of Read Cycles<sup>(5)</sup>

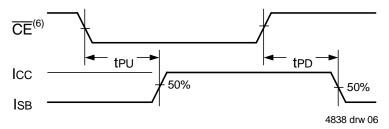

## Timing of Power-Up Power-Down

- 1. Timing depends on which signal is asserted last,  $\overline{OE}$ ,  $\overline{CE}$ ,  $\overline{LB}$  or  $\overline{UB}$ .

- 2. Timing depends on which signal is de-asserted first  $\overline{CE}$ ,  $\overline{OE}$ ,  $\overline{LB}$  or  $\overline{UB}$ .

- 3. tbbb delay is required only in cases where the opposite port is completing a write operation to the same address location. For simultaneous read operations BUSY has no relation to valid output data.

- 4. Start of valid data depends on which timing becomes effective last tage, tage, tage or tbdd.

- 5.  $\overline{SEM} = VIH.$

- 6. Refer to Chip Enable Truth Table.

# AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(5)</sup>

|            | 7037L15<br>Com'l Only                          |      |      | 703<br>Com' |      |      |

|------------|------------------------------------------------|------|------|-------------|------|------|

| Symbol     | Parameter                                      | Min. | Max. | Min.        | Max. | Unit |

| READ CYCLE |                                                |      |      |             |      |      |

| trc        | Read Cycle Time                                | 15   | _    | 20          | _    | ns   |

| taa        | Address Access Time                            | _    | 15   | _           | 20   | ns   |

| tace       | Chip Enable Access Time <sup>(4)</sup>         | _    | 15   | _           | 20   | ns   |

| tabe       | Byte Enable Access Time <sup>(4)</sup>         | _    | 15   | _           | 20   | ns   |

| taoe       | Output Enable Access Time                      | _    | 10   | _           | 12   | ns   |

| tон        | Output Hold from Address Change                | 3    | _    | 3           | _    | ns   |

| tLZ        | Output Low-Z Time <sup>(1,2)</sup>             | 3    | _    | 3           | _    | ns   |

| tHZ        | Output High-Z Time <sup>(1,2)</sup>            |      | 10   |             | 10   | ns   |

| tpu        | Chip Enable to Power Up Time (2)               | 0    | _    | 0           | _    | ns   |

| tPD        | Chip Disable to Power Down Time <sup>(2)</sup> | _    | 15   | _           | 20   | ns   |

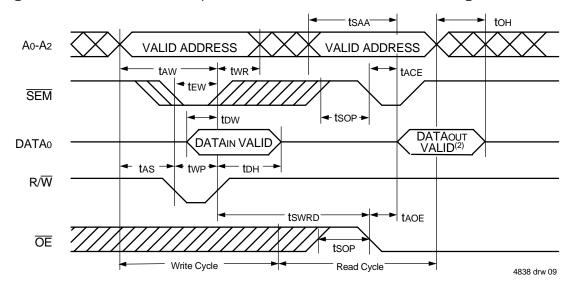

| tsop       | Semaphore Flag Update Pulse (OE or SEM)        | 10   | _    | 10          | _    | ns   |

| tsaa       | Semaphore Address Access Time                  | _    | 15   | _           | 20   | ns   |

4838 tbl 12

# AC Electrical Characteristics Over the Operating Temperature and Supply Voltage<sup>(5)</sup>

|             |                                                    |      | 7L15<br>I Only | 7037L20<br>Com'l Only |      |      |

|-------------|----------------------------------------------------|------|----------------|-----------------------|------|------|

| Symbol      | Parameter                                          | Min. | Max.           | Min.                  | Max. | Unit |

| WRITE CYCLE |                                                    |      |                |                       |      |      |

| twc         | Write Cycle Time                                   | 15   | _              | 20                    | _    | ns   |

| tew         | Chip Enable to End-of-Write <sup>(3)</sup>         | 12   | _              | 15                    | _    | ns   |

| taw         | Address Valid to End-of-Write                      | 12   | _              | 15                    | _    | ns   |

| tas         | Address Set-up Time <sup>(3)</sup>                 | 0    | _              | 0                     | _    | ns   |

| twp         | Write Pulse Width                                  | 12   | _              | 15                    | _    | ns   |

| twr         | Write Recovery Time                                | 0    | _              | 0                     | _    | ns   |

| tow         | Data Valid to End-of-Write                         | 10   | _              | 15                    | _    | ns   |

| tHZ         | Output High-Z Time <sup>(1,2)</sup>                | _    | 10             | _                     | 10   | ns   |

| tон         | Data Hold Time <sup>(4)</sup>                      | 0    | _              | 0                     | _    | ns   |

| twz         | Write Enable to Output in High-Z <sup>(1,2)</sup>  | _    | 10             | _                     | 10   | ns   |

| tow         | Output Active from End-of-Write <sup>(1,2,4)</sup> | 0    | _              | 0                     | _    | ns   |

| tswrd       | SEM Flag Write to Read Time                        | 5    |                | 5                     | _    | ns   |

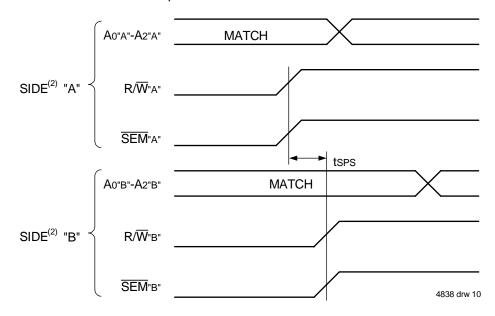

| tsps        | SEM Flag Contention Window                         | 5    |                | 5                     | _    | ns   |

NOTES

- 1. Transition is measured 0mV from Low or High-impedance voltage with Output Test Load (Figure 2).

- 2. This parameter is guaranted by device characterization, but is not production tested.

- 3. To access RAM,  $\overrightarrow{CE}$  = VIL and  $\overrightarrow{SEM}$  = VIH. To access semaphore,  $\overrightarrow{CE}$  = VIH and  $\overrightarrow{SEM}$  = VIL. Either condition must be valid for the entire tew time.

- 4. The specification for toh must be met by the device supplying write data to the RAM under all operating conditions. Although toh and tow values will vary over voltage and temperature, the actual toh will always be smaller than the actual tow.

- 5. Industrial Temperature: for specific speeds, packages and powers contact your sales office.

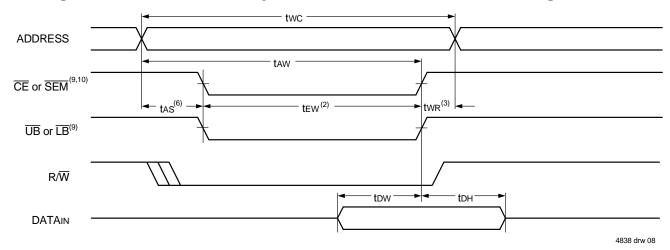

## Timing Waveform of Write Cycle No. 1, R/W Controlled Timing (1,5,8)

## Timing Waveform of Write Cycle No. 2, **CE** Controlled Timing<sup>(1,5)</sup>

- 1.  $R/\overline{W}$  or  $\overline{CE}$  or  $\overline{UB}$  and  $\overline{LB}$  = ViH during all address transitions.

- 2. A write occurs during the overlap (tew or twp) of a  $\overline{CE} = VIL$  and a  $R/\overline{W} = VIL$  for memory array writing cycle.

- 3. twn is measured from the earlier of  $\overline{\text{CE}}$  or  $\overline{\text{R/W}}$  (or  $\overline{\text{SEM}}$  or  $\overline{\text{R/W}}$ ) going HIGH to the end of write cycle.

- 4. During this period, the I/O pins are in the output state and input signals must not be applied.

- 5. If the  $\overline{\text{CE}}$  or  $\overline{\text{SEM}} = \text{VIL}$  transition occurs simultaneously with or after the  $R\overline{\text{W}} = \text{VIL}$  transition, the outputs remain in the High-impedance state.

- 6. Timing depends on which enable signal is asserted last,  $\overline{\text{CE}}$  or  $R/\overline{W}$ .

- 7. This parameter is guaranteed by device characterization, but is not production tested. Transition is measured 0mV from steady state with the Output Test Load (Figure 2).

- 8. If  $\overline{OE} = VIL$  during R/W controlled write cycle, the write pulse width must be the larger of twp or (twz + tow) to allow the I/O drivers to turn off and data to be placed on the bus for the required tow. If  $\overline{OE} = VIH$  during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified twp.

- 9. To access RAM,  $\overline{\text{CE}} = \text{V}_{\text{IL}}$  and  $\overline{\text{SEM}} = \text{V}_{\text{IH}}$ . To access semaphore,  $\overline{\text{CE}} = \text{V}_{\text{IH}}$  and  $\overline{\text{SEM}} = \text{V}_{\text{IL}}$ . Lew must be met for either condition.

- 10. Refer to Chip Enable Truth Table.

### Timing Waveform of Semaphore Read after Write Timing, Either Side(1)

#### NOTES:

- 1.  $\overline{\text{CE}} = \text{ViH}$  or  $\overline{\text{UB}}$  and  $\overline{\text{LB}} = \text{ViH}$  for the duration of the above timing (both write and read cycle) (Refer to Chip Enable Truth Table).

- 2. "DATAOUT VALID" represents all I/O's (I/Oo I/O17) equal to the semaphore value.

## Timing Waveform of Semaphore Write Contention (1,3,4)

- 1. DOR = DOL = VIL,  $\overline{CE}L = \overline{CE}R = VIH$  or both  $\overline{UB}$  and  $\overline{LB} = VIH$  (Refer to Chip Enable Truth Table).

- 2. All timing is the same for left and right ports. Port "A" may be either left or right port. "B" is the opposite from port "A".

- 3. This parameter is measured from R/W\*a" or SEM\*a" going HIGH to R/W\*B" or SEM\*B" going HIGH.

- 4. If tsps is not satisfied, the semaphore will fall positively to one side or the other, but there is no guarantee which side will obtain the flag.

# AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(6)</sup>

|                           |                                                    | 7037L15<br>Com'l Only |      | 7037L20<br>Com'l Only |      |      |  |  |  |

|---------------------------|----------------------------------------------------|-----------------------|------|-----------------------|------|------|--|--|--|

| Symbol                    | Parameter                                          | Min.                  | Max. | Min.                  | Max. | Unit |  |  |  |

| BUSY TIMII                | NG (M/S=ViH)                                       |                       |      |                       |      |      |  |  |  |

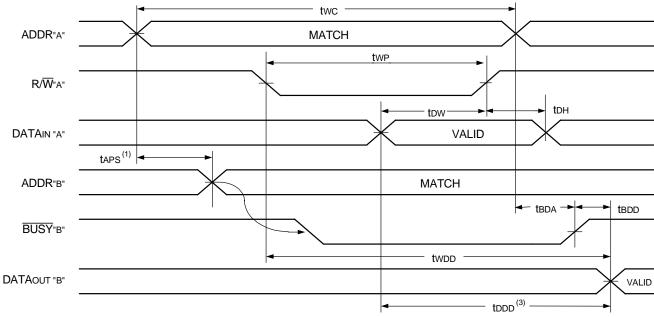

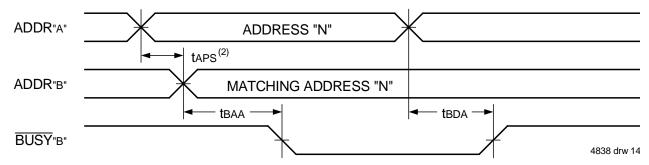

| tbaa                      | BUSY Access Time from Address Match                |                       | 15   |                       | 20   | ns   |  |  |  |

| tbda                      | BUSY Disable Time from Address Not Matched         |                       | 15   | _                     | 20   | ns   |  |  |  |

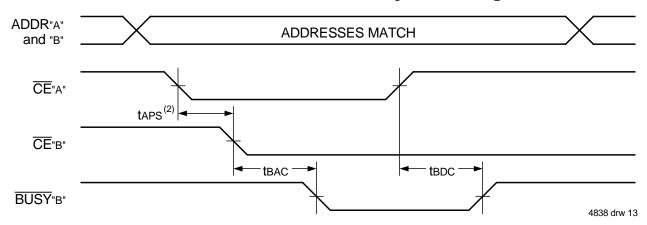

| tBAC                      | BUSY Access Time from Chip Enable Low              |                       | 15   | _                     | 20   | ns   |  |  |  |

| tBDC                      | BUSY Access Time from Chip Enable High             | _                     | 15   | _                     | 17   | ns   |  |  |  |

| taps                      | Arbitration Priority Set-up Time <sup>(2)</sup>    | 5                     | _    | 5                     | _    | ns   |  |  |  |

| tBDD                      | BUSY Disable to Valid Data <sup>(3)</sup>          | _                     | 15   | _                     | 17   | ns   |  |  |  |

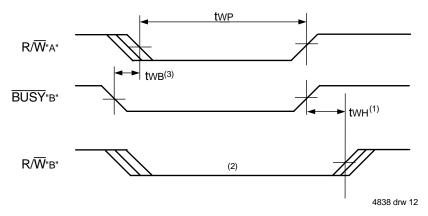

| twn                       | Write Hold After BUSY <sup>(5)</sup>               | 12                    |      | 15                    | _    | ns   |  |  |  |

| BUSY TIMII                | BUSY TIMING (M/S=VIL)                              |                       |      |                       |      |      |  |  |  |

| twB                       | BUSY Input to Write <sup>(4)</sup>                 | 0                     | _    | 0                     | _    | ns   |  |  |  |

| twн                       | Write Hold After BUSY <sup>(5)</sup>               | 12                    | _    | 15                    | _    | ns   |  |  |  |

| PORT-TO-PORT DELAY TIMING |                                                    |                       |      |                       |      |      |  |  |  |

| twdd                      | Write Pulse to Data Delay <sup>(1)</sup>           | _                     | 30   |                       | 45   | ns   |  |  |  |

| todd                      | Write Data Valid to Read Data Delay <sup>(1)</sup> | _                     | 25   | _                     | 30   | ns   |  |  |  |

4838 tbl 14

- 1. Port-to-port delay through RAM cells from writing port to reading port, refer to "Timing Waveform of Write with Port-to-Port Read and BUSY (M/S = VIH)".

- 2. To ensure that the earlier of the two ports wins.

- 3. tbdd is a calculated parameter and is the greater of 0, twdd twp (actual) or tddd tdw (actual).

- 4. To ensure that the write cycle is inhibited on port "B" during contention on port "A".

- 5. To ensure that a write cycle is completed on port "B" after contention on port "A".

- 6. Industrial Temperature: for specific speeds, packages and powers contact your sales office.

4838 drw 11

## Timing Waveform of Write with Port-to-Port Read and $\overline{\textbf{BUSY}}$ (M/ $\overline{\textbf{S}}$ = VIH) $^{(2,4,5)}$

#### NOTES

- 1. To ensure that the earlier of the two ports wins. taps is ignored for  $M/\overline{S} = VIL$  (SLAVE).

- 2.  $\overline{CE}_L = \overline{CE}_R = V_{IL}$ , refer to Chip Enable Truth Table.

- 3.  $\overline{OE} = V_{IL}$  for the reading port.

- 4. If M/S = VIL (SLAVE), BUSY is an input. Then for this example BUSY "A" = VIH and BUSY "B" input is shown above.

- 5. All timing is the same for left and right ports. Port "A" may be either the left or right port. Port "B" is the port opposite from port "A".

### Timing Waveform of Write with **BUSY** (M/**S** = VIL)

- 1. twn must be met for both  $\overline{BUSY}$  input (SLAVE) and output (MASTER).

- 2. BUSY is asserted on port "B" blocking R/W"B", until BUSY"B" goes HIGH.

- 3. twb is only for the 'Slave' version.

Waveform of **BUSY** Arbitration Controlled by **CE** Timing (M/**S** = VIH)<sup>(1,3)</sup>

Waveform of  $\overline{\textbf{BUSY}}$  Arbitration Cycle Controlled by Address Match Timing (M/ $\overline{\textbf{S}}$  = VIH)<sup>(1)</sup>

#### NOTES:

- 1. All timing is the same for left and right ports. Port "A" may be either the left or right port. Port "B" is the port opposite from port "A".

- 2. If taps is not satisfied, the BUSY signal will be asserted on one side or another but there is no guarantee on which side BUSY will be asserted.

- 3. Refer to Chip Enable Truth Table.

# AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(1)</sup>

|           |                      | 7037L15<br>Com'l Only |      | 7037L20<br>Com'l Only |      |      |

|-----------|----------------------|-----------------------|------|-----------------------|------|------|

| Symbol    | Parameter            | Min.                  | Max. | Min.                  | Max. | Unit |

| INTERRUPT | TIMING               |                       |      |                       |      |      |

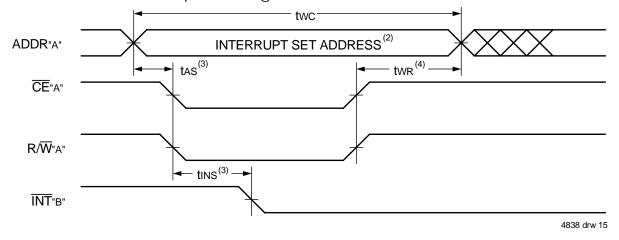

| tas       | Address Set-up Time  | 0                     | _    | 0                     | _    | ns   |

| twr       | Write Recovery Time  | 0                     | _    | 0                     | _    | ns   |

| tins      | Interrupt Set Time   | _                     | 15   |                       | 20   | ns   |

| tinr      | Interrupt Reset Time | _                     | 15   | _                     | 20   | ns   |

NOTES:

1. Industrial Temperature: for specific speeds, packages and powers contact your sales office.

### Waveform of Interrupt Timing(1,5)

tRC INTERRUPT CLEAR ADDRESS (2) ADDR"B" tas<sup>(3)</sup> CE"B" ŌE"B" tinr (3) -ĪNT<sub>"B"</sub> 4838 drw 16

- 1. All timing is the same for left and right ports. Port "A" may be either the left or right port. Port "B" is the port opposite from port "A".

- 2. See Interrupt Truth Table.

- 3. Timing depends on which enable signal ( $\overline{\text{CE}}$  or  $R/\overline{W}$ ) is asserted last.

- 4. Timing depends on which enable signal (CE or R/W) is de-asserted first.

- 5. Refer to Chip Enable Truth Table.

## Truth Table IV — Interrupt Flag<sup>(1,4,5)</sup>

| Left Port |     |             |          |                  | Right Port |     |             |          |                  |                       |

|-----------|-----|-------------|----------|------------------|------------|-----|-------------|----------|------------------|-----------------------|

| R/₩L      | CEL | <u>ŌĒ</u> L | A14L-A0L | ĪNT∟             | R/W̄R      | CER | <b>ŌĒ</b> R | A14R-A0R | Ī <b>NT</b> R    | Function              |

| L         | L   | Х           | 7FFF     | Х                | Х          | Х   | Х           | Х        | L <sup>(2)</sup> | Set Right INTR Flag   |

| X         | Х   | Х           | Х        | Х                | Х          | L   | L           | 7FFF     | H <sup>(3)</sup> | Reset Right INTR Flag |

| X         | Х   | Х           | Х        | L <sup>(3)</sup> | L          | L   | Х           | 7FFE     | Х                | Set Left INTL Flag    |

| Х         | L   | L           | 7FFE     | H <sup>(2)</sup> | Х          | Х   | Х           | X        | Х                | Reset Left INTL Flag  |

NOTES:

- 1. Assumes  $\overline{BUSY}_L = \overline{BUSY}_R = V_{IH}$ .

- 2. If  $\overline{BUSY}L = VIL$ , then no change.

- 3. If  $\overline{BUSY}R = VIL$ , then no change.

- 4. INTL and INTR must be initialized at power-up.

- 5. Refer to Chip Enable Truth Table.

## Truth Table V —Address **BUSY** Arbitration<sup>(4)</sup>

| Inputs |             |                      | Out      |                       |                                 |

|--------|-------------|----------------------|----------|-----------------------|---------------------------------|

| CEL    | <b>ՇĒ</b> r | Aol-A14l<br>Aor-A14r | BUSYL(1) | BUSY <sub>R</sub> (1) | Function                        |

| Х      | Χ           | NO MATCH             | Н        | Н                     | Normal                          |

| Н      | Χ           | MATCH                | Н        | Н                     | Normal                          |

| Х      | Н           | MATCH                | Н        | Н                     | Normal                          |

| L      | L           | MATCH                | (2)      | (2)                   | Write<br>Inhibit <sup>(3)</sup> |

NOTES:

4838 tbl 17

- 1. Pins  $\overline{\text{BUSY}}_{\text{L}}$  and  $\overline{\text{BUSY}}_{\text{R}}$  are both outputs when the part is configured as a master. Both are inputs when configured as a slave.  $\overline{\text{BUSY}}$  outputs on the IDT7037 are push-pull, not open drain outputs. On slaves the  $\overline{\text{BUSY}}$  input internally inhibits writes.

- 2. "L" if the inputs to the opposite port were stable prior to the address and enable inputs of this port. "H" if the inputs to the opposite port became stable after the address and enable inputs of this port. If taps is not met, either BUSYL or BUSYR = LOW will result. BUSYL and BUSYR outputs can not be LOW simultaneously.

- 3. Writes to the left port are internally ignored when BUSYL outputs are driving LOW regardless of actual logic level on the pin. Writes to the right port are internally ignored when BUSYR outputs are driving LOW regardless of actual logic level on the pin.

- 4. Refer to Chip Enable Truth Table.

### Truth Table VI — Example of Semaphore Procurement Sequence (1,2,3)

| Functions                          | Do - D17 Left | Do - D17 Right | Status                                                 |

|------------------------------------|---------------|----------------|--------------------------------------------------------|

| No Action                          | 1             | 1              | Semaphore free                                         |

| Left Port Writes "0" to Semaphore  | 0             | 1              | Left port has semaphore token                          |

| Right Port Writes "0" to Semaphore | 0             | 1              | No change. Right side has no write access to semaphore |

| Left Port Writes "1" to Semaphore  | 1             | 0              | Right port obtains semaphore token                     |

| Left Port Writes "0" to Semaphore  | 1             | 0              | No change. Left port has no write access to semaphore  |

| Right Port Writes "1" to Semaphore | 0             | 1              | Left port obtains semaphore token                      |

| Left Port Writes "1" to Semaphore  | 1             | 1              | Semaphore free                                         |

| Right Port Writes "0" to Semaphore | 1             | 0              | Right port has semaphore token                         |

| Right Port Writes "1" to Semaphore | 1             | 1              | Semaphore free                                         |

| Left Port Writes "0" to Semaphore  | 0             | 1              | Left port has semaphore token                          |

| Left Port Writes "1" to Semaphore  | 1             | 1              | Semaphore free                                         |

NOTES: 4833 tol 18

- 1. This table denotes a sequence of events for only one of the eight semaphores on the IDT7037.

- 2. There are eight semaphore flags written to via I/Oo and read from all I/O's (I/Oo-I/O17). These eight semaphores are addressed by Ao-A2.

- 3.  $\overline{CE} = V_{IH}$ ,  $\overline{SEM} = V_{IL}$  to access the semaphores. Refer to the Semaphore Read/Write Control Truth Table.

### Functional Description

The IDT7037 provides two ports with separate control, address and I/O pins that permit independent access for reads or writes to any location in memory. The IDT7037 has an automatic power down feature controlled by  $\overline{\text{CE}}$ . The  $\overline{\text{CE}}$ 0 and  $\overline{\text{CE}}$ 1 control the on-chip power down circuitry that permits the respective port to go into a standby mode when not selected  $\overline{\text{CE}}$  = HIGH). When a port is enabled, access to the entire memory array is permitted.

### Interrupts

If the user chooses the interrupt function, a memory location (mail box or message center) is assigned to each port. The left port interrupt flag

$(\overline{\text{INTL}})$  is asserted when the right port writes to memory location 7FFE (HEX), where a write is defined as  $\overline{\text{CE}}_R = R/\overline{W}_R = \text{VIL}$  per Truth Table IV. The left port clears the interrupt through access of address location 7FFE when  $\overline{\text{CE}}_L = \overline{\text{OE}}_L = \text{VIL}$ ,  $R/\overline{W}$  is a "don't care". Likewise, the right port interrupt flag ( $\overline{\text{INTR}}$ ) is asserted when the left port writes to memory location 7FFF (HEX) and to clear the interrupt flag ( $\overline{\text{INTR}}$ ), the right port must read the memory location 7FFF. The message (18 bits) at 7FFE or 7FFF is user-defined since it is an addressable SRAM location. If the interrupt function is not used, address locations 7FFE and 7FFF are not used as mail boxes, but as part of the random access memory. Refer to Table IV for the interrupt operation.

### **Busy Logic**

Busy Logic provides a hardware indication that both ports of the RAM have accessed the same location at the same time. It also allows one of the two accesses to proceed and signals the other side that the RAM is "busy". The  $\overline{\text{BUSY}}$  pin can then be used to stall the access until the operation on the other side is completed. If a write operation has been attempted from the side that receives a  $\overline{\text{BUSY}}$  indication, the write signal is gated internally to prevent the write from proceeding.

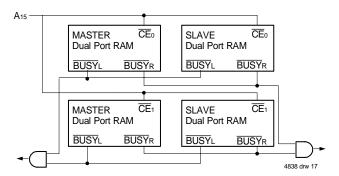

The use of BUSY logic is not required or desirable for all applications. In some cases it may be useful to logically OR the BUSY outputs together and use any BUSY indication as an interrupt source to flag the event of an illegal or illogical operation. If the write inhibit function of BUSY logic is not desirable, the BUSY logic can be disabled by placing the part in slave mode with the  $M/\overline{S}$  pin. Once in slave mode the BUSY pin operates solely as a write inhibit input pin. Normal operation can be programmed by tying the  $\overline{B}\overline{U}\overline{S}\overline{Y}$  pins HIGH. If desired, unintended write operations can be prevented to a port by tying the  $\overline{B}\overline{U}\overline{S}\overline{Y}$  pin for that port LOW.

The BUSY outputs on the IDT7037 RAM in master mode, are pushpull type outputs and do not require pull up resistors to operate. If these RAMs are being expanded in depth, then the BUSY indication for the resulting array requires the use of an external AND gate.

Figure 3. Busy and chip enable routing for both width and depth expansion with IDT7037 RAMs.

# Width Expansion Busy Logic Master/Slave Arrays

When expanding an IDT7037 RAM array in width while using  $\overline{B}USY$  logic, one master part is used to decide which side of the RAMs array will receive a  $\overline{B}USY$  indication, and to output that indication. Any number of slaves to be addressed in the same address range as the master, use the  $\overline{B}USY$  signal as a write inhibit signal. Thus on the IDT7037 RAM the  $\overline{B}USY$  pin is an output if the part is used as a master (M/ $\overline{S}$  pin = VIL), and the  $\overline{B}USY$  pin is an input if the part used as a slave (M/ $\overline{S}$  pin = VIL) as shown in Figure 3.

If two or more master parts were used when expanding in width, a split decision could result with one master indicating  $\overline{BUSY}$  on one side of the array and another master indicating  $\overline{BUSY}$  on one other side of the array. This would inhibit the write operations from one port for part of a word and inhibit the write operations from the other port for the other part of the word.

The BUSY arbitration, on a master, is based on the chip enable and address signals only. It ignores whether an access is a read or write. In a master/slave array, both address and chip enable must be valid long enough for a BUSY flag to be output from the master before the actual write pulse can be initiated with the RiW signal. Failure to observe this timing can

result in a glitched internal write inhibit signal and corrupted data in the slave.

### Semaphores

The IDT7037 is an extremely fast Dual-Port  $32K \times 18$  CMOS Static RAM with an additional 8 address locations dedicated to binary semaphore flags. These flags allow either processor on the left or right side of the Dual-Port RAM to claim a privilege over the other processor for functions defined by the system designer's software. As an example, the semaphore can be used by one processor to inhibit the other from accessing a portion of the Dual-Port RAM or any other shared resource.

The Dual-Port RAM features a fast access time, and both ports are completely independent of each other. This means that the activity on the left port in no way slows the access time of the right port. Both ports are identical infunction to standard CMOS Static RAM and can be read from, or written to, at the same time with the only possible conflict arising from the simultaneous writing of, or a simultaneous READ/WRITE of, a non-semaphore location. Semaphores are protected against such ambiguous situations and may be used by the system program to avoid any conflicts in the non-semaphore portion of the Dual-Port RAM. These devices have an automatic power-down feature controlled by  $\overline{\text{CE}}$ , the Dual-Port RAM enable, and  $\overline{\text{SEM}}$ , the semaphore enable. The  $\overline{\text{CE}}$  and  $\overline{\text{SEM}}$  pins control on-chip power down circuitry that permits the respective port to go into standby mode when not selected. This is the condition which is shown in Truth Table II where  $\overline{\text{CE}}$  and  $\overline{\text{SEM}}$  are both HIGH.

Systems which can best use the IDT7037 contain multiple processors or controllers and are typically very high-speed systems which are software controlled or software intensive. These systems can benefit from a performance increase offered by the IDT7037s hardware semaphores, which provide a lockout mechanism without requiring complex programming.

Software handshaking between processors offers the maximum in system flexibility by permitting shared resources to be allocated invarying configurations. The IDT7037 does not use its semaphore flags to control any resources through hardware, thus allowing the system designer total flexibility in system architecture.

An advantage of using semaphores rather than the more common methods of hardware arbitration is that wait states are never incurred in either processor. This can prove to be a major advantage in very high-speed systems.

### How the Semaphore Flags Work

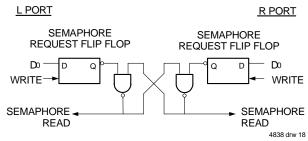

The semaphore logic is a set of eight latches which are independent of the Dual-Port RAM. These latches can be used to pass a flag, or token, from one port to the other to indicate that a shared resource is in use. The semaphores provide a hardware assist for a use assignment method called "Token Passing Allocation." In this method, the state of a semaphore latch is used as a token indicating that shared resource is in use. If the left processor wants to use this resource, it requests the token by setting the latch. This processor then verifies its success in setting the latch by reading it. If it was successful, it proceeds to assume control over the shared resource. If it was not successful in setting the latch, it determines that the right side processor has set the latch first, has the token and is using the shared resource. The left processor can then either repeatedly request that semaphore's status or remove its request for that semaphore to perform another task and occasionally attempt again to gain control of the token via

the set and test sequence. Once the right side has relinquished the token, the left side should succeed in gaining control.

The semaphore flags are active LOW. A token is requested by writing a zero into a semaphore latch and is released when the same side writes a one to that latch.

The eight semaphore flags reside within the IDT7037 in a separate memory space from the Dual-Port RAM. This address space is accessed by placing a LOW input on the  $\overline{\text{SEM}}$  pin (which acts as a chip select for the semaphore flags) and using the other control pins (Address,  $\overline{\text{CE}}$ , and R/ $\overline{\text{W}}$ ) as they would be used in accessing a standard Static RAM. Each of the flags has a unique address which can be accessed by either side through address pins A0 – A2. When accessing the semaphores, none of the other address pins has any effect.

When writing to a semaphore, only data pin Do is used. If a LOW level is written into an unused semaphore location, that flag will be set to a zero on that side and a one on the other side (see Table VI). That semaphore can now only be modified by the side showing the zero. When a one is written into the same location from the same side, the flag will be set to a one for both sides (unless a semaphore request from the other side is pending) and then can be written to by both sides. The fact that the side which is able to write a zero into a semaphore subsequently locks out writes from the other side is what makes semaphore flags useful in interprocessor communications. (A thorough discussion on the use of this feature follows shortly.) A zero written into the same location from the other side will be stored in the semaphore request latch for that side until the semaphore is freed by the first side.

When a semaphore flag is read, its value is spread into all data bits so that a flag that is a one reads as a one in all data bits and a flag containing a zero reads as all zeros. The read value is latched into one side's output register when that side's semaphore select ( $\overline{SEM}$ ) and output enable ( $\overline{OE}$ ) signals go active. This serves to disallow the semaphore from changing state in the middle of a read cycle due to a write cycle from the other side. Because of this latch, a repeated read of a semaphore in a test loop must cause either signal ( $\overline{SEM}$  or  $\overline{OE}$ ) to go inactive or the output will never change.

A sequence WRITE/READ must be used by the semaphore in order to guarantee that no system level contention will occur. A processor requests access to shared resources by attempting to write a zero into a semaphore location. If the semaphore is already in use, the semaphore request latch will contain a zero, yet the semaphore flag will appear as one, a fact which the processor will verify by the subsequent read (see Table VI). As an example, assume a processor writes a zero to the left port at a free semaphore location. On a subsequent read, the processor will verify that it has written successfully to that location and will assume control over the resource in question. Meanwhile, if a processor on the right side attempts to write a zero to the same semaphore flag it will fail, as will be verified by the fact that a one will be read from that semaphore on the right

side during subsequent read. Had a sequence of READ/WRITE been used instead, system contention problems could have occurred during the gap between the read and write cycles.

It is important to note that a failed semaphore request must be followed by either repeated reads or by writing a one into the same location. The reason for this is easily understood by looking at the simple logic diagram of the semaphore flag in Figure 4. Two semaphore request latches feed into a semaphore flag. Whichever latch is first to present a zero to the semaphore flag will force its side of the semaphore flag LOW and the other side HIGH. This condition will continue until a one is written to the same semaphore request latch. Should the other side's semaphore request latch have been written to a zero in the meantime, the semaphore flag will flip

Figure 4. IDT7037 Semaphore Logic

over to the other side as soon as a one is written into the first side's request latch. The second side's flag will now stay LOW until its semaphore request latch is written to a one. From this it is easy to understand that, if a semaphore is requested and the processor which requested it no longer needs the resource, the entire system can hang up until a one is written into that semaphore request latch.

The critical case of semaphore timing is when both sides request a single token by attempting to write a zero into it at the same time. The semaphore logic is specially designed to resolve this problem. If simultaneous requests are made, the logic guarantees that only one side receives the token. If one side is earlier than the other in making the request, the first side to make the request will receive the token. If both requests arrive at the same time, the assignment will be arbitrarily made to one port or the other.

One caution that should be noted when using semaphores is that semaphores alone do not guarantee that access to a resource is secure. As with any powerful programming technique, if semaphores are misused or misinterpreted, a software error can easily happen.

Initialization of the semaphores is not automatic and must be handled via the initialization program at power-up. Since any semaphore request flag which contains a zero must be reset to a one, all semaphores on both sides should have a one written into them at initialization from both sides to assure that they will be free when needed.

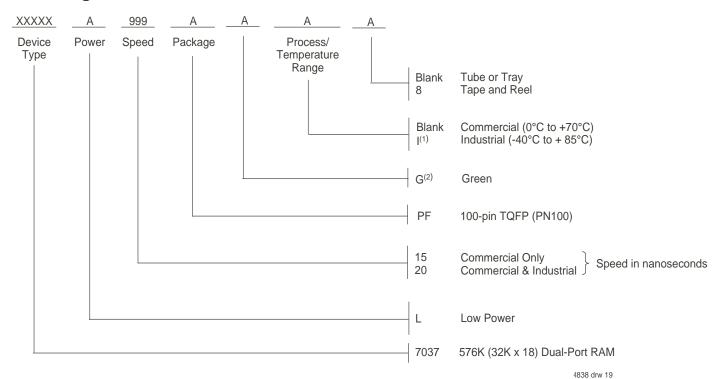

### Ordering Information

- 1. Contact your local sales office for industrial temp range for other speeds, packages and powers.

- 2. Green parts available. For specific speeds, packages and powers contact your local sales office. LEAD FINISH (SnPb) parts are in EOL process. Product Discontinuation Notice - PDN# SP-17-02

### Datasheet Document History

09/30/99: Initial Public Release 11/10/99:

Replaced IDT logo

Page 2 Fixed pin 19, to GND

05/23/00: Page 3 Increased storage temperature parameter

Clarified TA parameter

Page 5 DC Electrical parameters—changed wording from "open" to "disabled"

Page 14 Added IV to Truth Table in "Interrupts" paragraph Page 15 Changed part number 7008 to 7037 in third paragraph

Changed ±200mV to 0mV in notes Removed Preliminary status

01/29/09: Page 17 Removed "IDT" from orderable part number Page 1 Added Green availability to Features 06/09/15:

Page 2 Removed IDT in reference to fabrication

Page 2 & 17 The package code for PN100-1 changed to PN100 to match the standard package codes Page 17 Added Green and T&R indicators and the correlating footnotes to Ordering Information

Product Discontinuation Notice - PDN# SP-17-02 06/07/18:

Last time buy expires June 15, 2018

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.