## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

## 3851 Group (Built-in 16 KB ROM)

\*This data sheet explains the products which have 16 KB ROM.

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### **DESCRIPTION**

The 3851 group is the 8-bit microcomputer based on the 740 family core technology.

The 3851 group is designed for the household products and office automation equipment and includes serial I/O functions, 8-bit timer, A-D converter, and I<sup>2</sup>C-bus interface.

### **FEATURES**

| FEATURES                                                             |

|----------------------------------------------------------------------|

| ●Basic machine-language instructions                                 |

| $ullet$ Minimum instruction execution time 0.5 $\mu s$               |

| (at 8 MHz oscillation frequency)                                     |

|                                                                      |

| ROM16 Kbytes                                                         |

| RAM 512 bytes                                                        |

| ● Programmable input/output ports                                    |

| ●Interrupts                                                          |

| ●Timers                                                              |

| ● Serial I/O 8-bit X 1(UART or Clock-synchronized)                   |

| ●Multi-master I <sup>2</sup> C-bus interface (option) 1 channel      |

| ●PWM                                                                 |

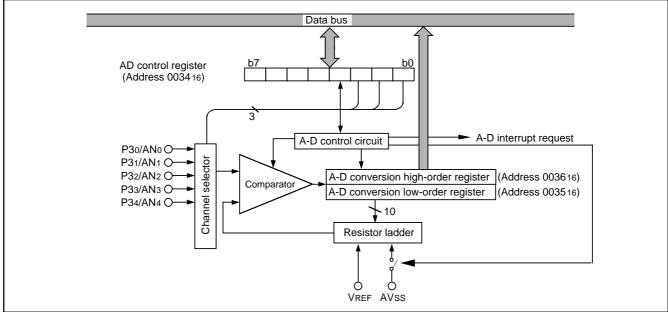

| ●A-D converter 10-bit X 5 channels                                   |

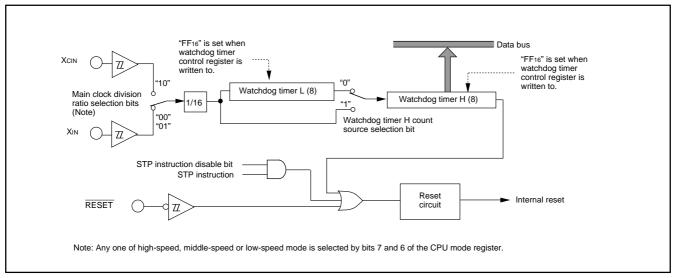

| ●Watchdog timer16-bit X 1                                            |

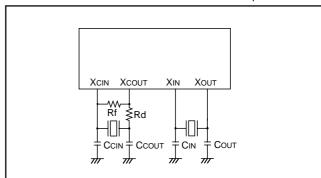

| ●Clock generating circuit Built-in 2 circuits                        |

| (connect to external ceramic resonator or quartz-crystal oscillator) |

| ◆Power source voltage                                          |

|----------------------------------------------------------------|

| In high-speed mode                                             |

| (at 8 MHz oscillation frequency)                               |

| In high-speed mode                                             |

| (at 4 MHz oscillation frequency)                               |

| In middle-speed mode                                           |

| (at 8 MHz oscillation frequency)                               |

| In low-speed mode                                              |

| (at 32 kHz oscillation frequency)                              |

| ◆Power dissipation                                             |

| In high-speed mode34 mW                                        |

| (at 8 MHz oscillation frequency, at 5 V power source voltage)  |

| In low-speed mode 60 $\mu W$                                   |

| (at 32 kHz oscillation frequency, at 3 V power source voltage) |

| ●Operating temperature range —20 to 85°C                       |

### **APPLICATION**

Office automation equipment, FA equipment, Household products, Consumer electronics, etc.

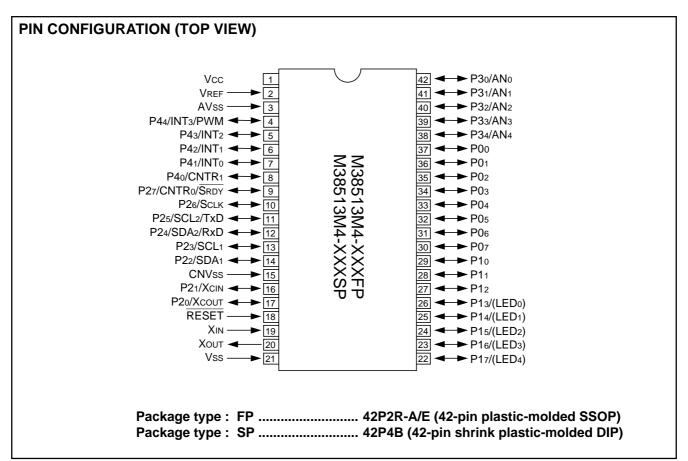

Fig. 1 M38513M4-XXXFP/SP pin configuration

## **FUNCTIONAL BLOCK**

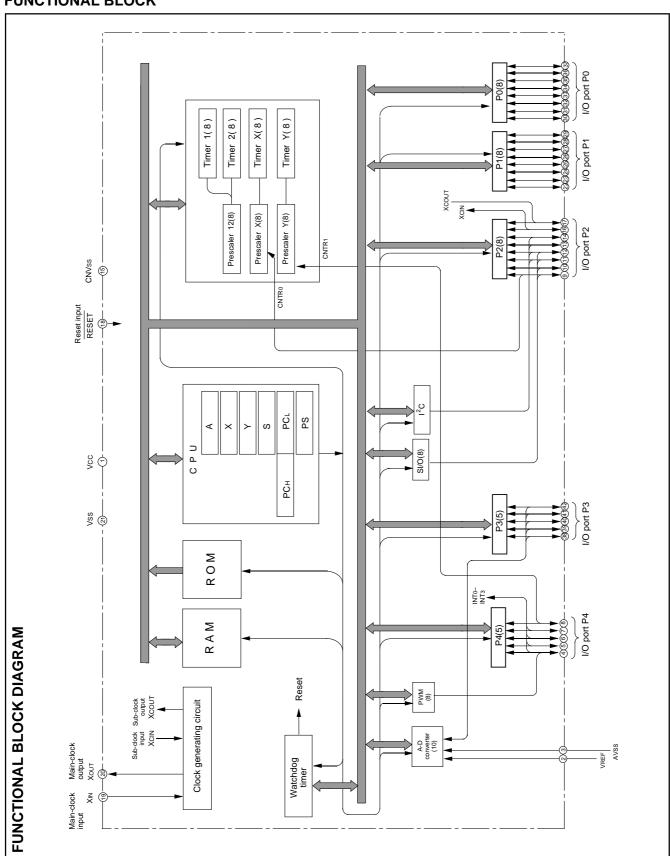

Fig. 2 Functional block diagram

## **PIN DESCRIPTION**

### Table 1 Pin description

| Pin                     | Name                    | Functions                                                                                | Function except a port function              |  |  |  |  |

|-------------------------|-------------------------|------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|

| Vcc, Vss                | Power source            | •Apply voltage of 2.7 V – 5.5 V to Vcc, and 0 V to Vss.                                  | runction except a port function              |  |  |  |  |

| CNVss                   | CNVss input             | 117                                                                                      |                                              |  |  |  |  |

| CINVSS                  | CIAV 55 Input           | •This pin controls the operation mode of the chip.                                       |                                              |  |  |  |  |

| \/p==                   | Deference               | •Normally connected to Vss.                                                              |                                              |  |  |  |  |

| VREF                    | Reference voltage input | Reference voltage input pin for A-D converter.                                           |                                              |  |  |  |  |

| AVss                    | Analog power            | •Analog power source input pin for A-D converter.                                        |                                              |  |  |  |  |

|                         | source input            | •Connect to Vss.                                                                         |                                              |  |  |  |  |

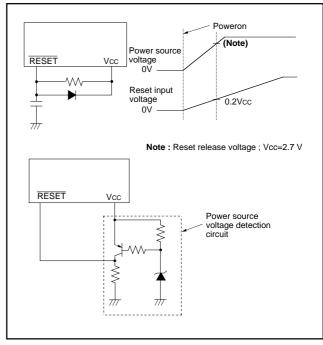

| RESET                   | Reset input             | •Reset input pin for active "L."                                                         |                                              |  |  |  |  |

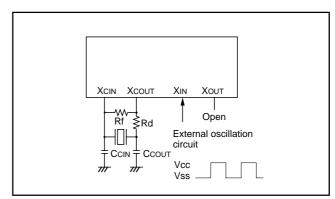

| XIN                     | Clock input             | •Input and output pins for the clock generating circuit.                                 |                                              |  |  |  |  |

|                         |                         | •Connect a ceramic resonator or quartz-crystal oscillator                                | between the XIN and XOUT pins to se          |  |  |  |  |

| Xout                    | Clock output            | the oscillation frequency.                                                               |                                              |  |  |  |  |

|                         |                         | <ul> <li>When an external clock is used, connect the clock sour<br/>pin open.</li> </ul> | rce to the XIN pin and leave the XOU         |  |  |  |  |

| P00-P07                 | I/O port P0             | •8-bit CMOS I/O port.                                                                    |                                              |  |  |  |  |

|                         |                         | •I/O direction register allows each pin to be individually pi                            | rogrammed as either input or output.         |  |  |  |  |

|                         |                         | •CMOS compatible input level.                                                            |                                              |  |  |  |  |

| P10-P17                 | I/O port P1             | •CMOS 3-state output structure.                                                          |                                              |  |  |  |  |

|                         |                         | •P13 to P17 (5 bits) are enabled to output large current for LED drive.                  |                                              |  |  |  |  |

| P20/XCOUT               | I/O port P2             | •8-bit CMOS I/O port.                                                                    | Sub-clock generating circuit I/O             |  |  |  |  |

| P21/XCIN                | "0 port 2               | •I/O direction register allows each pin to be individually                               | pins (connect a resonator)                   |  |  |  |  |

| P22/SDA1                | -                       | programmed as either input or output.                                                    | I <sup>2</sup> C-BUS interface function pins |  |  |  |  |

| P23/SCL1                |                         | •CMOS compatible input level.                                                            | ·                                            |  |  |  |  |

| P24/SDA2/RxD            | †                       | •P22 to P25 can be switched between CMOS compat-                                         | I <sup>2</sup> C-BUS interface function pin/ |  |  |  |  |

| P25/SCL2/TxD            |                         | ible input level or SMBUS input level in the I <sup>2</sup> C-BUS interface function.    | Serial I/O function pins                     |  |  |  |  |

| P26/SCLK                | 7                       | •P20, P21, P24 to P27: CMOS3-state output structure.                                     | Serial I/O function pin                      |  |  |  |  |

| P27/CNTR <sub>0</sub> / | +                       | •P24, P25: N-channel open-drain structure in the I <sup>2</sup> C-                       | Serial I/O function pin/                     |  |  |  |  |

| SRDY                    |                         | BUS interface function.                                                                  | Timer X function pin                         |  |  |  |  |

|                         |                         | •P22, P23: N-channel open-drain structure.                                               |                                              |  |  |  |  |

| P30/AN0-                | I/O port P3             | •8-bit CMOS I/O port with the same function as port P0.                                  | A-D converter input pin                      |  |  |  |  |

| P34/AN4                 | "O port i o             | •CMOS compatible input level.                                                            | , and the second                             |  |  |  |  |

| 1 34/7(1)4              |                         | CMOS 3-state output structure.                                                           |                                              |  |  |  |  |

| P40/CNTR1               | I/O port P4             | •8-bit CMOS I/O port with the same function as port P0.                                  | Timer Y function pin                         |  |  |  |  |

| P41/INT0-               | "O poit i 4             | •CMOS compatible input level.                                                            | Interrupt input pins                         |  |  |  |  |

| P41/INT0=<br>P43/INT2   |                         | CMOS 3-state output structure.                                                           |                                              |  |  |  |  |

|                         | +                       | -OMOO 3-state output structure.                                                          | Interrupt input pin                          |  |  |  |  |

| P44/INT3/PWM            |                         |                                                                                          |                                              |  |  |  |  |

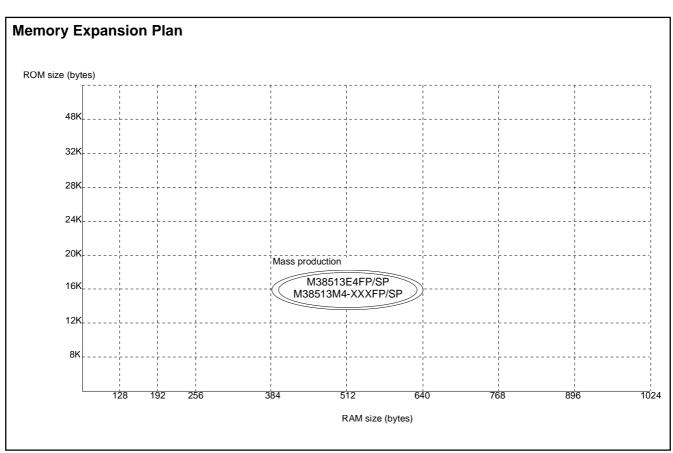

### **GROUP EXPANSION**

Mitsubishi plans to expand the 3851 group as follows:

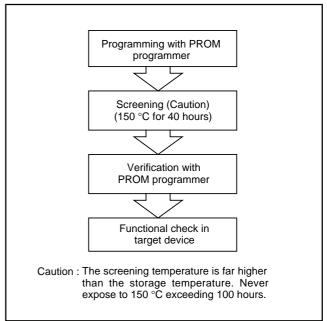

## **Memory Type**

Support for mask ROM and One Time PROM versions.

## **Memory Size**

| ROM/PROM size | 16 K bytes  |

|---------------|-------------|

| RAM size      | . 512 bytes |

## **Packages**

Fig. 3 Memory expansion plan

## FUNCTIONAL DESCRIPTION CENTRAL PROCESSING UNIT (CPU)

The 3851 group uses the standard 740 Family instruction set. Refer to the table of 740 Family addressing modes and machine instructions or the 740 Family Software Manual for details on the instruction set.

Machine-resident 740 Family instructions are as follows:

The FST and SLW instructions cannot be used.

The STP, WIT, MUL, and DIV instructions can be used.

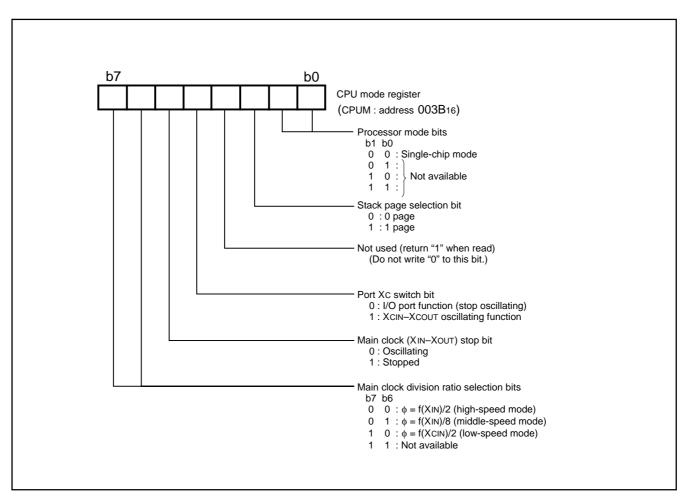

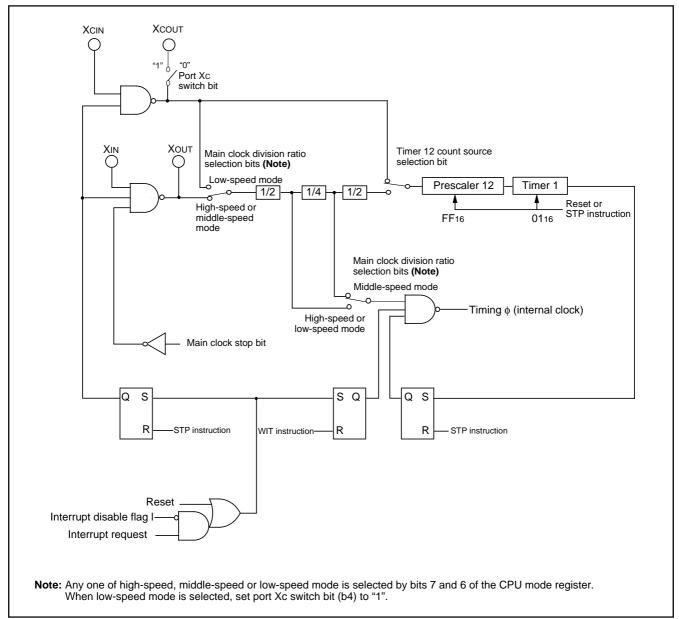

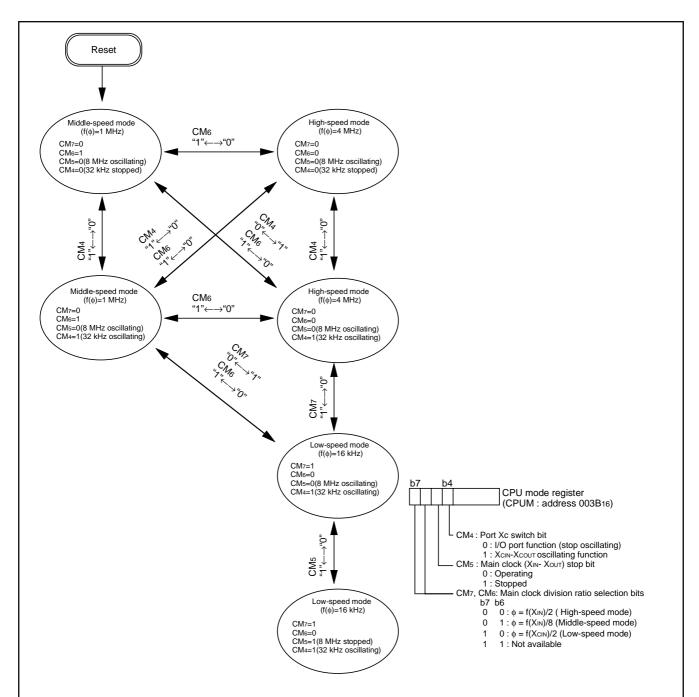

## [CPU Mode Register (CPUM)] 003B16

The CPU mode register contains the stack page selection bit, etc.

The CPU mode register is allocated at address 003B16.

Fig. 4 Structure of CPU mode register

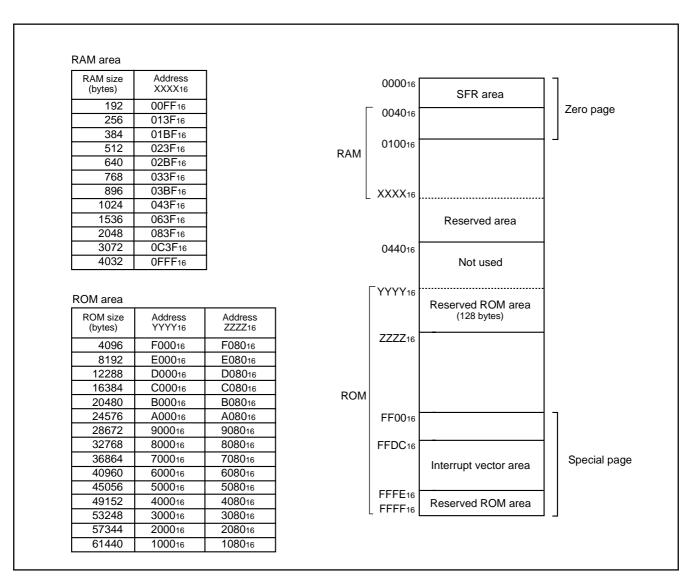

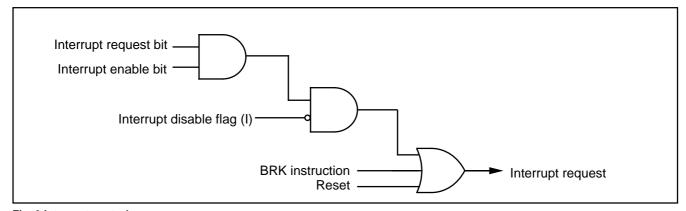

## MEMORY Special Function Register (SFR) Area

The Special Function Register area in the zero page contains control registers such as I/O ports and timers.

#### **RAM**

RAM is used for data storage and for stack area of subroutine calls and interrupts.

#### **ROM**

The first 128 bytes and the last 2 bytes of ROM are reserved for device testing and the rest is user area for storing programs.

#### **Interrupt Vector Area**

The interrupt vector area contains reset and interrupt vectors.

## **Zero Page**

Access to this area with only 2 bytes is possible in the zero page addressing mode.

## **Special Page**

Access to this area with only 2 bytes is possible in the special page addressing mode.

Fig. 5 Memory map diagram

## 3851 Group (Built-in 16 KB ROM)

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

| 00016              | Port P0 (P0)                             | 002016             | Prescaler 12 (PRE12)                                         |

|--------------------|------------------------------------------|--------------------|--------------------------------------------------------------|

| 00116              | Port P0 direction register (P0D)         | 002116             | Timer 1 (T1)                                                 |

| 000216             | Port P1 (P1)                             | 002216             | Timer 2 (T2)                                                 |

| 000316             | Port P1 direction register (P1D)         | 002316             | Timer XY mode register (TM)                                  |

| 000416             | Port P2 (P2)                             | 002416             | Prescaler X (PREX)                                           |

| 000516             | Port P2 direction register (P2D)         | 002516             | Timer X (TX)                                                 |

| 000616             | Port P3 (P3)                             | 002616             | Prescaler Y (PREY)                                           |

| 000716             | Port P3 direction register (P3D)         | 002716             | Timer Y (TY)                                                 |

| 000816             | Port P4 (P4)                             | 002816             | Timer count source selection register (TCSS)                 |

| 000916             | Port P4 direction register (P4D)         | 002916             |                                                              |

| 000A16             |                                          | 002A <sub>16</sub> |                                                              |

| 000B16             |                                          | 002B <sub>16</sub> | I <sup>2</sup> C data shift register (S0)                    |

| 000C16             |                                          | 002C <sub>16</sub> | I <sup>2</sup> C address register (S0D)                      |

| 000D16             |                                          | 002D16             | I <sup>2</sup> C status register (S1)                        |

| 000E16             |                                          | 002E16             | I <sup>2</sup> C control register (S1D)                      |

| 000F16             |                                          | 002F16             | I <sup>2</sup> C clock control register (S2)                 |

| 001016             |                                          | 003016             | I <sup>2</sup> C start/stop condition control register (S2D) |

| 001116             |                                          | 003116             | Reserved *                                                   |

| 001216             |                                          | 003216             |                                                              |

| 001316             |                                          | 003316             |                                                              |

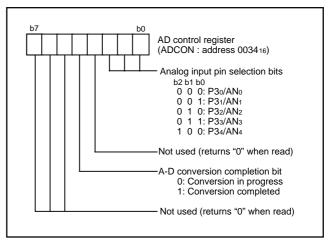

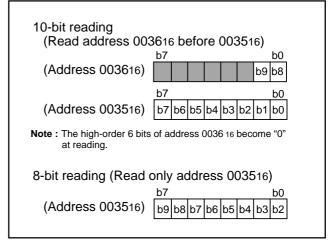

| 001416             |                                          | 003416             | A-D control register (ADCON)                                 |

| 001516             | Reserved *                               | 003516             | A-D conversion low-order register (ADL)                      |

| 001616             | Reserved *                               | 003616             | A-D conversion high-order register (ADH)                     |

| 001716             | Reserved *                               | 003716             |                                                              |

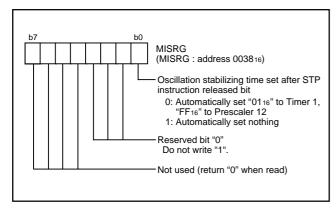

| 001816             | Transmit/Receive buffer register (TB/RB) | 003816             | MISRG                                                        |

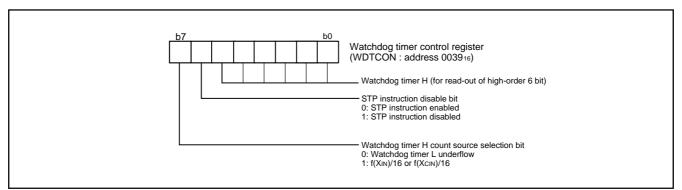

| 001916             | Serial I/O status register (SIOSTS)      | 003916             | Watchdog timer control register (WDTCON)                     |

| 001A16             | Serial I/O control register (SIOCON)     | 003A <sub>16</sub> | Interrupt edge selection register (INTEDGE)                  |

| 001B <sub>16</sub> | UART control register (UARTCON)          | 003B <sub>16</sub> | CPU mode register (CPUM)                                     |

| 001C <sub>16</sub> | Baud rate generator (BRG)                | 003C16             | Interrupt request register 1 (IREQ1)                         |

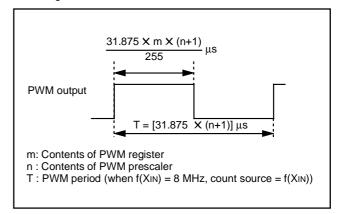

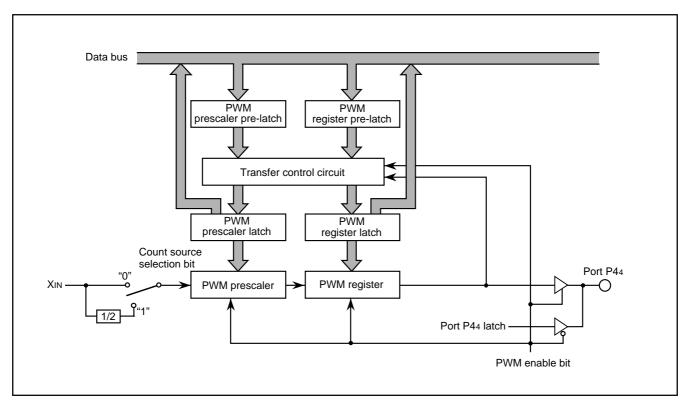

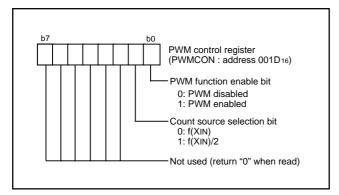

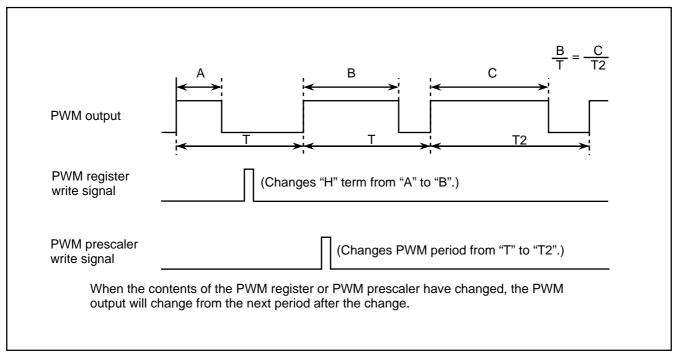

| 001D16             | PWM control register (PWMCON)            | 003D16             | Interrupt request register 2 (IREQ2)                         |

| 001E <sub>16</sub> | PWM prescaler (PREPWM)                   | 003E16             | Interrupt control register 1 (ICON1)                         |

| 001F <sub>16</sub> | PWM register (PWM)                       | 003F <sub>16</sub> | Interrupt control register 2 (ICON2)                         |

Fig. 6 Memory map of special function register (SFR)

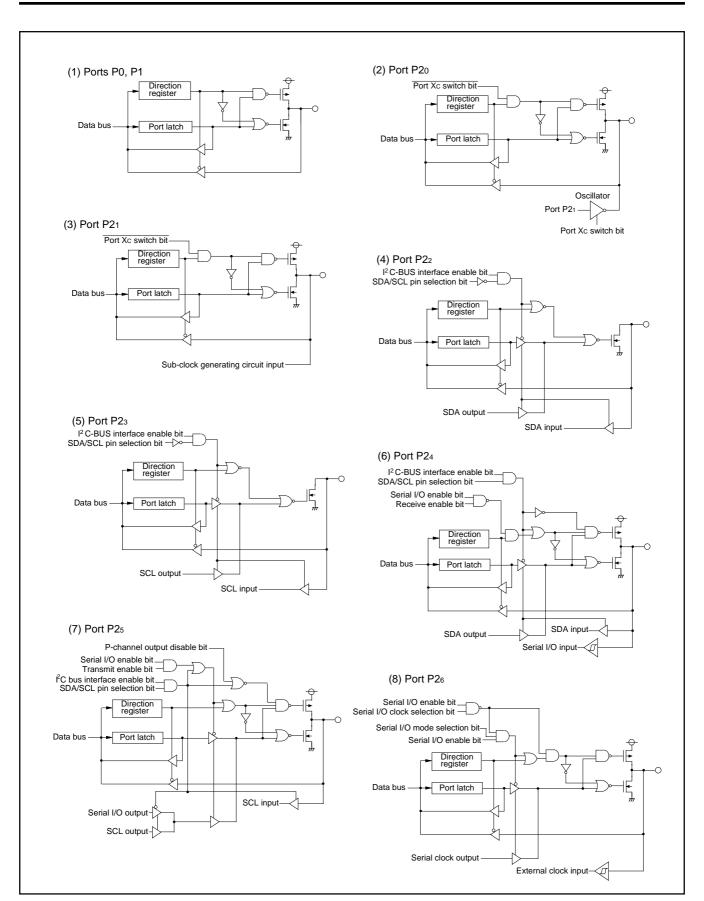

#### I/O PORTS

The I/O ports have direction registers which determine the input/output direction of each individual pin. Each bit in a direction register corresponds to one pin, and each pin can be set to be input port or output port.

When "0" is written to the bit corresponding to a pin, that pin becomes an input pin. When "1" is written to that bit, that pin becomes an output pin.

If data is read from a pin which is set to output, the value of the port output latch is read, not the value of the pin itself. Pins set to input are floating. If a pin set to input is written to, only the port output latch is written to and the pin remains floating.

Table 2 I/O port function

| Pin                          | Name    | Input/Output                        | I/O Structure                                                                                                                                                                                                        | Non-Port Function                                                   | Related SFRs                                                        | Ref.No.    |

|------------------------------|---------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|------------|

| P00-P07                      | Port P0 |                                     |                                                                                                                                                                                                                      |                                                                     |                                                                     | (4)        |

| P10-P17                      | Port P1 |                                     | CMOS compatible input level                                                                                                                                                                                          |                                                                     |                                                                     | (1)        |

| P20/XCOUT                    |         |                                     | CMOS 3-state output                                                                                                                                                                                                  | Sub-clock generating                                                | ODII I I                                                            | (2)        |

| P21/XCIN                     |         |                                     |                                                                                                                                                                                                                      | circuit                                                             | CPU mode register                                                   | (3)        |

| P22/SDA1<br>P23/SCL1         |         |                                     | CMOS compatible input level CMOS/SMBUS input level (when selecting I <sup>2</sup> C-BUS interface function) N-channel open-drain output                                                                              | I <sup>2</sup> C-BUS interface function I/O                         | I <sup>2</sup> C control register                                   | (4)<br>(5) |

| P24/SDA2/RxD<br>P25/SCL2/TxD | Port P2 | Input/output,<br>individual<br>bits | CMOS compatible input level CMOS/SMBUS input level (when selecting I <sup>2</sup> C-BUS interface function) CMOS 3-state output N-channel open-drain output (when selecting I <sup>2</sup> C-BUS interface function) | I <sup>2</sup> C-BUS interface function I/O Serial I/O function I/O | I <sup>2</sup> C control register<br>Serial I/O control<br>register | (6)<br>(7) |

| P26/SCLK                     |         |                                     |                                                                                                                                                                                                                      | Serial I/O function I/O                                             | Serial I/O control register                                         | (8)        |

| P27/CNTR0/SRDY               |         |                                     |                                                                                                                                                                                                                      | Serial I/O function I/O Timer X function I/O                        | Serial I/O control<br>register<br>Timer XY mode register            | (9)        |

| P30/AN0—                     | Port P3 |                                     | CMOS compatible input level                                                                                                                                                                                          | A-D conversion input                                                | A-D control register                                                | (10)       |

| P34/AN4<br>P40/CNTR1         |         |                                     | CMOS 3-state output                                                                                                                                                                                                  | Timer Y function I/O                                                | Timer XY mode register                                              | (11)       |

| P41/INT0—                    |         |                                     |                                                                                                                                                                                                                      |                                                                     | Interrupt edge selection                                            | <u> </u>   |

| P43/INT2                     |         |                                     |                                                                                                                                                                                                                      | External interrupt input                                            | register                                                            | (12)       |

| P44/INT3/PWM                 | Port P4 |                                     |                                                                                                                                                                                                                      | External interrupt input PWM output                                 | Interrupt edge selection register PWM control register              | (13)       |

Fig. 7 Port block diagram (1)

Fig. 8 Port block diagram (2)

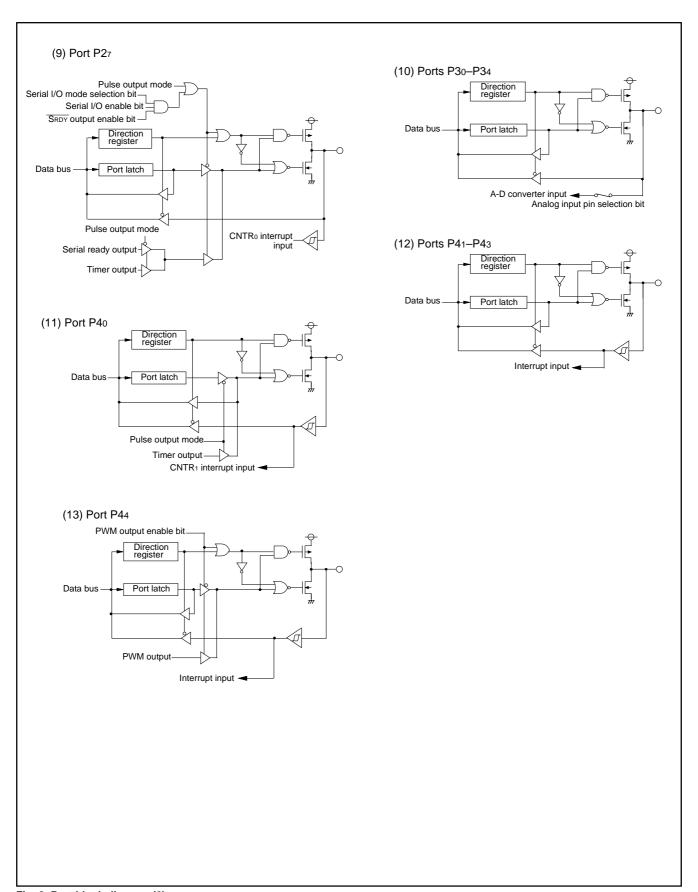

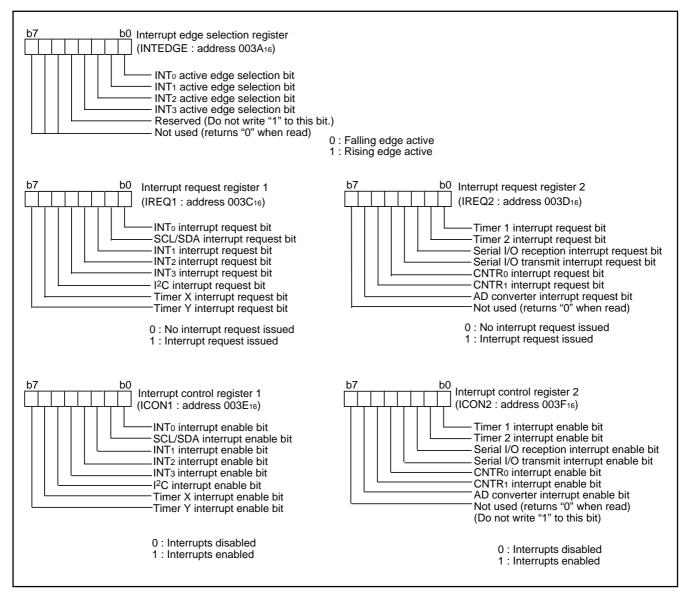

#### **INTERRUPTS**

Interrupts occur by 16 sources among 16 sources: seven external, eight internal, and one software.

## **Interrupt Control**

Each interrupt is controlled by an interrupt request bit, an interrupt enable bit, and the interrupt disable flag except for the software interrupt set by the BRK instruction. An interrupt occurs if the corresponding interrupt request and enable bits are "1" and the interrupt disable flag is "0".

Interrupt enable bits can be set or cleared by software.

Interrupt request bits can be cleared by software, but cannot be set by software.

The BRK instruction cannot be disabled with any flag or bit. The I (interrupt disable) flag disables all interrupts except the BRK instruction interrupt.

When several interrupts occur at the same time, the interrupts are received according to priority.

#### **Interrupt Operation**

By acceptance of an interrupt, the following operations are automatically performed:

- The contents of the program counter and the processor status register are automatically pushed onto the stack.

- 2. The interrupt disable flag is set and the corresponding interrupt request bit is cleared.

- 3. The interrupt jump destination address is read from the vector table into the program counter.

#### ■Notes

When setting the followings, the interrupt request bit may be set to "1"  $\,$

- •When setting external interrupt active edge

Related register: Interrupt edge selection register (address 3A16)

Timer XY mode register (address 2316)

- •When switching interrupt sources of an interrupt vector address where two or more interrupt sources are allocated

Related register: Interrupt edge selection register (address 3A<sub>16</sub>) When not requiring for the interrupt occurrence synchronized with these setting, take the following sequence.

- ①Set the corresponding interrupt enable bit to "0" (disabled).

- ②Set the interrupt edge select bit or the interrupt source select bit.

- ③Set the corresponding interrupt request bit to "0" after 1 or more instructions have been executed.

- Set the corresponding interrupt enable bit to "1" (enabled).

Table 3 Interrupt vector addresses and priority

| Interrupt Course Drierity  |          | Vector Addresses (Note 1) |        | Interrupt Request                                                                       | Develop                                     |  |

|----------------------------|----------|---------------------------|--------|-----------------------------------------------------------------------------------------|---------------------------------------------|--|

| Interrupt Source           | Priority | High                      | Low    | Generating Conditions                                                                   | Remarks                                     |  |

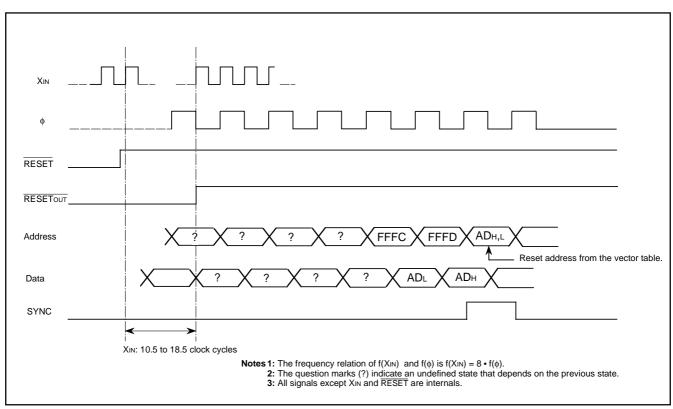

| Reset (Note 2)             | 1        | FFFD16                    | FFFC16 | At reset                                                                                | Non-maskable                                |  |

| INT <sub>0</sub>           | 2        | FFFB16                    | FFFA16 | At detection of either rising or falling edge of INTo input                             | External interrupt (active edge selectable) |  |

| SCL, SDA                   | 3        | FFF916                    | FFF816 | At detection of either rising or falling edge of SCL or SDA input                       | External interrupt (active edge selectable) |  |

| INT1                       | 4        | FFF716                    | FFF616 | At detection of either rising or falling edge of INT1 input                             | External interrupt (active edge selectable) |  |

| INT2                       | 5        | FFF516                    | FFF416 | At detection of either rising or falling edge of INT2 input                             | External interrupt (active edge selectable) |  |

| INT3                       | 6        | FFF316                    | FFF216 | At detection of either rising or falling edge of INT3 input                             | External interrupt (active edge selectable) |  |

| I <sup>2</sup> C           | 7        | FFF116                    | FFF016 | At completion of data transfer                                                          |                                             |  |

| Timer X                    | 8        | FFEF16                    | FFEE16 | At timer X underflow                                                                    |                                             |  |

| Timer Y                    | 9        | FFED16                    | FFEC16 | At timer Y underflow                                                                    |                                             |  |

| Timer 1                    | 10       | FFEB16                    | FFEA16 | At timer 1 underflow                                                                    | STP release timer underflow                 |  |

| Timer 2                    | 11       | FFE916                    | FFE816 | At timer 2 underflow                                                                    |                                             |  |

| Serial I/O reception       | 12       | FFE716                    | FFE616 | At completion of serial I/O data reception                                              | Valid when serial I/O is selected           |  |

| Serial I/O<br>Transmission | 13       | FFE516                    | FFE416 | At completion of serial I/O trans-<br>fer shift or when transmission<br>buffer is empty | Valid when serial I/O is selected           |  |

| CNTR <sub>0</sub>          | 14       | FFE316                    | FFE216 | At detection of either rising or falling edge of CNTRo input                            | External interrupt (active edge selectable) |  |

| CNTR1                      | 15       | FFE116                    | FFE016 | At detection of either rising or falling edge of CNTR1 input                            | External interrupt (active edge selectable) |  |

| A-D converter              | 16       | FFDF16                    | FFDE16 | At completion of A-D conversion                                                         |                                             |  |

| BRK instruction            | 17       | FFDD16                    | FFDC16 | At BRK instruction execution                                                            | Non-maskable software interrupt             |  |

Notes 1: Vector addresses contain interrupt jump destination addresses.

<sup>2:</sup> Reset function in the same way as an interrupt with the highest priority.

Fig. 9 Interrupt control

Fig. 10 Structure of interrupt-related registers (1)

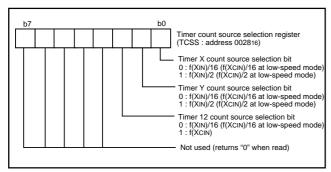

#### **TIMERS**

The 3851 group has four timers: timer X, timer Y, timer 1, and timer 2

The division ratio of each timer or prescaler is given by 1/(n + 1), where n is the value in the corresponding timer or prescaler latch. All timers are count down. When the timer reaches "0016", an underflow occurs at the next count pulse and the corresponding timer latch is reloaded into the timer and the count is continued. When a timer underflows, the interrupt request bit corresponding to that timer is set to "1".

Fig. 11 Structure of timer XY mode register

Fig. 12 Structure of timer count source selection register

#### **Timer 1 and Timer 2**

The count source of prescaler 12 is the oscillation frequency divided by 16. The output of prescaler 12 is counted by timer 1 and timer 2, and a timer underflow sets the interrupt request bit.

#### Timer X and Timer Y

Timer X and Timer Y can each select in one of four operating modes by setting the timer XY mode register.

## (1) Timer Mode

The timer counts the count source selected by Timer count source selection bit.

## (2) Pulse Output Mode

The timer counts the count source selected by Timer count source selection bit. Whenever the contents of the timer reach "0016", the signal output from the CNTR0 (or CNTR1) pin is inverted. If the CNTR0 (or CNTR1) active edge selection bit is "0", output begins at "H".

If it is "1", output starts at "L". When using a timer in this mode, set the corresponding port P27 (or port P40) direction register to output mode.

## (3) Event Counter Mode

Operation in event counter mode is the same as in timer mode, except that the timer counts signals input through the CNTR0 or CNTR1 pin.

When the CNTR0 (or CNTR1) active edge selection bit is "0", the rising edge of the CNTR0 (or CNTR1) pin is counted.

When the CNTR0 (or CNTR1) active edge selection bit is "1", the falling edge of the CNTR0 (or CNTR1) pin is counted.

## (4) Pulse Width Measurement Mode

If the CNTR0 (or CNTR1) active edge selection bit is "0", the timer counts the selected signals by the count source selection bit while the CNTR0 (or CNTR1) pin is at "H". If the CNTR0 (or CNTR1) active edge selection bit is "1", the timer counts it while the CNTR0 (or CNTR1) pin is at "L".

The count can be stopped by setting "1" to the timer X (or timer Y) count stop bit in any mode. The corresponding interrupt request bit is set each time a timer overflows.

#### ■Note

When switching the count source by the timer 12, X and Y count source bit, the value of timer count is altered in unconsiderable amount owing to generating of a thin pulses in the count input signals.

Therefore, select the timer count source before set the value to the prescaler and the timer.

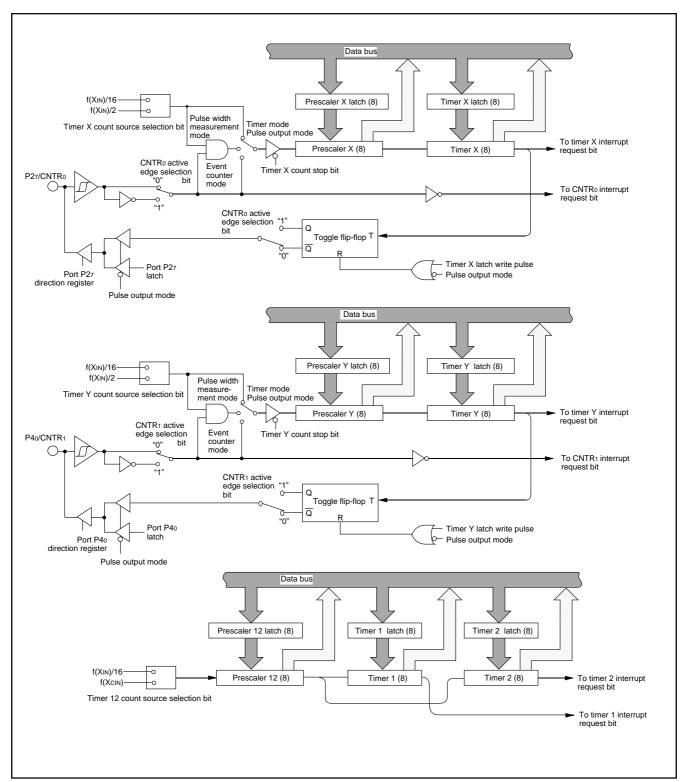

Fig. 13 Block diagram of timer X, timer Y, timer 1, and timer 2

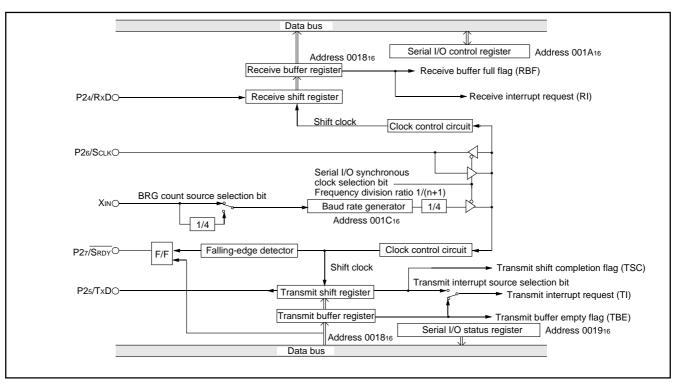

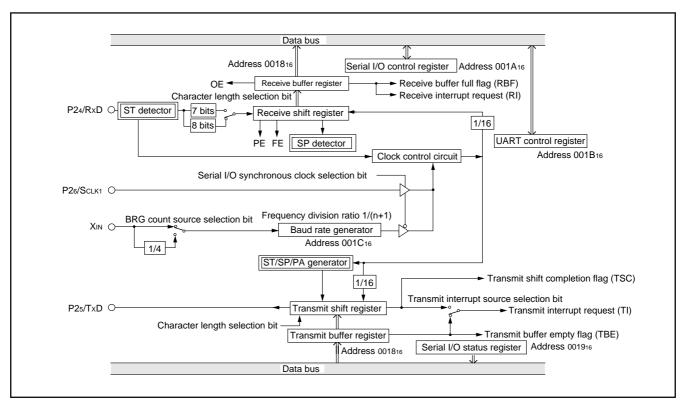

#### SERIAL I/O

Serial I/O can be used as either clock synchronous or asynchronous (UART) serial I/O. A dedicated timer is also provided for baud rate generation.

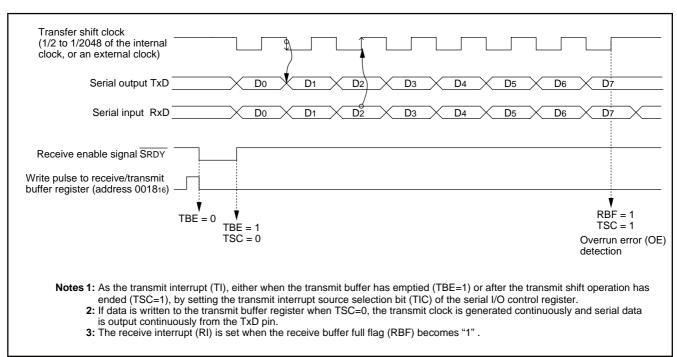

## (1) Clock Synchronous Serial I/O Mode

Clock synchronous serial I/O mode can be selected by setting the serial I/O mode selection bit of the serial I/O control register (bit 6 of address 001A16) to "1".

For clock synchronous serial I/O, the transmitter and the receiver must use the same clock. If an internal clock is used, transfer is started by a write signal to the TB/RB.

Fig. 14 Block diagram of clock synchronous serial I/O

Fig. 15 Operation of clock synchronous serial I/O function

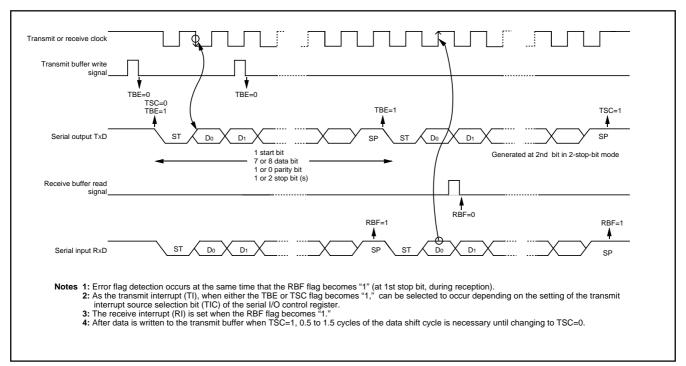

## (2) Asynchronous Serial I/O (UART) Mode

Clock asynchronous serial I/O mode (UART) can be selected by clearing the serial I/O mode selection bit (b6) of the serial I/O control register to "0".

Eight serial data transfer formats can be selected, and the transfer formats used by a transmitter and receiver must be identical.

The transmit and receive shift registers each have a buffer, but the

two buffers have the same address in memory. Since the shift register cannot be written to or read from directly, transmit data is written to the transmit buffer register, and receive data is read from the receive buffer register.

The transmit buffer register can also hold the next data to be transmitted, and the receive buffer register can hold a character while the next character is being received.

Fig.16 Block diagram of UART serial I/O

Fig. 17 Operation of UART serial I/O function

## [Transmit Buffer Register/Receive Buffer Register (TB/RB)] 001816

The transmit buffer register and the receive buffer register are located at the same address. The transmit buffer is write-only and the receive buffer is read-only. If a character bit length is 7 bits, the MSB of data stored in the receive buffer is "0".

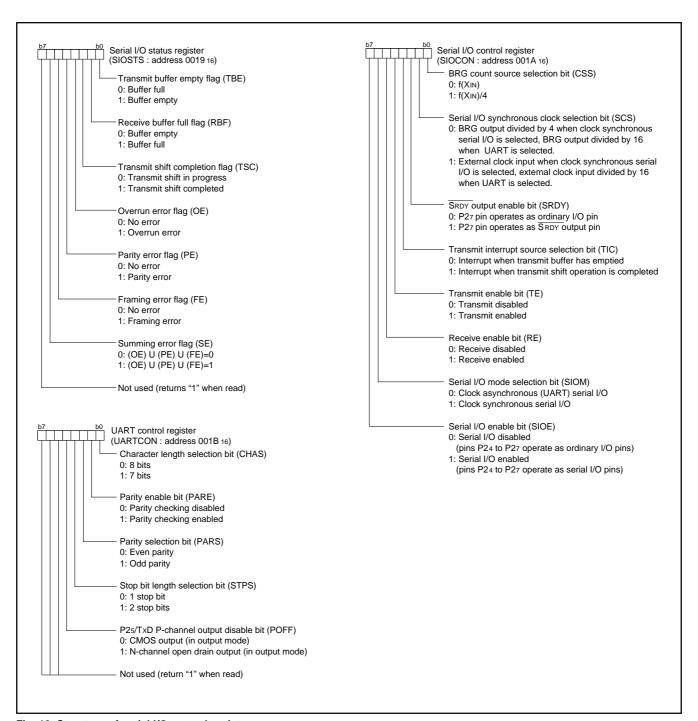

#### [Serial I/O Status Register (SIOSTS)] 001916

The read-only serial I/O status register consists of seven flags (bits 0 to 6) which indicate the operating status of the serial I/O function and various errors.

Three of the flags (bits 4 to 6) are valid only in UART mode.

The receive buffer full flag (bit 1) is cleared to "0" when the receive buffer register is read.

If there is an error, it is detected at the same time that data is transferred from the receive shift register to the receive buffer register, and the receive buffer full flag is set. A write to the serial I/O status register clears all the error flags OE, PE, FE, and SE (bit 3 to bit 6, respectively). Writing "0" to the serial I/O enable bit SIOE (bit 7 of the serial I/O control register) also clears all the status flags, including the error flags.

Bits 0 to 6 of the serial I/O status register are initialized to "0" at reset, but if the transmit enable bit (bit 4) of the serial I/O control register has been set to "1", the transmit shift completion flag (bit 2) and the transmit buffer empty flag (bit 0) become "1".

## [Serial I/O Control Register (SIOCON)] 001A16

The serial I/O control register consists of eight control bits for the serial I/O function.

#### [UART Control Register (UARTCON)] 001B16

The UART control register consists of four control bits (bits 0 to 3) which are valid when asynchronous serial I/O is selected and set the data format of an data transfer and one bit (bit 4) which is always valid and sets the output structure of the P25/TxD pin.

## [Baud Rate Generator (BRG)] 001C16

The baud rate generator determines the baud rate for serial transfer

The baud rate generator divides the frequency of the count source by 1/(n + 1), where n is the value written to the baud rate generator.

#### ■Notes on Serial I/O

- 1. When using the serial I/O, clear the  $I^2C$ -BUS interface enable bit to "0" or the ScL/SDA interrupt pin selection bit to "0".

- 2. When setting the transmit enable bit of serial I/O to "1", the serial I/O transmit interrupt request bit is automatically set to "1". When not requiring the interrupt occurrence synchronized with the transmission enalbed, take the following sequence.

- ①Set the serial I/O transmit interrupt enable bit to "0" (disabled).

- ②Set the transmit enable bit to "1".

- ③Set the serial I/O transmit interrupt request bit to "0" after 1 or more instructions have been executed.

- Set the serial I/O transmit interrupt enable bit to "1" (enabled).

Fig. 18 Structure of serial I/O control registers

## MULTI-MASTER I<sup>2</sup>C-BUS INTERFACE

The multi-master  $I^2C$ -BUS interface is a serial communications circuit, conforming to the Philips  $I^2C$ -BUS data transfer format. This interface, offering both arbitration lost detection and a synchronous functions, is useful for the multi-master serial communications.

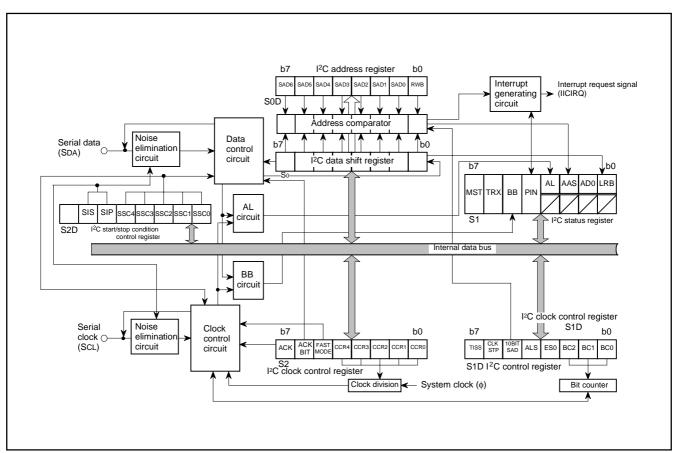

Figure 19 shows a block diagram of the multi-master I<sup>2</sup>C-BUS interface and Table 4 lists the multi-master I<sup>2</sup>C-BUS interface functions.

This multi-master I $^2$ C-BUS interface consists of the I $^2$ C address register, the I $^2$ C data shift register, the I $^2$ C clock control register, the I $^2$ C control register, the I $^2$ C status register, the I $^2$ C start/stop condition control register and other control circuits.

When using the multi-master I^2C-BUS interface, set 1 MHz or more to  $\boldsymbol{\varphi}.$

Note: Mitsubishi Electric Corporation assumes no responsibility for infringement of any third-party's rights or originating in the use of the connection control function between the I<sup>2</sup>C-BUS interface and the ports SCL1, SCL2, SDA1 and SDA2 with the bit 6 of I<sup>2</sup>C control register (002E16).

Table 4 Multi-master I<sup>2</sup>C-BUS interface functions

| Item                | Function                                                                                                                                             |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Format              | In conformity with Philips I <sup>2</sup> C-BUS standard: 10-bit addressing format 7-bit addressing format High-speed clock mode Standard clock mode |

| Communication mode  | In conformity with Philips I <sup>2</sup> C-BUS standard: Master transmission Master reception Slave transmission Slave reception                    |

| SCL clock frequency | 16.1 kHz to 400 kHz (at φ= 4 MHz)                                                                                                                    |

System clock  $\phi = f(XIN)/2$  (high-speed mode)  $\phi = f(XIN)/8$  (middle-speed mode)

Fig. 19 Block diagram of multi-master I<sup>2</sup>C-BUS interface

\*: Purchase of MITSUBISHI ELECTRIC CORPORATIONS I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

## [I<sup>2</sup>C Data Shift Register (S0)] 002B<sub>16</sub>

The  $I^2C$  data shift register (S0 : address 002B16) is an 8-bit shift register to store receive data and write transmit data.

When transmit data is written into this register, it is transferred to the outside from bit 7 in synchronization with the SCL clock, and each time one-bit data is output, the data of this register are shifted by one bit to the left. When data is received, it is input to this register from bit 0 in synchronization with the SCL clock, and each time one-bit data is input, the data of this register are shifted by one bit to the left. The minimum 2 machine cycles are required from the rising of the SCL clock until input to this register.

The  $I^2C$  data shift register is in a write enable status only when the  $I^2C$ -BUS interface enable bit (ES0 bit : bit 3 of address 002E16) of the  $I^2C$  control register is "1". The bit counter is reset by a write instruction to the  $I^2C$  data shift register. When both the ES0 bit and the MST bit of the  $I^2C$  status register (address 002D16) are "1," the SCL is output by a write instruction to the  $I^2C$  data shift register. Reading data from the  $I^2C$  data shift register is always enabled regardless of the ES0 bit value.

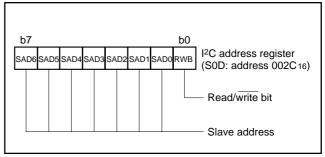

## [I<sup>2</sup>C Address Register (S0D)] 002C16

The I<sup>2</sup>C address register (address 002C<sub>16</sub>) consists of a 7-bit slave address and a read/write bit. In the addressing mode, the slave address written in this register is compared with the address data to be received immediately after the START condition is detected.

#### •Bit 0: Read/write bit (RWB)

This is not used in the 7-bit addressing mode. In the 10-bit addressing mode, the first address data to be received is compared with the contents (SAD6 to SAD0 + RWB) of the  $I^2C$  address register.

The RWB bit is cleared to "0" automatically when the stop condition is detected.

## •Bits 1 to 7: Slave address (SAD0-SAD6)

These bits store slave addresses. Regardless of the 7-bit addressing mode and the 10-bit addressing mode, the address data transmitted from the master is compared with the contents of these bits.

Fig. 20 Structure of I<sup>2</sup>C address register

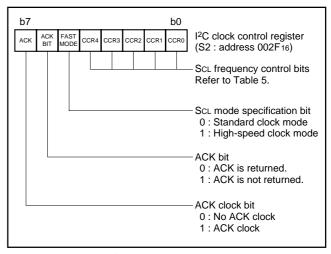

## [I<sup>2</sup>C Clock Control Register (S2)] 002F<sub>16</sub>

The  $I^2C$  clock control register (address 002F<sub>16</sub>) is used to set ACK control, SCL mode and SCL frequency.

#### •Bits 0 to 4: SCL frequency control bits (CCR0-CCR4)

These bits control the SCL frequency. Refer to Table 5.

#### •Bit 5: SCL mode specification bit (FAST MODE)

This bit specifies the SCL mode. When this bit is set to "0," the standard clock mode is selected. When the bit is set to "1," the high-speed clock mode is selected.

When connecting the bus of the high-speed mode  $I^2C$  bus standard (maximum 400 kbits/s), use 8 MHz or more oscillation frequency f(XIN) and 2 division clock.

#### •Bit 6: ACK bit (ACK BIT)

This bit sets the SDA status when an ACK clock\* is generated. When this bit is set to "0," the ACK return mode is selected and SDA goes to "L" at the occurrence of an ACK clock. When the bit is set to "1," the ACK non-return mode is selected. The SDA is held in the "H" status at the occurrence of an ACK clock.

However, when the slave address agree with the address data in the reception of address data at ACK BIT = "0," the SDA is automatically made "L" (ACK is returned). If there is a disagreement between the slave address and the address data, the SDA is automatically made "H" (ACK is not returned).

\*ACK clock: Clock for acknowledgment

#### •Bit 7: ACK clock bit (ACK)

This bit specifies the mode of acknowledgment which is an acknowledgment response of data transfer. When this bit is set to "0," the no ACK clock mode is selected. In this case, no ACK clock occurs after data transmission. When the bit is set to "1," the ACK clock mode is selected and the master generates an ACK clock each completion of each 1-byte data transfer. The device for transmitting address data and control data releases the SDA at the occurrence of an ACK clock (makes SDA "H") and receives the ACK bit generated by the data receiving device.

**Note:** Do not write data into the  $I^2C$  clock control register during transfer. If data is written during transfer, the  $I^2C$  clock generator is reset, so that data cannot be transferred normally.

Fig. 21 Structure of I<sup>2</sup>C clock control register

Table 5 Set values of I<sup>2</sup>C clock control register and SCL frequency

| Setting value of CCR4–CCR0 |      |      |      |      | equency<br>z, unit : kHz) |                            |

|----------------------------|------|------|------|------|---------------------------|----------------------------|

| CCR4                       | CCR3 | CCR2 | CCR1 | CCR0 | Standard clock mode       | High-speed clock mode      |

| 0                          | 0    | 0    | 0    | 0    | Setting disabled          | Setting disabled           |

| 0                          | 0    | 0    | 0    | 1    | Setting disabled          | Setting disabled           |

| 0                          | 0    | 0    | 1    | 0    | Setting disabled          | Setting disabled           |

| 0                          | 0    | 0    | 1    | 1    | - (Note 2)                | 333                        |

| 0                          | 0    | 1    | 0    | 0    | - (Note 2)                | 250                        |

| 0                          | 0    | 1    | 0    | 1    | 100                       | 400 (Note 3)               |

| 0                          | 0    | 1    | 1    | 0    | 83.3                      | 166                        |

| :                          | :    | :    | :    | :    | 500/CCR value (Note 3)    | 1000/CCR value<br>(Note 3) |

| 1                          | 1    | 1    | 0    | 1    | 17.2                      | 34.5                       |

| 1                          | 1    | 1    | 1    | 0    | 16.6                      | 33.3                       |

| 1                          | 1    | 1    | 1    | 1    | 16.1                      | 32.3                       |

Notes 1: Duty of ScL clock output is 50 %. The duty becomes 35 to 45 % only when the high-speed clock mode is selected and CCR value = 5 (400 kHz, at φ = 4 MHz). "H" duration of the clock fluctuates from –4 to +2 machine cycles in the standard clock mode, and fluctuates from –2 to +2 machine cycles in the high-speed clock mode. In the case of negative fluctuation, the frequency does not increase because "L" duration is extended instead of "H" duration reduction.

These are value when ScL clock synchronization by the synchronous function is not performed. CCR value is the decimal notation value of the ScL frequency control bits CCR4 to CCR0.

- 2: Each value of ScL frequency exceeds the limit at φ = 4 MHz or more. When using these setting value, use φ of 4 MHz or less.

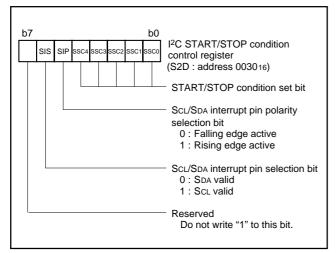

## [I<sup>2</sup>C Control Register (S1D)] 002E<sub>16</sub>

The I<sup>2</sup>C control register (address 002E<sub>16</sub>) controls data communication format.

#### •Bits 0 to 2: Bit counter (BC0-BC2)

These bits decide the number of bits for the next 1-byte data to be transmitted. The I<sup>2</sup>C interrupt request signal occurs immediately after the number of count specified with these bits (ACK clock is added to the number of count when ACK clock is selected by ACK clock bit (bit 7 of address 002F16)) have been transferred, and BC0 to BC2 are returned to "0002".

Also when a START condition is received, these bits become "0002" and the address data is always transmitted and received in 8 bits.

#### •Bit 3: I<sup>2</sup>C interface enable bit (ES0)

This bit enables to use the multi-master I<sup>2</sup>C-BUS interface. When this bit is set to "0," the use disable status is provided, so that the SDA and the SCL become high-impedance. When the bit is set to "1," use of the interface is enabled.

When ES0 = "0," the following is performed.

- PIN = "1," BB = "0" and AL = "0" are set (which are bits of the I<sup>2</sup>C status register at address 002D16).

- Writing data to the I<sup>2</sup>C data shift register (address 002B16) is disabled.

#### •Bit 4: Data format selection bit (ALS)

This bit decides whether or not to recognize slave addresses. When this bit is set to "0," the addressing format is selected, so that address data is recognized. When a match is found between a slave address and address data as a result of comparison or when a general call (refer to "I<sup>2</sup>C Status Register," bit 1) is received, transfer processing can be performed. When this bit is set to "1," the free data format is selected, so that slave addresses are not recognized.

#### •Bit 5: Addressing format selection bit (10BIT SAD)

This bit selects a slave address specification format. When this bit is set to "0," the 7-bit addressing format is selected. In this case, only the high-order 7 bits (slave address) of the  $I^2C$  address register (address 002C16) are compared with address data. When this bit is set to "1," the 10-bit addressing format is selected, and all the bits of the  $I^2C$  address register are compared with address

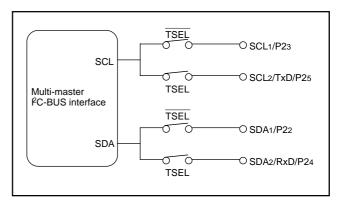

### •Bit 6: SDA/SCL pin selection bit

This bit selects the input/output pins of SCL and SDA of the multi-master I<sup>2</sup>C-BUS interface.

#### •Bit 7: I<sup>2</sup>C-BUS interface pin input level selection bit

This bit selects the input level of the SCL and SDA pins of the multi-master I<sup>2</sup>C-BUS interface.

Fig. 22 SDA/SCL pin selection bit

Fig. 23 Structure of I<sup>2</sup>C control register

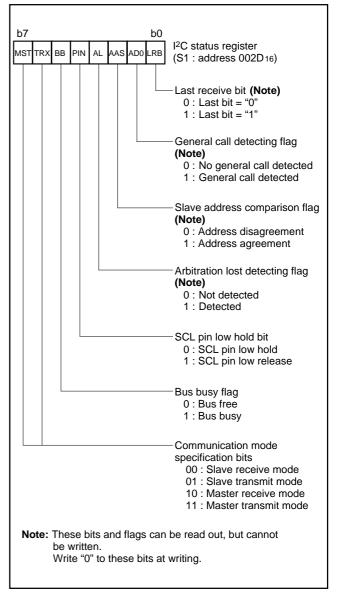

## [I<sup>2</sup>C Status Register (S1)] 002D16

The I<sup>2</sup>C status register (address 002D<sub>16</sub>) controls the I<sup>2</sup>C-BUS interface status. The low-order 4 bits are read-only bits and the high-order 4 bits can be read out and written to.

Set "00002" to the low-order 4 bits, because these bits become the reserved bits at writing.

#### •Bit 0: Last receive bit (LRB)

This bit stores the last bit value of received data and can also be used for ACK receive confirmation. If ACK is returned when an ACK clock occurs, the LRB bit is set to "0." If ACK is not returned, this bit is set to "1." Except in the ACK mode, the last bit value of received data is input. The state of this bit is changed from "1" to "0" by executing a write instruction to the I<sup>2</sup>C data shift register (address 002B16).

#### •Bit 1: General call detecting flag (AD0)

When the ALS bit is "0", this bit is set to "1" when a general call\* whose address data is all "0" is received in the slave mode. By a general call of the master device, every slave device receives control data after the general call. The AD0 bit is set to "0" by detecting the STOP condition or START condition, or reset.

\*General call: The master transmits the general call address "0016" to all slaves.

#### •Bit 2: Slave address comparison flag (AAS)

This flag indicates a comparison result of address data when the ALS bit is "0".

- ① In the slave receive mode, when the 7-bit addressing format is selected, this bit is set to "1" in one of the following conditions:

- The address data immediately after occurrence of a START condition agrees with the slave address stored in the high-order 7 bits of the I<sup>2</sup>C address register (address 002C16).

- A general call is received.

- ② In the slave receive mode, when the 10-bit addressing format is selected, this bit is set to "1" with the following condition:

- When the address data is compared with the I<sup>2</sup>C address register (8 bits consisting of slave address and RWB bit), the first bytes agree.

- This bit is set to "0" by executing a write instruction to the I<sup>2</sup>C data shift register (address 002B16) when ES0 is set to "1" or reset.

## •Bit 3: Arbitration lost\* detecting flag (AL)

In the master transmission mode, when the SDA is made "L" by any other device, arbitration is judged to have been lost, so that this bit is set to "1." At the same time, the TRX bit is set to "0," so that immediately after transmission of the byte whose arbitration was lost is completed, the MST bit is set to "0." The arbitration lost can be detected only in the master transmission mode. When arbitration is lost during slave address transmission, the TRX bit is set to "0" and the reception mode is set. Consequently, it becomes possible to detect the agreement of its own slave address and address data transmitted by another master device.

\*Arbitration lost :The status in which communication as a master is disabled.

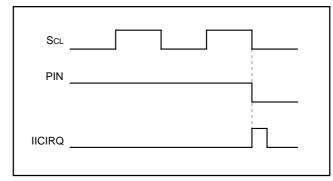

#### •Bit 4: SCL pin low hold bit (PIN)

This bit generates an interrupt request signal. Each time 1-byte data is transmitted, the PIN bit changes from "1" to "0." At the same time, an interrupt request signal occurs to the CPU. The PIN bit is set to "0" in synchronization with a falling of the last clock (including the ACK clock) of an internal clock and an interrupt request signal occurs in synchronization with a falling of the PIN bit. When the PIN bit is "0," the SCL is kept in the "0" state and clock generation is disabled. Figure 25 shows an interrupt request signal generating timing chart.

The PIN bit is set to "1" in one of the following conditions:

- Executing a write instruction to the I<sup>2</sup>C data shift register (address 002B<sub>16</sub>). (This is the only condition which the prohibition of the internal clock is released and data can be communicated except for the start condition detection.)

- When the ES0 bit is "0"

- · At reset

- When writing "1" to the PIN bit by software

The conditions in which the PIN bit is set to "0" are shown below:

- Immediately after completion of 1-byte data transmission (including when arbitration lost is detected)

- Immediately after completion of 1-byte data reception

- In the slave reception mode, with ALS = "0" and immediately after completion of slave address agreement or general call address reception

- In the slave reception mode, with ALS = "1" and immediately after completion of address data reception

#### •Bit 5: Bus busy flag (BB)

This bit indicates the status of use of the bus system. When this bit is set to "0," this bus system is not busy and a START condition can be generated. The BB flag is set/reset by the SCL, SDA pins input signal regardless of master/slave. This flag is set to "1" by detecting the start condition, and is set to "0" by detecting the stop condition. The condition of these detecting is set by the start/stop condition setting bits (SSC4–SSC0) of the I<sup>2</sup>C start/stop condition control register (address 003016). When the ES0 bit of the I<sup>2</sup>C control register (address 002E16) is "0" or reset, the BB flag is set to "0"

For the writing function to the BB flag, refer to the sections "START Condition Generating Method" and "STOP Condition Generating Method" described later.

## •Bit 6: Communication mode specification bit (transfer direction specification bit: TRX)

This bit decides a direction of transfer for data communication. When this bit is "0," the reception mode is selected and the data of a transmitting device is received. When the bit is "1," the transmission mode is selected and address data and control data are output onto the SDA in synchronization with the clock generated on the SCL.

This bit is set/reset by software and hardware. About set/reset by hardware is described below. This bit is set to "1" by hardware when all the following conditions are satisfied:

- When ALS is "0"

- In the slave reception mode or the slave transmission mode

- When the R/W bit reception is "1"

This bit is set to "0" in one of the following conditions:

- · When arbitration lost is detected.

- When a STOP condition is detected.

- When writing "1" to this bit by software is invalid by the START condition duplication preventing function (Note).

- With MST = "0" and when a START condition is detected.

- With MST = "0" and when ACK non-return is detected.

- At reset

#### Bit 7: Communication mode specification bit (master/slave specification bit: MST)

This bit is used for master/slave specification for data communication. When this bit is "0," the slave is specified, so that a START condition and a STOP condition generated by the master are received, and data communication is performed in synchronization with the clock generated by the master. When this bit is "1," the master is specified and a START condition and a STOP condition are generated. Additionally, the clocks required for data communication are generated on the SCL.

This bit is set to "0" in one of the following conditions.

- Immediately after completion of 1-byte data transfer when arbitration lost is detected

- When a STOP condition is detected.

- Writing "1" to this bit by software is invalid by the START condition duplication preventing function (**Note**).

- At reset

Note: START condition duplication preventing function

The MST, TRX, and BB bits is set to "1" at the same time after confirming that the BB flag is "0" in the procedure of a START condition occurrence. However, when a START condition by another master device occurs and the BB flag is set to "1" immediately after the contents of the BB flag is confirmed, the START condition duplication preventing function makes the writing to the MST and TRX bits invalid. The duplication preventing function becomes valid from the rising of the BB flag to reception completion of slave address.

Fig. 24 Structure of I<sup>2</sup>C status register

Fig. 25 Interrupt request signal generating timing

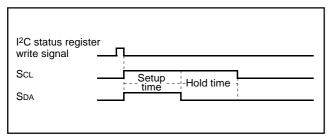

## **START Condition Generating Method**

When writing "1" to the MST, TRX, and BB bits of the I<sup>2</sup>C status register (address 002D<sub>16</sub>) at the same time after writing the slave address to the I<sup>2</sup>C data shift register (address 002B<sub>16</sub>) with the condition in which the ES0 bit of the I<sup>2</sup>C control register (address 002E<sub>16</sub>) and the BB flag are "0", a START condition occurs. After that, the bit counter becomes "0002" and an ScL for 1 byte is output. The START condition generating timing is different in the standard clock mode and the high-speed clock mode. Refer to Figure 26, the START condition generating timing diagram, and Table 6, the START condition generating timing table.

Fig. 26 START condition generating timing diagram

Table 6 START condition generating timing table

| Item       | Standard clock mode | High-speed clock mode |  |  |  |  |

|------------|---------------------|-----------------------|--|--|--|--|

| Setup time | 5.0 μs (20 cycles)  | 2.5 μs (10 cycles)    |  |  |  |  |

| Hold time  | 5.0 μs (20 cycles)  | 2.5 μs (10 cycles)    |  |  |  |  |

**Note:** Absolute time at  $\phi = 4$  MHz. The value in parentheses denotes the number of  $\phi$  cycles.

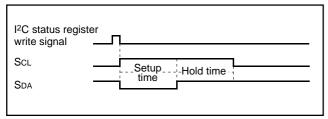

#### **STOP Condition Generating Method**

When the ES0 bit of the I<sup>2</sup>C control register (address 002E16) is "1," write "1" to the MST and TRX bits, and write "0" to the BB bit of the I<sup>2</sup>C status register (address 002D16) simultaneously. Then a STOP condition occurs. The STOP condition generating timing is different in the standard clock mode and the high-speed clock mode. Refer to Figure 27, the STOP condition generating timing diagram, and Table 7, the STOP condition generating timing table.

Fig. 27 STOP condition generating timing diagram

Table 7 STOP condition generating timing table

| Item       | Standard clock mode | High-speed clock mode |

|------------|---------------------|-----------------------|

| Setup time | 5.0 μs (20 cycles)  | 3.0 μs (12 cycles)    |

| Hold time  | 4.5 μs (18 cycles)  | 2.5 μs (10 cycles)    |

Note: Absolute time at  $\varphi$  = 4 MHz. The value in parentheses denotes the number of  $\varphi$  cycles.

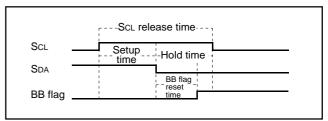

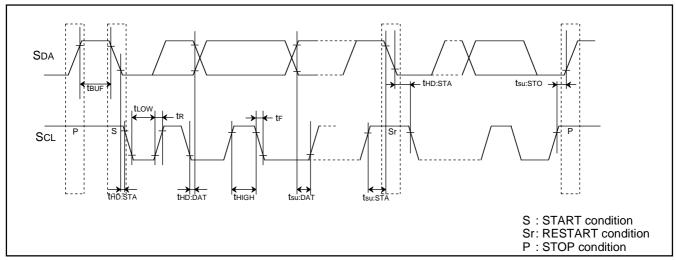

## START/STOP Condition Detecting Operation

The START/STOP condition detection operations are shown in Figures 28, 29, and Table 8. The START/STOP condition is set by the START/STOP condition set bit.

The START/STOP condition can be detected only when the input signal of the SCL and SDA pins satisfy three conditions: SCL release time, setup time, and hold time (see Table 8).

The BB flag is set to "1" by detecting the START condition and is reset to "0" by detecting the STOP condition.

The BB flag set/reset timing is different in the standard clock mode and the high-speed clock mode. Refer to Table 8, the BB flag set/reset time.

Note: When a STOP condition is detected in the slave mode (MST = 0), an interrupt request signal "IICIRQ" occurs to the CPU.

Fig. 28 START condition detecting timing diagram

Fig. 29 STOP condition detecting timing diagram

Table 8 START condition/STOP condition detecting conditions

|                            | Standard clock mode                                                      | High-speed clock mode |

|----------------------------|--------------------------------------------------------------------------|-----------------------|

| Scl release time           | SSC value + 1 cycle (6.25 µs)                                            | 4 cycles (1.0 μs)     |

| Setup time                 | $\frac{\text{SSC value} + 1}{2}$ cycle < 4.0 µs (3.125 µs)               | 2 cycles (1.0 μs)     |

| Hold time                  | $\frac{\text{SSC value} + 1}{2}$ cycle < 4.0 µs (3.125 µs)               | 2 cycles (0.5 μs)     |

| BB flag set/<br>reset time | $\frac{\text{SSC value } -1}{2} + 2 \text{ cycles } (3.375 \mu\text{s})$ | 3.5 cycles (0.875 μs) |

Note: Unit: Cycle number of system clock  $\phi$

SSC value is the decimal notation value of the START/STOP condition set bits SSC4 to SSC0. Do not set "0" or an odd number to SSC value. The value in parentheses is an example when the  $I^2$ C START/STOP condition control register is set to "1816" at  $\phi = 4$  MHz.

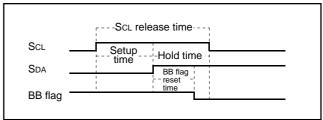

## [I<sup>2</sup>C START/STOP Condition Control Register (S2D)] 0030<sub>16</sub>

The I<sup>2</sup>C START/STOP condition control register (address 003016) controls START/STOP condition detection.

#### •Bits 0 to 4: START/STOP condition set bit (SSC4-SSC0)

SCL release time, setup time, and hold time change the detection condition by value of the main clock divide ratio selection bit and the oscillation frequency f(XIN) because these time are measured by the internal system clock. Accordingly, set the proper value to the START/STOP condition set bits (SSC4 to SSC0) in considered of the system clock frequency. Refer to Table 8.

Do not set "000002" or an odd number to the START/STOP condition set bit (SSC4 to SSC0).

Refer to Table 9, the recommended set value to START/STOP condition set bits (SSC4–SSC0) for each oscillation frequency.

#### •Bit 5: SCL/SDA interrupt pin polarity selection bit (SIP)

An interrupt can occur when detecting the falling or rising edge of the SCL or SDA pin. This bit selects the polarity of the SCL or SDA pin interrupt pin.

## •Bit 6: SCL/SDA interrupt pin selection bit (SIS)

This bit selects the pin of which interrupt becomes valid between the SCL pin and the SDA pin.

Note: When changing the setting of the ScL/SDA interrupt pin polarity selection bit, the ScL/SDA interrupt pin selection bit, or the I<sup>2</sup>C-BUS interface enable bit ES0, the ScL/SDA interrupt request bit may be set. When selecting the ScL/SDA interrupt source, disable the interrupt before the ScL/SDA interrupt pin polarity selection bit, the ScL/SDA interrupt pin selection bit, or the I<sup>2</sup>C-BUS interface enable bit ES0 is set. Reset the request bit to "0" after setting these bits, and enable the interrupt.

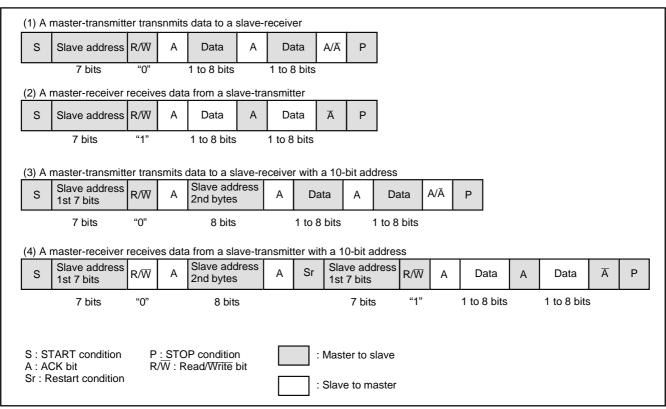

#### Address Data Communication

There are two address data communication formats, namely, 7-bit addressing format and 10-bit addressing format. The respective address communication formats are described below.

### ① 7-bit addressing format

To adapt the 7-bit addressing format, set the 10BIT SAD bit of the  $I^2C$  control register (address 002E16) to "0." The first 7-bit address data transmitted from the master is compared with the high-order 7-bit slave address stored in the  $I^2C$  address register (address 002C16). At the time of this comparison, address comparison of the RWB bit of the  $I^2C$  address register (address 002C16) is not performed. For the data transmission format when the 7-bit addressing format is selected, refer to Figure 31, (1) and (2).

#### 2 10-bit addressing format

To adapt the 10-bit addressing format, set the 10BIT SAD bit of the  $I^2C$  control register (address 002E16) to "1." An address comparison is performed between the first-byte address data transmitted from the master and the 8-bit slave address stored in the  $I^2C$  address register (address 002C16). At the time of this comparison, an address comparison between the RWB bit of the  $I^2C$  address register (address 002C16) and the  $R/\overline{W}$  bit which is the last bit of the address data transmitted from the master is made. In the 10-bit addressing mode, the RWB bit which is the last bit of the address data not only specifies the direction of communication for control data, but also is processed as an address data bit.

When the first-byte address data agree with the slave address, the AAS bit of the  $\rm I^2C$  status register (address 002D16) is set to "1." After the second-byte address data is stored into the  $\rm I^2C$  data shift register (address 002B16), perform an address comparison between the second-byte data and the slave address by software. When the address data of the 2 bytes agree with the slave address, set the RBW bit of the  $\rm I^2C$  address register (address 002C16) to "1" by software. This processing can make the 7-bit slave address and  $\rm R/\overline{W}$  data agree, which are received after a RESTART condition is detected, with the value of the  $\rm I^2C$  address register (address 002C16). For the data transmission format when the 10-bit addressing format is selected, refer to Figure 31, (3) and (4).

Fig. 30 Structure of I<sup>2</sup>C START/STOP condition control register

Table 9 Recommended set value to START/STOP condition set bits (SSC4-SSC0) for each oscillation frequency

| Oscillation frequency f(XIN) (MHz) | Main clock divide ratio | System clock ¢ (MHz) | START/STOP<br>condition<br>control register | SCL release time (μs) | Setup time<br>(μs)     | Hold time<br>(μs)      |

|------------------------------------|-------------------------|----------------------|---------------------------------------------|-----------------------|------------------------|------------------------|

| 8                                  | 2                       | 4                    | XXX11010                                    | 6.75 μs (27 cycles)   | 3.375 µs (13.5 cycles) | 3.375 μs (13.5 cycles) |