# **ZSSC3170 - SSOP20 and DFN20** Package Dimensions

# **Contents**

| 1 ZSSC     | 3170 SSOP20 Package                                       | 2 |

|------------|-----------------------------------------------------------|---|

| 1.1. SS    | SOP20 Package Dimensions                                  | 2 |

|            | ecommended Printed Circuit Board Layout – SSOP20 Package  |   |

| 1.3. SS    | SOP20 Package Marking and Pin Assignments                 | 3 |

| 2 DFN2     | 0 Package                                                 | 5 |

| 2.1. DF    | FN20 Package Dimensions                                   | 5 |

| 2.2. Fo    | otprint and Wettable Flank Description                    | 6 |

| 2.3. DF    | FN20 Package Marking                                      | 7 |

| 3 Storag   | ge Conditions                                             | 7 |

| 4 Relate   | ed Documents                                              | 8 |

| 5 Docur    | ment Revision History                                     | 8 |

|            | Figures                                                   |   |

| Figure 1.1 | Package View and Dimensions                               | 2 |

| Figure 1.2 | Recommended Printed Circuit Board Layout – SSOP20 Package | 3 |

| -          | Outline Drawing for DFN20 Package with Wettable Flanks    |   |

| _          | Recommended Printed Circuit Board Footprint – DFN20       |   |

|            | Wettable Flank General Concept                            |   |

| Figure 2.4 | Footprint Dimensions for DFN20 with Wettable Flanks       | 7 |

| List of    | Tables                                                    |   |

| Table 1.1  | SSOP20 Package Marking                                    | 3 |

|            | Pin Assignments                                           |   |

| Table 2.1  | DFN20 Package Marking                                     | 7 |

# 1 ZSSC3170 SSOP20 Package

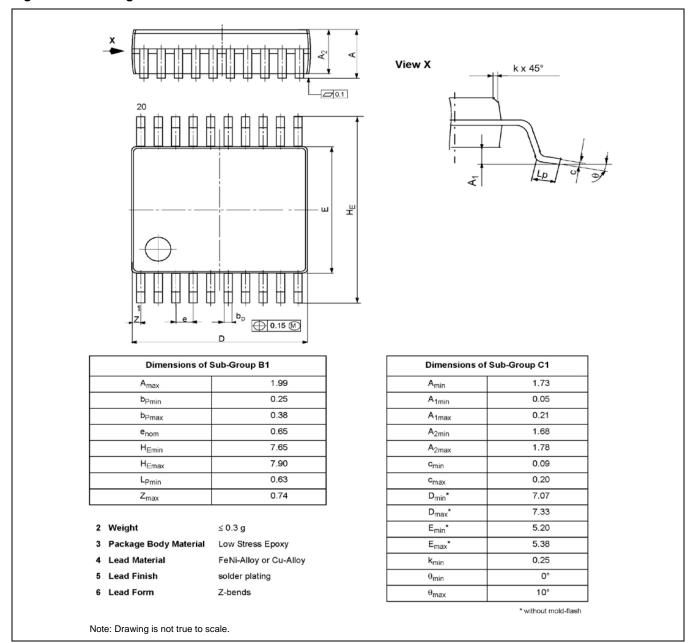

The SSOP20 package is RoHS-compliant and based on JEDEC JEP95: MO-150. Package dimensions are given in millimeters in Figure 1.1.

## 1.1. SSOP20 Package Dimensions

Figure 1.1 Package View and Dimensions

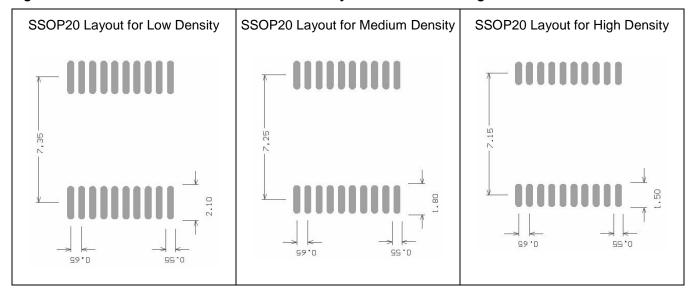

## 1.2. Recommended Printed Circuit Board Layout - SSOP20 Package

The recommended printed circuit board layout for the SSOP20 package depends on the board density.

Figure 1.2 Recommended Printed Circuit Board Layout - SSOP20 Package

## 1.3. SSOP20 Package Marking and Pin Assignments

Table 1.1 SSOP20 Package Marking

| Top Side             |                        | Comments                                                                                                                                                        |

|----------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 <sup>st</sup> Line | ZSSC                   |                                                                                                                                                                 |

| 2 <sup>nd</sup> Line | 3170EA<br>or<br>3170EE | 3170 = Product name; E = Revision Identifier; A= Temperature Range Identifier or 3170 = Product name; E = Revision Identifier; E = Temperature Range Identifier |

| 3 <sup>rd</sup> Line | XXXXXXXX               | Lot number                                                                                                                                                      |

| 4 <sup>th</sup> Line | YYWW                   | YY = Year (e.g., 14 for 2014, 15 for 2015,); WW = Workweek (e.g., 15)                                                                                           |

Table 1.2 Pin Assignments

| SSOP20 Pin | Name  | Description                             | Remarks                        |

|------------|-------|-----------------------------------------|--------------------------------|

| 1          | n.c.  | No connection                           |                                |

| 2          | VDDA  | Positive Analog Supply Voltage          | Power supply                   |

| 3          | VSSA  | Negative Analog Supply Voltage          | Ground                         |

| 4          | SDA   | I2C™* Data I/O                          | Analog I/O, internal pull-up   |

| 5          | SCL   | I <sup>2</sup> C™ Clock                 | Analog input, internal pull-up |

| 6          | VDD   | Positive Digital Supply Voltage         | Power supply                   |

| 7          | HOUT  | PWM High-Side Switch                    | High voltage I/O               |

| 8          | VB    | Positive External Supply Voltage        | High voltage I/O               |

| 9          | VSSE  | External Ground (PWM Modes)             | High voltage I/O               |

| 10         | VSS   | Ground (LIN Mode)                       | Ground                         |

| 11         | LIN   | LIN                                     | LIN high voltage I/O           |

| 12         | LOUT  | PWM Low-Side Switch                     | High voltage I/O               |

| 14         | VBN   | Negative Input Sensor Bridge            | Analog input                   |

| 15         | VBR_B | Negative (Bottom) Bridge Supply Voltage | Analog I/O                     |

| 16         | VBP   | Positive Input Sensor Bridge            | Analog input                   |

| 17         | VTN1  | Temperature Sensor 1                    | Analog I/O                     |

| 18         | VBR_T | Positive (Top) Bridge Supply Voltage    | Analog I/O                     |

| 19         | VTN2  | Temperature Sensor 2                    | Analog I/O                     |

| 20         | n.c.  | No connection                           |                                |

<sup>\*</sup>  $I^2C^{\intercal M}$  is a trademark of NXP.

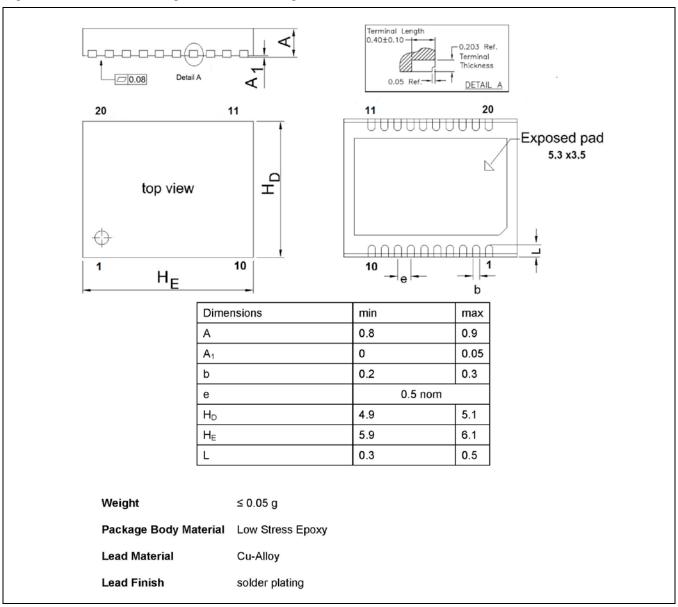

# 2 DFN20 Package

The ZSSC3170 is also available assembled in a DFN20 package (sales codes ZSSC3170EE3R and ZSSC3170EA3R) with wettable flanks. For this package option, the pin assignments are the same as for the SSOP20 package. The DFN20 package is RoHS-compliant.

#### 2.1. DFN20 Package Dimensions

The figure below provides the dimensions in mm for the DFN20 package, which are based on JEDEC MO-229.

Figure 2.1 Outline Drawing for DFN20 Package with Wettable Flanks

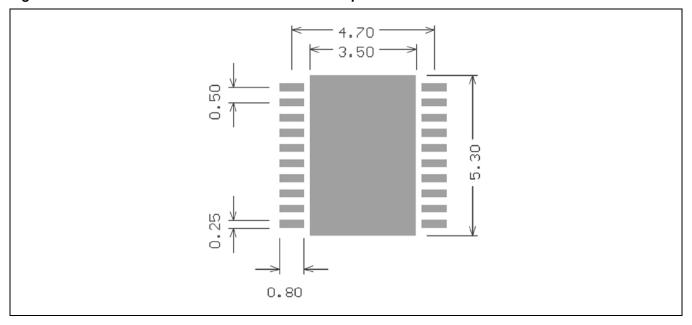

## 2.2. Footprint and Wettable Flank Description

Figure 2.2 Recommended Printed Circuit Board Footprint – DFN20

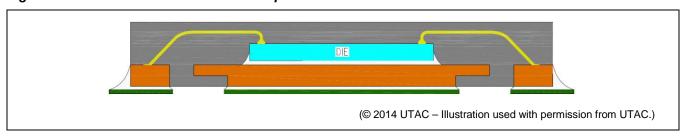

Figure 2.3 illustrates the general concept of the wettable flank (side plating), which allows automatic optical inspection.

Figure 2.3 Wettable Flank General Concept

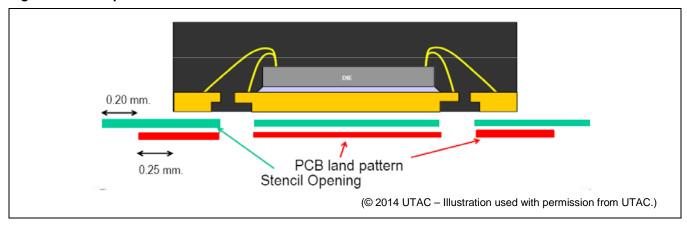

Figure 2.4 illustrates a suggested footprint for printed circuit board (PCB) designs using the ZSSC3170 DFN20.

- The exposed area of the landing pattern is 0.25mm for the unit edge.

- The stencil opening excess is about 0.2mm from the landing pattern.

Figure 2.4 Footprint Dimensions for DFN20 with Wettable Flanks

#### 2.3. DFN20 Package Marking

Table 2.1 DFN20 Package Marking

| Top Side             |                        | Comments                                                                                                                                                        |

|----------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 <sup>st</sup> Line | 3170EA<br>or<br>3170EE | 3170 = Product name; E = Revision Identifier; A= Temperature Range Identifier or 3170 = Product name; E = Revision Identifier; E = Temperature Range Identifier |

| 2 <sup>nd</sup> Line | XXXXX                  | Last five digits of IDT lot number                                                                                                                              |

| 3 <sup>rd</sup> Line | YYWW                   | YY = Year (e.g., 14 for 2014, 15 for 2015,); WW = Workweek (e.g., 15)                                                                                           |

## 3 Storage Conditions

For detailed information about storage conditions requirements, refer to the document *IDT Storage Conditions*. This document is included in all deliveries of packaged parts. It is also available upon request (see contact information on page 8).

# 4 Related Documents

| Document                        |  |

|---------------------------------|--|

| ZSSC3170 Data Sheet             |  |

| ZSSC3170 Functional Description |  |

| IDT Storage Conditions          |  |

Visit the ZSSC3170 product page (<u>www.IDT.com/ZSSC3170</u>) or contact your nearest sales office for the latest version of these documents.

# 5 Document Revision History

| Revision | Date               | Description                                                                                                                                                   |

|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.00     | April 5, 2009      | First release.                                                                                                                                                |

| 2.00     | March 31, 2010     | Update for revision C.                                                                                                                                        |

| 2.10     | July 19, 2010      | Change of product name to ZSSC3170. Change to IDT's new documentation template. Completely revised version.                                                   |

| 2.20     | September 14, 2010 | Update for revision D of the ZSSC3170                                                                                                                         |

| 2.30     | April 11, 2013     | Update for revision E of the ZSSC3170. Pad layout and SSOP20 drawings added.                                                                                  |

| 2.40     | February 12, 2014  | Added wafer drawing and defined scribe line.                                                                                                                  |

| 2.50     | December 3, 2014   | DFN20 package added. Update for contact information.                                                                                                          |

| 2.51     | December 10, 2014  | Correction for definitions of SDA and SCL in Table 1.2. Update for e-mail contact.                                                                            |

| 2.60     | December 8, 2015   | Separation of document into separate technical notes for die dimensions and for package dimensions. Addition of land patterns. Updates for related documents. |

|          | April 1, 2016      | Changed to IDT branding.                                                                                                                                      |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.