# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# アプリケーション・ノート

V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2 32ピット・シングルチップ・マイクロコンピュータ PCIホスト・ブリッジ・マクロ編

V850E/MA1: V850E/MA2: V850E/MA3: V850E/ME2:

μΡD703103A μΡD703108 μΡD703131A μΡD703111A

$\mu$ PD703105A  $\mu$ PD703131AY

μPD703106A μPD703132A

$\mu$ PD703106A(A)  $\mu$ PD703132AY

$\mu$ PD703107A  $\mu$ PD703133A

$\mu$ PD703107A(A)  $\mu$ PD703133AY

$\mu$ PD70F3107A  $\mu$ PD703134A

$\mu PD70F3107A(A)$   $\mu PD703134AY$

μPD70F3134A

μPD70F3134AY

資料番号 U17121JJ1V1AN00 (第1版) 発行年月 May 2004 NS CP(K) (メ モ)

# 目次要約

| 第1章         | <b>各製品の概要</b> 10           |        |

|-------------|----------------------------|--------|

| 第2章         | PCI <b>ホスト・ブリッジ・マクロの概要</b> | <br>29 |

| 第3章         | PCI <b>ホスト・ブリッジ・マクロの仕様</b> | <br>31 |

| <b>第</b> 4章 | FPGA <b>への組み込み構成例</b> 57   |        |

| <b>第</b> 5音 | <b>アプリケーション例</b> 67        |        |

### CMOSデバイスの一般的注意事項

#### 入力端子の印加波形

#### 入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。

CMOSデバイスの入力がノイズなどに起因して、 $V_L$ (MAX.)から $V_H$ (MIN.)までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定な場合はもちろん、 $V_L$ (MAX.)から $V_H$ (MIN.)までの領域を通過する遷移期間中にチャタリングノイズ等が入らないようご使用ください。

#### 未使用入力の処理

#### CMOSデバイスの未使用端子の入力レベルは固定してください。

未使用端子入力については、CMOSデバイスの入力に何も接続しない状態で動作させるのではなく、プルアップかプルダウンによって入力レベルを固定してください。また、未使用の入出力端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVpoまたはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については、その内容を守ってください。

#### 静電気対策

#### MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また,MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 初期化以前の状態

#### 電源投入時, MOSデバイスの初期状態は不定です。

電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象とないます

リセット機能を持つデバイスの電源投入後は、まずリセット動作を実行してください。

注意: µPD703131AY, 703132AY, 703133AY, 703134AY, 70F3134AYは『Cバス・インタフェース回路を内蔵しています。

PCバス・インタフェースを使用される場合には,カスタム・コードをご発注いただく時に,事前にその旨ご申告下さい。申告に基づき,以下の特典が受けられます。

当社のPCバス対応部品をご購入いただくことにより、これらの部品をPCシステムに使用する実施権がフィリップス社PC特許に基づき許諾されることになります。ただし、これらのPCシステムはフィリップス社によって設定されたPC標準規格に合致しているものとします。

Purchase of NEC Electronics I<sup>2</sup>C components conveys a license under the Phillips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Phillips.

本資料に記載しているPCIホスト・ブリッジ・マクロの著作権は、NECエンジニアリング(株)デバイスソリューション事業部 システムインターフェース開発部が保有しています。

Green Hills Software, MULTIは,米国Green Hills Software, Inc. の商標です。

本製品が外国為替及び外国貿易法の規定により規制貨物等(または役務)に該当するか否かは,ユーザ (仕様を決定した者)が判定してください。該当する場合,日本国外に輸出する際には日本国政府の輸 出許可が必要です。

非該当品 : μ PD703103A, 70F3107A, 70F3107A(A),

μ PD703108,

$\mu$  PD70F3134A,

μ PD703111A

ユーザ判定品 : µ PD703105A, 703106A, 703106A(A), 703107A, 703107A(A),

$\mu$  PD703131A, 703131AY, 703132A, 703132AY, 703133A, 703133AY, 703134A, 703134AY

- ◆本資料に記載されている内容は2004年3月現在のもので、今後、予告なく変更することがあります。量 産設計の際には最新の個別データ・シート等をご参照ください。

- ●文書による当社の事前の承諾なしに本資料の転載複製を禁じます。当社は,本資料の誤りに関し,一切 その責を負いません。

- ●当社は,本資料に記載された当社製品の使用に関連し発生した第三者の特許権,著作権その他の知的財産権の侵害等に関し,一切その責を負いません。当社は,本資料に基づき当社または第三者の特許権,著作権その他の知的財産権を何ら許諾するものではありません。

- •本資料に記載された回路,ソフトウエアおよびこれらに関する情報は,半導体製品の動作例,応用例を 説明するものです。お客様の機器の設計において,回路,ソフトウエアおよびこれらに関する情報を使 用する場合には,お客様の責任において行ってください。これらの使用に起因しお客様または第三者に 生じた損害に関し,当社は,一切その責を負いません。

- 当社は,当社製品の品質,信頼性の向上に努めておりますが,当社製品の不具合が完全に発生しないことを保証するものではありません。当社製品の不具合により生じた生命,身体および財産に対する損害の危険を最小限度にするために,冗長設計,延焼対策設計,誤動作防止設計等安全設計を行ってください。

- ●当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定していただく「特定水準」に分類しております。また,各品質水準は,以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認ください。

標準水準:コンピュータ, OA機器, 通信機器, 計測機器, AV機器, 家電, 工作機械, パーソナル機器, 産業用ロボット

特別水準:輸送機器(自動車,電車,船舶等),交通用信号機器,防災・防犯装置,各種安全装置, 生命維持を目的として設計されていない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート,データ・ブック等の資料で特に品質水準の表示がない場合は,標準水準製品であることを表します。意図されていない用途で当社製品の使用をお客様が希望する場合には,事前に当社販売窓口までお問い合わせください。

(注)

- (1)本事項において使用されている「当社」とは、NECエレクトロニクス株式会社およびNECエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいう。

- (2)本事項において使用されている「当社製品」とは,(1)において定義された当社の開発,製造製品をいう。

M8E 02.11

# はじめに

**対象者** このアプリケーション・ノートは, V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2, およびPCIバスの機能を理解し, それらを使用した応用システムを設計するユーザを対象とします。

構 成 このアプリケーション・ノートは大きく分けて次の内容で構成しています。

各製品の概要

PCIホスト・ブリッジ・マクロの概要 PCIホスト・ブリッジ・マクロの仕様 FPGAへの組み込み構成例 アプリケーション例

読み方 このマニュアルの読者には、電気、論理回路、およびマイクロコンピュータに関する一般知識を必要とします。

V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2のハードウエア機能, および電気的特性を知りたいとき

個別の**ユーザーズ・マニュアル ハードウエア編**を参照してください。

V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2の命令機能を知りたいとき 別冊のV850E1 **ユーザーズ・マニュアル** アーキテクチャ編を参照してください。

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記: xxx(端子,信号名称に上線)または

/xxx(信号名称の前に"/"記号)

メモリ・マップのアドレス : 上部 - 上位 , 下部 - 下位 注 : 本文中に付けた注の説明

注意: 気を付けて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数 ... xxxxまたはxxxxB

10進数 ... xxxx 16進数 ... xxxxH

2のべき数を示す接頭語(アドレス空間,メモリ容量) : K(キロ) ...2<sup>10</sup> = 1024

M (メガ) ...2<sup>20</sup> = 1024<sup>2</sup>

G( ギガ $) ...2^{30} = 1024^3$

# **関連資料** 関連資料は暫定版の場合がありますが,この資料では「暫定」の表示をしておりません。 あらかじめご了承ください。

### V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2**に関する資料**

| 資 料 名                                                   | 資料番号    |

|---------------------------------------------------------|---------|

| V850E1 ユーザーズ・マニュアル アーキテクチャ編                             | U14559J |

| V850E/MA1 ユーザーズ・マニュアル ハードウエア編                           | U14359J |

| V850E/MA1 アプリケーション・ノート ハードウエア編                          | U15179J |

| V850E/MA2 ユーザーズ・マニュアル ハードウエア編                           | U14980J |

| V850E/MA3 ユーザーズ・マニュアル ハードウエア編                           | U16397J |

| V850E/ME2 ユーザーズ・マニュアル ハードウエア編                           | U16031J |

| V850E/ME2 アプリケーション・ノート ハードウエア編                          | U16794J |

| V850E/ME2 アプリケーション・ノート USBファンクション・ドライバ編                 | U17069J |

| V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2 アプリケーション・ノート | このマニュアル |

| PCIホスト・ブリッジ・マクロ編                                        |         |

### 開発ツールに関する資料(ユーザーズ・マニュアル)

| 資 料 名                                  | 資料番号           |         |

|----------------------------------------|----------------|---------|

| IE-V850E-MC, IE-V850E-MC-A インサーキット・エミュ | U14487J        |         |

| IE-703107-MC-EM1 インサーキット・エミュレータ・オ      | U14481J        |         |

| IE-V850E1-CD-NW PCMCIAカード型オンチップ・ディル    | バグ・エミュレータ      | U16647J |

| CA850 Ver.2.50 Cコンパイラ・パッケージ            | 操作編            | U16053J |

|                                        | C言語編           | U16054J |

|                                        | アセンブリ言語編       | U16042J |

| PM plus Ver.5.20                       |                | U16934J |

| ID850 Ver.2.50 統合ディバッガ                 | 操作編            | U16217J |

| ID850NW Ver.2.51 統合ディバッガ               | 操作編            | U16454J |

| SM850 Ver.2.40 システム・シミュレータ             | 操作編            | U15182J |

| SM850 Ver.2.00以上 システム・シミュレータ           | 外部部品ユーザ・オープン・イ | U14873J |

|                                        | ンタフェース仕様編      |         |

| RX850 Ver.3.13以上 リアルタイムOS              | 基礎編            | U13430J |

|                                        | インストレーション編     | U13410J |

|                                        | テクニカル編         | U13431J |

| RX850 Pro Ver.3.15 リアルタイムOS            | 基礎編            | U13773J |

|                                        | インストレーション編     | U13774J |

|                                        | テクニカル編         | U13772J |

| RX-NET TCP/IPライブラリ                     |                | U15083J |

| RD850 Ver.3.01 タスク・ディバッガ               |                | U13737J |

| RD850 Pro Ver.3.01 タスク・ディバッガ           | U13916J        |         |

| AZ850 Ver.3.0 システム・パフォーマンス・アナライヤ       | Ť              | U14410J |

| PG-FP4 フラッシュ・メモリ・プログラマ                 |                | U15260J |

# 目 次

| 第1章         | <b>各製品の概要</b> 10                  |

|-------------|-----------------------------------|

|             | 概 説 10<br>特 徵 11                  |

|             |                                   |

|             | オーダ情報 12<br>端子接続図 14              |

|             |                                   |

| 1. 5        | <b>P3마ノロック区</b> 25                |

| <b>第</b> 2章 | PCI <b>ホスト・ブリッジ・マクロの概要</b> 29     |

| 2. 1        | 概 説 29                            |

| 2. 2        | 特 徵 30                            |

|             |                                   |

| <b>第</b> 3章 | PCI <b>ホスト・ブリッジ・マクロの仕様</b> 31     |

|             |                                   |

|             | PCI <b>ホスト・ブリッジ・マクロの内部ブロック</b> 31 |

|             | <b>内部ブロックと信号の関係</b> 32            |

| 3. 3        | <b>端子機能</b> 33                    |

|             | 3.3.1 外部バス・スレーブ・インタフェース端子 33      |

|             | 3. 3. 2 SDRAMバス・インタフェース端子 33      |

|             | 3. 3. 3 PCIバス・インタフェース端子 34        |

| 3. 4        | レジスタ 35                           |

|             | 3. 4. 1 PCI_CONFIG_DATAレジスタ 35    |

|             | 3.4.2 PCI_CONFIG_ADDレジスタ 36       |

|             | 3. 4. 3 PCI_CONTROLレジスタ 37        |

|             | 3. 4. 4 PCI_IO_BASEレジスタ 38        |

|             | 3. 4. 5 PCI_MEM_BASEレジスタ 38       |

|             | 3. 4. 6 PCI_INT_CTLレジスタ 39        |

|             | 3. 4. 7 PCI_ERR_ADDレジスタ 40        |

|             | 3.4.8 SYSTEM_MEM_BASEレジスタ 41      |

|             | 3. 4. 9 SYSTEM_MEM_RANGEレジスタ … 41 |

|             | 3. 4. 10 SDRAM_CTLレジスタ 42         |

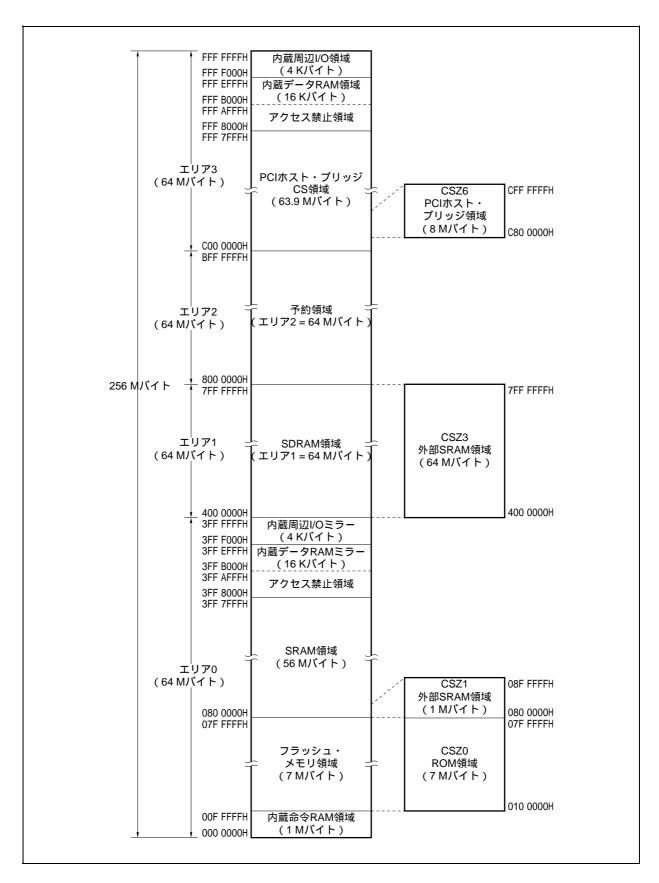

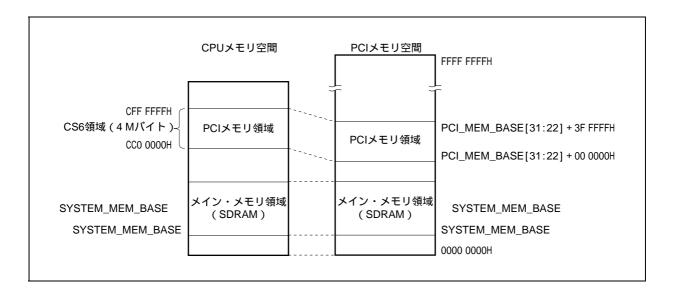

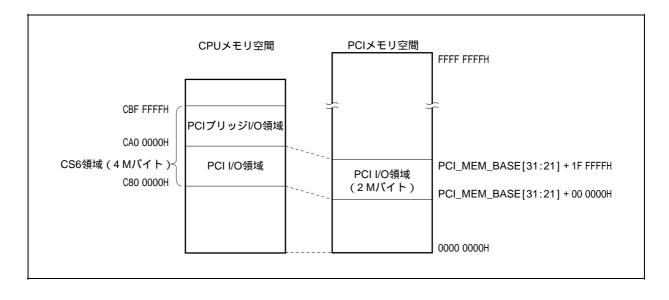

|             | アドレス・マップ 44                       |

|             | PCI <b>ホスト・ブリッジ・マクロ初期化方法</b> 45   |

|             | 外部バス・インタフェースのバス幅について 46           |

| 3. 8        | タイミング 47                          |

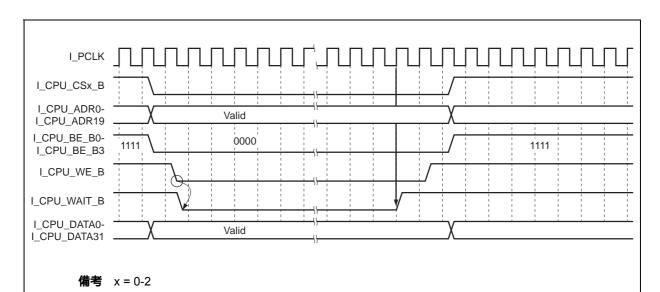

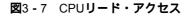

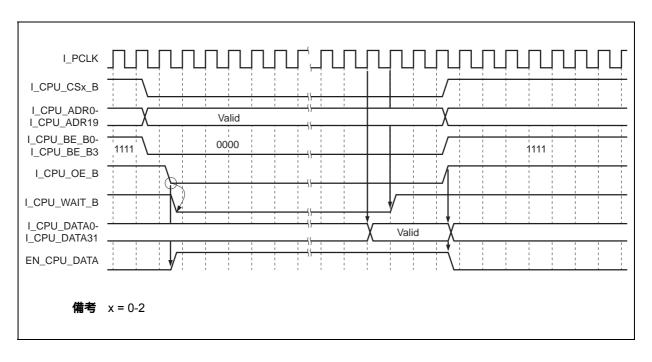

|             | 3. 8. 1 外部バス・インタフェース・タイミング 47     |

|             | 3.8.2 PCIバス・インタフェース・タイミング 50      |

### **第4章** FPGA**への組み込み構成例** ... 57

- 4.1 FPGA**組み込み構成例の条件** ... 57

- 4.2 FPGA トップ階層作成時の留意点 ... 57

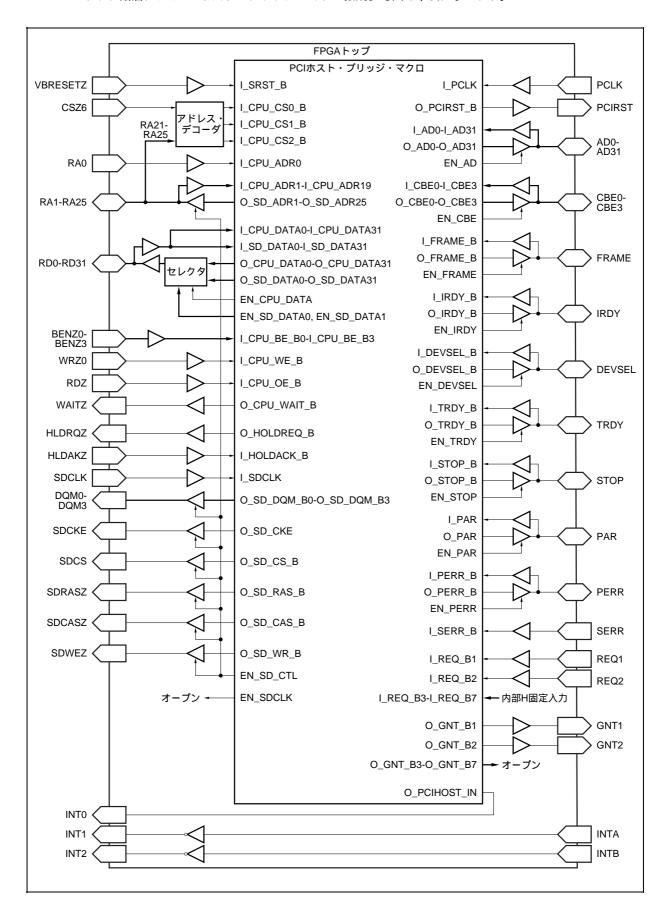

- 4.3 FPGA**トップ接続参考図** ... 58

- 4.4 FPGA**トップ端子機能** ... 59

- 4.4.1 CPUバス・スレーブ・インタフェース端子 ... 59

- 4.4.2 SDRAMバス・インタフェース端子 ... 59

- 4.4.3 PCIバス・インタフェース端子 ... 60

- 4.5 FPGA トップ端子接続図 ... 61

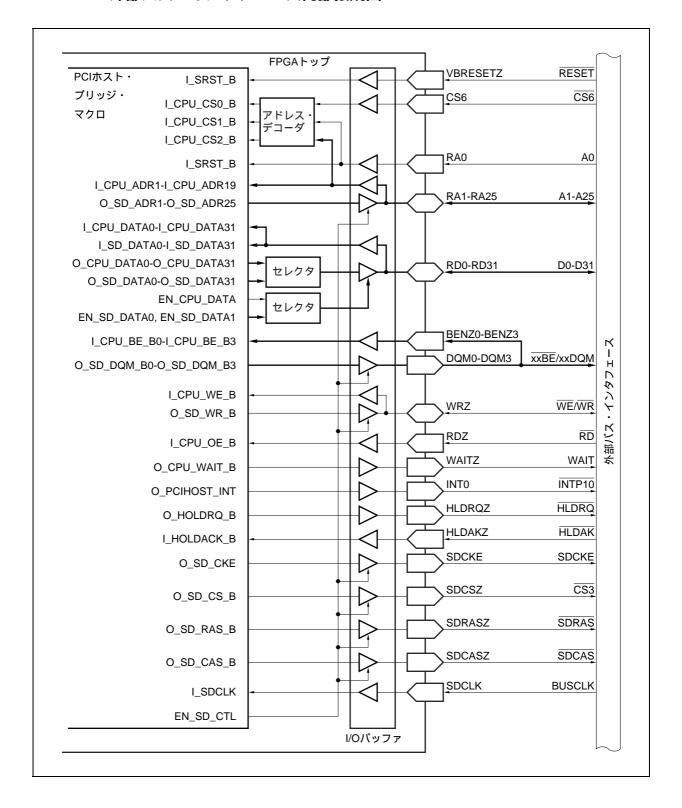

- 4.5.1 外部バス・インタフェース内部接続図 ... 61

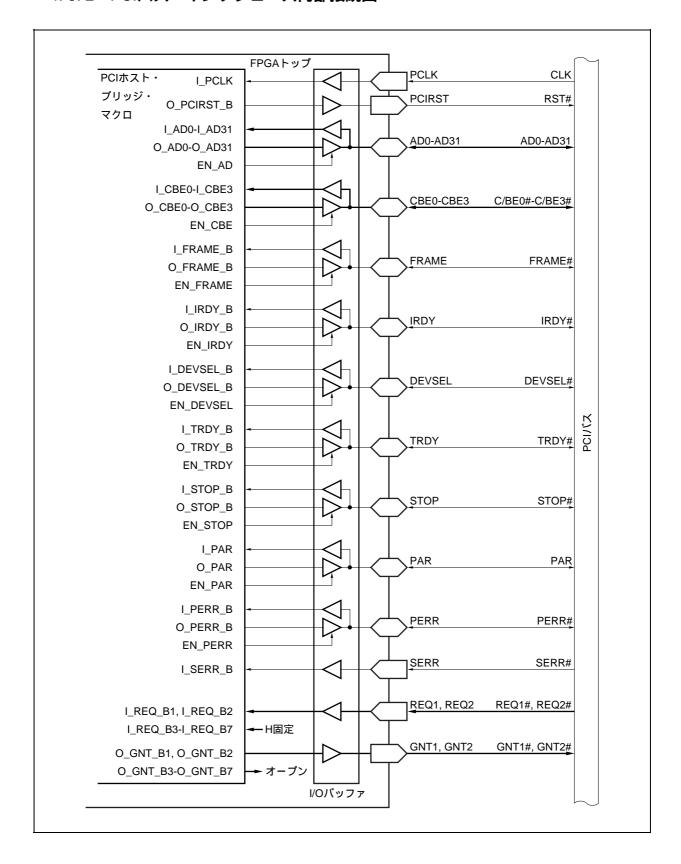

- 4.5.2 PCIバス・インタフェース内部接続図 ... 62

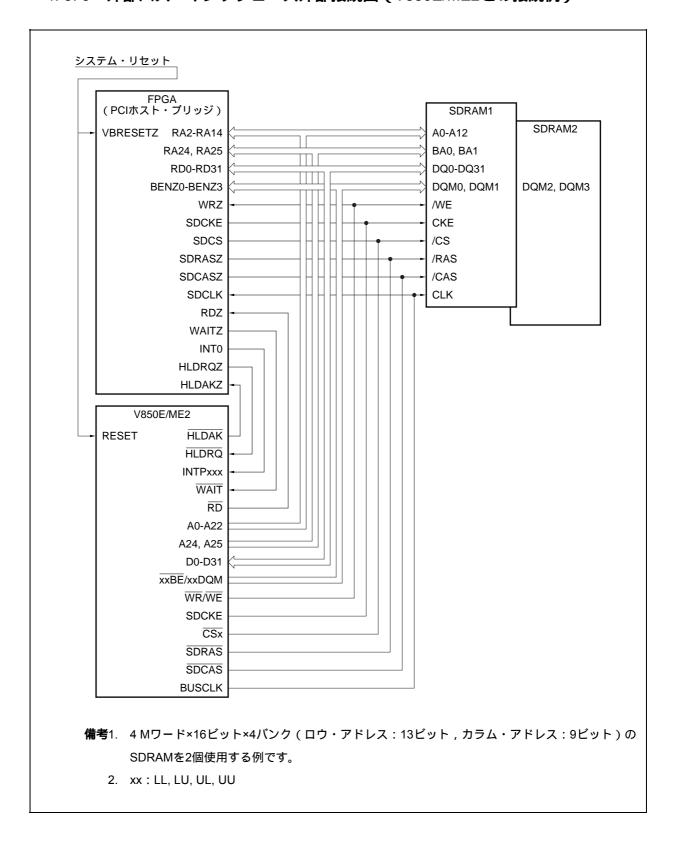

- 4.5.3 外部バス・インタフェース外部接続図(V850E/ME2との接続例) ... 63

- 4.5.4 PCIバス・インタフェース外部接続図 ... 64

- 4.6 FPGA**設計における注意点** ... 65

- 4.6.1 FPGA Fitting設計について ... 65

- 4. 6. 2 PCIバス・インタフェースTiming Parameterについて (PCI CLK = 33 MHzの制約条件として) ... 65

- 4.6.3 SDRAMインタフェース・タイミング ... 66

### 第5章 アプリケーション例 ... 67

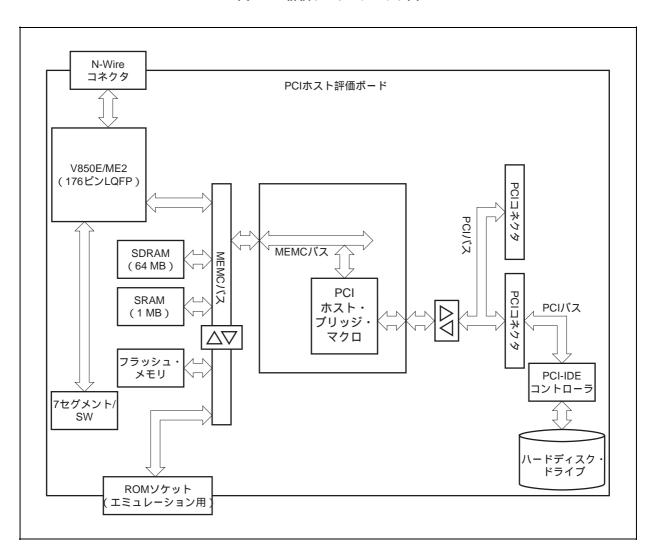

- 5.1 評価ボードのブロック図 ... 67

- 5.2 評価ボードの仕様 ... 68

- 5.3 評価ボードの接続回路例 ... 69

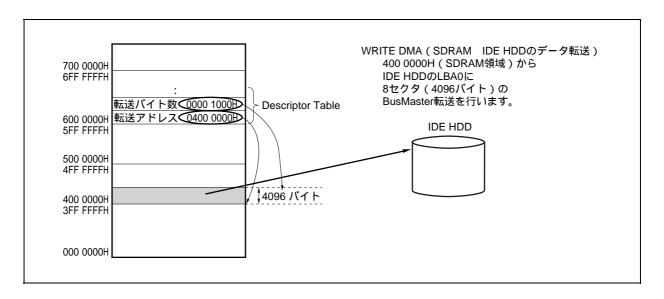

- 5.4 評価ボードのメモリ空間 ... 70

- 5.5 **サンプル・プログラム例** ... 72

- 5.5.1 開発ツール ... 72

- 5.5.2 プログラムの構成 ... 72

- 5. 5. 3 V850E/ME2 PCIホスト・ブリッジ・マクロ初期化サンプル・プログラム・リスト ... 73

- 5.5.4 PCIコンフィギュレーション空間アクセス・サンプル・プログラム・リスト ... 77

- 5. 5. 5 IDE HDDアクセス・サンプル・プログラム・リスト ... 81

# 第1章 各製品の概要

V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2は, NECエレクトロニクスのシングルチップ・マイクロコン ピュータ「V850シリーズ」の1製品です。この章では, 各製品の概要を簡単に説明します。

### 1.1 概 説

V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2は,システム・オン・チップ時代のシステムLSIの核となる ASIC用32ビットRISC命令型CPUコア「V850E1 CPU」を搭載した32ビット・シングルチップ・マイクロコンピュータです。内蔵メモリや,各種メモリ・コントローラ,DMAコントローラ,タイマ/カウンタ,シリアル・インタフェース,A/Dコンバータなどの周辺機能を内蔵し,大容量データ処理と高度なリアルタイム制御を実現します。

# 1.2 特 徵

| 愛 称          |             | V850E/MA1   |        |                  | V850E/MA2 |                 | V850E/MA3 |                    | V850E/ME2 |                     |                   |                   |            |        |                   |                 |                          |  |

|--------------|-------------|-------------|--------|------------------|-----------|-----------------|-----------|--------------------|-----------|---------------------|-------------------|-------------------|------------|--------|-------------------|-----------------|--------------------------|--|

| 最大動作周波数      |             |             | 50 MHz |                  | 40 MHz    | 80 MI           | 30 MHz    |                    |           | 150 MHz             |                   |                   |            |        |                   |                 |                          |  |

|              |             | マスク         | RON    | Л                | -         | 12              | 8         | 256                | -         | -                   | 25                | 6                 | 5′         | 12     | -                 | -               |                          |  |

|              | 7           | フラッ         | シュ     | ・メモリ             |           | -               |           |                    | 256       | -                   |                   |                   | -          |        | 512               | -               |                          |  |

| 内部メモ         | Kバイト        | RAM         |        |                  | 4         | 4               |           | 10                 |           | 4                   | 16                | 32                | 16         | 3      | 32                | 命令RAM: 12       | 28                       |  |

| ₹.           | Ċ           |             |        |                  |           |                 |           |                    |           |                     |                   |                   |            |        |                   | データRAM:         | 16                       |  |

| ++           | フツ          | シュ (        | Kバイ    | `F)              |           |                 |           |                    |           |                     | _                 |                   |            |        |                   | 命令キャッシ          | ュ:8                      |  |

|              | バス          | ス・タ         | イプ     |                  | セパ        | レート             |           |                    |           | セパレート               | セパ                | ノート               | . /        |        |                   | セパレート           |                          |  |

| ĸ            |             |             |        |                  |           |                 |           |                    |           |                     | マル                | チプレ               | クス         |        |                   |                 |                          |  |

| 部バス          |             | ドレス         |        | ζ                | 26ビ       | ット              |           |                    |           | 25ビット               | 26ビ               | ット                |            |        |                   | 26ビット           |                          |  |

| 外            | デ-          | -タ・.        | バス     |                  | 8/16      | ビット             |           |                    |           | 8/16ビット             | 8/16 (            | ごット               |            |        |                   | 16/32ビット        |                          |  |

|              | チャ          | ップ・         | セレク    | 7ト信号             | 8本        |                 |           |                    |           | 4本                  | 8本                |                   |            |        |                   | 8本              |                          |  |

| J Ŧ          | IJ          | ・コン         |        |                  | SDRA      | M, EDC          | DRAN      | /I, SRAI           | Mなど       | SDRAM, SRAMなる       | ど                 |                   |            |        |                   |                 |                          |  |

| 割り           | ) 込         | み           |        | 外部 <sup>注1</sup> | 17 (      | 17)             |           |                    |           | 4(4)                | 26 (2             | 26)               |            |        |                   | 40 (31)         |                          |  |

|              |             |             |        | 内部               | 41        |                 |           |                    |           | 27                  | 49                |                   |            |        |                   | 59              |                          |  |

| DSF          | >           | 32×         | 32     | 64               | 20-40     | ) ns ( 5        | 50 M⊦     | lz)                |           | 25-50 ns ( 40 MHz ) | 12.5-             | 25 ns             | (801)      | MHz)   | )                 | 6.7-13.3 ns ( ' | 150 MHz )                |  |

| 機能           | S S         | 32 ×        | 32+    | 32 32            | 60 ns     | s (50 N         | ИHz)      |                    |           | 75 ns ( 40 MHz )    | 37.5              | ns (8             | 0 MHz      | z)     |                   | 20 ns ( 150 M   | ИHz)                     |  |

|              | TM          | С           |        |                  | 4 ch      |                 |           |                    |           | 2 ch                |                   |                   | -          |        |                   | 6 ch            |                          |  |

| 41           | TM          | Р           |        |                  |           |                 | -         |                    |           | -                   | 3 ch              | 3 ch              |            |        |                   | -               |                          |  |

| _            | TM          | Q           |        |                  |           |                 | -         |                    |           | -                   | 1 ch              |                   |            |        | -                 |                 |                          |  |

| ير<br>ٽ      | イン          | ノターノ        | いル・    | タイマ              | 4 ch      |                 |           | 4 ch               | 4 ch      |                     |                   |                   | 4 ch       |        |                   |                 |                          |  |

|              |             |             |        | カウンタ             | -         |                 |           | -                  | 1 ch      |                     |                   |                   | 2 ch       |        |                   |                 |                          |  |

| ウォ           | _           | チドッ         | グ・     | タイマ              | -         |                 | -         | 1 ch               |           |                     |                   |                   | -          |        |                   |                 |                          |  |

|              | Κ           | CSI         |        |                  | 1 ch      |                 |           |                    |           | -                   |                   |                   | -          |        |                   | 1 ch            |                          |  |

| <u> ሀ</u> ፖル | 7 1         | UART        | •      |                  | 1 ch      |                 | -         |                    |           | -                   |                   |                   | 1 ch       |        |                   |                 |                          |  |

| シリ           | ンタ          | CSI/U       |        |                  | 2 ch      |                 | 2 ch      | 3 ch               |           |                     |                   | 1 ch              |            |        |                   |                 |                          |  |

|              | 7           | UART        |        |                  | -         |                 | -         | 1 ch <sup>注2</sup> |           | -                   |                   |                   |            |        |                   |                 |                          |  |

| -            |             | ⊦A/D:       |        |                  | 8 ch      |                 | 4 ch      | 8 ch               |           |                     |                   | 8 ch              |            |        |                   |                 |                          |  |

| 8ビ           | ット          | -D/A⊐       | ンバ     | ータ               | -         |                 | -         | 2 ch               | 2 ch      |                     |                   | -                 |            |        |                   |                 |                          |  |

| DM.          | Α⊐          | ントロ         | ーラ     |                  | 4 ch      |                 | 4 ch      | 4 ch               |           |                     | 4 ch              |                   |            |        |                   |                 |                          |  |

| ポー           | -           | (           | CMO    | S入力              | 9         |                 |           |                    |           | 5                   | 11                |                   |            |        |                   | 7               |                          |  |

|              |             | (           | CMOS   | S入出力             | 106       |                 |           |                    |           | 74                  | 101               |                   |            |        | 77                |                 |                          |  |

| ディ           | バ!          | グ機能         |        |                  |           |                 | -         |                    |           | -                   | あり(RUN,ブレーク)      |                   | 7)         | あり(RUN | •                 |                 |                          |  |

|              |             |             |        |                  |           |                 |           |                    |           |                     |                   |                   |            | ク,トレース |                   |                 |                          |  |

| その           | 他           | 周辺機         | 能      |                  | PWM       | 1 × 2 ch        | 1         |                    |           | - ROMコレクション機能       |                   | E<br>E            | USBファンク    | ション,   |                   |                 |                          |  |

|              |             |             |        |                  |           |                 |           |                    |           |                     |                   |                   |            |        |                   | SSCG,           |                          |  |

|              |             |             |        |                  | 0.0       | 0.01:           |           |                    |           |                     | 0.0               | <u> </u>          | , <u>.</u> | , ,    |                   | PWM x 2 ch      |                          |  |

| 電源           | 電           | 土           |        |                  | 3.0 ~     | 3.6 V           |           |                    |           |                     | 2.3 ~ :           |                   |            |        |                   | 1.5 V (内部)      |                          |  |

| ) 보 #        |             | <del></del> | 7 -    | KTVP \           | F00       | \^/             |           |                    |           | 446                 | 3.0 ~             |                   | はかり        | )      |                   | 3.3 V (外部)      |                          |  |

| -            |             |             | スクド    | 饭TYP.)           | 528 r     |                 | -D / 1    | 00 . 00            |           | 416 mW              |                   | 575 mW            |            |        | 20.)              | 200 mW          |                          |  |

| ハッ           | <i>iT</i> . | ージ          |        |                  |           | ピンLQI           |           |                    |           | 100ピンLQFP           | 144ピンLQFP (20×20) |                   |            |        | 176ピンLQFP (20×20) |                 |                          |  |

| 舌 かか         | - E         | 田油井         |        |                  |           | ピンFB(<br>- 40 ~ |           | 13 X 13            | , ,       | (14×14)             | 1016              | 161ピンFBGA (13×13) |            | 13)    | 240ピンFBGA(16×16)  |                 |                          |  |

| 里川竹          | - /司        | 囲温度         |        |                  | IA =      | - 40 ~          | ⊤ ძე      |                    |           |                     |                   |                   |            |        |                   |                 | (133 MHz時)<br>(150 MHz時) |  |

|              |             |             |        |                  |           |                 |           |                    |           |                     |                   |                   |            |        |                   | IA = -40 - +10  | ( IOO IVII IZI时)         |  |

注1. ( )内は,STOPモード解除可能な外部割り込み本数です。

2. I<sup>2</sup>C内蔵品 (Y品)だけ有効です。

# 1.3 オーダ情報

### (1) V850E/MA1

| 品名                           | パッケージ                            | 内蔵ROM               |

|------------------------------|----------------------------------|---------------------|

| $\mu$ PD703103AGJ-UEN        | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | ROMレス               |

| $\mu$ PD703105AGJ-xxx-UEN    | u .                              | マスクROM(128 Kバイト)    |

| $\mu$ PD703106AGJ-xxx-UEN    | u .                              | II .                |

| $\mu$ PD703106AGJ(A)-xxx-UEN | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | "                   |

| $\mu$ PD703106AF1-xxx-EN4    | 161ピン・プラスチックFBGA(13×13)          | II .                |

| $\mu$ PD703107AGJ-xxx-UEN    | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | マスクROM ( 256 Kバイト ) |

| $\mu$ PD703107AGJ(A)-xxx-UEN | <i>u</i>                         | "                   |

| $\mu$ PD703107AF1-xxx-EN4    | 161ピン・プラスチックFBGA(13×13)          | II .                |

| $\mu$ PD70F3107AGJ-UEN       | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | フラッシュ・メモリ (512Kバイト) |

| $\mu$ PD70F3107AGJ(A)-UEN    | <i>u</i>                         | "                   |

| μ PD70F3107AF1-EN4           | 161ピン・プラスチックFBGA(13×13)          | II .                |

| (2) V850E/MA2                |                                  |                     |

| 品名                           | パッケージ                            | 内蔵ROM               |

| μ PD703108GC-8EU             | 100ピン・プラスチックLQFP(ファインピッチ)(14 ×   | (14) ROMレス          |

### (3) V850E/MA3

| 品 名                        | パッケージ                            | 内蔵ROM              |

|----------------------------|----------------------------------|--------------------|

| $\mu$ PD703131AGJ-xxx-UEN  | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | マスクROM( 256 Kバイト ) |

| μ PD703131AF1-xxx-EN4      | 161ピン・プラスチックFBGA(13×13)          | "                  |

| $\mu$ PD703131AYGJ-xxx-UEN | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | "                  |

| μ PD703131AYF1-xxx-EN4     | 161ピン・プラスチックFBGA(13×13)          | <i>II</i>          |

| $\mu$ PD703132AGJ-xxx-UEN  | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | "                  |

| $\mu$ PD703132AF1-xxx-EN4  | 161ピン・プラスチックFBGA(13×13)          | <i>II</i>          |

| $\mu$ PD703132AYGJ-xxx-UEN | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | <i>II</i>          |

| μ PD703132AYF1-xxx-EN4     | 161ピン・プラスチックFBGA(13×13)          | <i>II</i>          |

| $\mu$ PD703133AGJ-xxx-UEN  | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | マスクROM( 512 Kバイト ) |

| $\mu$ PD703133AF1-xxx-EN4  | 161ピン・プラスチックFBGA(13×13)          | "                  |

| $\mu$ PD703133AYGJ-xxx-UEN | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | "                  |

| $\mu$ PD703133AYF1-xxx-EN4 | 161ピン・プラスチックFBGA(13×13)          | "                  |

| $\mu$ PD703134AGJ-xxx-UEN  | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | "                  |

| $\mu$ PD703134AF1-xxx-EN4  | 161ピン・プラスチックFBGA(13×13)          | "                  |

| $\mu$ PD703134AYGJ-xxx-UEN | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | "                  |

| $\mu$ PD703134AYF1-xxx-EN4 | 161ピン・プラスチックFBGA(13×13)          | "                  |

| $\mu$ PD70F3134AGJ-UEN     | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | フラッシュ・メモリ(512Kバイト) |

| $\mu$ PD70F3134AF1-EN4     | 161ピン・プラスチックFBGA(13×13)          | "                  |

| $\mu$ PD70F3134AYGJ-UEN    | 144ピン・プラスチックLQFP(ファインピッチ)(20×20) | "                  |

| $\mu$ PD70F3134AYF1-EN4    | 161ピン・プラスチックFBGA(13×13)          | "                  |

|                            |                                  |                    |

### (4) V850E/ME2

| 品 名                      | パッケージ                            | 最高動作周波数 |

|--------------------------|----------------------------------|---------|

| $\mu$ PD703111AGM-10-UEU | 176ピン・プラスチックLQFP(ファインピッチ)(24×24) | 100 MHz |

| $\mu$ PD703111AGM-13-UEU | II .                             | 133 MHz |

| $\mu$ PD703111AGM-15-UEU | II .                             | 150 MHz |

| $\mu$ PD703111AF1-10-GA3 | 240ピン・プラスチックFBGA(16×16)          | 100 MHz |

| $\mu$ PD703111AF1-13-GA3 | II .                             | 133 MHz |

| $\mu$ PD703111AF1-15-GA3 | II .                             | 150 MHz |

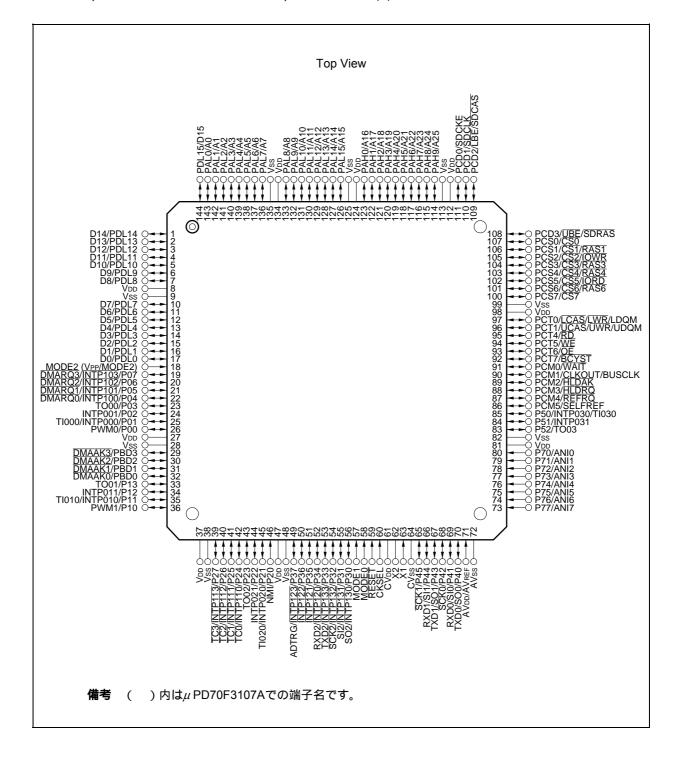

### 1.4 端子接続図

#### (1) V850E/MA1

・144ピン・プラスチックLQFP (ファインピッチ) (20×20)

$\mu$  PD703103AGJ-UEN  $\mu$  PD703106AGJ(A)-xxx-UEN  $\mu$  PD $\pi$ 03105AGJ-xxx-UEN  $\mu$  PD $\pi$ 03107AGJ-xxx-UEN  $\mu$  PD $\pi$ 03107AGJ-xxx-UEN  $\mu$  PD $\pi$ 03107AGJ-xxx-UEN

$\mu$  PD703106AGJ-xxx-UEN  $\mu$  PD703107AGJ(A)-xxx-UEN

$\mu$  PD70F3107AGJ-UEN  $\mu$  PD70F3107AGJ(A)-UEN

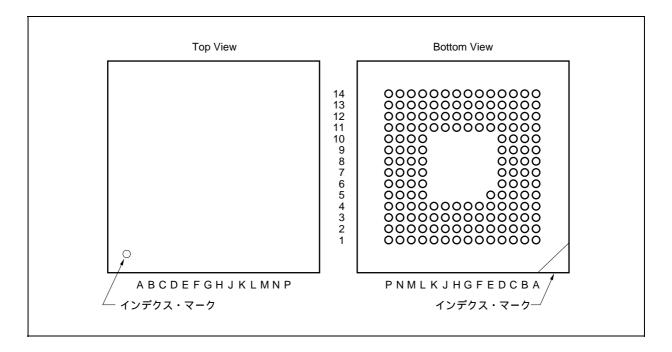

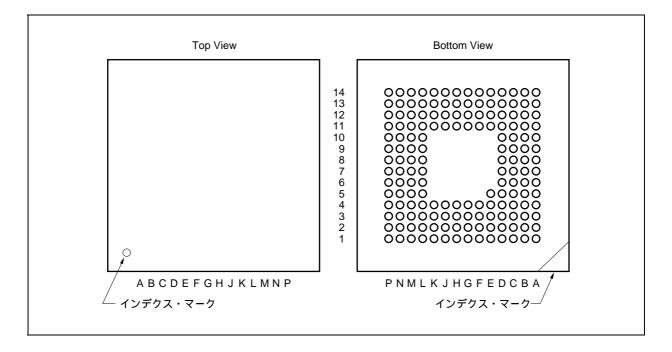

・161ピン・プラスチックFBGA (13×13)

$\mu$  PD703106AF1-xxx-EN4  $\mu$  PD703107AF1-xxx-EN4  $\mu$  PD70F3107AF1-EN4

(1/2)

| ピン番号 | 名 称             | ピン番号 | 名 称             | ピン番号 | 名 称           |

|------|-----------------|------|-----------------|------|---------------|

| A1   | -               | В9   | A18/PAH2        | D3   | D14/PDL14     |

| A2   | D15/PDL15       | B10  | A21/PAH5        | D4   | A3/PAL3       |

| A3   | A2/PAL2         | B11  | A25/PAH9        | D5   | A6/PAL6       |

| A4   | A5/PAL5         | B12  | SDCLK/PCD1      | D6   | A10/PAL10     |

| A5   | -               | B13  | CS1/RAS1/PCS1   | D7   | A14/PAL14     |

| A6   | A9/PAL9         | B14  | -               | D8   | A16/PAH0      |

| A7   | A12/PAL12       | C1   | -               | D9   | A20/PAH4      |

| A8   | A15/PAL15       | C2   | D9/PDL9         | D10  | A23/PAH7      |

| A9   | A17/PAH1        | C3   | D13/PDL13       | D11  | SDCKE/PCD0    |

| A10  | -               | C4   | A1/PAL1         | D12  | CS0/PCS0      |

| A11  | A24/PAH8        | C5   | A7/PAL7         | D13  | CS5/IORD/PCS5 |

| A12  | V <sub>DD</sub> | C6   | V <sub>DD</sub> | D14  | -             |

| A13  | LBE/SDCAS/PCD2  | C7   | A11/PAL11       | E1   | D5/PDL5       |

| A14  | UBE/SDRAS/PCD3  | C8   | V <sub>DD</sub> | E2   | D7/PDL7       |

| B1   | -               | C9   | A19/PAH3        | E3   | D8/PDL8       |

| B2   | D12/PDL12       | C10  | A22/PAH6        | E4   | D11/PDL11     |

| В3   | A0/PAL0         | C11  | Vss             | E5   | -             |

| B4   | A4/PAL4         | C12  | CS3/RAS3/PCS3   | E11  | CS6/RAS6/PCS6 |

| B5   | Vss             | C13  | CS2/IOWR/PCS2   | E12  | CS4/RAS4/PCS4 |

| В6   | A8/PAL8         | C14  | -               | E13  | CS7/PCS7      |

| B7   | A13/PAL13       | D1   | Vss             | E14  | Vss           |

| B8   | Vss             | D2   | D10/PDL10       | F1   | D2/PDL2       |

(2/2)

| ピン番号 | 名 称                             | ピン番号 | 名 称               | ピン番号 | 名 称               |

|------|---------------------------------|------|-------------------|------|-------------------|

| F2   | D3/PDL3                         | K2   | Vss               | M12  | ANI6/P76          |

| F3   | D4/PDL4                         | K3   | DMAAK1/PBD1       | M13  | ANI5/P75          |

| F4   | V <sub>DD</sub>                 | K4   | DMAAK3/PBD3       | M14  | -                 |

| F11  | RD/PCT4                         | K11  | ANI1/P71          | N1   | -                 |

| F12  | V <sub>DD</sub>                 | K12  | ANI0/P70          | N2   | PWM1/P10          |

| F13  | LCAS/LWR/LDQM/PCT0              | K13  | Vss               | N3   | TC3/INTP113/P27   |

| F14  | UCAS/UWR/UDQM/PCT1              | K14  | V <sub>DD</sub>   | N4   | TC0/INTP110/P24   |

| G1   | MODE2 ( MODE2/V <sub>PP</sub> ) | L1   | -                 | N5   | NMI/P20           |

| G2   | DMARQ3/INTP103/P07              | L2   | DMAAK2/PBD2       | N6   | ADTRG/INTP123/P37 |

| G3   | D0/PDL0                         | L3   | TI010/INTP010/P11 | N7   | TXD2/INTP133/P33  |

| G4   | D6/PDL6                         | L4   | DMAAK0/PBD0       | N8   | SO2/INTP130/P30   |

| G11  | WAIT/PCM0                       | L5   | TO02/P23          | N9   | X2                |

| G12  | WE/PCT5                         | L6   | V <sub>DD</sub>   | N10  | CVss              |

| G13  | BCYST/PCT7                      | L7   | INTP122/P36       | N11  | SCK0/P42          |

| G14  | OE/PCT6                         | L8   | SI2/INTP131/P31   | N12  | AVDD/AVREF        |

| H1   | DMARQ2/INTP102/P06              | L9   | RESET             | N13  | AVss              |

| H2   | DMARQ1/INTP101/P05              | L10  | TXD1/SO1/P43      | N14  | -                 |

| Н3   | DMARQ0/INTP100/P04              | L11  | ANI7/P77          | P1   | V <sub>DD</sub>   |

| H4   | D1/PDL1                         | L12  | ANI4/P74          | P2   | Vss               |

| H11  | REFRQ/PCM4                      | L13  | ANI3/P73          | P3   | TC1/INTP111/P25   |

| H12  | HLDRQ/PCM3                      | L14  | ANI2/P72          | P4   | INTP021/P22       |

| H13  | HLDAK/PCM2                      | M1   | -                 | P5   | -                 |

| H14  | CLKOUT/BUSCLK/PCM1              | M2   | INTP011/P12       | P6   | INTP121/P35       |

| J1   | TO00/P03                        | М3   | TO01/P13          | P7   | SCK2/INTP132/P32  |

| J2   | TI000/INTP000/P01               | M4   | TC2/INTP112/P26   | P8   | MODE1             |

| J3   | V <sub>DD</sub>                 | M5   | TI020/INTP020/P21 | P9   | CV <sub>DD</sub>  |

| J4   | INTP001/P02                     | M6   | Vss               | P10  | X1                |

| J11  | TO03/P52                        | M7   | RXD2/INTP120/P34  | P11  | -                 |

| J12  | TI030/INTP030/P50               | M8   | MODE0             | P12  | RXD1/SI1/P44      |

| J13  | SELFREF/PCM5                    | M9   | CKSEL             | P13  | RXD0/SI0/P41      |

| J14  | INTP031/P51                     | M10  | SCK1/P45          | P14  | -                 |

| K1   | PWM0/P00                        | M11  | TXD0/SO0/P40      |      |                   |

**備考**1. A1, A5, A10, B1, B14, C1, C14, D14, E5, L1, M1, M14, N1, N14, P5, P11, P14の端子は,オープンにしてください。

2. ( ) は*μ* PD70F3107Aでの端子名です。

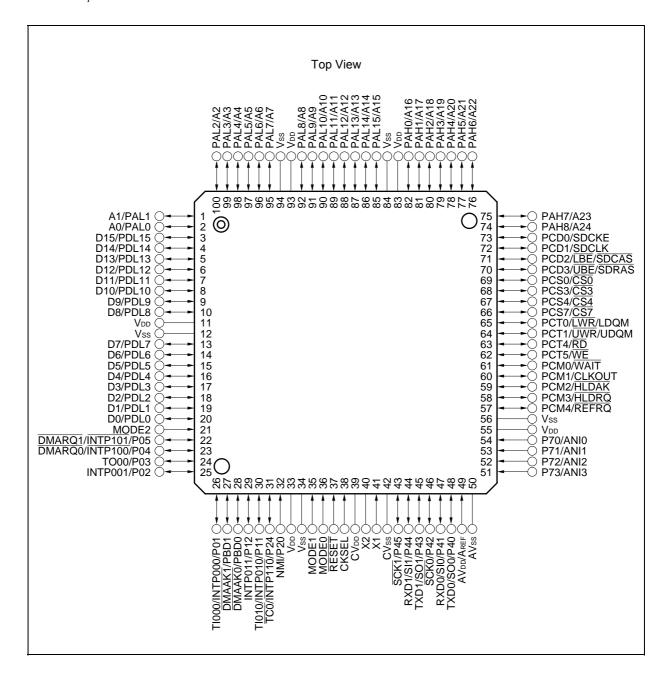

#### (2) V850E/MA2

・100ピン・プラスチックLQFP(ファインピッチ)(14 × 14) μ PD703108GC-8EU

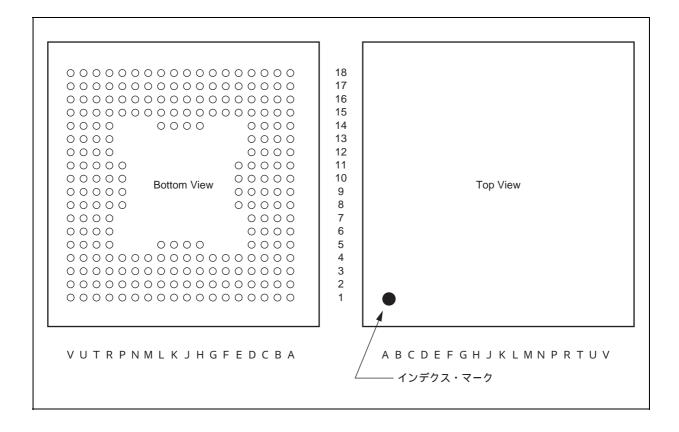

#### (3) V850E/MA3

・144ピン・プラスチックLQFP (ファインピッチ) (20×20)

$\mu$  PD703131AGJ-xxx-UEN  $\mu$  PD703133AGJ-xxx-UEN  $\mu$  PD7053134AGJ-UEN  $\mu$  PD703131AYGJ-xxx-UEN  $\mu$  PD703133AYGJ-xxx-UEN  $\mu$  PD703134AGJ-uEN  $\mu$  PD703134AGJ-xxx-UEN

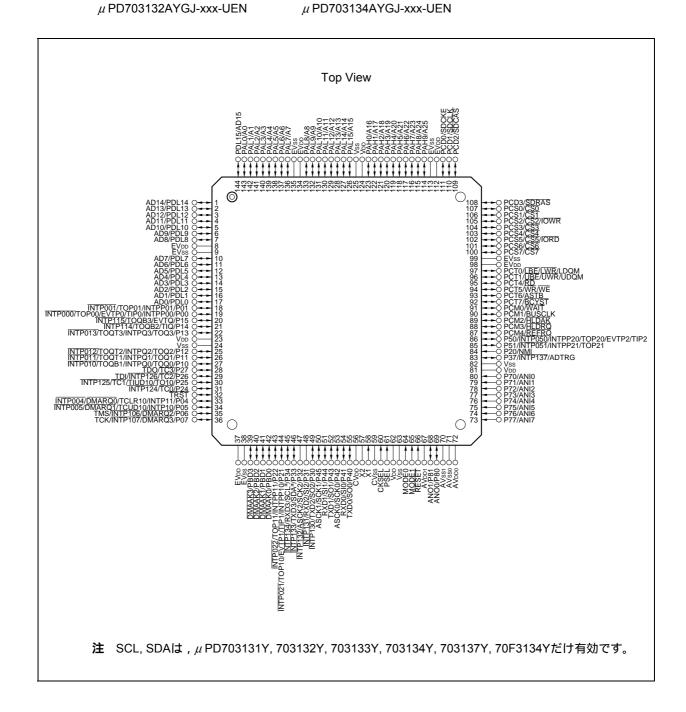

#### ・161ピン・プラスチックFBGA (13×13)

```

μ PD703131AF1-EN4 μ PD703133AF1-xxx-EN4 μ PD70F3134AF1-EN4 μ PD703131AYF1-xxx-EN4 μ PD703133AYF1-xxx-EN4 μ PD703132AF1-xxx-EN4 μ PD703134AF1-xxx-EN4 μ PD703134AYF1-xxx-EN4 μ PD703134AYF1-xxx-EN4

```

(1/2)

| ピン番号 | 名 称              | ピン番号 | 名 称              | ピン番号 | 名 称           |

|------|------------------|------|------------------|------|---------------|

| A1   | EVss             | В8   | Vss              | D1   | EVss          |

| A2   | AD15/PDL15       | В9   | A18/PAH2         | D2   | AD10/PDL10    |

| A3   | A2/PAL2          | B10  | A21/PAH5         | D3   | AD14/PDL14    |

| A4   | A5/PAL5          | B11  | A25/PAH9         | D4   | A3/PAL3       |

| A5   | EVss             | B12  | SDCLK/PCD1       | D5   | A6/PAL6       |

| A6   | A9/PAL9          | B13  | CS1/PCS1         | D6   | A10/PAL10     |

| A7   | A12/PAL12        | B14  | EVss             | D7   | A14/PAL14     |

| A8   | A15/PAL15        | C1   | EVss             | D8   | A16/PAH0      |

| A9   | A17/PAH1         | C2   | AD9/PDL9         | D9   | A20/PAH4      |

| A10  | -                | C3   | AD13/PDL13       | D10  | A23/PAH7      |

| A11  | A24/PAH8         | C4   | A1/PAL1          | D11  | SDCKE/PCD0    |

| A12  | EV <sub>DD</sub> | C5   | A7/PAL7          | D12  | CS0/PCS0      |

| A13  | SDCAS/PCD2       | C6   | EV <sub>DD</sub> | D13  | CS5/IORD/PCS5 |

| A14  | SDRAS/PCD3       | C7   | A11/PAL11        | D14  | EVss          |

| B1   | EVss             | C8   | V <sub>DD</sub>  | E1   | AD5/PDL5      |

| B2   | AD12/PDL12       | С9   | A19/PAH3         | E2   | AD7/PDL7      |

| В3   | A0/PAL0          | C10  | A22/PAH6         | E3   | AD8/PDL8      |

| B4   | A4/PAL4          | C11  | EVss             | E4   | AD11/PDL11    |

| B5   | EVss             | C12  | CS3/PCS3         | E5   | -             |

| В6   | A8/PAL8          | C13  | CS2/IOWR/PCS2    | E11  | CS6/PCS6      |

| В7   | A13/PAL13        | C14  | EVss             | E12  | CS4/PCS4      |

(2/2)

| ピン番号 | 名 称                                  | ピン番号 | 名 称                                | ピン番号 | 名 称                                  |

|------|--------------------------------------|------|------------------------------------|------|--------------------------------------|

| E13  | CS7/PCS7                             | J14  | NMI/P20                            | M11  | AVss0                                |

| E14  | EVss                                 | K1   | TOQT1/INTP011/INTPQ1/TOQ1/P11      | M12  | ANI6/P76                             |

| F1   | AD2/PDL2                             | K2   | TC3/TDO/P27                        | M13  | ANI5/P75                             |

| F2   | AD3/PDL3                             | K3   | TC0/INTP124/P24                    | M14  | -                                    |

| F3   | AD4/PDL4                             | K4   | TC2/TDI/INTP126/P26                | N1   | EVss                                 |

| F4   | EV <sub>DD</sub>                     | K11  | ANI1/P71                           | N2   | DMARQ3/TCK/INTP107/P07               |

| F11  | RD/PCT4                              | K12  | ANI0/P70                           | N3   | DMAAK3/PBD3                          |

| F12  | EV <sub>DD</sub>                     | K13  | Vss                                | N4   | DMAAK0/PBD0                          |

| F13  | LBE/LWR/LDQM/PCT0                    | K14  | V <sub>DD</sub>                    | N5   | TXD3/SDA <sup>注</sup> /INTP133/P33   |

| F14  | UBE/UWR/UDQM/PCT1                    | L1   | EVss                               | N6   | TXD2/SO2/INTP130/P30                 |

| G1   | TOP01/INTP001/INTPP01/P01            | L2   | TC1/TIUD10/TO10/INTP125/P25        | N7   | ASCK0/SCK0/P42                       |

| G2   | TOP00/INTP000/EVTP0/TIP0/INTPP00/P00 | L3   | DMARQ2/TMS/INTP106/P06             | N8   | Vss                                  |

| G3   | AD0/PDL0                             | L4   | TRST                               | N9   | X2                                   |

| G4   | AD6/PDL6                             | L5   | TOP11/INTPP11/INTP022/P22          | N10  | CVss                                 |

| G11  | WAIT/PCM0                            | L6   | ASCK2/SCK2/INTP132/P32             | N11  | ANO1/P81                             |

| G12  | WR/WE/PCT5                           | L7   | ASCK1/SCK1/P45                     | N12  | AVss1                                |

| G13  | BCYST/PCT7                           | L8   | TXD0/SO0/P40                       | N13  | AV <sub>DD1</sub>                    |

| G14  | ASTB/PCT6                            | L9   | MODE0                              | N14  | -                                    |

| H1   | TOQB3/INTP115/EVTQ/P15               | L10  | AVDDO                              | P1   | EVDD                                 |

| H2   | TOQB2/INTP114/TIQ/P14                | L11  | ANI7/P77                           | P2   | EVss                                 |

| Н3   | TOQT3/INTP013/INTPQ3/TOQ3/P13        | L12  | ANI4/P74                           | P3   | DMAAK1/PBD1                          |

| H4   | AD1/PDL1                             | L13  | ANI3/P73                           | P4   | TOP10/INTPP10/EVTP1/TIP1/INTP021/P21 |

| H11  | REFRQ/PCM4                           | L14  | ANI2/P72                           | P5   | EVss                                 |

| H12  | HLDRQ/PCM3                           | M1   | EVss                               | P6   | RXD1/SI1/P44                         |

| H13  | HLDAK/PCM2                           | M2   | DMARQ1/TCUD10/INTP10/INTP005/P05   | P7   | RXD0/SI0/P41                         |

| H14  | BUSCLK/PCM1                          | М3   | DMARQ0/INTP11/TCLR10/INTP004/P04   | P8   | PSEL                                 |

| J1   | VDD                                  | M4   | DMAAK2/PBD2                        | P9   | CV <sub>DD</sub>                     |

| J2   | TOQT2/INTP012/INTPQ2/TOQ2/P12        | M5   | RXD3/SCL <sup>™</sup> /INTP134/P34 | P10  | X1                                   |

| J3   | TOQB1/INTP010/INTPQ0/TOQ0/P10        | М6   | RXD2/SI2/INTP131/P31               | P11  | -                                    |

| J4   | Vss                                  | M7   | TXD1/SO1/P43                       | P12  | RESET                                |

| J11  | ADTRG/INTP137/P37                    | M8   | VDD                                | P13  | ANO0/P80                             |

| J12  | TOP21/INTPP21/INTP051/P51            | M9   | CKSEL                              | P14  | -                                    |

| J13  | TOP20/INTPP20/EVTP2/TIP2/INTP050/P50 | M10  | MODE1                              |      |                                      |

注 SCL, SDAは, μPD703131AY, 703132AY, 703133AY, 703134AY, 70F3134AYだけ有効です。

**備考** A10, E5, M14, N14, P11, P14の端子は, オープンにしてください。

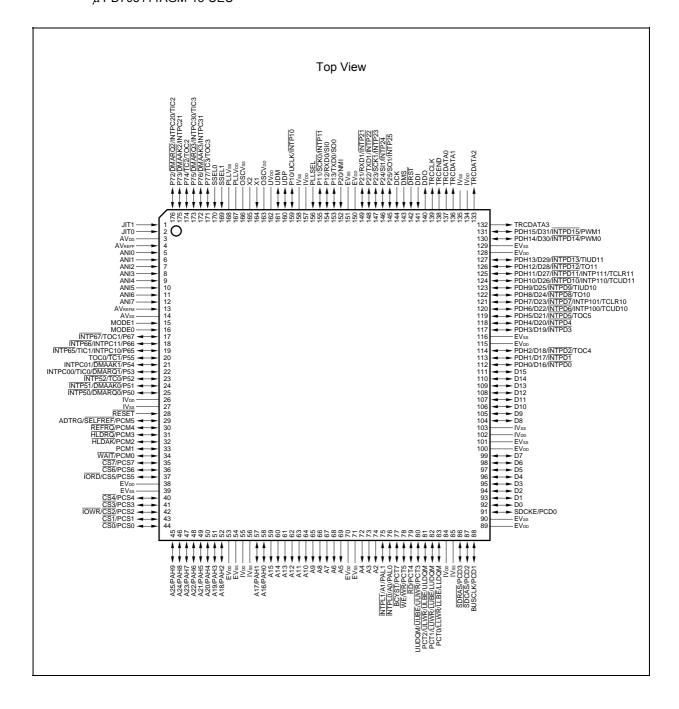

#### (4) V850E/ME2

・176ピン・プラスチックLQFP(ファインピッチ)(24 × 24)  $\mu$  PD703111AGM-10-UEU  $\mu$  PD703111AGM-13-UEU  $\mu$  PD703111AGM-15-UEU

・240ピン・プラスチックFBGA (16×16)

μ PD703111AF1-10-GA3

$\mu$  PD703111AF1-13-GA3

$\mu$  PD703111AF1-15-GA3

(1/2)

| ピン番号 | 名 称                   | ピン番号 | 名 称                  | ピン番号 | ( 1/2 )<br>名 称          |

|------|-----------------------|------|----------------------|------|-------------------------|

| A1   | -                     | C12  | IVDD                 | G3   | EVss                    |

| A2   | IVss                  | C13  | PAH2/A18             | G4   | D7                      |

| A3   | PCT0/LLWR/LLBE/LLDQM  | C14  | PAH4/A20             | G15  | PCM1                    |

| A4   | TOTO/LEWITELDE/LEDQWI | C15  | PAH6/A22             | G16  | PCM3/HLDRQ              |

|      | PCT4/RD               |      | PAH0/AZZ             | G17  | PCM4/REFRQ              |

| A5   | PC14/RD               | C16  | -                    |      |                         |

| A6   | -                     | C17  | PCS0/CS0             | G18  | PCM5/ADTRG/SELFREF      |

| A7   | -                     | C18  | -                    | H1   | -                       |

| A8   | EVDD                  | D1   | D0                   | H2   | D8                      |

| A9   | A9                    | D2   | EVss                 | H3   | D9                      |

| A10  | -                     | D3   | PCD0/SDCKE           | H4   | D10                     |

| A11  | A14                   | D4   | EV <sub>DD</sub>     | H5   | IVss                    |

| A12  | IVss                  | D5   | PCT1/LUWR/LUBE/LUDQM | H14  | -                       |

| A13  | EV <sub>DD</sub>      | D6   | -                    | H15  | RESET                   |

| A14  | -                     | D7   | PAL0/INTPL0/A0       | H16  | IVss                    |

| A15  | PAH5/A21              | D8   | A4                   | H17  | -                       |

| A16  | PAH7/A23              | D9   | A6                   | H18  | IV <sub>DD</sub>        |

| A17  | PAH9/A25              | D10  | -                    | J1   | -                       |

| A18  | -                     | D11  | A13                  | J2   | D11                     |

| B1   | -                     | D12  | EVss                 | J3   | D12                     |

| B2   | PCD1/BUSCLK           | D13  | PAH3/A19             | J4   | -                       |

| В3   | PCD2/SDCAS            | D14  | -                    | J5   | D13                     |

| B4   | -                     | D15  | -                    | J14  | -                       |

| B5   | PCT3/UUWR/UUBE/UUDQM  | D16  | PCS2/CS2/IOWR        | J15  | P50/INTP50/DMARQ0       |

| В6   | PCT7/BCYST            | D17  | PCS3/CS3             | J16  | P51/INTP51/DMAAK0       |

| В7   | A2                    | D18  | EV <sub>DD</sub>     | J17  | P52/INTP52/TC0          |

| В8   | -                     | E1   | D3                   | J18  | P53/INTPC00/TIC0/DMARQ1 |

| В9   | A8                    | E2   | D2                   | K1   | D14                     |

| B10  | A12                   | E3   | D1                   | K2   | D15                     |

| B11  | PAH0/A16              | E4   | -                    | K3   | PDH0/D16/INTPD0         |

| B12  | -                     | E8   | A3                   | K4   | PDH1/D17/INTPD1         |

| B13  | -                     | E9   | A5                   | K5   | PDH2/D18/INTPD2/TOC4    |

| B14  | -                     | E10  | A10                  | K14  | P55/TOC0/TC1            |

| B15  | -                     | E11  | PAH1/A17             | K15  | P54/INTPC01/DMAAK1      |

| B16  | PAH8/A24              | E15  | PCS4/CS4             | K16  | P65/INTP65/INTPC10/TIC1 |

| B17  | -                     | E16  | EVss                 | K17  | P66/INTP66/INTPC11      |

| B18  | PCS1/CS1              | E17  | PCS5/CS5/IORD        | K18  | -                       |

| C1   | -                     | E18  | PCS6/CS6             | L1   | EV <sub>DD</sub>        |

| C2   | _                     | F1   | D6                   | L2   | -                       |

| C3   | PCD3/SDRAS            | F2   | D5                   | L3   | EVss                    |

| C4   | IV <sub>DD</sub>      | F3   | D4                   | L4   | PDH3/D19/INTPD3         |

| C5   | PCT2/ULWR/ULBE/ULDQM  | F4   |                      | L5   | PDH4/D20/INTPD4         |

| C6   | PCT5/WE/WR            | F15  |                      | L14  | MODE1                   |

| C7   | PAL1/INTPL1/A1        | F16  | PCS7/ <del>CS7</del> | L14  | WODLI                   |

|      | EVss                  | F10  | PCS7/CS7 PCM0/WAIT   |      | MODEO -                 |

| C8   |                       |      |                      | L16  | MODE0                   |

| C9   | A7                    | F18  | PCM2/HLDAK           | L17  |                         |

| C10  | A11                   | G1   | IV <sub>DD</sub>     | L18  | P67/INTP67/TOC1         |

| C11  | A15                   | G2   | EV <sub>DD</sub>     | M1   | -                       |

(2/2)

| ピン番号 | 名 称                              | ピン番号 | 名 称                     | ピン番号 | 名 称                     |

|------|----------------------------------|------|-------------------------|------|-------------------------|

| M2   | PDH5/D21/INTPD5/TOC5             | R7   | DCK                     | U4   | -                       |

| М3   | PDH6/D22/INTPD6/INTP100/TCUD10   | R8   | EV <sub>DD</sub>        | U5   | TRCCLK                  |

| M4   | -                                | R9   | P11/INTP11/SCK0         | U6   | DRST                    |

| M15  | ANI6                             | R10  | IVss                    | U7   | P25/INTP25/SO1          |

| M16  | AVREFM                           | R11  | UDM                     | U8   | P22/INTP22/TXD1         |

| M17  | ANI7                             | R12  | X2                      | U9   | EVss                    |

| M18  | AVss                             | R13  | PLLV <sub>DD</sub>      | U10  | IV <sub>DD</sub>        |

| N1   | PDH7/D23/INTPD7/INTP101/TCLR10   | R14  | SSEL0                   | U11  | -                       |

| N2   | PDH8/D24/INTPD8/TO10             | R15  | -                       | U12  | OSCVDD                  |

| N3   | PDH9/D25/INTPD9/TIUD10           | R16  | AVREFP                  | U13  | -                       |

| N4   | PDH10/D26/INTPD10/INTP110/TCUD11 | R17  | AVDD                    | U14  | -                       |

| N15  | ANI2                             | R18  | -                       | U15  | P76/INTPC31/DMAAK3      |

| N16  | ANI3                             | T1   | EV <sub>DD</sub>        | U16  | P73/INTPC21/DMAAK2      |

| N17  | ANI4                             | T2   | TRCDATA3                | U17  | P72/INTPC20/TIC2/DMARQ2 |

| N18  | ANI5                             | Т3   | -                       | U18  | -                       |

| P1   | -                                | T4   | TRCDATA1                | V1   | -                       |

| P2   | PDH11/D27/INTPD11/INTP111/TCLR11 | T5   | TRCEND                  | V2   | TRCDATA2                |

| P3   | PDH13/D29/INTPD13/TIUD11         | Т6   | DDI                     | V3   | IVss                    |

| P4   | -                                | T7   | -                       | V4   | TRCDATA0                |

| P8   | P23/INTP23/SCK1                  | T8   | P21/INTP21/RXD1         | V5   | -                       |

| P9   | P12/SI0/RXD0                     | Т9   | P20/NMI                 | V6   | DMS                     |

| P10  | -                                | T10  | -                       | V7   | P24/INTP24/SI1          |

| P11  | UV <sub>DD</sub>                 | T11  | UDP                     | V8   | -                       |

| P15  | -                                | T12  | X1                      | V9   | P13/S00/TXD0            |

| P16  | ANI0                             | T13  | OSCVss                  | V10  | PLLSEL                  |

| P17  | ANI1                             | T14  | SSEL1                   | V11  | P10/INTP10/UCLK         |

| P18  | -                                | T15  | P75/INTPC30/TIC3/DMARQ3 | V12  | -                       |

| R1   | PDH12/D28/INTPD12/TO11           | T16  | -                       | V13  | -                       |

| R2   | EVss                             | T17  | JIT1                    | V14  | -                       |

| R3   | PDH14/D30/INTPD14/PWM0           | T18  | JIT0                    | V15  | PLLVss                  |

| R4   | IV <sub>DD</sub>                 | U1   | PDH15/D31/INTPD15/PWM1  | V16  | P77/TOC3/TC3            |

| R5   | -                                | U2   | -                       | V17  | P74/TOC2/TC2            |

| R6   | DDO                              | U3   | -                       | V18  | -                       |

**備考** A1, A4, A6, A7, A10, A14, A18, B1, B4, B8, B12-B15, B17, C1, C2, C16, C18, D6, D10, D14, D15, E4, F4, F15, H1, H14, H17, J1, J4, J14, K18, L2, L15, L17, M1, M4, P1, P4, P10, P15, P18, R5, R15, R18, T3, T7, T10, T16, U2-U4, U11, U13, U14, U18, V1, V5, V8, V12-V14, V18の端子は,オープンにしてください。

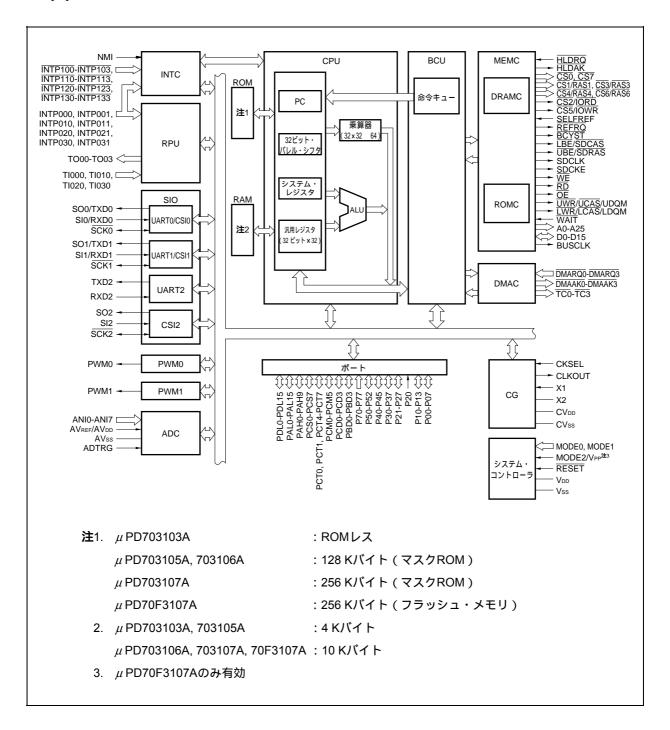

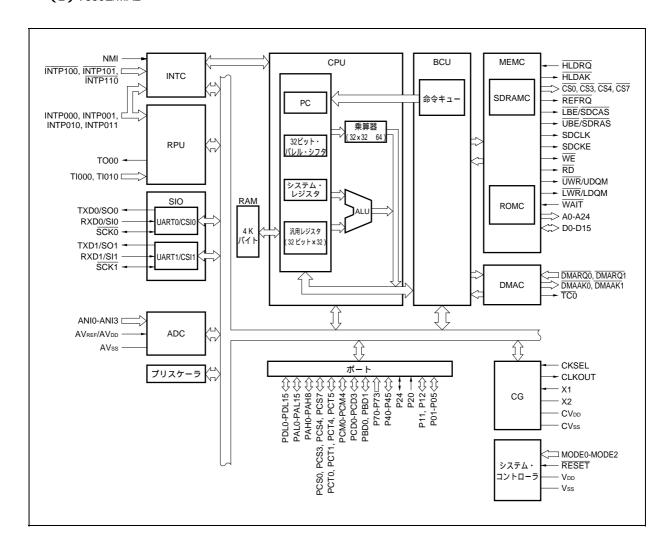

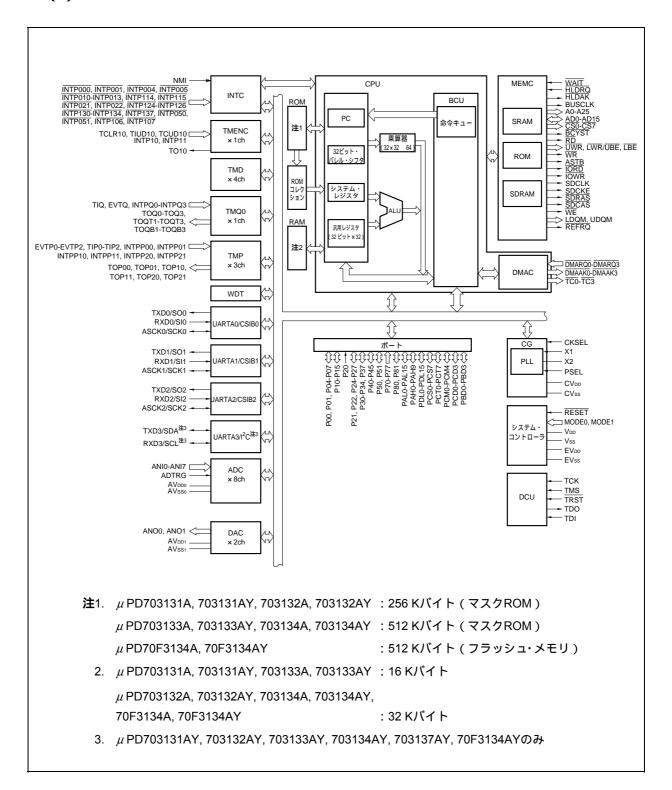

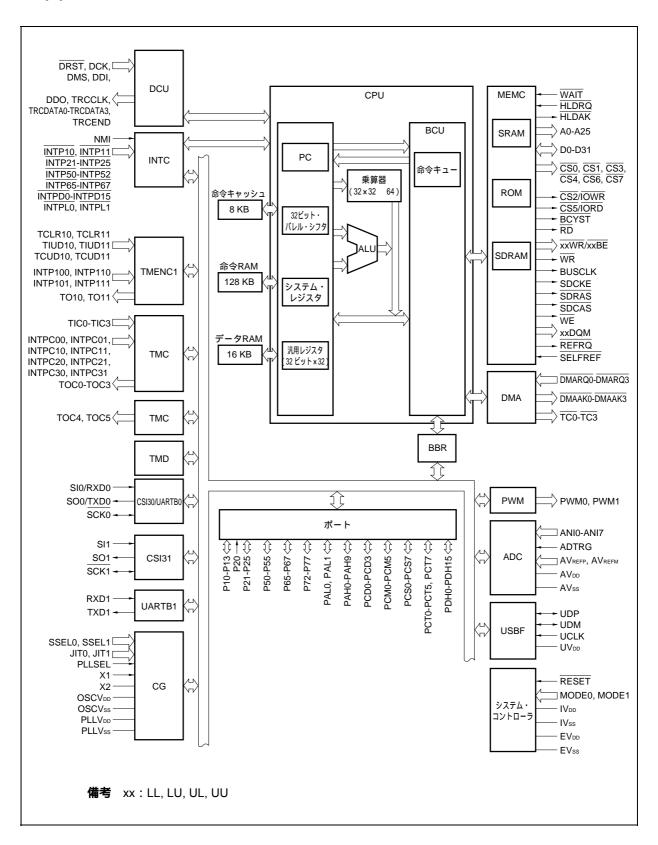

# 1.5 内部プロック図

#### (1) V850E/MA1

#### (2) V850E/MA2

#### (3) V850E/MA3

#### (4) V850E/ME2

# 第2章 PCIホスト・ブリッジ・マクロの概要

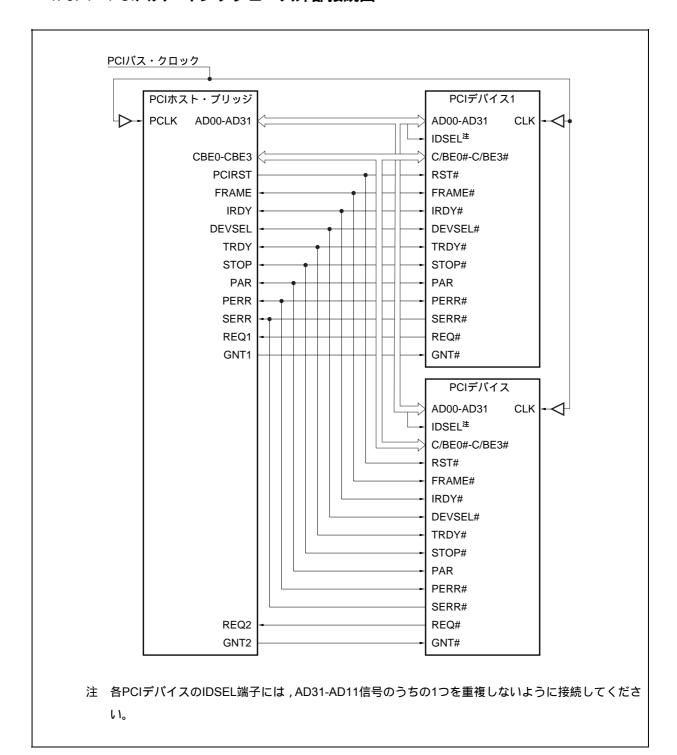

PCIホスト・ブリッジ・マクロは, V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2の外部バス・インタフェースとPCIバス・インタフェースの接続を可能にするマクロです。この章では, PCIホスト・ブリッジ・マクロの概要を説明します。

### 2.1 概 説

PCIホスト・ブリッジ・マクロは, V850E/MA1, V850E/MA2, V850E/MA3, V850E/ME2の外部バス・インタフェース(メモリ・コントローラ(MEMC))とPCIバス・インタフェースを接続するブリッジ制御マクロです。 PCIデバイスからメイン・メモリ(SDRAM)へのアクセス時に,直接SDRAMを制御できます。

### 2.2 特 徵

PCIホスト・ブリッジ・マクロの特徴を次に示します。

#### PCIバス・マスタ・サイクル制御

PCI Configuration Register Read/Write Single Cycle

PCI I/O Register Read/Write Single Cycle

PCI Memory Read/Write Single Cycle

#### PCIバス・スレーブ・サイクル制御

PCI Memory Read/Write Cycle (最大8ダブル・ワードのバースト転送(32ビット×8バースト))

#### PCIバス・アービタ制御

最大8マスタまで制御可能(そのうちの1つはPCIホスト・ブリッジ・マクロが占有)

バス・パーキング・マスタ: PCIホスト・ブリッジ・マクロ限定/最後にアクセスしたマスタから選択可能

#### PCIバス・エラー処理

マスタ・アボート / ターゲット・アボート / PERR#受信 / SERR#受信に対してエラー割り込みを発生エラー発生直前のアドレスを保持

#### PCIバス・アドレス変換制御

PCIバスに対してCPUからの物理アドレスを変換するためのPCI I/Oアドレス・レジスタおよびPCIメモリ・アドレス・レジスタを備えて対応

#### CPUインタフェース制御

外部バス・インタフェース (MEMC)

データ・バス幅:32ビット/16ビット

ハードウエア・ウエイト制御によるサイクル制御

#### SDRAM制御

PCIデバイスからのメイン・メモリ (SDRAM) アクセスに応答してSDRAMを制御

データ・バス幅:16ビット/32ビットに対応

#### PCIクロック

33 MHzに対応

SDRAM制御とPCI制御のクロックは非同期設計

# 第3章 PCIホスト・ブリッジ・マクロの仕様

この章では、PCIホスト・ブリッジ・マクロのブロック図、信号、レジスタ仕様、動作仕様について説明します。

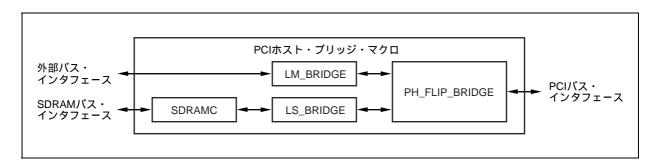

### 3.1 PCIホスト・ブリッジ・マクロの内部プロック

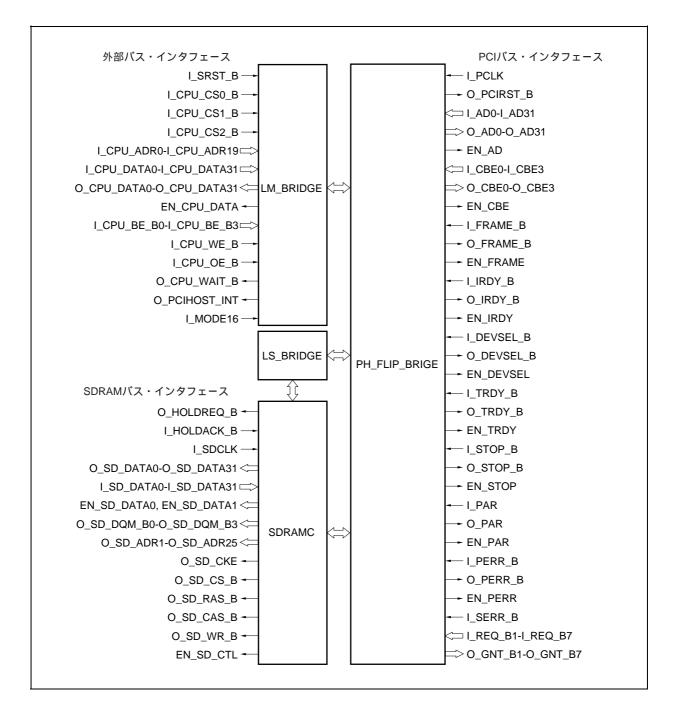

PCIホスト・ブリッジ・マクロは,**図3-1** PCI**ホスト・ブリッジ・マクロ概略プロック図**に示すように,4つのブロックから構成されています。各ブロックの機能について,次に説明します。

#### (1) LM BRIDGE:外部パス・インタフェース・マスタ制御回路

外部バス・インタフェースに接続され、CPUからのアクセスに対して応答し、PCIバス・コントロール回路のPH\_FLIP\_BRIDGEブロックに対してアクセス要求を出します。CPUからは、16ビット/32ビットのバス幅のアクセスが可能です。

#### (2) LS\_BRIDGE:外部パス・インタフェース・スレープ制御回路

PCIデバイスからのメモリ・データ転送要求に対して,PCIバス・コントロール回路のPH\_FLIP\_BRIDGE ブロックからのアクセスに対して応答し,SDRAMCへアクセス要求を出します。

#### (3) SDRAMC: 外部パス・インタフェースSDRAM制御回路

SDRAMバスに接続され,LS\_BRIDGEブロックを通したPCIデバイスからのメモリ要求を,SDRAMバスを起動してデータ転送を行います。

SDRAMのバス幅が16ビットの場合,最大で8バーストのメモリ・サイクルを起動します。また,32ビットの場合,最大で4バーストのメモリ・サイクルを起動します。

#### (4) PH\_FLIP\_BRIDGE:外部パス・インタフェース・ホスト制御回路

PCIバスに接続され, PCIホスト・デバイスとして動作します。

LM\_BRIDGEプロックからの要求に対して, PCI Configuration Register Read/Write Cycle, PCI IO Register Read/Write Cycle, およびPCI Memory Read/Write Cycleを起動します。

また,PCIバスに接続されているPCIデバイスからのメモリ・データ転送要求に対して,LS\_BRIDGEブロックへ要求を出します。

図3 - 1 PCIホスト・ブリッジ・マクロ概略ブロック図

# 3.2 内部プロックと信号の関係

PCIホスト・ブリッジ・マクロとしての各ブロックに対する入出力信号を,次に示します。

図3 - 2 PCIホスト・ブリッジ・マクロのブロックと端子信号

# 3.3 端子機能

各インタフェースにおける端子機能について,次に説明します。

# 3.3.1 外部パス・スレーブ・インタフェース端子

| 端子名称                     | 入出力 | 機能                          | アクティブ     |

|--------------------------|-----|-----------------------------|-----------|

| I_SRST_B                 | 入力  | システム・リセット入力                 | ロウ        |

| I_CPU_CS0_B              | 入力  | PCIホスト・ブリッジ・レジスタ・チップ・セレクト入力 | ロウ        |

| I_CPU_CS1_B              | 入力  | PCI I/O領域チップ・セレクト入力         | ロウ        |

| I_CPU_CS2_B              | 入力  | PCIメモリ領域チップ・セレクト入力          | ロウ        |

| I_CPU_ADR0-I_CPU_ADR19   | 入力  | CPUアドレス入力                   | -         |

| I_CPU_DATA0-I_CPU_DATA31 | 入力  | CPUデータ入力                    | -         |

| O_CPU_DATA0-O_CPU_DATA31 | 出力  | CPUデータ出力                    | -         |

| EN_CPU_DATA              | 出力  | CPUデータ・アウトプット・イネーブル出力       | ハイ        |

| I_CPU_BE_B0-I_CPU_BE_B3  | 入力  | CPUデータ・バイト・イネーブル入力          | -         |

| I_CPU_WE_B               | 入力  | CPUライト・データ・イネーブル入力          | ロウ        |

| I_CPU_OE_B               | 入力  | CPUリード・データ・アウトプット・イネーブル入力   | ロウ        |

| O_CPU_WAIT_B             | 出力  | CPUデータ・ウエイト出力               | ロウ        |

| O_PCIHOST_INT            | 出力  | PCIホスト・ブリッジ割り込み出力           | ロウ        |

| I_MODE16                 | 入力  | CPUデータ・バス幅セレクト入力            | ロウ:32ビット幅 |

|                          |     |                             | ハイ:16ビット幅 |

# 3.3.2 SDRAM**パス・インタフェース端子**

| 端子名称                     | 入出力 | 機能                                          | アクティブ |

|--------------------------|-----|---------------------------------------------|-------|

| O_HOLDREQ_B              | 出力  | SDRAMバス・ホールド・リクエスト出力                        | ロウ    |

| I_HOLDACK_B              | 入力  | SDRAMバス・ホールド・アクノリッジ入力                       | ロウ    |

| I_SDCLK                  | 入力  | SDRAMクロック入力                                 | -     |

| O_SD_DATA0-O_SD_DATA31   | 出力  | SDRAMデータ出力                                  | -     |

| I_SD_DATA0-I_SD_DATA31   | 入力  | SDRAMデータ入力                                  | -     |

| EN_SD_DATA0, EN_SD_DATA1 | 出力  | SDRAMデータ・イネーブル出力                            |       |

|                          |     | ロウ:下位16ビット(O_SD_DATA0-O_SD_DATA15)          |       |

|                          |     | ハイ:上位16ビット(O_SD_DATA16-O_SD_DATA31)         |       |

| O_SD_DQM_B0-O_SD_DQM_B3  | 出力  | SDRAMデータ・マスク出力                              | ロウ    |

| O_SD_ADR1-O_SD_ADR25     | 出力  | SDRAMアドレス出力                                 | -     |

| O_SD_CKE                 | 出力  | SDRAMクロック・イネーブル出力                           | ハイ    |

| O_SD_CS_B                | 出力  | SDRAMチップ・セレクト出力                             | ロウ    |

| O_SD_RAS_B               | 出力  | SDRAMロウ・アドレス・ストローブ出力                        | ロウ    |

| O_SD_CAS_B               | 出力  | SDRAMカラム・アドレス・ストローブ出力                       | ロウ    |

| O_SD_WR_B                | 出力  | SDRAMリード/ライト出力                              | ロウ    |

| EN_SD_CTL                | 出力  | SDRAM制御信号アウトプット・イネーブル出力                     | ハイ    |

|                          |     | (O_SD_ADR1-O_SD_ADR25, O_SD_CKE, O_SD_CS_B, |       |

|                          |     | O_SD_RAS_B, O_SD_CAS_B, O_SD_WR_Bの各端子出力     |       |

|                          |     | バッファ・イネーブル )                                |       |

# 3.3.3 PCIバス・インタフェース端子

| 端子名称              | 入出力 | 機能                              | アクティブ |

|-------------------|-----|---------------------------------|-------|

| I_PCLK            | 入力  | PCIクロック入力                       | -     |

| O_PCIRST_B        | 出力  | PCIリセット出力                       | ロウ    |

| I_AD0-I_AD31      | 入力  | PCIアドレス / データ入力                 | -     |

| O_AD0-O_AD31      | 出力  | PCIアドレス / データ出力                 | -     |

| EN_AD             | 出力  | PCIアドレス / データ・アウトプット・イネーブル出力    | ハイ    |

|                   |     | (O_AD0-O_AD31の出力バッファ・イネーブル)     |       |

| I_CBE0-I_CBE3     | 入力  | PCIコマンド / バイト・イネーブル入力           | ロウ    |

| O_CBE0-O_CBE3     | 出力  | PCIコマンド / バイト・イネーブル出力           | ロウ    |

| EN_CBE            | 出力  | PCIコマンド / バイト・イネーブル・アウトプット・イネーブ | ハイ    |

|                   |     | ル出力                             |       |

|                   |     | (O_CBE0-O_CBE3の出力バッファ・イネーブル)    |       |

| I_FRAME_B         | 入力  | PCIフレーム入力                       | ロウ    |

| O_FRAME_B         | 出力  | PCIフレーム出力                       | ロウ    |

| EN_FRAME          | 出力  | PCIフレーム・アウトプット・イネーブル出力          | ハイ    |

|                   |     | (O_FRAME_Bの出力バッファ・イネーブル )       |       |

| I_IRDY_B          | 入力  | PCIイニシエータ・レディ入力                 | ロウ    |

| O_IRDY_B          | 出力  | PCIイニシエータ・レディ出力                 | ロウ    |

| EN_IRDY           | 出力  | PCIイニシエータ・レディ・アウトプット・イネーブル出力    | ハイ    |

|                   |     | (O_IRDY_Bの出力バッファ・イネーブル )        |       |

| I_DEVSEL_B        | 入力  | PCIデバイス・セレクト入力                  | ロウ    |

| O_DEVSEL_B        | 出力  | PCIデバイス・セレクト出力                  | ロウ    |

| EN_DEVSEL         | 出力  | PCIデバイス・セレクト・アウトプット・イネーブル出力     | ハイ    |

|                   |     | (O_DEVSEL_Bの出力バッファ・イネーブル )      |       |

| I_TRDY_B          | 入力  | PCIターゲット・レディ入力                  | ロウ    |

| O_TRDY_B          | 出力  | PCIターゲット・レディ出力                  | ロウ    |

| EN_TRDY           | 出力  | PCIターゲット・レディ・アウトプット・イネーブル出力     | ハイ    |

|                   |     | (O_TRDY_Bの出力バッファ・イネーブル )        |       |

| I_STOP_B          | 入力  | PCIストップ入力                       | ロウ    |

| O_STOP_B          | 出力  | PCIストップ出力                       | ロウ    |

| EN_STOP           | 出力  | PCIストップ・アウトプット・イネーブル出力          | ハイ    |

|                   |     | (O_STOP_Bの出力バッファ・イネーブル )        |       |

| I_PAR             | 入力  | PCIパリティ入力                       | -     |

| O_PAR             | 出力  | PCIパリティ出力                       | -     |

| EN_PAR            | 出力  | PCIパリティ・アウトプット・イネーブル出力          | ハイ    |

|                   |     | (O_PARの出力バッファ・イネーブル )           |       |

| I_PERR_B          | 入力  | PCIパリティ・エラー入力                   | ロウ    |

| O_PERR_B          | 出力  | PCIパリティ・エラー出力                   | ロウ    |

| EN_PERR           | 出力  | PCIパリティ・エラー・アウトプット・イネーブル出力      | ハイ    |

|                   |     | (O_PERR_Bの出力バッファ・イネーブル )        |       |

| I_SERR_B          | 入力  | PCIシステム・エラー入力                   | ロウ    |

| I_REQ_B1-I_REQ_B7 | 入力  | PCIリクエスト入力                      | ロウ    |

| O_GNT_B1-O_GNT_B7 | 出力  | PCIグラント出力                       | ロウ    |

# 3.4 レジスタ

PCIホスト・ブリッジ・マクロのレジスタ一覧を次に示します。レジスタのビット幅はすべて32ビットです。 各レジスタのオフセット・アドレスは,I\_CPU\_CS0\_B端子がアクティブとなる領域のベース・アドレスからの オフセット値です。

| オフセット・アドレス | レジスタ名            | R/W | 機能                                    |

|------------|------------------|-----|---------------------------------------|

| 00H        | PCI_CONFIG_DATA  | R/W | PCI Configuration Registerアクセス・データ設定  |

| 04H        | PCI_CONFIG_ADD   | R/W | PCI Configuration Registerアクセス・アドレス設定 |

| 08H        | PCI_CONTROL      | R/W | PCIバス制御                               |

| 0CH        | 予約               |     |                                       |

| 10H        | PCI_IO_BASE      | R/W | CPUメモリ・マップ上のPCI I/O領域からアクセスするPCIバス    |

|            |                  |     | I/O空間のベース・アドレスを設定                     |

| 14H        | PCI_MEM_BASE     | R/W | CPUメモリ・マップ上のPCIメモリ領域からアクセスするPCI       |

|            |                  |     | バス・メモリ空間のベース・アドレスを設定                  |

| 18H        | PCI_INT_CTL      | R/W | PCIエラー割り込み制御                          |

| 1CH        | PCI_ERR_ADD      | R   | PCIエラー発生アドレス保持                        |

| 20H-3FH    | 予約               |     |                                       |

| 40H        | SYSTEM_MEM_BASE  | R/W | PCIバス・メモリ空間にマッピングするシステム・メモリ領域の        |

|            |                  |     | ベース・アドレスを設定                           |

| 44H        | SYSTEM_MEM_RANGE | R/W | PCIバス・メモリ空間にマッピングするシステム・メモリ領域の        |

|            |                  |     | 範囲を設定                                 |

| 48H        | SDRAM_CTL        | R/W | SDRAMアクセス制御                           |

| 4CH-FFH    | 予約               |     |                                       |

# 3.4.1 PCI\_CONFIG\_DATAレジスタ

リセット時:不定 R/W オフセット・アドレス:00H

31 0

CDATA

| ビット名  | R/W | 機能                                                             |

|-------|-----|----------------------------------------------------------------|

| CDATA | R/W | このフィールドにデータをライトすることにより ,PCI Configuration Register Writeアクセスを実 |

|       |     | 行し,このフィールドにライトしたデータをアクセス対象レジスタにライトします。                         |

|       |     | このフィールドをリードすることにより ,PCI Configuration Register Readアクセスを実行し ,ア |

|       |     | クセス対象レジスタのデータをリードします。                                          |

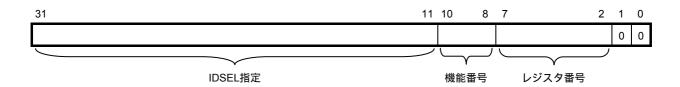

# 3.4.2 PCI\_CONFIG\_ADDレジスタ

リセット時:00000000H R/W オフセット・アドレス:04H

| ビット名 | R/W | 機能                                           |

|------|-----|----------------------------------------------|

| CADD | R/W | アクセス対象のPCI Configuration Registerアドレスを設定します。 |

#### (1) PCI CONFIG ADD レジスタの設定方法

#### (a) タイプ0 (PCIデバイス)

IDSEL指定 : アクセス対象PCIデバイスに対応するIDSEL信号を選択します。

このPCIホスト・ブリッジ・マクロは,各PCIデバイスに対するIDSEL信号をAD31-AD11信号で代用するため,各PCIデバイスのIDSEL端子に接続しているAD信号をこのフィールドで指定します。たとえば,あるPCIデバイスのIDSEL端子にAD31信号が接続されている場合,CADDのビット31に1を設定することにより,

アクセスが可能となります。

機能番号 : マルチファンクション・デバイスに対する機能番号を指定します。 レジスタ番号 : アクセス対象PCI Configuration Registerの番号を指定します。

#### (b) タイプ1 (PCI-PCIブリッジ)

バス番号:アクセス対象PCIデバイスが接続されているPCIバスの番号を指定します。

デバイス番号 : アクセス対象PCIデバイスのデバイス番号を指定します。

機能番号 : マルチファンクション・デバイスに対する機能番号を指定します。

レジスタ番号 : アクセス対象PCI Configuration Registerの番号を指定します。

#### (2) PCI Configuration Registerへのアクセス方法

・ライト・アクセス

PCI\_CONFIG\_ADDレジスタにアクセス対象レジスタのアドレスを設定

PCI\_CONFIG\_DATAレジスタにアクセス対象レジスタへの設定値をライト

・リード・アクセス

PCI\_CONFIG\_ADDレジスタにアクセス対象レジスタのアドレスを設定

PCI\_CONFIG\_DATAレジスタをリード

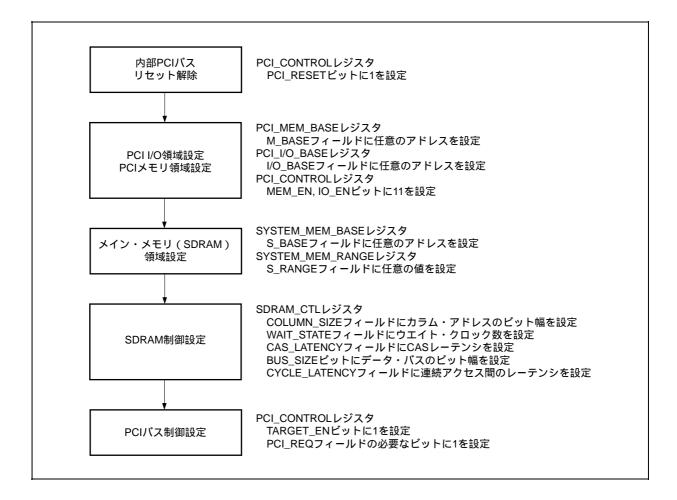

# 3.4.3 PCI\_CONTROLレジスタ

リセット時:07000100H R/W オフセット・アドレス:08H

| 31 |             | 24 | 23 |   |   |   |   |   | 17 | 16         | 15 |         | 8 | 7 |   | 5 | 4         | 3 | 2         | 1      | 0     |

|----|-------------|----|----|---|---|---|---|---|----|------------|----|---------|---|---|---|---|-----------|---|-----------|--------|-------|

|    | PCI_PARKCNT |    | 0  | 0 | 0 | 0 | 0 | 0 | 0  | PCI_BPMODE |    | PCI_REQ |   | 0 | 0 | 0 | PCI_RESET | 0 | TARGET_EN | MEM_EN | IO_EN |

| ビット名        | R/W | 機能                                                  |

|-------------|-----|-----------------------------------------------------|

| PCI_PARKCNT | R/W | バス・パーキングに移行する時間を設定します。                              |

|             |     | ディフォールト値では,バスがIDLE状態になってから7クロック後にバス・パーキングを行いま       |

|             |     | す。                                                  |

|             |     | カウンタ開始はFRAME# = High & IRDY# = Highです。              |

| PCI_BPMODE  | R/W | バス・パーキング・マスタを設定します。                                 |

|             |     | 0:このマクロ限定                                           |

|             |     | 1:最後にアクセスしたマスタ                                      |

| PCI_REQ     | R/W | バス・マスタからのREQ#信号(I_REQ_B1-I_REQ_B7端子)の有効 / 無効を設定します。 |

|             |     | このフィールドのビット0(PCI_CONTROLレジスタのビット8)はこのPCIホスト・ブリッジ・   |

|             |     | マクロに割り当てられており,常に1となります。                             |

|             |     | 0:無効                                                |

|             |     | 1:有効                                                |

| PCI_RESET   | R/W | PCIバスのリセット状態を設定します。                                 |

|             |     | 0:リセット状態                                            |

|             |     | 1:リセット解除                                            |

| TARGET_EN   | R/W | このPCIホスト・ブリッジ・マクロのPCIバス・ターゲットとしての動作を設定します。          |

|             |     | 0:PCIデバイスからのメイン・メモリ(SDRAM)アクセスに応答しない                |

|             |     | 1:PCIデバイスからのメイン・メモリ(SDRAM)アクセスに応答する                 |

| MEM_EN      | R/W | CPUからPCIメモリ領域へのアクセスの許可/禁止を設定します。                    |

|             |     | 0:アクセス禁止                                            |

|             |     | 1:アクセス許可                                            |

| IO_EN       | R/W | CPUからPCI I/O領域へのアクセスの許可/禁止を設定します。                   |

|             |     | 0:アクセス禁止                                            |

|             |     | 1:アクセス許可                                            |

#### 3.4.4 PCI IO BASEレジスタ

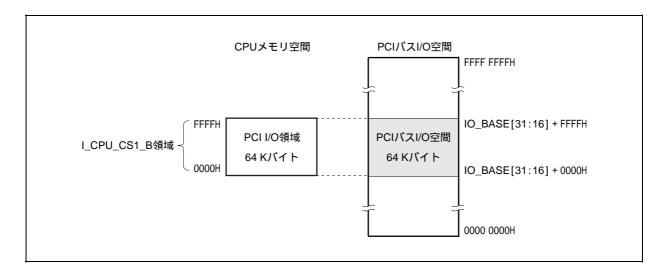

PCI I/O領域(I\_CPU\_CS1\_B端子がアクティブとなる領域: 64 Kバイト)を介してPCIバスI/O空間へのI/Oアクセスを行うとき,このレジスタへの設定によって,4 GバイトのPCIバスI/O空間のうち任意の領域にアクセスできます。

リセット時:00000000H R/W オフセット・アドレス:10H

| 31 16   | 15 |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 0 |

|---------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| IO_BASE | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ビット名    | R/W | 機能                                                     |

|---------|-----|--------------------------------------------------------|

| IO_BASE | R/W | CPUからPCI I/O領域(I_CPU_CS1_B端子がアクティブとなる領域)にアクセスするときの,PCI |

|         |     | バスI/O空間ベース・アドレスの上位16ビット(ビット16-31)を設定します。               |

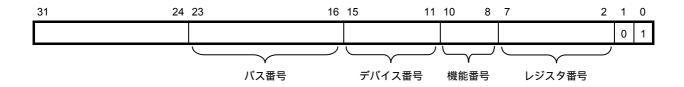

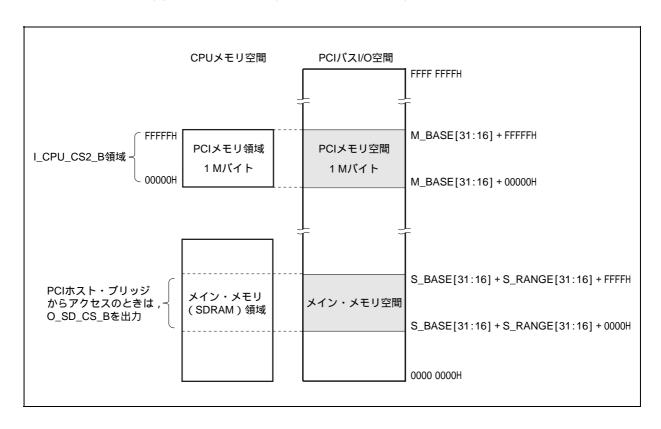

#### 3.4.5 PCI MEM BASEレジスタ

PCIメモリ領域 (I\_CPU\_CS2\_B端子がアクティブとなる領域: 1 Mバイト)を介してPCIバス・メモリ空間へのメモリ・アクセスを行うとき、このレジスタへの設定によって、4 GバイトのPCIバス・メモリ空間のうち任意の領域にアクセスできます。

ただし、PCIバス・メモリ空間上にメイン・メモリ(SDRAM)がマッピングされているので、後述の  $SYSTEM\_MEM\_BASE$ レジスタおよび $SYSTEM\_MEM\_RANGE$ レジスタで設定される領域と重複しないように 注意してください。

リセット時:80000000H R/W オフセット・アドレス:14H

| ビット名   | R/W | 機能                                                 |

|--------|-----|----------------------------------------------------|

| M_BASE | R/W | CPUからPCIメモリ領域(I_CPU_CS2_B端子がアクティブとなる領域)にアクセスするときの, |

|        |     | PCIバス・メモリ空間ベース・アドレスの上位12ビット(ビット20-31)を設定します。       |

# 3.4.6 PCI\_INT\_CTLレジスタ

PCI\_INT\_CTLレジスタは, PCIバス・エラー割り込み(O\_PCIHOST\_INT)の割り込み要因を示し,それらに対するマスク制御およびクリア制御を行います。

この機能は,ディバグ時だけ使用されます。通常時には使用しません。

リセット時:000x0F00H R/W オフセット・アドレス:18H

| 31 |   |   |   |   |   |   |   |   |   |   | 20 | 19       | 18       | 17      | 16      | 15 |   |   | 12 | 11       | 10       | 9       | 8       | 7 |   |   | 4 | 3    | 2    | 1      | 0      |

|----|---|---|---|---|---|---|---|---|---|---|----|----------|----------|---------|---------|----|---|---|----|----------|----------|---------|---------|---|---|---|---|------|------|--------|--------|

| 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | CLR_SERR | CLR_PERR | CLR_MAB | CLR_TAB | 0  | 0 | 0 | 0  | MSK_SERR | MSK_PERR | MSK_MAB | MSK_TAB | 0 | 0 | 0 | 0 | SERR | PERR | MABORT | TABORT |

| ビット名     | R/W | 機能                                       |

|----------|-----|------------------------------------------|

| CLR_SERR | W   | PCIバス・システム・エラー(SERR#受信)割り込みをクリアします。      |

|          |     | 1 : クリア                                  |

| CLR_PERR | W   | PCIバス・パリティ・エラー(PERR#受信)割り込みをクリアします。      |

|          |     | 1 : クリア                                  |

| CLR_MAB  | W   | PCIバス・マスタ・アボート割り込みをクリアします。               |

|          |     | 1 : クリア                                  |

| CLR_TAB  | W   | PCIバス・ターゲット・アボート割り込みをクリアします。             |

|          |     | 1 : クリア                                  |

| MSK_SERR | R/W | PCIバス・システム・エラー(SERR#受信)割り込みのマスク状態を設定します。 |

|          |     | 0:マスクしない                                 |

|          |     | 1:マスクする                                  |

| MSK_PERR | R/W | PCIバス・パリティ・エラー(PERR#受信)割り込みのマスク状態を設定します。 |

|          |     | 0:マスクしない                                 |

|          |     | 1:マスクする                                  |

| MSK_MAB  | R/W | PCIバス・マスタ・アボート割り込みのマスク状態を設定します。          |

|          |     | 0:マスクしない                                 |

|          |     | 1:マスクする                                  |

| MSK_TAB  | R/W | PCIバス・ターゲット・アボート割り込みのマスク状態を設定します。        |

|          |     | 0:マスクしない                                 |

|          |     | 1:マスクする                                  |

| SERR     | R   | PCIパス・システム・エラー(SERR#受信)の発生状態を検出します。      |

|          |     | 1:システム・エラー発生                             |

| PERR     | R   | PCIバス・パリティ・エラー(PERR#受信)の発生状態を検出します。      |

|          |     | 1:パリティ・エラー発生                             |

| MABORT   | R   | PCIバス・マスタ・アボートの発生状態を検出します。               |

|          |     | 1:マスタ・アボート発生                             |

| TABORT   | R   | PCIバス・ターゲット・アボートの発生状態を検出します。             |

|          |     | 1:ターゲット・アボート発生                           |

# 3.4.7 PCI\_ERR\_ADDレジスタ

PCI\_ERR\_ADDレジスタは,次に示したエラー要因が発生したときのPCIバス・アドレスを保持します。

- ・システム・エラー (SERR#受信)

- ・パリティ・エラー (PERR#受信)

- ・マスタ・アボート

- ・ターゲット・アボート

PCI\_ERR\_ADDレジスタをリードすると,すべてのビットがクリアされます。一度エラーが発生し,PCI\_ERR\_ADDレジスタに値が設定されると,リード・アクセスを受けるか,新たなエラーが発生して値が更新されるまでは,最初の値を保持します。

この機能は,ディバグ時だけ使用されます。通常時には使用しません。

リセット時:00000000H R オフセット・アドレス:1CH

31 0 ERR\_ADR

| ビット名    | R/W | 機能                       |

|---------|-----|--------------------------|

| ERR_ADR | R   | PCIバス・エラー発生時のアドレスを保持します。 |

# 3.4.8 SYSTEM\_MEM\_BASEレジスタ

SYSTEM\_MEM\_BASEレジスタとSYSTEM\_MEM\_RANGEレジスタの設定によって,PCIデバイスからのメイン・メモリ・アクセスが発生した場合,一致したアドレスへのアクセスに対して応答します。

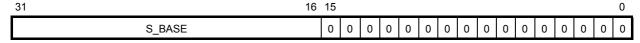

リセット時:00000000H R/W オフセット・アドレス:40H

| ビット名   | R/W | 機能                                              |

|--------|-----|-------------------------------------------------|

| S_BASE | R/W | メイン・メモリ(SDRAM)をマッピングするPCIバス・メモリ空間上ベース・アドレスの上位16 |

|        |     | ビット(ビット16-31)を設定します。                            |

# 3.4.9 SYSTEM\_MEM\_RANGEレジスタ

リセット時:0000FFFFH R/W オフセット・アドレス:44H

| 31 16   | 15 |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 0 |

|---------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S_RANGE | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| ビット名    | R/W | 機能                                              |

|---------|-----|-------------------------------------------------|

| S_RANGE | R/W | メイン・メモリ ( SDRAM ) をマッピングするPCIバス・メモリ空間の範囲を設定します。 |

|         |     | 64Kバイト単位で設定できます。                                |

|         |     | 0000H : 64 Kバイト                                 |

|         |     | 0001H: 128 Kバイト                                 |

|         |     | · ·                                             |

|         |     | 000FH : 1 Mバイト                                  |

|         |     | :                                               |

|         |     | 00FFH: 16 Mバイト                                  |

|         |     | :                                               |

|         |     | 0FFFH: 256 Mバイト                                 |

|         |     | :                                               |

|         |     | FFFFH: 4 Gパイト                                   |

# 3. 4. 10 SDRAM\_CTL**レジスタ**

リセット時:00070230H R/W オフセット・アドレス:48H

| 31    |         | 24 | 23            | 16 | 15 |   | 13 | 12       | 11 | 10 | 9 8         | 7 | 6 | 5 4        | 3 | 2 | 1 0         |

|-------|---------|----|---------------|----|----|---|----|----------|----|----|-------------|---|---|------------|---|---|-------------|

| 0 0 0 | 0 0 0 0 | 0  | CYCLE_LATENCY |    | 0  | 0 | 0  | BUS_SIZE | 0  | 0  | CAS_LATENCY | 0 | 0 | WAIT_STATE | 0 | 0 | COLUMN_SIZE |

| ビット名          | R/W | 機能                                             |

|---------------|-----|------------------------------------------------|

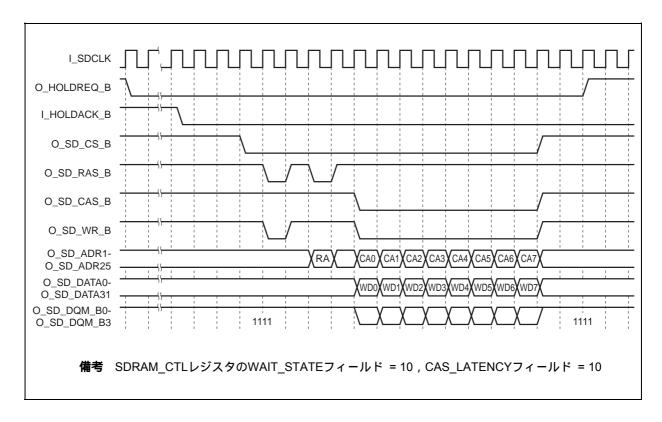

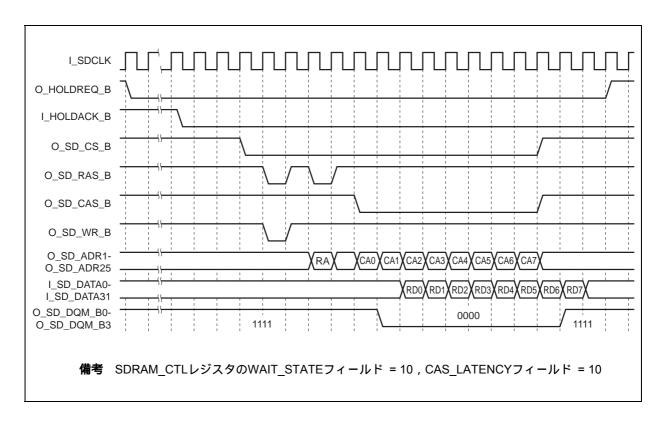

| CYCLE_LATENCY | R/W | PCIデバイスからの連続したメイン・メモリ(SDRAM)アクセスに対するレーテンシを設定しま |

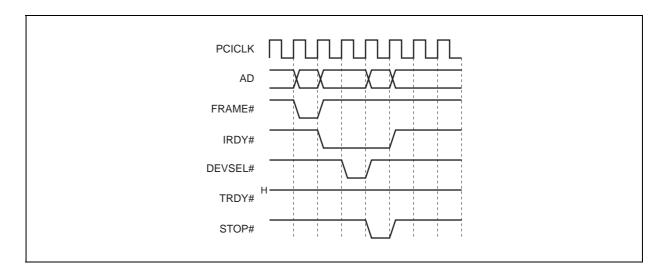

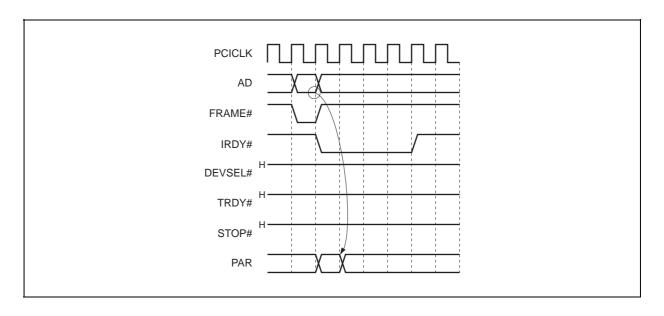

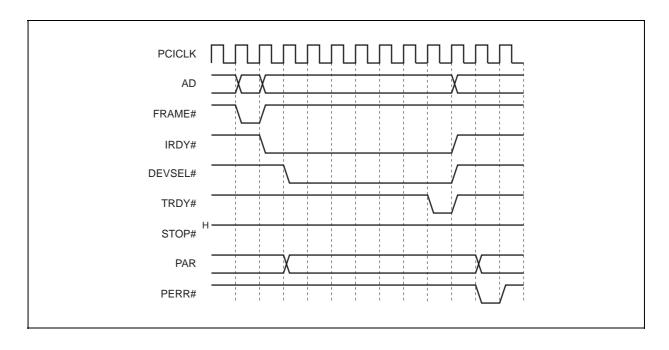

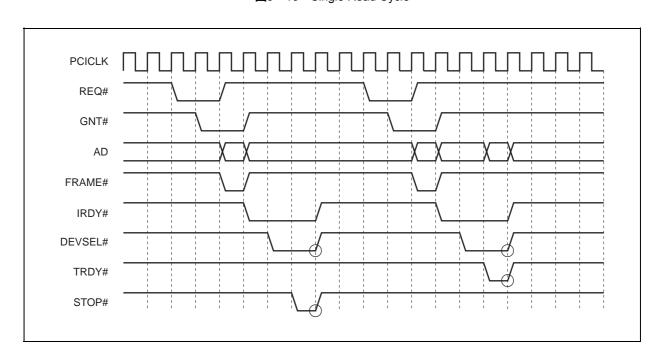

|               |     | す。                                             |