# Tsi110™ Software Initialization Application Note

80E5000\_AN002\_03

October 2009

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775

Printed in U.S.A.

©2009 Integrated Device Technology, Inc.

#### GENERAL DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### CODE DISCLAIMER

Code examples provided by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of the code examples below is completely at your own risk. IDT MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. FURTHER, IDT MAKES NO REPRESENTATIONS OR WARRANTIES AS TO THE TRUTH, ACCURACY OR COMPLETENESS OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR THAT IS CONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, INDIRECT, PUNITIVE OR SPECIAL DAMAGES, HOWEVER THEY MAY ARISE, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES. The code examples also may be subject to United States export control laws and may be subject to the export or import laws of other countries and it is your responsibility to comply with any applicable laws or regulations.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- 1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

IDT, the IDT logo, and Integrated Device Technology are trademarks or registered trademarks of Integrated Device Technology, Inc.

# **Contents**

| 1. | Inte | rnal R              | Register Access                                                    | 7  |  |  |  |  |

|----|------|---------------------|--------------------------------------------------------------------|----|--|--|--|--|

|    | 1.1  | Device              | e Register Map                                                     | 7  |  |  |  |  |

|    | 1.2. | Require             | red Initialization from PCI/X and Processor Interface              | 8  |  |  |  |  |

|    |      | 1.2.1               | How to Initialize from the Process Bus Interface                   | 8  |  |  |  |  |

|    |      | 1.2.2               | How to Initialize from the PCI/X Bus                               | 9  |  |  |  |  |

| 2. | Por  | t-to-Po             | ort Access                                                         | 11 |  |  |  |  |

|    | 2.1. | Process             | sor to Memory Controller (Direct Path)                             | 11 |  |  |  |  |

|    |      | 2.1.1               | How to Initialize the Processor Bus to SDRAM BARs                  | 12 |  |  |  |  |

|    |      | 2.1.2               | Processor to Memory Controller (Direct Path) Examples              | 14 |  |  |  |  |

|    | 2.2. | Process             | sor to Memory Controller (Non-direct Path)                         | 16 |  |  |  |  |

|    |      | 2.2.1               | How to Initialize the Processor Bus to SDRAM Non-direct Path       | 18 |  |  |  |  |

|    |      | 2.2.2               | Processor to Memory Controller (Non-direct) Examples               | 21 |  |  |  |  |

|    | 2.3. | Process             | sor to PCI/X                                                       | 24 |  |  |  |  |

|    |      | 2.3.1               | How to Initialize the Processor Bus to PCI/X Path                  | 25 |  |  |  |  |

|    |      | 2.3.2               | Processor to PCI/X Examples                                        | 25 |  |  |  |  |

|    |      | 2.3.3               | Additional Switch Fabric to PCI/X Transaction Mapping Capabilities | 28 |  |  |  |  |

|    |      | 2.3.4               | How to Initialize the Switch Fabric to PCI/X Transaction Mapping   | 29 |  |  |  |  |

|    | 2.4. | Switch              | Fabric to PCI/X Configuration Cycle Example                        | 32 |  |  |  |  |

|    | 2.5  | .5 Processor to HLP |                                                                    |    |  |  |  |  |

|    |      | 2.5.1               | How to Initialize the Processor Bus to HLP Path                    | 35 |  |  |  |  |

|    |      | 2.5.2               | Processor to HLP Examples (After Initial BOOT)                     | 35 |  |  |  |  |

|    | 2.6. | PCI/X               | to Memory Controller (Non-snoop Path)                              |    |  |  |  |  |

|    |      | 2.6.1               | How to Initialize the PCI/X Bus to SDRAM Non-snoop Path            |    |  |  |  |  |

|    |      | 2.6.2               | PCI/X to Memory Controller (Non-snoop) Example                     | 44 |  |  |  |  |

|    | 2.7. | PCI/X               | to Memory Controller (Snoop Path)                                  | 46 |  |  |  |  |

|    |      | 2.7.1               | How to Initialize the PCI/X Bus to SDRAM Snoop Path                |    |  |  |  |  |

|    |      | 2.7.2               | PCI/X to Memory (Snoop) Example                                    |    |  |  |  |  |

|    | 2.8. | PCI/X               | to HLP.                                                            |    |  |  |  |  |

|    |      | 2.8.1               | How to Initialize the PCI/X Bus to HLP Path                        |    |  |  |  |  |

|    |      | 2.8.2               | PCI/X to HLP Example                                               |    |  |  |  |  |

|    | 2.0  | Etherne             | et Controller to Memory                                            |    |  |  |  |  |

4 Contents

# **About this Document**

This section discusses the following topics:

- "Scope" on page 5

- "Revision History" on page 5

# Scope

This document explains how to write initialization software for use with the Tsi110, such as how to access its registers from the PCI/X and Processor Interfaces. It also describes the Tsi110's main data paths and how to program its registers for efficient port-to-port access.

# **Revision History**

#### 80E5000\_AN002\_03, Formal, October 2009

This version of the document was rebranded as IDT. It does not include any technical changes.

#### 80E5000\_AN002\_02, Formal, March 2007

Changed item 3 in Figures 9 and 10 to indicate "The Switch Fabric address forwarded to the HLP Interface." This item previously incorrectly indicated the address was forwarded to the PCI/X Interface.

#### 80E5000\_AN002\_01, Formal, February 2007

This is the first version of the *Tsi110 Software Initialization Application Note*.

6 About this Document

# 1. Internal Register Access

This section describes how to access the Tsi110's registers in order to place the device in an operational state. It is assumed that the correct hardware configuration has been chosen for the given design. For information on the complete Tsi110 programming model, see the Register section of the *Tsi110 User Manual*.

Using software, the Tsi110 register space can be configured from the PCI/X, Processor, or I<sup>2</sup>C Interface depending on the system architecture requirements. The I<sup>2</sup>C Interface, however, can only initialize a sub-set of the Tsi110's registers. For information on initializing the Tsi110's registers through the I<sup>2</sup>C Interface, see the I<sup>2</sup>C Interface section of the *Tsi110 User Manual*.

In order to initialize the Tsi110, the user must have a detailed understanding of the *Tsi110 User Manual*, relevant bus specifications, and overall system configuration.

# 1.1 Device Register Map

The Tsi110 contains 64 Kbytes of internal register space for initialization and configuration. Each of the Tsi110's interfaces has a separate register block, as indicated in Table 1.

Table 1: Device Register Map

| Address[15:0] <sup>a</sup> | Register Block              |

|----------------------------|-----------------------------|

| 0x0000 — 0x0FFF            | HLP Interface               |

| 0x1000 – 0x1FFF            | PCI/X Interface             |

| 0x2000 – 0x2FFF            | Clock Generator             |

| 0x3000 – 0x3FFF            | Processor Interface         |

| 0x4000 – 0x4FFF            | Memory Controller           |

| 0x5000 – 0x5FFF            | DMA Controller              |

| 0x6000 – 0x6FFF            | Ethernet Controller         |

| 0x7000 – 0x73FF            | I <sup>2</sup> C Controller |

| 0x7400 – 0x77FF            | Interrupt Controller        |

| 0x7800 – 0x79FF            | UART 0 Interface            |

| 0x7A00 – 0x7BFF            | GPIO Interface              |

| 0x7C00 – 0x7FFF            | UART 1 Interface            |

a. The Address bus in the table defines the 16 least significant bits of the Address bus. For example, when accessing Tsi110's registers from the PCI/X bus this would be AD[15:0]. When accessing the Tsi110 from the Processor bus it would be processor address bits A[20:35] for a 36-bit processor, and processor address bits A[16:31] for a 32-bit processor.

# 1.2. Required Initialization from PCI/X and Processor Interface

This section describes the necessary register accesses that the Tsi110 must receive to enable its registers to be visible from the PCI/X Interface and the Processor Interface.

#### 1.2.1 How to Initialize from the Process Bus Interface

The PB\_REG\_BAR register (offset 0x410) must be programmed in order to get access to the 64 Kbytes of internal register space (see Table 2). The PB\_REG\_BAR window differs from other address windows because it is enabled upon power-up. The reset value for PB\_REG\_BAR is 0xC000\_0001.

PB\_REG\_BAR[BA] must be initialized in order for the Tsi110 to know what address range to decode for access to the Tsi110 registers. If the Processor is operating in 36-bit mode the base address upper field, BA\_UPPER, is required as well. Once these fields are programmed, Tsi110's register space is accessible from the Processor bus.

**Table 2: Processor Bus Register Access**

| Register   | Field         | Description                                                                                                                                                                                                                                   |

|------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB_REG_BAR | BA[4:19]      | Base Address: These bits are compared with processor address bits A[4:19] when connected to a 36-bit processor bus or A[0:15] when connected to a 32-bit processor bus to determine if the transaction falls within the PB_REG_BAR.           |

| PB_REG_BAR | BA_UPPER[0:3] | Base Address Upper: When the processor is operating in 36-bit mode these bits are compared with processor address bus bits A[0:3] to determine if the transaction falls within the PB_REG_BAR. These bits are ignored in 32-bit address mode. |

| PB_REG_BAR | END_MODE[1:0] | Endian Mode: These bits allow for swapping between Big-endian and Little-endian mode. These bits should be programmed based on whether the processor is operating in Big-endian or Little-endian mode.                                        |

| PB_REG_BAR | EN            | Enable: This bit is written to enable/disable the PB_REG_BAR.                                                                                                                                                                                 |

#### 1.2.2 How to Initialize from the PCI/X Bus

The following Tsi110 registers must be accessed through PCI/X configuration cycles in order to get access to the 64 Kbytes of internal register space:

- 1. PE\_CSR[MS] (offset 0x004) must be enabled to allow the Tsi110 to accept memory cycles as a PCI/X target (see Table 3).

- 2. MISC\_CSR[BAR0\_EN] (offset 0x040) must be enabled to allow write access to PCI Base Address Register 0 and PCI Base Address Upper Register 0.

- 3. The base address field (BA[31:16]) within P2O\_BAR0 (offset 0x010) and the upper base address field (BA[63:32]) within P2O\_BAR0\_UPPER (offset 0x014) must be initialized for the Tsi110 to know what address range to decode for access to its registers. Once these fields are programmed, Tsi110's 64 Kbytes of register space is accessible from the PCI/X bus through memory cycles.

Table 3: PCI/X Bus Register Access

| Register       | Field     | Description                                                                                                                                                                                                                                                                     |

|----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PE_CSR         | MS        | Memory Space Enable: This bit is written to allow the Tsi110 to accept memory cycles as a PCI/X target.                                                                                                                                                                         |

| MISC_CSR       | BAR0_EN   | Base Address Register 0 Enable: This register must be enabled so that the P2O_BAR0 and P2O_BAR0_UPPER registers are visible in PCI/X configuration space. If this bit is cleared reads to the P2O_BAR0 and P2O_BAR0_UPPER registers will return zero and writes have no effect. |

| P20_BAR0       | BA[31:16] | Base Address: These bits are compared with PCI/X address bits A[31:16] to determine if the transaction falls within the 64-bit register bar.                                                                                                                                    |

| P2O_BAR0_UPPER | BA[63:32] | Base Address Upper: These bits are compared with PCI/X address bits A[63:32] to determine if the transaction falls within the 64-bit register bar.                                                                                                                              |

In order for port-to-port access to occur through the Tsi110, certain registers must be initialized with software. This section describes the necessary accesses to Tsi110's registers to allow port-to-port communication. It explains the various paths through the device and the register settings required to access these paths.

The main Tsi110 data paths are indicated in the following list. The remainder of this section describes the required Tsi110 register settings to enable access through these data paths:

- 1. Processor Interface to Memory Controller (Direct path)

- 2. Processor Interface to Memory Controller (Non-direct path)

- 3. Processor Interface to PCI/X Interface

- 4. Processor Interface to HLP Interface

- 5. PCI/X Interface to Memory Controller (Non-Snoop path)

- 6. PCI/X Interface to Memory Controller (Snoop path)

- 7. PCI/X Interface to HLP Interface

- 8. Ethernet Controller to Memory Controller (Transmit and Receive paths)

For all accesses through the Memory Controller to SDRAM it is assumed that the specific memory configuration has already been configured. The configuration of the Memory Controller registers depends on the type of system memory used and where it is located.

When the Tsi110 is connected to a 36-bit processor, Tsi110 bits PB\_A[0:35] connect to Processor Bus bits A[0:35]. When the Tsi110 is connected to a 32-bit processor, Tsi110 bits PB\_A[4:35] are connected to Processor Bus bits A[0:31] and PB\_A[0:3] should be pulled low on the board.

# 2.1. Processor to Memory Controller (Direct Path)

In order to communicate through the Tsi110 from the Processor bus directly to memory (Direct path) through the Memory Controller, a Processor bus to SDRAM base address register must be initialized with software. This base address register defines an address range (in Processor bus address space) where the Tsi110 responds to a Processor's request. If the Processor's request falls within one of the Tsi110 Processor bus to SDRAM base address ranges, the transaction is forwarded through the Memory Controller to memory (SDRAM). The Tsi110 supports two Processor Bus to SDRAM base address registers: PB\_SDRAM\_BAR1 (offset 0x41C) and PB\_SDRAM\_BAR2 (offset 0x420) (see Tables 4, 5, and 6).

#### 2.1.1 How to Initialize the Processor Bus to SDRAM BARs

The Processor bus to SDRAM BARs can be initialized using PCI/X memory write cycles from the PCI/X bus through the P2O\_BAR0 and P2O\_BAR0\_UPPER registers, or from the Processor bus through the PB\_REG\_BAR. Table 4 describes the internal register settings associated with mapping Processor bus transactions directly to memory (SDRAM) through the Memory Controller.

Table 4: PB SDRAM Base Address Register Initialization

| Register <sup>a</sup> | Field         | Description                                                                                                                                                                                                                                      |

|-----------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB_SDRAM_BAR[1:2]     | BA[4:7]       | Base Address: These bits are compared with processor address bits A[4:7] when connected to a 36-bit processor bus or A[0:3] when connected to a 32-bit processor bus to determine if the transaction falls within the PB_SDRAM_BAR.              |

| PB_SDRAM_BAR[1:2]     | TA[4:7]       | Translation Address: When address translation is enabled (ATE set to 1), these bits replace processor address bits A[4:7] when connected to a 36-bit processor bus or A[0:3] when connected to a 32-bit processor bus to address memory (SDRAM). |

| PB_SDRAM_BAR[1:2]     | ATE           | Address Translation Enable: When enabled the TA and TA_UPPER fields replace the appropriate processor bus address when forwarding to memory (SDRAM).                                                                                             |

| PB_SDRAM_BAR[1:2]     | BA_UPPER[0:3] | Base Address Upper: When the processor is operating in 36-bit mode these bits are compared with processor address bus bits A[0:3] to determine if the transaction falls within the PB_SDRAM_BAR. These bits are ignored in 32-bit address mode.  |

| PB_SDRAM_BAR[1:2]     | TA_UPPER[0:3] | Translation Address Upper: When address translation is enabled (ATE set to 1), these bits replace processor address bits A[0:3] when the processor bus is operating in 36-bit mode to address memory (SDRAM).                                    |

| PB_SDRAM_BAR[1:2]     | SIZE[3:0]     | Size: These bits define the PB_SDRAM_BAR window size, see Tables 5 and 6.                                                                                                                                                                        |

| PB_SDRAM_BAR[1:2]     | WR_PRTC       | Write Protect: This bit indicates whether the address window is write-protected. If enabled the address window is write-protected and any writes to it will cause an error.                                                                      |

| PB_SDRAM_BAR[1:2]     | EN            | Enable: This bit enables the PB_SDRAM_BAR address window.                                                                                                                                                                                        |

a. The Tsi110 supports two Processor to SDRAM base address windows.

Table 5: PB\_SDRAM\_BAR Address Window Size for 36-bit Processors

| SIZE[3:0]         | Window Size (Bytes) | Active BAR<br>(32-bit mode, 36-bit mode) | Offset<br>(32-bit mode, 36-bit mode) |

|-------------------|---------------------|------------------------------------------|--------------------------------------|

| 0000              | 256M                | A[4:7], A[0:7]                           | A[8:35], A[8:35]                     |

| 0001              | 512M                | A[4:6], A[0:6]                           | A[7:35], A[7:35]                     |

| 0010              | 1G                  | A[4:5], A[0:5]                           | A[6:35], A[6:35]                     |

| 0011              | 2G                  | A[4], A[0:4]                             | A[5:35], A[5:35]                     |

| 0100 <sup>a</sup> | 4G                  | NA, A[0:3]                               | A[4:35}, A[4:35]                     |

| 0101              | 8G                  | NA, A[0:2]                               | NA, A[3:35]                          |

| 0110              | 16G                 | NA, A[0:1]                               | NA, A[2:35]                          |

| 0111              | 32G                 | NA, A[0]                                 | NA, A[1:35]                          |

| 1000 <sup>b</sup> | 64G                 | NA, NA                                   | NA, A[0:35]                          |

a. If extended addressing (36-bit mode) is disabled in the processor and the SIZE is 4'b0100, then any address on the processor bus is claimed by the Tsi110 and forwarded to memory.

Table 6: PB\_SDRAM\_BAR Address Window Size for 32-bit Processors

| SIZE[3:0]         | Window Size (Bytes) | Active BAR | Offset  |

|-------------------|---------------------|------------|---------|

| 0000              | 256M                | A[0:3]     | A[4:31] |

| 0001              | 512M                | A[0:2]     | A[3:31] |

| 0010              | 1G                  | A[0:1]     | A[2:31] |

| 0011              | 2G                  | A[0]       | A[1:31] |

| 0100 <sup>a</sup> | 4G                  | NA         | A[0:31] |

a. If the SIZE is 4'b0100 then any address on the processor bus is claimed by the Tsi110 and forwarded to memory.

b. If extended addressing is enabled in the processor and the SIZE is 4'b1000, then any address on the processor bus is claimed by the Tsi110 and forwarded to memory.

RENESAS

#### 2.1.2 Processor to Memory Controller (Direct Path) Examples

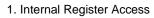

**Example 1:** 36-bit Processor with extended addressing enabled, access to memory through the Direct path from the processor bus.

In this example a 256-Mbyte window is configured using the PB\_SDRAM\_BAR2 register. All processor bus accesses that fall within that window are forwarded directly to the Memory Controller and onto memory. The values programmed in the PB\_SDRAM\_BAR2 for this example will forward all processor bus addresses that fall within 36'h1\_1000\_0000 – 36'h1\_1FFF\_FFFF directly to the Memory Controller as 36'hA\_0000\_0000 – 36'hA\_0FFF\_FFFF. Using the PB\_SDRAM\_BAR2 register the following fields are programmed as described below. Figure 1 shows the address translation process resulting from a Processor bus address (36'h1\_1F00\_0004) hitting the PB\_SDRAM\_BAR2.

Register settings:

• **PB\_SDRAM\_BAR2:** BA = 4'h1; TA = 4'h0; ATE = 1; BA\_UPPER = 4'h1; TA\_UPPER = 4'hA; SIZE = 4'h0 (256M); WR\_PRTC = 0; EN = 1

Figure 1: Direct Path Address Translation Process, 36-bit Processor

1. Processor Bus address hitting the PB SDRAM BAR

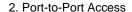

**Example 2**: 32-bit Processor, access to memory through the Direct path from the processor bus.

In this example a 256-Mbyte window is configured using the Tsi110 PB\_SDRAM\_BAR2 register. All processor bus accesses that fall within that window are forwarded directly to the Memory Controller and onto memory. The values programmed in the PB\_SDRAM\_BAR2 for this example will forward all processor bus addresses that fall within 32'h1000\_0000 – 32'h1FFF\_FFFF directly to the Memory Controller as 32'h3000\_0000 – 32'h3FFF\_FFFF. Using the PB\_SDRAM\_BAR2 register the following fields are programmed as described below. Figure 2 shows the address translation process resulting from a Processor bus address (32'h1E00\_0008) hitting the PB\_SDRAM\_BAR2.

#### Register settings:

• **PB\_SDRAM\_BAR2:** BA = 4'h1; TA = 4'h3; ATE = 1; SIZE = 4'h0 (256M); WR\_PRTC = 0; EN = 1

Figure 2: Direct Path Address Translation Process, 32-bit Processor

1. Processor Bus address hitting the PB\_SDRAM\_BAR

**Note:** The upper 4 address bits are pulled down on the board and passed to the Memory Controller.

# 2.2. Processor to Memory Controller (Non-direct Path)

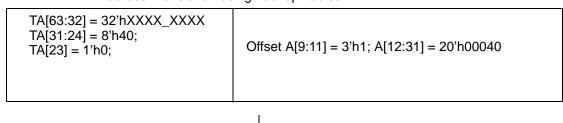

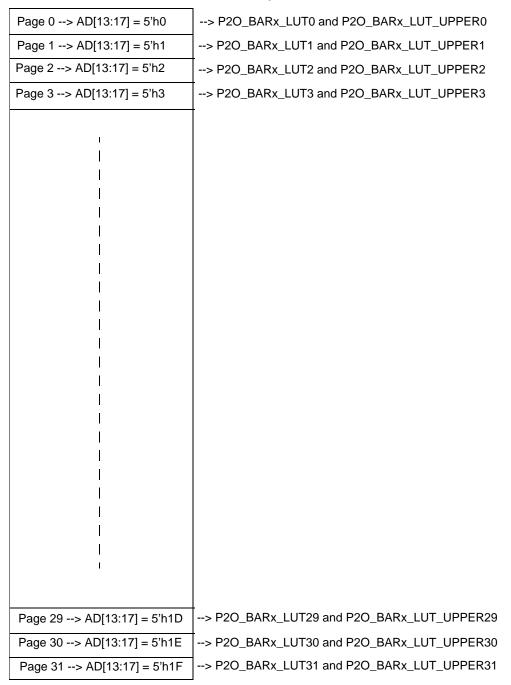

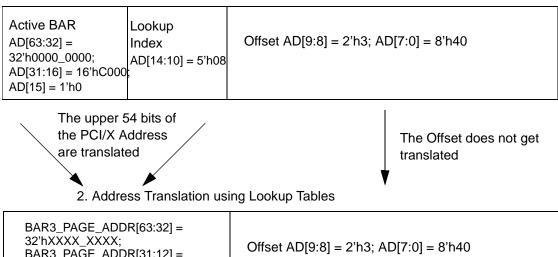

In order to communicate from the Processor bus through the Switch Fabric to memory (Non-direct path) through the Memory Controller, the following registers must be initialized: one of the PB to Switch Fabric Base Address Registers (PB\_OCN\_BARx), as well as the associated PB Switch Fabric BAR Lower (PB\_BARx\_LOWER\_LUT\_ADDRy) and Upper (PB\_BARx\_UPPER\_LUT\_ADDRy) Lookup Table Address Registers. A PB to Switch Fabric base address register defines an address range (in Processor bus address space) where the Tsi110 responds to a Processor's request.

If the processor's request falls within one of the Tsi110's PB to Switch Fabric base address ranges, the transaction is forwarded to the Tsi110 Switch Fabric. The Tsi110 supports two unique PB to Switch Fabric BARs: PB\_OCN\_BAR1 (offset 0x414) and PB\_OCN\_BAR2 (offset 0x418) (see Tables 7 to 10).

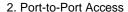

In order to direct the request from the Switch Fabric to another Tsi110 interface the address must be translated. The PB Switch Fabric BAR Upper and Lower Lookup Table Address Registers must be programmed to provide the proper address translation to target the Memory Controller to memory. Each of the PB to Switch Fabric BARs (PB\_OCN\_BAR1 and PB\_OCN\_BAR2) can have up to 32 pages of memory associated with them. The PB to Switch Fabric BAR Upper and Lower Lookup Tables make up those 32 pages, each individual page of memory requires an initialization of an Upper and Lower BAR Lookup (see Figure 3 along with Tables 11 and 12).

The PB to Switch Fabric BAR Upper and Lower Lookup Table Address Registers (PB\_BAR[1:2]\_LOWER\_LUT\_ADDR{0:31} and PB\_BAR[1:2]\_UPPER\_LUT\_ADDR{0:31}) are located in the Processor bus register block at offsets 0x800 – 0x9FC.

#### Figure 3: PB to Switch Fabric BAR Lookup Table Addressing

This example describes the Page addressing and address translation process for a 256M window, processor operating in 36-bit mode.

#### **Lookup Tables used for address translation**

#### 2.2.1 How to Initialize the Processor Bus to SDRAM Non-direct Path

The PB to Switch Fabric Base Address, PB Switch Fabric BAR Upper and Lower Lookup Table Address Registers can be initialized using PCI/X memory write cycles from the PCI/X bus through the P2O\_BAR0 and P2O\_BAR0\_UPPER Registers, or from the Processor bus through the PB\_REG\_BAR. Tables 7 to 13 describe the internal register settings associated with mapping Processor Bus transactions through the Switch Fabric to the Memory Controller and onto memory.

Table 7: PB Switch Fabric Base Address Register 1 Initialization

| Register                 | Field         | Description                                                                                                                                                                                                                                |

|--------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB_OCN_BAR1 <sup>a</sup> | BA[4:7]       | Base Address: These bits are compared with processor address bits A[4:7] when connected to a 36-bit processor bus or A[0:3] when connected to a 32-bit processor bus to determine if the transaction falls within PB_OCN_BAR1.             |

| PB_OCN_BAR1              | BA_UPPER[0:3] | Base Address Upper: When the processor is operating in 36-bit mode these bits are compared with processor address bus bits A[0:3] to determine if the transaction falls within PB_OCN_BAR1. These bits are ignored in 32-bit address mode. |

| PB_OCN_BAR1              | SIZE[3:0]     | Size: These bits define the PB_OCN_BAR1 window size, see Tables 9 and 10.                                                                                                                                                                  |

| PB_OCN_BAR1              | воот          | Boot from HLP Interface: Used for booting the processor from the Host Local Port (HLP) Interface. When enabled all processor bus accesses to PB_OCN_BAR1 are forwarded to the HLP Interface as well as:                                    |

|                          |               | All memory regions are write-protected                                                                                                                                                                                                     |

|                          |               | Tsi110 lookup tables are not used                                                                                                                                                                                                          |

|                          |               | Endian mode is set as "packet swap"  Add to SE                                                                                                                                                                                             |

|                          |               | <ul> <li>Address bits, indicated by signals PB_A[16:35], are used as the<br/>offset; the remainder of the address is zero.</li> </ul>                                                                                                      |

|                          |               | <b>Note</b> : Software must clear this bit after the processor finishes booting from the HLP and the PB_LOWER_LUT_ADDRx/PB_UPPER_LUT_ADDRx registers are programmed.                                                                       |

|                          |               | Caution: When BOOT is 0, PB_OCN_BAR1 must not be accessed until the corresponding lookup table registers, PB_UPPER_LUT_ADDRx and PB_LOWER_LUT_ADDRx, are programmed. This sequence must be followed or Tsi110 behavior is undefined.       |

| PB_OCN_BAR1              | EN            | Enable: This bit enables the PB_OCN_BAR1.                                                                                                                                                                                                  |

a. The PB\_OCN\_BAR1 register differs from PB\_OCN\_BAR2 in that it comes up enabled and at a pre-defined base address to the HLP Interface for accessing boot-up flash. The PB\_OCN\_BAR1's reset value is 0xF000\_0003.

#### Table 8: PB Switch Fabric Base Address Register 2 Initialization

| Register                 | Field         | Description                                                                                                                                                                                                                                |

|--------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB_OCN_BAR2 <sup>a</sup> | BA[4:7]       | Base Address: These bits are compared with processor address bits A[4:7] when connected to a 36-bit processor bus or A[0:3] when connected to a 32-bit processor to determine if the transaction falls within PB_OCN_BAR2.                 |

| PB_OCN_BAR2              | BA_UPPER[0:3] | Base Address Upper: When the processor is operating in 36-bit mode these bits are compared with processor address bus bits A[0:3] to determine if the transaction falls within PB_OCN_BAR2. These bits are ignored in 32-bit address mode. |

| PB_OCN_BAR2              | SIZE[3:0]     | Size: These bits define the PB_OCN_BAR2 window size, see Tables 9 and 10.                                                                                                                                                                  |

| PB_OCN_BAR2              | EN            | Enable: This bit enables the PB_OCN_BAR2.                                                                                                                                                                                                  |

a. The PB\_OCN\_BAR2 register's reset value is 0x0000\_0000.

Table 9: PB\_OCN\_BAR[1:2] Window Size for 36-bit Processors

| Size[3:0]         | Window Size<br>(Bytes) | Page Size (Bytes) | Active BAR<br>(32-bit, 36-bit<br>mode) | Lookup Index <sup>a</sup><br>(32-bit, 36-bit<br>mode) | Offset<br>(32-bit, 36-bit<br>mode) |

|-------------------|------------------------|-------------------|----------------------------------------|-------------------------------------------------------|------------------------------------|

| 0000              | 256M                   | 8M                | A[4:7], A[0:7]                         | A[8:12], A[8:12]                                      | A[13:35],A[13:35]                  |

| 0001              | 512M                   | 16M               | A[4:6], A[0:6]                         | A[7:11], A[7:11]                                      | A[12:35],A[12:35]                  |

| 0010              | 1G                     | 32M               | A[4:5], A[0:5]                         | A[6:10], A[6:10]                                      | A[11:35],A[11:35]                  |

| 0011              | 2G                     | 64M               | A[4], A[0:4]                           | A[5:9], A[5:9]                                        | A[10:35],A[10:35]                  |

| 0100 <sup>b</sup> | 4G                     | 128M              | NA, A[0:3]                             | A[4:8], A[4:8]                                        | A[9:35],A[9:35]                    |

| 0101              | 8G                     | 256M              | NA, A[0:2]                             | NA, A[3:7]                                            | NA, A[8:35]                        |

| 0110              | 16G                    | 512M              | NA, A[0:1]                             | NA, A[2:6]                                            | NA, A[7:35]                        |

| 0111              | 32G                    | 1G                | NA, A[0]                               | NA, A[1:5]                                            | NA, A[6:35]                        |

| 1000 <sup>c</sup> | 64G                    | 2G                | NA, NA                                 | NA, A[0:4]                                            | NA, A[5:35]                        |

a. The address bits that comprise the Lookup Index define which page within the window the access is destined for. Each PB\_OCN\_BAR window is comprised of 32 distinct memory pages.

b. If extended addressing (36-bit mode) is disabled in the processor and the SIZE is 4'b0100, then any address on the processor bus is claimed by the Tsi110 and forwarded to the Switch Fabric.

c. If extended addressing is enabled in the processor and the SIZE is 4'b1000, then any address on the processor bus is claimed by the Tsi110 and forwarded to the Switch Fabric.

Table 10: PB\_OCN\_BAR[1:2] Window Size for 32-bit Processors

| Size[3:0]         | Window Size<br>(Bytes) | Page Size (Bytes) | Active BAR | Lookup Index | Offset  |

|-------------------|------------------------|-------------------|------------|--------------|---------|

| 0000              | 256M                   | 8M                | A[0:3]     | A[4:8]       | A[9:31] |

| 0001              | 512M                   | 16M               | A[0:2]     | A[3:7]       | A[8:31] |

| 0010              | 1G                     | 32M               | A[0:1]     | A[2:6]       | A[7:31] |

| 0011              | 2G                     | 64M               | A[0]       | A[1:5]       | A[6:31] |

| 0100 <sup>a</sup> | 4G                     | 128M              | NA         | A[0:4]       | A[5:31] |

a. If the SIZE is 4'b0100 then any address on the processor bus is claimed by the Tsi110 and forwarded to the Switch Fabric.

Table 11: PB Switch Fabric BAR Lower Lookup Table Address Register Initialization

| Register                            | Field         | Description                                                                                                                                                              |

|-------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB_BAR[1:2]_LOWER_<br>LUT_ADDR{031} | TA[31:23]     | Translation Address [31:23]: When the ATE bit is enabled these bits replace the processor bus address.                                                                   |

| PB_BAR[1:2]_LOWER_                  | END_MODE[1:0] | Endian Mode of destination Port:                                                                                                                                         |

| LUT_ADDR{031}                       |               | 00 = No Swap (data invariant)                                                                                                                                            |

|                                     |               | 01 = Endian Swap (swapping based on address and size of the transaction) used when processor is in Little-endian mode.                                                   |

|                                     |               | 10 = Packet swap (byte swap)                                                                                                                                             |

|                                     |               | 11 = Word swap (position of upper and lower 4 bytes reversed)                                                                                                            |

|                                     |               | <b>Note:</b> When swapping is enabled, some combinations of transaction alignments and sizes are not supported because they lead to non-contiguous bytes being accessed. |

| PB_BAR[1:2]_LOWER_<br>LUT_ADDR{031} | WR_PRTC       | Write Protect: When enabled this bit indicates the window is write-protected.  Note: Writing to a write-protected window will cause an error.                            |

| PB_BAR[1:2]_LOWER_<br>LUT_ADDR{031} | ATE           | Address Translation Enable: This bit when enabled enables the TA field TA[63:10] to overwrite the processor bus address.                                                 |

| PB_BAR[1:2]_LOWER_<br>LUT_ADDR{031} | DST_PORT[3:0] | Switch Fabric Destination Port Number: Each Tsi110 external interface is connected to a Switch Fabric port (see Table 13).                                               |

Table 12: PB Switch Fabric BAR Upper Lookup Table Address Register Initialization

| Register                            | Field     | Description                                                                                            |

|-------------------------------------|-----------|--------------------------------------------------------------------------------------------------------|

| PB_BAR[1:2]_UPPER_L<br>UT_ADDR{031} | TA[63:32] | Translation Address [63:32]: When the ATE bit is enabled these bits replace the processor bus address. |

| Table 13. | Switch | Eabric | Dort | <b>Encoding</b> |

|-----------|--------|--------|------|-----------------|

| Table 13: | Switch | rapric | POIT | Encoama         |

| DST_PORT[3:0] | Device Block                 |

|---------------|------------------------------|

| 0000          | HLP Interface                |

| 0001          | PCI/X Interface              |

| 0010          | Processor Interface (Master) |

| 0011          | Processor Interface (Slave)  |

| 0100          | Memory Controller            |

| 0101          | DMA Controller               |

| 0110          | Ethernet Controller          |

| 0111          | Reserved                     |

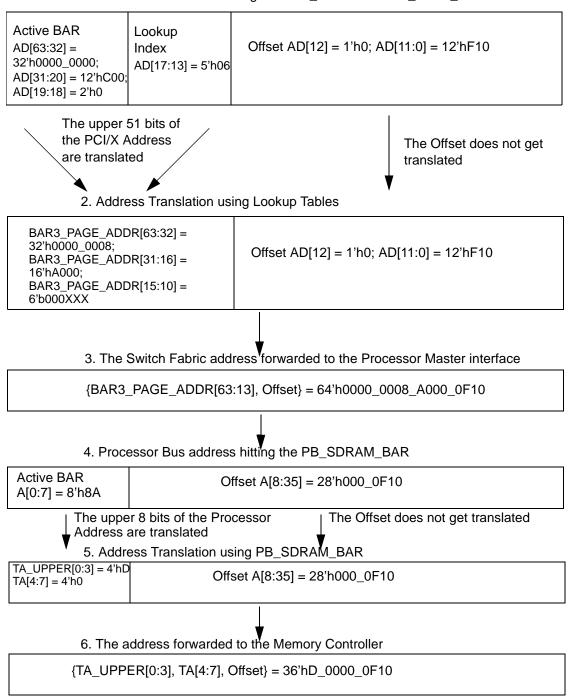

#### 2.2.2 Processor to Memory Controller (Non-direct) Examples

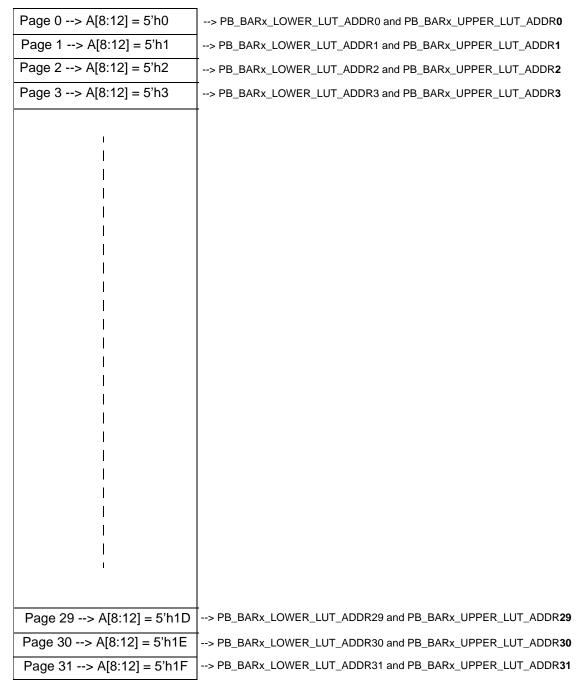

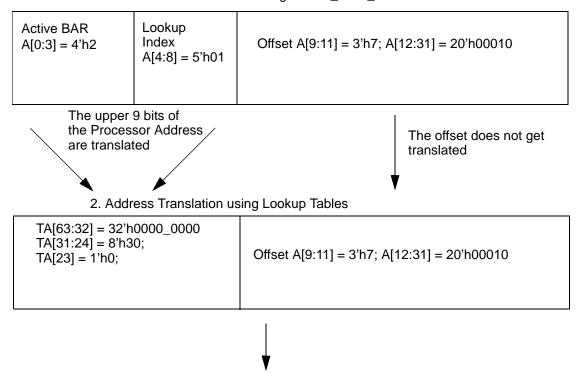

**Example 1:** 36-bit Processor with extended addressing enabled, access to memory through the Non-direct path from the processor bus.

In this example the PB\_OCN\_BAR2 window size has been programmed to 256M, all processor bus addresses that fall within 36'h1\_1000\_0000 – 36'h1\_1FFF\_FFFF will be accepted and forwarded through the Switch Fabric as indicated by the values programmed in the PB\_OCN\_BAR2 register below. Once the transaction has been accepted through the PB\_OCN\_BAR2 register it is up to the associated lookup tables to determine both the destination port and proper address translation. Since the window size programmed in the PB\_OCN\_BAR2 register is 256 Mbytes, that means there are 32, 8-Mbyte pages associated with that address window.

The PB\_BARx\_UPPER\_LUT\_ADDR{0..31} and PB\_BARx\_LOWER\_LUT\_ADDR{0..31} registers must be programmed to determine both the destination port and address translation associated with the 32 pages. In this example, only one 8-Mbyte page (page 0) of the 256-Mbyte window is configured to access memory, by programming the PB\_BAR2\_UPPER\_LUT\_ADDR0 and PB\_BAR2\_LOWER\_LUT\_ADDR0 registers, page 0 addresses memory as indicated by the DST\_PORT field (see Table 13). Address translation has been enabled and all Switch Fabric address accesses that address page 0 will be forwarded to the Memory Controller as 64'h0000\_000E\_1100\_0000 - 64'h0000\_000E\_117F\_FFFF.

Address hits to page 0 are determined as follows using the information provided in Table 9. Processor bits A[0:7] define the active BAR which in this example are defined as 8'h11. Processor bits A[8:12] define the lookup index (that is, what page the access is mapped to), in order to hit page 0, these bits need to be 5'h00. The remaining Processor bits A[13:35] define the address offset which in this case address the entire 8M page of memory. Figure 4 shows the address translation process resulting from a Processor bus address (36'h1\_1070\_0010) hitting the PB\_OCN\_BAR2.

RENESAS

Register settings:

- **PB\_OCN\_BAR2:** BA = 4'h1; BA\_UPPER = 4'h1; SIZE = 4'h0 (256M Window); EN = 1

- **PB\_BAR2\_UPPER\_LUT\_ADDR0:** TA[63:32] = 32'h0000\_000E

- **PB\_BAR2\_LOWER\_LUT\_ADDR0:** TA[31:24] = 8'h11, TA[23] = 1'h0; END\_MODE = 2'b00; WR\_PRTC = 0; ATE = 1; DST\_PORT = 4'b0100 (Memory Controller)

Figure 4: Non-direct Path Address Translation Process, 36-bit Processor

1. Processor bus address hitting the PB\_OCN\_BAR

3. The Switch Fabric address forwarded to the Memory Controller

$\{TA[63:23], Offset\} = 64'h0000\_000E\_1170\_0010$

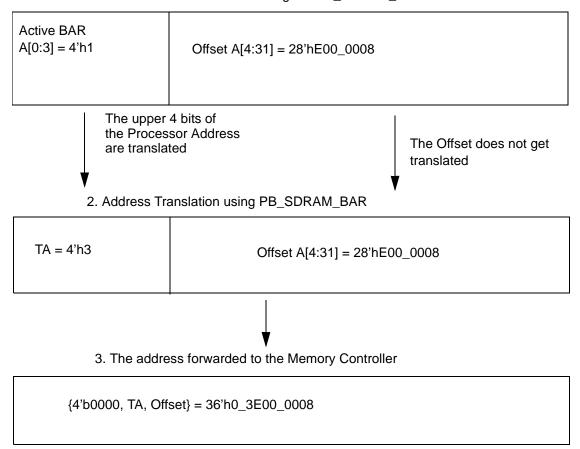

**Example 2**: 32-bit Processor, access to memory through the Non-direct path from the processor bus.

In this example the PB\_OCN\_BAR2 window size has been programmed to 256 Mbytes, all processor bus addresses that fall within 36'h2000\_0000 – 36'h2FFF\_FFFF will be accepted and forwarded through the Switch Fabric as indicated by the values programmed in the PB\_OCN\_BAR2 register below. Once the transaction has been accepted through the PB\_OCN\_BAR2 register it is up to the associated lookup tables to determine both the destination port and proper address translation. Since the window size programmed in the PB\_OCN\_BAR2 register is 256 Mbytes, that means there are 32, 8-Mbyte pages associated with that address window. The PB\_BARx\_UPPER\_LUT\_ADDR{0..31} and PB\_BARx\_LOWER\_LUT\_ADDR{0..31} registers must be programmed to determine both the destination port and address translation associated with those 32 pages.

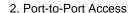

In this example only one 8-Mbyte page (page 1) of the 256-Mbyte window is configured to access memory (SDRAM), by programming the PB\_BAR2\_UPPER\_LUT\_ADDR1 and PB\_BAR2\_LOWER\_LUT\_ADDR1 registers, page 1 addresses memory as indicated by the DST\_PORT field (see Table 13). Address translation has been enabled and all Switch Fabric address accesses that address page 1 will be forwarded to the Memory Controller as 64'h0000\_0000\_3000\_0000 - 64'h0000\_0000\_307F\_FFFF. Address hits to page 1 are determined as follows using the information provided in Table 10. Processor bits A[0:3] define the active BAR which in this example are defined as 4'h2. Processor bits A[4:8] define the lookup index (that is, what page the access is mapped to), in order to hit page 1, these bits need to be 5'h01. The remaining Processor bits A[9:31] define the address offset which in this case address the entire 8-Mbyte page of memory. Figure 5 shows the address translation process resulting from a Processor bus address (32'h20F0\_0010) hitting the PB\_OCN\_BAR2.

#### Register settings:

- **PB\_OCN\_BAR2:** BA = 4'h2; SIZE = 4'h0 (256M Window); EN = 1

- **PB\_BAR2\_UPPER\_LUT\_ADDR1:** TA[63:32] = 32'h0000\_0000

- **PB\_BAR2\_LOWER\_LUT\_ADDR1:** TA[31:24] = 8'h30, TA[23] = 1'h0; END\_MODE = 2'b00; WR\_PRTC = 0; ATE = 1; DST\_PORT = 4'b0100 (Memory Controller)

Figure 5: Non-direct Path Address Translation Process, 32-bit Processor

1. Processor bus address hitting the PB\_OCN\_BAR

3. Switch Fabric address forwarded to the Memory Controller

$\{TA[63:23], Offset\} = 64'h0000_0000_3070_0010$

### 2.3. Processor to PCI/X

In order to communicate through the Tsi110 from the Processor bus through the Switch Fabric to the PCI/X Interface, the following registers must be initialized: a PB to Switch Fabric Base Address Register (PB\_OCN\_BARx), as well as the associated PB Switch Fabric BAR Lower (PB\_BARx\_LOWER\_LUT\_ADDRy) and Upper (PB\_BARx\_UPPER\_LUT\_ADDRy) Lookup Table Address Registers.

A PB to Switch Fabric BAR defines an address range (in Processor bus address space) where the Tsi110 responds to a Processor's request. If the Processor's request falls within one of the Tsi110's PB to Switch Fabric base address ranges, the transaction is forwarded to the Switch Fabric. The Tsi110 supports two unique PB to Switch Fabric BARs, PB\_OCN\_BAR1 (offset 0x414) and PB\_OCN\_BAR2 (offset 0x418).

In order to direct the request from the Switch Fabric to another Tsi110 interface the address must be translated. The PB Switch Fabric BAR Upper and Lower Lookup Table Address Registers must be programmed to provide the proper address translation to target the PCI/X Interface. Each of the PB to Switch Fabric BARs (PB\_OCN\_BAR1 and PB\_OCN\_BAR2) can have up to 32 pages of memory associated with them. The PB to Switch Fabric BAR Upper and Lower Lookup Tables make up those 32 pages, each individual page of memory requires an initialization of an Upper and Lower BAR Lookup. The PB to Switch Fabric BAR Upper and Lower Lookup Table Address Registers (PB\_BAR[1:2]\_LOWER\_LUT\_ADDR{0:31} and PB\_BAR[1:2]\_UPPER\_LUT\_ADDR{0:31}) are located in the Processor bus register block at offsets 0x800 - 0x9FC.

#### 2.3.1 How to Initialize the Processor Bus to PCI/X Path

The PB to Switch Fabric Base Address, PB Switch Fabric BAR Upper and Lower Lookup Table Address Registers can be initialized using PCI/X memory write cycles from the PCI/X bus through the P2O\_BAR0 and P2O\_BAR0\_UPPER registers, or from the Processor bus through the PB\_REG\_BAR. Tables 7 through 13 describe the internal register settings associated with mapping Processor bus transactions through the Switch Fabric to the PCI/X interface.

#### 2.3.2 Processor to PCI/X Examples

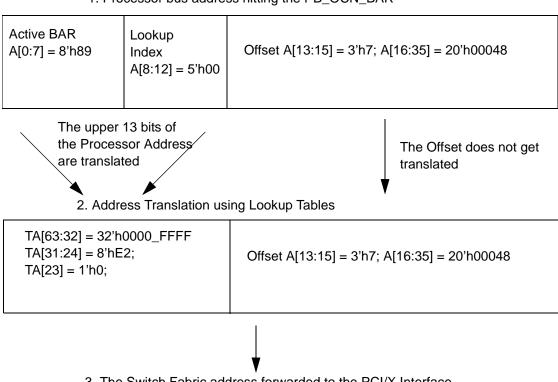

**Example 1:** 36-bit Processor with extended addressing enabled, access to PCI/X from the processor bus.

In this example the PB\_OCN\_BAR2 window size has been programmed to 256 Mbytes, all processor bus addresses that fall within 36'h8\_9000\_0000 – 36'h8\_9FFF\_FFFF will be accepted and forwarded through the Switch Fabric as indicated by the values programmed in the PB\_OCN\_BAR2 register below. Once the transaction has been accepted through the PB\_OCN\_BAR2 register it is up to the associated lookup tables to determine both the destination port and proper address translation. Since the window size programmed in the PB\_OCN\_BAR2 register is 256 Mbytes, that means there are 32, 8-Mbyte pages associated with that address window. The PB\_BARx\_UPPER\_LUT\_ADDR{0..31} and PB\_BARx\_LOWER\_LUT\_ADDR{0..31} registers must be programmed to determine both the destination port and address translation associated with those 32 pages.

In this example only one 8-Mbyte page (page 0) of the 256-Mbyte window is configured to access the PCI/X Interface, by programming the PB\_BAR2\_UPPER\_LUT\_ADDR0 and PB\_BAR2\_LOWER\_LUT\_ADDR0 registers, page 0 addresses the PCI/X port as indicated by the DST\_PORT field (see Table 13). Address translation has been enabled and all Switch Fabric address accesses that address page 0 will be forwarded to the PCI/X Interface as 64'h0000\_FFFF\_E200\_0000 – 64'h0000\_FFFF\_E27F\_FFFF. Address hits to page 0 are determined as follows using the information provided in Table 9. Processor bits A[0:7] define the active BAR which in this example are defined as 8'h89. Processor bits A[8:12] define the lookup index (that is, what page the access is mapped to), in order to hit page 0, these bits need to be 5'h00. The remaining Processor bits A[13:35] define the address offset which in this case address the entire 8-Mbyte page of memory. Figure 6 shows the address translation process resulting from a Processor bus address (36'h8\_9070\_0048) hitting the PB\_OCN\_BAR2.

Register settings:

- **PB\_OCN\_BAR2:** BA = 4'h9; BA\_UPPER = 4'h8; SIZE = 4'h0 (256M Window); EN = 1

- **PB\_BAR2\_UPPER\_LUT\_ADDR0:** TA[63:32] = 32'h0000\_FFFF

- **PB\_BAR2\_LOWER\_LUT\_ADDR0:** TA[31:24] = 8'hE2, TA[23] = 1'h0; END\_MODE = 2'b00; WR PRTC = 0; ATE = 1; DST PORT = 4'b0001 (PCI/X Interface)

Figure 6: PCI/X Path Address Translation Process, 36-bit Processor

1. Processor bus address hitting the PB\_OCN\_BAR

3. The Switch Fabric address forwarded to the PCI/X Interface

$\{TA[63:23], Offset\} = 64'h0000\_FFFF\_E270\_0048$

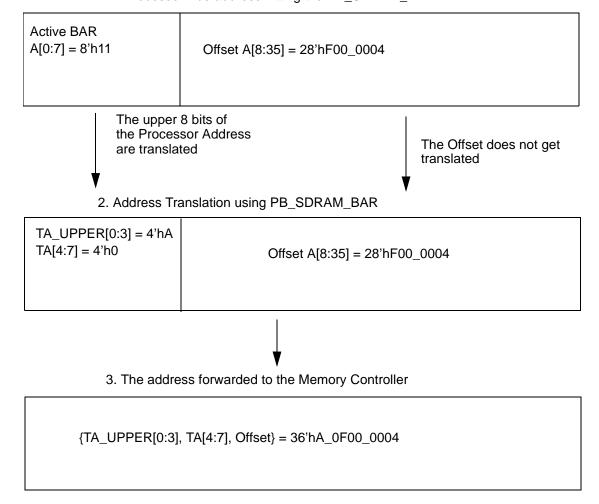

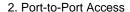

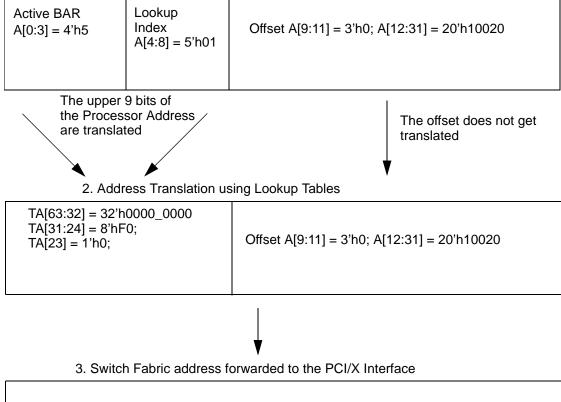

#### **Example 2**: 32-bit Processor, access to PCI/X from the processor bus.

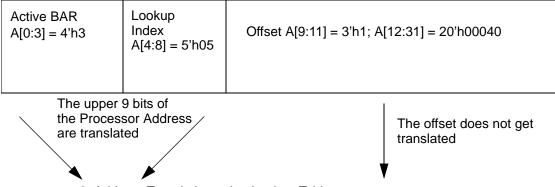

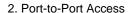

In this example the PB\_OCN\_BAR2 window size has been programmed to 256 Mbytes, all processor bus addresses that fall within 36'h5000\_0000 – 36'h5FFF\_FFFF will be accepted and forwarded through the Switch Fabric as indicated by the values programmed in the PB\_OCN\_BAR2 register below. Once the transaction has been accepted through the PB\_OCN\_BAR2 register it is up to the associated lookup tables to determine both the destination port and proper address translation. Since the window size programmed in the PB\_OCN\_BAR2 register is 256 Mbytes, that means there are 32, 8-Mbyte pages associated with that address window. The PB\_BARx\_UPPER\_LUT\_ADDR{0..31} and PB\_BARx\_LOWER\_LUT\_ADDR{0..31} registers must be programmed to determine both the destination port and address translation associated with those 32 pages.

In this example only one 8-Mbyte page (page 1) of the 256-Mbyte window is configured to access the PCI/X Interface, by programming the PB\_BAR2\_UPPER\_LUT\_ADDR1 and PB\_BAR2\_LOWER\_LUT\_ADDR1 registers, page 1 addresses the PCI/X port as indicated by the DST\_PORT field (see Table 13). Address translation has been enabled and all Switch Fabric address accesses that address page 1 will be forwarded to the PCI/X Interface as 64'h0000\_0000\_F000\_0000 – 64'h0000\_0000\_F07F\_FFFF. Address hits to page 1 are determined as follows using the information provided in Table 10. Processor bits A[0:3] define the active BAR which in this example are defined as 4'h5. Processor bits A[4:8] define the lookup index (that is, what page the access is mapped to), in order to hit page 1, these bits need to be 5'h01. The remaining Processor bits A[9:31] define the address offset which in this case address the entire 8-Mbyte page of memory. Figure 7 shows the address translation process resulting from a Processor bus address (32'h5081\_0020) hitting the PB\_OCN\_BAR2.

#### Register settings:

- **PB\_OCN\_BAR2:** BA = 4'h5; SIZE = 4'h0 (256M Window); EN = 1

- **PB\_BAR2\_UPPER\_LUT\_ADDR1:** TA[63:32] = 32'h0000\_0000

- **PB\_BAR2\_LOWER\_LUT\_ADDR1:** TA[31:24] = 8'hF0, TA[23] = 1'h0; END\_MODE = 2'b00; WR\_PRTC = 0; ATE = 1; DST\_PORT = 4'b0001 (PCI/X Interface)

Figure 7: PCI/X Path Address Translation Process, 32-bit Processor

1. Processor bus address hitting the PB\_OCN\_BAR

$\{TA[63:23], Offset\} = 64'h0000\_0000\_F001\_0020$

#### 2.3.3 Additional Switch Fabric to PCI/X Transaction Mapping Capabilities

The previous sections describe how to map Processor bus accesses to the PCI/X bus through the Switch Fabric. Based on that configuration, the Tsi110 will only initiate memory cycles on the PCI/X bus. As a result, all read and write commands from the Processor bus or any other Tsi110 port that get mapped to the PCI/X bus will result in the Tsi110 initiating a memory type transaction on the PCI/X bus (that is, Memory Read, Memory Read Line, Memory Read Multiple, Memory Read Block, Memory Read DWORD, Memory Write, Memory Write Block and Dual Address Cycle).

The Switch Fabric to PCI/X path offers additional functionality to convert Switch Fabric addresses received because of a Processor bus access (for example, into a Configuration or an I/O access on the PCI/X bus by implementing a 64-bit Configuration BAR and a 64-bit I/O BAR). It also supports an additional layer of address translation by implementing three additional translation BARs: two 64-bit Prefetchable Memory BARs, and one 32-bit Memory BAR.

The configuration BAR registers (PFAB\_BAR0 and PFAB\_BAR0\_UPPER), when enabled define a 16-Mbyte fixed address window that is used to generate configuration transactions on the PCI/X bus. The I/O Switch Fabric BAR registers (PFAB\_IO and PFAB\_IO\_UPPER), when enabled define a 64-Kbyte fixed address window that is used to generate I/O transactions on the PCI/X bus. The MEM32 Switch Fabric BAR register (PFAB\_MEM32), when enabled defines an address window that is used for address translation from the Switch Fabric to 32-bit Memory transactions on the PCI/X bus. The PFAB MEM32 BAR supports a 32-bit address decode (that is, the upper Switch Fabric address bits [63:32] must be zeros), and can be a minimum of 512M to 1G in size. The PFAB\_MEM32 address window supports address translation through the use of a remap register (PFAB MEM32 REMAP) and a mask register (PFAB MEM32 MASK). The PFM Switch Fabric BAR registers (PFAB PFM3 and PFAB\_PFM4), when enabled define an address window used for address translation from the Switch Fabric to 64-bit Memory transactions on the PCI/X bus. The PFAB\_PFM3 and PFAB\_PFM4 BARs support a 64-bit address decode, and can be a minimum of 1G to 2G in size. The PFAB\_PFM3 and PFAB\_PFM4 address windows support address translation through the use of remap registers (PFAB PFM[3:4] REMAP UPPER and PFAB PFM[3:4] REMAP LOWER) and mask registers  $(PFAB\_PFM[3:4]\_MASK).$

When any of the above mentioned Switch Fabric to PCI/X BARs are enabled and the Switch Fabric address falls within the defined address window, the PCI/X address or command are altered as described within the individual BAR. These registers are located in the PCI/X bus register block at offsets 0x204 through 0x23C.

#### 2.3.4 How to Initialize the Switch Fabric to PCI/X Transaction Mapping

The Switch Fabric to PCI/X BARs can be initialized using PCI/X memory write cycles from the PCI/X bus through the P2O\_BAR0 and P2O\_BAR0\_UPPER registers, or from the Processor bus through the PB\_REG\_BAR. Tables 14 to 24 describe the internal register settings associated with setting up the optional Switch Fabric to PCI/X bus transaction mapping.

Table 14: PFAB\_BAR0 Configuration Address Register Initialization

| Register  | Field           | Description                                                                                                                                                                                                                                        |

|-----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFAB_BAR0 | PFAB_BAR[31:24] | PCI/X Configuration Generation Base Address bits [31:24]: These bits are compared with the Switch Fabric address bits [31:24].                                                                                                                     |

| PFAB_BAR0 | BAR0_EN         | PFAB BAR0 Window Enable: Writing a 1 to this location enables the configuration address window. When enabled all Switch Fabric transactions with addresses that fall within the window are get initiated as configuration cycles on the PCI/X bus. |

Table 15: PFAB\_BAR0\_UPPER Configuration Address Register Initialization

| Register        | Field            | Description                                                                                                                    |

|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|

| PFAB_BAR0_UPPER | PFAB_BAR0[63:32] | PCI/X Configuration Generation Base Address bits [63:32]: These bits are compared with the Switch Fabric address bits [63:32]. |

Table 16: PFAB\_IO Base Address Register Initialization

| Register | Field      | Description                                                                                                                                                                                                             |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFAB_IO  | BAR[31:16] | PCI/X IO Generation Base Address bits [31:16]: These bits are compared with the Switch Fabric address bits [31:16].                                                                                                     |

| PFAB_IO  | EN         | PFAB_IO Window Enable: Writing a 1 to this location enables the IO address window. When enabled all Switch Fabric transactions with addresses that fall within the window get initiated as I/O cycles on the PCI/X bus. |

#### Table 17: PFAB\_IO\_UPPER Base Address Register Initialization

| Register      | Field      | Description                                                                                                         |

|---------------|------------|---------------------------------------------------------------------------------------------------------------------|

| PFAB_IO_UPPER | BAR[63:32] | PCI/X IO Generation Base Address bits [63:32]: These bits are compared with the Switch Fabric address bits [63:32]. |

#### Table 18: PFAB\_MEM32 Base Address Register Initialization

| Register   | Field     | Description                                                                                                                                                                                                                                                                                        |

|------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFAB_MEM32 | BA[31:29] | 32-bit Memory Base Address bits [31:29]: These bits are compared with the Switch Fabric address bits [31:29].                                                                                                                                                                                      |

| PFAB_MEM32 | SIZE      | MEM_32 Window Size: 0 = 512 Mbytes 1= 1 Gbyte                                                                                                                                                                                                                                                      |

| PFAB_MEM32 | EN        | MEM_32 Window Enable: Writing a 1 to this location enables the MEM_32 address window. When enabled all Switch Fabric transactions with addresses that fall within the window get translated as defined by the appropriate remap and mask registers defined in Tables 19 and 20 onto the PCI/X bus. |

Table 19: PFAB\_MEM32\_REMAP Register Initialization

| Register             | Field        | Description                                                                                                                                  |

|----------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| PFAB_MEM32_<br>REMAP | Remap[31:12] | MEM_32 Remap Value: These bits are substituted with the Switch Fabric address bits [31:12] provided the corresponding Mask value is enabled. |

#### Table 20: PFAB\_MEM32\_MASK Register Initialization

| Register        | Field       | Description                                                                                                                                             |

|-----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFAB_MEM32_MASK | Mask[31:12] | MEM_32 Mask Value: These bits when enabled, enable the substitution of the Switch Fabric address bits [31:12] with the MEM_32 Remap Value Remap[31:12]. |

Table 21: PFAB\_PFM[3:4] Base Address Register Initialization

| Register      | Field <sup>a</sup> | Description                                                                                                                                                                                                                                                                                            |

|---------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFAB_PFM[3:4] | BA[31:30]          | PFM[3:4] Base Address bits [31:30]: These bits are compared with the Switch Fabric address bits [31:30].                                                                                                                                                                                               |

| PFAB_PFM[3:4] | BA[59:48]          | PFM[3:4] Base Address bits [59:48]: These bits are compared with the Switch Fabric address bits [59:48].                                                                                                                                                                                               |

| PFAB_PFM[3:4] | SIZE               | PFM[3:4] Window Size: 0 = 1 Gbytes 1= 2 Gbyte                                                                                                                                                                                                                                                          |

| PFAB_PFM[3:4] | EN                 | PFM[3:4] Window Enable: Writing a 1 to this location enables the PFM[3:4] address window. When enabled all Switch Fabric transactions with addresses that fall within the window get translated as defined by the appropriate remap and mask registers defined in Tables 22 and 24 onto the PCI/X bus. |

| PFAB_PFM[3:4] | BA[47:32]          | PFM[3:4] Base Address bits [47:32]: These bits are compared with the Switch Fabric address bits [47:32].                                                                                                                                                                                               |

a. The BA[63:60] value is hardwired to 4'h0.

Table 22: PFAB\_PFM[3:4]\_REMAP\_UPPER Register Initialization

| Register                      | Field        | Description                                                                                                                                          |

|-------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFAB_PFM[3:4]_<br>REMAP_UPPER | Remap[63:44] | PFM[3:4] Upper Remap Value: These bits are substituted with the Switch Fabric address bits [63:44] provided the corresponding Mask value is enabled. |

Table 23: PFAB\_PFM[3:4]\_REMAP\_LOWER Register Initialization

| Register                      | Field        | Description                                                                                                                                          |

|-------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFAB_PFM[3:4]_<br>REMAP_LOWER | Remap[31:12] | PFM[3:4] Lower Remap Value: These bits are substituted with the Switch Fabric address bits [31:12] provided the corresponding Mask value is enabled. |

| PFAB_PFM[3:4]_<br>REMAP_LOWER | Remap[43:32] | PFM[3:4] Lower Remap Value: These bits are substituted with the Switch Fabric address bits [43:32] provided the corresponding Mask value is enabled. |

Table 24: PFAB\_PFM[3:4]\_MASK Register Initialization

| Register           | Field <sup>a</sup> | Description                                                                                                                                                 |

|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFAB_PFM[3:4]_MASK | Mask[31:12]        | PFM[3:4] Mask Value: These bits when enabled, enable the substitution of the Switch Fabric address bits [31:12] with the PFM[3:4] Remap Value Remap[31:12]. |

| PFAB_PFM[3:4]_MASK | Mask[43:32]        | PFM[3:4] Mask Value: These bits when enabled, enable the substitution of the Switch Fabric address bits [43:32] with the PFM[3:4] Remap Value Remap[43:32]. |

Remap[63:44] are always substituted for Switch Fabric address bits[63:44] as the Mask bits only provide selectable replacement for bits [43:12] of the original Switch Fabric address.

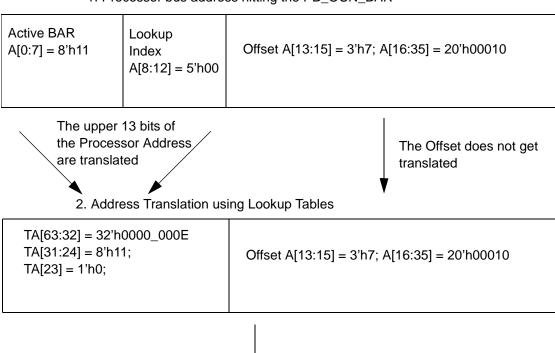

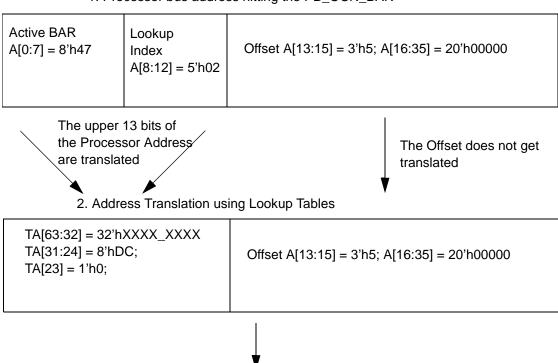

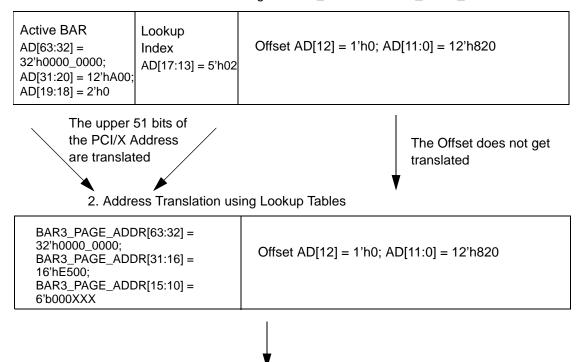

# 2.4. Switch Fabric to PCI/X Configuration Cycle Example

**Example 1:** The following example describes the most common use of the Switch Fabric to PCI/X transaction mapping capabilities. The example will describe the use of the Configuration BAR to transform the Switch Fabric address received into a Type 0 configuration cycle on the PCI/X bus (the example assumes the PCI/X Interface is connected to PCI/X Bus #1).

In this example the PFAB\_BAR0 and PFAB\_BAR0\_UPPER registers are programmed such that all Switch Fabric addresses destined for the PCI/X Interface that fall within 64'h0000\_0000\_F000\_0000 – 64'h0000\_0000\_F0FF\_FFFF will be accepted and forwarded to the PCI/X bus as a configuration cycle. Figure 8 uses the Switch Fabric address as a result of a Processor bus access destined for the PCI/X Interface, as defined in the previous example (see Figure 7). The Switch Fabric address (64'h0000\_0000\_F001\_0020) falls within the window defined by the PFAB\_BAR0 and PFAB\_BAR0\_UPPER registers.

#### Register settings:

- **PFAB\_BAR0:** PFAB\_BAR0[31:24] = 8'hF0; BAR0\_EN = 1

- **PFAB BAR0 UPPER:** PFAB BAR0[63:32]= 32'h0000 0000

Figure 8: Switch Fabric to PCI/X Configuration Cycle Generation

1. Switch Fabric address hitting the PFAB\_BAR0 and PFAB\_BAR0\_UPPER

| BAR Decode<br>Addr[63:24] =<br>40'h0000_0000_F0 | Outgoing<br>Bus #<br>Addr[23:16] =<br>8'h01 | Outgoing<br>Device #<br>Addr[15:11] =<br>5'b00000 | Outgoing<br>Func. #<br>Addr[10:8] =<br>3'b000 | Outgoing<br>Register #<br>Addr[7:2] =<br>6'b001000 | Addr[1:0] =<br>Undefined |  |

|-------------------------------------------------|---------------------------------------------|---------------------------------------------------|-----------------------------------------------|----------------------------------------------------|--------------------------|--|

|-------------------------------------------------|---------------------------------------------|---------------------------------------------------|-----------------------------------------------|----------------------------------------------------|--------------------------|--|

The transformation from Switch Fabric address to Configuration Address is defined in the PCI/X Interface section of the *Tsi110 User Manual* as well as Table 25 below. The fields described above determine what type of configuration cycle (Type 0 or Type 1) as well as which address line is selected for the IDSEL.

3. Configuration Type 0 Transaction Address forwarded to the PCI/X Interface

Configuration Type 0 at Address = 32'h0001\_0020

**Note**: Bit AD[16] of the above configuration address is asserted due to the Outgoing Device # above being 5'b00000. The device number determines which PCI Address line will be asserted when the Tsi110 initiates the Type0 Configuration cycle. The device the Tsi110 is addressing the Type 0 configuration cycle to should have its IDSEL input connected to AD[16]. This is PCI spec. and is described in Table 26.

Table 25: Switch Fabric Address and its conversion to PCI/X Configuration Cycles

| Incoming Switch Fabric<br>Address Bits | Used For                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addr[63:24]                            | PFAB_BAR0 decode.                                                                                                                                                                                                                                                                                                                                               |

| Addr[23:16]                            | Outgoing PCI/X bus number.  The configuration type is based on the value in this field. For example, if the value matches our destination bus number (the BUS_NUM field in the PE_PCI/X_S, PCI/X offset 0x0F4) then the Tsi110 will generate a Type 0 configuration cycle on the PCI/X bus, at all other times the Tsi110 will generate a configuration Type 1. |

| Addr[15:11]                            | Outgoing device number.  For Type 0 configuration cycles this number determines which Address line is asserted for the IDSEL connection. This comes directly out of the PCI specification as well as Table 26 below.                                                                                                                                            |

| Addr[10:8]                             | Outgoing function number.                                                                                                                                                                                                                                                                                                                                       |

| Addr[7:2]                              | Outgoing register number.                                                                                                                                                                                                                                                                                                                                       |

| Addr[1:0]                              | These bits have no effect and are undefined.                                                                                                                                                                                                                                                                                                                    |

**Table 26: IDSEL Generation**

| Device Number | Address AD[31:16]    |

|---------------|----------------------|

| 0 0000b       | 0000 0000 0000 0001b |

| 0 0001b       | 0000 0000 0000 0010b |

| 0 0010b       | 0000 0000 0000 0100b |

| 0 0011b       | 0000 0000 0000 1000b |

| 0 0100b       | 0000 0000 0001 0000b |

| 0 0101b       | 0000 0000 0010 0000b |

| 0 0110b       | 0000 0000 0100 0000b |

| 0 0111b       | 0000 0000 1000 0000b |

| 0 1000b       | 0000 0001 0000 0000b |

| 0 1001b       | 0000 0010 0000 0000b |

| 0 1010b       | 0000 0100 0000 0000b |

| 0 1011b       | 0000 1000 0000 0000b |

| 0 1100b       | 0001 0000 0000 0000b |

| 0 1101b       | 0010 0000 0000 0000b |

| 0 1110b       | 0100 0000 0000 0000b |

| 0 1111b       | 1000 0000 0000 0000b |

| 1 XXXXb       | 0000 0000 0000 0000b |

# 2.5 Processor to HLP

In order to communicate through the Tsi110 from the Processor bus through the Switch Fabric to the Host Local Port (HLP) Interface the following registers must be initialized: a PB to Switch Fabric Base Address Register (PB\_OCN\_BARx), as well as the associated PB Switch Fabric BAR Lower (PB\_BARx\_LOWER\_LUT\_ADDRy) and Upper (PB\_BARx\_UPPER\_LUT\_ADDRy) Lookup Table Address Registers. A PB to Switch Fabric BAR defines an address range (in Processor bus address space) where the Tsi110 responds to a Processor's request. If the Processor's request falls within one of the Tsi110's PB to Switch Fabric base address ranges, the transaction is forwarded through to the Switch Fabric. The Tsi110 supports two unique PB to Switch Fabric BARs: PB\_OCN\_BAR1 (offset 0x414) and PB\_OCN\_BAR2 (offset 0x418).