# RENESAS

# Tsi107™ Revision 1.3/1.4 Device Differences

80C2000\_AN002\_02

November 3, 2009

6024 Silver Creek Valley Road San Jose, California 95138 Telephone: (408) 284-8200 • FAX: (408) 284-3572 Printed in U.S.A. ©2009 Integrated Device Technology, Inc.

© 2019 Renesas Electronics Corporation

#### GENERAL DISCLAIMER

GENERAL DISCLAIMER Integrated Device Technology, Inc. ("IDT") reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance. IDT does not assume responsibility for use of any circuitry described herein other than the circuitry embodied in an IDT product. Disclosure of the information herein does not convey a license or any other right, by implication or otherwise, in any patent, trademark, or other intellectual property right of IDT. IDT products may contain errata which can affect product performance to a minor or immaterial degree. Current characterized errata will be made available upon request. Items identified herein as "reserved" or "undefined" are reserved for future definition. IDT does not assume responsibility for conflicts or incompatibilities arising from the future definition of such items. IDT products have not been designed, tested, or manufactured for use in, and thus are not warranted for, applications where the failure, malfunction, or any inaccuracy in the application carries a risk of death, serious bodily injury, or damage to tangible property. Code examples provided herein by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of such code examples shall be at the user's sole risk.

Copyright  $^{\odot}$  2009 Integrated Device Technology, Inc. All Rights Reserved.

The IDT logo is registered to Integrated Device Technology, Inc. IDT is a trademark of Integrated Device Technology, Inc.

# **About this Document**

This document describes electrical and functional differences between Revision 1.3 and Revision 1.4 of the Tsi107 PowerPC Host Bridge, which provides system interconnect between PowerPC processors, PCI peripherals and local memory.

This document covers the following topics:

| Торіс                               | Page |

|-------------------------------------|------|

| Section 1, "Overview"               | 3    |

| Section 2, "Electrical Differences" | 4    |

| Section 3, "Functional Differences" | 5    |

| Section 4, "Compatibility Factors"  | 7    |

| Section 5, "Conclusion"             | 9    |

# 1 Overview

Revision 1.3 of the Tsi107 is limited to a processor/memory bus frequency of 100 MHz, and has errata that some customers have deemed unsuitable for their design requirements. Revision 1.4 of the Tsi107 implements fixes for the errata to make it more suitable for new designs. Specification changes for Rev 1.4 address the frequency limitation. Because many existing designs are unaffected by the 100-MHz limit and the errata on Rev 1.3, and because Rev 1.4 introduces timing and functional changes to the Tsi107, many customers choose to continue specifying Rev 1.3 in their designs.

This document describes the differences between Rev 1.3 and Rev 1.4. It helps to assess which revision is appropriate for a specific design and what changes may be necessary when migrating a system design from Rev 1.3 to Rev 1.4.

Table 1 describes how to distinguish between Rev 1.3 and Rev 1.4 devices. The orderable part number and the part marking contain a revision code that refers to the die mask revision number. Reading the Revision ID register at configuration address offset 0x08 can determine the revision level of an installed device.

| Tsi107 Die Mask Revision Level | Revision Code | Revision ID Register (offset 0x08) |

|--------------------------------|---------------|------------------------------------|

| 1.3                            | С             | 0x13                               |

| 1.4                            | D             | 0x14                               |

Table 1. Identifying Revision Level

#### **Electrical Differences** 2

The only changes in the electrical specifications are to allow the Tsi107 to achieve 133-MHz processor/memory bus operation timing. Note that these are specification changes that manufacturing supports, and are not design changes. Therefore, Rev 1.4 devices marked for 100-MHz operation have the same electrical characteristics as Rev 1.3 devices. Table 2 summarizes the changes for the 133-MHz-rated Rev 1.4 Tsi107.

| Electrical Characteristic                                                                              | <b>Rev 1.3/Rev 1.4</b><br>(100-MHz Device)                                          | Rev 1.4<br>(133-MHz Device Only)<br>133 MHz                                         |  |  |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|

| Maximum 60x and memory bus frequency                                                                   | 100 MHz                                                                             |                                                                                     |  |  |

| Supply voltages—core, PLL, and<br>DLL<br>(V <sub>DD</sub> , AV <sub>DD</sub> , and LAV <sub>DD</sub> ) | 2.5 V <sub>DC</sub>                                                                 | 2.7 V <sub>DC</sub>                                                                 |  |  |

| 60x and memory interface signals<br>—output valid time (Specs 12 b<br>and 12e)                         | 5.5 nsec                                                                            | 4.5 nsec                                                                            |  |  |

| Maximum die junction<br>temperature (T <sub>j</sub> )                                                  | 105 °C                                                                              | 85 °C                                                                               |  |  |

| Power consumption                                                                                      | See Tsi107 Hardware Specification                                                   | Slightly higher due to elevated supply voltage                                      |  |  |

| 1 <sup>2</sup> C frequencies                                                                           | See Tsi107 Hardware Specification                                                   | Higher due to higher memory bus frequency<br>of 133 MHz (the divisors are the same) |  |  |

| PLL[0:4] configurations                                                                                | Frequency range limited to 100 MHz for<br>PLL[0:4] configurations 0x5, 0x8, and 0xC | Frequency range higher for PLL[0:4] configurations 0x5, 0x8, and 0xC                |  |  |

| Table 2. Electrical Differences- | -100 MHz/133 MHz      |

|----------------------------------|-----------------------|

| Table 2. Electrical Differences  | -100 11111/ 100 11111 |

© 2019 Renesas Electronics Corporation

## **3** Functional Differences

Rev 1.3 of the Tsi107 has known errata that affect functionality. Rev 1.4 fixes some of those errata, but implementing the fixes introduced functionality changes. The following sections describe the specific Rev 1.3 errata that Rev 1.4 addresses.

### 3.1 Fast Back-to-Back Capability

For all revisions of the Tsi107 before Rev 1.4, bit 7 of the PCI status register is hardwired to 1, indicating that the Tsi107 can support fast back-to-back transactions. Due to a chip errata, if an external PCI master issues a type 2 fast back-to-back transaction (read or write) to a Tsi107, the transaction causes data corruption. (Type 2 fast back-to-back transactions access multiple targets sequentially.)

The suggested work-around for this errata is to use software to disable the ability to run fast back-to-back transactions on any potential master devices by clearing bit 9 of the PCI command register in the master device. The solution implemented in Rev 1.4 of the Tsi107 is to hardwire bit 7 of the PCI status register to 0, indicating that it is not capable of accepting fast back-to back transactions as a target.

## 3.2 MPC7450 Compatibility

Revisions of the Tsi107 before Rev 1.4 have compatibility issues with the MPC7450 and its derivatives. The compatibility issues are documented in the *Tsi107 PowerPC Host Bridge Device Errata*. The MPC7450 implementation of the 60x bus protocol is slightly more restrictive, in that data must never be transferred before the last cycle of the ARTRY window (the cycle after AACK is asserted). Similarly, TEA must not be asserted to terminate a data tenure before the last cycle of the ARTRY window.

The actual protocol restriction for the MPC7450 is that any transaction receiving a simultaneous  $\overline{AACK}$  and  $\overline{TA}/\overline{TEA}$  must not be retried. Improperly forwarded data causes data corruption in the code stream. In addition, any transaction that requires a data tenure that follows a transaction receiving a simultaneous  $\overline{AACK}$  and  $\overline{TA}/\overline{TEA}$  must not be retried. When the MPC7450 receives a simultaneous  $\overline{AACK}$  and  $\overline{TA}/\overline{TEA}$ , it sets an internal sticky flag that causes the next transaction to ignore  $\overline{ARTRY}$ .

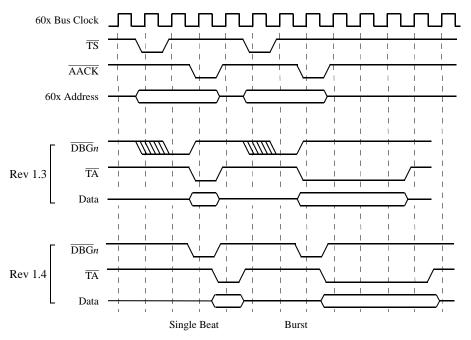

For revisions of the Tsi107 before Rev 1.4, data is returned to the processor starting with the cycle when  $\overline{AACK}$  is asserted, which is one cycle before that permitted by the MPC7450. Before Rev 1.4, the Tsi107 may drive  $\overline{DBGn}$  (and  $\overline{DBGLB}$ ) as early as the cycle in which  $\overline{TS}$  is asserted.

The problem is aggravated in dual-processor systems and systems where PCI accesses to memory cause significant snoop or retry activity on the 60x bus where 60x bus traffic is high.

Beginning with Rev 1.4, the Tsi107 no longer issues the first  $\overline{TA}$  (or  $\overline{TEA}$ ) for a data tenure simultaneously with the associated  $\overline{AACK}$  for any transactions. To guarantee that  $\overline{TA}$  is not asserted on or before  $\overline{AACK}$ , the timings for  $\overline{DBGn}$  and  $\overline{DBGLB}$  were also changed.

### 3.2.1 Local Bus Slave Parameters

To implement the fix for MPC7450 compatibility, two local bus slave parameters, PICR1[CF\_LBA\_EN] and PICR2[CF\_LBCLAIM\_WS], were eliminated beginning with Rev 1.4. The CF\_LBA\_EN parameter enables or disables the local bus slave functionality on revisions before Rev 1.4, whereas, starting with Rev 1.4, local bus slave functionality is always enabled.

The CF\_LBCLAIM\_WS parameter controls when the Tsi107 samples the  $\overline{LBCLAIM}$  input signal from the local bus slave on revisions before 1.4. Starting with Rev 1.4 of the Tsi107, the PICR2[CF\_APHASE\_WS] parameter controls the timing of both the address phase and the sampling of LBCLAIM.

### 3.3 Latency for PCI Accesses to Local Memory

Due to a chip errata on revisions of the Tsi107 before Rev 1.4, the processor can prevent a PCI agent or DMA transfer from accessing the SDRAM. This affects the minimum PCI and/or DMA access latency if the processor is performing a series of pipelined reads or writes. PCI and DMA accesses to local memory may stall if snooping is disabled (PICR2[NO\_SNOOP\_EN] = 1) because pipelined processor transactions have a priority 1.5 (see the *Tsi107 User Manual*). The suggested work-around is to enable snooping (PICR2[NO\_SNOOP\_EN] = 1), even though the hardware-managed coherency is not needed. As an additional step, in single-processor systems, the GBL signal to the processor may be pulled down to eliminate false ARTRYs due to pipeline collisions.

The solution implemented in Rev 1.4 of the Tsi107 is to add fairness to the internal arbitration logic that does not allow the pipelined 60x transaction to keep winning over non-snooped PCI/DMA initiated read transactions.

### 3.4 60x Bus Grants After sync or eieio Broadcasts

Due to a chip errata on Tsi107 devices before Rev 1.4, if the processor issues a **sync** or **eieio** instruction to the Tsi107, the Tsi107 does not grant the 60x bus to any processor until all the internal write buffers are empty. These buffers are the processor-to-PCI-write data buffers (PRPWB0 and PRPWB1), the PCI-to-local-memory-write buffers (PCMWB0, and PCMWB1), and the copyback buffer.

In this case, a PCI device can perform continuous accesses into SDRAM so that the internal buffers (PCMWB0, PCMWB1, and copyback) are never empty. In such a case, the processor is prevented from progressing beyond the **sync/eieio** address broadcast.

The suggested work-around is to disable broadcasts of address-only transactions (HID0[ABE]=0) on processors that implement the ABE bit. For systems using processors that do not implement the ABE bit (such as the MPC7410), the work-around is much more difficult, involving external logic that decodes address-only broadcasts and inhibits the PCI arbitration signals to allow for transactions in the internal PCMWBs buffers to complete to memory before resuming normal operation.

The solution implemented in Rev 1.4 of the Tsi107 is to remove the dependency on flushing the PCI-to-local-memory-write buffers (PCMWBs) after a **sync/eieio** broadcast before the Tsi107 can grant the bus to the processor. Thus, only the processor-to-PCI-write buffers (PRPWBs) are flushed before the bus is granted to the processor.

# 4 Compatibility Factors

This section describes compatibility issues that may arise when migrating a Tsi107-based design from Rev 1.3 to Rev 1.4.

# 4.1 **DBG***n* and **DBGLB** Timing

As described in Section 3.2, "MPC7450 Compatibility," to guarantee that  $\overline{\text{TA}}$  is not asserted on or before AACK, the timings for  $\overline{\text{DBGn}}$  and  $\overline{\text{DBGLB}}$  were changed in Rev 1.4 to fix the MPC7450-compatibility problem. Before Rev 1.4, the Tsi107 may drive  $\overline{\text{DBGn}}$  (and  $\overline{\text{DBGLB}}$ ) as early as the cycle in which  $\overline{\text{TS}}$  is asserted. Figure 1 shows the signal timing for  $\overline{\text{DBGn}}$  and  $\overline{\text{DBGLB}}$  on Rev 1.3 and Rev 1.4 devices.

Figure 1. Rev 1.3 and Rev 1.4 DBGn Signal Timing

#### NOTE

For Rev 1.4 of the Tsi107,  $\overline{\text{DBGn}}$  is asserted coincident with  $\overline{\text{AACK}}$ . If a Rev 1.3 system design incorporates external logic that depends on the timing of  $\overline{\text{DBGn}}$  or  $\overline{\text{DBGLB}}$ , the external logic must be modified to accommodate the altered timing of Rev 1.4.

### 4.2 Local Bus Slave Compatibility

As described in Section 3.2.1, "Local Bus Slave Parameters," an impact occurs on local bus slave functionality when moving from Rev 1.3 to Rev 1.4. Two local bus slave parameters, PICR1[CF\_LBA\_EN] and PICR2[CF\_LBCLAIM\_WS] were eliminated

Even though the CF\_LBA\_EN parameter was eliminated in Rev 1.4, initialization software that sets this bit to enable the local bus slave functionality do not cause any errors. Software that clears CF\_LBA\_EN to disable the

local bus slave functionality does not cause any errors; however, the functionality is always enabled in Rev 1.4 and the clearing of this bit is ignored. A Rev 1.3 design has no reason to rely on disabling the local bus slave functionality, and thus software should not be impacted.

The elimination of the CF\_LBCLAIM\_WS parameter in Rev 1.4 may affect initialization software. Starting with Rev 1.4 of the Tsi107, the PICR2[CF\_APHASE\_WS] parameter controls the timing of both the address phase and the sampling of  $\overline{LBCLAIM}$ . Software that attempts to program CF\_LBCLAIM\_WS does not cause any errors on Rev 1.4, but the  $\overline{LBCLAIM}$  sampling logic ignores the parameter. Consider this situation to assert  $\overline{LBCLAIM}$  in the appropriate cycle.

Many customers use equal settings for CF\_APHASE\_WS and CF\_LBCLAIM\_WS, and the change does not affect them. However, if the initialization code is setting CF\_APHASE\_WS greater than CF\_LBCLAIM\_WS and a local bus slave asserts LBCLAIM before CF\_APHASE\_WS expires, a Rev 1.4 Tsi107 does not recognize the assertion of LBCLAIM and asserts the appropriate number of TAs for the transaction. Typically in this situation, the system eventually hangs. The work-around is to adjust CF\_APHASE\_WS for a shorter duration to accommodate the assertion of LBCLAIM or to modify the local bus slave to delay the assertion of LBCLAIM until CF\_APHASE\_WS expires.

### 4.3 Migrating from 100 MHz to 133 MHz

If the purpose of migrating to Rev 1.4 is to increase the processor/memory bus frequency from 100 MHz to 133 MHz, the system design must account for the electrical differences that Table 2 describes. Note that not all Rev 1.4 devices are rated for 133-MHz operation. In 133-MHz systems, use only those devices that are specifically rated for 133-MHz operation.

Most, but not necessarily all, system designs should be re-laid out to operate properly at 133 MHz. Because the 133-MHz Rev 1.4 Tsi107 requires 2.7  $V_{DC}$  supply voltages for the core, PLL, and DLL, the power supply of an existing Rev 1.3 design should be augmented to support the additional increased supply voltage. Follow the recommendations in the Tsi107 *Hardware Specification* and in the *Tsi107 Design Guide* concerning memory timing. In general, for best signal integrity, keep trace lengths for SDRAM signals as short as possible and keep capacitive loads to a minimum (or use registered DIMMs that buffer the memory control signals).

# 5 Conclusion

Table 3 provides a summary of which revision of the Tsi107 is appropriate for specific design requirements. For designs that do not depend on the listed requirements, either revision provides the functionality described in the *Tsi107 User Manual*.

| Design Requirement                                                                         | Tsi107 Rev 1.3      | Tsi107 Rev 1.4                                                                                                                                                               |

|--------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 133-MHz processor/memory bus                                                               | Not suitable        | Suitable (with<br>133 MHz-rated part)                                                                                                                                        |

| External PCI masters that may run Type 2 fast-back-to-back transactions                    | May not be suitable | Suitable, but fast<br>back-to-back transactions to<br>the Tsi107 are still not<br>supported. See Section 3.1,<br>"Fast Back-to-Back<br>Capability," for more<br>information. |

| MPC7450 family processor                                                                   | Not-suitable        | Suitable                                                                                                                                                                     |

| Local bus slave device                                                                     | Suitable            | Existing logic/initialization<br>software may need<br>modification. See<br>Section 4.2, "Local Bus<br>Slave Compatibility," for<br>more information.                         |

| External logic that relies on $\overline{\text{DBG}n}$ or $\overline{\text{DBGLB}}$ timing | Suitable            | Existing logic may need<br>modification. See<br>Section 4.1, "DBGn and<br>DBGLB Timing," for more<br>information.                                                            |

| Snooping of PCI-to-local memory transactions disabled<br>(PICR2[NO_SNOOP_EN] = 1)          | May not be suitable | Suitable                                                                                                                                                                     |

| MPC7400/MPC7410 processor                                                                  | May not be suitable | Suitable                                                                                                                                                                     |

| Table 3. | Which | Revision | То | Use? |

|----------|-------|----------|----|------|

|----------|-------|----------|----|------|

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.