**Application Note**

# Switch reluctance motor control with µPD78K0/KX2

Document No. U18498EE1V0AN00 Date published December 2006 © NEC Electronics 2006 Printed in Germany The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

## **Legal Notes**

- The information contained in this document is being issued in advance of the production cycle for the product. The parameters for the product may change before final production or NEC Electronics Corporation, at its own discretion, may withdraw the product prior to its production.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special", and "Specific". The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics products before using it in a particular application.

"Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

"Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

"Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc. The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

"NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

"NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

## **Regional Information**

Some information contained in this document may vary from country tocountry. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and otherlegal issues may also vary from country to country.

#### **NEC Electronics Corporation**

1753, Shimonumabe, Nakahara-ku, Kawasaki, Kanagawa 211-8668, Japan Tel: 044 4355111 http://www.necel.com/

#### [America]

U.S.A.

2880 Scott Blvd.

Tel: 408 5886000

**NEC Electronics America, Inc.**

Santa Clara, CA 95050-2554,

http://www.am.necel.com/

#### [Europe]

#### NEC Electronics (Europe) GmbH

Arcadiastrasse 10 40472 Düsseldorf, Germany Tel: 0211 65030 http://www.eu.necel.com/

#### **United Kingdom Branch**

Cygnus House, Sunrise Parkway Linford Wood, Milton Keynes MK14 6NP, U.K. Tel: 01908 691133

#### Succursale Française

9, rue Paul Dautier, B.P. 52 78142 Velizy-Villacoublay Cédex France Tel: 01 30675800

#### Sucursal en España

Juan Esplandiu, 15 28007 Madrid, Spain Tel: 091 5042787

#### **Tyskland Filial**

Täby Centrum Entrance S (7th floor) 18322 Täby, Sweden Tel: 08 6387200

#### Filiale Italiana

Via Fabio Filzi, 25/A 20124 Milano, Italy Tel: 02 667541

## Branch The Netherlands

Steijgerweg 6 5616 HS Eindhoven, The Netherlands Tel: 040 2654010

#### [Asia & Oceania]

#### NEC Electronics (China) Co., Ltd

7th Floor, Quantum Plaza, No. 27 ZhiChunLu Haidian District, Beijing 100083, P.R.China Tel: 010 82351155 http://www.cn.necel.com/

#### **NEC Electronics Shanghai Ltd.**

Room 2511-2512, Bank of China Tower, 200 Yincheng Road Central, Pudong New Area, Shanghai 200120, P.R. China Tel: 021 58885400 http://www.cn.necel.com/

#### **NEC Electronics Hong Kong Ltd.**

12/F., Cityplaza 4, 12 Taikoo Wan Road, Hong Kong Tel: 2886 9318 http://www.hk.necel.com/

#### NEC Electronics Taiwan Ltd.

7F, No. 363 Fu Shing North Road Taipei, Taiwan, R.O.C. Tel: 02 27192377

#### NEC Electronics Singapore Pte. Ltd.

238A Thomson Road, #12-08 Novena Square, Singapore 307684 Tel: 6253 8311 http://www.sg.necel.com/

#### NEC Electronics Korea Ltd.

11F., Samik Lavied'or Bldg., 720-2, Yeoksam-Dong, Kangnam-Ku, Seoul, 135-080, Korea Tel: 02-558-3737 http://www.kr.necel.com/

## Preface

This application note proposes how to implement a 4-Phase Switched Reluctance (SR) motor drive using the  $\mu$ PD78K0/KC2 along with an analogue Drive circuit.

Schematic, bill of material and board layout files are also provided.

## **Table of Contents**

| Chap     | oter 1     | Overview                                       | 9  |

|----------|------------|------------------------------------------------|----|

| 1.1      | Introdu    | iction                                         | 9  |

| 1.2      | Overvie    | ew of μPD78F0515D Series                       | 9  |

| Char     | oter 2     | Switched Reluctance Motor Basics               | 14 |

| •<br>2.1 |            | ed Reluctance Motor Basics                     |    |

| 2.2      |            | ed Reluctance Motor Control Requirements       |    |

| Char     |            | System Design Concept                          |    |

| 3.1      |            | Concept                                        |    |

| 3.2      | -          | Configuration                                  |    |

| 0.2      | 3.2.1      | Start-Up Sequence                              |    |

|          | 3.2.2      | Position and Speed Sensing                     |    |

|          | 3.2.3      | Commutation Algorithm                          |    |

|          | 3.2.4      | Current Limiter                                |    |

|          | 3.2.5      | Current Sensing                                | 25 |

| Chap     | oter 4     | Hardware Configuration                         | 27 |

| 4.1      | µPD78⋫     | K0/KC2 Configuration                           | 27 |

| 4.2      | Periphe    | erals I/O Assignments                          | 28 |

| 4.3      | Motor S    | Specification                                  | 29 |

| 4.4      | Encode     | er Specification                               | 29 |

| 4.5      | SR Mot     | tor Driving Circuit and User Interface Circuit | 30 |

| Chap     | oter 5     | Software Process Description                   | 32 |

| -<br>5.1 | Initializa | ation                                          | 33 |

| 5.2      | Interval   | l Timer                                        | 33 |

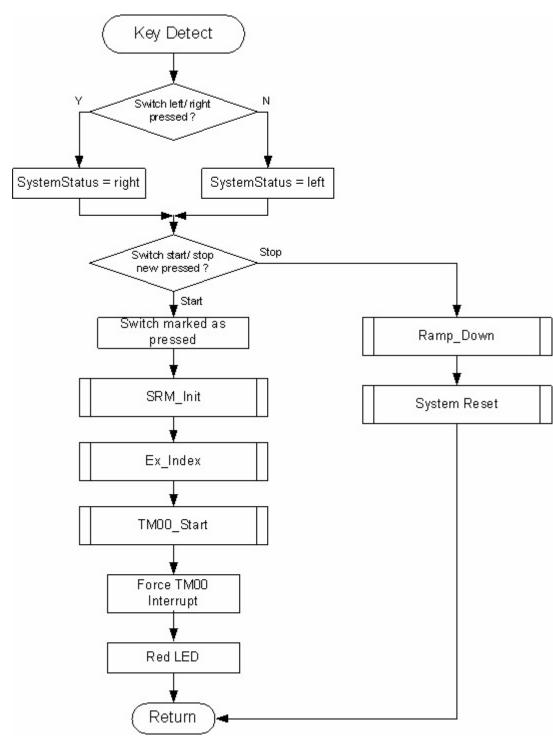

| 5.3      | Key Inp    | out, Potentiometer function                    | 33 |

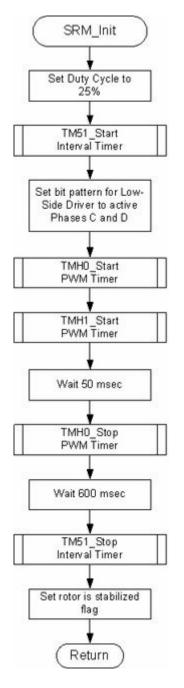

| 5.4      | Start Se   | equence                                        | 34 |

| 5.5      | Speed (    | Calculation                                    | 34 |

| 5.6      | PI-Regu    | ulator                                         | 34 |

| 5.7      | Commu      | utation Angle Calculation                      | 35 |

| 5.8      | Current    | t Limiter                                      | 35 |

| 5.9      | Commu      | utation                                        | 36 |

| 5.10     | LEDs .     |                                                | 36 |

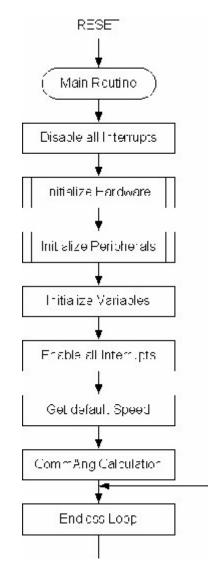

| Char     | oter 6     | Software Flow Charts                           | 37 |

| •<br>6.1 |            | pt and Main Flow Diagram                       |    |

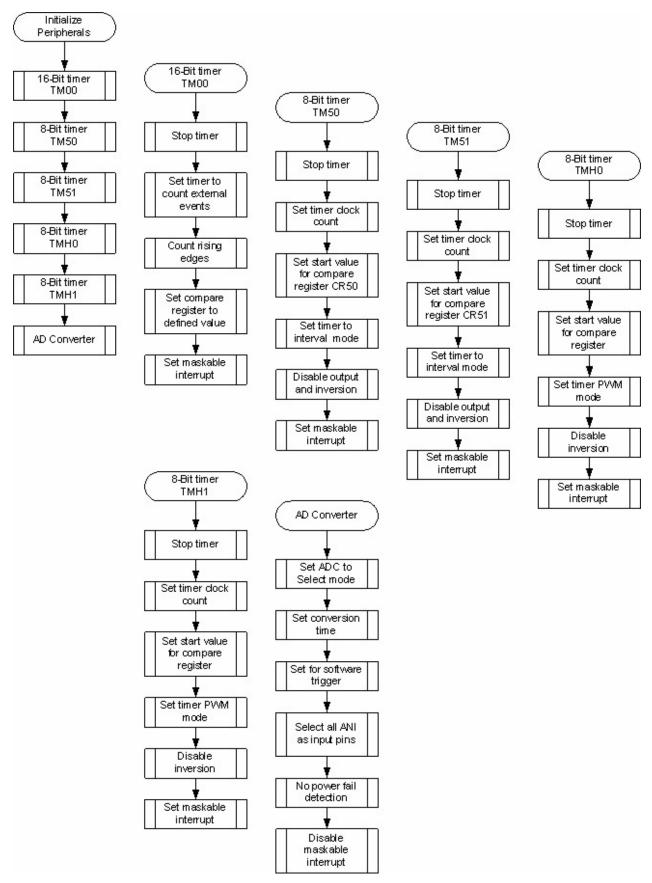

| 6.2      | -          | erals Initialization                           |    |

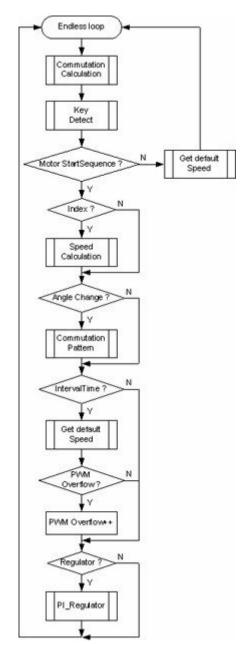

| 6.3      | •          | oop                                            |    |

| 6.4      |            | utation Calculation                            |    |

| 6.5      |            | tect                                           |    |

| 6.6      | •          |                                                |    |

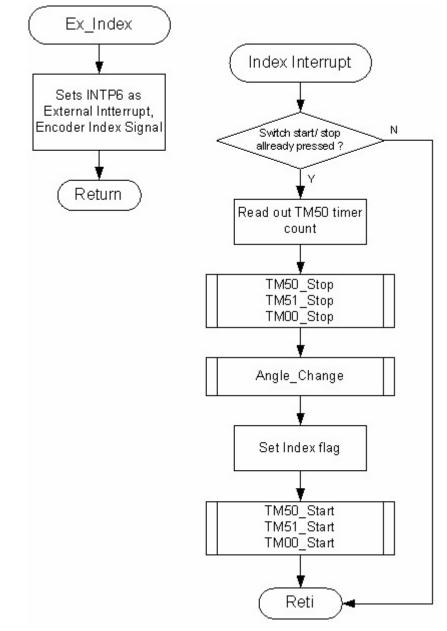

| 6.7      |            | al Index                                       |    |

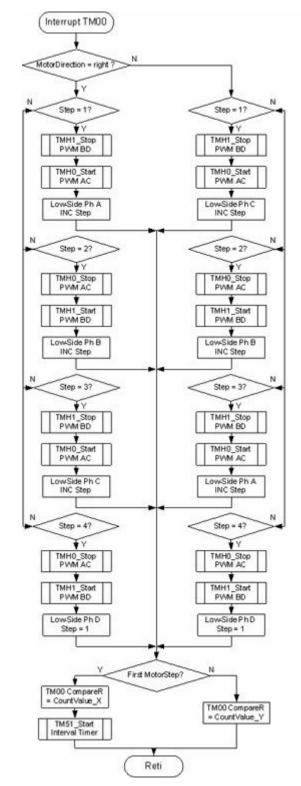

| 6.8      | TM00 in    | nterrupt                                       | 44 |

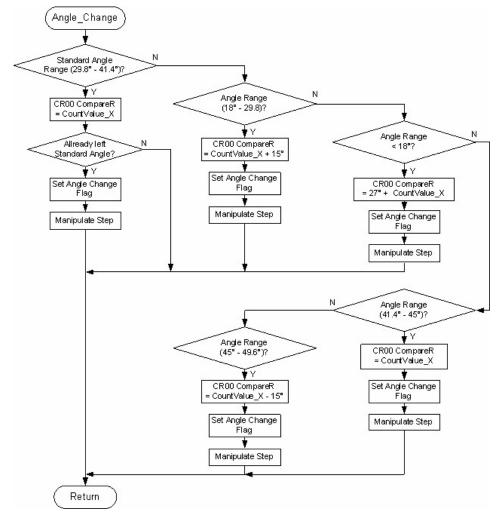

| 6.9  | Angle Change        | 45 |

|------|---------------------|----|

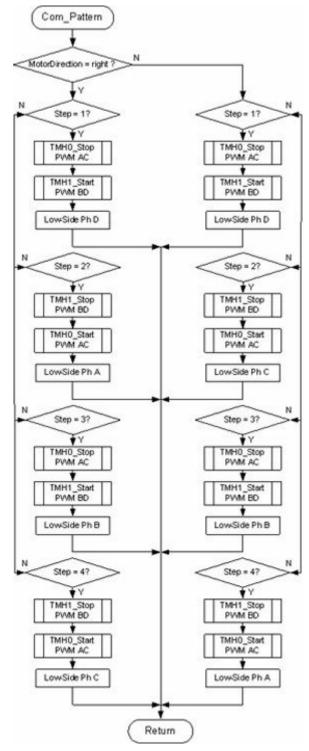

| 6.10 | Commutation Pattern | 46 |

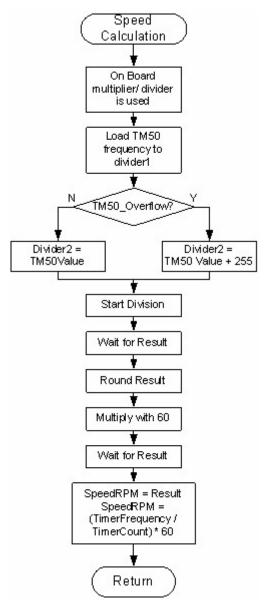

| 6.11 | Speed Calculation   | 47 |

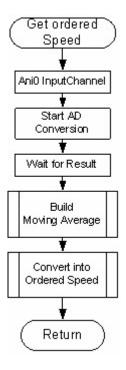

| 6.12 | Get ordered Speed   | 48 |

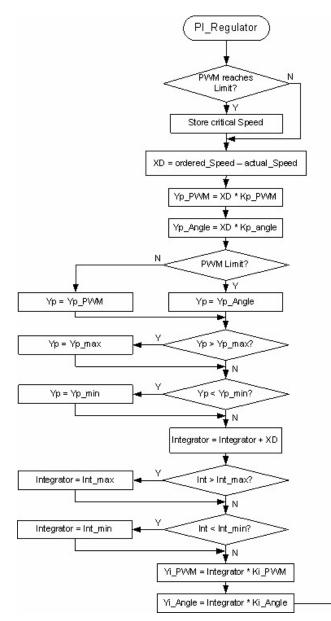

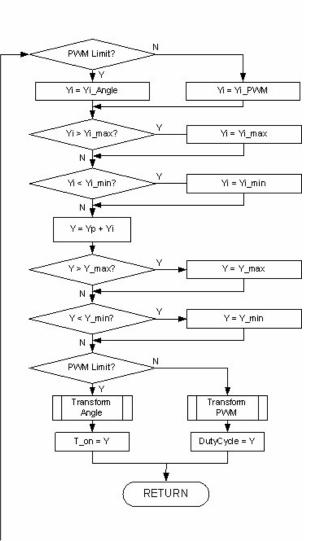

| 6.13 | PI-Regulator        | 49 |

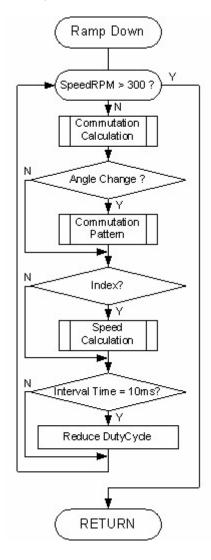

| 6.14 | Ramp Down           | 50 |

# **Chapter 1 Overview**

## 1.1 Introduction

Switched reluctance motors are gaining wider popularity among variable speed drives. This is due to their simple low-cost construction characterized by an absence of magnets and rotor winding, high level of performance over a wide range of speeds, and fault-tolerant power stage design. For numerous applications, availability and the moderate cost of the necessary electronic components make SR drives a viable alternative to other commonly used motors.

Purpose of this application note is to show how a SR motor control is realised on the  $\mu$ PD78K0/KC2 along with a drive circuit. The software and hardware configurations published here are just examples and are not intend for mass production.

## 1.2 Overview of µPD78F0515D Series

|                                    |                        | Functional Outline 1/2                   | N   |            |              |                      |                                                                                                |                                       |                                  |                       |                       |                                                                                                                                                       |          |    |

|------------------------------------|------------------------|------------------------------------------|-----|------------|--------------|----------------------|------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------|-----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----|

|                                    |                        | Part number                              |     | 78K0/KB2   | /KB2         |                      |                                                                                                |                                       |                                  | 78K0/KC2              | /KC2                  |                                                                                                                                                       |          |    |

| ltem                               |                        |                                          |     | 30/36 pins | pins         |                      |                                                                                                | 44 pins                               |                                  |                       |                       | 48 pins                                                                                                                                               |          |    |

| Flash memory (KB)                  |                        |                                          | 8   | 16         | 24           | 32                   | 16                                                                                             | 24                                    | 32                               | 16                    | 24                    | 32                                                                                                                                                    | 48       | 60 |

| RAM (KB)                           |                        |                                          | 0.5 | 0.75       | -            | ۰                    | 0.75                                                                                           | 1                                     | ۰                                | 0.75                  | ٢                     | 1                                                                                                                                                     | 2        | З  |

| Bank (Flash memory)                | (                      |                                          |     |            |              |                      |                                                                                                | I                                     |                                  |                       |                       |                                                                                                                                                       |          |    |

| Power supply voltage               | ē                      |                                          |     |            |              |                      | _                                                                                              | V <sub>DD</sub> = 1.8 to 5.5 V        | to 5.5 \                         |                       |                       |                                                                                                                                                       |          |    |

| Regulator                          |                        |                                          |     |            |              |                      |                                                                                                | Provided                              | ded                              |                       |                       |                                                                                                                                                       |          |    |

| Minimum instruction execution time | execution              | time                                     |     | 0.1        | µs (20 N     | 1Hz: V <sub>DI</sub> | $_{0.4}$ = 4.0 to 5.5 V) / 0.2 µs (10 MHz: )<br>0.4 µs (5 MHz: V <sub>DD</sub> = 1.8 to 5.5 V) | 5.5 V) /<br>MHz: V <sub>C</sub>       | 0.2 µs (1<br><sub>00</sub> = 1.8 | 0 MHz: \<br>to 5.5 V) | / <sub>DD</sub> = 2.7 | 0.1 µs (20 MHz: V <sub>DD</sub> = 4.0 to 5.5 V) / 0.2 µs (10 MHz: V <sub>DD</sub> = 2.7 to 5.5 V) /<br>0.4 µs (5 MHz: V <sub>DD</sub> = 1.8 to 5.5 V) | /(       |    |

|                                    |                        | High-speed system                        |     | 20 MHz:    | $V_{DD} = 4$ | .0 to 5.5            | V / 10 N                                                                                       | IHz: V <sub>DD</sub>                  | = 2.7 to                         | 5.5 V / 5             | MHz: V                | 20 MHz: $V_{DD}$ = 4.0 to 5.5 V / 10 MHz: $V_{DD}$ = 2.7 to 5.5 V / 5 MHz: $V_{DD}$ = 1.8 to 5.5 V                                                    | to 5.5 V |    |

|                                    | Mail                   | Int. high-speed osc.                     |     |            |              |                      | 8 MHz (                                                                                        | 8 MHz (TYP.): $V_{DD} = 1.8$ to 5.5 V | <sub>D</sub> = 1.8               | to 5.5 V              |                       |                                                                                                                                                       |          |    |

| CLOCK                              | Subsystem              | E                                        |     |            |              |                      |                                                                                                | 32                                    | 768 kH                           | lz (ТҮР.):            | $V_{DD} = 1$          | 32.768 kHz (ТҮР.): V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                     | >        |    |

|                                    | Internal lo            | Internal low-speed oscillation           |     |            |              |                      | 240 kHz (TYP.): $V_{DD} = 1.8$ to 5.5 V                                                        | (ТҮР.): V                             | <sub>DD</sub> = 1.8              | to 5.5 V              |                       |                                                                                                                                                       |          |    |

|                                    | Total                  |                                          |     | 23         | 8            |                      |                                                                                                | 37                                    |                                  |                       |                       | 41                                                                                                                                                    |          |    |

|                                    | N-ch O.D.              | N-ch O.D. (6 V tolerance)                |     | 2          |              |                      |                                                                                                | 4                                     |                                  |                       |                       | 4                                                                                                                                                     |          |    |

|                                    | 16 bits (TM0)          | (O)                                      |     |            |              |                      |                                                                                                | 1-ch                                  | Ч                                |                       |                       |                                                                                                                                                       |          |    |

|                                    | 8 bits (TM5)           | 5)                                       |     |            |              |                      |                                                                                                | 2-ch                                  | h                                |                       |                       |                                                                                                                                                       |          |    |

| Timer                              | 8 bits (TMH)           | (H)                                      |     |            |              |                      |                                                                                                | 2-ch                                  | ų                                |                       |                       |                                                                                                                                                       |          |    |

|                                    | Watch                  |                                          |     | '          |              |                      |                                                                                                |                                       |                                  | 1-ch                  | ch                    |                                                                                                                                                       |          |    |

|                                    | WDT                    |                                          |     |            |              |                      |                                                                                                | 1-ch                                  | ų                                |                       |                       |                                                                                                                                                       |          |    |

|                                    | 3-wire CSI             |                                          |     |            |              |                      |                                                                                                | '                                     |                                  |                       |                       |                                                                                                                                                       |          |    |

|                                    | Automatic<br>3-wire CS | Automatic transmit/receive<br>3-wire CSI |     |            |              |                      |                                                                                                | I                                     |                                  |                       |                       |                                                                                                                                                       |          |    |

| Serial Interface                   | UART/3-w               | UART/3-wire CSI <sup>Note</sup>          |     |            |              |                      |                                                                                                | 1-ch                                  | ų                                |                       |                       |                                                                                                                                                       |          |    |

|                                    | UART sup               | UART supporting LIN bus                  |     |            |              |                      |                                                                                                | 1-ch                                  | ۴                                |                       |                       |                                                                                                                                                       |          |    |

|                                    | I²C bus                |                                          |     |            |              |                      |                                                                                                | 1-ch                                  | ų                                |                       |                       |                                                                                                                                                       |          |    |

| 10-bit A/D                         |                        |                                          |     | 4-ch       | h            |                      |                                                                                                |                                       |                                  | 8-ch                  | ch                    |                                                                                                                                                       |          |    |

| 2          |

|------------|

| -          |

| ()<br>()   |

| ž          |

|            |

| H          |

| ีอี        |

| $\leq$     |

| g          |

|            |

| <u>e</u> . |

| な          |

| Ĕ          |

|            |

| LL.        |

|            |

| -          |

| ÷г.,       |

| <b>T</b>   |

| <u>e</u>   |

| ρ          |

| , a        |

|            |

10

|                               | Part number                                        | 78K0/KB2                      |                                                                      | 78K0/KC2                  |     |

|-------------------------------|----------------------------------------------------|-------------------------------|----------------------------------------------------------------------|---------------------------|-----|

| ltem                          |                                                    | 30/36 pins                    | 44 pins                                                              | 48 pins                   |     |

| +                             | External                                           | 9                             | 2                                                                    | 8                         |     |

| Interrupt                     | Internal                                           | 14                            |                                                                      | 16                        |     |

| Key interrupt                 |                                                    | •                             |                                                                      | 4-ch                      |     |

|                               | RESET pin                                          |                               | Provided                                                             |                           |     |

|                               | POC                                                | 1.59 V                        | $1.59 V \pm 0.15 V$ (rise time to 1.8 V: 3.6 ms (MIN.))              | :: 3.6 ms (MIN.))         |     |

| Heset                         | LVI                                                | The detection le              | The detection level of the supply voltage is selectable in 16 steps. | s selectable in 16 steps. |     |

|                               | WDT                                                |                               | Provided                                                             |                           |     |

| Clock output/buzzer output    | r output                                           | 1                             |                                                                      | Clock output only         |     |

| Multiplier/divider            |                                                    |                               | I                                                                    | Provided                  | led |

| On-chip debug function        | tion                                               | µPD78F0503D only              | hPD78F0513D only                                                     | µPD78F0515D only          |     |

| Operating ambient temperature | emperature                                         |                               | $T_A = -40$ to $+85^{\circ}C$                                        |                           |     |

| Note: Select either           | Note: Select either of the functions of these alte | nese alternate-function pins. |                                                                      |                           |     |

)

Application Note U18498EE1V0AN00

|                                    | I anie 1-2           | runctional Outline Z/Z                   | 212  |    |    |          |                           |          |                          |                                                                                                                                                       |                                |                                |                  |                            |                      |          |       |          |     |     |

|------------------------------------|----------------------|------------------------------------------|------|----|----|----------|---------------------------|----------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|------------------|----------------------------|----------------------|----------|-------|----------|-----|-----|

|                                    |                      | Part number                              |      |    | 78 | 78K0/KD2 | 12                        |          |                          |                                                                                                                                                       |                                | 78.                            | 78K0/KE2         | 2                          |                      |          |       | 78K0/KF2 | KF2 |     |

| ltem                               |                      |                                          |      |    | 4) | 52 pins  |                           |          |                          |                                                                                                                                                       |                                | 9                              | 64 pins          |                            |                      |          |       | 80 pins  | su  |     |

| Flash memory (KB)                  | (B)                  |                                          | 16   | 24 | 32 | 48       | 60                        | 96       | 128                      | 16                                                                                                                                                    | 24                             | 32                             | 48               | 60                         | 96                   | 128      | 48    | 60       | 96  | 128 |

| RAM (KB)                           |                      |                                          | 0.75 | 1  | 1  | 2        | 3                         | 5        | 7                        | 0.75                                                                                                                                                  | 1                              | ٢                              | 2                | 3                          | 5                    | 7        | 2     | 3        | 5   | 7   |

| Bank (Flash memory)                | nory)                |                                          |      |    | ı  |          |                           | 4        | 9                        |                                                                                                                                                       |                                | I                              |                  |                            | 4                    | 9        | I     |          | 4   | 9   |

| Power supply voltage               | oltage               |                                          |      |    |    |          |                           |          |                          | ۷D                                                                                                                                                    | 0 = 1.8                        | V <sub>DD</sub> = 1.8 to 5.5 V | >                |                            |                      |          |       |          |     |     |

| Regulator                          |                      |                                          |      |    |    |          |                           |          |                          |                                                                                                                                                       | Provided                       | ded                            |                  |                            |                      |          |       |          |     |     |

| Minimum instruction execution time | tion execu           | ution time                               |      |    |    | Ö        | 1 µs (2                   | 0 MHz:   | V <sub>DD</sub> =<br>0.4 | 0.1 µs (20 MHz: V <sub>DD</sub> = 4.0 to 5.5 V) / 0.2 µs (10 MHz: V <sub>DD</sub> = 2.7 to 5.5 V) /<br>0.4 µs (5 MHz: V <sub>DD</sub> = 1.8 to 5.5 V) | .5 V) /<br>IHz: V <sub>E</sub> | 0.2 µs (<br><sub>D</sub> = 1.8 | 10 MHz<br>to 5.5 | z: V <sub>DD =</sub><br>V) | = 2.7 to             | 5.5 V) / |       |          |     |     |

|                                    | :<br>:<br>           | High-speed system                        |      |    |    | 20 MH:   | 20 MHz: V <sub>DD</sub> = | = 4.0 to | 5.5 V /                  | 4.0 to 5.5 V / 10 MHz: $V_{DD}$ = 2.7 to 5.5 V / 5 MHz: $V_{DD}$ = 1.8 to                                                                             | z: V <sub>DD</sub>             | = 2.7 tc                       | 5.5 V            | / 5 MH;                    | :: V <sub>DD</sub> = | = 1.8 to | 5.5 V |          |     |     |

|                                    | Main                 | Int. high-speed osc.                     |      |    |    |          |                           |          | 8                        | 8 MHz (TYP.): V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                          | 'Ρ.): V <sub>Γ</sub>           | <sub>D</sub> = 1.8             | to 5.5           | >                          |                      |          |       |          |     |     |

| CIOCK                              | Subsystem            | m                                        |      |    |    |          |                           |          | 32.7(                    | 32.768 kHz (TYP.): V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                     | TYP.):                         | $V_{DD} = 1$                   | .8 to 5.         | 5 V                        |                      |          |       |          |     |     |

|                                    | Internal I           | Internal low-speed oscillation           |      |    |    |          |                           |          | 240                      | 240 kHz (TYP.): V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                        | YP.): V                        | DD = 1.                        | 3 to 5.5         | >                          |                      |          |       |          |     |     |

|                                    | Total                |                                          |      |    |    | 45       |                           |          |                          |                                                                                                                                                       |                                |                                | 55               |                            |                      |          |       | 71       |     |     |

|                                    | N-ch O.E             | N-ch O.D. (6 V tolerance)                |      |    |    | 4        |                           |          |                          |                                                                                                                                                       |                                |                                | 4                |                            |                      |          |       | 4        |     |     |

|                                    | 16 bits (TM0)        | (OM                                      |      |    |    |          | 1-ch                      | ň        |                          |                                                                                                                                                       |                                |                                |                  |                            |                      | 2-ch     | ň     |          |     |     |

|                                    | 8 bits (TM5)         | M5)                                      |      |    |    |          |                           |          |                          |                                                                                                                                                       | 2-ch                           | ų                              |                  |                            |                      |          |       |          |     |     |

| Timer                              | 8 bits (TMH)         | (HV                                      |      |    |    |          |                           |          |                          |                                                                                                                                                       | 2-ch                           | ň                              |                  |                            |                      |          |       |          |     |     |

|                                    | Watch                |                                          |      |    |    |          |                           |          |                          |                                                                                                                                                       | 1-ch                           | h                              |                  |                            |                      |          |       |          |     |     |

|                                    | WDT                  |                                          |      |    |    |          |                           |          |                          |                                                                                                                                                       | 1-ch                           | ň                              |                  |                            |                      |          |       |          |     |     |

|                                    | 3-wire CSI           | SI                                       |      |    |    |          | T                         |          |                          |                                                                                                                                                       |                                |                                |                  |                            |                      | 1-ch     | Ŕ     |          |     |     |

|                                    | Automati<br>3-wire C | Automatic transmit/receive<br>3-wire CSI |      |    |    |          |                           |          | I                        |                                                                                                                                                       |                                |                                |                  |                            |                      |          |       | 1-ch     | c   |     |

| Serial Interface                   | UART/3-              | UART/3-wire CSI <sup>Note</sup>          |      |    |    |          |                           |          |                          |                                                                                                                                                       | 1-ch                           | Ч                              |                  |                            |                      |          |       |          |     |     |

|                                    | UART su              | UART supporting LIN bus                  |      |    |    |          |                           |          |                          |                                                                                                                                                       | 1-ch                           | h                              |                  |                            |                      |          |       |          |     |     |

|                                    | I²C bus              |                                          |      |    |    |          |                           |          |                          |                                                                                                                                                       | 1-ch                           | h                              |                  |                            |                      |          |       |          |     |     |

| 10-bit A/D                         |                      |                                          |      |    |    |          |                           |          |                          |                                                                                                                                                       | 8-ch                           | ň                              |                  |                            |                      |          |       |          |     |     |

|                                    |                      |                                          |      |    |    |          |                           |          |                          |                                                                                                                                                       |                                |                                |                  |                            |                      |          |       |          |     |     |

12

|                               | Part number                                                            | 78K0/KD2                 | 78                                                      | 78K0/KE2                                                             | 78K0/KF2         |

|-------------------------------|------------------------------------------------------------------------|--------------------------|---------------------------------------------------------|----------------------------------------------------------------------|------------------|

| ltem                          |                                                                        | 52 pins                  | 9                                                       | 64 pins                                                              | 80 pins          |

| +                             | External                                                               | ω                        |                                                         | 0                                                                    |                  |

| Interrupt                     | Internal                                                               | 16                       |                                                         | 19                                                                   | 20               |

| Key interrupt                 |                                                                        |                          | 8-ch                                                    |                                                                      |                  |

|                               | RESET pin                                                              |                          | Provided                                                |                                                                      |                  |

|                               | POC                                                                    | 1.59 V ± 0.              | 1.59 V $\pm$ 0.15 V (rise time to 1.8 V: 3.6 ms (MIN.)) | V: 3.6 ms (MIN.))                                                    |                  |

| Heset                         | LVI                                                                    | The detection level      | of the supply voltage                                   | The detection level of the supply voltage is selectable in 16 steps. |                  |

|                               | WDT                                                                    |                          | Provided                                                |                                                                      |                  |

| Clock output/buzzer output    | zzer output                                                            | Clock output only        |                                                         | Provided                                                             |                  |

| Multiplier/divider            | ~                                                                      | - Provided               | I                                                       | Provided                                                             | ded              |

| On-chip debug function        | function                                                               | µPD78F0527D only         | µPD78                                                   | µPD78F0537D only                                                     | µPD78F0547D only |

| Operating ambient temperature | ent temperature                                                        |                          | $T_A = -40$ to $+85^{\circ}C$                           | O                                                                    |                  |

| Note: Select eit              | Note: Select either of the functions of these alternate-function pins. | alternate-function pins. |                                                         |                                                                      |                  |

runctions of these alternate-function pins. or the Note: Select either

# **Chapter 2 Switched Reluctance Motor Basics**

## 2.1 Switched Reluctance Motor Basics

A Switched Reluctance (SR) motor is an electromagnetic, rotary machine in which torque is produced by the tendency of its movable part to move to a position where the inductance of the excited winding is maximized. The SR motor has the simplest mechanical structure compared with other types of electrical machines. Both stator and rotor have salient poles, the stator winding is compromised of a set of coils, each wound on pole, the rotor is only made with steal lamination stacked onto the shaft. This is the main difference with conventional motors like DC or induction motors which have rotor windings or permanent magnets.

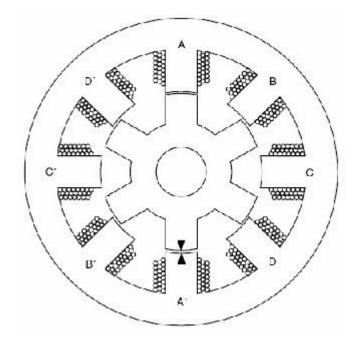

Various options of rotor and stator poles may be used. By increasing the number of phases the torque ripple can be reduced, but more electronic will be needed increasing the whole solution price. A compromise has to be chosen knowing that different number of rotor and stator poles and a minimum of two phases are necessary to start the motor, and three phases to choose the starting direction. This Application Note deals with a four phase regular 8/6 motor shown in *Figure 2-1*. This combination is far spread and provides lesser torque ripple.

#### Figure 2-1 Four-phase 8/6 SR motor

The advantage of the easy build up rotor carries also some disadvantages. The reliance on a single excitation source, coupled with the effects of fringing fields and magnetic saturation, renders the switched reluctance motor nonlinear in its control characteristics.

As mentioned above the torque is produced by the rotors tendency to move to the position of least reluctance / highest inductance. The motor is excited by a sequence of current pulses applied at each phase. The individual phases are consequently excited, forcing the motor to rotate. This way of driving is similar to the one used for stepper motors.

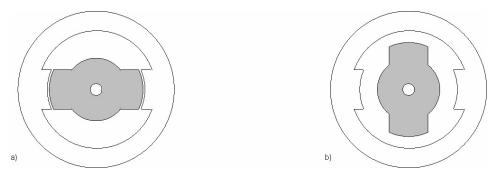

The basic movement of the motor can be best shown by reducing the defaults to the simplest arrangements. We look at the rotor as one pole-pair and the stator comes down to two magnetic poles with one phase.

#### Figure 2-2 One-phase SR motor, aligned, unaligned position

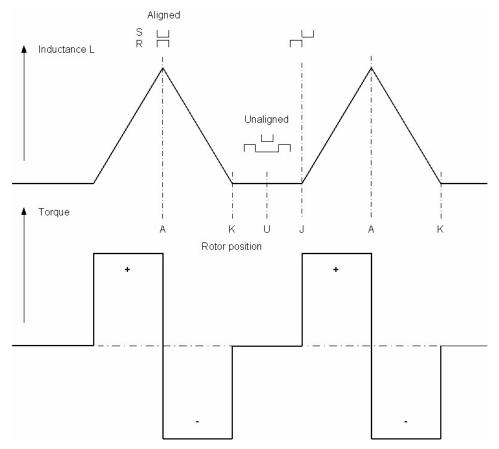

In this simple machine the coil inductance L varies with the rotor position  $\theta$  as shown in *Figure 2-3*. Assume that the coil carries a constant current. Positive motoring torque is only produced while the inductance is increasing as the rotor approaches the aligned position between positions J and A. At J, the leading edge of the rotor pole is aligned with the first edge of the stator pole; at A, the rotor and stator poles are fully aligned Figure 2-2 a). Thus J defines the start of overlap, A the maximum, and K the end of the overlap.

An important occurrence is that the torque changes direction at the aligned position. If the rotor continues past A, the attractive force between the poles produces a braking torque.

To eliminate these negative torque impulses, the constant current must be switched off during this pole separating time period.

The ideal current waveform is therefore a series of pulses synchronized with the rising inductance intervals. The cycle of torque production associated with one current pulse is called a stroke.

Figure 2-3 Variation of inductance and torque with rotor position

Although the torque maintains a nonzero average value during a rotation, it's discontinues and the rotation is only kept up due to the flywheel effect of the rotating inertia.

A big disadvantage is also that the motor can't self-start from every rotor position (e.g. the aligned position).

To compensate these disadvantages the motor is generally provided with additional phases which leads to more stator/rotor poles.

The number of strokes per revolution is related to the number of rotor poles  $N_{\text{R}}$  and the number of phases m

$$S = m * N_R(1)$$

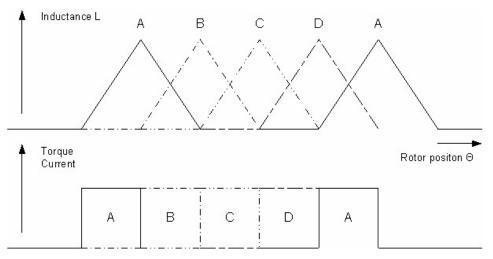

The motor in Figure 2-1 has m = 4 and N<sub>R</sub> = 6, so S = 24. The so called stroke angle or dwell angle is now  $\epsilon$  = 360 / 24 = 15°. The ideal current/torque pulses of the four phases are shown in Figure 2-3. The resultant torque is ideally constant and covers 360° of rotation.

Figure 2-4 Inductance profile 8/6 SR machine

To get better understanding of motor control requirements a knowledge of the basic formulas for SR machines is required. For simplicity we ignore the effect of fringing flux around the pole corners, magnetic saturation and assume that all the flux crosses the air gap in the radial direction.

The voltage equation for one phase is

$$v = R \cdot i + \frac{d\psi}{dt} = R \cdot i + \omega_{m} \frac{d\psi}{d\theta}$$

$$= R \cdot i + \omega_{m} \frac{d(Li)}{d\theta}$$

(2)

$$= R \cdot i + L \frac{di}{dt} + \omega_{m} \cdot i \frac{dL}{d\theta}$$

where v is the voltage across one phase, i the current,  $\psi$  the flux linkage, R the phase resistance, L inductance,  $\theta$  is the rotor position, and  $\omega_m$  is the angular velocity.

Due to the pole saliency, the magnetic path is different during the rotor motion since the reluctance is minimal when stator and rotor poles are aligned and maximum when poles are not aligned. Formally, the inductance can be written as follows:

$$\mathsf{L}(\theta) = \frac{\mathsf{N}^2}{\Re(\theta)} \quad (3)$$

with N number of coils and R phase reluctance. The equation above and the reluctance profile are responsible for inductive curves. Energy and inductance considerations lead to the following definition of the motor torque expression

$$T_{e} = \frac{1}{2}i^{2} \cdot \frac{dL}{d\theta} \qquad (4)$$

...

The equitation above says that the torque does not depend on the direction of the current. In order to obtain positive torque the phase coil needs, as already mentioned, current only during the rising edge of the inductance profile.

The synchronization of the phase polarization with the rotor poles positions is the main task of the electronic driver.

## 2.2 Switched Reluctance Motor Control Requirements

In a switch reluctance motor drive the number of motor phases, the pole geometry, the possibility for more than one phase to ensure current flow, the whole commutation concept greatly affects the drive topology.

There is a wide variety of drive circuits in use and not one topology that fits all.

Voltage supply, number of external parts, current/voltage protection, and overall flexibility are just a few aspects to consider.

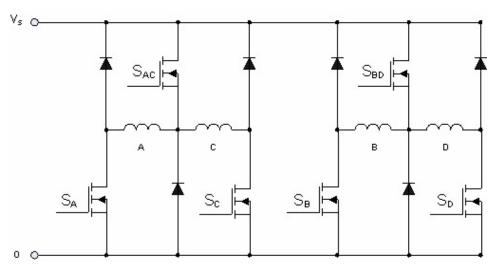

This Application Note deals with the drive topology shown in *Figure 2-5*, this "multiphase-switch" configuration is build up as an asymmetric bridge. The main advantages are the low power loss, few external parts and lesser complex drive algorithm. The circuit contains six power mosfets responsible for the current flow through the windings. Each coil can be energized in one direction by turning on the appropriate mosfets. Implicitly this configuration never energizes phases A, C or B and D at the same time.

Figure 2-5 Multiphase-switch drive topology

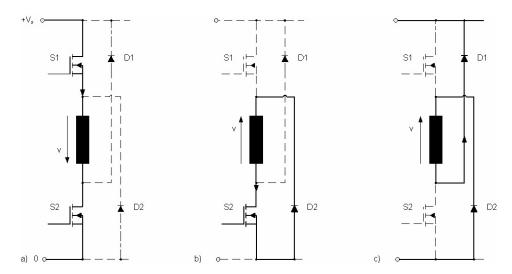

In the following we want to look closer at this drive topology. Note that the ideal current and inductance waveforms imply a saw tooth waveform of flux-linkage  $\psi$  = Li. So the flux-linkage is build up from zero every stroke and diminishes to zero back again, to do so the voltage must be reversed at the end of each stroke. *Figure 2-6* shows the half-bridge phase leg circuit in detail. This circuit can supply current in one direction, but it can supply positive, negative, or zero voltage at the phase winding.

The whole working area of the motor can be divided in two parts, the Low-speed motoring and High-speed motoring phase. At low speed the motor EMF is low compared to the available supply voltage  $V_S$ , and the current can be regulated by chopping. At a certain "base speed" the back EMF rises to a level at which the transistors must be kept throughout the stroke to sustain the rated current. Any chopping would reduce the average applied voltage and therefore the current and torque. Here the torque can only be controlled by varying the firing angles, so called single pulse control. Both regulation forms are discussed in the following.

Low-speed motoring, the voltage applied to the phase winding is  $+V_S$  if both mosfets are on, 0 if one is on and the other is off, and  $-V_S$  if both power switches are off and the phase current is freewheeling through both diodes. These three conduction modes are shown in *Figure 2-6*.

The process of fluxing and de-fluxing is controlled by switching the supply voltage on at the turn-on angle  $\theta_{On}$  and switching off at the commutation angle  $\theta_{C}$ .

At low/medium motor speeds almost all supply voltage is available to force the increase in current, subsequently to the low back-EMF. Current control is necessary at low speed.

The method of current regulation is a question of timing and width of the voltage pulses. Broadly speaking there are two main methods: current hysteresis control and voltage-PWM.

In both cases, as mentioned above, there is a flux building interval from  $\theta_{On}$  to  $\theta_{C}$ , called dwell, and the interval where both mosfets are switched off and the flux decays to zero.

In Voltage PWM there is no closed loop control of the instantaneous current. The current waveform has its natural shape at all speeds, as though the supply voltage was chopped down. For safety issues a current limiting function must be included, but because no attempt is made to control the current instantaneous there is no need to sense the current in every motor phase. Voltage PWM tends to produce quieter operation than current hysteresis control therefore this regulation form was chosen in this Application Note.

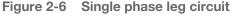

Voltage PWM chopping can be realised in two ways with this drive topology, soft chopping and hard chopping. *Figure 2-7* shows the difference and the pertinent phase current, flux linkage, voltage and inductance profile. Soft chopping is when only the high side power switch is chopping; the other switch remains permanently on. Hard chopping is when both transistors are switched on/off

together. It generally produces more acoustic and electric noise, it also generates more current ripples, therefore soft chopping was realised in this application.

Figure 2-7 Voltage PWM – soft/hard chopping

This control principle can be applied until a certain speed limit is reached. Indeed as the speed increases, the current becomes harder to control because of the back EMF and because the PWM maximum duty cycle/ frequency is reached. For this final stage the speed could be increased by advancing the firing angles  $\theta_{On}$  and  $\theta_{C}$ , the torque being than maximum as soon as the inductance increases. This is even more convenient, as longer time will be available to decrease the current before the inductance starts decreasing.

As mentioned in this and the previous section, knowing the position of the rotor is a key issue to be able to control the current and then the torque. A good torque control will require knowing the inductance profile, the moment when it is at the maximum and minimum values.

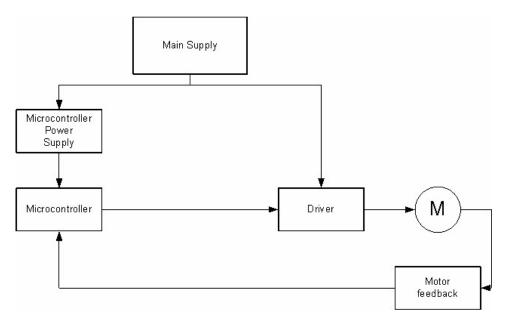

The following figure shows a schematic for general motor control design with a microcontroller.

#### Figure 2-8 General motor control design

The functions of the components in detail:

| Main supply                 | Provides circuit energy                                                                                                                                                                                                   |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MicrocontrollerPower Supply | Regulates voltage and current for the microcontroller                                                                                                                                                                     |

| Microcontroller             | Produces the accurate signals for switching the mosfets<br>also contains protection circuit, which ensures that a<br>certain current value is not exceeded. Microcontroller<br>observes and regulates the motor velocity. |

| Driver                      | Switches the power necessary for the motor phases.                                                                                                                                                                        |

| Motor feedback              | Gives continuously information about the position of the rotor, speed and spinning direction.                                                                                                                             |

Switched reluctance motor control requirements are summarized below:

- Driver circuit to provide necessary power for the SR machine

- Current limiting device (software based)

- Interrupted based microcontroller algorithm to produce exact output signals

For the velocity control of the motor

- · Information about exact rotor position

- Measurement of the motor speed

- PWM Signal to control motor current and power

# **Chapter 3 System Design Concept**

## 3.1 System Concept

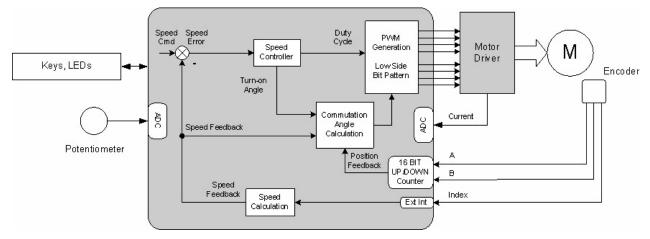

*Figure 3-9* shows the principal block diagram of the system concept for the switched reluctance motor.

Figure 3-9 Principal block diagram of the system configuration

This system is designed to drive a 4-Phase SR motor. The application meets the following performance specifications:

- Speed control of SR motor with encoder position sensor

- Targeted for 78K0/Kx2 Series

- Variable line voltage up to rated 42V DC

- Control techniques incorporates

- voltage SRM control with speed closed loop

- motor starts from any position with rotor alignment

- two directions of rotation

- motoring mode

- minimal speed 600 rpm (can be set by user)

- maximal speed depended on line voltage 4320 rpm (can be set by user)

- Encoder position reference for commutation

• User Interface (start/stop switch, right/left switch, potentiometer for speed adjustment, LED indicators)

DC-Bus over current protection

## 3.2 System Configuration

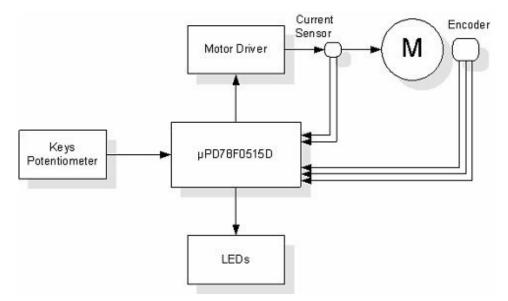

*Figure 3-10* shows the system configurations and the peripherals of the  $\mu$ PD78F0515D device used for the SR motor control.

Figure 3-10 System Configuration with the peripherals of the µPD78F0515D

The microcontroller runs the main control algorithm. It generates 4-Phase PWM output signals for the SR motor power stage according to the user interface input and feedback signals. The required speed is set by a potentiometer, furthermore a start/stop and right/left

switch is provided. When the start command is given the start-up sequence with the rotor alignment is performed and the motor is started in the desired direction.

The rotor position is evaluated using the external encoder and the commutation angle is calculated. When the actual position of the motor is equal to the reference position, the commutation of the phases in the desired direction of rotation is done; the actual phase is turned off and the following phase is turned on.

For the speed calculation no additional velocity sensor is needed, motor speed is derived from the position information.

The reference speed is calculated from user defined potentiometer value. The speed error between commanded speed and actual speed is used in the speed controller to manipulate the voltage applied to each phase winding and the firing angles. As mentioned earlier PWM Voltage regulation is used in low- and mid-speed regions, whereas advancing the turn-on angle in the single-pulse control comes active in the high speed area. The control algorithm is build up in such a matter, when the PWM regulation reaches its limits the single-pulse regulation takes over. Then during the PWM cycle, the actual phase current is compared with the absolute maximum value for the rated current. As soon as the actual current exceeds this value the PWM duty cycle is restricted.

The procedure is repeated for each commutation cycle of the motor.

## 3.2.1 Start-Up Sequence

As mentioned in the previous section one task of this application is to ensure rotor movement in both directions. Before the motor can be started in the desired rotation direction rotor alignment and initialization of the control algorithm must be performed since the absolute rotor position is not known. The start-up is performed in several steps; the result is that the rotor is aligned to a known position. Therefore at first two phases are turned on simultaneously, after 50 msec one phase is turned off and the other stays powered. After an additional 550 msec, the rotor is stabilized enough in the aligned position in respect to the powered phase.

The whole stabilization takes about one second and after this period the motor is stable enough to reliably start the motor in any direction of rotation.

## 3.2.2 Position and Speed Sensing

The position information is a key factor to generate accurate switching for the power converters and is of most importance ensuring drive stability and fast dynamic control. Speed calculation can also be derived from the position information and there is no need for additional velocity sensors.

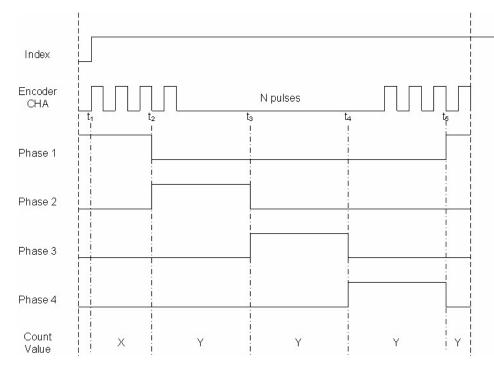

The presented application uses the on-chip 16-bit timer of the 78K0/KC2 as an Up/Down Counter. The timer counts the externally number of pulses provided by the encoder and the software determines the required values to load into the counter compare register in the correct sequence. In this application a 1000- line encoder is used so the 16- bit timer can produce defined interrupts with a resolution precision of 0.36°.

The speed can be computed by calculating the change in time of the index signal per resolution. An 8-bit interval timer is used to guarantee total independence of positioning sensing and speed sensing. It measures the time and provides the information in rpm to the system.

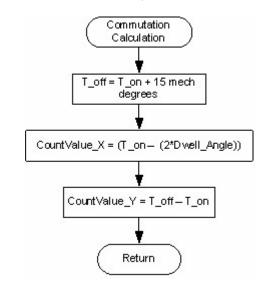

## 3.2.3 Commutation Algorithm

The SR motor commutation strategy uses rotor position feedback to drive the signals for the inverter switches. The core of the control algorithm includes the calculation of the commutation angles, and phases commutation.

Due to the 8/6 SR motor topology a fixed dwell angle of  $15^{\circ}$  is chosen to assure in cooperation with the turn-on angle that the flux should be zero throughout the period of falling inductance. Assuming the software routine outputs the commutations angles in terms of encoder counts then the next requirement is for the software to determine the required values to load into the counter in the correct sequence. The current flow through the stator windings is restricted to 15 mechanic degrees. A closer view at the Index signal of the encoder is also necessary to ensure right commutation values. To synchronize the software with the actual rotor movement, the compare value has to be manipulated every time the Index signal comes active. The values that are loaded into the timer are calculated as followed,  $T_{ON}$ ,  $T_{OFF}$  are the appropriate turn-on turn-off angles:

CountValueX =  $T_{ON}$  - (2 · DwellAngle) CountValueY =  $T_{OFF}$  -  $T_{ON}$

The software determines the values at which the system has to react and change the commutation pattern.

*Figure 3-11* shows commutation control with a high-resolution encoder and the distinct values x and y for the 16-bit timer capture compare register.

The presented commutation algorithm does not allow parallel current conduction of two phases at the same time.

## 3.2.4 Current Limiter

The application deals with voltage PWM control, there is only need for a current security loop so rated current is not exceeded. As soon as this state is detected the PWM is manipulated to prevent further current rise.

### 3.2.5 Current Sensing

Current measurement needs to be investigated according to current sensors used and the influence of noise on the measurement

The quality of current measurement depends heavily on the type of current sensor used. In this application the voltage drop across a sense resistor is used to calculate the actual current. Shunt resistors in combination with RC Low-Passes are a cheap solution and the current only needs to be limited, therefore expensive Hall Effect sensors are not used.

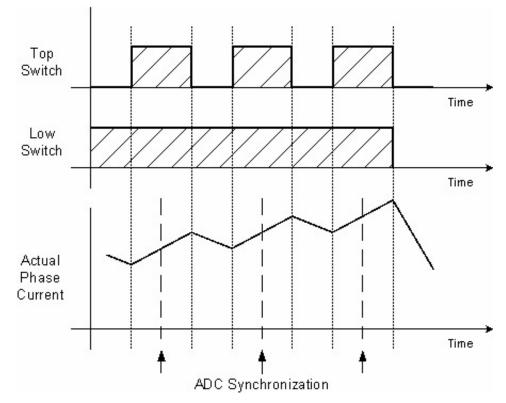

The sensing needs to be synchronized with the actual PWM signal to ensure current flow and to reduce voltage ripples. *Figure 3-12* shows the actual phase current measured on the shunt resistor as described above.

Figure 3-12 Soft switching current sensed on ADC

# **Chapter 4 Hardware Configuration**

This section describes the hardware requirements for this application example.

## 4.1 µPD78K0/KC2 Configuration

The µPD78K0/KC2 device is a member of the high performance 78K0/Kx2 Family 8-bit microcontrollers. The configuration of the device and the operating environment used in this application is listed below:

- CPU:

- Operating clock:

- Operating Voltage:

- Internal ROM:

- Internal RAM:

- External expansion memory:

µPD78F0515D System clock 20 MHz 5 V 60 Kbytes 1024 bytes not used

# 4.2 Peripherals I/O Assignments

Table 4-1 lists all pins of the  $\mu$ PD78K0/KC2 device and the ones that are used in this application are described with their associated function.

Table 4-1 µPD78K0/KC2 Peripherals I/O Assignments

| Pin no. | Pin name  | Mode setting | Function                       |

|---------|-----------|--------------|--------------------------------|

| 1       | P60/SCL0  | Output       | Not used                       |

| 2       | P61/SDA0  | Output       | Not used                       |

| 3       | P62       | Output       | Not used                       |

| 4       | P63       | Output       | Not used                       |

| 5       | P33/TO51  | Output       | Not used                       |

| 6       | P75       | Output       | Motor start/stop switch        |

| 7       | P74       | Output       | Not used                       |

| 8       | P73/KR3   | Output       | Motor direction switch         |

| 9       | P72/KR2   | Output       | LED green, regulator           |

| 10      | P71/KR1   | Output       | LED yellow, rotation direction |

| 11      | P70/KR0   | Output       | LED red, motor running         |

| 12      | P32/INTP3 | Output       | Not used                       |

| 13      | P31/INTP2 | Output       | Not used                       |

| 14      | P30/INTP1 | Output       | Not used                       |

| 15      | P17/TO50  | Output       | Not used                       |

| 16      | P16/TOH1  | Output       | Motor highside BD              |

| 17      | P15/TOH0  | Output       | Motor highside AC              |

| 18      | P14/RxD6  | Output       | Not used                       |

| 19      | P13/TxD6  | Output       | Motor lowside D                |

| 20      | P12/SO10  | Output       | Motor lowside C                |

| 21      | P11/SI10  | Output       | Motor lowside B                |

| 22      | P10/TxD0  | Output       | Motor lowside A                |

| 23      | AVREF     |              | Connect to VDD                 |

| 24      | AVSS      |              | Connect to ground              |

| 25      | ANI7/P27  | Input        | Not used                       |

| 26      | ANI6/P26  | Input        | Not used                       |

| 27      | ANI5/P25  | Input        | Not used                       |

| 28      | ANI4/P24  | Input        | Not used                       |

| 29      | ANI3/P23  | Input        | Not used                       |

| 30      | ANI2/P22  | Input        | Current sensing BD+            |

| 31      | ANI1/P21  | Input        | Current sensing AC+            |

| 32      | P20/ANI0  | Input        | Potentiometer voltage          |

| 33      | P130      | Output       | Potentiometer                  |

| 34      | P01/TI010 | Input        | Encoder channel B              |

| 35      | P00/TI000 | Input        | Encoder channel A              |

| 36      | P140/PCL  | Output       | Not used                       |

| Pin no. | Pin name   | Mode setting | Function     |

|---------|------------|--------------|--------------|

| 37      | P120/INTP0 | Output       | Not used     |

| 38      | P41        | Output       | Not used     |

| 39      | P40        | Output       | Not used     |

| 40      | RESET      | Output       | Reset input  |

| 41      | P124/XT2   | Output       | Not used     |

| 42      | P123/XT1   | Output       | Not used     |

| 43      | FLMD0      | Input        | Not used     |

| 44      | P122/X2    | Output       | System clock |

| 45      | P121/X1    | Output       | System clock |

| 46      | REGC       | Output       | Not used     |

| 47      | VSS        | Output       | Ground       |

| 48      | VDD        | Output       | Power supply |

## 4.3 Motor Specification

The 4-Phase switched reluctance motor used in this application note has eight stator poles and six rotor poles. This combination yields 24 strokes per single revolution. The mechanical angle 60° corresponds to one electrical stroke.

| Motor Type          | 4-Phase SR Motor |

|---------------------|------------------|

| Stator/ Rotor Poles | 8/6              |

| Rated Volts         | 42VDC            |

| Rated RPM           | 3500             |

| Rated Power         | 200 W            |

| Rated Current       | 10A / PH         |

## 4.4 Encoder Specification

The optional included encoder should generally have following specification and provide the signals shown in *Figure 4-13*.

Figure 4-13 General signal process of the encoder

The encoder also provides an additional Index signal, which occurs once a revolution.

## 4.5 SR Motor Driving Circuit and User Interface Circuit

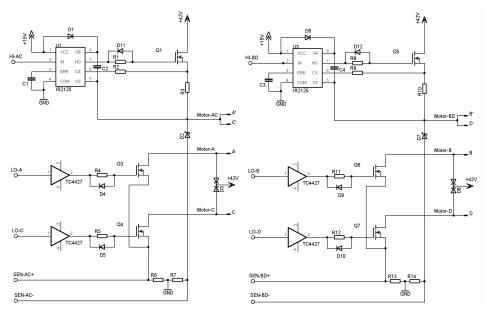

*Figure 4-14* is a schematic of the driving circuit used in the development of this application note.

Complete part list for *Figure 4-14* :

| Resistors                         |         |

|-----------------------------------|---------|

| R1, R2, R5, R4, R8, R9, R11, R12  | 10 Ω    |

| R3, R6, R7, R10, R13, R14         | 0.01 Ω  |

| Capacitors                        |         |

| C1, C3                            | 560 pF  |

| C2, C4                            | 100 nF  |

| Diodes                            |         |

| D1, D4, D5, D6, D9, D10, D11, D12 | 1N4148  |

| D2, D7                            | BYW81P  |

| D3, D8                            | BYV72   |

| MOSFET                            |         |

| Q1, Q2, Q3, Q4, Q5, Q6            | IRFP150 |

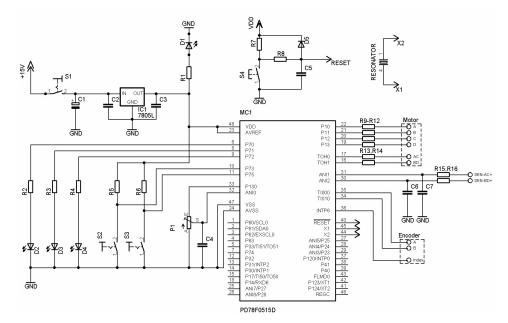

*Figure 4-15* is a schematic of the User Interface and micro peripherals used in this application note.

Complete part list for Figure 4-15 :

| Resistors                   |         |

|-----------------------------|---------|

| R1, R2, R3, R4              | 330 Ω   |

| R5, R6                      | 10 kΩ   |

| R7                          | 1 kΩ    |

| R8                          | 10 Ω    |

| R9, R10, R11, R12, R13, R14 | 100 Ω   |

| R15, R16                    | 500 Ω   |

| Capacitors                  |         |

| C1                          | 470 μF  |

| C2                          | 0.33 μF |

| C3                          | 0.1 μF  |

| C4                          | 100 pF  |

| C5                          | 1 µF    |

| C6, C7                      | 100 nF  |

Figure 4-14 Motor Driver for SR Motor

Figure 4-15 User Interface for SR Motor

# **Chapter 5 Software Process Description**

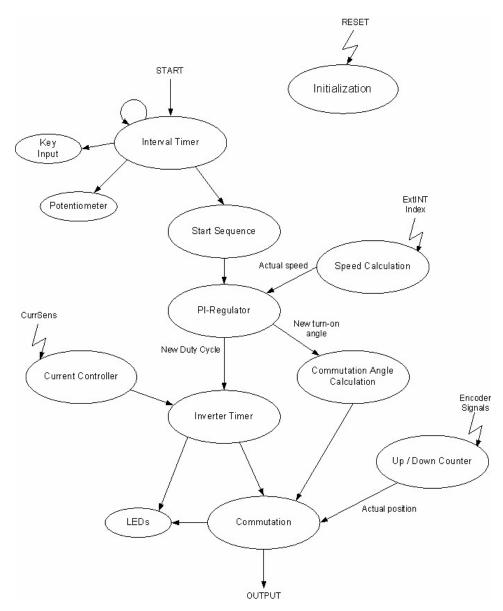

This section describes the software implementation for this application example. *Figure 5-16* shows the principal data flow diagram and the relationship between the software modules and hardware peripherals that are involved in the control of the motor.

Figure 5-16 Principal data flow diagram

The functions of the system shown in *Figure 5-16* are sequential and implemented and executed in the main endless loop of the software. The individual processes are described in detail in the following sections.

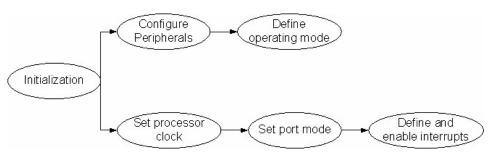

## 5.1 Initialization