# SH7786 グループ SH7786 DMAC 転送例

R01AN0807JJ0100 Rev1.00 2011.10.01

# 要旨

この資料は、SH7786 のダイレクトメモリアクセスコントローラ 0/1(DMAC0/1)、HPB-DMAC のデータ転送 例を掲載しています。

動作確認デバイス

SH7786

# 目次

| 1.     | はじめに                                                                                               | 5  |

|--------|----------------------------------------------------------------------------------------------------|----|

| 1.1    | 仕様                                                                                                 | 5  |

| 1.2    | —··                                                                                                |    |

| 1.3    | 適用条件                                                                                               |    |

| 1.4    | 関連アプリケーションノート                                                                                      |    |

| 1      |                                                                                                    | 0  |

| 2.     | DMAC0 メモリ間転送例                                                                                      | 7  |

|        |                                                                                                    |    |

| 2.1    | 応用例の説明                                                                                             |    |

| 2.1.1  | 使用機能の動作概要                                                                                          |    |

| 2.1.2  | 転送方法                                                                                               |    |

| 2.1.3  | 参考プログラムの説明                                                                                         | 13 |

| 2.1.4  | 参考プログラムのレジスタ設定                                                                                     | 14 |

| 2.1.5  | プログラム作成の注意点                                                                                        | 23 |

|        |                                                                                                    |    |

| 3.     | DMAC1 メモリ間転送例                                                                                      | 24 |

| 3.1    | 応用例の説明                                                                                             | 24 |

| 3.1.1  | 使用機能の動作概要                                                                                          | 24 |

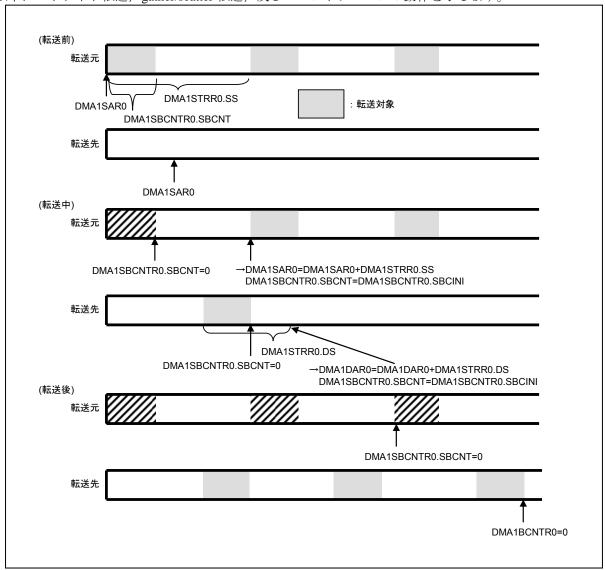

| 3.1.2  | 転送方法                                                                                               |    |

| 3.1.3  |                                                                                                    |    |

| 3.1.4  | 参考プログラムのレジスタ設定                                                                                     |    |

| 3.1.5  | プログラム作成の注意点                                                                                        |    |

| 0.1.0  |                                                                                                    | 00 |

| 4.     | HPB-DMAC データ転送例                                                                                    | 27 |

|        |                                                                                                    |    |

| 4.1    | 応用例の説明                                                                                             |    |

| 4.1.1  | 使用機能の動作概要                                                                                          |    |

| 4.1.2  | 転送方法                                                                                               |    |

| 4.1.3  | 参考プログラムの説明                                                                                         |    |

| 4.1.4  | 参考プログラムのレジスタ設定                                                                                     |    |

| 4.1.5  | プログラム作成の注意点                                                                                        | 42 |

|        |                                                                                                    |    |

| 5.     | 参考プログラムの処理手順                                                                                       |    |

| 5.1    | 共通処理手順                                                                                             | 43 |

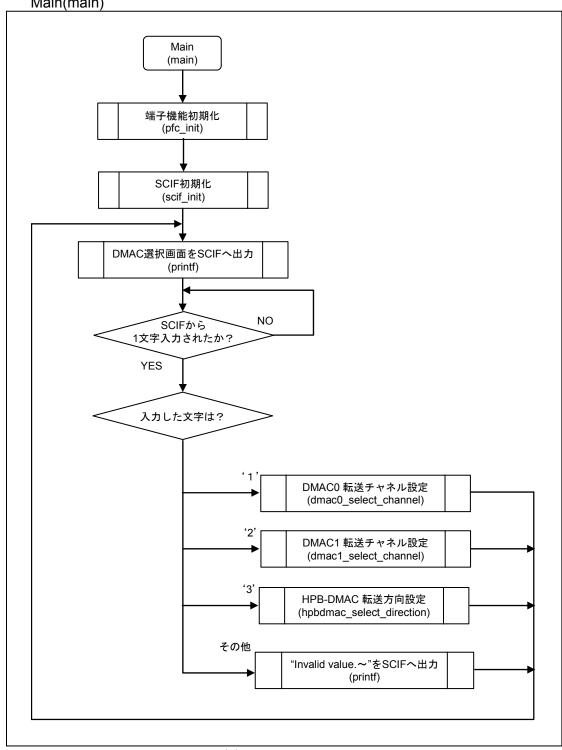

| 5.1.1  | Main(main)                                                                                         | 43 |

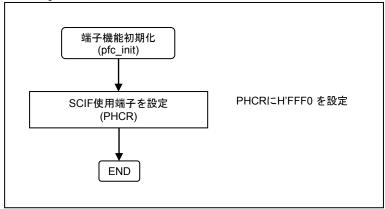

| 5.1.2  | 端子機能初期化(pfc_init)                                                                                  | 44 |

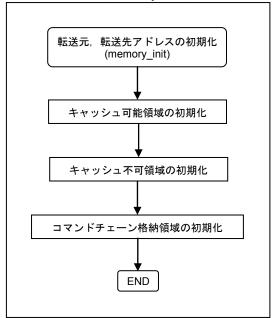

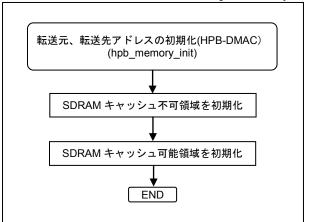

| 5.1.3  | 転送元, 転送先アドレスの初期化(memory_init)                                                                      | 44 |

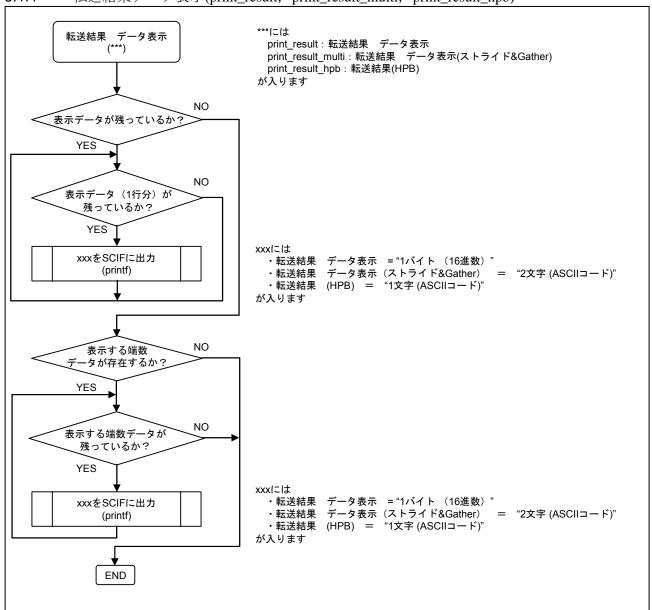

| 5.1.4  | 転送結果データ表示(print_result, print_result_multi, print_result_hpb)                                      |    |

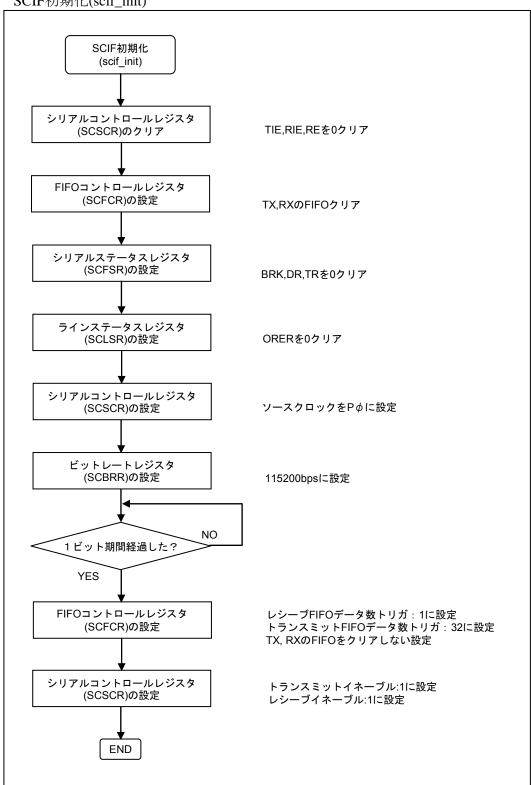

| 5.1.5  | SCIF初期化(scif_init)                                                                                 |    |

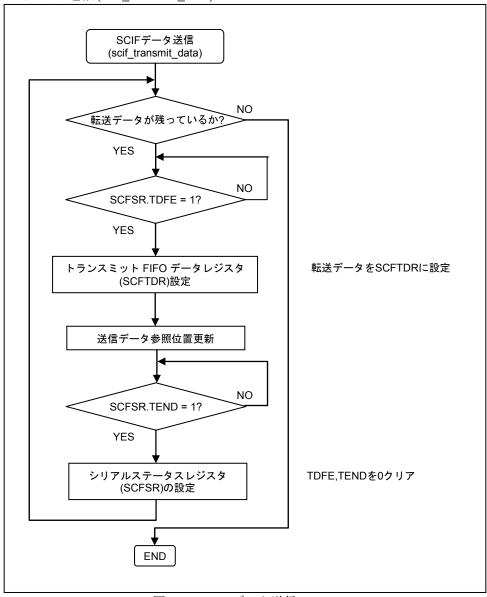

|        | SCIFデータ送信(scif_transmit_data)                                                                      |    |

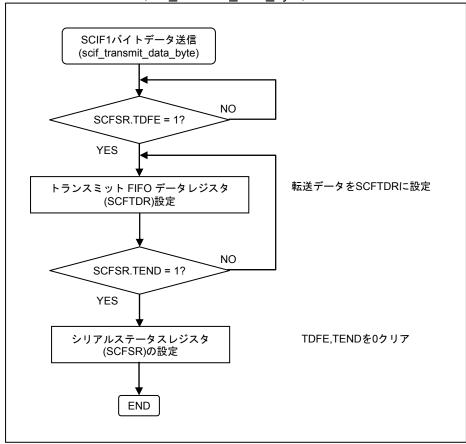

|        | SCIF1 バイトデータ送信(scif_transmit_data_byte)                                                            |    |

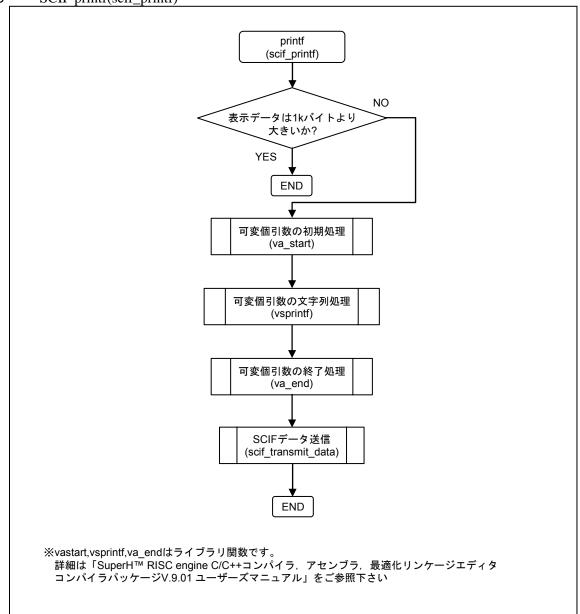

|        | SCIF printf(scif_printf)                                                                           |    |

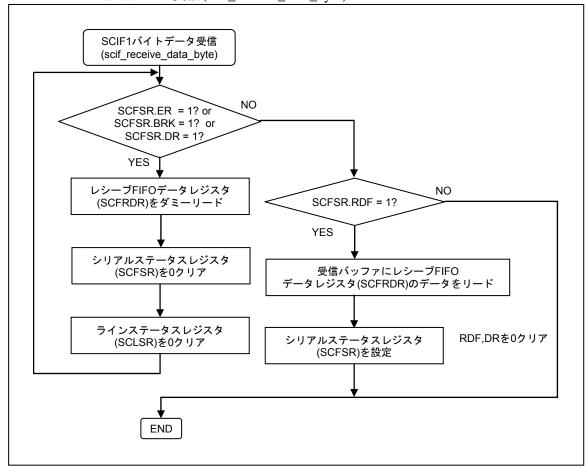

| 5.1.9  | SCIF1 バイトデータ受信(scif_recieve_data_byte)                                                             | 50 |

|        | DMAC0 処理手順                                                                                         |    |

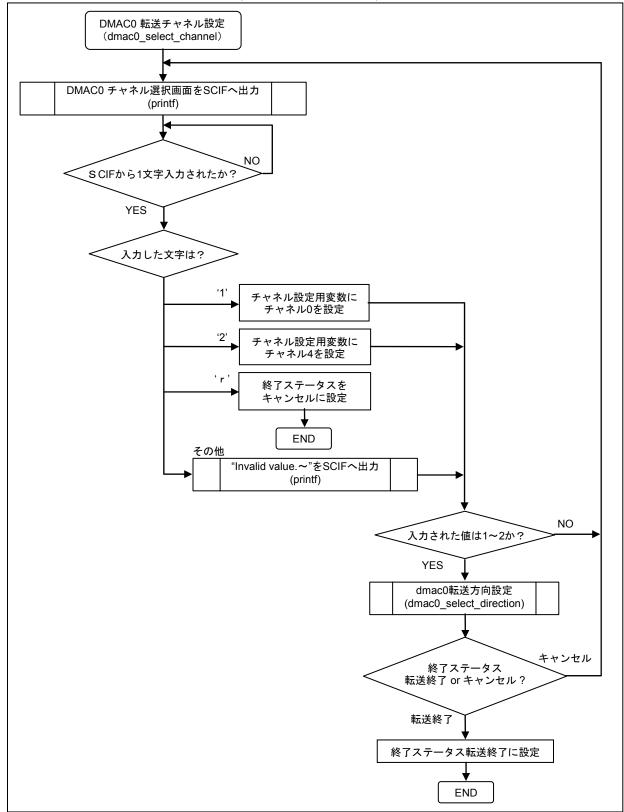

| 5.2.1  | DMAC0 転送チャネル設定(dmac0_select_channel)                                                               |    |

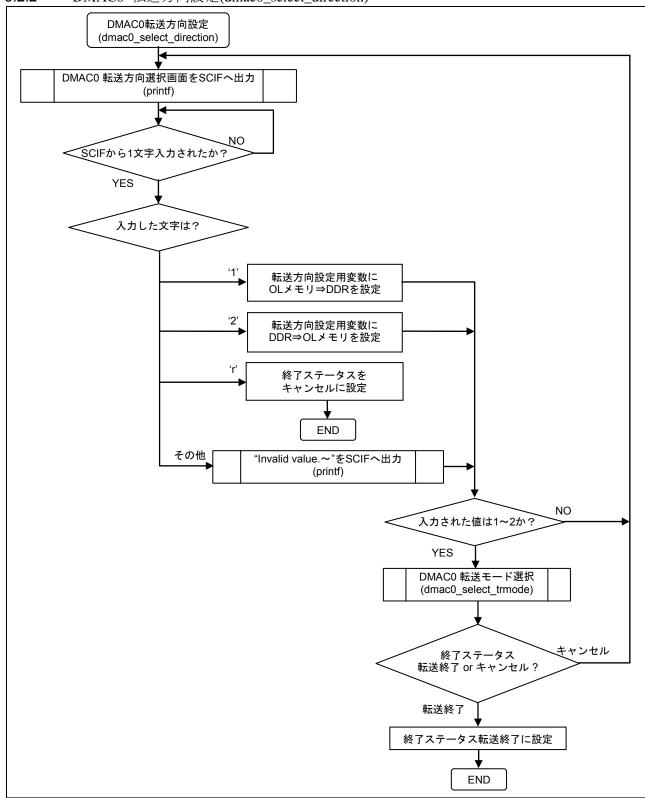

|        | DMAC0 転送方向設定(dmac0_select_direction)                                                               |    |

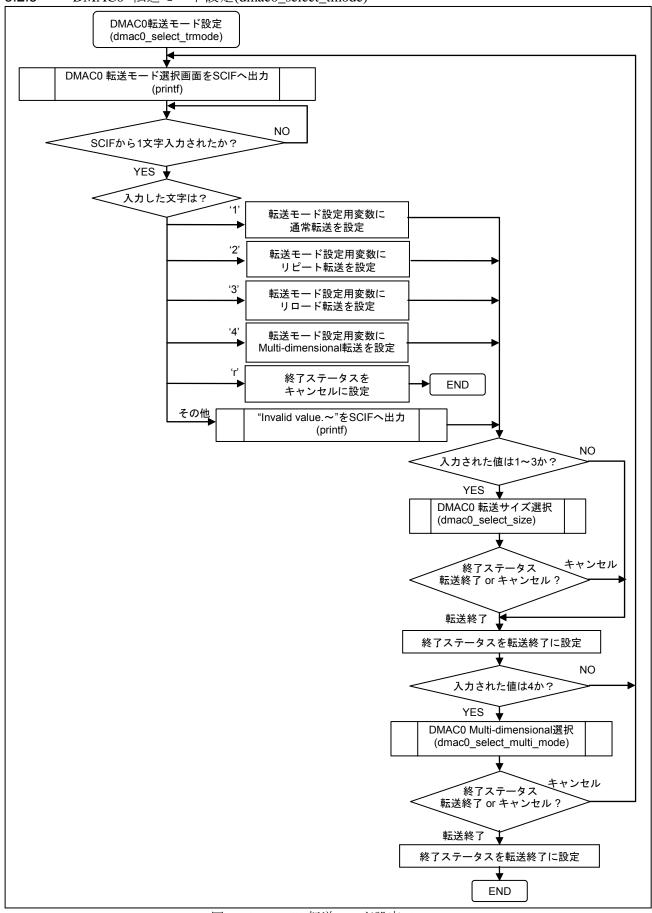

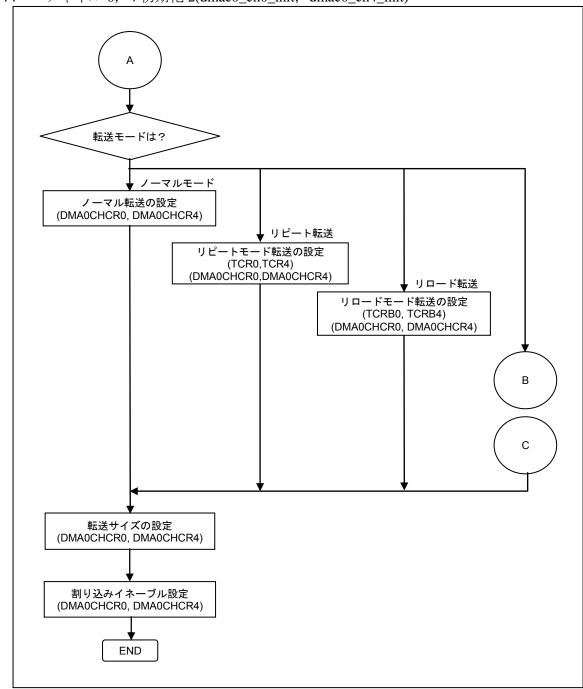

|        | DMAC0 転送モード設定(dmac0_select_tmode)                                                                  |    |

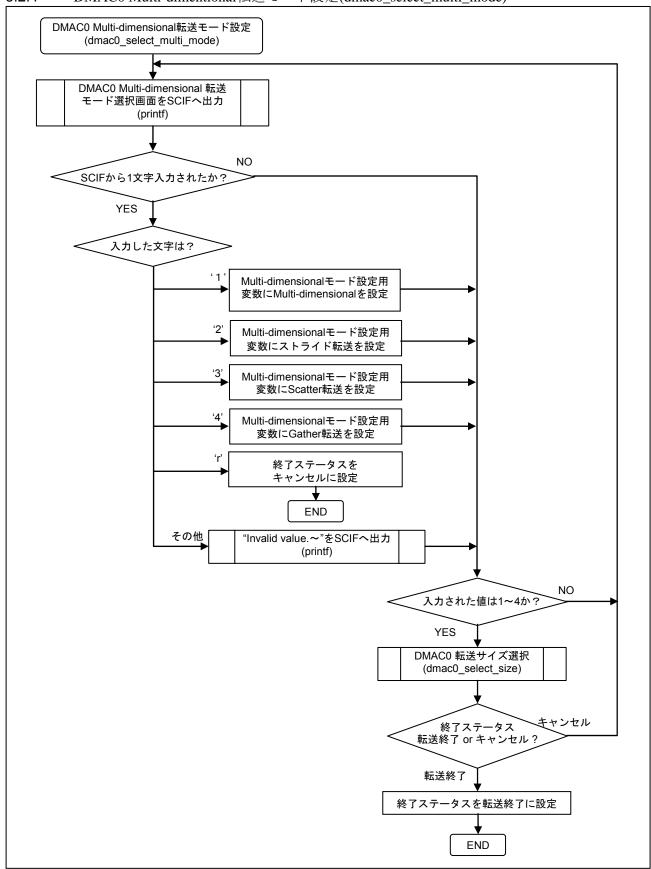

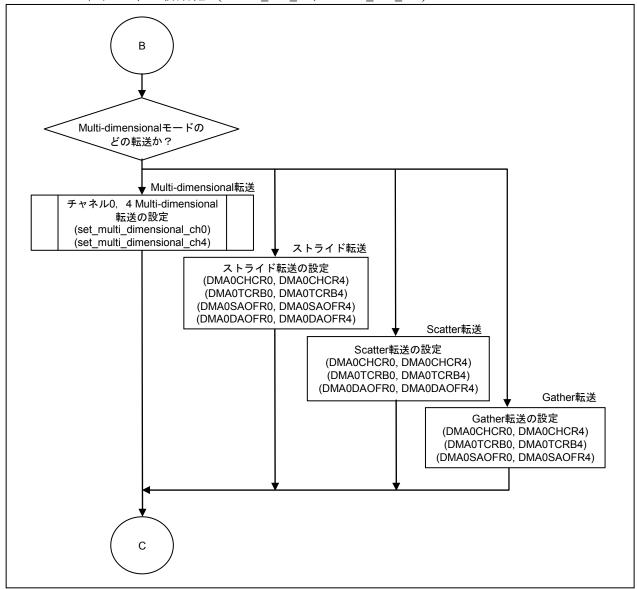

|        | DMAC0 Multi-dimentional転送モード設定(dmac0_select_multi_mode)                                            |    |

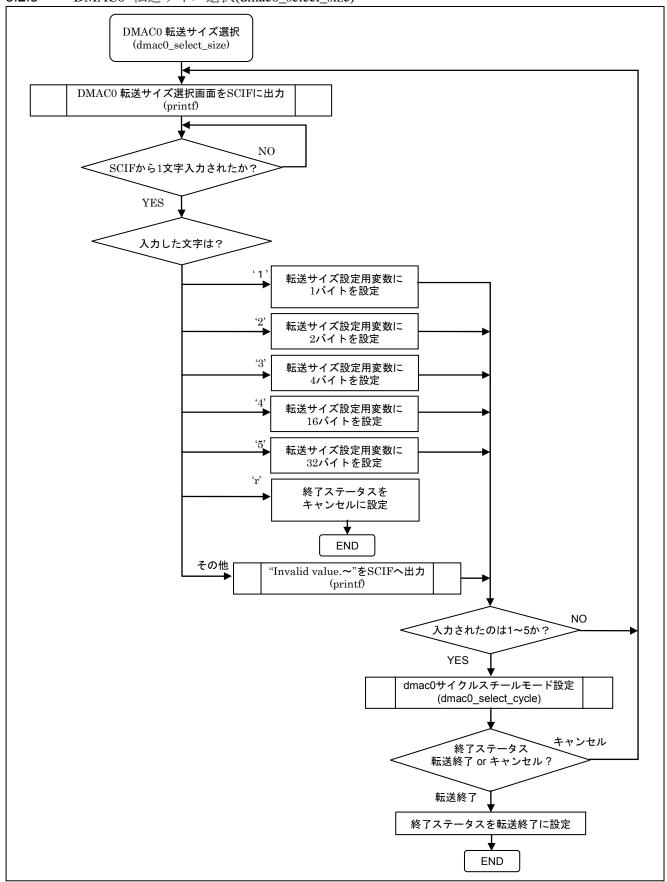

|        | DMACO width-differentional 文法と 「一般と(diffaco_select_indiff_inode)  DMACO 転送サイズ選択(dmaco_select_size) |    |

|        | DMAC0 転送 9 イス選択(dmaco_select_size)                                                                 |    |

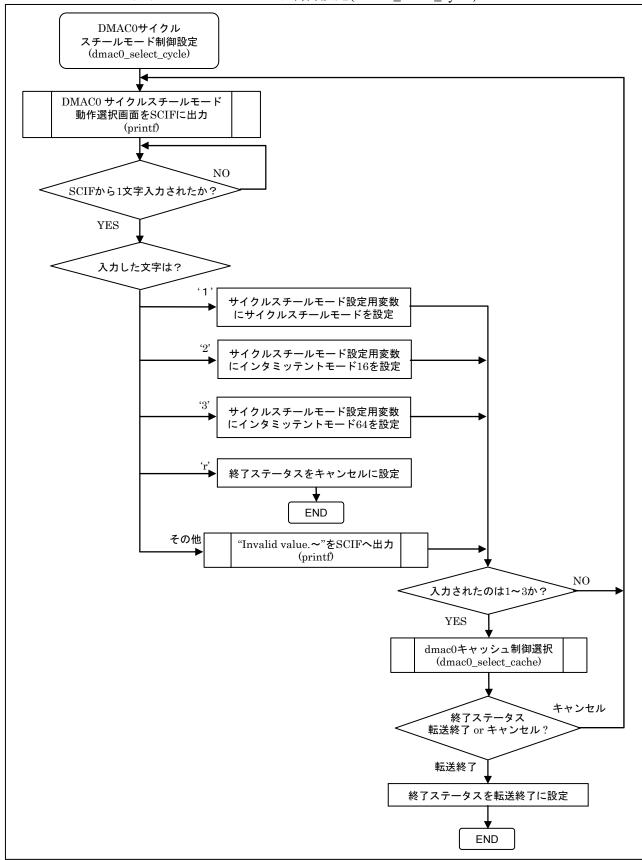

|        | DMAC0 ケイクルスケールモード制御設定(dmac0_select_cycle)                                                          |    |

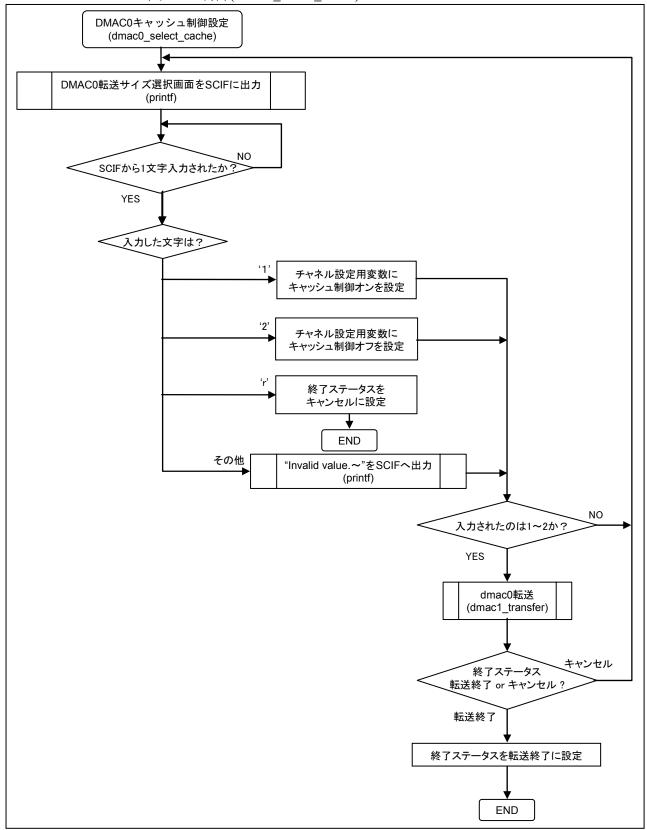

|        | DMAC0 ヤヤックユ制御(dmaco_select_cache)  DMAC0 転送(dmac0_transfer)                                        |    |

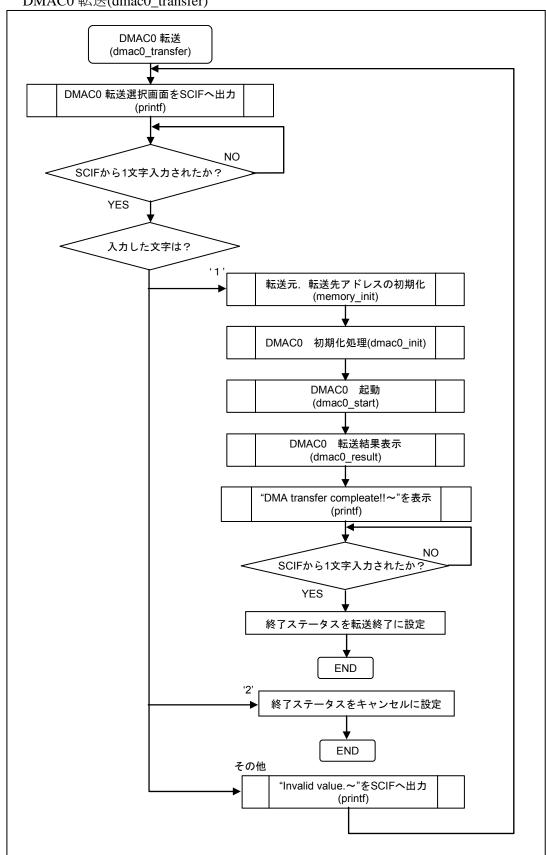

|        | DMACO 報送(dmacO_transfer)                                                                           |    |

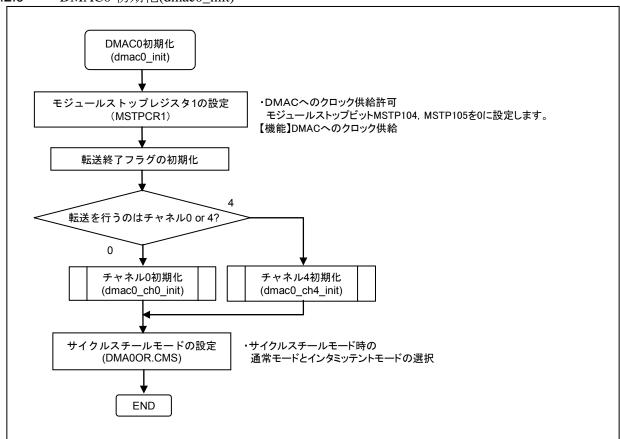

|        | DMAC0 初期に(dmac0_init)                                                                              |    |

|        | $\cdot$                    |    |

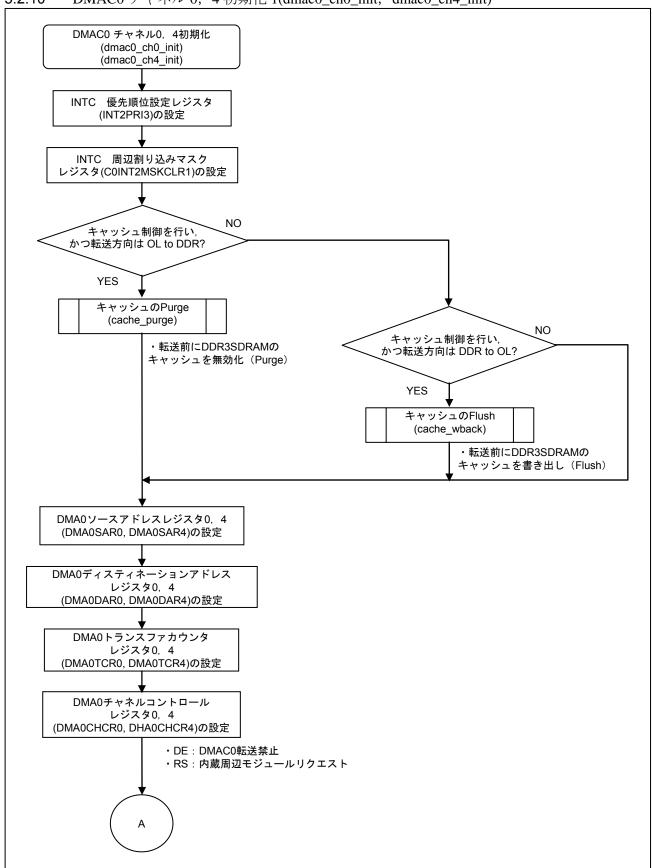

|        | チャネル 0, 4 初期化 2(dmac0_ch0_init, dmac0_ch4_init)                                                    |    |

|        | チャネル 0, 4 初期化 3(dmac0_ch0_int, dmac0_ch4_init)                                                     |    |

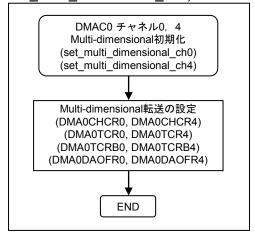

|        | DMAC0 チャネル 0, 4 Multi-dimensional初期化                                                               |    |

| (set_n | nulti_dimensional_ch0, set_multi_dimensional_ch4)                                                  | 02 |

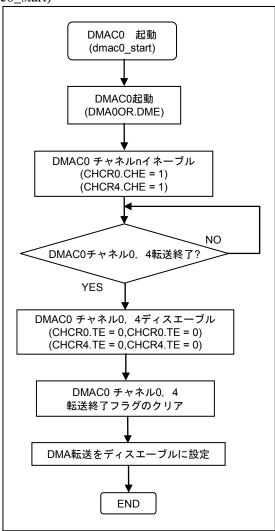

| 5.2.14 DMAC0 起動(dmac0_start)                                                              |     |

|-------------------------------------------------------------------------------------------|-----|

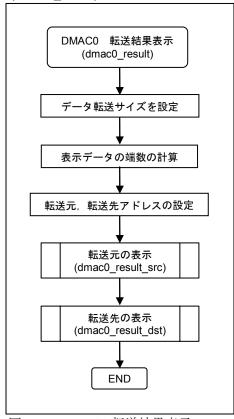

| 5.2.15 DMAC0 転送結果表示(dmac0_result)                                                         |     |

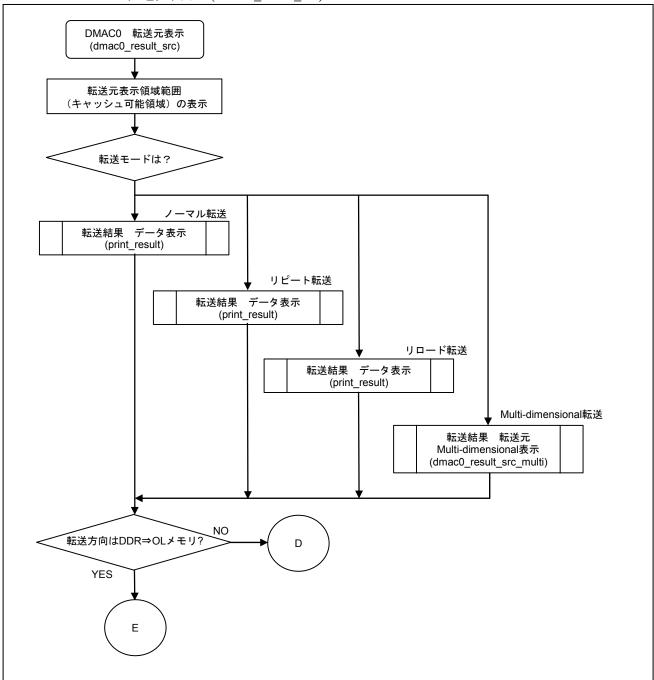

| 5.2.16 DMAC0 転送元表示 1(dmac0_result_src)                                                    |     |

| 5.2.17 DMAC0 転送元表示 2(dmac0_result_src)                                                    |     |

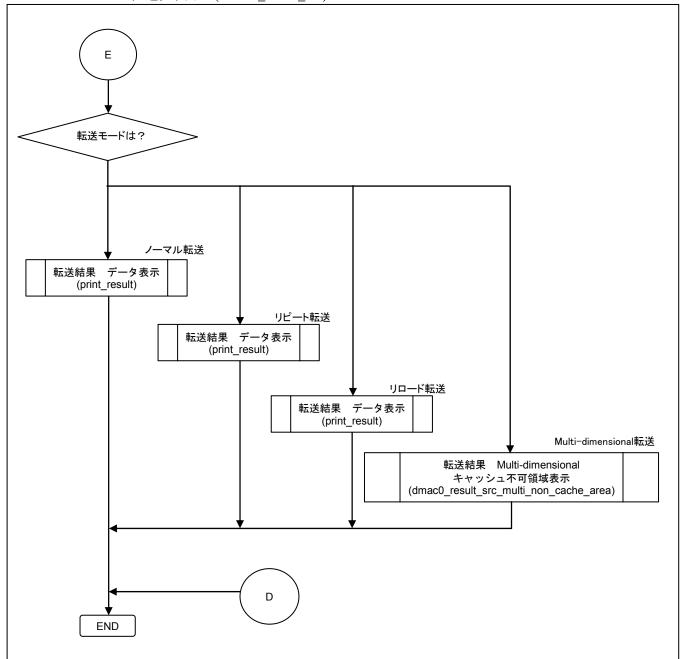

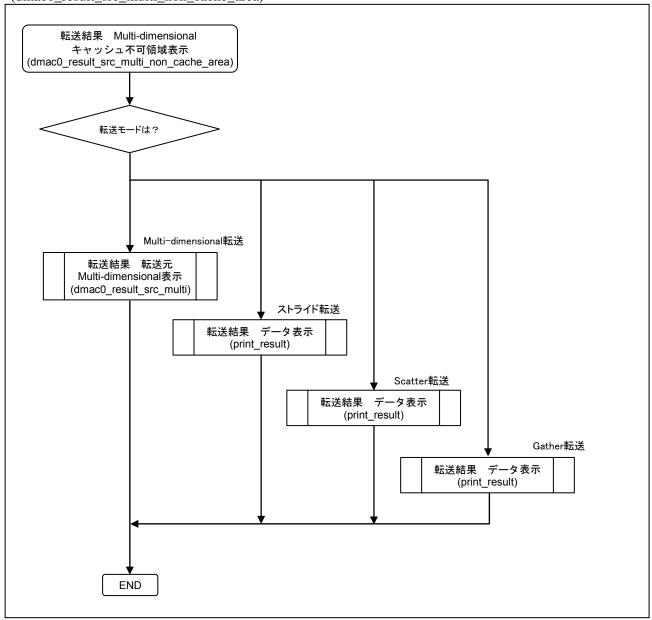

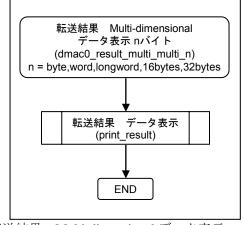

| 5.2.18 転送結果Multi-dimensionalキャッシュ不可領域表示                                                   |     |

| (dmac0_result_src_multi_non_cache_area)                                                   |     |

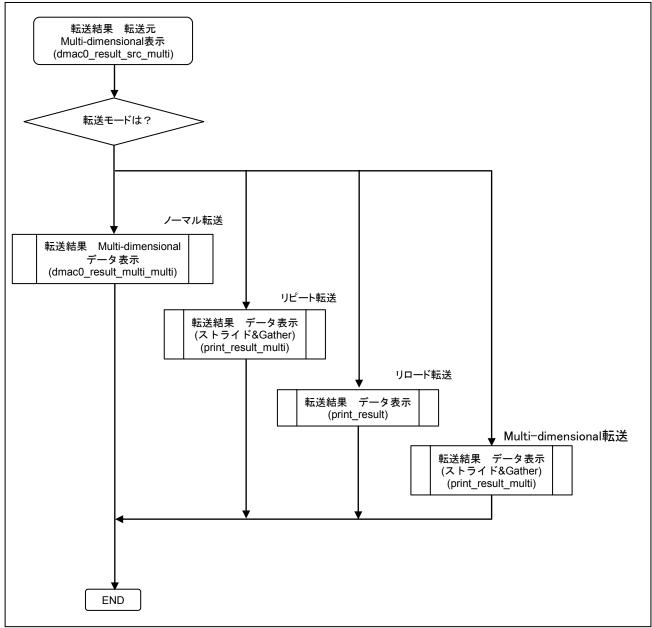

| 5.2.19 転送結果 転送元 Multi-dimensional表示(dmac0_result_src_multi)                               |     |

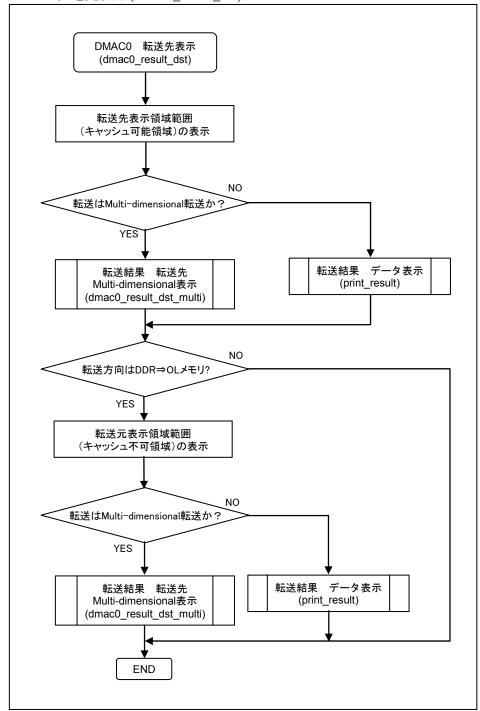

| 5.2.20 DMAC0 転送先表示(dmac0_result_dst)                                                      |     |

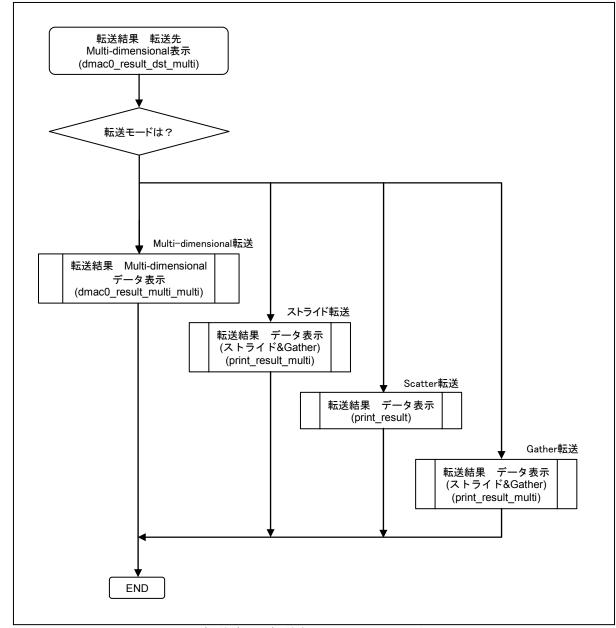

| 5.2.21 転送結果 転送先Multi-dmensional表示(dmac0_result_dst_multi)                                 |     |

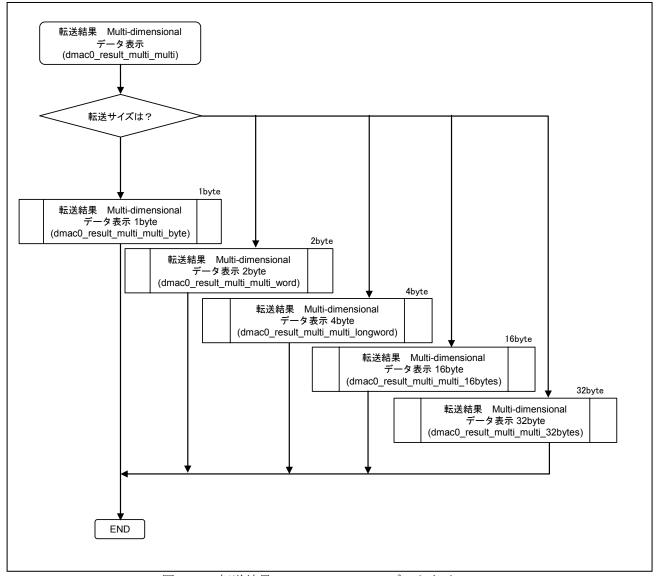

| 5.2.22 転送結果 Multi-dimensionalデータ表示(dmac0_result_multi_multi)                              |     |

| 5.2.23 転送結果 Multi-dimensionalデータ表示nバイト(dmac0_result_multi_multi_n, n=byte, word, lo       |     |

| 16bytes, 32bytes)                                                                         |     |

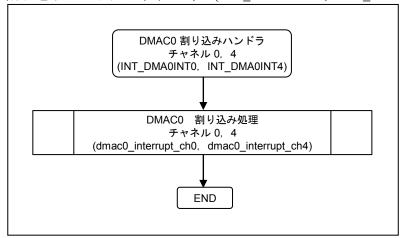

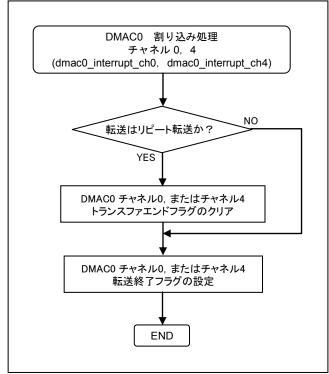

| 5.2.24 DMACO 割り込みハフトラテャネル 0, 4(IN I_DMAOIN 10, IN I_DMAOIN 14)                            |     |

| 5.2.25 DMAC0 割り込み処理デヤイル 0, 4(dmaco_mterrupt_cno, dmaco_mterrupt_cn4)                      |     |

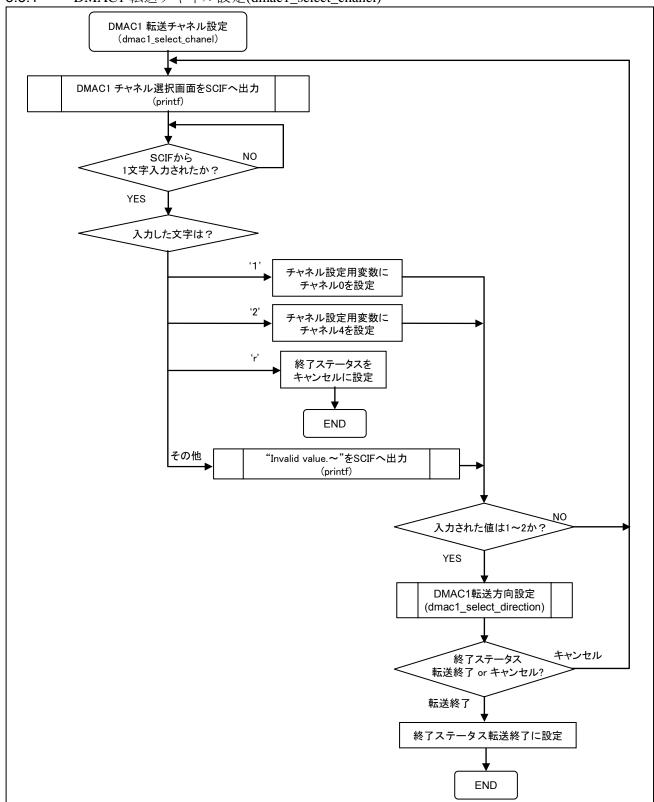

| 5.3.1 DMAC1 転送チャネル設定(dmac1_select_chanel)                                                 |     |

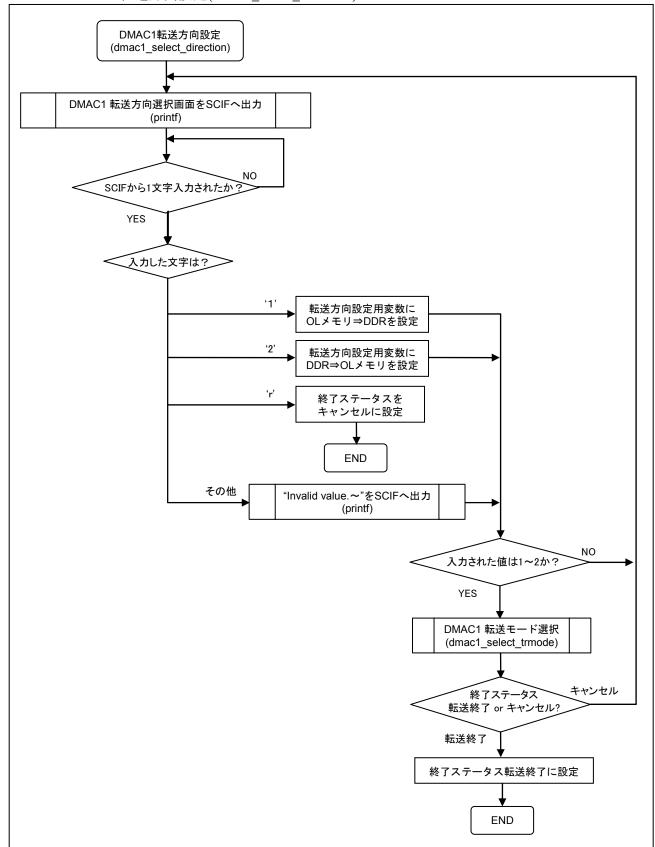

| 5.3.2 DMAC1 転送 ケャイル設定(dmac1_select_challer)                                               |     |

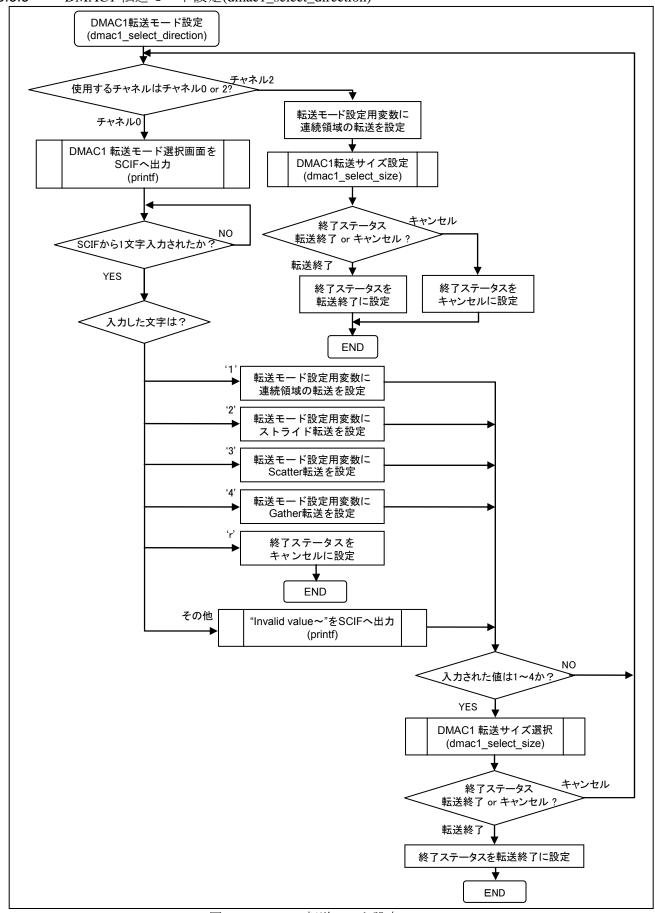

| 5.3.3 DMAC1 転送モード設定(dmac1 select direction)                                               |     |

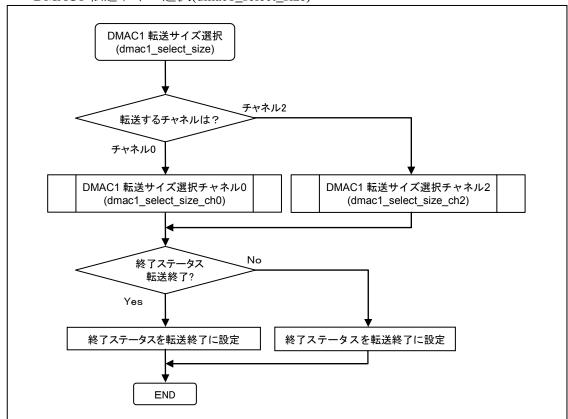

| 5.3.4 DMAC1 転送せイズ選択(dmac1_select_size)                                                    |     |

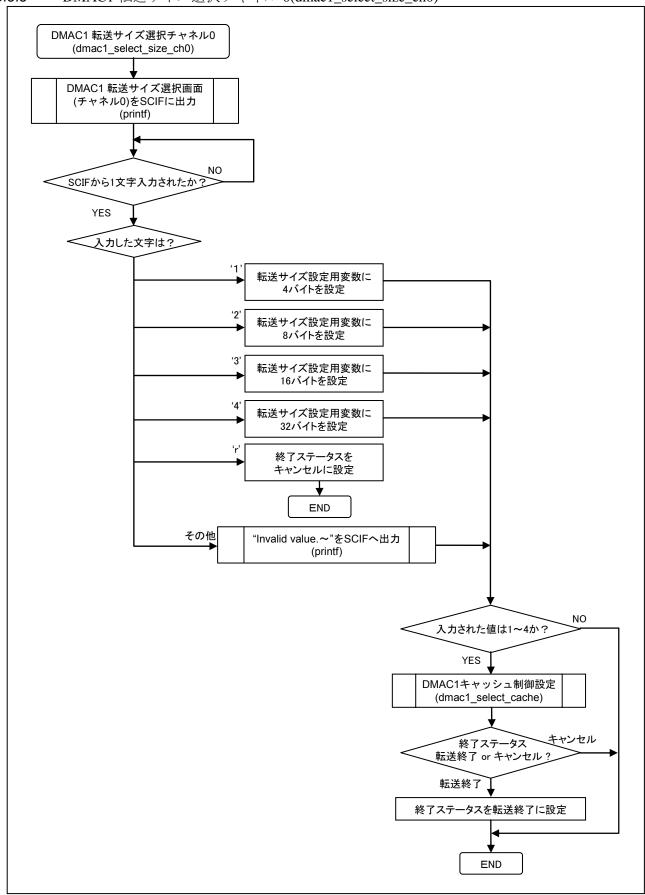

| 5.3.5 DMAC1 転送サイズ選択チャネル 0(dmac1_select_size_ch0)                                          |     |

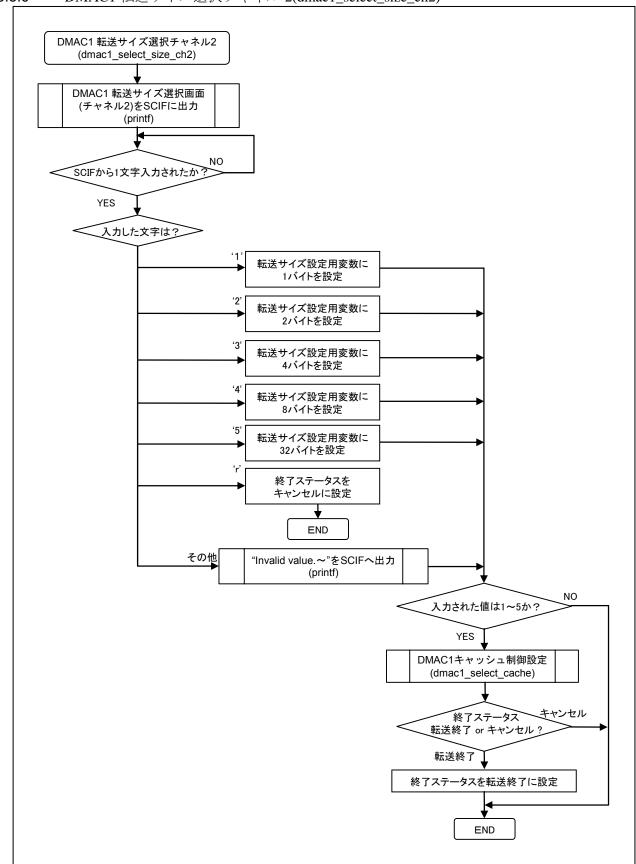

| 5.3.6 DMAC1 転送サイズ選択チャネル 2(dmac1_select_size_ch2)                                          |     |

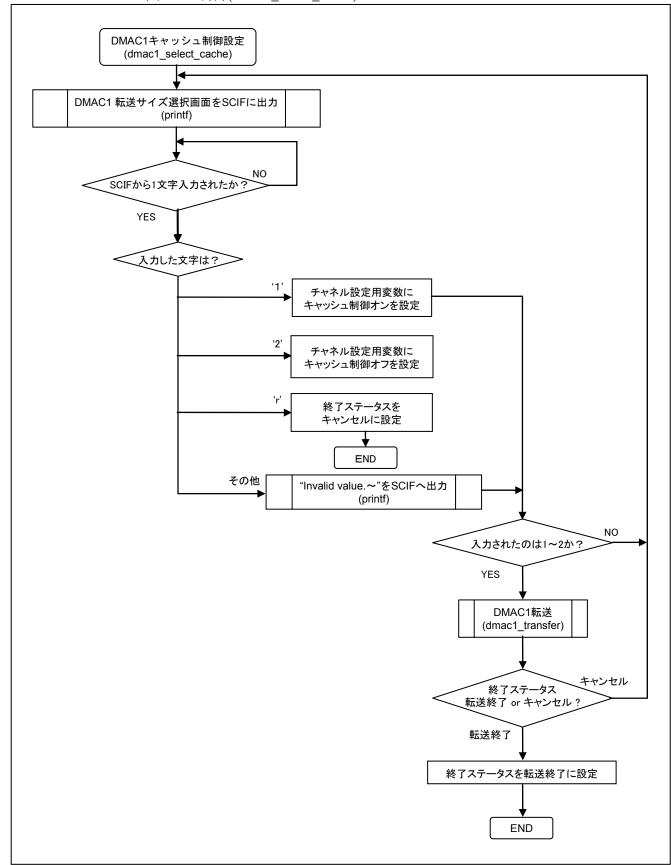

| 5.3.7 DMAC1 キャッシュ制御(dmac1_select_cache)                                                   |     |

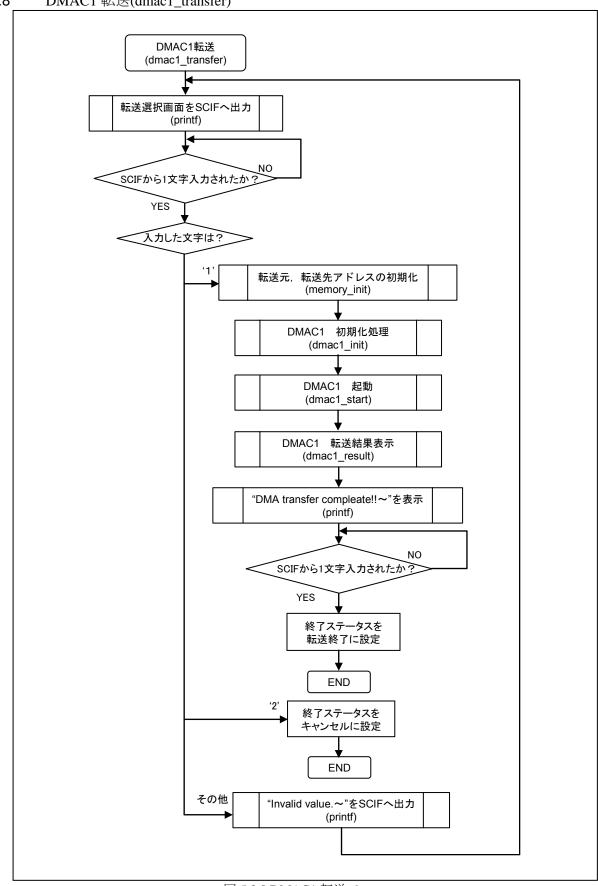

| 5.3.8 DMAC1 転送(dmac1_transfer)                                                            |     |

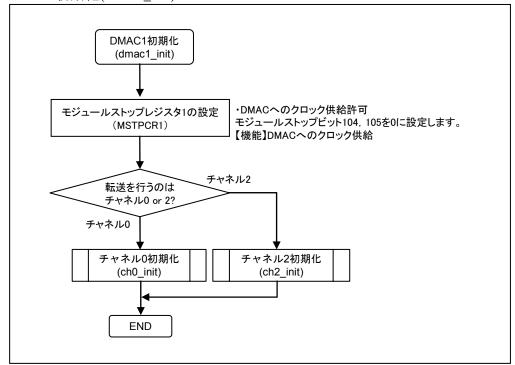

| 5.3.9 DMAC1 初期化(dmac1_init)                                                               |     |

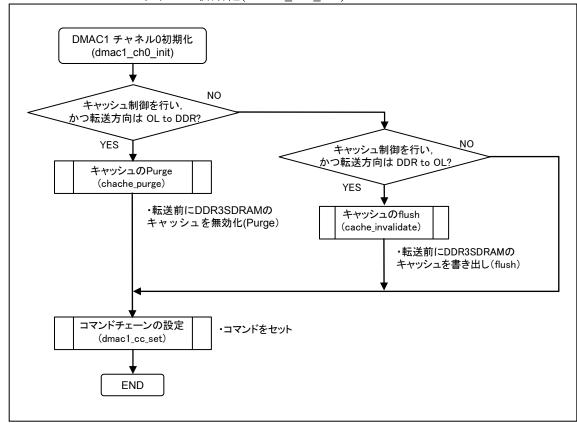

| 5.3.10 DMAC1 チャネル 0 初期化(dmac1_ch0_init)                                                   |     |

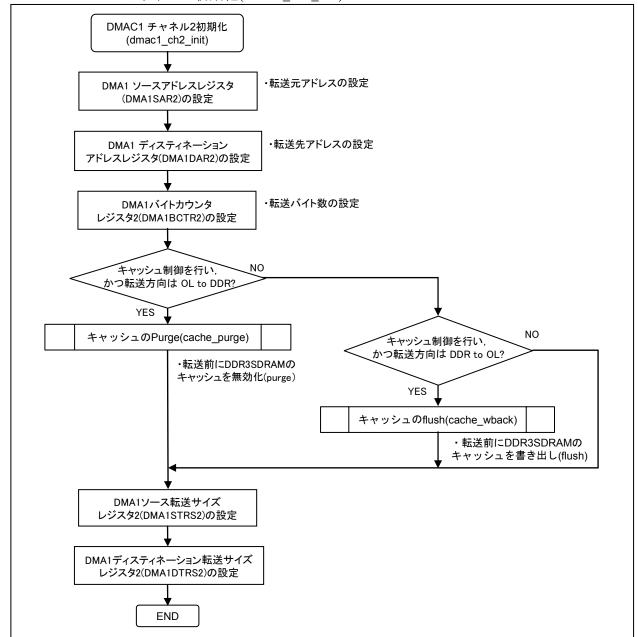

| 5.3.11 DMAC1 チャネル 2 初期化(dmac1_ch2_init)                                                   |     |

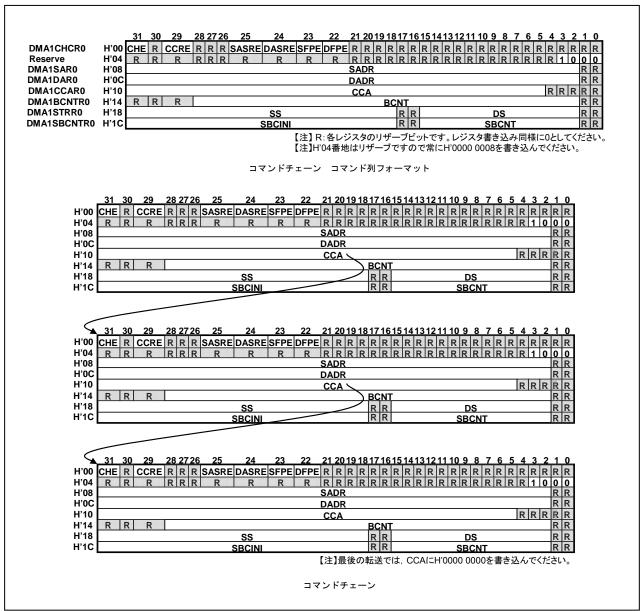

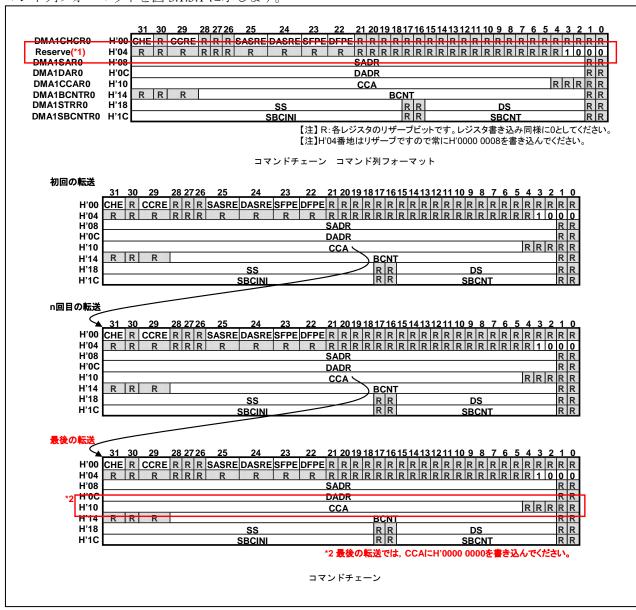

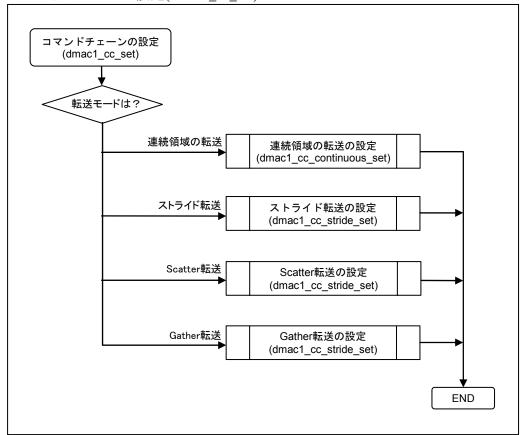

| 5.3.12 コマンドチェーンの設定(dmac1_cc_set)                                                          |     |

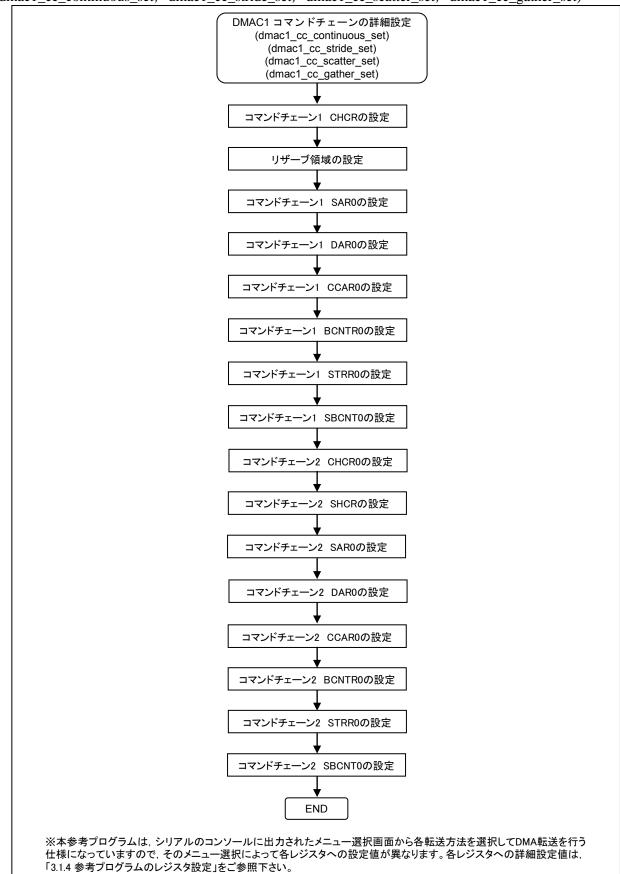

| 5.3.13 DMAC1 コマンドチェーンの詳細設定                                                                |     |

| (dmac1_cc_continuous_set, dmac1_cc_stride_set, dmac1_cc_scatter_set, dmac1_cc_gather_set) |     |

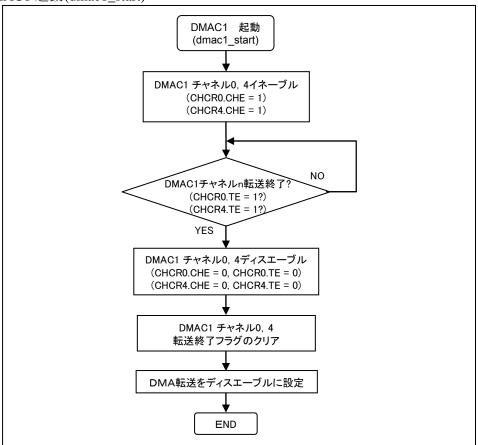

| 5.3.14 DMAC1 起動(dmac1 start)                                                              |     |

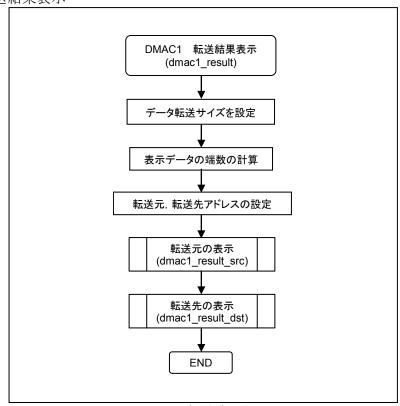

| 5.3.15 DMA転送結果表示                                                                          | 85  |

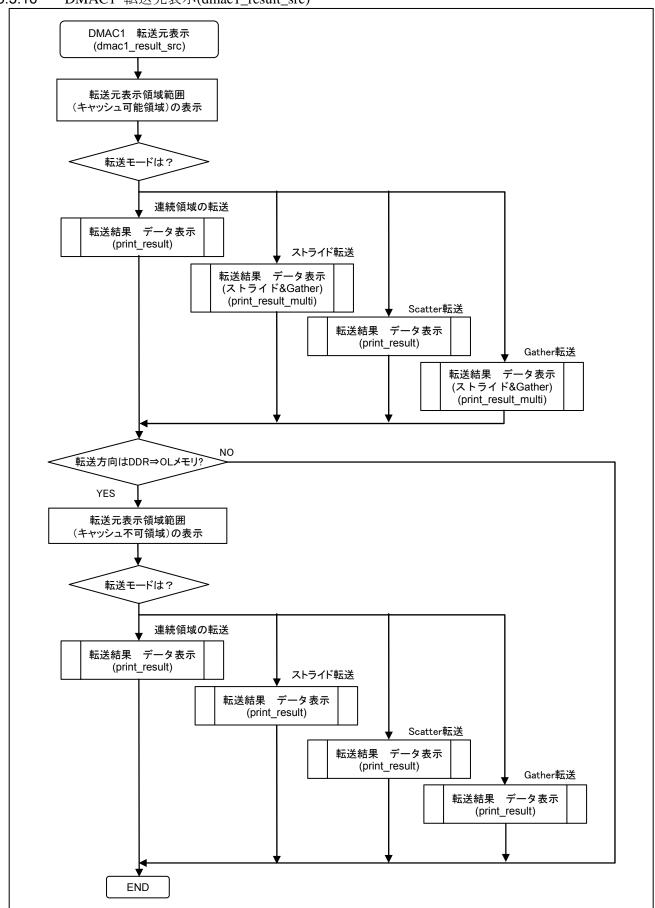

| 5.3.16 DMAC1 転送元表示(dmac1_result_src)                                                      | 86  |

| 5.3.17 DMAC1 転送先表示(dmac1_result_dst)                                                      | 87  |

| 5.4 HPB-DMAC 処理手順                                                                         | 88  |

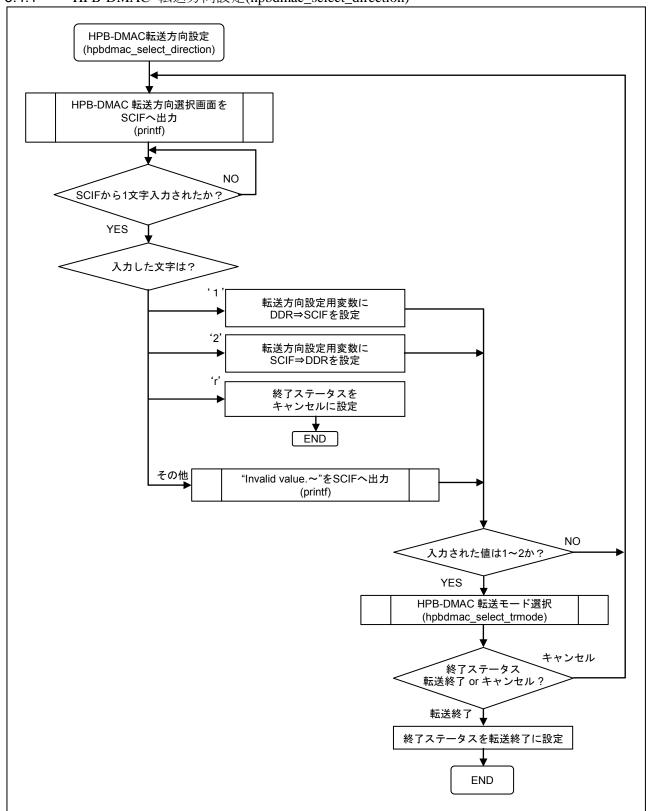

| 5.4.1 HPB-DMAC 転送方向設定(hpbdmac_select_direction)                                           | 88  |

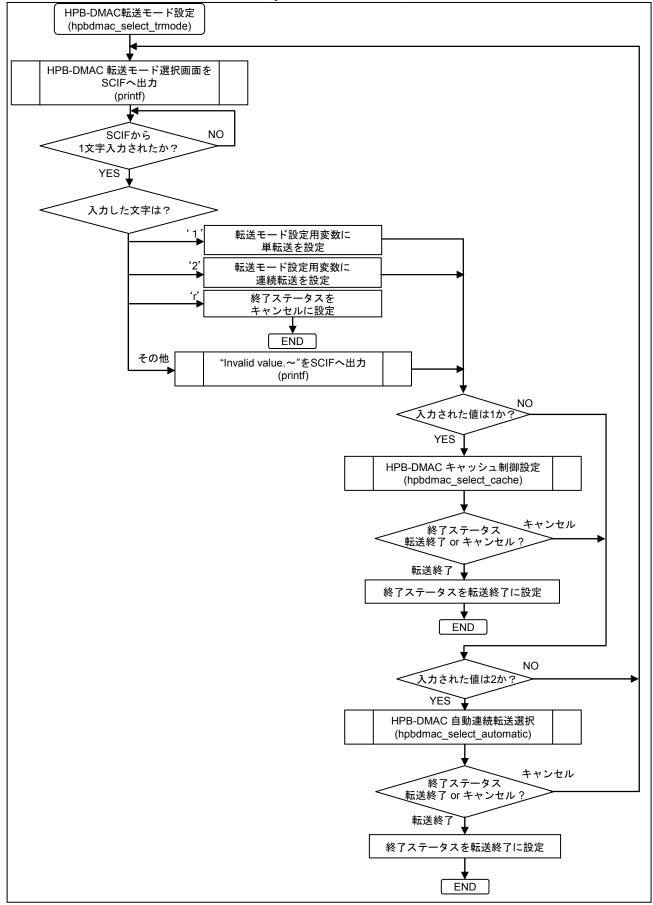

| 5.4.2 HPB-DMAC 転送モード設定(hpbdmac_select_tmode)                                              |     |

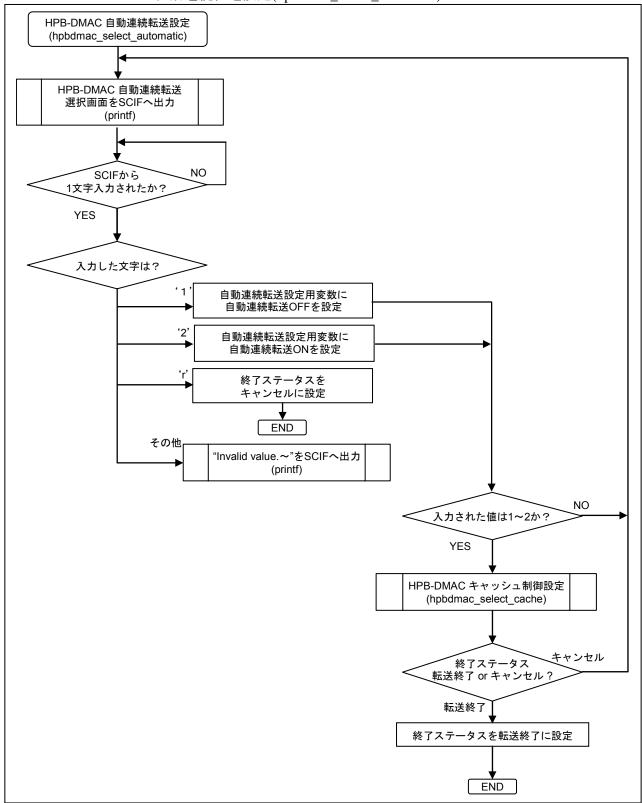

| 5.4.3 HPB-DMAC 自動連続転送設定(hpbdmac_select_automatic)                                         |     |

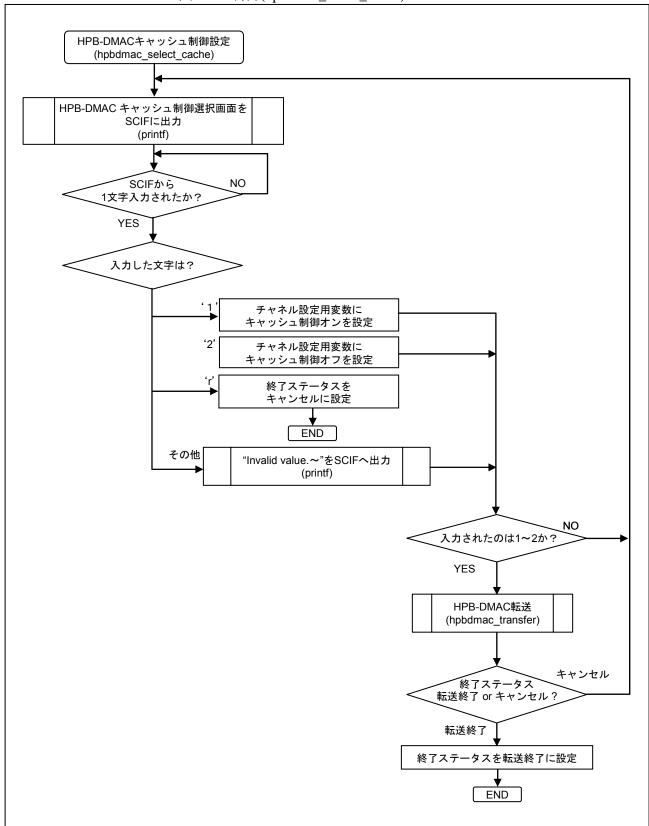

| 5.4.4 HPB-DMAC キャッシュ制御(hpbdmac_select_cache)                                              |     |

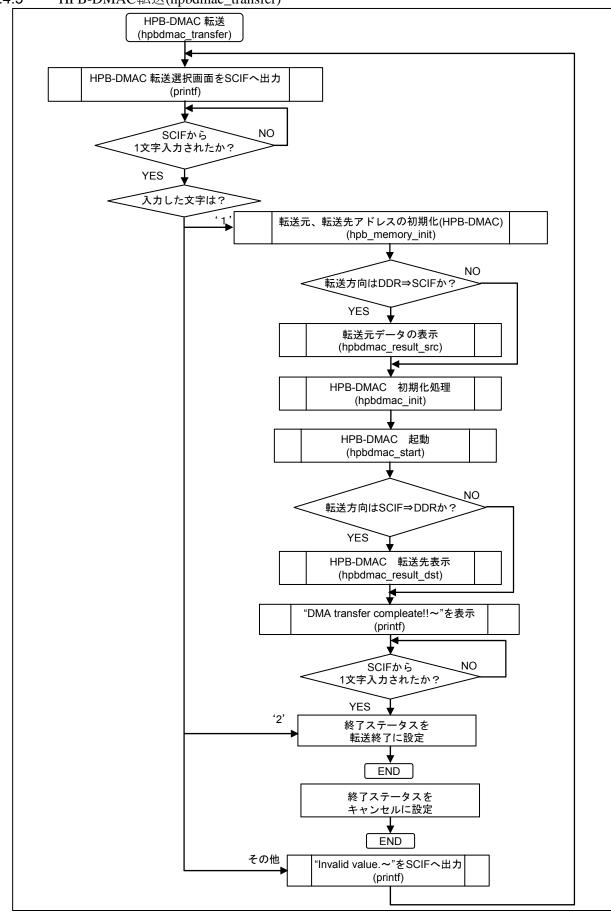

| 5.4.5 HPB-DMAC転送(hpbdmac_transfer)                                                        | 92  |

| 5.4.6 転送元, 転送先アドレスの初期化(HPB-DMAC)(hpb_memory_init)                                         |     |

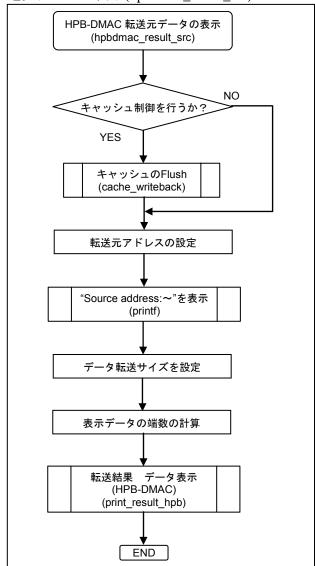

| 5.4.7 HPB-DMAC 転送元データの表示(hpbdmac_result_src)                                              |     |

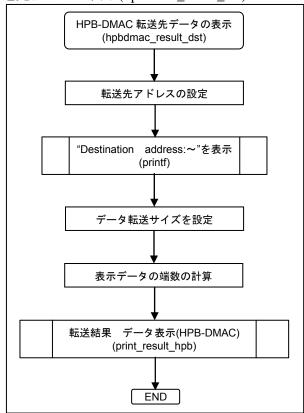

| 5.4.8 HPB-DMAC 転送先データの表示(hpbdmac_result_dst)                                              |     |

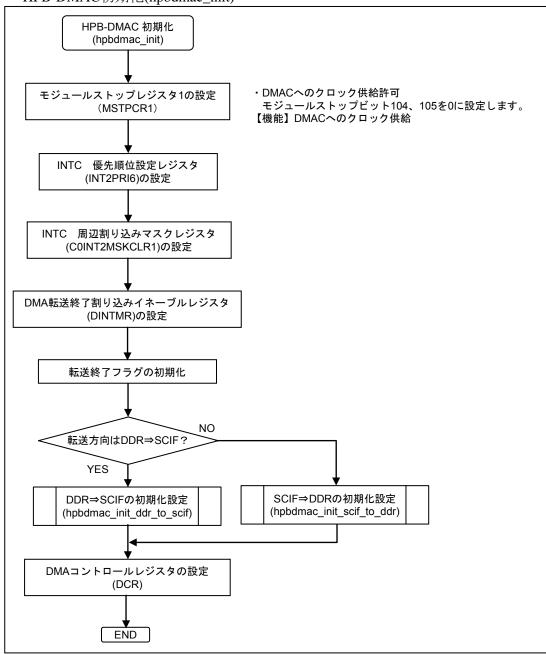

| 5.4.9 HPB-DMAC初期化(hpbdmac_init)                                                           |     |

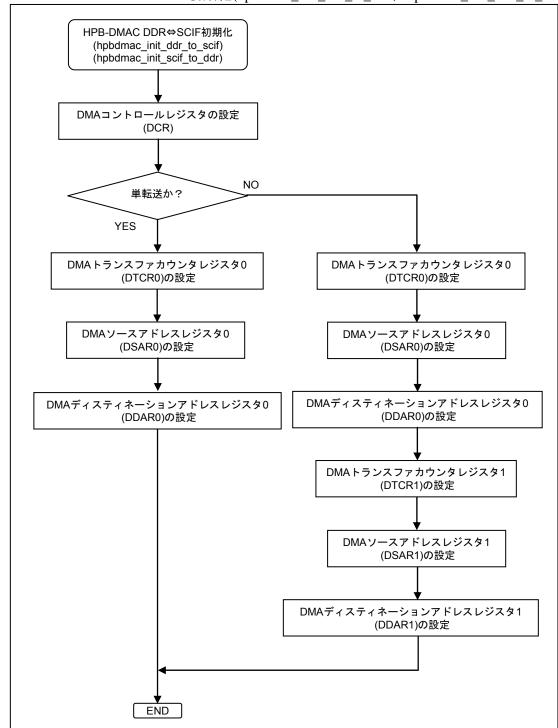

| 5.4.10 HPB-DMAC DDR⇔SCIF初期化(hpbdmac_init_ddr_to_scif, hpbdmac_init_scif_to_ddr)           |     |

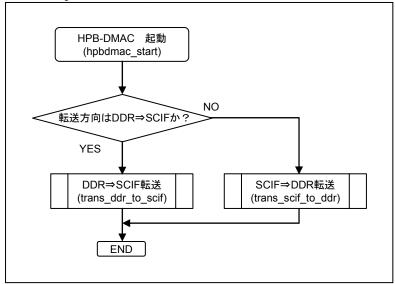

| 5.4.11 HPB-DMAC起動(hpbdmac_start)                                                          |     |

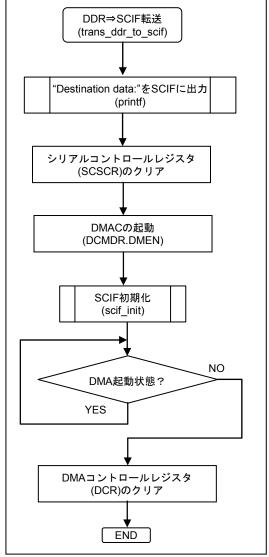

| 5.4.12 DDR→SCIF転送(trans_ddr_to_scif)                                                      |     |

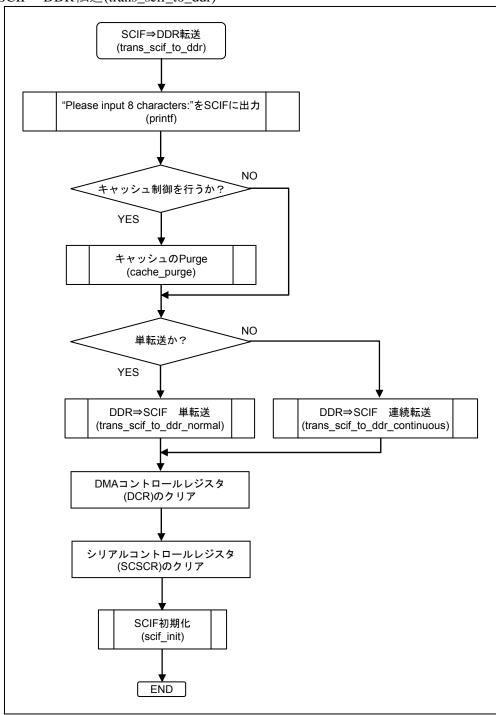

| 5.4.13 SCIF→DDR転送(trans_scif_to_ddr)                                                      |     |

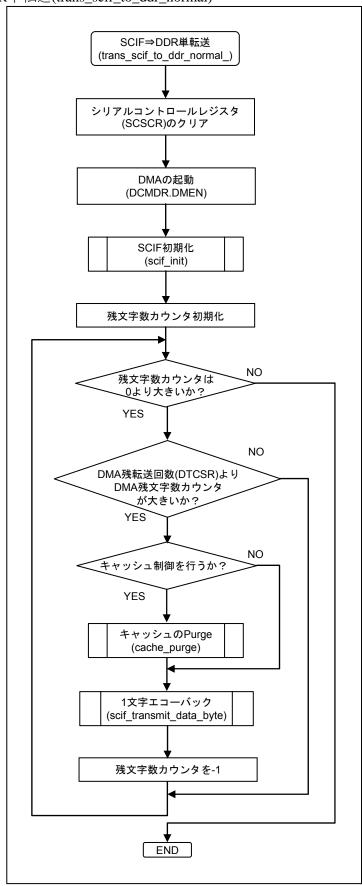

| 5.4.14 SCIF→DDR単転送(trans_scif_to_ddr_normal)                                              |     |

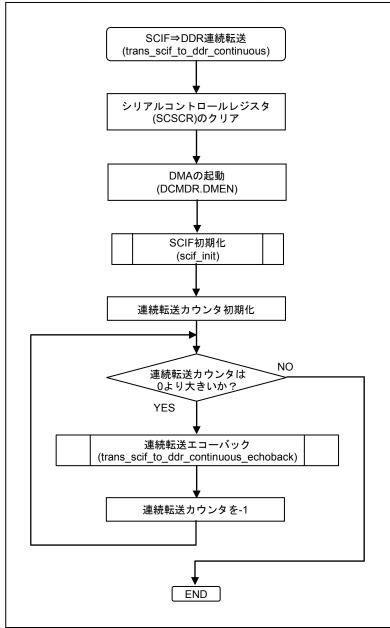

| 5.4.15 SCIF→DDR連続転送(trans_scif_to_ddr_continuous)                                         |     |

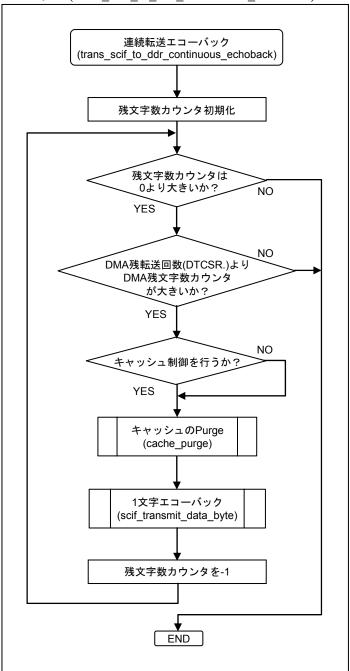

| 5.4.16 連続転送エコーバック(trans_scif_to_ddr_continuous_echoback)                                  |     |

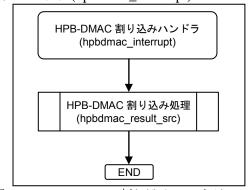

| 5.4.17 HPB-DMAC割り込みハンドラ(hpbdmac_interrupt)                                                |     |

| 5.4.18 HPB-DMAC割り込み処理(hpbdmac_result_src)                                                 |     |

| 5.4.19 割り込み処理連続転送(hpbdmac_result_src)                                                     | 103 |

| ᆼ 송광국의 다시 기계                                                                              | 404 |

| 6. 参考プログラム例                                                                               |     |

| 6.1 サンプルプログラムリスト"sh7786_DMAC_sample.c"                                                    |     |

| 6.2 サンプルプログラムリスト(scif.c)                                                                  |     |

| 6.3 サンプルプログラム"cachecontorol.c"                                                            | 118 |

|     | サンプルプログラムリスト"dmac0.c"    |       |

|-----|--------------------------|-------|

|     | サンプルプログラムリスト"dmac1.c"    |       |

| 6.6 | サンプルプログラムリスト"hpbdmac.c"  | . 190 |

|     |                          |       |

| 7.  | キャッシュと外部メモリのコヒーレンシ制御について | . 214 |

|     |                          |       |

| 8.  | 参考ドキュメント                 | . 215 |

|     |                          |       |

| #-  | - / ページとサポート窓口           | 215   |

# 1. はじめに

# 1.1 仕様

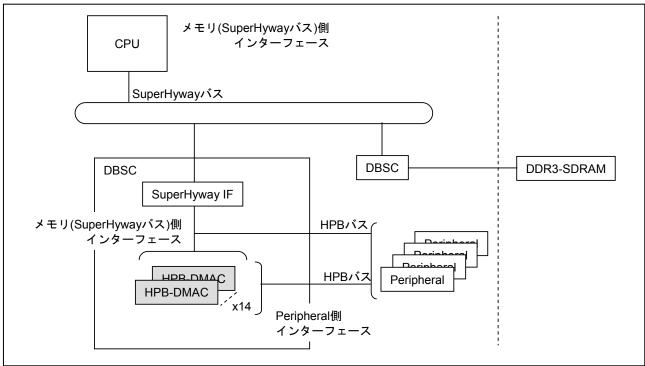

本アプリケーションノートでは、ダイレクトメモリアクセスコントローラ 0/1 (DMAC0/1)の使用方法を内蔵メモリー外部メモリ間のデータ転送を例に、また HPB-DMAC の使用方法を Peripheral モジュール-外部メモリ間のデータ転送を例にして掲載しています。

# 1.2 使用機能

- ダイレクトメモリアクセスコントローラ 0(DMAC0 チャネル 0, チャネル 4)

- ダイレクトメモリアクセスコントローラ 1(DMAC1 チャネル 0, チャネル 2)

- HPB-DMAC

- DDR3-SDRAM インターフェース(DBSC3)

- 内蔵メモリ(OLメモリ)

- FIFO 内蔵シリアルコミュニケーションインターフェース(SCIF チャネル 0)

# 1.3 適用条件

| 評価ボード      | アルファプロジェクト製 AP-AH4AD-0A(注 1)                                                                                                                |  |  |  |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|            | 外付けメモリ (エリア 0):                                                                                                                             |  |  |  |  |  |  |  |

|            | NOR 型 Flash メモリ 16M バイト                                                                                                                     |  |  |  |  |  |  |  |

|            | Spansion 製 S29GL128P90TFIR20                                                                                                                |  |  |  |  |  |  |  |

|            | (エリア 2~5):                                                                                                                                  |  |  |  |  |  |  |  |

|            | DDR3-SDRAM 256M バイト                                                                                                                         |  |  |  |  |  |  |  |

|            | Micron 製 MT41J64M16LA-187E (2 個)                                                                                                            |  |  |  |  |  |  |  |

| マイコン       | SH7786                                                                                                                                      |  |  |  |  |  |  |  |

| 動作周波数      | 内部クロック 533MHz                                                                                                                               |  |  |  |  |  |  |  |

|            | SuperHyway クロック 267MHz                                                                                                                      |  |  |  |  |  |  |  |

|            | 周辺クロック 44MHz                                                                                                                                |  |  |  |  |  |  |  |

|            | DDR3 クロック 533MHz                                                                                                                            |  |  |  |  |  |  |  |

|            | 外部バスクロック 89MHz                                                                                                                              |  |  |  |  |  |  |  |

| エリア 0 バス幅  | 16bit(MD4 端子=Low レベル, MD5 端子=High レベル, MD6 端子=Low レベル)                                                                                      |  |  |  |  |  |  |  |

| クロック動作モード  | クロックモード3                                                                                                                                    |  |  |  |  |  |  |  |

|            | (MD0 端子=High レベル,MD1 端子=High レベル,                                                                                                           |  |  |  |  |  |  |  |

|            | MD2 端子=Low レベル, MD3 端子=Low レベル)                                                                                                             |  |  |  |  |  |  |  |

| エンディアン     | リトルエンディアン(MD8 端子=High レベル)                                                                                                                  |  |  |  |  |  |  |  |

| アドレスモード    | 29 ビットアドレスモード(MD10 端子=Low レベル)                                                                                                              |  |  |  |  |  |  |  |

| ツールチェイン    | Super-H RISC engine Standard Toolchain Ver9.3.2.0                                                                                           |  |  |  |  |  |  |  |

| コンパイルオプション | High-performance Embedded Workshop で include 指定以外はデフォルト設定                                                                                   |  |  |  |  |  |  |  |

|            | -cpu=sh4a -endian=little -include="\$(PROJDIR)\footnote{\text{inc}\footnote{\text{VIV}}", \text{"\$(PROJDIR)\footnote{\text{Yinc}\text{"}}} |  |  |  |  |  |  |  |

|            | -object="\$(CONFIGDIR)\pmu\\$(FILELEAF).obj" -debug -gbr=auto -chgincpath -errorpath                                                        |  |  |  |  |  |  |  |

|            | -global_volatile=0 -opt_range=all -infinite_loop=0 -del_vacant_loop=0 -struct_alloc=1                                                       |  |  |  |  |  |  |  |

|            | -nologo                                                                                                                                     |  |  |  |  |  |  |  |

| アセンブラオプション | cpu=sh4a -endian=little -round=zero -denormalize=off                                                                                        |  |  |  |  |  |  |  |

|            | -include="\$(PROJDIR)\foots   "\$(PROJDIR)\foots   "                                                                                        |  |  |  |  |  |  |  |

|            | -object="\$(CONFIGDIR)\forall \\$(\text{FILELEAF}).obj" -literal=pool, branch, jump, return -nolist                                         |  |  |  |  |  |  |  |

|            | -nologo -chgincpath -errorpath                                                                                                              |  |  |  |  |  |  |  |

(注 1) AP-AH4AD-0A の使用方法等の詳細は、「AP-AH4AD-0A Hardware Manual」を参照してください。

表 1.3 に本参考プログラムのセクション配置を示します。

表 1.3 セクション配置

| セクション名 セクション用途 |                  | 領域  | 配置アドレス     | マ(仮想アドレス)  |

|----------------|------------------|-----|------------|------------|

| INTHandler     | 例外/割込みハンドラ       | ROM | 0x00000800 | P0 領域      |

| VECTTBL        | リセットベクタテーブル      | ROM |            | (キャッシング可   |

| VECTIBL        | 割込みベクタテーブル       |     |            | 能, MMU アドレ |

| INTTBL         | 割込みマスクテーブル       | ROM |            | ス変換不可)     |

| PIntPRG        | 割込み関数            | ROM |            |            |

| PResetPRG      | リセットプログラム        | ROM | 0x00002000 |            |

| Р              | プログラム領域          | ROM | 0x00004000 |            |

| С              | 定数領域             | ROM |            |            |

| C\$BSEC        | 未初期化データ領域用アドレス構造 | ROM |            |            |

| C\$DSEC        | 初期化データ領域用アドレス構造  | ROM |            |            |

| D              | 初期化データ           | ROM |            |            |

| В              | 未初期化データ領域        | RAM | 0x0DF00000 |            |

| R              | 初期化データ領域         | RAM |            |            |

| S              | スタック領域           | RAM | 0x0DFF0000 |            |

|                |                  |     | 0xA0000000 | P2 領域      |

| RSTHandler     | landler リセットハンドラ |     |            | (キャッシング不   |

| Normanulei     |                  | ROM |            | 可, MMUアドレ  |

|                |                  |     |            | ス変換不可)     |

# 1.4 関連アプリケーションノート

本資料の参考プログラムは、「SH7786 グループ アプリケーションノート SH7786 初期設定例 (R01AN0519JJ0101)」の設定条件で動作確認しています。

SCIF調歩同期式初期設定例は,「SH7786 グループ アプリケーションノート SH7786 PCI express コントローラ(PCIEC) 初期化設定例(R01AN557JJ0100)」で使用している SCIFO の設定条件で動作確認しています。 そちらも合わせてご参照ください。

# 2. DMAC0 メモリ間転送例

# 2.1 応用例の説明

DMACO チャネル 0,4 を使用して内蔵 RAM と外部メモリ間(双方向)でデータ転送を行います。内蔵 RAM は OL メモリ,外部メモリは DDR3-SDRAM を使用します。データ転送はサイクルスチールモードで行い,通常モード,インタミッテントモード 16/32 を使用します。また DMA 転送要求として,オートリクエストを使用します。転送方法の選択は、FIFO 内蔵シリアルコミュニケーションインターフェース(SCIF チャネル 0)を使用して、シリアルコンソールからキー入力で選択して行います。

#### 2.1.1 使用機能の動作概要

DMAC0はDMA転送要求があると、決められたチャネルの優先順位にしたがって転送を開始し、転送終了条件が満たされると転送を終了します。転送要求にはオートリクエスト、外部リクエスト、内蔵周辺モジュールリクエストの3種類のモードがあります。バスモードはバーストモードとサイクルスチールモードがあります。サイクルスチールモードは通常モードとインタミッテントモードを選択することができます。

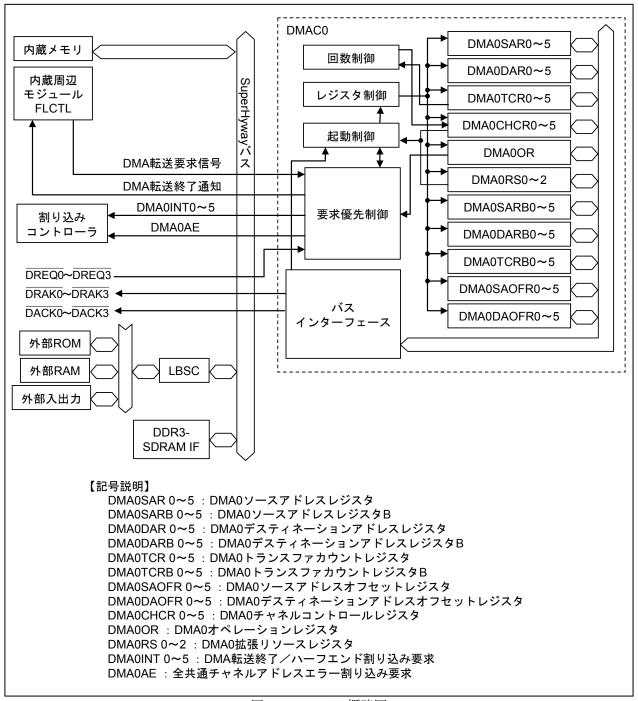

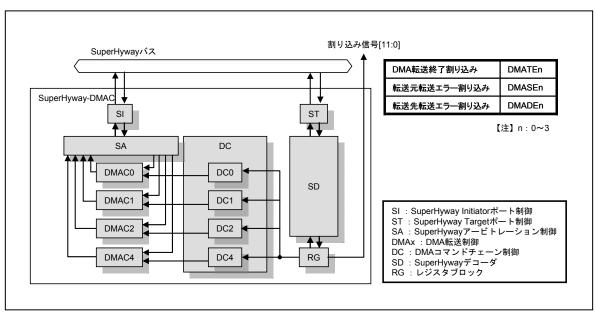

表 2.1.1 に DMAC0 の概要を示します。図 2.1.1 に DMAC0 の概念図を示します。

表 2.1.1 DMAC0 の概要

| 項目 概要  Fャネル数  -6 チャネル(チャネル 0~5)  □チャネル 0~3 は外部リクエストの受け付けが可能  アドレス空間  ・アーキテクチャ上は 4G バイト  転送データ長  - バイト, ワード(2 バイト), ロングワード(4 バイト), 16 バイト, 32 バイト  最大転送回数  - 16,777,216 回  アドレスモード  ・ デュアルアドレスモード  転送要求  - 外部リクエスト(チャネル 0~3), 内蔵周辺モジュールリクエスト, オートリエストの 3 種類から選択可能  - 内蔵周辺モジュールリクエストを発行できるものは FLCTL モジュールのみ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>□ チャネル 0~3 は外部リクエストの受け付けが可能</li> <li>□ アドレス空間 - アーキテクチャ上は 4G バイト</li> <li>転送データ長 - バイト, ワード(2 バイト), ロングワード(4 バイト), 16 バイト, 32 バイト</li> <li>最大転送回数 - 16,777,216 回</li> <li>□ アドレスモード - デュアルアドレスモード</li> <li>転送要求 - 外部リクエスト(チャネル 0~3), 内蔵周辺モジュールリクエスト, オートリエストの 3 種類から選択可能</li> </ul>              |

| アドレス空間- アーキテクチャ上は 4G バイト転送データ長- バイト, ワード(2 バイト), ロングワード(4 バイト), 16 バイト, 32 バイト最大転送回数- 16,777,216 回アドレスモード- デュアルアドレスモード転送要求- 外部リクエスト(チャネル 0~3), 内蔵周辺モジュールリクエスト, オートリエストの 3 種類から選択可能                                                                                                                        |

| 転送データ長- バイト, ワード(2 バイト), ロングワード(4 バイト), 16 バイト, 32 バイト最大転送回数- 16,777,216 回アドレスモード- デュアルアドレスモード転送要求- 外部リクエスト(チャネル 0~3), 内蔵周辺モジュールリクエスト, オートリエストの3種類から選択可能                                                                                                                                                  |

| 最大転送回数 - 16,777,216 回<br>アドレスモード - デュアルアドレスモード<br>転送要求 - 外部リクエスト(チャネル 0~3), 内蔵周辺モジュールリクエスト, オートリエストの 3 種類から選択可能                                                                                                                                                                                           |

| アドレスモード - デュアルアドレスモード 転送要求 - 外部リクエスト(チャネル 0~3), 内蔵周辺モジュールリクエスト, オートリエストの 3 種類から選択可能                                                                                                                                                                                                                       |

| 転送要求 - 外部リクエスト(チャネル 0~3), 内蔵周辺モジュールリクエスト, オートリエストの3種類から選択可能                                                                                                                                                                                                                                               |

| エストの3種類から選択可能                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                           |

| - 内蔵周辺モジュールリクエストを発行できるものは FLCTL モジュールのみ                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                           |

| バスモード - サイクルスチールモード                                                                                                                                                                                                                                                                                       |

| (通常モードとインタミッテントモード 16/32)                                                                                                                                                                                                                                                                                 |

| - バーストモード                                                                                                                                                                                                                                                                                                 |

| (外部リクエストモードで PCMCIA ATA 補完モード有効時のみ設定可能)                                                                                                                                                                                                                                                                   |

| データ転送 - リピートモード                                                                                                                                                                                                                                                                                           |

| - リロードモード                                                                                                                                                                                                                                                                                                 |

| - Multi-dimensional モード                                                                                                                                                                                                                                                                                   |

| ∟Multi-dimensional 転送,scatter 転送,gather 転送,ストライド転送                                                                                                                                                                                                                                                        |

| 優先順位 - チャネル優先順位固定モード                                                                                                                                                                                                                                                                                      |

| - ラウンドロビンモード                                                                                                                                                                                                                                                                                              |

| 割り込み要求 - データ転送ハーフエンド時およびデータ転送終了時、また、アドレスエラー                                                                                                                                                                                                                                                               |

| 発生時に CPU へ割り込み要求を発生可能                                                                                                                                                                                                                                                                                     |

| 外部リクエスト検出 - DREQ 入力のロー/ハイレベル検出,立ち上がり/立ち下がりエッジ検出か                                                                                                                                                                                                                                                          |

| 選択可能                                                                                                                                                                                                                                                                                                      |

| 転送終了通知信号 - DACK は独立にアクティブレベルを設定可能                                                                                                                                                                                                                                                                         |

図 2.1.1 DMAC0 概略図

#### 2.1.2 転送方法

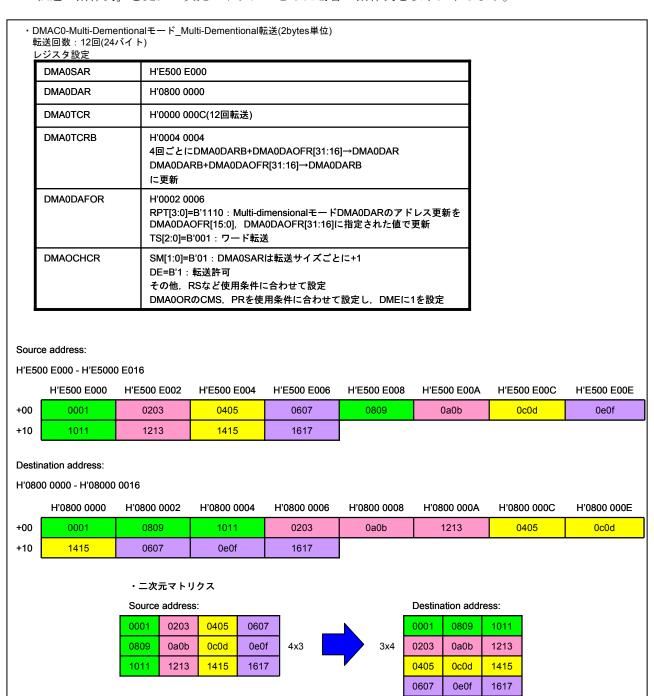

DMAC0 のデータ転送には,通常モード,リピートモード,リロードモード,Multi-dimensional モードがあります。また Multi-dimensional モードには,Multi-dimensional 転送,scatter 転送,gather 転送,ストライド転送があります。以下に各転送の動作と設定例を示します。

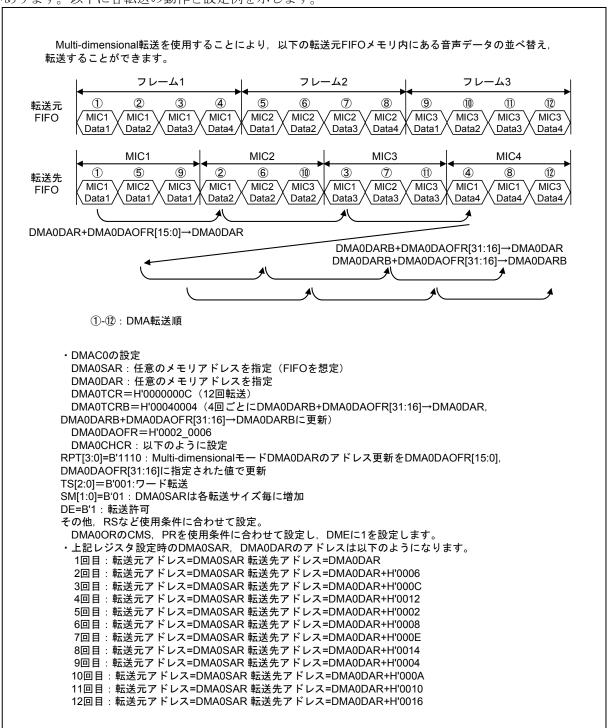

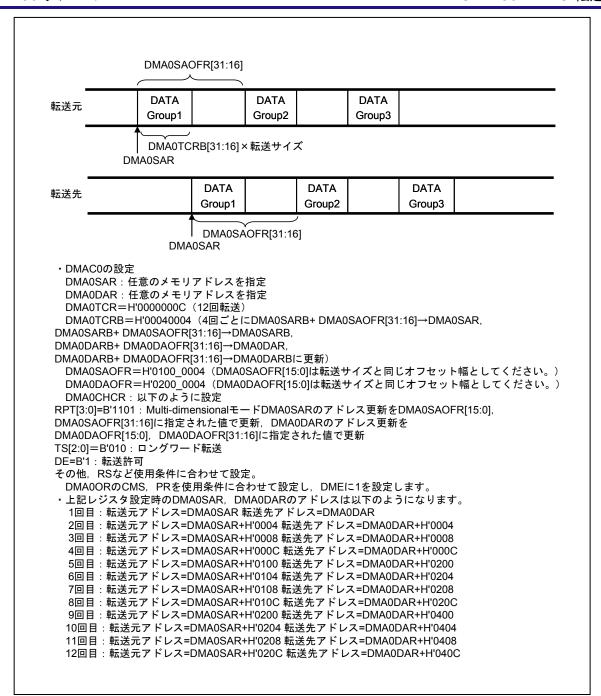

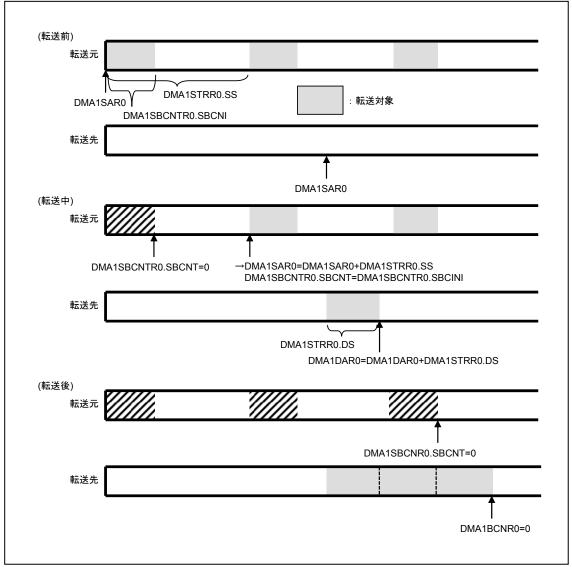

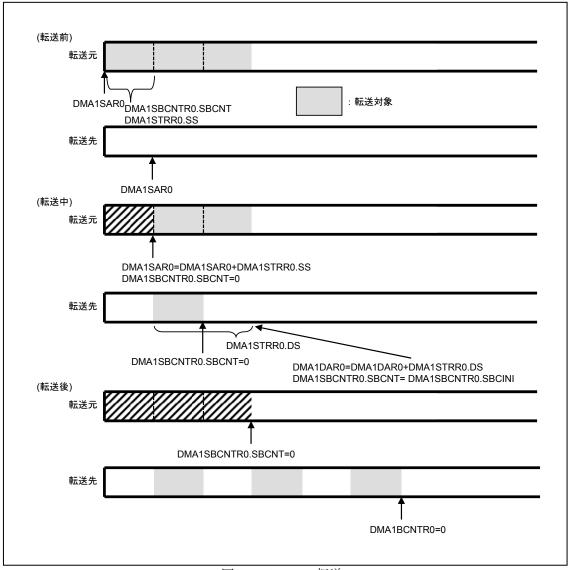

図 2.1.2.1 Multi-dimensional 転送例

**※Multi-dimensional**転送については、「<u>2.1.5.1 Multi dimensionalモード Multi dimensional転送について</u>」をご参照ください。

図 2.1.2.2 Scatter 転送例

図 2.1.2.3 Gather 転送例

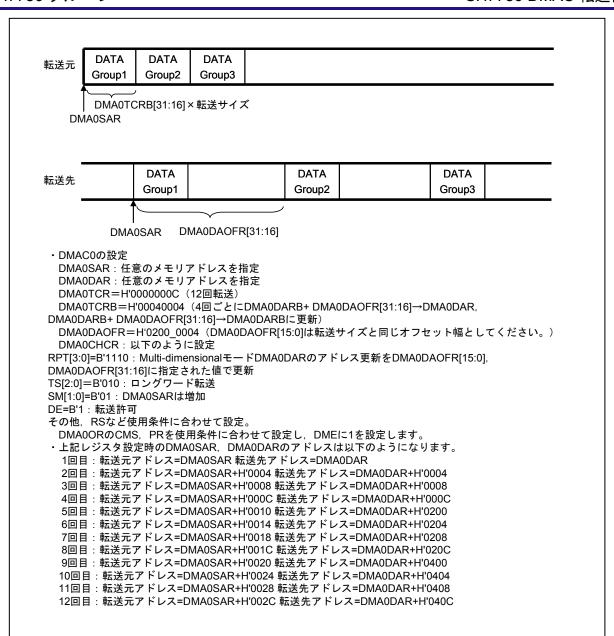

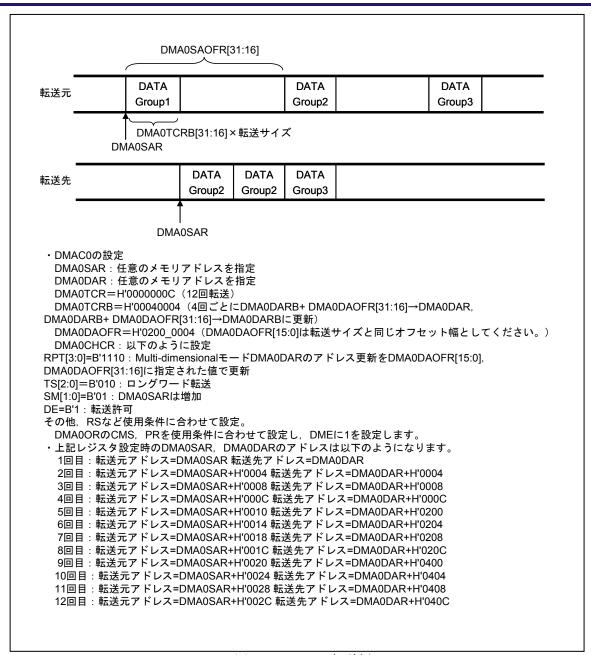

図 2.1.2.4 ストライド転送

# 2.1.3 参考プログラムの説明

参考プログラムではオートリクエストモードによりDMAC0のチャネル0,またはチャネル4を起動し、内蔵RAM-外部メモリ間のデータ転送をサイクルスチールモードで双方向に行います。サイクルスチール転送のため、1データ転送ごとにDMACはバス権をCPUに解放します。

また、DMA転送時にキャッシュと外部メモリのコヒーレンシを保証するためのFlush/Purgeを行うかどうかの選択も可能です。Flush/Purgeはソフトウェアで制御しており、Flush/Purgeをしない場合は、転送元のデータと転送先のデータが不一致となる可能性があります。詳細は、「7.キャッシュと外部メモリのコヒーレンシ制御について」をご参照ください。

表2.1.3 に参考プログラムの仕様を示します。

表 2.1.3 参考プログラムの仕様

| 項目                 | 仕様                                                |

|--------------------|---------------------------------------------------|

| 使用チャネル             | - チャネル 0                                          |

|                    | - チャネル 4                                          |

| メモリ                | - OL メモリ(内蔵メモリ)                                   |

|                    | - DDR3-SDRAM(外部メモリ)                               |

| 転送方向               | - OL メモリ → DDR3-SDRAM                             |

|                    | - DDR3-SDRAM → OL メモリ                             |

| 転送データ量             | - チャネル 0:4 バイト単位                                  |

|                    | - チャネル4:1バイト単位                                    |

| 転送データサイズ           | - チャネル 0: ロングワード(4 バイト), 16 バイト, 32 バイト           |

|                    | - チャネル4:バイト, ワード(2バイト), ロングワード(4バイト), 16バイト,      |

|                    | 32 バイト                                            |

| 転送回数               | - 転送データサイズより算出                                    |

| 転送要求               | - オートリクエスト                                        |

| バスモード              | - サイクルスチールモード                                     |

|                    | □ □通常モード                                          |

|                    | ∟インタミッテントモード 16                                   |

|                    | ∟インタミッテントモード 32                                   |

| データ転送              | - 通常モード(連続転送)                                     |

|                    | - リピートモード                                         |

|                    | - リロードモード                                         |

|                    | - Multi-dimensional モード                           |

|                    | ∟ Multi-dimensional 転送                            |

|                    | 」 scatter 転送<br>□ gather 転送                       |

|                    | □ □ gauner 転送<br>  □ ストライド転送                      |

|                    | - チャネル優先順位固定モード                                   |

| 割り込み要求             | - 「「「「「」」」」 - 転送終了時、またはアドレスエラー発生時に CPU へ割り込み要求を発生 |

| キャッシュと外部メ          | - コピーバックモード                                       |

| モリのコヒーレンシ          | - コピーハックピート<br>  - オペランドキャッシュ,2次キャッシュを有効          |

| しりのコピーレフラー<br>  制御 | - キャッシュの Flush/Purge をソフトウェアによって制御                |

| -1- 3 leaf.        | (メニューから ON(制御する)/OFF(制御しない)を選択)                   |

|                    | * コピーバックモードでは、キャッシュのコヒーレンシ制御を行わない場合、オ             |

|                    | ペランドキャッシュと外部メモリの内容が一致しない場合があります。詳細は、              |

|                    | 「7 キャッシュと外部メモリのコヒーレンシ制御について」をご参照ください。             |

# 2.1.4 参考プログラムのレジスタ設定

以下に本参考プログラムで使用するレジスタの機能を以下に示します。

表 2.1.4.1 DMAC0 レジスタ設定値(チャネル共通)

| レジスタ名称(呼称)       | アドレス         | R/W | サイズ | 設定値    | 動作仕様                                                                                               |                                                                                   |  |  |  |  |  |

|------------------|--------------|-----|-----|--------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|--|

|                  | H'FE80 8060  | R/W | 16  | H'0001 | <ul><li>・サイクルスチールモードセレクト<br/>ー初期化時<br/>CMS = B'00:通常モード<br/>DMA1E = B'1:全チャネルの DMA 転送を許可</li></ul> |                                                                                   |  |  |  |  |  |

|                  |              |     |     | H'2001 | ・サイクルスチールモードセレクト<br>CMS = B'10 : インタミッテントモード 16<br>DMA1E = B'1 : 全チャネルの DMA 転送を許可                  |                                                                                   |  |  |  |  |  |

| DMA1 オペレーションレジスタ |              |     |     | 16     | H'3001                                                                                             | ・サイクルスチールモードセレクト<br>CMS = B'11 : インタミッテントモード 64<br>DMA1E = B'1 : 全チャネルの DMA 転送を許可 |  |  |  |  |  |

| (DMA1OR)         | 111 250 5550 |     |     |        |                                                                                                    |                                                                                   |  |  |  |  |  |

|                  |              |     |     | H'2000 | ・サイクルスチールモードセレクト<br>CMS = B'10 : インタミッテントモード 16<br>DMA1E = B'0 : 全チャネルの DMA 転送を禁止                  |                                                                                   |  |  |  |  |  |

|                  |              |     |     | H'3000 | ・サイクルスチールモードセレクト<br>CMS = B'11 : インタミッテントモード 64<br>DMA1E = B'0 : 全チャネルの DMA 転送を禁止                  |                                                                                   |  |  |  |  |  |

※本プログラムで使用していないレジスタや設定をしていないビットは初期値のままです。

表 2.1.4.2 DMAC0 レジスタ設定値 1(チャネル 0)

| レジスタ名称(呼称)                | アドレス        | R/W   | サイズ | 設定値 1(ナヤ 設定値 | 動作仕様                                                           |                                                                |             |                                                       |                                                                                                                  |                         |                                                                                            |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---------------------------|-------------|-------|-----|--------------|----------------------------------------------------------------|----------------------------------------------------------------|-------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------|----|-------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----|-------------|------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| レジスタ名称(呼称)                | , r D X     | IT/VV | 91. | <b>政</b> 上但  |                                                                |                                                                |             |                                                       |                                                                                                                  |                         |                                                                                            |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| DMA0 ソースアドレスレジスタ 0        | LUEE22 2222 | R/W   | 32  | 22           | H'1400 E000                                                    | ・転送元の開始アドレスを指定<br>OL メモリを指定した場合<br>(DMA0DAR0 は DDR3-SDRAM を指定) |             |                                                       |                                                                                                                  |                         |                                                                                            |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| (DMA0SAR0)                | H'FE80 8020 |       |     | H'0800 0000  | ・転送元の開始アドレスを指定<br>DDR3-SDRAM を指定した場合<br>(DMA0DAR0 は OL メモリを指定) |                                                                |             |                                                       |                                                                                                                  |                         |                                                                                            |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| DMAO ディスティネーション           |             |       |     | H'1400 E000  | ・転送先の開始アドレスを指定<br>OL メモリを指定した場合<br>(DMA0SAR0 は DDR3-SDRAM を指定) |                                                                |             |                                                       |                                                                                                                  |                         |                                                                                            |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| アドレスレジスタ 0<br>(DMA0DAR0)  | H'FE80 8024 | R/W   | 32  | H'0800 0000  | ・転送先の開始アドレスを指定<br>DDR3-SDRAM を指定した場合<br>(DMA0SAR0 は OL メモリを指定) |                                                                |             |                                                       |                                                                                                                  |                         |                                                                                            |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                           |             |       |     | H'0000 0064  | ・転送回数の設定<br>100回(転送サイズ1バイト時)<br>※通常、リロード、ストライドモード転送時           |                                                                |             |                                                       |                                                                                                                  |                         |                                                                                            |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                           |             |       |     | H'0000 0032  | ・転送回数の設定<br>50回(転送サイズ 2 バイト時)<br>※通常、リロード、ストライドモード転送時          |                                                                |             |                                                       |                                                                                                                  |                         |                                                                                            |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                           | H'FE80 8028 |       |     | 32           | 32                                                             | 32                                                             | H'0000 0020 | ・転送回数の設定<br>32回(転送サイズ 4 バイト時)<br>※通常,リロード,ストライドモード転送時 |                                                                                                                  |                         |                                                                                            |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                           |             | R/W   |     |              |                                                                |                                                                | 32          | H'0000 0008                                           | ・転送回数の設定<br>8回(転送サイズ 16 バイト時)<br>※通常,リロード,ストライドモード転送時                                                            |                         |                                                                                            |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                           |             |       | 32  |              |                                                                |                                                                |             | 32                                                    | 32                                                                                                               | 32                      | 32                                                                                         | 32 | H'0000 0004 | ・転送回数の設定<br>4回(転送サイズ 32 バイト時)<br>※通常, リロード, ストライドモード転送時 |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| DMA0 トランスファカウント<br>レジスタ 0 |             |       |     |              |                                                                |                                                                |             |                                                       |                                                                                                                  |                         |                                                                                            |    | 32          | 32                                                      | 32                                                                                                          | 32 | 32          | 32                                                                                                               | 32 | 32 | 32 | 32 | 32 | 32 | 32 | 32 | 32 | 32 | 32 | 32 | 32 | 32 | 32 |

| (DMA0TCR0)                |             |       |     |              |                                                                |                                                                |             |                                                       |                                                                                                                  |                         |                                                                                            |    |             | H'0000 0016                                             | ・転送回数の設定<br>32回(転送サイズ2バイト時)<br>※リピートモード、Scatter、Gather 転送時<br>(Scatter、Gather 転送は Multi-dimensional<br>モード) |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                           |             |       |     |              |                                                                |                                                                |             |                                                       |                                                                                                                  | H'0000 0010   ※リピートモード, | 16 回(転送サイズ 4 バイト時)<br>※リピートモード,Scatter,Gather 転送時<br>(Scatter,Gather 転送は Multi-dimensional |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                           |             |       |     |              |                                                                |                                                                |             | H'0000 0004                                           | ・転送回数の設定<br>4回(転送サイズ 16 バイト時)<br>※リピートモード, Scatter, Gather 転送時<br>(Scatter, Gather 転送は Multi-dimensional<br>モード) |                         |                                                                                            |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                           |             |       |     |              |                                                                |                                                                |             |                                                       |                                                                                                                  |                         |                                                                                            |    |             |                                                         |                                                                                                             |    | H'0000 0002 | ・転送回数の設定<br>2回(転送サイズ 32 バイト時)<br>※リピートモード, Scatter, Gather 転送時<br>(Scatter, Gather 転送は Multi-dimensional<br>モード) |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                           |             |       |     |              | H'0000 000C                                                    | ・転送回数の設定<br>12 回(全転送サイズ)<br>Multi-dimensional 転送時              |             |                                                       |                                                                                                                  |                         |                                                                                            |    |             |                                                         |                                                                                                             |    |             |                                                                                                                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

表 2.1.4.3 DMAC0 レジスタ設定値 2(チャネル 0)

|                                             | 衣 2.1.4.3 DN   | IACU | レンハク | 設定値 2(チャ <sup>)</sup> | · /                                                                                                  |                                                                                                     |                                 |

|---------------------------------------------|----------------|------|------|-----------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------|

| レジスタ名称(呼称)                                  | アドレス           | R/W  | サイズ  | 設定値                   | 動作仕様                                                                                                 |                                                                                                     |                                 |

| DMA0 ソースアドレス<br>レジスタ B0                     | H'FE80 8120    | R/W  | 32   | H'1400 E032           | ・DMA0DAR0 に再設定するアドレス<br>OL メモリの場合<br>リピートモードで転送サイズが 1~2<br>バイト時                                      |                                                                                                     |                                 |

| (DMA0SARB0)                                 | = 50 5 . = 5   |      |      | H'1400 E040           | ・DMA0DAR0 に再設定するアドレス<br>OL メモリの場合<br>リピートモードで転送サイズが 4~32<br>バイト時                                     |                                                                                                     |                                 |

| DMA0 ディスティネーション<br>アドレスレジスタ B0              | H'FE80 8124    | R/W  | 32   | H'0800 0032           | ・DMA0DAR0 に再設定するアドレス<br>DDR3-SDRAM の場合<br>リピートモードで転送サイズが 1~2<br>バイト時                                 |                                                                                                     |                                 |

| (DMA0DARB0)                                 | = 55 5 1 = 1   |      | 02   | H'0800 0040           | DMA0DAR0 に再設定するアドレス・<br>DDR3-SDRAM の場合<br>リピートモードで転送サイズが 4~32<br>バイト時                                |                                                                                                     |                                 |

|                                             |                | R/W  |      | H'0001 0001           | ・リロードモード, Scatter, Gather 転送<br>bit[31:16]: bit[15:0]にリロードする転送<br>回数を指定<br>bit[15:0]: 転送回数カウンタ       |                                                                                                     |                                 |

| DMA0 トランスファカウント<br>レジスタ B0<br>(DMA0TCRB0)   | H'FE80 8128    |      | R/W  | 32                    | 32                                                                                                   | 日 0002 0002   回数を指定                                                                                 | bit[31:16] : bit[15:0]にリロードする転送 |

|                                             |                |      |      | H'0004 0004           | ・Multi-dimensional 転送<br>bit[31:16]: bit[15:0]にリロードする転送<br>回数を指定<br>bit[15:0]: 転送回数カウンタ              |                                                                                                     |                                 |

|                                             | H'FE80 8220 R/ | R/W  | 32   | H'0002 0002           | ・ストライド,Gather 転送(転送サイズ:<br>1 バイト)<br>bit[31:16]: リロードするアドレスオフセットを設定<br>bit[15:0]: 1 転送毎にアドレス増加分を設定   |                                                                                                     |                                 |

|                                             |                |      |      | H'0004 0004           | ・ストライド, Gather 転送(転送サイズ:<br>2 バイト)<br>bit[31:16]: リロードするアドレスオフセットを設定<br>bit[15:0]: 1 転送毎にアドレス増加分を設定  |                                                                                                     |                                 |

| DMA0 ソースアドレス<br>オフセットレジスタ 0<br>(DMA0SAOFR0) |                |      |      | 32                    | H'0004 0004                                                                                          | ・ストライド, Gather 転送(転送サイズ:<br>4 バイト)<br>bit[31:16]: リロードするアドレスオフセットを設定<br>bit[15:0]: 1 転送毎にアドレス増加分を設定 |                                 |

|                                             |                |      |      | H'0020 0020           | ・ストライド, Gather 転送(転送サイズ:<br>16 バイト)<br>bit[31:16]: リロードするアドレスオフセットを設定<br>bit[15:0]: 1 転送毎にアドレス増加分を設定 |                                                                                                     |                                 |

|                                             |                |      |      |                       |                                                                                                      |                                                                                                     | H'0040 0040                     |

表 2.1.4.4 DMAC0 レジスタ設定値 3 (チャネル 0)

| レジスタ名称(呼称)                      | アドレス               | R/W             | サイズ           | 設定値         | 動作仕様                                                                                                  |                                                                                                       |                                                                                                           |                                                                                                                    |                                                                                                        |  |             |                                                                                                      |  |  |  |  |

|---------------------------------|--------------------|-----------------|---------------|-------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|-------------|------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                 |                    |                 |               |             |                                                                                                       | H'0002 0002                                                                                           | ・ストライド, Scatter 転送(転送サイズ:<br>1 バイト)<br>bit[31:16]: リロードするアドレスオフセットを設定<br>bit[15:0]: 1 転送毎にアドレス増加分を設定      |                                                                                                                    |                                                                                                        |  |             |                                                                                                      |  |  |  |  |

|                                 |                    |                 |               | H'0004 0004 | ・ストライド, Scatter 転送(転送サイズ:<br>2 バイト)<br>bit[31:16]: リロードするアドレスオフセットを設定<br>bit[15:0]: 1 転送毎にアドレス増加分を設定  |                                                                                                       |                                                                                                           |                                                                                                                    |                                                                                                        |  |             |                                                                                                      |  |  |  |  |

|                                 |                    |                 |               |             |                                                                                                       |                                                                                                       |                                                                                                           |                                                                                                                    |                                                                                                        |  | H'0004 0004 | ・ストライド, Scatter 転送(転送サイズ:<br>4 バイト)<br>bit[31:16]: リロードするアドレスオフセットを設定<br>bit[15:0]: 1 転送毎にアドレス増加分を設定 |  |  |  |  |

|                                 |                    | H'FE80 8224 R/W |               | H'0020 0020 | ・ストライド, Scatter 転送(転送サイズ:<br>16 バイト)<br>bit[31:16]: リロードするアドレスオフセットを設定<br>bit[15:0]: 1 転送毎にアドレス増加分を設定 |                                                                                                       |                                                                                                           |                                                                                                                    |                                                                                                        |  |             |                                                                                                      |  |  |  |  |

| DMA0 ディスティネーション                 | H'FE80 8224 R/W 32 |                 |               | 32          | H'0040 0040                                                                                           | ・ストライド, Scatter 転送(転送サイズ:<br>32 バイト)<br>bit[31:16]: リロードするアドレスオフセットを設定<br>bit[15:0]: 1 転送毎にアドレス増加分を設定 |                                                                                                           |                                                                                                                    |                                                                                                        |  |             |                                                                                                      |  |  |  |  |

| アドレスオフセットレジスタ 0<br>(DMA0DAOFR0) |                    |                 | 0 8224 R/W 32 |             | R/W 32 -                                                                                              | H'0001 0003                                                                                           | Multi-dimensional 転送(転送サイズ:     1 バイト)     bit[31:16]: リロードするアドレスオフセットを設定     bit[15:0]: 1 転送毎にアドレス増加分を設定 |                                                                                                                    |                                                                                                        |  |             |                                                                                                      |  |  |  |  |

|                                 |                    |                 |               |             |                                                                                                       | H'0002 0006                                                                                           | Multi-dimensional 転送(転送サイズ: 2<br>バイト)<br>bit[31:16]: リロードするアドレスオフセットを設定<br>bit[15:0]: 1 転送毎にアドレス増加分を設定    |                                                                                                                    |                                                                                                        |  |             |                                                                                                      |  |  |  |  |

|                                 |                    |                 |               |             |                                                                                                       |                                                                                                       |                                                                                                           | H'0004 0010                                                                                                        | Multi-dimensional 転送(転送サイズ: 4<br>バイト)<br>bit[31:16]: リロードするアドレスオフセットを設定<br>bit[15:0]: 1 転送毎にアドレス増加分を設定 |  |             |                                                                                                      |  |  |  |  |

|                                 |                    |                 |               |             |                                                                                                       |                                                                                                       | H'0010 0030                                                                                               | Multi-dimensional 転送(転送サイズ:     16 バイト)     bit[31:16]: リロードするアドレスオフセットを設定     bit[15:0]: 1 転送毎にアドレス増加分を設定     を設定 |                                                                                                        |  |             |                                                                                                      |  |  |  |  |

|                                 |                    |                 |               |             |                                                                                                       |                                                                                                       |                                                                                                           |                                                                                                                    |                                                                                                        |  |             |                                                                                                      |  |  |  |  |

表 2.1.4.5 DMAC0 チャネルコントロールレジスタ 0 設定値 1(チャネル 0)

| 1 × 2 b D Ib (10T Ib) |             | 動作仕様                   |      |                                                 |          |  |

|-----------------------|-------------|------------------------|------|-------------------------------------------------|----------|--|

| レジスタ名称(呼称)<br>        | アドレス        | ビット名                   | 設定値  | 内容                                              |          |  |

|                       |             |                        | H'0  | ・通常モード                                          |          |  |

|                       |             |                        | H'3  | ・リピートモード                                        |          |  |

|                       |             |                        | -    | H'7                                             | ・リロードモード |  |

|                       |             |                        |      | ・Multi-dimensional モード                          |          |  |

|                       |             |                        | LED  | ストライド転送                                         |          |  |

|                       |             |                        | H'D  | ※SAR を SAOFR で変更                                |          |  |

|                       |             | RPT[3:0]               |      | DAR を DAOFR で変更                                 |          |  |

|                       |             | (bit28-25)             |      | ・Multi-dimensional モード                          |          |  |

|                       |             |                        | H'E  | Multi-dimensional 転送                            |          |  |

|                       |             |                        | 111  | Scatter 転送                                      |          |  |

|                       |             |                        |      | ※DAR を DAOFR で変更                                |          |  |

|                       |             |                        |      | ・Multi-dimensional モード                          |          |  |

|                       |             |                        | H'F  | Gather 転送                                       |          |  |

|                       | H'FE80 802C |                        |      | ※SAR を DASAR で変更                                |          |  |

|                       |             | TS[2:0]<br>(bit20,4,3) | H'0  | ・DMA 転送サイズ指定                                    |          |  |

|                       |             |                        | 11.0 | バイト単位                                           |          |  |

|                       |             |                        | H'1  | ・DMA 転送サイズ指定                                    |          |  |

|                       |             |                        |      | ワード単位                                           |          |  |

| _                     |             |                        | H'2  | ・DMA 転送サイズ指定                                    |          |  |

| DMA0 チャネルコントロール       |             |                        |      | ロングワード単位                                        |          |  |

| レジスタ 0                |             |                        | H'3  | ・DMA 転送サイズ指定                                    |          |  |

| (DMA0CHCR0)           |             |                        | H'4  | 16 バイト単位                                        |          |  |

|                       |             |                        |      | <ul><li>・DMA 転送サイズ指定</li><li>32 バイト単位</li></ul> |          |  |

|                       |             | DM                     | H'1  | 32 ハ1 下単位<br>  ・ディスティネーションアドレスモード               |          |  |

|                       |             | DM<br>(bit15,14)       |      |                                                 |          |  |

|                       |             | SM                     |      | ディスティネーションアドレスを増加<br>・ソースアドレスモード                |          |  |

|                       |             | (bit13,12)             | H'1  | ・ノーヘアトレスモート<br>  ソースアドレスを増加                     |          |  |

|                       |             | (bit13,12)<br>RS       |      | ・リソースセレクト                                       |          |  |

|                       |             | (bit11-6)              | H'8  | 内蔵周辺モジュールリクエスト                                  |          |  |

|                       |             | (2 0)                  |      | ・インタラプトイネーブル                                    |          |  |

|                       |             | IE                     | H'1  | 初期化時:許可                                         |          |  |

|                       |             | (bit2)                 |      | ・インタラプトイネーブル                                    |          |  |

|                       |             | ` ,                    | H'0  | 割り込み処理時:禁止                                      |          |  |

|                       |             | _                      |      | ・トランスファエンドフラグ                                   |          |  |

|                       |             | TE                     | H'0  | ※最終転送を開始する時に H'1                                |          |  |

|                       |             | (bit1)                 |      | にセットされます                                        |          |  |

|                       |             |                        | 1.00 | ・DMA イネーブル                                      |          |  |

|                       |             | DE                     | H'0  | 初期化,転送完了時                                       |          |  |

|                       |             | (bit0)                 | ⊔'4  | ・DMA イネーブル                                      |          |  |

|                       |             |                        | H'1  | 転送開始時                                           |          |  |

表 2.1.4.6 DMAC0 レジスタ設定値 1(チャネル 4)

| しごっちなみががか                     |              |     |           | タ 設 正 他 1(ナ・ | ĺ                                                                                                              |                                                                                                               |  |  |             |                                                                                                                 |  |  |  |  |  |  |  |  |             |                                                                                                               |

|-------------------------------|--------------|-----|-----------|--------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|-------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|-------------|---------------------------------------------------------------------------------------------------------------|

| レジスタ名称(呼称)<br>                | アドレス         | R/W | サイズ       | 設定値          | 動作仕様                                                                                                           |                                                                                                               |  |  |             |                                                                                                                 |  |  |  |  |  |  |  |  |             |                                                                                                               |

| DMA0 ソースアドレスレジスタ 4            | H'FE80 8070  | R/W | 32        | H'1400 E000  | ・転送元の開始アドレスを指定<br>OL メモリを指定した場合<br>(DMA0DAR4 は DDR3-SDRAM を指定)                                                 |                                                                                                               |  |  |             |                                                                                                                 |  |  |  |  |  |  |  |  |             |                                                                                                               |

| (DMA0SAR4)                    |              |     |           | H'0800 0000  | ・転送元の開始アドレスを指定<br>DDR3-SDRAM を指定した場合<br>(DMA0DAR 4 は OL メモリを指定)                                                |                                                                                                               |  |  |             |                                                                                                                 |  |  |  |  |  |  |  |  |             |                                                                                                               |

| DMA0 ディスティネーション<br>アドレスレジスタ 4 | H'FE80 8074  |     | 32        | H'1400 E000  | ・転送先の開始アドレスを指定<br>OL メモリを指定した場合<br>(DMA0SAR4 は DDR3-SDRAM を指定)                                                 |                                                                                                               |  |  |             |                                                                                                                 |  |  |  |  |  |  |  |  |             |                                                                                                               |

| (DMA0DAR4)                    | 111 200 0074 | R/W | <i>52</i> | H'0800 0000  | ・転送先の開始アドレスを指定<br>DDR3-SDRAM を指定した場合<br>(DMA0SAR4 は OL メモリを指定)                                                 |                                                                                                               |  |  |             |                                                                                                                 |  |  |  |  |  |  |  |  |             |                                                                                                               |

|                               |              |     |           | H'0000 0064  | ・転送回数の設定<br>100回(転送サイズ 1 バイト時)<br>※通常, リロード, ストライドモード転送時                                                       |                                                                                                               |  |  |             |                                                                                                                 |  |  |  |  |  |  |  |  |             |                                                                                                               |

|                               |              |     |           | H'0000 0032  | ・転送回数の設定<br>50回(転送サイズ2バイト時)<br>※通常、ェリロード、ストライドモード転送時                                                           |                                                                                                               |  |  |             |                                                                                                                 |  |  |  |  |  |  |  |  |             |                                                                                                               |