# SH7763 グループ

# LCD コントローラ設定例

R01AN0307JJ0100 Rev.1.00 2010.10.27

# 要旨

本アプリケーションノートは、SH7763 の LCD コントローラ (LCDC) の使用方法と、TFT-LCD モジュール の表示例を掲載しています。

# 動作確認デバイス

SH7763

# 目次

| 1. | はじめに                       | 2  |

|----|----------------------------|----|

| 2. | LCDC の動作説明                 | 4  |

| 3. | LCDC で表示可能な液晶モジュールのサイズについて | 15 |

| 4. | 応用例の説明                     | 16 |

| 5. | 参考プログラム例                   | 28 |

| 6. | 実行結果                       | 42 |

| 7  | <b>会老ドキュメント</b>            | 13 |

# 1. はじめに

# 1.1 仕様

● 本アプリケーションノートでは、2章で LCDC のハードウェアマニュアルを補足する説明を行い、3章ではシステム設計に必要な LCDC のバス負荷率について説明します。4章では、TFT-LCD モジュールに4種類の画像を交互に表示し、TFT-LCD モジュールの電源 ON/OFF を繰り返す応用例を掲載しています。

#### 1.2 使用機能

LCDC

## 1.3 適用条件

● 評価ボ・ド: 日立超 LSI システムズ製 SH7763 Solution Engine 型番 MS7763SE02

外付けメモリ (エリア 0): NOR 型フラッシュメモリ 16M バイト

Spansion 製 S29GL128M10TDIR90

(エリア 2, 3): DDR-SDRAM 128M バイト

Micron 製 MT46V32M16TG-6T×2

• マイコン: SH7763 (R5S77630AY266BGV)

● 動作周波数: CPU クロック: 266.6MHz

SH バスクロック: 133.3MHz バスクロック: 66.6MHz DDR-SDRAM クロック: 133.3MHz 周辺バス 0 クロック: 66.6MHz

エリア 0 バス幅: 16 ビット (MD3 端子 = Low レベル、MD4 端子 = High レベル)

クロック動作モード: モード 0 (MD0 ~ MD2 端子 = Low レベル)

エンディアン: ビッグエンディアン (MD5 端子 = Low レベル)

• ツールチェーン: ルネサス エレクトロニクス製 SuperH RISC engine Standard Toolchain Ver.9.3.0.0

• コンパイルオプション: High-performance Embedded Workshop での設定

(-cpu=sh4aldsp -endian=little -include="\$(PROJDIR)\formalism"

-object="\$(CONFIGDIR)\pmax\\$(FILELEAF).obj" -debug -optimize=0 -gbr=auto -chgincpath -errorpath -global volatile=0 -opt range=all -infinite loop=0

-del\_vacant\_loop=0 -struct\_alloc=1 -nologo)

# 1.4 本アプリケーションノートで用いる用語の説明

フレーム:

ディスプレイに表示するイメージの通りに画素情報をメモリに配置したもので、フレーム情報が配置されたバッファをフレームバッファと呼びます。LCDC はフレームバッファから画素情報を読み出して画像を表示します。

フレームレート[Hz]:

LCDC に接続された LCD モジュールが 1 秒間に何回画面を書き換えるかを表します。

# 1.5 本アプリケーションノートの適用範囲

本アプリケーションノートは、OS 非搭載でフレームバッファの画像を RGB インタフェース方式の LCD モジュールに連続モードで表示する、LCDC の基本的な使用方法について説明します。

# 1.6 関連アプリケーションノート

本資料の参考プログラムは,「SH7763 グループ アプリケーションノート SH7763 初期設定例 (RJJ06B1050)」の設定条件で動作確認しています。併せて参照ください。

# 2. LCDC の動作説明

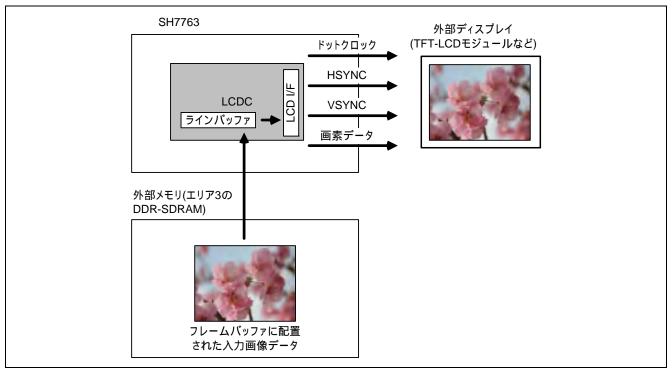

#### 2.1 LCDC の概要

LCDC は外部メモリ上に配置されたフレームバッファから画像データを読み出し、TFT-LCD モジュールに出力して画像を表示させることが可能な画像系モジュールです。本アプリケーションノートでは RGB 形式の画像データを読み出し、RGB インタフェース方式の LCD モジュールに画像を表示させる設定例を紹介します。

図1 LCDC の動作イメージ

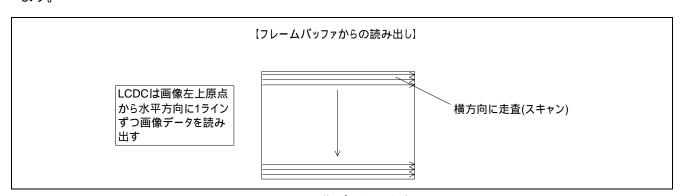

# 2.1.1 画像データの読み出し

LCDCは、フレームバッファを画像左上の原点から右方向に1画素ずつ読み出します。画像横幅分の画素情報を1ラインと呼びます。1ライン分読み出すと1つ下の左端に戻って読み出しを続け、画像縦幅に等しいライン数を読み出すと1フレームの読み出しが完了します。次フレームの読み出しは再び原点から読み出します。

図2 画像データの入力

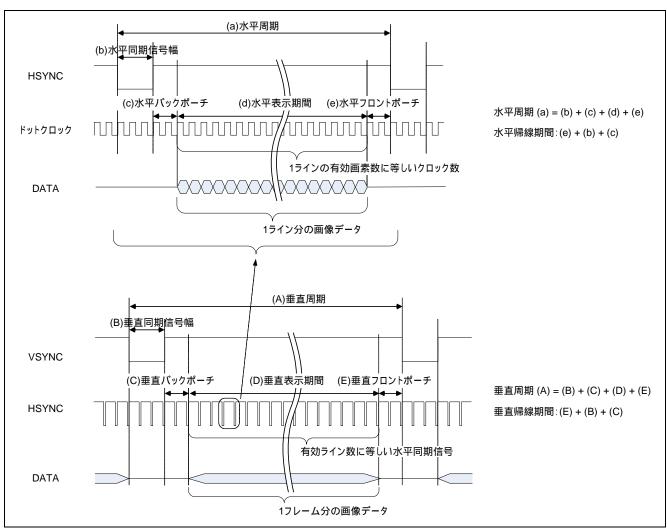

#### 2.1.2 画像データの出力

LCDCは、下記の3つの同期信号に同期して画像データを出力します。

- ドットクロック (DOTCLK): 1 画素の情報はドットクロックに同期して出力します。(端子名: LCD\_CL2, LCDM\_CL2)

- 水平同期信号 (HSYNC):

画像の横幅 1 ライン分の情報は水平同期信号に同期して出力します。同期信号の前後の画素情報を出力しない期間をそれぞれ水平フロントポーチ、水平バックポーチと呼びます。(端子名: LCD\_CL1, LCDM\_CL1)

- 垂直同期信号 (VSYNC):

画像 1 フレーム分の情報は垂直同期信号に同期して出力します。同期信号の前後の画素情報を出力しない期間をそれぞれ垂直フロントポーチ、垂直バックポーチと呼びます。(端子名: LCD FLM, LCDM FLM)

図3 画像データと同期信号の出力

同期信号の1周期中に、画像の表示期間と非表示期間が存在します。水平方向の非表示期間は、左から右へと1ラインの表示を終了してから、左へ戻って次の1ラインの表示を開始するまでの期間で、水平帰線期間と呼びます。垂直方向の非表示期間は、1フレームの表示を終了してから、次の1フレームの表示を開始するまでの時間で、垂直帰線期間と呼びます。

#### 2.2 LCDC の特長

LCDC の主な特長を表1に示します。

表 1 LCDC の特長

| 項目               | 仕様                                                                                     |

|------------------|----------------------------------------------------------------------------------------|

| 表示システム構成         | ユニファイドメモリアークテクチャ: 表示用の画像をエリア 3 の                                                       |

|                  | DDR-SDRAM 上に格納することで、専用の表示用メモリが不要                                                       |

|                  | (エリア 3 の DDR-SDRAM 以外の領域では表示不可)                                                        |

| サポートする表示パネル      | ● 液晶タイプ: STN/Dual STN/TFT パネル                                                          |

|                  | ● バス幅: 4/8/12/16/18*ビット                                                                |

|                  | 【注】 * 18 ビットバス幅の TFT パネル接続時は、未結線となる下位ビットの信号を GND またはデータが出力される最下位ビットに接続してください。          |

| <br>サポートする色表示    | ● 4/8/15/16bpp (ビットパーピクセル) カラーモード                                                      |

| ラが ドッる巴松が        | <ul><li>1/2/4/6bpp グレイスケールモード</li></ul>                                                |

| 表示可能な LCD モジュールの | 16×1~1024×1024 までの液晶パネルサイズをサポート                                                        |

| サイズ              | 【注】 外部メモリに表示バッファを置くため、実際にはバス占有率によって表示サイズが制限されます。 目安としては WVGA 程度となりますが、詳細は3章の計算を参照ください。 |

| 色制御              | 24 ビットカラーパレットメモリを使用することで、16M 色中 256 エントリの同時発色が可能です。                                    |

## 2.3 LCDC の設定

LCDC の機能およびレジスタへの設定方法を示します。

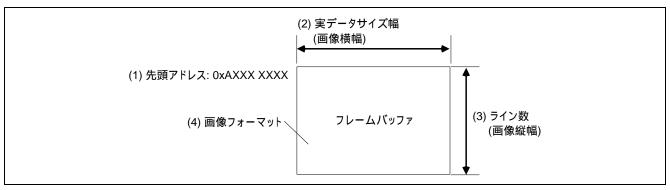

#### 2.3.1 フレームバッファの設定

LCDC がメモリから画像データを読み出す際に必要とするフレームバッファ情報を図 4 に示します。

図4 フレームバッファ構成

- (1) 先頭アドレス: フレームバッファの原点のアドレスを 512 バイトアライメントで指定します。アドレスは 物理アドレスがアクセス可能なキャッシュオフ領域を設定します。

- (2) 実データサイズ幅: 画像の横幅を画素単位で指定します。ただし、LCDC は水平方向についてはキャラクタ単位 (1 キャラクタ: 8 画素) で取り扱うため、8 の倍数である必要があります (2.3.5 章を参照)。

- (3) ライン数: 画像の縦幅を画素単位で指定します (2.3.5 章を参照)。

- (4) 画像フォーマット: LCDC に入力可能なデータフォーマットについては、「SH7763 グループ ハードウェアマニュアル (RJJ09B0260) 37.4.4 データフォーマット」をご参照ください。表 2 に LCDC 表示データの設定で使用するレジスタを示します。

- (5) ラインアドレスオフセット: フレームバッファの Y 座標のインクリメント幅を設定します。LDLAOR の最小アライメント単位は 16 バイトです。

表 2 LCDC表示データの設定

| 機能                               | レジスタ                                        |

|----------------------------------|---------------------------------------------|

| • エンディアンの設定                      | LCDC データフォーマットレジスタ (LDDFR)                  |

| ● データフォーマットの設定                   |                                             |

| 表示データ取り込み開始アドレス<br>設定            | LCDC 上部表示パネル用データ取り込み開始アドレスレジスタ<br>(LDSARU)  |

| 下部表示パネルデータ取り込み開始アドレス設定 (DSTN のみ) | LCDC 下部表示パネル用データ取り込み開始アドレスレジスタ<br>(LDSARL)  |

| フレームバッファのY座標のインク<br>リメント幅の設定     | LCDC 表示パネル用取り込みデータラインアドレスオフセットレジスタ (LDLAOR) |

#### 2.3.2 LCDC 出力端子の設定

LCDC 出力端子には、表 3 に示すように LCDC 出力端子とマルチプレクスされた他の端子機能を有効に選択するため、通常出力グループとミラー出力グループの 2 つの端子グループがあります。端子グループの選択は汎用入出力ポート (GPIO) のピンセレクトレジスタで行います。LCDC の設定は不要です。

2つのグループ間では、端子の出力タイミングが異なりますので、2つのグループの端子を混在して使用することはできません。

表 3 に LCDC の入出力端子のグループを示します。

表 3 LCDC 入出力端子

| 端子グループ名   | 端子名                                                 |

|-----------|-----------------------------------------------------|

| 通常出力グループ  | LCD_D15 ~ 0, LCD_DON, LCD_CL1, LCD_CL2, LCD_M_DISP, |

|           | LCD_FLM, LCD_VCPWC, LCD_VEPWC                       |

| ミラー出力グループ | LCDM_D15 ~ 0, LCDM_DON, LCDM_CL1, LCDM_CL2,         |

|           | LCDM_M_DISP, LCDM_FLM, LCDM_VCPWC, LCDM_VEPWC       |

| 共通入力端子    | LCD_CLK                                             |

#### 2.3.3 LCDC 入力クロックの設定

LCDC の動作クロック源の選択と、入力クロックの分周率の設定を行います。

設定された値は DOTCLK として LCD\_CL2 (ミラー端子の場合は LCDM\_CL2) から LCD モジュールに供給されます (TFT パネルの場合)。接続する LCD モジュールの仕様に併せて設定してください。

なお、LCDCへの入力クロックは66MHz以下となるように設定してください。

- (1) 入力クロック選択: LCDC の入力クロック源を周辺クロック 0、外部クロックのいずれかから選択します。

- (2) クロック分周比: 入力クロックの分周比を設定します。

表 4 に LCDC 入力クロックの設定で使用する LCDC のレジスタを示します。

表 4 LCDC 入力クロックの設定

| 機能            | レジスタ                        |

|---------------|-----------------------------|

| LCD 入力クロックの設定 | LCDC インプットクロックレジスタ (LDICKR) |

#### 2.3.4 LCD モジュールタイプの設定

使用する LCD モジュールの仕様により、LCD モジュールインタフェース、信号極性などを設定します。使用する LCD モジュールのデータシートを参考に、各値を設定してください。

- (1) モジュールインタフェース: 液晶パネルタイプ (STN/DSTN/TFT) と液晶パネルへの出力データバス幅を選択します。本アプリケーションノートでは、TFT カラー16 ビットデータバスモジュールを選択した際の設定内容を示します。

- (2) 同期信号極性: 垂直同期信号 LCD\_FLM (VSYNC) と水平同期信号 LCD\_CL1 (HSYNC) をローアクティブまたはハイアクティブに設定します。ローアクティブのとき、同期信号 (2.3.5 章の HSYNW/VSYNW) の期間に Low を出力します。ハイアクティブのときは逆に High を出力します。

- (3) 水平同期信号出力制御: VSYNC の帰線期間中に水平同期信号 LCD\_CL1 (HSYNC) を出力する/しないを設定します。

- (4) ドットクロック制御: VSYNC・HSYNC の帰線期間中にドットクロック LCD\_CL2 を出力する/しないを設定します。

- (5) 表示イネーブル信号極性: 表示イネーブル信号 LCD\_M\_DISP をローアクティブまたはハイアクティブに 設定します。

- (6) 表示イネーブル信号出力制御:表示イネーブル信号 LCD\_M\_DISP を出力する/しないを設定します。

- (7) 表示データ極性: 表示データをハイアクティブ (値をそのまま出力) またはローアクティブ (ビット反転して出力) に設定します。

各設定の詳細は、「SH7763グループ ハードウェアマニュアル (RJJ09B0260) 37章 LCD コントローラ (LCDC) 37.3.2 LCDC モジュールタイプレジスタ (LDMTR)」をご参照ください。

表 5 に LCD モジュールタイプの設定で使用する LCDC のレジスタを示します。

## 表 5 LCD インタフェースの設定

| 機能                 | レジスタ                      |

|--------------------|---------------------------|

| ● 液晶モジュールタイプの設定    | LCDC モジュールタイプレジスタ (LDMTR) |

| ● VSYNC 極性         |                           |

| ● HSYNC 極性         |                           |

| ● DISP (表示許可) 極性   |                           |

| ● 表示データ極性          |                           |

| ● M信号 (液晶交流化信号) 制御 |                           |

| ● HSYNC 制御         |                           |

| ● DOTCLK 制御        |                           |

#### 2.3.5 同期信号の設定

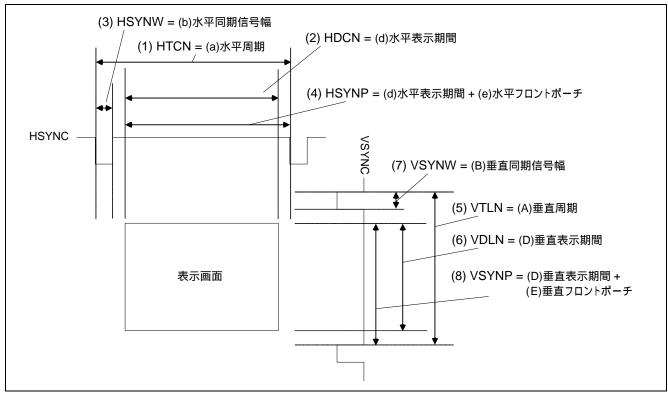

使用する LCD モジュールの、図 3 の(A) ~ (E)、(a) ~ (e)の特性に合わせて、図 5 の同期信号パラメータを設定します。

図5 同期信号の構成

- (1) HTCN: 水平周期 1 をキャラクタ単位で設定します。

- (2) HDCN: 水平表示期間 1 をキャラクタ単位で設定します。

- (3) HSYNW: 水平同期信号幅 1 をキャラクタ単位で設定します。

- (4) HSYNP: (水平表示期間 + 水平フロントポーチ幅) 1 をキャラクタ単位で設定します。

- (5) VTLN: 垂直周期 1 を水平同期信号単位で設定します。

- (6) VDLN: 垂直表示期間 1 を水平同期信号単位で設定します。

- (7) VSYNW: 垂直同期信号幅 1 を水平同期信号単位で設定します。

- (8) VSYNP: (垂直表示期間 + 垂直フロントポーチ幅) 2 を水平同期信号単位で設定します。

## 【水平方向の設定についての注意事項】

- 1キャラクタ=8画素(8ドットクロック)となります。そのため、水平方向の各パラメータはドットクロック単位で8の倍数でのみ設定できます。ご使用のLCDモジュールによっては、水平方向のパラメータがドットクロック単位で8の倍数以外の値が必要になる場合がありますが、この場合、最も値の近い8の倍数を指定し、それをキャラクタ単位に直した値(1/8にした値)を設定します。ご使用になるLCDモジュールで問題ないか、事前に十分ご確認ください。LCDモジュールが対応できない場合、左右どちらかの端に表示されない範囲が発生する可能性があります。

- HTCN ≥ HDCN の関係を満足するように設定してください。

- HTCN ≥ HSYNP + HSYNW + 1 の関係を満足するように設定してください。

- HSYNP≥HDCN+1の関係を満足するように設定してください。

- HDCNの設定は、使用するパネルの解像度によって制限があります。詳細はハードウェアマニュアルの該当するレジスタの設定をご参照ください。

#### 【垂直方向の設定についての注意事項】

• VTLN ≥ VDLN、VTLN ≥ 1 の関係を満足するように設定してください。

表 6 に同期信号の設定で使用する LCDC のレジスタを示します。

| 表 6  | 同期 | 信号の    | 設定 |

|------|----|--------|----|

| 1K U |    | ID 7 V | ᇄᇨ |

| 機能        | レジスタ                          |

|-----------|-------------------------------|

| 水平同期信号の設定 | LCDC 水平キャラクタナンバレジスタ (LDHCNR)  |

|           | LCDC 水平同期信号レジスタ (LDHSYNR)     |

| 垂直同期信号の設定 | LCDC 垂直表示ラインナンバレジスタ (LDVDLNR) |

|           | LCDC 垂直総ラインナンバレジスタ (LDVTLNR)  |

|           | LCDC 垂直同期信号レジスタ (LDVSYNR)     |

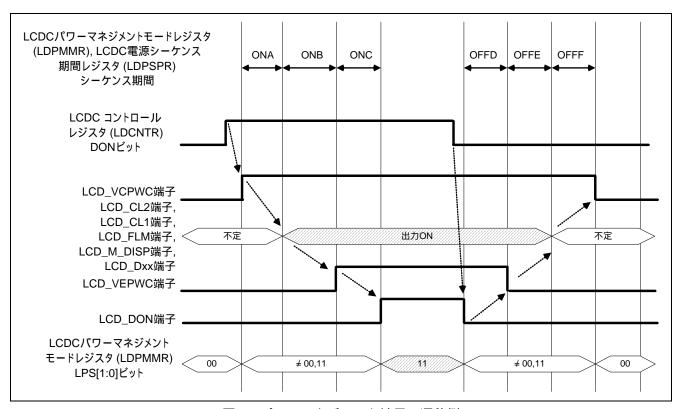

#### 2.3.6 パワーマネジメントの設定

LCDC には、液晶モジュールの電源管理を行うための3本の制御信号を、設定したシーケンスに従って操作する機能があります。この機能を用いると、液晶モジュールの電源制御を、LCDC の表示開始と表示停止に同期させることが可能です。本機能で制御できる外部端子は、下記の3本です(以下、パワーマネジメント端子と表記)。

- LCDVCPWC 端子:表示開始のとき最初に High になり、表示停止のとき最後に Low になります。

- LCDVEPWC 端子: 表示開始のとき 2番目に High になり、表示停止のとき 2番目に Low になります。

- LCDDON 端子: 表示開始のとき最後に High になり、表示停止のとき最初に Low になります。

表7にパワーマネジメントの設定で使用するLCDCのレジスタを示します。

表7 パワーマネジメントの設定

| 機能              | レジスタ                           |

|-----------------|--------------------------------|

| パワーマネジメント端子のタイミ | LCDC パワーマネジメントモードレジスタ (LDPMMR) |

| ング設定            | LCDC 電源シーケンス期間レジスタ (LDPSPR)    |

LCDC 起動時および停止時の各パワーマネジメント端子の信号レベルの遷移を図6に示します。

図 6 パワーマネジメント端子の遷移例

各信号間の遅延時間は、LDPMMR レジスタと LDPSPR レジスタのシーケンス期間を設定するビットの値に等しいフレーム期間となります。詳細は「SH7763 グループ ハードウェアマニュアル (RJJ09B0260) 37 章 LCD コントローラ (LCDC) 37.4.6 電源制御シーケンス処理」を参照ください。

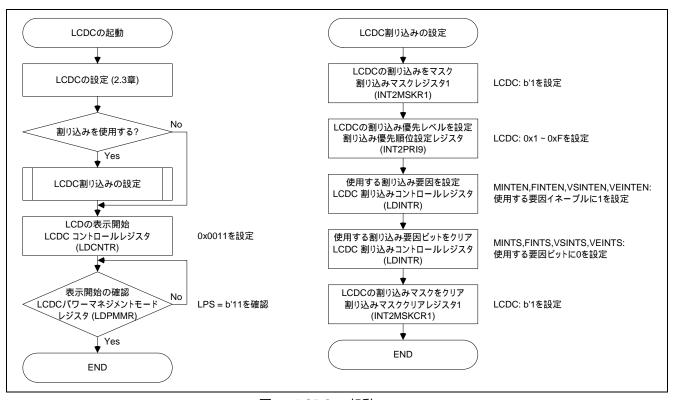

#### 2.4 LCDC の起動と停止

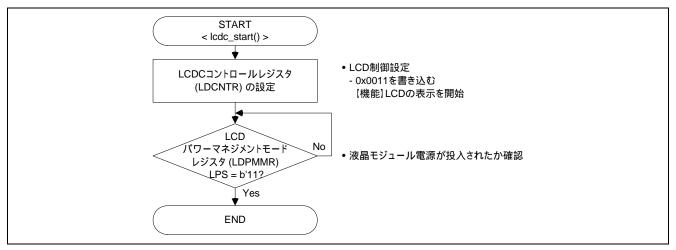

LCDC を起動してメイン LCD モジュールの表示を開始するフローを図 7 に示します。

図 7 LCDC の起動フロー

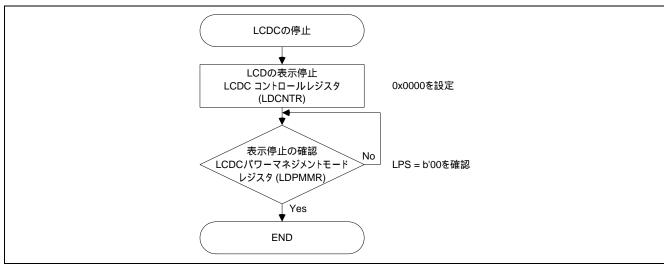

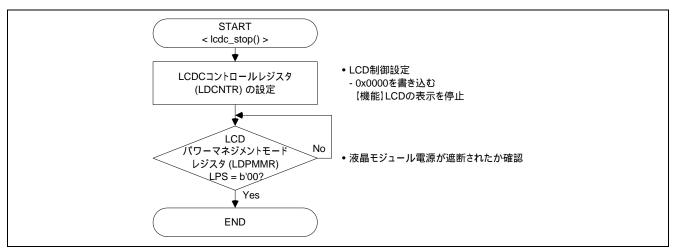

LCDC を停止して LCD モジュールの表示を停止するフローを図 8 に示します。

図 8 LCDC の停止フロー

- 2.3章の LCDC の設定は順不同です。どの設定から行ってもかまいません。

- LCDC 割り込みを使用する場合は、割り込みが発生可能な状態にしてから LCD の表示を開始してください。表示を開始してから LCDC の割り込み発生を許可 (割り込みマスクをクリアするなど) すると、意図しないタイミングで割り込みが発生する可能性があります。

- 表示終了時は、LDCNTR レジスタに 0x0000 を書き込みます。

- 表示開始・表示停止の確認は、パワーマネジメント使用の有無に関わらず、LCDC パワーマネジメントモードレジスタ (LDPMMR) の LPS ビットで判断します。

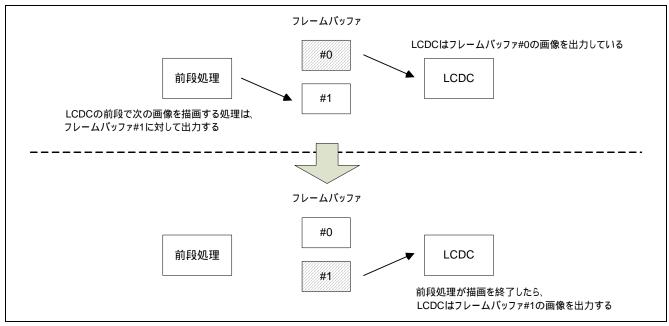

## 2.5 LCDC の同期設計

LCDC の表示する画像データを更新するとき、フレームバッファが 1 つのみの場合、LCDC が読み込んでいる最中にそのフレームバッファに新しいフレーム情報を描画することになるため、ティアリングなどの画像乱れが発生します。これを避けるために、フレームバッファを複数用意しておき、次に表示するフレームバッファの描画が完了したら LCDC の読み込み先を変更するという操作が必要となります。

図9 面切り替え操作の概要

# 2.5.1 取り込み開始アドレスレジスタ設定変更による複数バッファの切り替え

以下、表示中の面を使用面、表示していない面を非使用面と呼びます。次に表示するフレームバッファの情報を非使用面に設定し、非使用面のフレームバッファの準備が完了したら、使用面と非使用面を切り替えて新しいフレームバッファを表示します。

#### 【面切り替えの方法】

使用面を切り替えるには、LCDC の各種割り込みタイミングの割り込み処理ルーチンの中で、LCDC 上部表示パネル用データ取り込み開始アドレスレジスタ (LDSARU) を、非使用面のバッファの先頭アドレスに切り替えます。

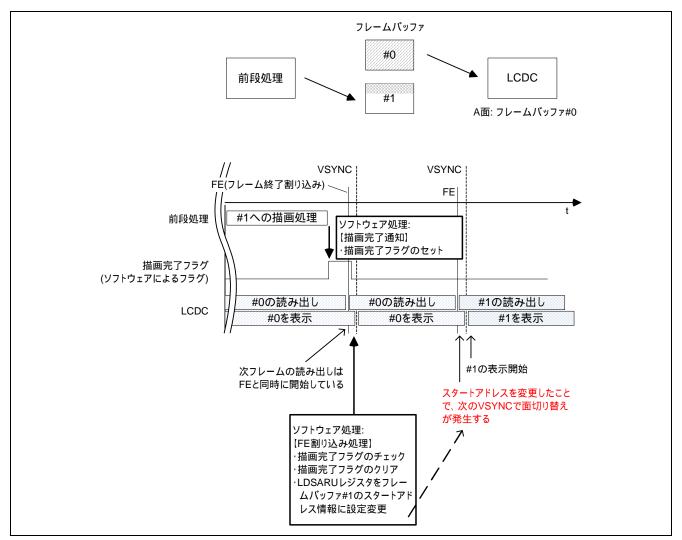

● ソフトウェア切り替えのタイミングチャートを図 10 に示します。ここでは前段処理との同期を取るために、ソフトウェアによるフラグでの運用例を示しています。

図 10 ソフトウェア切り替えの発生タイミング

前段処理は描画を完了したら描画完了フラグを立てます。LCDC はフレーム終了割り込み処理で描画 完了フラグを監視し、フラグが立っていれば非使用面のバッファの先頭アドレスを LDSARU レジスタ に設定します。LCDC は LDSARU レジスタを書き換えた次のフレームで表示する画像が更新されます。

# 2.6 注意事項

## 2.6.1 表示データ格納用 VRAM アクセスの停止手順

表示データ格納用 VRAM (エリア 3 の DDR-SDRAM) アクセスの停止手順は、以下のフローに従ってください。

- (1) 現在の状態がLDPMMR レジスタのLPS1,LPS0ビットが1であることを確認します。

- (2) LDCNTR レジスタの DON ビットを 0 (表示オフモード) に設定します。

- (3) LDPMMR レジスタの LPS1, LPS0 ビットが 0 になったことを確認します。

- (4) 1フレームの表示時間を待ちます。

#### 2.6.2 LDCNTR レジスタへの書き込みについて

LDCNTR レジスタへの書き込みは、表示開始時の 0x0011、表示終了時の 0x0000 以外の値は書き込まないでください。

表示動作開始時以外で 0x0011 等を重ね書きした場合、LCDC が不安定となり、意図しない動作をすることがあり、動作の保証ができません。

# 3. LCDC で表示可能な液晶モジュールのサイズについて

LCDC は、機能としては  $1024 \times 1024$  ドット、16bpp の表示が可能ですが、表示される画像のイメージは CPU と一部周辺機能が共有するエリア 3 に接続される DDR-SDRAM に格納されています。

よって CPU や他の周辺機能がエリア 3 の DDR-SDRAM にアクセスする状況によっては、表示が困難となる場合があります。

表示可能な液晶モジュールのサイズの目安は、下記で計算されるバス占有率が 40% を越えないようにして ください。

バス幅 (エリア 3 の DDR-SDRAM、固定): 32 ビットオーバヘッド係数 (固定): 1.375

#### 【計算例】

表示サイズ: 640×480 ピクセル

HDCN: 79 VDLN: 479

フレームレート: 60Hz

色数: 16bpp CLKOUT: 66MHz

$(1.375 \times (79 + 1) \times 8 \times (479 + 1) \times 60 \times 16 \times 100) / (66000000 \times 32) = 19.2\%$

# 4. 応用例の説明

LCDC を使用してグラフィック画像を表示するための参考例として、端子接続例と設定例を説明します。

## 4.1 TFT-LCD パネルの仕様

本アプリケーションノートで使用する TFT-LCD パネルの仕様を示します。仕様の詳細は TFT-LCD パネルによって異なりますので、使用する製品のデータシートを確認してください。

#### 4.1.1 一般仕様

表8に本アプリケーションノートで使用するTFT-LCDパネルの一般仕様を示します。

表 8 TFT-LCD パネルの一般仕様 (データシートから抜粋)

| 項目            | 仕様                                                             |

|---------------|----------------------------------------------------------------|

| 解像度           | VGA or QVGA (本応用例では VGA で使用)                                   |

| 画素数           | H480×V640 (ドット数: H (480×3)×V640)<br>R, G, B の 3 ドットで 1 画素となります |

| <br>カラーフィルタ配置 | R・G・B縦ストライプ                                                    |

| 入力信号          | CMOS, R・G・B 各 6 ビットデジタル                                        |

## 4.1.2 端子機能

表 9 に本アプリケーションノートで使用する TFT-LCD パネルの端子機能を示します。

表 9 TFT-LCD パネルの端子機能 (データシートから抜粋)

| 端子名   | 機能                              |

|-------|---------------------------------|

| RESB  | リセット信号                          |

| INI   | パワーオン制御                         |

| DEN   | 表示開始信号                          |

| HSYNC | 水平同期信号                          |

| VSYNC | 垂直同期信号                          |

| CLKIN | ドットクロック                         |

| R5-0  | 赤データ信号 (6 ビット、MSB: R5, LSB: R0) |

| G5-0  | 緑データ信号 (6 ビット、MSB: G5, LSB: G0) |

| B5-0  | 青データ信号 (6 ビット、MSB: B5, LSB: B0) |

# 4.1.3 インタフェースタイミング

表 10 に本アプリケーションノートで使用する TFT-LCD パネルのインタフェースタイミングとその特性を示します。

表 10 TFT-LCD パネルのタイミング特性 (データシートから抜粋)

|       | 項目          | MODE | 記号               | 最小  | 標準    | 最大   | 単位    |

|-------|-------------|------|------------------|-----|-------|------|-------|

| CLK   | サイクル時間      | VGA  | t <sub>CLK</sub> | 38  | 39.7  | 41.7 | ns    |

|       |             | QVGA |                  | 152 | 158.8 | 167  |       |

| HSYNC | サイクル時間      | VGA  | t <sub>HS</sub>  | _   | 648   |      | CLK   |

|       |             | QVGA |                  |     | 324   |      |       |

|       | 水平バックポーチ時間  | VGA  | t <sub>HBP</sub> | 28  | 78    | 166  |       |

|       |             | QVGA |                  | 14  | 38    | 82   |       |

|       | 水平フロントポーチ時間 | VGA  | t <sub>HFP</sub> | 0   | 88    | 138  |       |

|       |             | QVGA |                  | 0   | 44    | 68   |       |

|       | 有効表示期間      | VGA  | t <sub>HHW</sub> | _   | 480   |      |       |

|       |             | QVGA |                  | _   | 240   |      |       |

|       | 同期信号幅       |      | t <sub>HSW</sub> | _   | 2     | _    |       |

| VSYNC | サイクル時間      | VGA  | t <sub>VS</sub>  | _   | 648   |      | HSYNC |

|       |             | QVGA |                  | _   | 324   | _    |       |

|       | 垂直バックポーチ時間  | VGA  | _                | _   | (1)   |      |       |

|       |             | QVGA |                  | _   | (1)   |      |       |

|       | 垂直フロントポーチ時間 | VGA  | _                | _   | (6)   |      |       |

|       |             | QVGA |                  | _   | (2)   |      |       |

|       | 有効表示期間      | VGA  | _                | _   | 640   | _    |       |

|       |             | QVGA |                  | _   | 320   | _    |       |

|       | 同期信号幅       |      | t <sub>VSW</sub> | _   | 1     |      |       |

<sup>【</sup>注】 垂直バックポーチ時間と垂直フロントポーチ時間は AC 特性の表には記述が無いため、タイミング チャート図より判断しています。

表 10より算出した、VGA表示のためのLCDCのタイミング設定例を表 11に示します。

表 11 VGA タイミングの設定例

| 機能                  | レジスタ名                               | ビット名                                                  | 算出式例          | 設定値例  |

|---------------------|-------------------------------------|-------------------------------------------------------|---------------|-------|

| 水平方向<br>タイミング       | LCD<br>水平キャラクタナンバ                   | HTCN:<br>水平周期 – 1                                     | 648/8–1 = 80  | 0x50  |

| 設定                  | レジスタ (LDHCNR)                       | HDCN:<br>水平表示期間 – 1                                   | 480/8–1 = 59  | 0x3B  |

|                     | LCD<br>水平同期信号レジスタ<br>(LDHSYNR)      | HSYNW:<br>水平同期信号幅 – 1                                 | 8/8-1 = 0 *1  | 0x0   |

|                     |                                     | HSYNP:<br>(水平表示期間 +<br>水平フロントポーチ幅) – 1                | 568/8–1 = 70  | 0x46  |

| 垂直方向<br>タイミング<br>設定 | LCD<br>垂直総ラインナンバ<br>レジスタ (LDVTLNR)  | VTLN:<br>垂直周期 – 1                                     | 648–1 = 647   | 0x287 |

|                     | LCD<br>垂直表示ラインナンバ<br>レジスタ (LDVDLNR) | VDLN:<br>垂直表示期間 – 1                                   | 640–1 = 639   | 0x27F |

|                     | LCD<br>垂直同期信号レジスタ<br>(LDVSYNR)      | VSYNW:<br>垂直同期信号幅 – 1                                 | 1–1           | 0x0   |

|                     |                                     | VSYNP:<br>(垂直表示期間 +<br>垂直フロントポーチ幅) – 2 * <sup>2</sup> | 648–1–2 = 645 | 0x285 |

<sup>【</sup>注】 \*1 TFT パネルの同期信号幅は2のため、設定の最小幅8を代入して計算。

<sup>\*2</sup> TFT パネルのデータシートに垂直フロントポーチ幅の規定がないため、 (垂直周期 – 垂直同期信号幅) – 2 で計算しています。

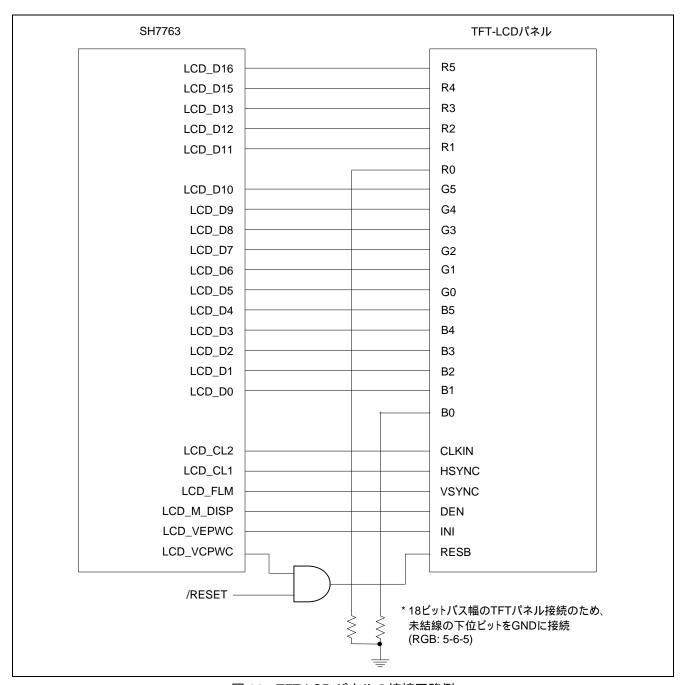

# 4.2 TFT-LCD パネル接続回路例

## 4.2.1 端子接続例

図 11 に本アプリケーションノートにおける TFT-LCD パネルの接続回路例を示します。

18 ビットバス幅の TFT パネルを R: 5、G: 6、B: 5 で接続しています。

図 11 TFT-LCD パネルの接続回路例

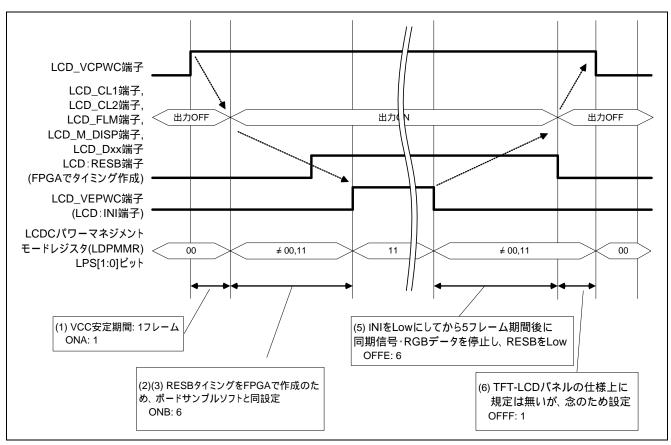

#### 4.2.2 パワーマネジメント設定

本応用例で使用する TFT-LCD パネルの電源制御タイミング要件より、LCDC のパワーマネジメント機能を以下のように設定します。

#### 【電源ON時】

- 要件(1): VCC (+3.3V) を 2 フレーム期間で安定させる: ONA は 1 に設定: RESB タイミングがボード上の FPGA で作成されているため、ボード添付のサンプル ソフトの期間に合わせる。

- 要件(2): 同期信号出力と RGB データ出力を、INI を High にする前に出力する:

RESB タイミングはボード上の FPGA で作成されている。

- 要件(3): RESB 信号は VCC (+3.3V) が安定した後に 20μs 期間以上 Low にする:

ONB を 6 に設定: RESB タイミングがボード上の FPGA で作成されているため、ボード添付のサンプルソフトの期間に合わせる。

- 要件(4): RESB は INI の前に High にする:

RESB タイミングはボード上の FPGA で作成されている。

## 【電源 OFF 時】

- 要件(5): INI を Low にしてから 5 フレーム期間後に同期信号停止・RGB データ停止・RESB を Low にする。 OFFE を 6 に設定する。

- 要件(6): TFT-LCD パネルの仕様上に規定は無いが、本応用例では OFFF を 1 に設定する。

図 12 パワーマネジメント設定例

# 4.3 参考プログラムの仕様

ここでは参考プログラムの仕様と各処理のフローチャートを説明します。

#### 4.3.1 仕様

- (1) 縦型 VGA サイズ (W480×H640) の TFT-LCD パネルへ、CPU により描画した赤・緑・青・グレースケール のグラデーション画像を交互に表示します。

- (2) LCDC を起動して 4 面のフレームバッファの面切り替えをしながら順番に表示した後、LCDC を停止します。

- (3)(2)の操作を無限ループします。

- (4) 面切り替えはソフトウェア切り替えで運用します。

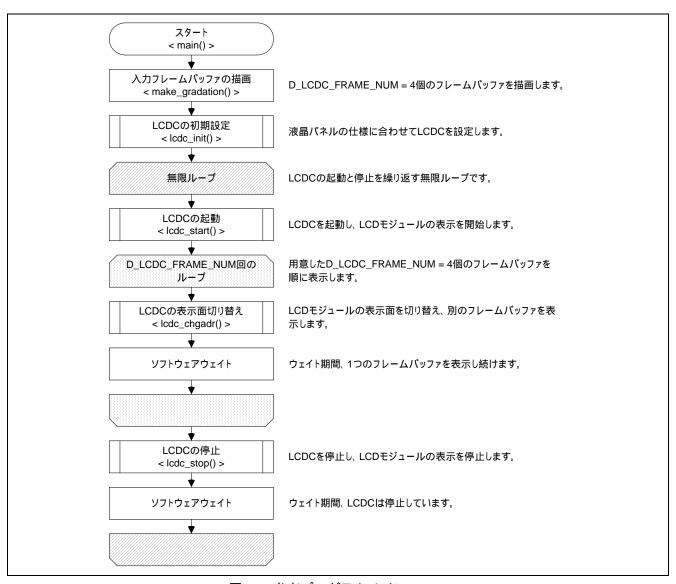

#### 4.3.2 参考プログラムメインフロー

図 13 に参考プログラムのメインフローを示します。

図 13 参考プログラムメインフロー

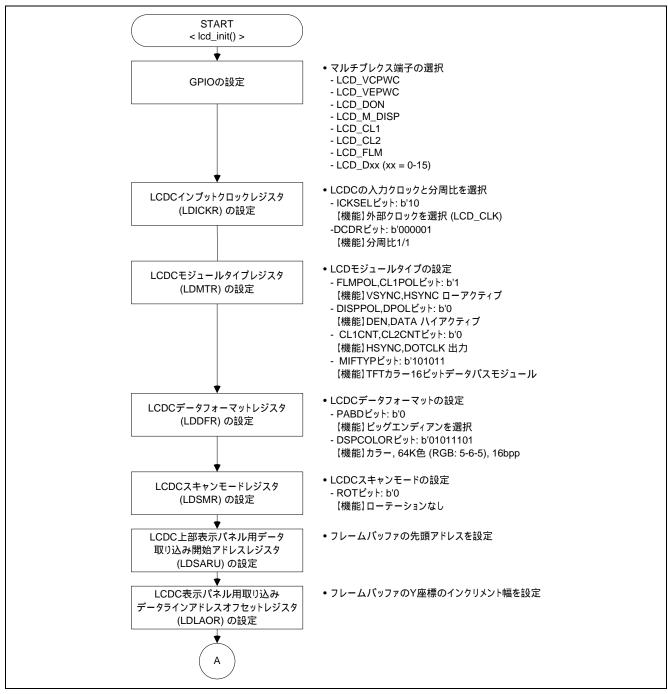

#### 4.3.3 LCDC の初期設定

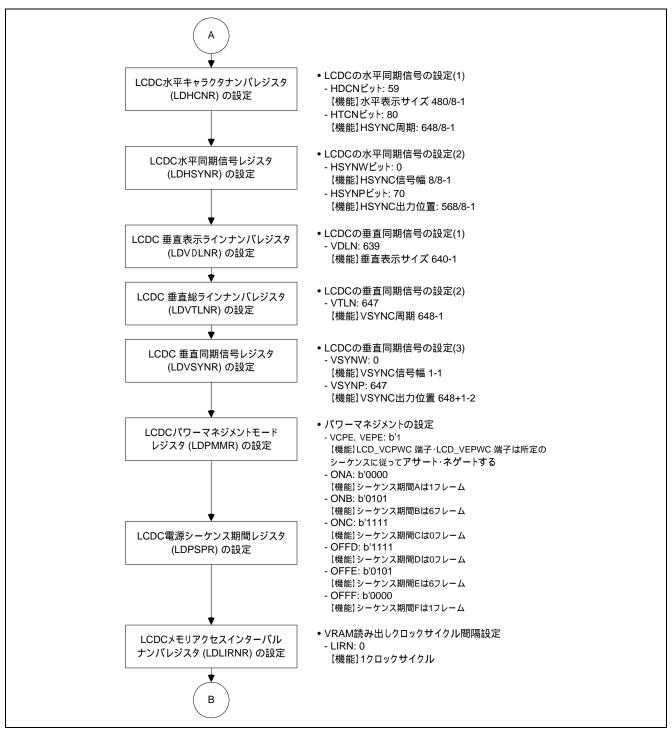

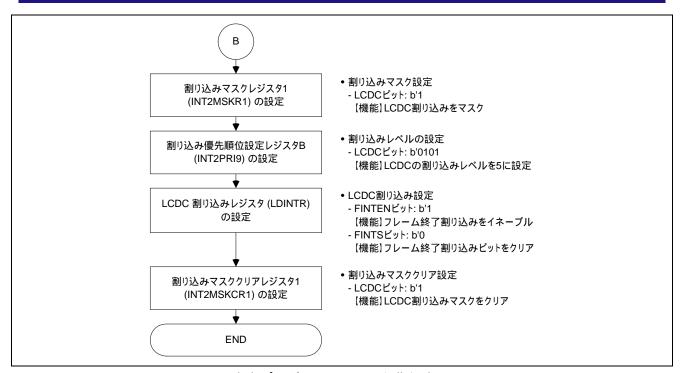

図 14~図 16に LCDC の初期設定フローを示します。

図 14 参考プログラム LCDC の初期設定フロー (1)

図 15 参考プログラム LCDC の初期設定フロー (2)

図 16 参考プログラム LCDC の初期設定フロー (3)

# 4.3.4 LCDC 表示開始・終了設定

図 17 に LCDC の表示開始フローを示します。

図 17 参考プログラム LCDC の起動フロー

図18にLCDC表示終了フローを示します。

図 18 参考プログラム LCDC の終了フロー

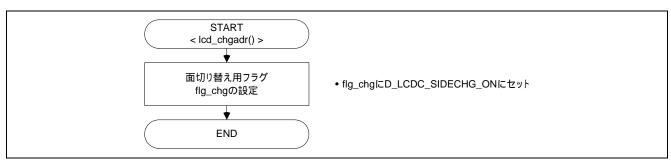

#### 4.3.5 LCDC 面切り替え設定

図 19 に LCDC の面切り替えフローを示します。本フローでは面切り替えフラグをセットします。LCDC への面切り替え設定はフレーム終了割り込み処理で行います。

図 19 参考プログラム LCDC の面切り替えフロー

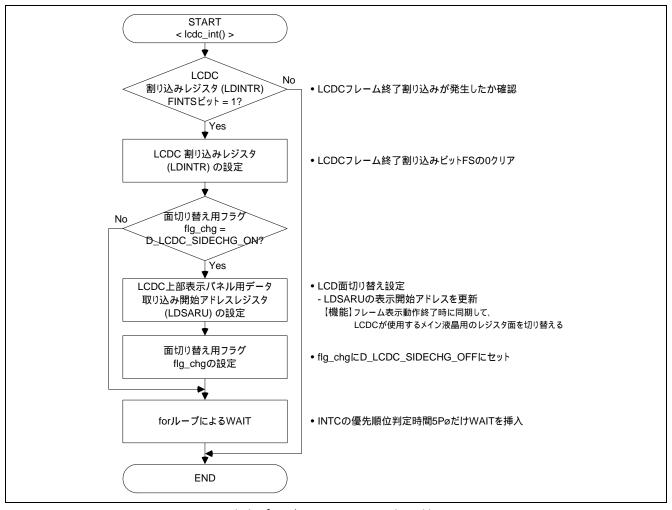

## 4.3.6 LCDC フレーム終了割り込み設定

図 20 に LCDC のフレーム終了割り込みを示します。面切り替えのフラグがセットされていれば、LCDC に面切り替えを設定します。実際の面切り替えは次のフレーム終了時に発生します。終了割り込みビット FINTS のクリアが INTC に反映されるよう、INTC の優先順位判定時間 ( $P\phi$ で 5 クロック) だけ WAIT を挿入します。

図 20 参考プログラム LCDC の面切り替えフロー

# 4.3.7 セクション配置

表 12 に本応用例での各セクション配置を示します。

# 表 12 セクション配置

| セクション名     | セクション用途               | 領域  | 配置アドレス (仮想アドレス) |                |  |

|------------|-----------------------|-----|-----------------|----------------|--|

| Р          | プログラム領域 (指定なしの場合)     | ROM | 0x00002000      | P0 領域          |  |

| С          | 定数領域                  | ROM |                 | (キャッシング可能 ,MMU |  |

| C\$BSEC    | 未初期化データ領域用アドレス構造体     | ROM |                 | アドレス変換可能)      |  |

| C\$DSEC    | 初期化データ領域用アドレス構造体      | ROM |                 |                |  |

| D          | 初期化データ (初期値)          | ROM |                 |                |  |

| В          | 未初期化データ領域             |     | 0x0800000       |                |  |

| R          | 初期化データ領域              | RAM |                 |                |  |

| S          | スタック領域                | RAM | 0x0FFFF9F0      |                |  |

| INTHandler | 例外/割り込みハンドラ           | ROM | 0x80000400      | P1 領域          |  |

| VECTTBL    | リセットベクタテーブル           | ROM |                 | (キャッシング可能 ,MMU |  |

|            | 割り込みベクタテーブル           |     |                 | アドレス変換不可)      |  |

| INTTBL     | 割り込みマスクテーブル           | ROM |                 |                |  |

| PIntPRG    | 割り込み関数                | ROM |                 |                |  |

| SP_S       | TLB ミスハンドラ専用スタック      | RAM | 0x8FFFFDF0      |                |  |

| RSTHandler | リセットハンドラ              | ROM | 0xA0000000      | P2 領域          |  |

| PResetPRG  | リセットプログラム             | ROM |                 | (キャッシング不可 ,MMU |  |

| PnonCACHE  | プログラム領域 (キャッシュ無効アクセス) | ROM |                 | アドレス変換不可)      |  |

| B_LCD_BUFF | LCDC フレームバッファ         | RAM | 0xAE000000      |                |  |

# 5. 参考プログラム例

(1) サンプルプログラムリスト"main.c"

```

1

2

* DISCLAIMER

3

4

* This software is supplied by Renesas Electronics Corporation. and is only

5

* intended for use with Renesas products. No other uses are authorized.

6

* This software is owned by Renesas Electronics Corporation. and is protected under

* all applicable laws, including copyright laws.

8

9

* THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

10

11

* REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

* INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

12

13

* PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

* DISCLAIMED.

15

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

16

17

* TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

18

* FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

* FOR ANY REASON RELATED TO THE THIS SOFTWARE, EVEN IF RENESAS OR ITS

* AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

2.0

21

2.2

\mbox{\ensuremath{^{\star}}} Renesas reserves the right, without notice, to make changes to this

* software and to discontinue the availability of this software.

23

^{\star} By using this software, you agree to the additional terms and

2.4

25

* conditions found by accessing the following link:

* http://www.renesas.com/disclaimer

*************************

^{\prime *} Copyright (C) 2010. Renesas Electronics Corporation., All Rights Reserved. ^{*\prime}

/*""FILE COMMENT""******* Technical reference data ************

29

30

* System Name : SH7763 Sample Program

31

* File Name

: main.c

* Abstract

: SH7763 LCDC の表示例

32

* Version

: Ver 1.00

33

* Device

: SH7763

34

* Tool-Chain : High-performance Embedded Workshop (Version 4.05.01.001)

35

36

: C/C++ Compiler Package for SuperH Family (V.9.03 release00)

* OS

37

: None

* H/W Platform : MS7763SE02

* Description : SH7763 LCDC の表示例

39

40

* Operation

41

42

* Limitation :

43

******************

44

* History : 08.July.2010 Ver. 1.00 First Release

45

46

47

48

#include <machine.h>

49

#include "iodefine.h"

#include "lcdc.h"

#include "framebuf.h"

/* ==== プロトタイプ宣言 ==== */

54

void main(void);

55

56

57

* ID

58

* Outline

: サンプルプログラムメイン

59

```

```

(LCDC の表示)

60

* Include

61

62

* Declaration

: void main(void)

* Description

: メイン LCD に VGA 画像を表示し、(LCDC_WAIT_CHGSIDE)のソフトウェイト後に

63

: 表示画面の切り替えを繰り返した後、表示を停止します。

64

65

: (LCDC_WAIT_STOP)のソフトウェイト後に表示を再開します。

66

* Limitation

67

68

* Argument

: none

69

* Return Value

70

: none

* Calling Functions

71

72

73

void main(void)

74

75

unsigned long j;

76

77

/* フレームバッファに画像を描画 */

make_gradation();

79

/* LCDC 初期設定:メイン LCD VGA 表示 */

80

81

lcdc_init();

82

8.3

while(1)

84

/* LCDC の起動:メイン LCD 表示開始 */

85

lcdc_start();

86

87

88

for(g_tbl_num=0;g_tbl_num<D_LCDC_FRAME_NUM;g_tbl_num++)</pre>

89

90

91

/* LCDC の表示面切り替え */

92

lcdc_chgadr();

93

/* ウェイト */

94

for(j=0;j<D_LCDC_WAIT_CHGSIDE;j++)</pre>

95

96

97

98

99

/* LCDC の停止:メイン LCD 表示停止 */

100

101

lcdc_stop();

102

/* ウェイト */

103

104

for(j=0;j<D_LCDC_WAIT_STOP;j++)</pre>

105

106

107

}

108

109

110

111

112

113

/* End of File */

```

#### (2) サンプルプログラムリスト"framebuf.c"

```

1

* DISCLAIMER

2

3

4

* This software is supplied by Renesas Electronics Corporation. and is only

* intended for use with Renesas products. No other uses are authorized.

5

6

7

* This software is owned by Renesas Electronics Corporation. and is protected under

8

* all applicable laws, including copyright laws.

9

* THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

10

* REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

11

* INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

12

13

* PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14

* DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

* TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

* FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

* FOR ANY REASON RELATED TO THE THIS SOFTWARE, EVEN IF RENESAS OR ITS

20

* AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21

22

* Renesas reserves the right, without notice, to make changes to this

23

* software and to discontinue the availability of this software.

\ensuremath{^{\star}} By using this software, you agree to the additional terms and

2.4

25

* conditions found by accessing the following link:

26

* http://www.renesas.com/disclaimer

************************

/* Copyright (C) 2010. Renesas Electronics Corporation., All Rights Reserved. */

29

/*""FILE COMMENT""******* Technical reference data **********

* System Name : SH7763 Sample Program

* File Name

31

: framebuf.c

: SH7763 LCDC の表示例

* Abstract

32

* Version

: Ver 1.00

33

* Device

: SH7763

34

* Tool-Chain : High-performance Embedded Workshop (Version 4.05.01.001)

35

36

: C/C++ Compiler Package for SuperH Family (V.9.03 release00)

* OS

: None

37

* H/W Platform : MS7763SE02

38

39

* Description : SH7763 LCDC の表示例

40

* Operation :

41

* Limitation :

42

43

*********************

44

* History : 08.July.2010 Ver. 1.00 First Release

45

46

47

48

49

#include <machine.h>

50

#include "iodefine.h"

51

#include "framebuf.h"

52

53

unsigned long g_tbl_num = 0;

/* ==== フレームバッファ ==== */

55

#pragma section _LCD_BUFF

56

57

unsigned short lcdc_buf0[D_LCDC_HEIGHT][D_LCDC_WIDTH];

58

unsigned short lcdc_buf1[D_LCDC_HEIGHT][D_LCDC_WIDTH];

59

unsigned short lcdc_buf2[D_LCDC_HEIGHT][D_LCDC_WIDTH];

unsigned \ short \ lcdc\_buf3[D\_LCDC\_HEIGHT][D\_LCDC\_WIDTH];\\

60

61

#pragma section

62

```

```

/* ==== フレームバッファテーブル ==== */

63

void* tbl_lcdc_buf[4] = {

64

lcdc_buf0,

65

66

lcdc_buf1,

lcdc_buf2,

67

lcdc_buf3

69

70

/* ==== プロトタイプ宣言 ==== */

71

72

void make_gradation(void);

73

74

75

76

* ID

: サンプルプログラムメイン

77

* Outline

78

: ( LCDC の表示)

* Include

79

* Declaration

: void make_gradation(void)

80

: フレームバッファに RGB565 16bpp のグラデーション画像を描画します

* Description

81

82

83

* Limitation

84

* Argument

85

: none

* Return Value

86

: none

* Calling Functions

87

88

89

void make_gradation(void)

90

91

static unsigned long i;

static unsigned long j;

unsigned short pixel0 = 0;

unsigned short pixel1 = 0;

95

unsigned short pixel2 = 0;

96

unsigned short pixel3 = 0;

97

98

for(i=0;i<D_LCDC_HEIGHT;i++)</pre>

99

for(j=0;j<D_LCDC_WIDTH;j++)</pre>

100

101

102

lcdc_buf0[i][j] = pixel0;

103

lcdc_buf1[i][j] = pixel1;

104

lcdc_buf2[i][j] = pixel2;

105

lcdc_buf3[i][j] = pixel3;

106

107

if((j!=0)\&\&((j\%60)==0))

108

109

pixel0 += D_LCDC_PATTERN0;

110

pixel1 += D_LCDC_PATTERN1;

111

pixel2 += D_LCDC_PATTERN2;

112

pixel3 += D_LCDC_PATTERN3;

113

114

}

pixel0 = 0;

115

116

pixel1 = 0;

117

pixel2 = 0;

118

pixel3 = 0;

119

120

121

122

/* End of File */

123

```

#### (3) サンプルプログラムリスト"framebuf.h"

```

1

* DISCLAIMER

2

3

4

* This software is supplied by Renesas Electronics Corporation. and is only

* intended for use with Renesas products. No other uses are authorized.

5

6

7

* This software is owned by Renesas Electronics Corporation. and is protected under

8

* all applicable laws, including copyright laws.

9

* THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

10

* REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

11

* INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

12

13

* PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14

* DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

* TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

* FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

* FOR ANY REASON RELATED TO THE THIS SOFTWARE, EVEN IF RENESAS OR ITS

20

* AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21

22

* Renesas reserves the right, without notice, to make changes to this

23

* software and to discontinue the availability of this software.

\ensuremath{^{\star}} By using this software, you agree to the additional terms and

2.4

25

* conditions found by accessing the following link:

26

* http://www.renesas.com/disclaimer

************************

/* Copyright (C) 2010. Renesas Electronics Corporation., All Rights Reserved. */

29

/*""FILE COMMENT""******* Technical reference data **********

* System Name : SH7763 Sample Program

* File Name

31

: framebuf.h

: SH7763 LCDC の表示例

* Abstract

32

: Ver 1.00

* Version

33

* Device

: SH7763

34

* Tool-Chain : High-performance Embedded Workshop (Version 4.05.01.001)

35

36

: C/C++ Compiler Package for SuperH Family (V.9.03 release00)

: None

* OS

37

* H/W Platform : MS7763SE02

38

39

* Description : SH7763 LCDC の表示例

40

* Operation :

41

* Limitation :

42

43

*********************

44

* History : 08.July.2010 Ver. 1.00 First Release

45

46

47

48

#ifndef _FRAMEBUF_H_

#define _FRAMEBUF_H_

49

50

51

/* ==== マクロ定義 ==== */

52

#define D_LCDC_FRAME_NUM

53

#define D_LCDC_WIDTH

480 /* 画像横幅 */

54

#define D_LCDC_HEIGHT

640 /* 画像縦幅 */

55

56

57

#define D_LCDC_PATTERN0 0x2000

58

#define D_LCDC_PATTERN1 0x0100

59

#define D_LCDC_PATTERN2 0x0004

60

#define D_LCDC_PATTERN3 0x2104

61

/* ==== フレームバッファ ==== */

62

```

```

63  extern void* tbl_lcdc_buf[D_LCDC_FRAME_NUM];

64

65    /* ==== 変数宣言 ==== */

66    extern unsigned long g_tbl_num;

67

68    #endif /* _FRAMEBUF_H_ */

69    /* End of File */

```

#### (4) サンプルプログラムリスト"lcdc.c"

```

1

* DISCLAIMER

2

3

* This software is supplied by Renesas Electronics Corporation. and is only

* intended for use with Renesas products. No other uses are authorized.

5

7

* This software is owned by Renesas Electronics Corporation. and is protected under

8

* all applicable laws, including copyright laws.

9

* THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

10

* REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

11

* INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

12

13

* PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14

* DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

* TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

* FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

* FOR ANY REASON RELATED TO THE THIS SOFTWARE, EVEN IF RENESAS OR ITS

20

* AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21

22

* Renesas reserves the right, without notice, to make changes to this

23

* software and to discontinue the availability of this software.

\ensuremath{^{\star}} By using this software, you agree to the additional terms and

2.4

25

* conditions found by accessing the following link:

26

* http://www.renesas.com/disclaimer

************************

/* Copyright (C) 2010. Renesas Electronics Corporation., All Rights Reserved. */

29

/*""FILE COMMENT""******* Technical reference data **********

* System Name : SH7763 Sample Program

31

* File Name

: lcdc.c

: SH7763 LCDC の表示例

* Abstract

32

: Ver 1.00

* Version

33

* Device

: SH7763

34

* Tool-Chain : High-performance Embedded Workshop (Version 4.05.01.001)

35

36

: C/C++ Compiler Package for SuperH Family (V.9.03 release00)

: None

* OS

37

* H/W Platform : MS7763SE02

38

39

* Description : SH7763 LCDC の表示例

40

* Operation :

41

* Limitation :

42

43

*******************

44

* History : 08.July.2010 Ver. 1.00 First Release

45

46

47

48

#include <machine.h>

49

50

#include "iodefine.h"

51

#include "lcdc.h"

52

#include "framebuf.h"

53

54

55

long g_flg_chg = D_LCDC_SIDECHG_OFF;

56

57

58

* ID

59

* Outline

: サンプルプログラムメイン

60

: (LCDC の表示)

61

* Include

62

```

```

63

* Declaration

: void lcdc_init(void)

64

* Description

: LCDC を初期化します。

65

: メイン LCD を表示可能な状態にします。

66

67

68

* Limitation

69

70

* Argument

71

* Return Value

72

: none

* Calling Functions

73

74

void lcdc_init()

75

76

77

unsigned long dummy;

78

/* GPIO の設定 */

79

/* ---- ピンセレクトレジスタ ---- */

80

81

GPIO.PSEL2.BIT.PTSEL25 = 0;

GPIO.PSEL2.BIT.PTSEL24 = 0;

83

GPIO.PSEL2.BIT.PTSEL22 = 0;

84

GPIO.PSEL3.BIT.PTSEL33 = 0;

85

GPIO.PSEL3.BIT.PTSEL31 = 0;

GPIO.PSEL3.BIT.PTSEL30 = 0;

86

87

/* ---- ポートコントロールレジスタ --- */

88

GPIO.PICR.BIT.PI5MD = 0;

89

GPIO.PJCR.WORD = 0 \times 0000;

90

91

GPIO.PKCR.WORD = 0 \times 0000;

92

GPIO.PLCR.WORD = 0 \times 0000;

93

94

/* ---- クロック選択、分周比設定 ---- */

95

LCDC.LDICKR.WORD = 0x2101;

/* bit13:12(ICKSEL)=01 LCD_CLK(外部端子)使用 */

96

/* bit5:0(DCDR)=000001 分周比 1/1 */

97

98

/* ---- 端子極性選択 ---- */

99

LCDC.LDMTR.WORD = 0xC42B;

100

/* bit15(FLMPOL)=1

Vsync は"L"アクティブ */

101

/* bit14(CL1POL)=1

Hsync は"L"アクティブ */

102

/* bit13(DISPPOL)=0

DEN は"H"アクティブ */

103

/* bit12(DPOL)=0

DATA は"H"アクティブ */

104

/* bit10(MCNT)=1

м 信号は出力しない */

/* bit9(CL1CNT)=0

垂直期間中、Hsync 出力 */

106

107

/* bit8(CL2CNT)=0

垂直期間中、DotCLK 出力 */

108

109

/* ---- データフォーマット設定 ---- */

110

111

LCDC.LDDFR.WORD = 0 \times 0.02D;

/* bit8(PABD)=0

ビックエンディアン */

112

/* bit6:0(DSPCOLOR)=0101101 64k-Color RGB:5-6-5 */

113

114

115

/* ---- スキャンモード設定 ---- */

116

LCDC.LDSMR.WORD = 0 \times 0000;

117

/* ローテーションなし */

118

119

/* 外部メモリからの画像の読み出し設定 ----*/

120

LCDC.LDSARU = (void *)(unsigned long )tbl_lcdc_buf[0];

121

/* ---- ラインオフセット設定 ----*/

122

LCDC.LDLAOR = LINE_OFFSET * DATA_FORMAT;

123

124

/* ---- 水平方向表示キャラクタ、総キャラクタ設定 ---- */

125

LCDC.LDHCNR.BIT.HDCN = (TFT_PANEL_CLOCK / 8) - 1;

126

```

```

LCDC.LDHCNR.BIT.HTCN = (TFT_TOTAL_CLOCK / 8) - 1;

127

128

129

/* ---- 垂直方向表示ライン、総ライン数設定 ---- */

130

LCDC.LDVDLNR.BIT.VDLN = TFT_PANEL_LINE - 1;

131

LCDC.LDVTLNR.BIT.VTLN = TFT_TOTAL_LINE - 1;

/* ---- 水平、垂直同期信号タイミング設定 ---- */

134

LCDC.LDHSYNR.BIT.HSYNW = (TFT_HSYNC_WIDTH / 8) - 1;

135

LCDC.LDHSYNR.BIT.HSYNP = (TFT_HSYNC_START / 8) - 1;

LCDC.LDVSYNR.BIT.VSYNW = TFT_VSYNC_WIDTH - 1;

136

LCDC.LDVSYNR.BIT.VSYNP = (TFT_TOTAL_LINE - TFT_VSYNC_WIDTH) - 2;

137

138

/* ---- 電源制御端子設定 ---- */

139

I.CDC.I.DPMMR.WORD = 0xFF60;

140

/* bit[15:12](ONC) = 1111 ONC;0xVSYNC */

141

/* bit[11:8](OFFD) = 1111 OFFD;0xVSYNC */

142

/* bit[6](VCPE) = 1 LCD_VCPWC 端子使用 */

143

/* bit[5](VEPE) = 1

LCD_VEPWC 端子使用 */

LCDC.LDPSPR.WORD = 0 \times 0550;

145

/* bit[15:12](ONA) = 0000 ONA;1xVSYNC */

147

/* bit[11:8](ONB) = 0101 ONB;6xVSYNC */

148

/* bit[3:0](OFFF) = 0000 OFFF;1xVSYNC */

149

150

/* ---- VRAM 読み出しクロックサイクル間隔設定 ---- */

151

LCDC.LDLIRNR.WORD = 0 \times 0000;

152

153

/* 割り込みの設定 */

154

/* LCDC の割り込みをマスク */

INTC.INT2MSKR1.BIT._LCDC = 1;

/* LCDC の割り込み優先順位を設定 */

INTC.INT2PRI9.BIT._LCDC = 5;

159

/* LCDC モジュールの割り込み設定 */

LCDC.LDINTR.WORD = D_LCDC_INT_ON;

/* LCDC モジュールの割り込み要因クリア */

161

LCDC.LDINTR.WORD &= ~D_LCDC_INT_FLG;

162

/* LCDC の割り込みマスクをクリア */

163

INTC.INT2MSKCR1.BIT._LCDC = 1;

164

165

166

}

167

/*""FUNC COMMENT""*******************************

168

* ID

169

170 * Outline

: サンプルプログラムメイン

171

: (LCDC の表示)

172 * Include

173

* Declaration

: void lcdc_start(void)

174

* Description

: LCDC を起動します。

175

* Limitation

176

177

* Argument

178

: none

179

* Return Value

: none

180

* Calling Functions

181

182

void lcdc_start(void)

183

184

/* ---- LCDC 表示動作開始 ---- */

185

LCDC.LDCNTR = 0 \times 0011;

/* bit[4](DON2) = 1 LCDC 表示動作開始 */

186

/* bit[0](DON) = 1 表示オンモード */

187

188

/* ステータスが表示中になるまで待つ */

189

190

while( LCDC.LDPMMR.BIT.LPS != 3 )

```

```

191

192

/* DO NOTHING */

193

}

}

194

196

* ID

:

: サンプルプログラムメイン

: / rong の表示 )

* Outline

198

: (LCDC の表示)

199

* Include

200

: void lcdc_chgadr(void)

: LCDC の画面切り替えフラグをセット。

* Declaration

201

202 * Description

203

204 * Limitation

205

206 * Argument

: none

207 * Return Value

: none

208 * Calling Functions

210 void lcdc_chgadr(void)

211 {

/* 表示開始アドレス変更のタイミングフラグ ON */

212

213

g_flg_chg = D_LCDC_SIDECHG_ON;

214

215

/*""FUNC COMMENT""********************************

216

* ID

217

: サンプルプログラムメイン

* Outline

218

219

: (LCDC の表示)

* Include

* Declaration

: void lcdc_stop(void)

: LCDC を停止します。

221

* Description

222

223

* Limitation

224

225

* Argument

: none

226

* Return Value

: none

2.2.7

228 * Calling Functions

230 void lcdc_stop(void)

231 {

/* ---- LCDC 表示動作終了 ---- */

232

LCDC.LDCNTR = 0 \times 0000;

233

234

/* bit[0](DON) = 0 表示オフモード */

235

/* ステータスが停止になるまで待つ */

236

237

while( LCDC.LDPMMR.BIT.LPS != 0 )

238

239

/* DO NOTHING */

}

240

241

242

243 /* End of File */

```

#### (5) サンプルプログラムリスト"lcdc.h"

```

1

* DISCLAIMER

2

3

4

* This software is supplied by Renesas Electronics Corporation. and is only

* intended for use with Renesas products. No other uses are authorized.

5

6

7

* This software is owned by Renesas Electronics Corporation. and is protected under

8

* all applicable laws, including copyright laws.

9

* THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

10

* REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

11

* INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

12

13

* PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14

* DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

* TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

* FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

* FOR ANY REASON RELATED TO THE THIS SOFTWARE, EVEN IF RENESAS OR ITS

20

* AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21

22

* Renesas reserves the right, without notice, to make changes to this

23

* software and to discontinue the availability of this software.

\ensuremath{^{\star}} By using this software, you agree to the additional terms and

2.4

25

* conditions found by accessing the following link:

26

* http://www.renesas.com/disclaimer

************************

/* Copyright (C) 2010. Renesas Electronics Corporation., All Rights Reserved. */

29

/*""FILE COMMENT""******* Technical reference data **********

* System Name : SH7763 Sample Program

* File Name

31

: lcdc.h

: SH7763 LCDC の表示例

* Abstract

32

* Version

: Ver 1.00

33

* Device

: SH7763

34

* Tool-Chain : High-performance Embedded Workshop (Version 4.05.01.001)

35

36

: C/C++ Compiler Package for SuperH Family (V.9.03 release00)

: None

* OS

37

* H/W Platform : MS7763SE02

38

39

* Description : SH7763 LCDC の表示例

40

* Operation :

41

* Limitation :

42

43

*********************

44

* History : 08.July.2010 Ver. 1.00 First Release

45

46

47

48

#ifndef _LCDC_H_

#define _LCDC_H_

49

50

51

/* ==== マクロ定義 ==== */

/* ---- TFT 液晶表示モジュール ---- */

52

/* 帰線期間を含む幅

TFT_TOTAL_CLOCK 648

53

#define

TFT_TOTAL_LINE

/* 帰線期間を含む高さ

#define

648

54

#define

480

/* 水平方向の画素数

55

TFT PANEL CLOCK

TFT_PANEL_LINE 640

/* 垂直方向の画素数

#define

56

TFT_H_FRONT_PORCH 88

/* 水平フロントポーチ

57

#define

TFT_HSYNC_START

58

#define

(TFT_PANEL_CLOCK + TFT_H_FRONT_PORCH)

/* 水平方向の表示開始位置 */

59

60

#define

TFT_HSYNC_WIDTH

/* Hsync のパルス幅(min = 8dot) */

8

1

/* Vsync のパルス幅 */

61

#define

TFT VSYNC WIDTH

480 /* ラインオフセット */

62

#define

LINE_OFFSET

```

```

#define

/* 表示データサイズ(バイト) */

63

DATA_FORMAT

64

/* ---- ウェイト時間設定 ---- */

65

#define D_LCDC_WAIT_CHGSIDE

(266000000/2*1) /* 周波数÷(for ループの命令数)×秒 */

66

67

#define D_LCDC_WAIT_STOP

(266000000/2*1) /* 周波数÷(for ループの命令数)×秒 */

/* ---- LCDC 割り込み ---- */

69

#define D_LCDC_INT_ON 0x4000

70

71

#define D_LCDC_INT_FLG 0x0400

72

73

enum {

D_LCDC_SIDECHG_OFF = 0,

74

75

D_LCDC_SIDECHG_ON,

76

};

77

/* ==== 関数宣言 ==== */

78

79

void lcdc_init(void);

80

void lcdc_start(void);

81

void lcdc_chgadr(void);

82

void lcdc_stop(void);

83

void lcdc_int(void);

84

/* ==== 変数宣言 ==== */

85

extern long g_flg_chg;

86

87

#endif /* _LCDC_H_ */

88

89

/* End of File */

```

# (6) サンプルプログラムリスト"intprg.c"

```

1

* DISCLAIMER

2

3

* This software is supplied by Renesas Electronics Corporation. and is only

* intended for use with Renesas products. No other uses are authorized.

5

7

* This software is owned by Renesas Electronics Corporation. and is protected under

8

* all applicable laws, including copyright laws.

9

* THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

10

* REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

11

* INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

12

13

* PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14

* DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

* TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

* FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

* FOR ANY REASON RELATED TO THE THIS SOFTWARE, EVEN IF RENESAS OR ITS

20

* AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21

22

* Renesas reserves the right, without notice, to make changes to this

23

* software and to discontinue the availability of this software.

\ensuremath{^{\star}} By using this software, you agree to the additional terms and

2.4

* conditions found by accessing the following link:

26

* http://www.renesas.com/disclaimer

************************

/* Copyright (C) 2010. Renesas Electronics Corporation., All Rights Reserved. */

/*""FILE COMMENT""******* Technical reference data **********

* System Name : SH7763 Sample Program

* File Name

31

: intprq.c

: SH7763 LCDC の表示例

* Abstract

32

: Ver 1.00

* Version

33

* Device

: SH7763

34

* Tool-Chain : High-performance Embedded Workshop (Version 4.05.01.001)

35

36

: C/C++ Compiler Package for SuperH Family (V.9.03 release00)

: None

* OS

37

* H/W Platform : MS7763SE02

38

39

* Description : SH7763 LCDC の表示例

40

* Operation :

41

* Limitation :

42

43

*******************

44

* History : 08.July.2010 Ver. 1.00 First Release

45

46

47

#include <machine.h>

48

#include "iodefine.h"

49

50

#include "framebuf.h"

51

#include "lcdc.h"

53

#define I_DIV_P

4 /* Ick:Pck0 = 4:1 */

2 /* instruction number of for loop */

#define INST_NUM

#define PCLK_5CYC

( 5 * I_DIV_P / 2)

55

途中省略

```

```

/* H'620 LCDC */

255

/*""FUNC COMMENT""********************************

256

* ID

257

* Outline

: サンプルプログラムメイン

258

: (LCDC の表示)

259

* Include

260

: void INT_LCDCI(void)

: LCDC を初期化します。

* Declaration

261

* Description

262

: メイン LCD を表示可能な状態にします。

263

264

265

266

267 * Limitation

268

269 * Argument

: none

270 * Return Value

: none

271 * Calling Functions

void INT_LCDCI(void)

274

275

unsigned long i;

276

277

if( LCDC.LDINTR.WORD & D_LCDC_INT_FLG)

278

279

280

LCDC.LDINTR.WORD &= ~D_LCDC_INT_FLG;

281

282

if( g_flg_chg == D_LCDC_SIDECHG_ON )

283

284

LCDC.LDSARU = tbl_lcdc_buf[g_tbl_num]; /* 表示開始アドレスを更新 */

285

g_flg_chg = D_LCDC_SIDECHG_OFF;

286

287

/* INTC の優先順位判定時間だけ WAIT */

288

for(i=0;i<PCLK_5CYC;i++)</pre>

289

290

/* DO NOTHING */

291

292

}

293

}

294

}

以降省略

```

# 6. 実行結果

上記サンプルプログラムを実行すると、

- LCD モジュールの電源投入

- 赤のグラデーションパターン表示

- 緑のグラデーションパターン表示

- 青のグラデーションパターン表示

- グレーのグラデーションパターン表示

- LCD モジュールの電源遮断

- LCD モジュールの電源投入 (以降無限ループ)

が繰り返し実行されます。

# 7. 参考ドキュメント

- ソフトウェアマニュアル SH-4A ソフトウェアマニュアル (RJJ09B0090) (最新版をルネサス エレクトロニクスホームページから入手してください。)

- ハードウェアマニュアル SH7763 グループ ハードウェアマニュアル (RJJ09B0260) (最新版をルネサス エレクトロニクスホームページから入手してください。)

# ホームページとサポート窓口

ルネサス エレクトロニクスホームページ

http://japan.renesas.com/

## お問合せ先

http://japan.renesas.com/inquiry

すべての商標および登録商標は,それぞれの所有者に帰属します。

# 改訂記録

|      |            | 改訂内容 |      |  |

|------|------------|------|------|--|

| Rev. | 発行日        | ページ  | ポイント |  |

| 1.00 | 2010.10.27 | _    | 初版発行 |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

## 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の 記載が優先するものとします。

#### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

#### 2. 電源投入時の処置

【注意】電源投入時は,製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。 外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の 状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

#### 4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。

プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。 リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

# 5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、事前に問題ないことをご確認下さい。

同じグループのマイコンでも型名が違うと、内部メモリ、レイアウトパターンの相違などにより、特性が異なる場合があります。型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

# ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、 ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害 に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されて いる当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の 法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報 の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器

(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療

行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの) (厚生労働省定義の高度管理医療機器に相当) またはシステム等

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制するRoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関し て、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数を 直接または間接に保有する会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

■営業お問合せ窓口

http://www.renesas.com

※営業お問合せ窓口の住所・電話番号は変更になることがあります。最新情報につきましては、弊社ホームページをご覧ください。

ルネサス エレクトロニクス販売株式会社 〒100-0004 千代田区大手町2-6-2 (日本ビル)

(03)5201-5307

| 技術的なお問合せ | お | よび資料の        | ご請求は     | 下記へ      | : تع | 5  | ぞ。 |

|----------|---|--------------|----------|----------|------|----|----|

| 総合お問合せ窓口 | : | http://japar | renesas. | .com/ind | qui  | ry | 1  |